MYSON MTD502EG, MTD502EF Datasheet

without notice. No liability is assumed as a result of the use of this procuts. No rights under any patent accompany the sales o

MTD502EMYSON

GENERAL DESCRIPTION

IEEE802.3 and IEEE802.3u compliant.

A flexible MII interface design can directly con-

warding rate at full_wire speed.

supply voltage, 50 MHZ operation.

Provide 128 pin PQFP package (MTD502EF),

and 80 pin LQFP package (MTD502EG).

under half or full duplex mode.

(Am79c901, HomePNA PHY).

implemented in half duplex mode.

The MTD502E supports an effective

updating (aging time is 300 secs default).

Embedded Memory

TECHNOLOGY

2 Port 10M/100M Switch With Build_in Memory

FEATURES

•

• Single chip, low cost, two port switch controller.

• Build_in embedded memory on chip for packet

buffering.

• Provide 2 MII/RMII (Reduced Media Independent Interface) ports.

•

nect with standard MII or pseudo MII.

• Support half/full duplex operation per port.

• Optional back_pressure control for half_duplex

mode.

• Provide “store and forward” switching, and for-

• Support up to 2048 MAC addresses filtering

database, and automatical address aging_out

function (300 secs).

• Low power CMOS design, with single 3.3V

•

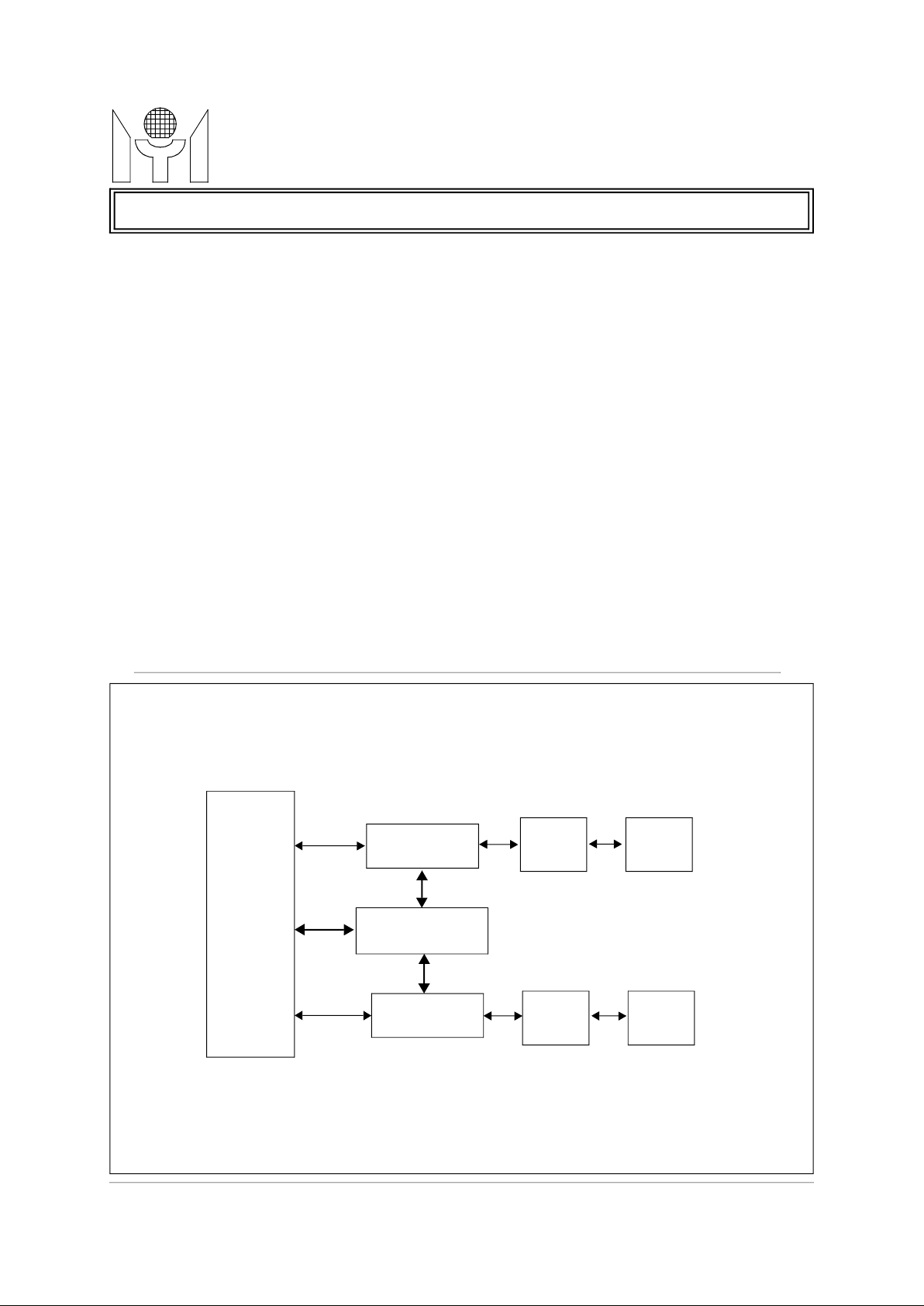

BL OCK DIAGRAM

The MTD502E is a highly integrated, 10M/

100M two port switch controller with build_in

embedded memory. It supports 2 MII/RMII ports

for 10M/100M operation, and both can operate

The MTD502E is an ideal solution for two

port bridge or dual speed hub application, and no

need any external memory buffers in application

design. The flexible MII interface design can

directly connect with pseudo MII interface

The MTD502E provides packet forwarding, address filtering, learning, and aging function, and have an optional back_presure control

address filtering database, which can recognize

up to 2048 MAC addresses. It also support an

automatical aging function for address table

Port0 DMA

Two

Port

Switch

Engine

Port1 DMA

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification

the product.

1/20 MTD502E Revision 1.3 12/07/2000

MAC0

MAC1

MII0

MII1

f

without notice. No liability is assumed as a result of the use of this procuts. No rights under any patent accompany the sales o

TECHNOLOGY

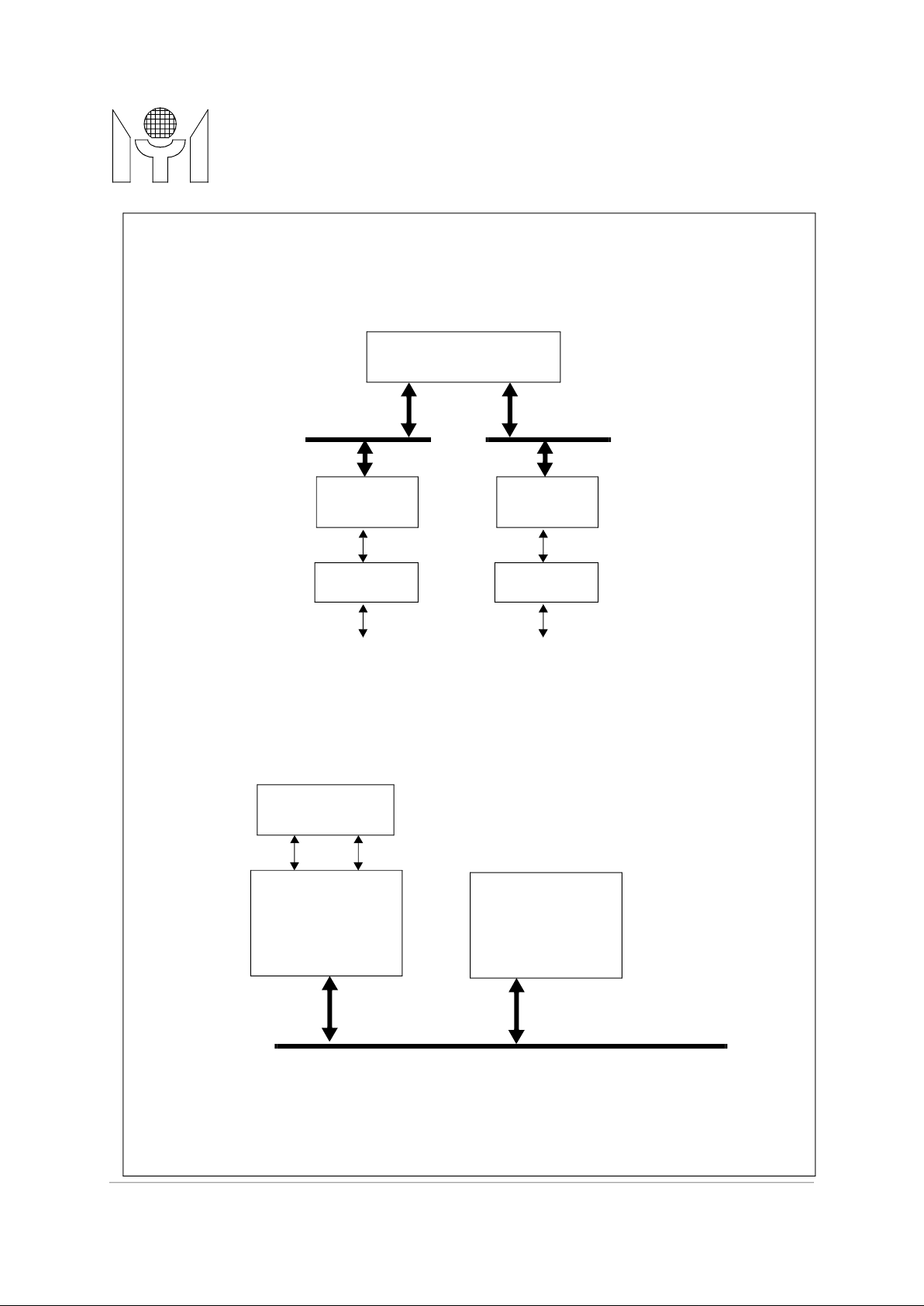

SYSTEM DIAGRAM

2). Dual Speed Hub Appl i c ati on

Transform er

(With out 2P_sw)

1). Two Port Swit c h App l i c atio n (HomePNA to LA N)

MTD502E

MTD502EMYSON

MII1

HomePNA

Transform er

RJ11

MTD502E

MII0

10M/100M

PHYsceiverPHYsceiver

RJ45

10M/100M

Repeater

(With out 2P_sw)

10M/100M

Repeater

.......

Expansion Bus

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification

the product.E

2/20 MTD502E Revision 1.3 12/07/2000

f

MTD502E Revision 1.3 12/07/2000

TECHNOLOGY

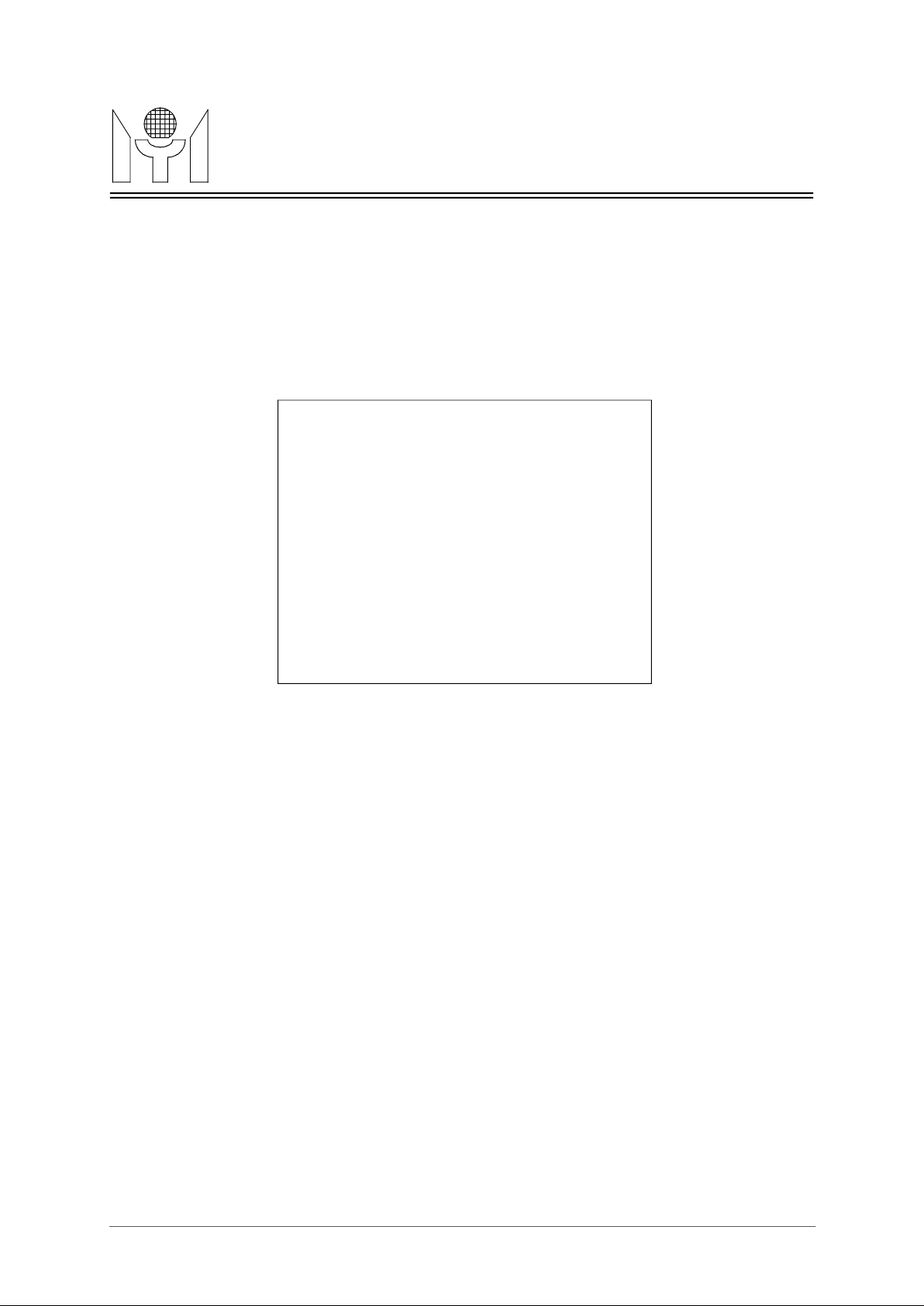

MT D502EF

1.0 PIN CONNECTION (under MII mode)

1) 128 Pin PQFP (MTD502EF)

NCNCNCNCLNKRX0_LED

LNKRX1_LED

LNKACT0_LED

LNKACT1_LED

FDCOL0_LED

FDCOL1_LED

GND

COL0_LED

COL1_LEDNCNCNCNCNCNCNCGNDNCNCNCNCNCNCNCGNDNCVCCNCNCNCNC

102

101

10099989796959493929190898887868584838281807978777675747372717069686766

VCC

NC

GND

NC

NC

NC

NC

NC

NC

NC

NC

CLK25OUT

NC

NC

GND

NC

NC

NC

VCC

SYSCLK

GND

NC

NC

NC

NC

RSTB

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

VCCNCNC

MTD502EMYSON

65

64

SPEED1

63

COL1

62

CRS1

61

RXDV1

60

GND

59

VCC

58

RXD1_3

57

RXD1_2

56

NC

55

NC

54

NC

53

FULL1

52

RXD1_1

51

RXD1_0

50

NC

49

NC

48

NC

47

RXC1

46

GND

45

VCC

44

NC

43

TXC1

42

TXEN1

41

TXD1_0

40

TXD1_1

39

NC

01020304050607080910111213141516171819202122232425262728293031323334353637

LINK0

TXD0_3

VCC

TXD0_2NCNCNCNC

TXD0_1

TXD0_0

TXEN0

TXC0NCGND

RXC0NCNCNCRXD0_0

RXD0_1

FULL0NCNCNCRXD0_2

RXD0_3

RXDV0

CRS0

COL0

SPEED0

VCC

GND

LINK1

TXD1_3

TXD1_2NCNC

38

NC

3/20

MTD502E Revision 1.3 12/07/2000

TECHNOLOGY

NCT

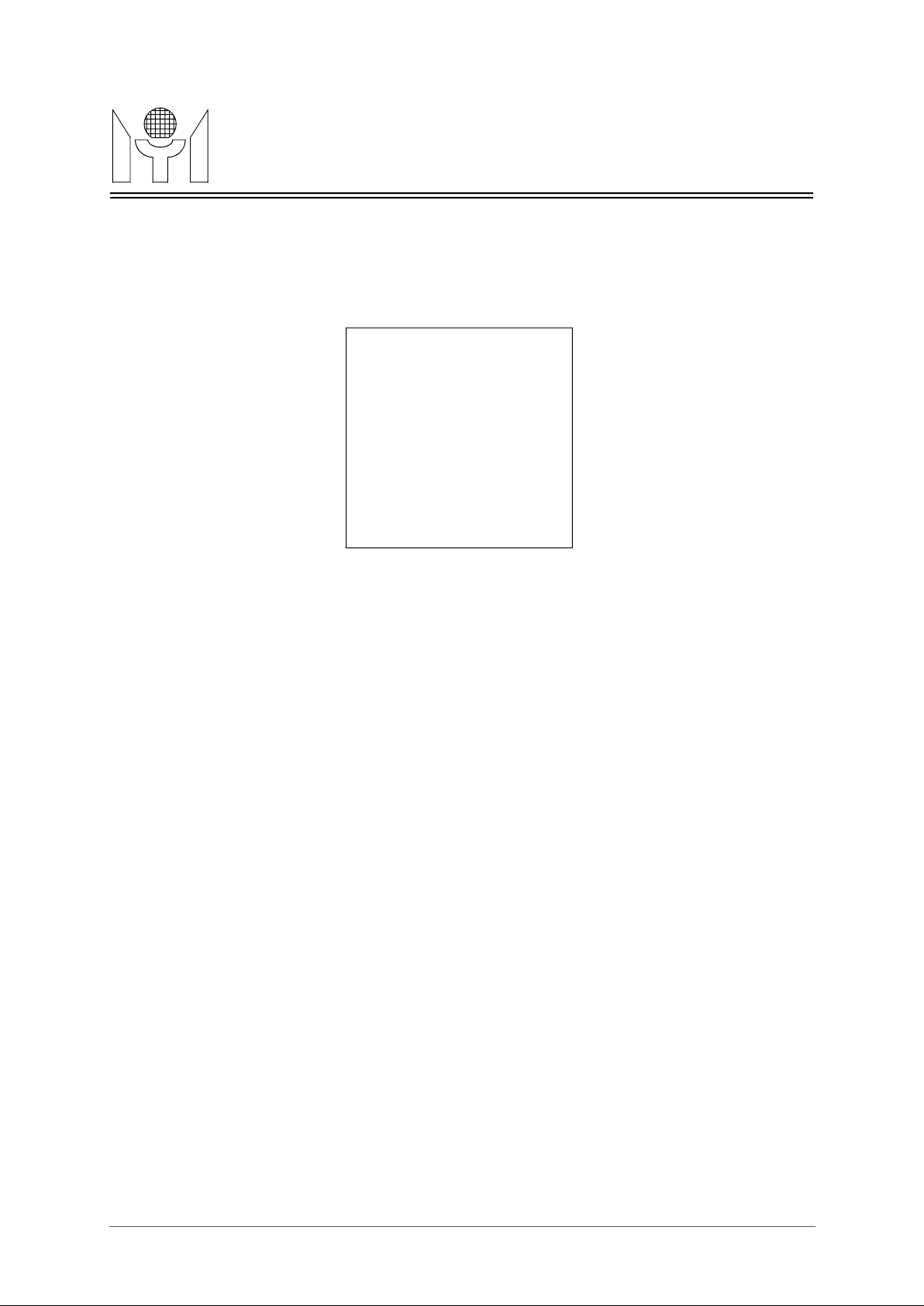

MT D502EG

2) 80 Pin LQFP (MTD502EG)

NCNCLNKRX0_LED

MTD502EMYSON

LNKRX1_LED

LNKACT0_LED

LNKACT1_LED

FDCOL0_LED

FDCOL1_LED

GND

GND

COL0_LED

COL1_LED

GND

GND

GND

GND

VCC

VCC

SPEED1

VCC

NC

VCC

NC

GND

NC

NC

NC

NC

NC

NC

NC

CLK25OUT

VCC

SYSCLK

NC

RSTB

LINK0

TXD0_3

VCC

TXD0_2

60595857565554535251504948474645444342

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

01020304050607080910111213141516171819

XD0_1TXD0_0TXEN0TXC0GNDRXC0NCNCNCRXD0_0RXD0_1FULL0NCRXD0_2RXD0_3RXDV0CRS0COL0SPEED0

41

40

COL1

39

CRS1

38

RXDV1

37

GND

36

VCC

35

RXD1_3

34

RXD1_2

33

NC

32

FULL1

31

RXD1_1

30

RXD1_0

29

RXC1

28

TXC1

27

TXEN1

26

TXD1_0

25

TXD1_1

24

NC

23

TXD1_2

22

TXD1_3

21

LINK1

20

4/20

MTD502E Revision 1.3 12/07/2000

TECHNOLOGY

Pin 1~32 for Port0, suitable for connecting with 10/

100PHY , RISC_CPU, Switch,....

Pin 33~64 for Port1, suitable for connecting with

HomePNA PHY.

2.0 PIN DESCRIPTIONS

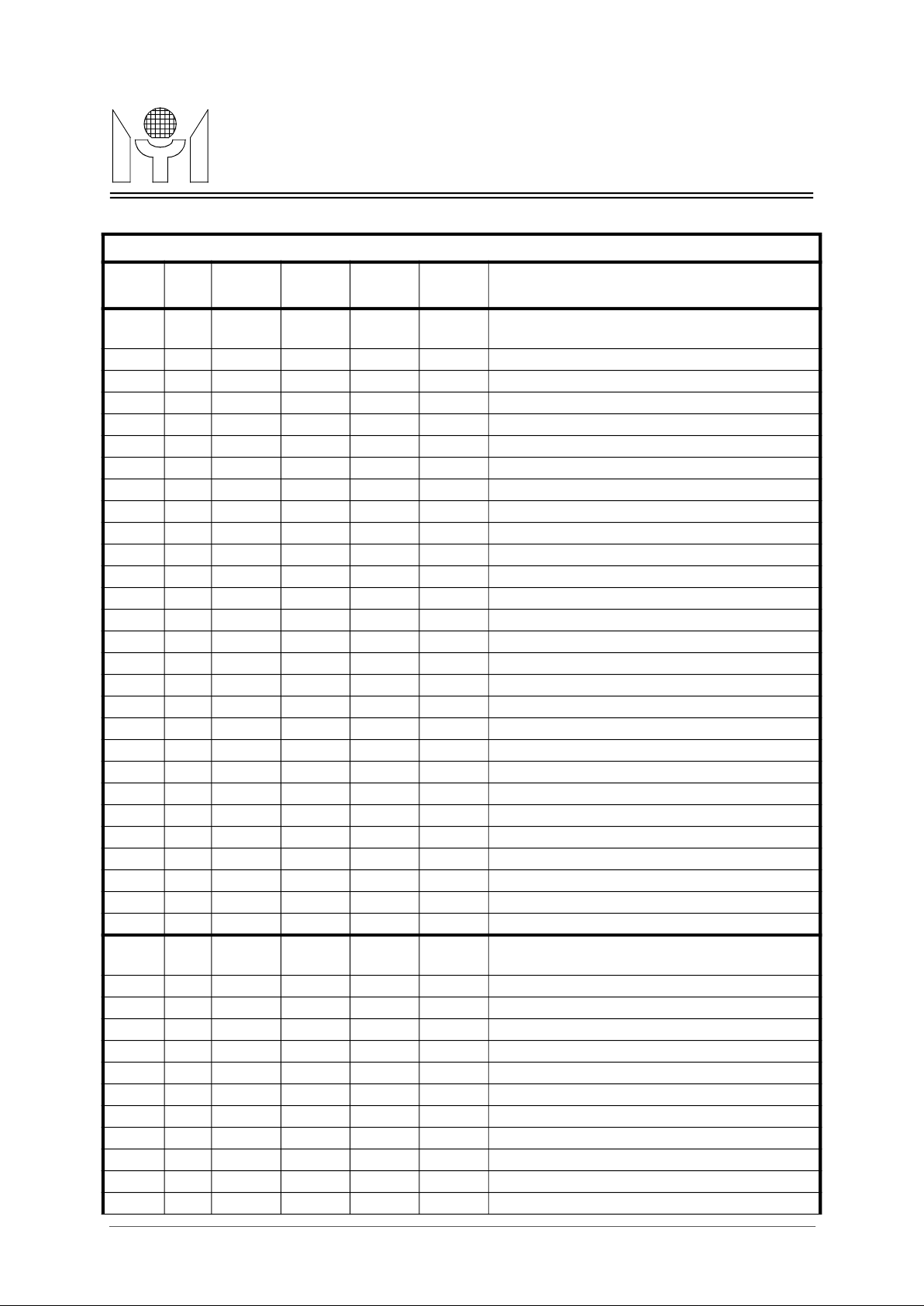

MTD502EF (128PQFP) Pin Defin i t i o n Mappin g Under Diff erent Conf i g u r ati o n s

MTD502EMYSON

Pin No. I/O

1 I LINK0 (NC) LINK0 (NC)

2 O TXD0_3 RXD0_3 (NC) (NC)

3 VCC

4 O TXD0_2 RXD0_2 (NC) (NC)

5 O (NC) CRS0 (NC) (NC)

6~8 I (NC) (NC) (NC) (NC)

9 O TXD0_1 RXD0_1 (NC) (NC)

10 O TXD0_0 RXD0_0 (NC) (NC)

11 O TXEN0 RXDV0 (NC) (NC)

12 I TXC0 (NC) (NC) (NC)

13 I (NC) (NC) (NC) (NC)

14 GND

15 I RXC0 (NC) CRSDV0 TXEN0

16 O (NC) RXC0 TXD0_1 RXD0_1

17 O (NC) COL0 TXD0_0 RXD0_0

18 O (NC) TXC0 TXEN0 CRSDV0

19 I RXD0_0 TXD0_0 RXD0_0 TXD0_0

20 I RXD0_1 TXD0_1 RXD0_1 TXD0_1

21 I FULL0 FULL0 FULL0 (NC)

22~24 O (NC) (NC) (NC) (NC)

25 I RXD0_2 TXD0_2 (NC) (NC)

26 I RXD0_3 TXD0_3 (NC) (NC)

27 I RX DV0 TXEN0 (NC) (NC)

28 I CRS0 SPEED0 SPEED0 (NC)

29 I COL0 (NC) (NC) (NC)

30 I SPEED0 (NC) (NC) (NC)

31 VCC

32 GND

33 I LINK1 (NC) LINK1 (NC)

MII

mode

Phy_MII

mode

Rmii

mode

Phy_Rm

ii mode

Descriptions

34 O TXD1_3 (NC) (NC) (NC)

35 O TXD1_2 (NC) (NC) (NC)

36 O (NC) (NC) (NC) (NC)

37,38 I (NC) (NC) (NC) (NC)

39 I (NC) (NC) CRSDV1 (NC)

40 O TXD1_1 (NC) TXD1_1 (NC)

41 O TXD1_0 (NC) TXD1_0 (NC)

42 O TXEN1 (NC) TXEN1 (NC)

43 I TXC1 (NC) RXD1_0 (NC)

44 I (NC) (NC) RXD1_1 (NC)

45 VCC

5/20

MTD502E Revision 1.3 12/07/2000

MTD502EMYSON

Port1: COL LED display, low_active. *

port1’s collision event.

Port0: COL LED display, low_active. *

port0’s collision event.

Port1: FULL/COL LED display, low_active. *

low_active.

TECHNOLOGY

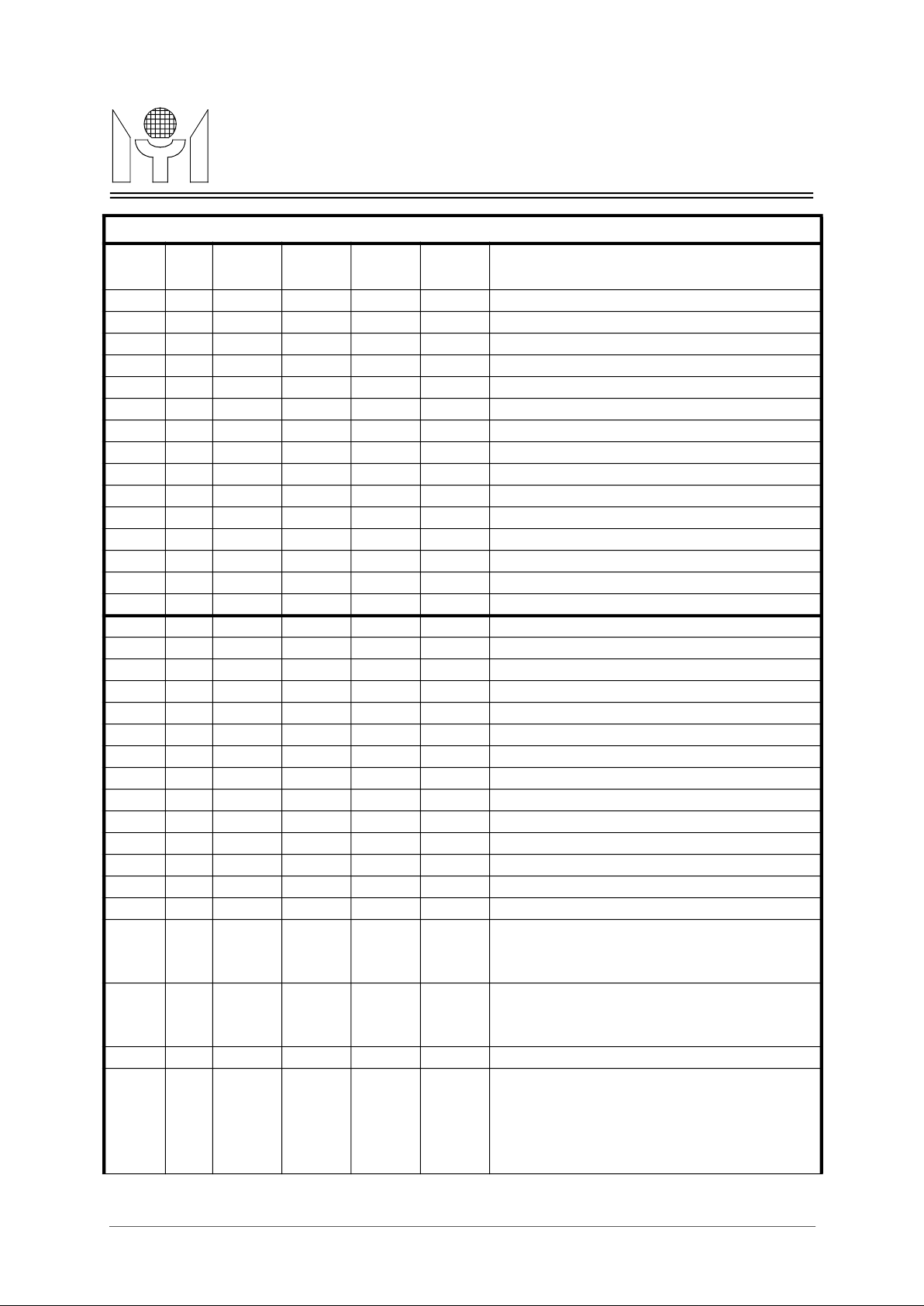

MTD502EF (128PQFP) Pin Defin i t i o n Mappin g Under Diff erent Conf i g u r ati o n s

Pin No. I/O

46 GND

47 I RXC1 (NC) FULL1 (NC)

48~50 O (NC) (NC) (NC) (NC)

51 I RXD1_0 (NC) (NC) (NC)

52 I RXD1_1 (NC) (NC) (NC)

53 I FULL1 (NC) SPEED1 (NC)

54~56 O (NC) (NC) (NC) (NC)

57 I RXD1_2 (NC) (NC) (NC)

58 I RXD1_3 (NC) (NC) (NC)

59 VCC

60 GND

61 I RXD V1 (NC) (NC) (NC)

62 I CRS1 (NC) (NC) (NC)

63 I COL1 (NC) (NC) (NC)

64 I SPEED1 (NC) (NC) (NC)

65~66 I (NC) (NC) (NC) (NC)

67 VCC *

68~71 IO (NC) (NC) (NC) (NC)

72 VCC

73 IO (NC) (NC) (NC) (NC)

74 GND

75,76 IO (NC) (NC) (NC) (NC)

77~79 I (NC) (NC) (NC) (NC)

80 O (NC) (NC) (NC) (NC)

81 IO (NC) (NC) (NC) (NC)

82 GND

83~85 IO (NC) (NC) (NC) (NC)

86~88 I (NC) (NC) (NC) (NC)

89 O (NC) (NC) (NC) (NC)

90 IO Co1_D Co1_D Co1_D Co1_D

MII

mode

Phy_MII

mode

Rmii

mode

Phy_Rm

ii mode

Descriptions

when in half duplex mode: this LED pin present

91 IO Co0_D Co0_D Co0_D Co0_D

92 GND

93 IO FdCo1_D FdCo1_D FdCo1_D FdCo1_D

when in half duplex mode: this LED pin present

when in full duplex mode: this LED pin is always in

when in half duplex mode: this LED pin present

port1’s collision event, using flash style for display.

6/20

Loading...

Loading...