MYSON MTD492N, MTD492V Datasheet

MYSON

TECHNOLOGY

MTD492

Coaxial Transceiver Interface

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification without notice. No

liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

MTD492 Revision 3.5 01/07/1997

1/8

FEATURES

•

Compatible with IEEE 802.3 10Base5 (Ethernet) and 10Base2 (Cheapernet).

• Internal A UI squelch circuitry for noise rejection.

• Transmission I DL detection at end of packet and dri bble bit rej ec tion window.

• Reception dribble bit rejection window.

• Reception and tr ansmission mode collision detection.

• Extended collision detection to turn off receiving path.

• CD heartbeat ex ternally controllabl e.

• Advanc ed low-power, high-perfor mance CMOS tec hnology.

• ESD protection greater than 2000 Volts.

•

16-pin PDIP and 28- pin PLCC packages.

GENERAL DESCRIPTION

The MTD492 transceiver integrates the coax ial cable interface functions of the Medium Attachm ent Unit

(MAU) in Ethernet or Cheapernet LAN applications. I n an Et hernet 10Base5 network, MTD492 is mounted

on the thick E thernet coaxial cable and connects to a station through an AUI cable. For Cheaper net

applicat ions, MTD492 is connected to the Cheapernet coax ial cable t hr ough a B NC c onnec tor and is

usually m ounted on the LAN adapter in a station.

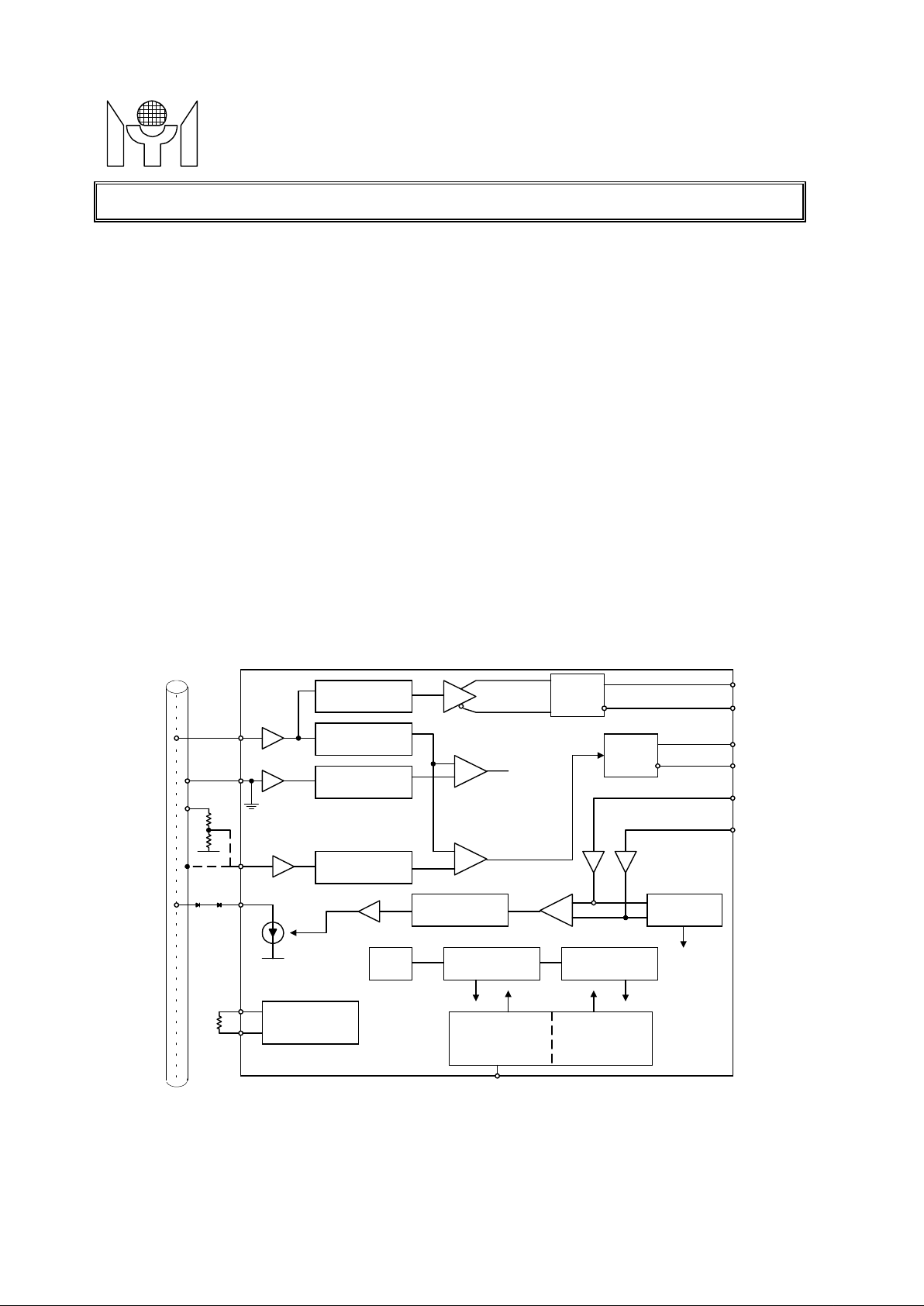

BLOCK DIAGRAM

HIGH PASS

EQUALIZATION

LOW PASS

FILTER

LOW PASS

FILTER

COM

-

+

LOW PASS

FILTER

125

10K

REFERENCE

CIRCUIT

1K

AUI

DRIVER

AUI

DRIVER

CARRIER

SENSE

-

+

WAVEFORM

SHAPING

+

-

DC/AC

SQUELCH

WATCH DOG

TIMER 26ms

JABBER RESET

TIMER 0.4sec

10MHz

OSC

TRANSMIT

STATE

MACHINE

RECEIVE

STATE

MACHINE

XMTSQ

CLK

VEE

COLLISION

HBE

FXI

GND

COAX

VEE

XMT

CDS

RECV

TXO

RR+

RR-

RX+

RX-

CD+

CD-

TX+

TX-

MYSON

TECHNOLOGY

MTD492

MTD492 Revision 3.5 01/07/1997

2/8

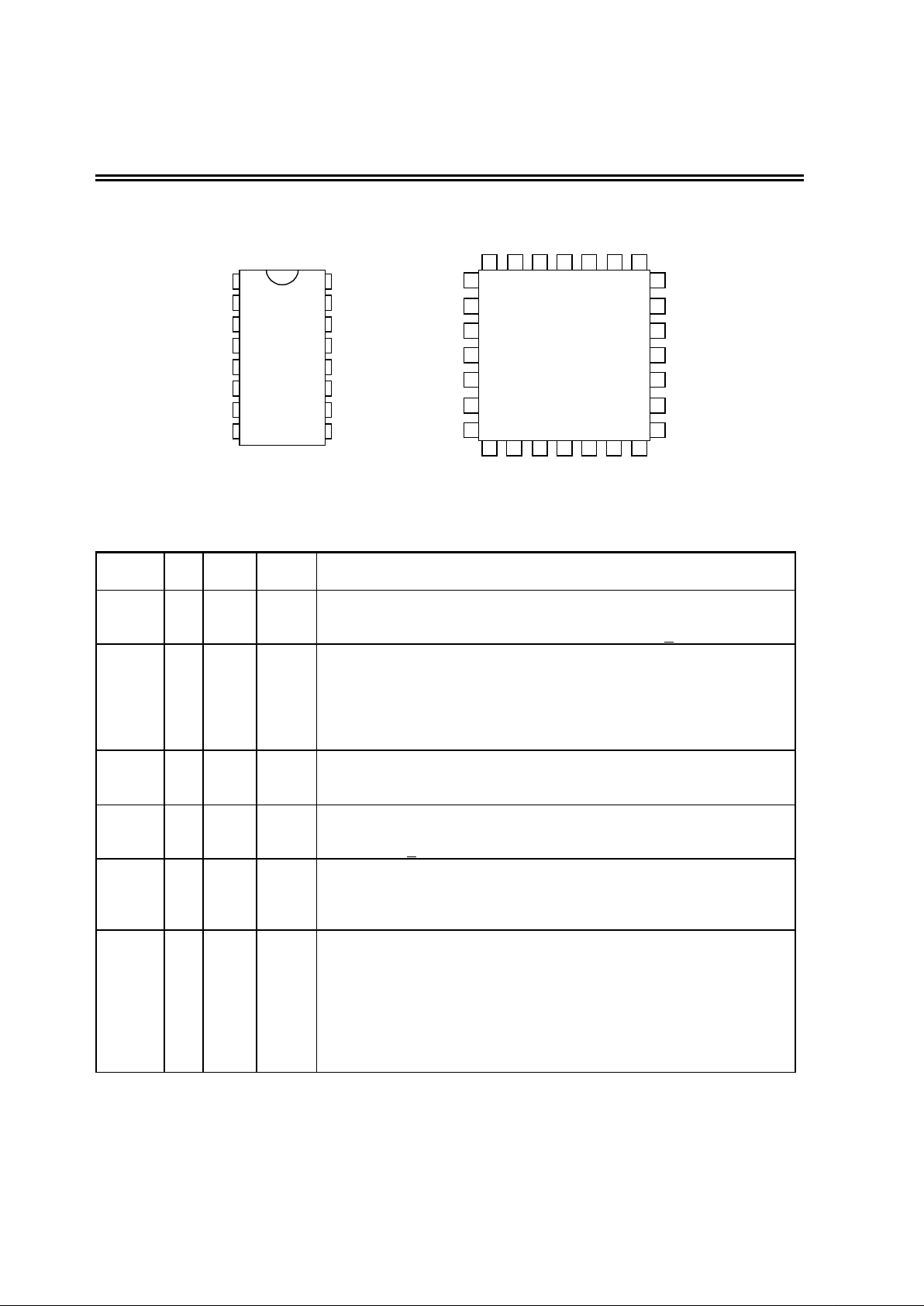

1.0 CONNECTION DIAGRAM

MTD492N

16 PIN PDIP

MTD492V

28 PIN PLCC

CD+

CD-

RX+

VEE

VEE

RX-

TX+

TX-

CDS

TX0

RXI

VEE

RRRR+

GND

HBE

VEE

VEE

VEE

VEE

VEE(NC)

VEE(NC)

VEE(NC)

RX+

CD-

CD+

CDS

TXDNCRXI

VEE(NC)

VEE

VEE

VEE

VEE

VEE(NC)

RR-

RX-

TX+

TX-

HBE

GND

GND

RR+

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

2.0 PIN DESCRIPTIONS

Name I/O PDIP

Pin#

PLCC

Pin#

Description

TX+,TX- I 7,8 13,14

Transmission Data Input.

A balanced differential line receiver which

receives inputs from the off-chip Manchester Code Converter(MCC) t o

the Transmitter. The c ommon m ode volt age on TX+ is set internally .

HBE I 9 15

Heartbeat Enab ler.

The CD heartbeat t est is enabled when HBE is

connected to Ground and di sabled when HBE is connected t o VEE.

This pin is i nternally biased at 0.5 VEE. Test mode i s enabl ed if thi s

pin is left floating or bi ased i n the range of -3.5V to -5.5V. Jabber is

disabled in t est mode. Exiting the jabber disable mode r equires at

least jabber reset time.

RR+,RR- I 11,12 18,19

External Resist or.

A 1kΩ/1% resistor should be connected across

these pins to correct ly set internal operating currents. RR+ is

internal ly shorted to GND.

RXI I 14 26

Network Receiving Input.

Should be connected to the COAX center

conductor. Signals meeting receiver squelch li mits are recovered and

output on RX+. RXI also detects the collision voltage level .

CDS I 16 1

Collision Detection Sense.

Connects directly to the COAX

shield, providing a reference for the collision detection voltage

level for r ec eption-mode det ec tion. An ex ternal bias network can be

used to shift the detection t hr eshol d for transmission-detection mode.

CD+,CD- O 1,2 2,3

Collision Output.

A balanced differential line driver drives this

output pair from the collision detection circuitry. A 10MHz signal from

the internal oscillator is transferred to these outputs in the event of

collision, excessive transmission (jabber), or duri ng hear tbeat

conditi on. These outputs are open sources, and pull- down resistors of

510Ω to VEE are required. To minimize power dissipation, both open

source outputs are disabled during idle condition, al lowing the

common mode on the pull- down resistors to be pulled to VEE.

MYSON

TECHNOLOGY

MTD492

MTD492 Revision 3.5 01/07/1997

3/8

RX+,RX- O 3,6 4,12

Reception Data Output.

A balanced differential output dr ives the

data

recov er ed from t he network to the MCC. These output s are also open

sources, and pull-down resistors of 510Ω to VEE are required. These

pins are biased at -2V during idle time. When an ext ended per iod of

collision condition happens, the receiving path is di sabl ed. Any

interruption of collision will re-enable the receivi ng path.

TXO O 15 28

Transmission Output.

Should be connected to the coaxi al cable via

either one (Cheapernet) or 2 serial i sol ation diodes (Ethernet).

GND 10 17

Positive Supply Pin(Ground).

Should be connected to the COAX

shield.

VEE 4,5,135, 6, 7,

8, 9, 10,

11, 20,

21, 22,

23, 24,

25

Negative Power Supply.

-9 Volts. A 0.1µF decoupli ng c apac itor

must be connected across GND and VEE as close to the device as

possible.

3.0 FUNCTIONAL DESCRIPTIONS

3.1. Transmission Path

The transmission data is input from TX+/ - pins differentially. In general, this differential signal is coupled

through an AUI i sol ation transfor mer. In the M A U desi gn, it is preferable that an equivalent 78 Ohm load be

placed across these 2 pins for pr oper loading for the signal source. Improper load terminati on may cause

excess undershoot at the end of the packet, whic h c auses the dribble bit t o be transmitt ed er r oneousl y .

The transmission signal is first checked against t he on- c hip DC/AC squelch condi tion. If the signal i s

greater than the squel c h threshold (-175 to -300 mV) and the width is wider t han 17 nsec, the squelch is

turned off. The squelch r emains off until the DC squelch condition is not met or an end- of-packet I DL is

detected (at the end of the packet, data remains at 1 for l onger than 175 nsec). Once IDL i s detec ted,

MTD492 provides a 0.8 usec reject ion window that prev ents dribble bit transmission at the A UI interface.

When the squelch is off, the transmission path is enabled and dat a is fed into a waveform shaping circuit

followed by the transmission out put buff er . The waveform shaping function contr ols the output rise/fall time

between 20nsec and 30 nsec, and mini mizes the m ismatch between the rise/fall time. MTD492 provides a

current source output that should be connected to the coaxial cable through at least one isolati on diode.

When data is high, the out put current is virtually zero (ther e is approximately less than 1mA output in t his

state to maintain the linearity of the output buffer) ; when data is low, the output cur r ent peaks at around 80

mA. T his provi des an approximat e 2V peak to peak swing on a 25 Ohm load. Due to the nature of

Manchester code, the average output DC c ur r ent is half of the peak - 40 mA, i.e. 1V DC average on the

cable 25 Ohm load.

3.2. Reception Path

The signal on the c oaxial cable is fi r st buffered. The DC aver age of the signal is extracted by a low pass

filter. When the DC average exceeds the carrier sense threshold (Vcs), the reception data path is turned

on. The signal goes thr ough a high pass filt er for equali z ation of high frequency loss on the cable and then

is compared wit h its center value. The comparator output is amplified by the A UI driver to provide adequate

driving for the RX+/- output.

The end of t he pac k et is determined by 2 conditi ons. If the received dat a is high longer than 175nsec or t he

DC average does not meet the carrier sense threshold, the recept ion data path is turned off. M TD492 then

appends the IDL pulse to the end of the packet. A r ejection window of 1 usec t hat blocks the data reception

path is also turned on.

Loading...

Loading...