MXIC MX98715AEC-E, MX98726EC Datasheet

1. FEATURES

ADVANCED INFORMATION

MX98715AEC-E

SINGLE CHIP FAST ETHERNET NIC CONTROLLER

- ENHANCED VERSION

• A single chip solution integrates 100/10 Base-T fast

Ethernet MAC, PHY and PMD.

• Microsoft PC97, 98, 99 and Novell 4.11/5.0 certified.

• Support DMI 2.0 management.

• Support Intel PXE remote boot device.

• Fully comply to IEEE 802.3u specification

• Operates over 100 meters of STP and category 5 UTP

cable

• Fully comply to PCI spec. 2.1 with clock frequency up

to 33MHz

• Fully comply to Advanced Configuration and Power

Interface (ACPI) Rev 1.1

• Fully comply to PCI Bus Power Management Interface spec. Rev 1.1

• Support full and half duplex operations in both 100

Base-TX and 10 Base-T mode

• Supports 3 kinds of wake up events defined in Network Device Class Power Management Spec 1.0.

Including:

- Magic Packet

- Link Change(link-on)

- Wake Up Frame

TM

2. GENERAL DESCRIPTIONS

• Supports IEEE802.3x Frame Based Flow Control

scheme in full duplex mode.

• Supports early interrupt on both transmit and receive

operations.

• 100/10 Base-T NWAY auto negotiation function

• Large on-chip FIFOs for both transmit and receive

operations without external local memory

• Bus master architecture with linked host buffers delivers the most optimized performance

• 32-bit bus master DMA channel provides ultra low

CPU utilization, best fit in server and windows application.

• Proprietary Adaptive Network Throughput Control

(ANTC) technology to optimize data integrity and

throughput

• Support up to 64K bytes boot ROM interface

• Three levels of loopback diagnositic capability

• Support a variety of flexible address filtering modes

with 16 CAM address and 128 bits hash

• MicroWire interface to EEPROM for customer's IDs

and configuration data

• Single +5V power supply, CMOS technology, 128-pin

PQFP package/LQPF package

( Magic packet technology is a trademark of advanced Micro Device Corp. )

The MX98715AEC-E controller is an IEEE802.3u compliant single chip 32-bit full duplex, 10/100Mbps highly

integrated Fast Ethernet combo solution, designed to

address high performance local area networking (LAN)

system application requirements.

MX98715AEC-E's PCI bus master architecture delivers

the optimized performance for future high speed and

powerful processor technologies. In other words, the

MX98715AEC-E not only keeps CPU utilization low while

maximizing data throughput, but it also optimizes the

PCI bandwidth providing the highest PCI bandwidth utilization. To further reduce maintenance costs the

MX98715AEC-E uses drivers that are backward compatible with the original MXIC MX98713 series controllers.

The MX98715AEC-E contains a PCI local bus glueless

interface, a Direct Memory Access (DMA) buffer management unit, an IEEE802.3u-compliant Media Access

Controller (MAC), large Transmit and Receive FIFOs,

P/N:PM0676 REV. 0.2, MAR. 04, 2000

and an on-chip 10 Base-T and 100 Base-TX transceiver

simplifying system design and improving high speed signal quality . Full-duple x operation are supported in both

10 Base-T and 100 Base-TX modes that increases the

controller's operating bandwidth up to 200Mbps.

Equipped with intelligent IEEE802.3u-compliant auto-negotiation, the MX98715AEC-E-based adapter allows a

single RJ-45 connector to link with the other IEEE802.3ucompliant device without re-configuration.

In MX98715AEC-E, an innovative and proprietary design "Adaptive Network Throughput Control" (ANTC) is

built-in to configure itself automatically by MXIC's driver

based on the PCI burst throughput of different PCs . With

this proprietary design, MX98715AEC-E can always

optimize its operating bandwidth, network data integrity

and throughput for different PCs.

The MX98715AEC-E features Remote-P ower-On and Remote-Wake-Up capability and is compliant with the Advanced Configuration and Power Interface version 1.0

1

MX98715AEC-E

(ACPI). This support enables a wide range of wak e-up

capabilities, including the ability to customize the content of specified packet which PC should be responded

to, e ven when it is in a lo w-power state. PCs and workstations could take advantage of these capabilities of

being waked up and served simultaneously ov er the network by remote server or workstation. It helps organizations reduce their maintenance cost of PC network.

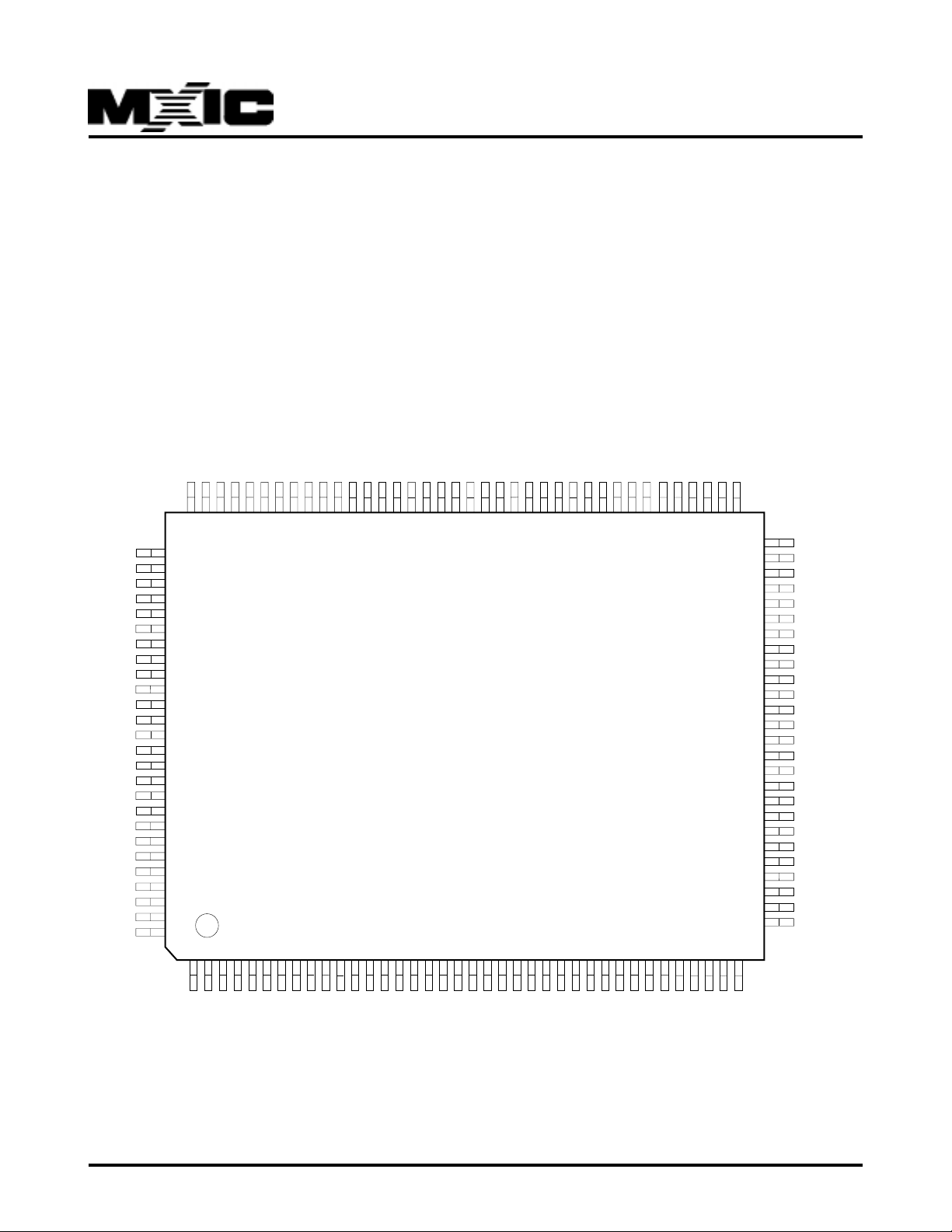

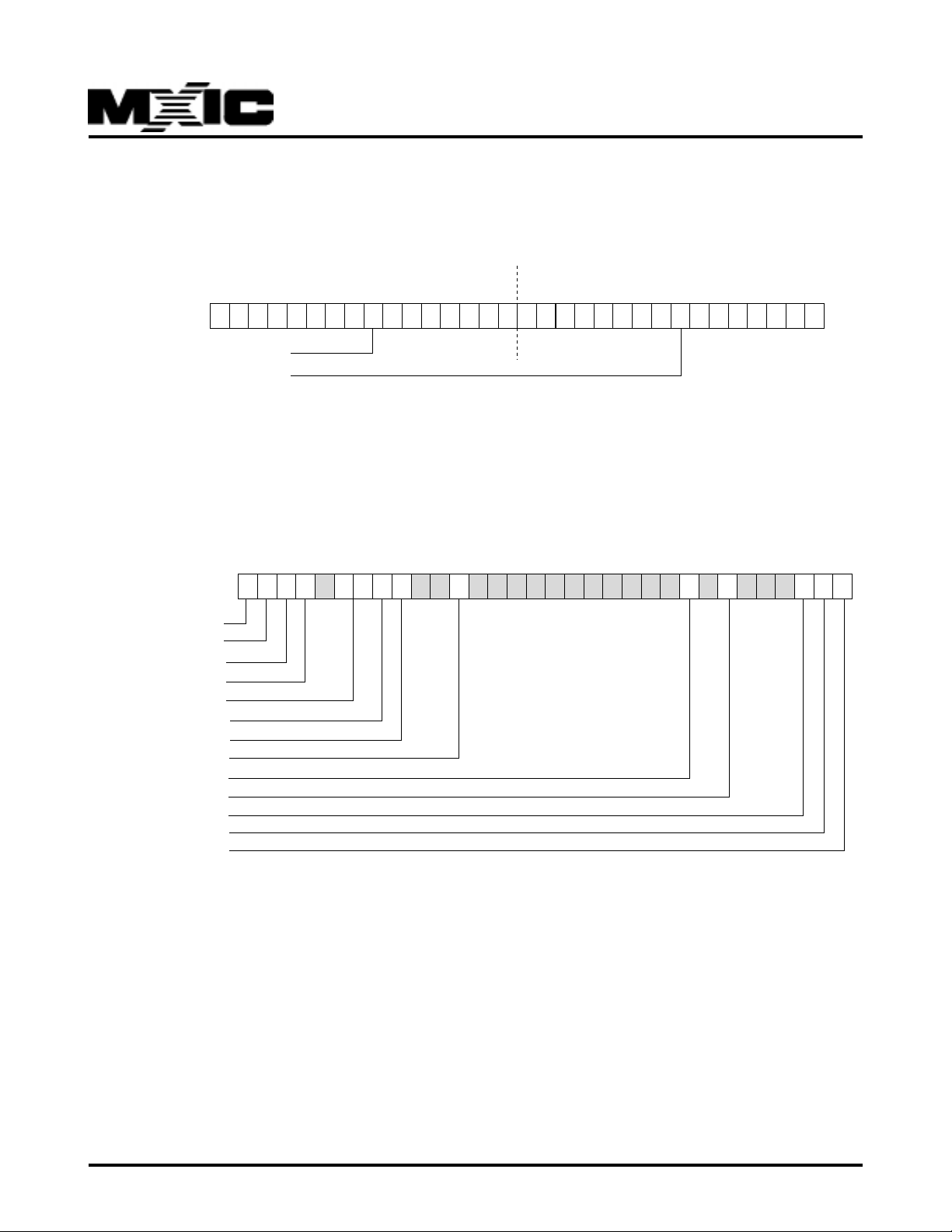

3. PIN CONFIGURATIONS

RTX

RTX2EQNCGND

TXOP

TXON

VDD

GND

GND

VDD

RXIP

RXIN

VDD

GND

VDD

GND

GND

CKREF/XI

9998979695949392919089888786858483828180797877767574737271706968676665

102

101

100

VDD

GND

GND

VDD

GND

VCC

GND

PMEB

INTAB

RSTB

PCICLK

GNTB

REQB

AD31

AD30

GND

AD29

AD28

VDD

AD27

GND

AD26

AD25

GND

AD24

CBEB3

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

12345678910111213141516171819202122232425262728293031323334353637

MX98715AEC-E

The 32-bit multiplexed bus interface unit of

MX98715AEC-E provides a direct interface to a PCI local bus, simplifing the design of an Ethernet adapter in a

PC system. With its on-chip support for both little and

big endian byte alignment, MX98715AEC-E can also address non-PC applications.

VDD

RDA

GND

VDD

LED1

LED0

BPA15

BPA14

BPA13

GND

VDD

BPA12

BPA11

BPA10

BPA9

BOEB

BPA8

BPA7

BPA6

BPA5

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

BPA4

BPA3

BPA2

BPA1(EEDI)

BPA0(EECK)

EECS

BPD0(EED0)

BPD1

BPD2

BPD3

BPD4

BPD5

BPD6

BPD7

GND

VDD

AD0

AD1

GND

AD2

AD3

VDD

AD4

AD5

GND

AD6

P/N:PM0676

GND

IDSEL

AD23

AD22

GND

AD21

AD20

VDD

AD19

AD18

GND

AD17

AD16

CBEB2

FRAMEB

GND

IRDYB

TRDYB

DEVSELSB

STOPB

2

VDD

PERRB

SERRB

PAR

AD15

CBEB1

GND

AD14

AD13

VDD

AD12

AD11

AD10

GND

AD9

AD8

AD7

CBEB0

REV. 0.2, MAR. 04, 2000

MX98715AEC-E

4. PIN DESCRIPTION ( 128 PIN PQFP )

( T/S : tri-state, S/T/S : sustended tri-state, I : input, O : output, O/D : open drain )

Pin Name Type Pin No 128 Pin Function and Driver

AD[31:0] T/S 116, 117 PCI address/data bus: shared PCI address/data bus lines. Little or big endian

119,120, byte ordering are supported.

122,124,

125,127,

3,4,6,7,9,

10,12,13,

26,28,29,

31-33,35,

36,38,39,

41,42,44,

45,47,48

CBE[3:0] T/S 128,14 PCI command and b yte enable b us: shared PCI command b yte enable b us,

25,37 during the address phase of the transaction, these four bits provide the bus

command. During the data phase, these f our bits provide the b yte enab le.

FRAMEB S/T/S 15 PCI FRAMEB signal: shared PCI cycle start signal, asserted to indicate the

beginning of a bus transaction. As long as FRAMEB is asserted, data

transfers continue.

TRD YB S/T/S 18 PCI Target ready: issued b y the target agent, a data phase is completed on

the rising edge of PCICLK when both IRD YB and TRDYB are asserted.

IRD Y B S/T/S 17 PCI Master ready: indicates the bus master's ability to complete the current

data phase of the transaction. A data phase is completed on any rising edge

of PCICLK when both IRDYB and TRDYB are asserted.

DEVSELB S/T/S 19 PCI slave device select: asserted by the target of the current bus access.

When 98715A is the initiator of current bus access, the target must assert

DEVSELB within 5 bus cycles, otherwise cycle is aborted.

IDSEL I 1 PCI initialization device select: target specific de vice select signal f or

configuration cycles issued by host.

PCICLK I 1 1 3 PCI bus clock input: PCI bus clock range from 16MHz to 33MHz.

RSTB I 112 PCI bus reset: host system hardware reset.

PMEB O 11 0 Po wer Management Event:When low indicating a pow er management event

occures, such as detection of a Magic packet, a wak e up frame, or link change.

INTAB O/D 111 PCI bus interrupt request signal: wired to INTAB line.

SERRB O/D 23 PCI bus system error signal: If an address parity error is detected and CFCS

bit 8 is enabled, SERRB and CFCS's bit 30 will be asserted.

PERRB S/T/S 22 PCI bus data error signal: As a b us master, when a data parity error is

detected and CFCS bit 8 is enabled, CFCS bit 24 and CSR5 bit 13 will be

asserted. As a bus target, a data parity error will cause PERRB to be

asserted.

P/N:PM0676

REV. 0.2, MAR. 04, 2000

3

MX98715AEC-E

Pin Name Type Pin No 128 Pin Function and Driver

P AR T/S 24 PCI bus parity bit: shared PCI b us ev en parity bit for 32 bits AD bus and CBE

bus.

STOPB S/T/S 20 PCI Target requested transfer stop signal: as bus master , assertion of STOPB

cause MX98715AEC-E either to retry , disconnect, or abort.

REQB T/S 115 PCI bus request signal: to initiate a bus master cycle request

GNTB I 114 PCI bus grant acknowledge signal: host asserts to inform MX98715AEC-E

that access to the bus is granted

BPA1 O 61 Boot PROM address bit 1(EECS=0): together with BPA[15:0] to access

(EEDI) external boot PROM up to 256KB.

EEPROM data in(EECS=1): EEPROM serial data input pin.

BPA0 O 60 Boot PROM address bit 0(EECS=0): together with BPA[15:0] to access

(EECK) external boot PROM up to 256KB.

EEPROM clock(EECS=1): EEPR OM clock input pin

BPA[15:0] O 78-76,

73-70, Boot PROM address line.

68-60

BPD0 T/S 58 Boot PROM data line 0(EECS=0): boot PR OM or flash data line 0.

(EEDO) EEPROM data out(EECS=1): EEPROM serial data outpin(during reset

initialization).

BPD[7:0] T/S 51-58 Boot PR OM data lines: boot PROM or flash data lines 7-0.

EECS O 59 EEPROM Chip Select pin.

BOEB O 69 Boot PROM Output Enable.

RDA O 83 Connecting an external resistor to ground, Resistor value=10K ohms

RTX O 10 2 Connecting an external resistor to ground, Resistor value=560 ohms

RTX2EQ O 101 Connecting an external resistor to ground, Resister value=1.4K ohms

NC I 100 No Connection.

RXIP I 92 Twisted pair receive differential input: Support both 10 Base-T and 100

Base-TX receive differential input.

RXIN I 91 Twisted pair receive differential input: Support both 10 Base-T and 100

Base-TX receive differential input

TXOP O 98 Twisted pair transmit differential output: Support both 10 Base-T and 100

Base-TX transmit differential output

TXON O 97 T wisted pair tr ansmit diff erential output: Support both 10 Base-T and 100

Base-TX transmit differential output

XI/CKREF I 85 Reference clock: 25MHz oscillator cloc k input. For crystal application, This

pin is XI.

LED0 O 79 Programmable LED pin 0:

CSR9.28=1 Set the LED as Link Speed (10/100) LED .

CSR9.28=0 Set the LED as Activity LED .

Default is activity LED after reset.

P/N:PM0676

REV. 0.2, MAR. 04, 2000

4

Pin Name Type Pin No 128 Pin Function and Driver

LED1 O 80 Programmable LED pin 1:

CSR9.29=1 Set the LED as Link/Activity LED .

CSR9.29=0 Set the LED as Good Link LED .

Default is Good Link LED after reset.

VDD I 8,21,30,43, Power pins.

49,74,81,84,

88,90,93,96,

103,106,108,

121

GND I 2,5,11,16,27 Ground pins.

34,40,46,50

75,82,86,87

89,94,95,99

104,105,107

109,118,123,

126

MX98715AEC-E

P/N:PM0676

REV. 0.2, MAR. 04, 2000

5

5. PROGRAMMING INTERFACE

5.1 PCI CONFIGURATION REGISTERS:

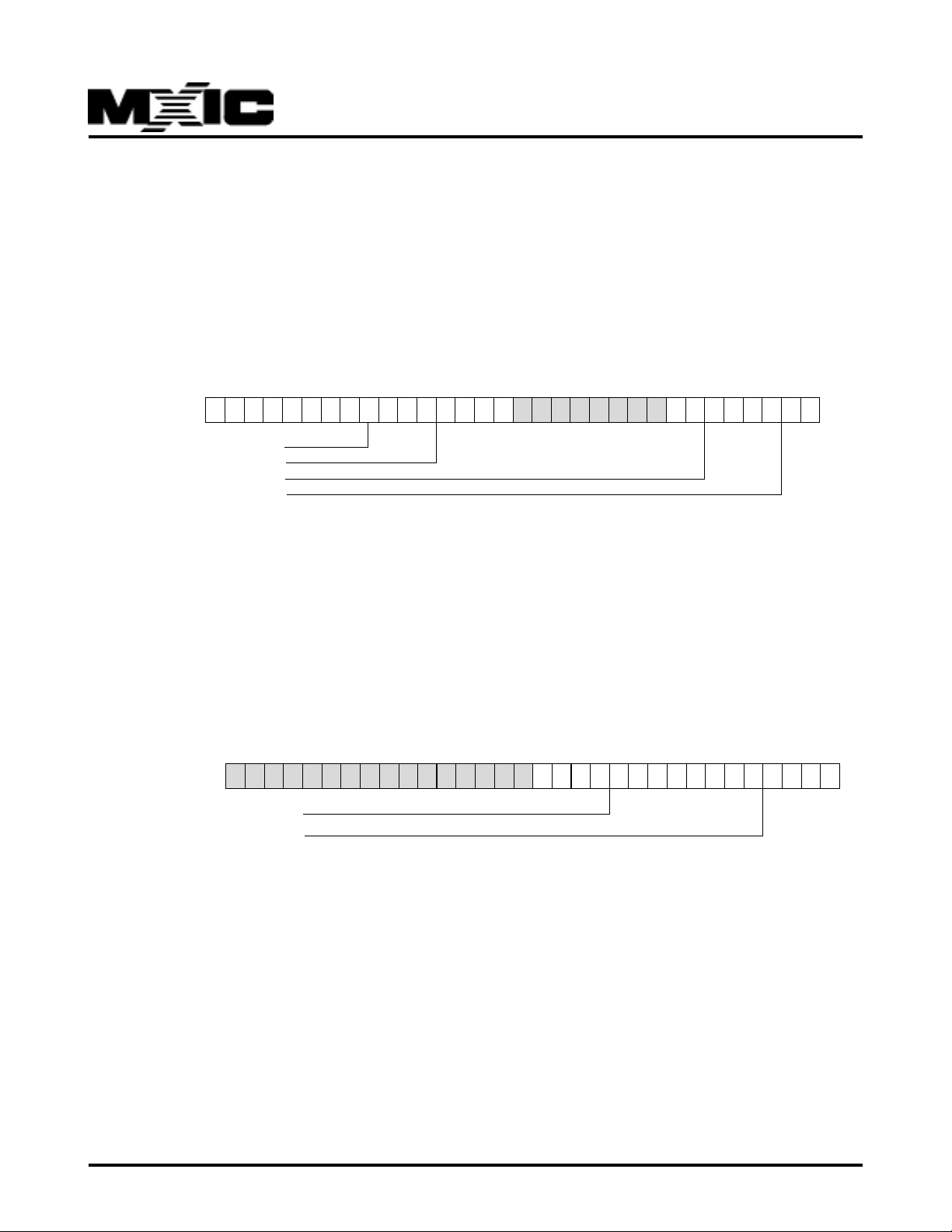

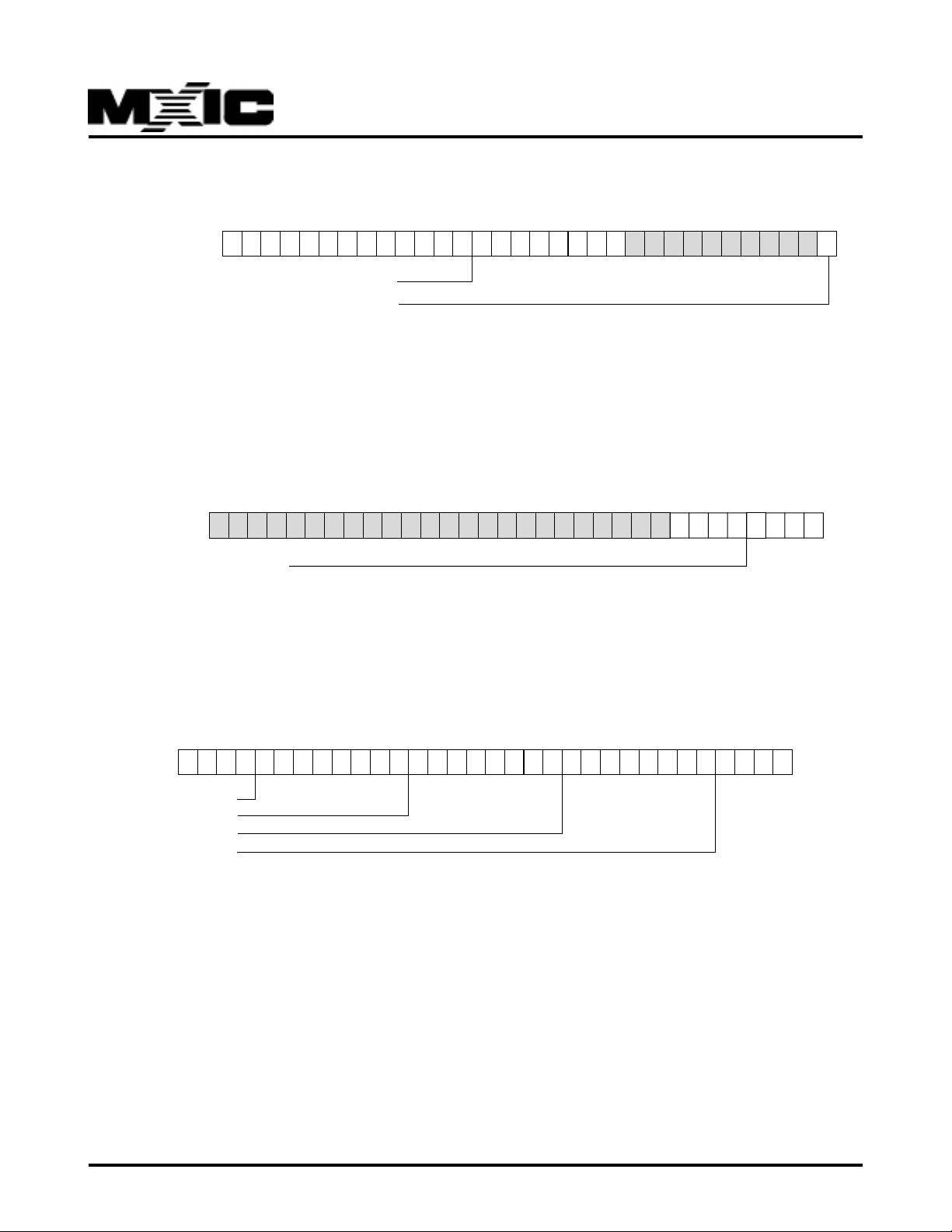

5.1.1 PCI ID REGISTER ( PFID ) ( Offset 03h-00h )

MX98715AEC-E

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Device ID (bit 31:16)

Vendor ID (bit 15:0)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

This register can be loaded from external serial EEPROM or use a MXIC preset value of "10D9" and "0531" for

vendor ID and device ID respectiv ely . W ord location 3Eh and 3Dh in serial EEPROM are used to configure customer's

vendor ID and device ID respectiv ely . If location 3Eh contains"FFFF" v alue then MXIC'svendor ID and device ID will

be set in this register, otherwise both 3Eh and 3Dh will be loaded into this register from serial EEPR OM.

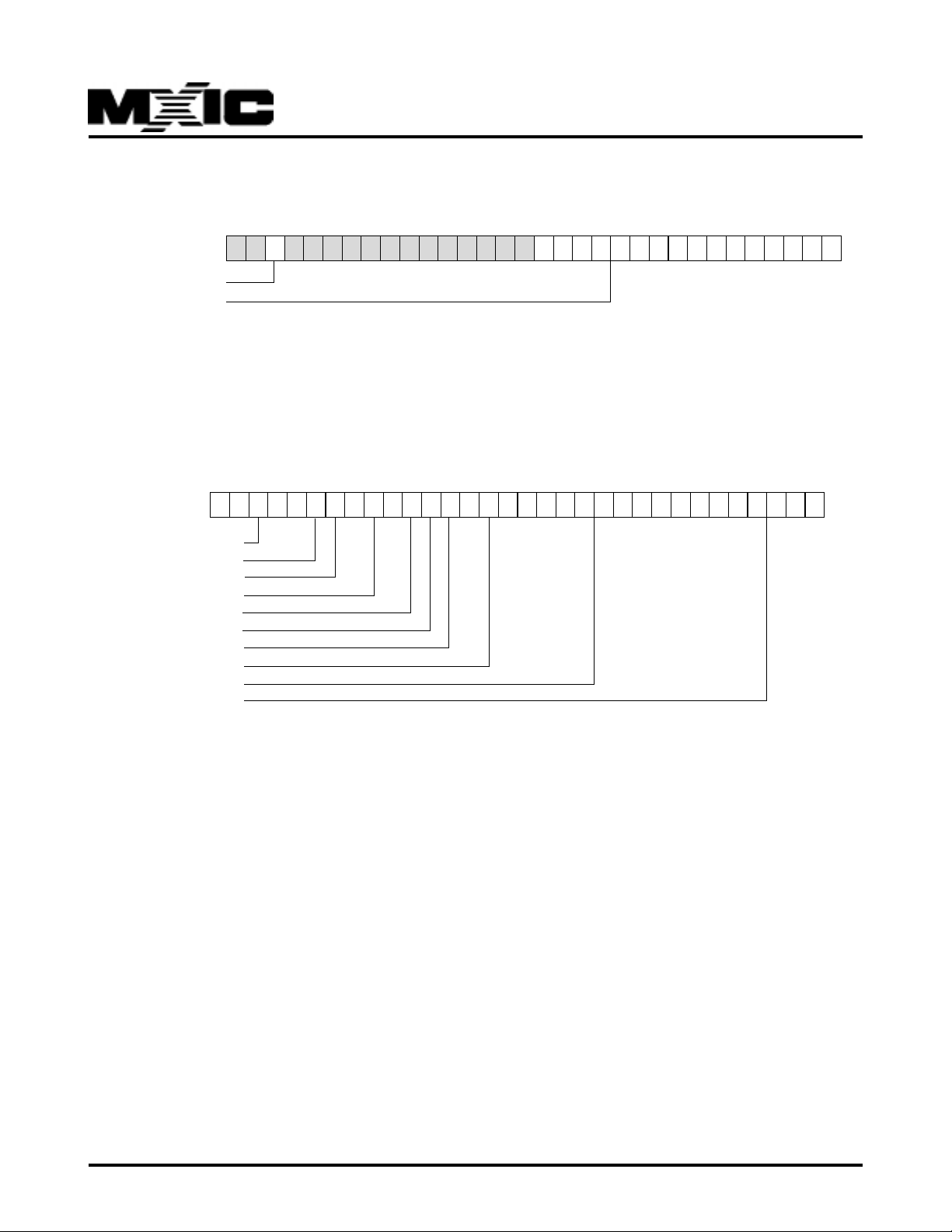

5.1.2 PCI COMMAND AND STATUS REGISTER ( PFCS ) ( Offset 07h-04h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Detect Party Error

Signal System Error

Receive Master Abort

Receive Target Abort

Device Select Timing

Data Parity Report

Fast Back-to-back

New Capability

System Error Enable

Parity Error Response

Master Operation

Memory Space Access

IO Space Access

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

The bit content will be reset to 0 when a 1 is written to the corresponding bit location.

bit 0 : IO Space Access , set to 1 enable IO access

bit 1 : Memory Space Access, set to 1 to enab le memory access

bit 2 : Master Operation, set to 1 to support bus master mode

bit 5-3 : not used

bit 6 : Parity Error Response, set to 1 to enable assertion of CSR<13> bit if parity error detected.

bit 7 : not used

bit 8 : System Error Enab le, set to 1 to enab le SERR# when parity error is detected on address lines and CBE[3:0].

bit 20 : Ne w capability. Set to support PCI power management.

bit 22-bit19 : not used

bit 23 : Fast Back-to bac k, alw a ys set to accept fast back-to-back transactions that are not sent to the same bus

device.

P/N:PM0676

6

REV. 0.2, MAR. 04, 2000

MX98715AEC-E

bit 24:Data parity Report, is set to 1 only if PERR# active and PFCS<6> is also set.

bit 26-25:Device Select Timing of DEVSELB pin.

bit 27:not used

bit 28:Receive Target Abort, is set to indicate a transaction is terminated by a target abort.

bit 29:Receive Master Abort, is set to indicate a master transaction with Master abort.

bit 30:Signal System Error, is set to indicate assertion of SERR#.

bit 31:Detected Parity Error , is set whene v er a parity error detected regardless of PFCS<6>.

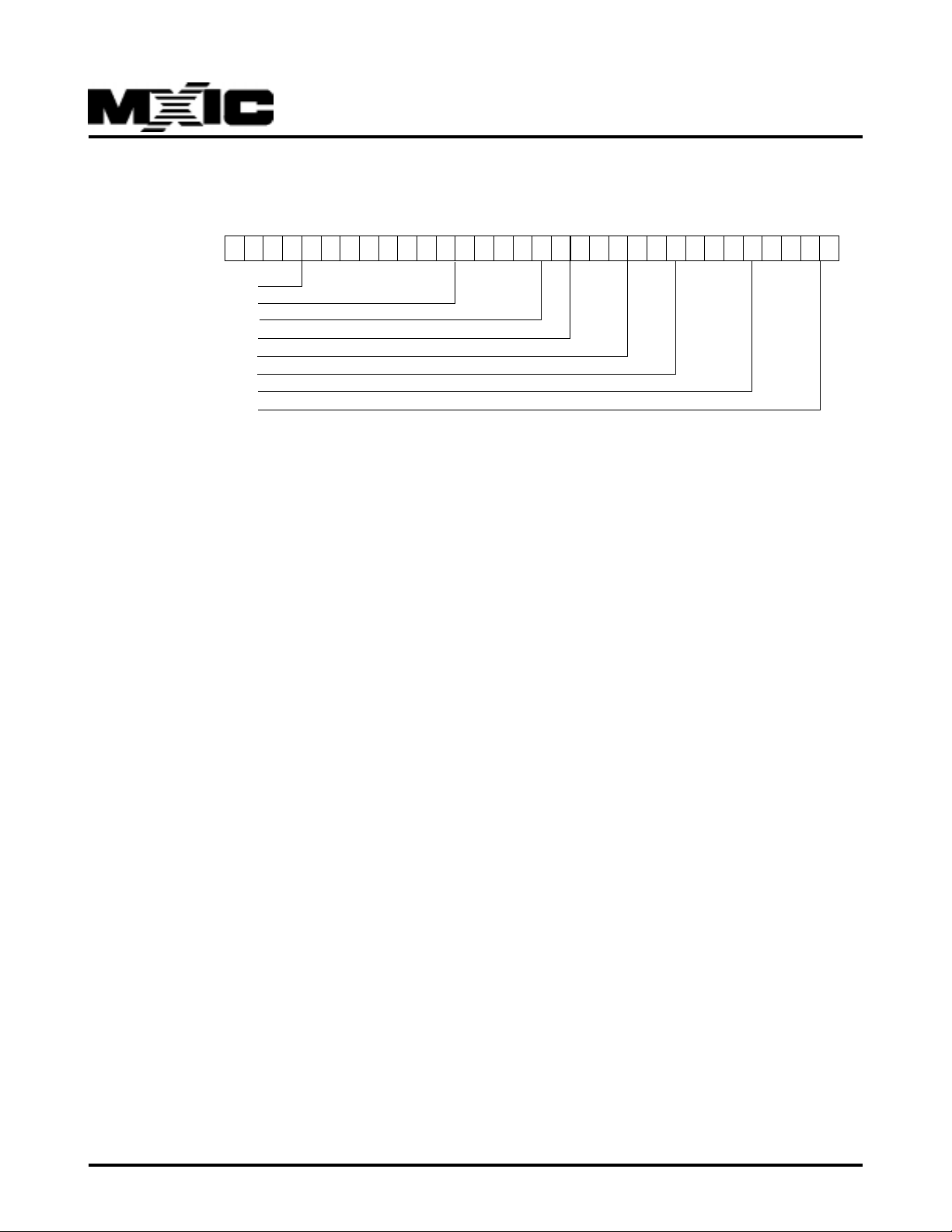

5.1.3 PCI REVISION REGISTER ( PFRV ) ( Offset 0Bh-08h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Base Class

Subclass

Revision Number

Step Number

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

bit 3 - 0 : Step Number, range from 0 to Fh.

bit 7 - 4 : Re vision Number, fixed to 2h for MX98715AEC-E

bit 15 - 8 : not used

bit 23 - 16 : Subclass, fixed to 0h.

bit 31 - 24 : Base Class, fixed to 2h.

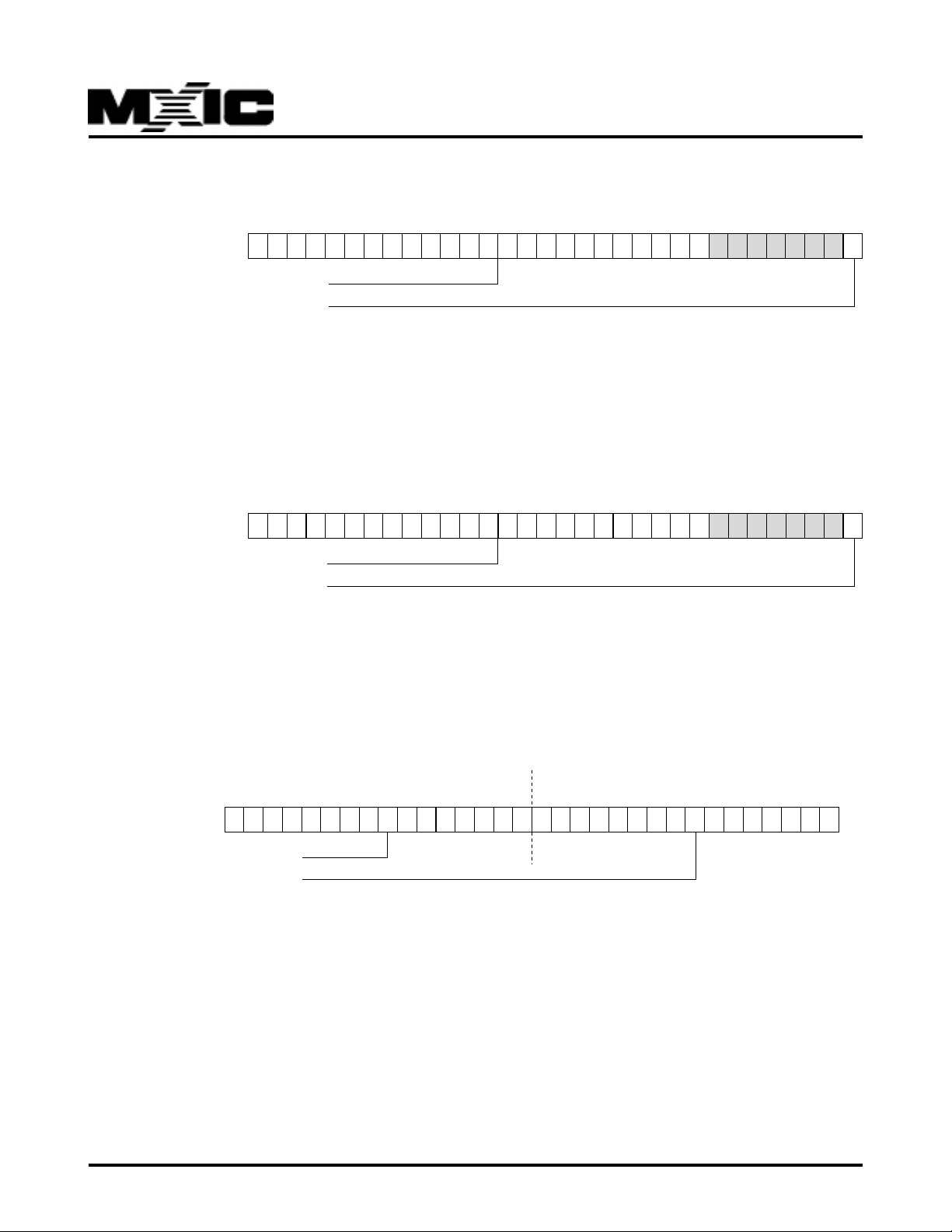

5.1.4 PCI LATENCY TIMER REGISTER ( PFLT ) (Offset 0Fh-0Ch)

PFLT Register (0Fh-0Ch)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Configuration Latency Timer

System cache line size

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

bit 0 - bit 7 : System cache line siz e in units of 32 bit word, device driver should use this value to prog ram CSR0<15:14>.

bit 8 - bit 15 : Configuration Latency Timer, when MX98715AEC-E assert FRAME#, it enables its latency timer to

count.

If MX98715AEC-E deasserts FRAME# prior to timer expiration, then timer is ignored. Otherwise , after timer expires,

MX98715AEC-E initiates transaction termination as soon as its GNT# is deasserted.

P/N:PM0676

7

REV. 0.2, MAR. 04, 2000

MX98715AEC-E

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Configuration Base IO Address

IO/Memory Spec Indicator

5.1.5 PCI BASE IO ADDRESS REGISTER ( PBIO ) ( Offset 13h-10h )

bit 0 : IO/Memory Space Indicator , fix ed to 1 in this field will map into the IO space . This is a read only field.

bit 7 - 1 : not used, all 0 when read

bit 31 - 8 : Defines the address assignment mapping of MX98715AEC-E CSR registers.

5.1.6 PCI Base Memory Address Register ( PBMA ) ( Offset 17h-14h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Configuration Base Memory Address

Memory Spec Indicator

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

bit 0 : Memory Space Indicator , fix ed to 0 in this field will map into the memory space. This is a read only field.

bit 6 - 1 : not used, all 0 when read

bit 31 - 7 : Defines the address assignment mapping of MX98715AEC-E CSR registers.

5.1.7 PCI SUBSYSTEM ID REGISTER ( PSID ) ( Offset 2Ch-2Fh )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Subsystem ID (31:16)

Subsystem Vendor ID (bit 15:0)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

This register is used to uniquely identify the add-on board or subsystem where the NIC controller resides. V alues in

this register are loaded directly from external serial EEPROM after system reset automatically . W ord location 36h of

EEPROM is subsystem vendor ID and location 35h is sub-system ID.

P/N:PM0676

REV. 0.2, MAR. 04, 2000

8

MX98715AEC-E

5.1.8 PCI BASE EXPANSION ROM ADDRESS REGISTER ( PBER ) ( Offset 33h-30h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Expansion ROM Base Address (upper 21 bit)

Address Decode Enable

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 0 0 0

bit 0 : Address Decode Enabl e, decoding will be enabled if only both enable bit in PFCS<1> and this e xpansion ROM

register are 1.

bit 10 - 1 : not use

bit 31 - 11 : Defines the upper 21 bits of expansion ROM base address.

5.1.9 PCI CAPABILITY POINTER REGISTER ( PFCP ) ( Offset 37h-34h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Capability Pointer (Set to 44h)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

bit 7- 0 : Capability pointer (Cap_Ptr) is set to 44h if PMEB is connected to PCI b us , otherwise 00.

bit 31- 8 : reserve d

5.1.10 INTERRUPT REGISTER ( PFIT ) ( Offset 3Fh-3Ch )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0 0 1 1 1 0 0 0 0 0 0 0 1 0 0 0

Max_Lat

Min-Gnt

Interrupt Pin

Interrupt Line

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

bit 7 - 0 : Interrupt Line, system BIOS will writes the routing inf ormation into this field, driver can use this information

to determine priority and interrupt vector.

bit 15 - 8 : Interrupt Pin, fix ed to 01h which use INTA#.

bit 31 - 24 : Max_Lat which is a maximum period f or a access to PCI b us .

bit 23 - 16 : Min_Gnt which is the maximum period that MX98715AEC-E needs to finish a brust PCI cycle.

P/N:PM0676

REV. 0.2, MAR. 04, 2000

9

5.1.11 PCI DRIVER AREA REGISTER ( PFDA ) ( 43h-40h )

MX98715AEC-E

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Board T ype

Driver Special Use

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

bit 29 : board type

bit 15 - 8 : driver is free to read and write this field for an y purpose.

bit 7 - 0 : not used.

5.1.12 PCI POWER MANAGEMENT CAPABILITY REGISTER ( PPMC ) ( 47h-44h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PME_Support

D2_Support

D1_Support

AUX_I

DSI

Auxiliary Power Source

PME Clock

Version

Next Pointer

Capability ID

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 0

bit 31- 27 : PME_Support, read only indicates the power states in which the function ma y assert LANWAKE pin.

bit 31 ---- PME_D3cold (value=1)

bit 30 ---- PME_D3warm (value=1)

bit 29 ---- PME_D2 (value=1)

bit 28 ---- PME_D1 (value=1)

bit 27 ---- PME_D0 (value=1)

bit 26 : D2 mode support, read only, set to 1.

bit 25 : D1 mode support, read only, set to 1.

bit 24-22 : AUX_I bits. Auxiliary current field, set to 100.

bit 21 : DSI, read only, set to 0.

bit 20 : Auxiliary power source, set to 1. This bit only valid when bit 15 is a '1'.

bit 19 : PME Cloc k, read only, set to 0.

bit 18-16 : PCI po wer management v ersion, set to 001, read only.

bit 15-8 : Ne xt Pointer, all bits set to 0.

bit 7-0 : Capability ID, read only, a 1 indicates that the data structure currently being pointed to is the PCI pow er

managment data structure.

P/N:PM0676

10

REV. 0.2, MAR. 04, 2000

MX98715AEC-E

5.1.13 PCI POWER MANAGEMENT COMMAND AND STATUS REGISTER ( PPMCSR ) ( 4Bh-48h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Data

Bridge Extension Support

PME_Status

Data_Scale

Data_Select

PME_EN

Reserved

Power State

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 0 0

bit 1-0 : Power_State , read/write, D0 mode is 00, D1 mode is 01, D2 mode is 10, D3 hot mode is 11.

bit7-2 : all 0. Reserved.

bit8 : PME_EN, set 1 to enab le LANWAKE. Set 0 to disable LANW AKE assertion.

bit 12-9 : Data_Select f or report in the Data register located at bit 31:24.

bit 14-13 : Data_Scale, read only.

bit 15 : PME_Status independent of the state of PME_EN.

When set, indicates a assertion of LANWAKE pin. (support D3 cold).

Write 1 to clear the LANWAKE signal. Write 0, no eff ect.

bit 21-16 : Reserved.

bit 22 : B2_B3#, B2_B3 support for D3 hot, meaningful only if BPCC_EN = 1, read only.

bit 23 : BPCC_EN, Bus Power/Clock Control Enable, read only.

bit 31-24 : Data, read only.

P/N:PM0676

REV. 0.2, MAR. 04, 2000

11

MX98715AEC-E

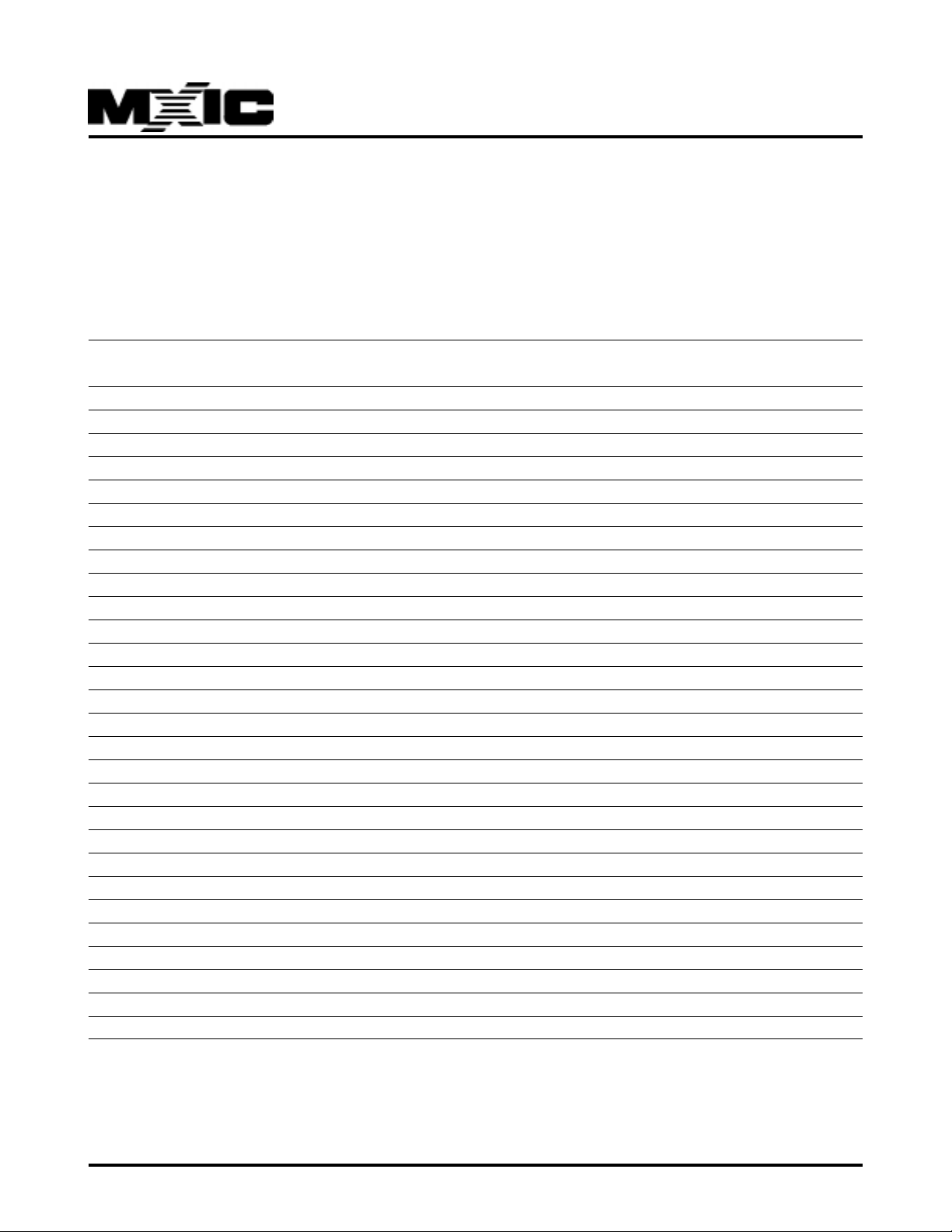

5.2 HOST INTERF ACE REGISTERS

MX98715AEC-E CSRs are located in the host I/O or memory address space. The CSRs are double word aligned and

32 bits long. Definitions and address for all CSRs are as follows :

CSR Mapping

Register Meaning Offset from CSR Base

Address ( PBIO and PBMA )

CSR0 Bus mode 0 0

CSR1 T ransmit poll demand 08 h

CSR2 Receive poll demand 10 h

CSR3 Receive list demand 18 h

CSR4 T ransmit list base address 20 h

CSR5 Interrupt status 28 h

CSR6 Operation mode 30h

CSR7 Interrupt enable 38 h

CSR8 Missed frame counter 40 h

CSR9 Serial ROM and MII management 48h

CSR10 Reserved 50h

CSR11 General Purpose timer 58 h

CSR12 10 Base-T status port 60h

CSR13 SIA Reset Register 68 h

CSR14 10 Base-T control port 70h

CSR15 Watchdog timer 7 8h

CSR20 Auto compensation A0h

CSR21 Flow control Register A8h

CSR22 MAC ID Byte 3-0 B0h

CSR23 Magic ID 5, 4 / MAC ID Byte 5, 4 B8h

CSR24 Magic ID Byte 3-0 C0h

CSR25 Filter 0 Byte Mask C8h

CSR26 Filter 1 Byte Mask D0h

CSR27 Filter 2 Byte Mask D8h

CSR28 Filter 3 Byte mask E0h

CRS29 Filter Offset E8h

CSR30 Filter 1&0 CRC-16 F0h

CSR31 Filter 3&2 CRC-16 F8h

P/N:PM0676

REV. 0.2, MAR. 04, 2000

12

Loading...

Loading...