MXIC MX98715AEC-D Datasheet

1. INTRODUCTION

PRELIMINARY

MX98715AEC-D

APPLICATION NOTE

The purpose of this application note is to describe the

implementation of a PCI bus master 100 Base-TX F ast

Ethernet node using MXIC’ highly integrated single chip

Fast Ethernet NIC controller MX98715AEC-D . In details,

this document presents product overview, programming guide, hardware design and layout recommendations that can help you to quickly and smoothly

implement a Fast Ethernet adapter card.

As you can find in the MX98715AEC-D driver diskette,

2. PRODUCT OVERVIEW

The MX98715AEC-D implements the 10/100Mbps MAC

layer and Physical layer on a single chip in accordance

with the IEEE 802.3 standard.

The MX98715AEC-D highly integrates with direct PCI

bus interface, including PCI bus master with DMA channel capability, direct EEPROM as well as Boot ROM

interface, and large on chip transmit/receiv e FIFOs. Also ,

the MX98715AEC-D is equipped with intelligent

MXIC already provided a complete set of high quality

drivers for easier and more efficient way to interface with

MX98715AEC-D on the most popular Network Operating Systems. Nev ertheless, there are still some special

applications or environment not covered in the

MX98715AEC-D driver diskette. Driver developers, however, could still refer to the section of driver programming guide to accomplish the required driver. It is recommended that you are familiar with the MX98715AECD data sheet before reading this guide.

IEEE802.3u-compliant Nway auto-negotiation capability

allowing a single RJ-45 connector to link with the other

IEEE802.3u-compliant device without re-configuration.

T o optimiz e operating bandwidth, network data integrity

and throughput, the proprietary Adaptive Network

Throughput Control (ANTC) function is implemented. For

detailed product specification information, please refer

to the MX98715AEC-D data sheet.

3. HARDWARE DESIGN CONSIDERATIONS

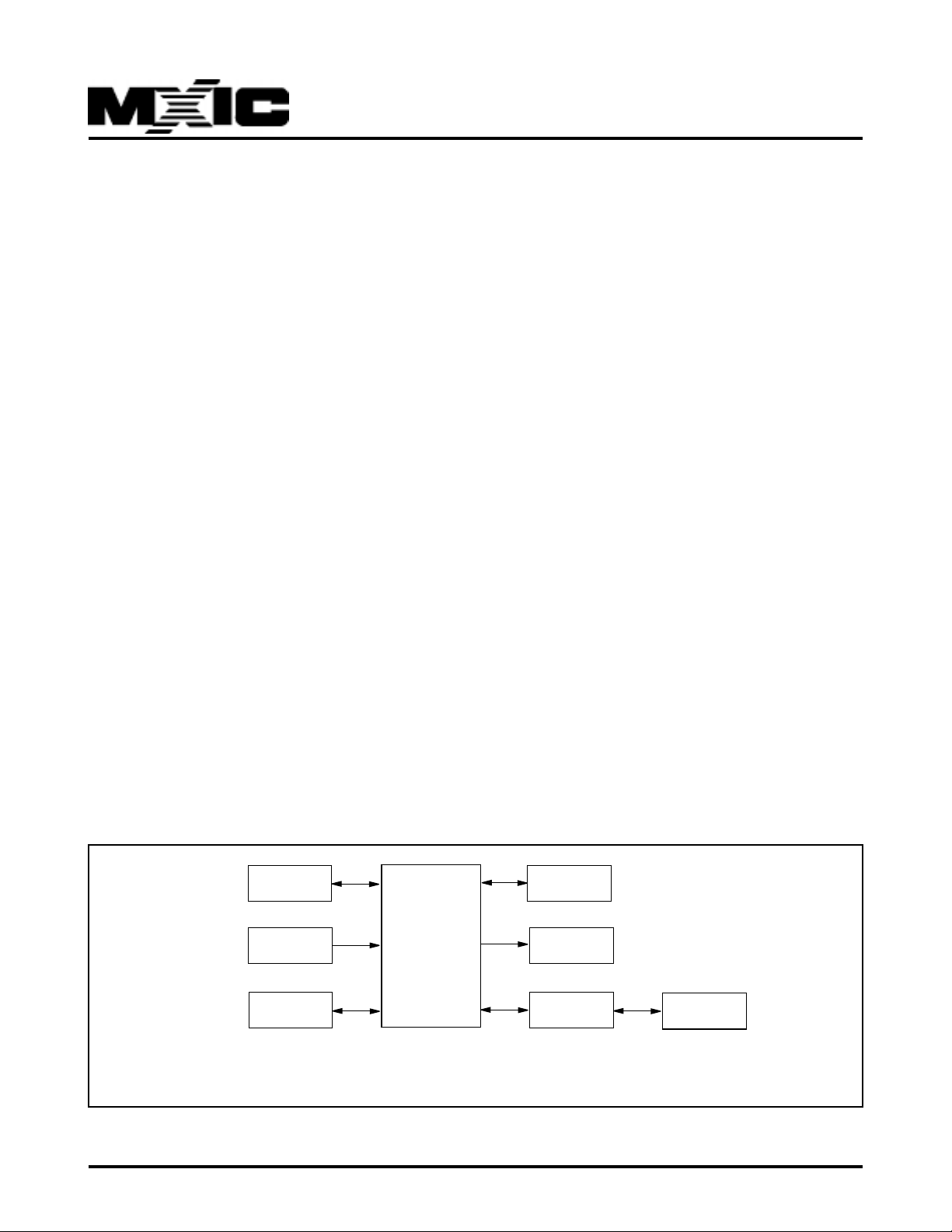

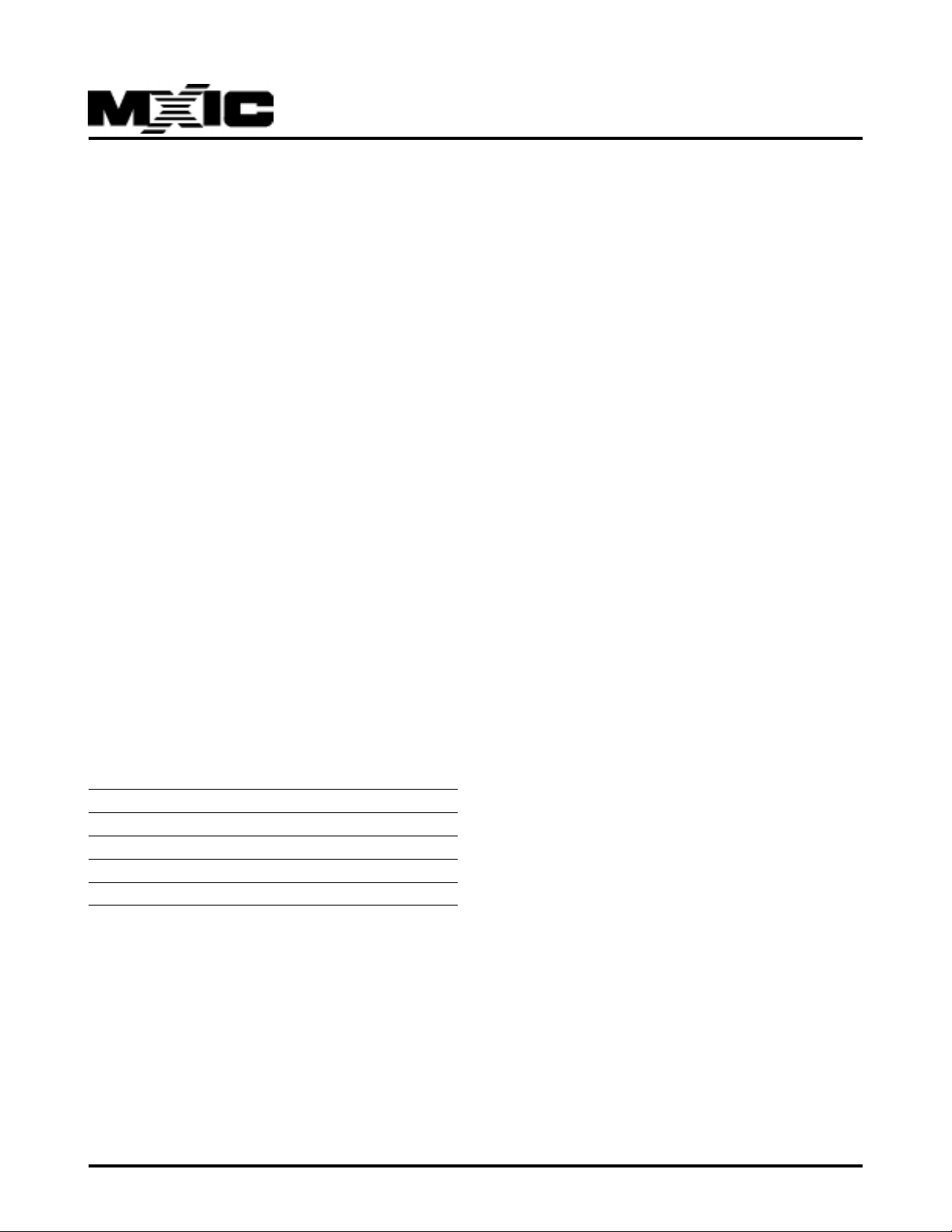

3.1 SYSTEM APPLICA TION BLOCK DIAGRAM

A system block diagram for the MX98715AEC-D based

Fast Ethernet adapter card is shown as f ollowing:

PCI Bus

Osc or Crystal

25MHz

EEPROM

MX98715AEC-D

Fig. 1

Boot ROM

LED

Magnetic

RJ45

P/N:PM0675

REV. 0.3, JUN. 21, 2000

1

MX98715AEC-D

3.2 PCI CONNECTION

The MX98715AEC-D provides direct PCI bus interface

to PCI connector. Board designers should especially

take care of the four pins of TDI,TDO,PRSNT1# &

PRSNT2# that are only related to PCI bus connector.

Boards that do not implement JTAG Boundary Scan

should tight TDI and TDO together to prevent the scan

chain from been broken.

Both pins PRSNT1# and PRSNT2# should be connected to ground indicating that the board is physically

presenting in a PCI slot and providing information about

the total power requirements ( less than 7.5W ) of the

board.

3.3 OSCILLA TOR OR CR YST AL

The MX98715AEC-D is designed to operate with a 25MHz

oscillator or crystal module. The clock specification of

this oscillator should meet 25MHz +/- 50PPM.

For oscillator application, X0 (pin87) should not connect

to ground.

3.4 BOOT R OM

The MX98715AEC-D support a direct boot ROM interface allowing diskless workstations to remotely download operating system from network server. F or proper

operation, the access time of adapt EPROM should not

excess 240ns.

3.5 SERIAL EEPROM

Current limiting resistor (560 ohm) should be added to

ensure proper operation. The f ollowing indicates the configuration setting table for LED display programming.

CSR 9 <28> 0 1

LED 0 Activity Link speed

CSR 9<29> 0 1

LED 1 Good Link Link Activity

CSR 9<30> 0 1

LED 2 Link Speed Colision

CSR 9<31> 0 1

LED 3 Receive F/H duplex

CSR 9<24> 0 1

LED 4 Colision PMEB

3.7 NETWORK INTERFACE TO MAGNETIC

COMPONENT

For isolating and impedance matching purpose, an isolating transformer with 1:1 transmit and 1:1 receive turns

ratio is required for transmit and receive twisted pair

interface. In Appendix B, several transformers that we

had verified successfully with MX98715AEC-D are listed

for quick reference purpose.

The MX98715AEC-D provides pins EECS,BP A0 (EECK),

BPA1 (EEDI) and BPD0 (EEDO) for directly accessing

the serial EEPROM. BPA0-1 and BPD0 serve as SK

(EECK), DI (EEDI) and DO (EEDO) respectively. The

contents of the EEPROM includes the ID information of

the MX98715AEC-D (V endorID, De viceID , Sub-vendorID ,

Sub-deviceID and MAC ID), and the configuration parameters for software driver. The EEPROM contents

should be programmed according to MXIC's definition

as mentioned in Appendix A. Detailed software programming example is described in section 4.5.

3.6 PROGRAMMABLE LED SUPPORT

The MX98715AEC-D provides five pins LED[0:4] to

control display LEDs. Displayed messages are programmable through setting CSR9 bits[31:28] & bit24. The

maximum sinking current of these output pins is 16mA.

P/N:PM0675 REV. 0.3, JUN. 21, 2000

3.8 OPTIMIZED EQUALIZER COMPONENTS

M XI C ’ Fast Ethernet solution utilizes adaptive equalizer to compensate the attenuation and phase distortion induced by different lengths of cable. To optimize

transmit and receive signal quality, pins RTX and

RTX2EQ should be connected to external resistors 560

ohm (±1%) and 1.4K ohm (±1%) and then to ground re-

spectively.

3.9 Remote-Power -On and ACPI application

MX98715AEC-D fully supports Remote-Power-ON and

ACPI spec that meet PC98 requirement for powersensitive applications. It accepts the following wake-up

events in the power-down mode.

* Reception of a Magic Pack et.

* Reception of a Network wake-up frame.

* Detection of change in the network link state.

2

MX98715AEC-D

T o put MX98715AEC-D into the sleep mode and enab le

the wake-up events detection are done as following:

1. Write 1 to PPMCSR [8] to enable power management

feature.

2. Write the value to PPMCSR [1:0] to determine which

power state to enter .

If D1, D2 or D3

state is set, the PC is still turned on

hot

and is commonly called entering the Remote W ak e-up

mode. Otherwise if the main power on a PC is totally

shut off, we call that it is in the D3

state or Remote

cold

Po wer-On mode. T o sustain the oper ation of the Lancard,

a 5V standby power is required. Once the PC is turned

on, MX98715AEC-D loads the magic ID from EEPROM

and set it up automatically. No register is needed to be

programmed. After then, simply turn of PC to enter D3

cold

state. In either Remote W ake-up mode or Remote P owerOn mode. The transceiver and the RX b lock are still alive

to monitor the network activity . If one of the three wak eup events occured, the following status is changed:

1. PPMCSR [15] (PME status) is set to 1.

2. CRS5 [28] (WKUPI) is set to 1.

3. PCI interrupt pin INTA# is asserted low.

4. LANWAKE pin is asserted high.

4. DRIVER PROGRAMMING GUIDE

tx_resource[i]=

(struct TX_RESOURCE *)((((unsigned int)tx_temp[i])+4)&

0xfffc);

}

for (i=0; i<NumTXBuffers; i++) {

/* initialize the own bit to host tdes0 */

tx_resource[i]->ownership=0x00;

tx_resource[i]->tstatus=0x0000;

tx_resource[i]->tdes0_unused=0x00;

/* fill buffer_1_address tdes2 */

get_ea((void far *)(tx_resource[i]->tx_buffer_data),

&physicaladdress);

tx_resource[i]->buff_1_addr=physicaladdress;

/* fill buffer_2_address tdes3 */

if (i==NumTXBuffers-1) j=0;

else j=i+1;

get_ea((void far *)(tx_resource[j], &physicaladdress);

tx_resource[i]->buff_2_addr=physicaladdress;

}

}

initializeTheReceiveRing()

{

unsigned int i,j;

unsigned long physicaladdress;

for (i=0; i<NumRXBuffers; i++) {

/* memory allocation for rx descriptor_buffer (allign 4) */

rx_resource[i]=

(struct RX_RESOURCE *)((((unsigned int)rx_temp[i])+4)&

0xfffc);

}

This chapter will provide you the necessary information

for programming driver for the MX98715AEC-D based

node. Initialization module is introduced first that describes how MX98715AEC-D is initialized before any

for (i=0; i<NumRXBuffers; i++) {

/* set the own bit to chip rdes0 */

rx_resource[i]->frame_length=RDES0_OWN_BIT;

rx_resource[i]->rstatus=0x0000;

other operations can commence, then followed by actual implementation examples for both transmit and receive operations.

/* fill rdes1 */

rx_resource[i]->command=RDES1_BUFFRX_BUFFER_SIZE+rxpkt_size[i];

4.1 INITIALIZA TION

initializeTheTransmitRing()

{

unsigned int i,j;

unsigned long physicaladdress;

for (i=0; i<NumTXBuffers; i++) {

/* memory allocation for tx descriptor_buffer (align 4) */

P/N:PM0675 REV. 0.3, JUN. 21, 2000

/* fill buffer_1_address rdes2 */

get_ea((void far *)(rx_resource[i]->rx_buffer_data),

&physicaladdress);

rx_resource[i]->buff_1_addr=physicaladdress;

/* fill buffer_2_address rdes3 */

if (i==NumRXBuffers-1) j=0;

else j=i+1;

3

MX98715AEC-D

get_ea((void far *)(rx_resource[j], &physicaladdress);

rx_resource[i]->buff_2_addr=physicaladdress;

}

}

initialize()

{

unsigned long physicaladdress;

NIC_read_reg(&csr6);

NIC_write_reg(&csr6,csr6.value&(~(CSR6_SR|CSR6_ST)));

delay(10);

InitializeTheTransmitRing (6);

InitializeTheReceiveRing (6);

NIC_write_reg(&csr0,CSR0_L_SWR);

delay(50);

NIC_write_reg(&csr0,csr0shadow);

get_ea((void far *)rx_resource[0],&physicaladdress);

NIC_write_reg(&csr3,physicaladdress);

get_ea((void far *)tx_resource[0],&physicaladdress);

NIC_write_reg(&csr4,physicaladdress);

NIC_read_reg(&csr16);

NIC_write_reg(&csr7,csr7shadow);

NIC_write_reg(&csr16,csr16shadow);

//Clear status register

NIC_write_reg(&csr5,(unsigned long)0xffffffff);

NIC_write_reg(&csr6,csr6shadow);

NIC_read_reg(&csr6);

setup_frame(TDES1_SETUP_LAST,perfect);

}

NIC_write_reg(&csr0,csr0.value|0x020000); //TAP=01

tx_pointer=tx_resource[0];

j=0;

editmode=1;

while (editmode) {

if ((tx_pointer->ownership & 0x80)==0) {

j++;

j%=tx_pkt_num;

if (tx_pointer->command & TDES1_LS_BIT)

tx_error_detect(tx_pointer->tstatus);

tx_pointer->ownership |= 0x80;

tx_pointer=tx_resource[j];

}

if (kbhit()) {

keycode_get();

if (M_code!=0) {

switch (M_code) {

case 0x1b: // ESC: quit

editmode=0;

break;

case 0x20:

NIC_read_reg(&csr6);

NIC_write_reg(&csr6,csr6.value^CSR6_ST);

break

default: break;

}

}

}

}

}

4.2 TRANSMISSION MODULE

bmtx()

{

unsigned char editmode, j;

struct TX_RESOURCE *tx_pointer;

initialize();

fill_pattern(6); //fill pattern

NIC_write_reg(&csr6,csr6.value&(~CSR6_ST)); //stop

NIC_read_reg(&csr6);

NIC_write_reg(&csr6,csr6.value|CSR6_SF); //store and

forward

NIC_read_reg(&csr0)

P/N:PM0675 REV. 0.3, JUN. 21, 2000

4.3 RECEPTION MODULE

bmrx()

{

unsigned char editmode,i,j;

unsigned long physicaladdress;

struct RX_RESOURCE *rcv_pointer;

initialize();

rcv_pointer=rx_resource[0];

j=0;

editmode=1;

while (editmode) {

// if data received

4

MX98715AEC-D

if ((rcv_pointer->frame_length & 0x8000)==0) {

j++;

j%=6;

if (rcv_pointer->rstatus & RDES0_LS)

rx_error_detect(rcv_pointer->rstatus);

rcv_pointer->frame_length |= 0x8000;

rcv_pointer=rx_resource[j];

}

if (kbhit()) {

keycode_get();

if (M_code!=0) {

switch (M_code) {

case 0x1b: // ESC: quit

editmode=0;

break;

default: break;

}

}

}

}

}

4.4 SPECIAL CODING of MX98715AEC-D

4.4.1 SPEED SELECTION

Speed selection for MX98715AEC-D is controlled by internal Nway registers.

The Internal NWay registers are remov ed and protocol

selection is controlled by Operation Mode Register

(CSR6) and 10Base-T Control Register (CSR14)

NWay Active 100F 100H 10F 10H

CSR6_PS 0 1 1 0 0

CSR6_PCS X 1 1 X X

CSR6_FD 1 1 0 1 0

CSR14_ANE 1 0 0 0 0

4.4.2 REGISTERS SETTING FOR DEVELOPING

Y OUR OWN DRIVER

The contents of CSR16 for MXIC 10/100Base NIC controllers should be set differently as follow:

CSR20.22 default value = 1 for IC revision H, for all

older IC revision, the default value =0.

CSR20.16 should be set to the same value as CSR20.22.

For PC99 certification, Rev.H IC is required, therefore

both CSR20.22 and CSR20.16 should be set to 1 by

drivers.

4.5 EEPROM ACCESSING

The following is a reference code for accessing the contents of EEPROM that stores ID information and node

configuration for the MX98715AEC-D .

/*************************************

* Read all content from EEPROM

**************************************/

eeprom_read()

{

unsigned int i, address, eeval;

char bit;

for (address=0; address<64; address++{

NIC_write_reg(&csr9,(unsigned long)0x04800);

eeprom_serial_in(0);

eeprom_serial_in(1); //command

eeprom_serial_in(1);

eeprom_serial_in(0);

for(i=0; i<6; i++){ //address serial in

bit = ((address>>(5-i)) & 0x01) ? 1:0;

eeprom_serial_in(bit);

}

eeval=0;

for(i=0; i<16; i++){ //dat serial out

NIC_write_reg(&csr9,(unsigned long)0x04803);

NIC_read_reg(&csr9);

eeval += (((unsigned long)0x008 & csr9.value)>>3)<<(15i);

NIC_write_reg(&csr9,(unsigned long)0x04801);

}

NIC_write_reg(&csr9,(unsigned long)0x04800);

c46[address*2] = eeval & 0x0ff;

c46[address*2+1] = (eeval >>8) & 0x0ff;

}

}

MX98715AEC-D = 0x0b3cXXXX

Meanwhile, you could directly access the Nway autonegotiation status from CSR20. Detailed format information please refer to MX98715AEC-D data sheet.

P/N:PM0675 REV. 0.3, JUN. 21, 2000

5

/*************************************

* Write a word to EEPROM

**************************************/

eeprom_write(unsigned int address, unsigned int data)

{

unsigned int i;

char bit;

eeprom_wen();

NIC_write_reg(&csr9,(unsigned long)0x04800);

eeprom_serial_in(0);

eeprom_serial_in(1); //command

eeprom_serial_in(0);

eeprom_serial_in(1);

for(i=0; i<6; i++){ //address serial in

bit = ((address>>(5-i)) & 0x01) ? 1:0;

eeprom_serial_in(bit);

}

for(i=0; i<16; i++){ //data serial in

bit = ((data>>(15-i)) & 0x01) ? 1:0;

eeprom_serial_in(bit);

}

NIC_write_reg(&csr9,(unsigned long)0x04800);

NIC_write_reg(&csr9,(unsigned long)0x04801);

i=0;

do{

i++;

NIC_read_reg(&csr9);

} while ((!(csr9.value & 0x08)) && (i<10000));

NIC_write_reg(&csr9,(unsigned long)0x04800);

if (i==10000) prstring (“Writing EEPROM error !!”);

eeprom_wds();

}

MX98715AEC-D

eeprom_wds()

{

NIC_write_reg(&csr9,(unsigned long)0x04800);

eeprom_serial_in(0);

eeprom_serial_in(1);

eeprom_serial_in(0);

eeprom_serial_in(0);

eeprom_serial_in(0);

eeprom_serial_in(0);

eeprom_serial_in(0);

eeprom_serial_in(0);

eeprom_serial_in(0);

eeprom_serial_in(0);

NIC_write_reg(&csr9,(unsigned long)0x04800);

}

/*************************************

* Serial inject a bit to EEPROM

**************************************/

eeprom_serial_in(unsigned int bit2)

{

NIC_write_reg(&csr9,(unsigned long)0x04800+4*bit2);

NIC_write_reg(&csr9,(unsigned long)0x04803+4*bit2);

NIC_write_reg(&csr9,(unsigned long)0x04801+4*bit2);

}

4.6 AUTO-COMPENSATION ON TRANSCEIVER

The driver must set bits CSR20<9> and CSR20<14> high to enable

auto-compensation function. Be careful not to clear these two bits

while accessing CRS20 at any time.

eeprom_wen()

{

NIC_write_reg(&csr9,(unsigned long)0x04800);

eeprom_serial_in(0);

eeprom_serial_in(1);

eeprom_serial_in(0);

eeprom_serial_in(0);

eeprom_serial_in(1);

eeprom_serial_in(1);

eeprom_serial_in(0);

eeprom_serial_in(0);

eeprom_serial_in(0);

eeprom_serial_in(0);

NIC_write_reg(&csr9,(unsigned long)0x04800);

}

P/N:PM0675 REV. 0.3, JUN. 21, 2000

6

MX98715AEC-D

5. PCB layout recommendation

Introduction:

Due to the high frequency and the increasing degree of integration, system board designs are becoming complex. The

purpose of this section is to give system designer more information. Such as pow er stability , placement, signal trace

routing and de-coupling capacitor.

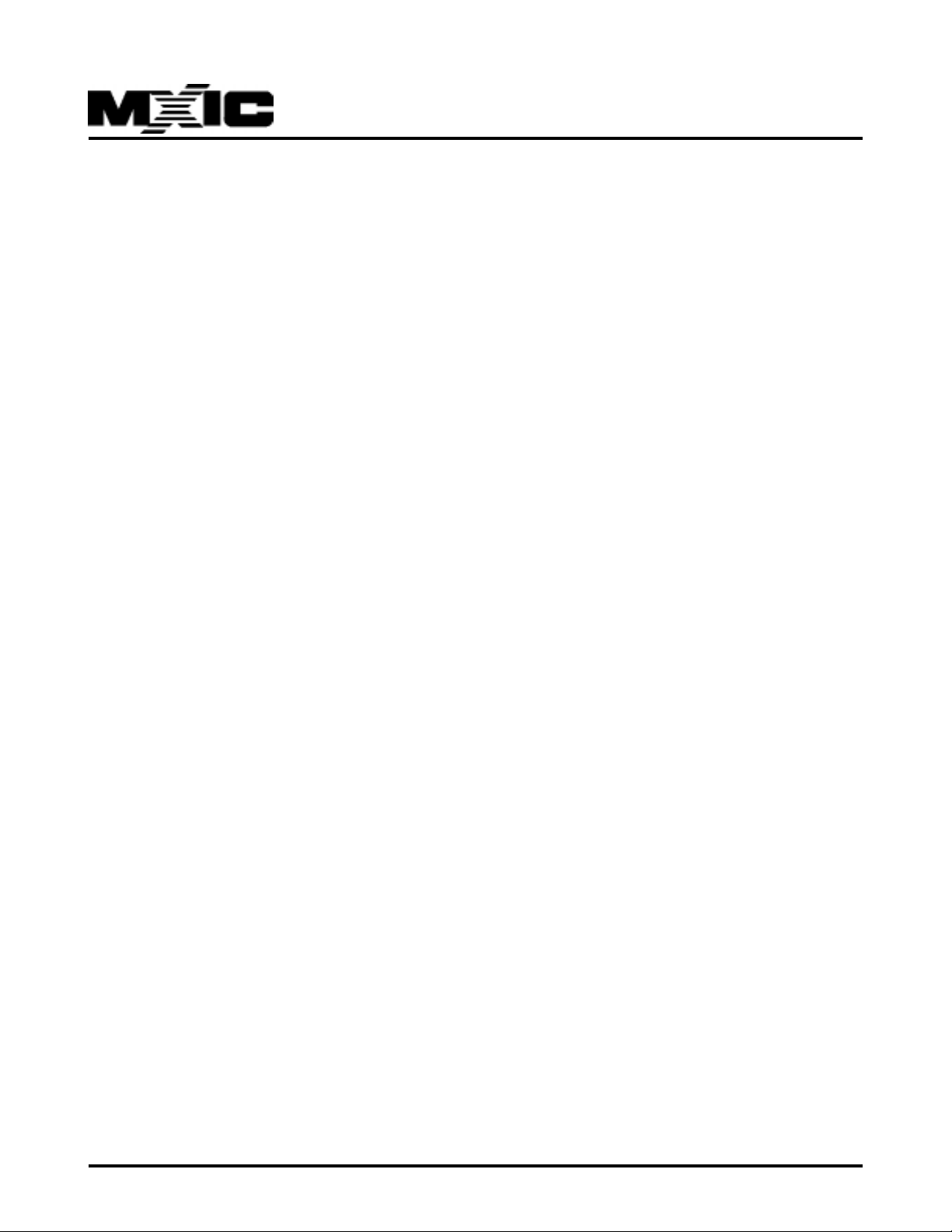

5.1 Power / Gr ound consideration

It is recommended to separate power plane into 3 domains (Power for digital , analog and receive section). Segmented power supplies reduces noise from one section to another .

It is also recommended to separate ground plane into 3 domains ( Digital Ground, Analog Ground and Receive

Ground). The reason f or separating is to prev ent digital noise from coupling onto the analog or receive ground.

All power/ground lines should be as wide as possible to allow noise de-coupling and efficient low resistive paths for

supply current.

5V

bead

V digital

V analog

GND GNDR

40mil

Bridge

V receive

GND GNDA

Depending upon the environment, any or all of these filters may be simplified.o

GNDR

(Receive ground)

GNDS

CardBus

GNDA

(Chassis

Interface

(Analog ground)

ground)

GND

(digital ground)

P/N:PM0675 REV. 0.3, JUN. 21, 2000

7

MX98715AEC-D

Oscillat

5.2 Board Layout / Trace Routing

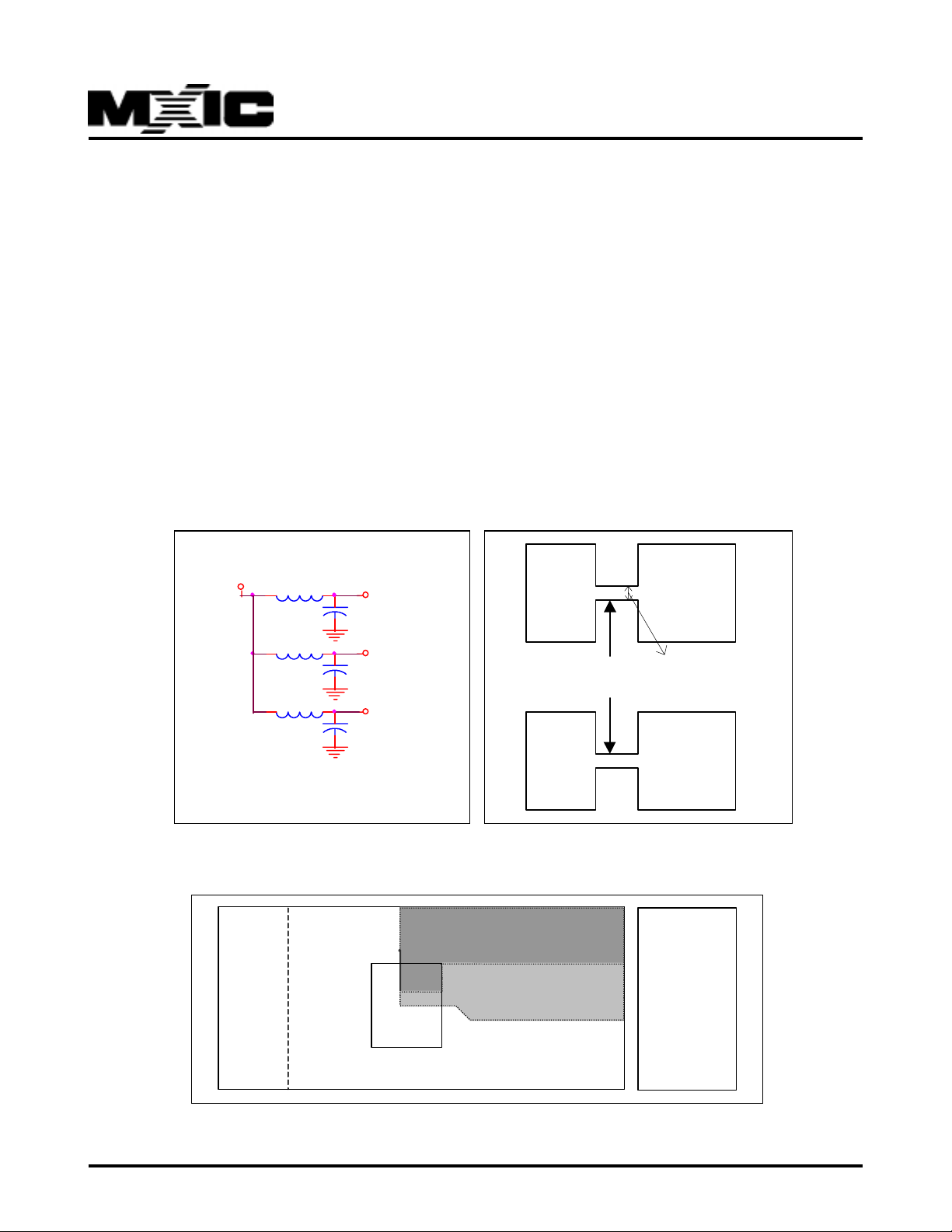

¨ 90 degree corners should be avoided, smooth cornering is preferred.

¨ Keep the lengths of clock lines short and minimize the numbers of VIAs.

¨ All pair lines ( i.e. TX+/- , RX+/-) are of the equal length and run in parallel

then possible noise is common and can be ignored on different inputs.

Magnetic

Tx+

Tx-

Tx+

Tx-

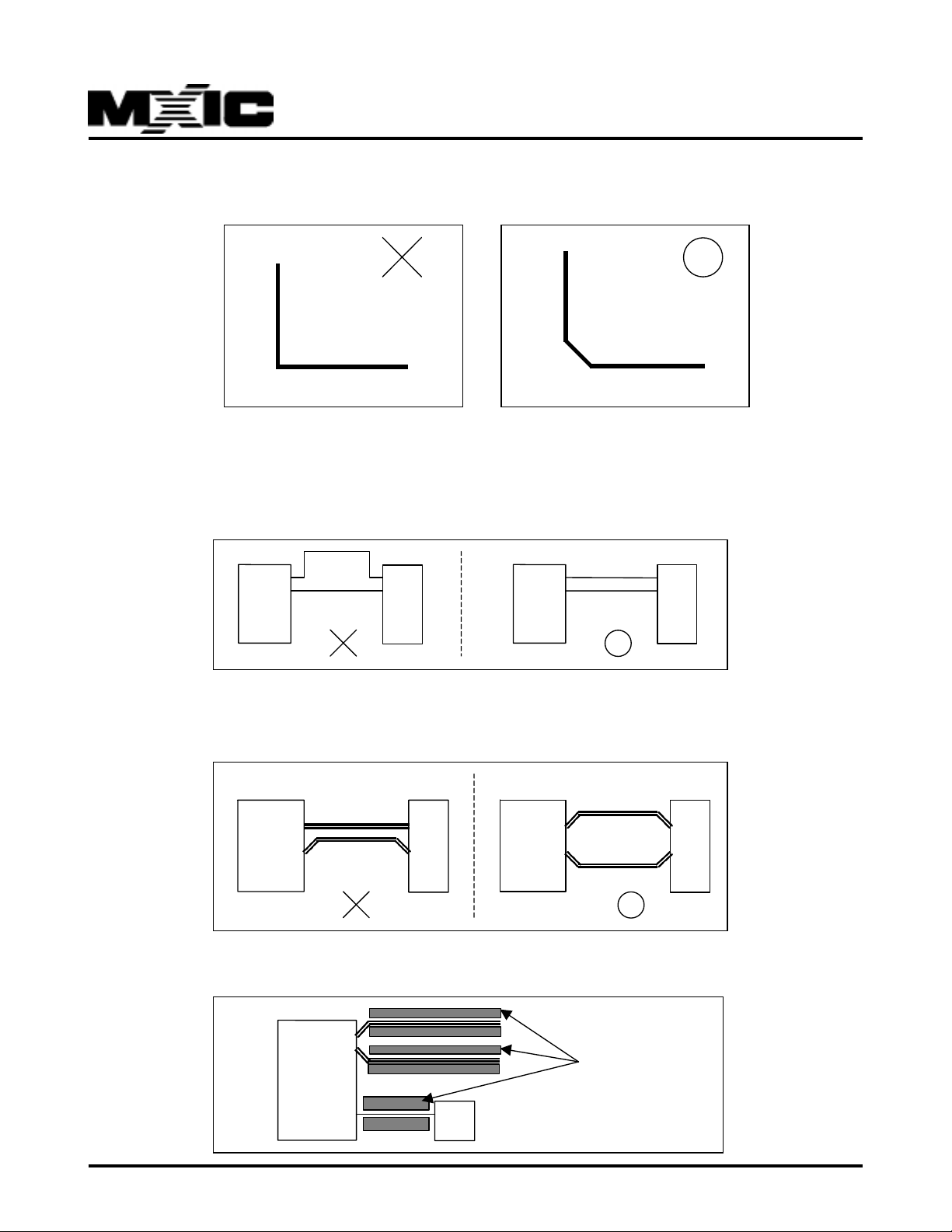

¨ A good practice is that never run transmit and receive pair too close.

Crosstalk may become a problem.

Tx+

Tx-

Rx+

Rx-

Magnetic

Tx+

Tx-

Rx+

Rx-

¨ The ground shield of clock line may reduce extra noise.

Magnetic

Magnetic

Tx+

Tx-

Rx+

Rx-

Ground Shield

or

P/N:PM0675 REV. 0.3, JUN. 21, 2000

8

Loading...

Loading...