MXIC MX27C512 Technical data

FEATURES

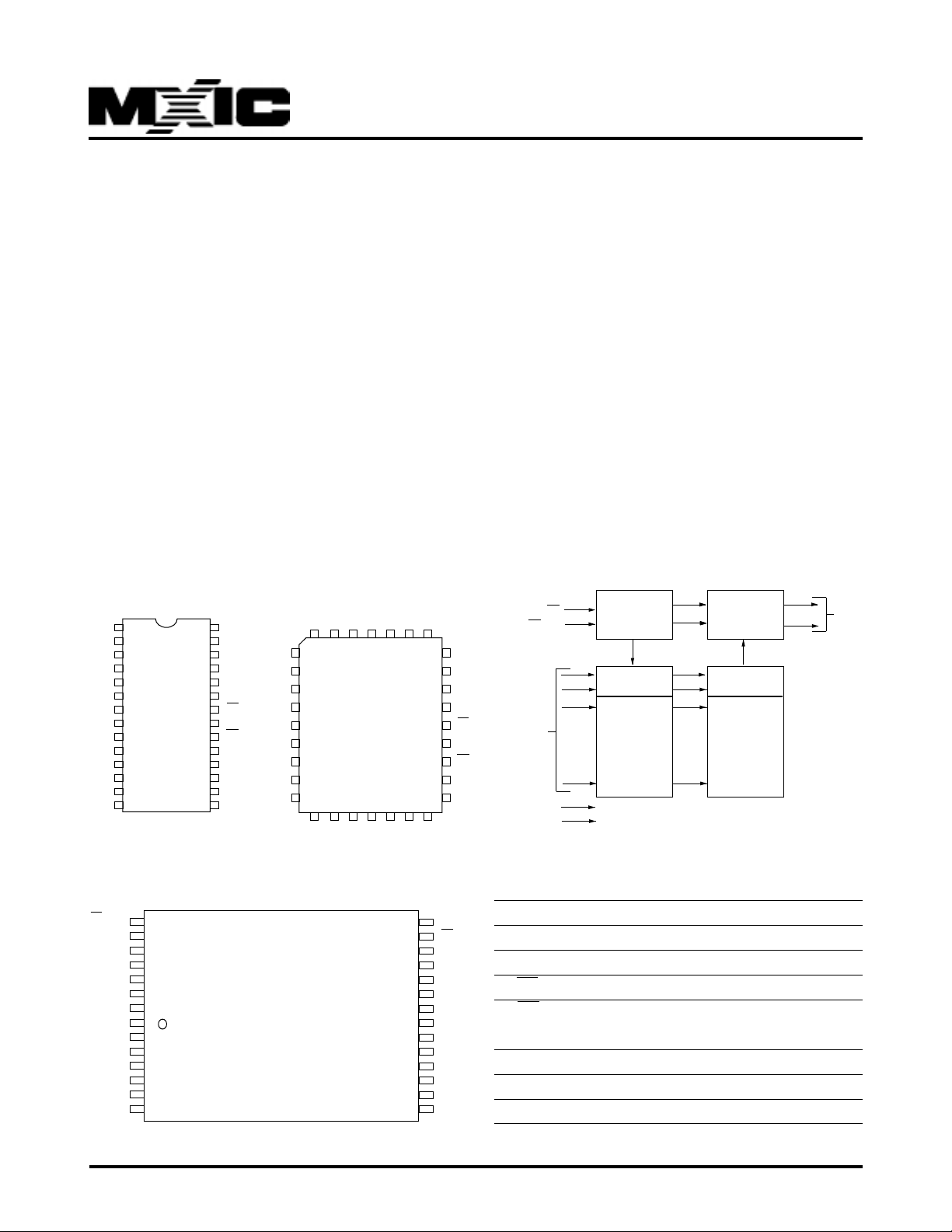

CONTROL

LOGIC

OUTPUT

BUFFERS

Q0~Q7

CE

OE/VPP

A0~A15

ADDRESS

INPUTS

Y-DECODER

X-DECODER

Y-SELECT

512K BIT

CELL

MAXTRIX

VCC

GND

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

MX27C512

512K-BIT [64Kx8] CMOS EPROM

• 64K x 8 organization

• Single +5V power supply

• +12.5V programming voltage

• Fast access time: 45/55/70/90/100/120/150ns

• Totally static operation

• Completely TTL compatible

GENERAL DESCRIPTION

The MX27C512 is a 5V only, 512K-bit, ultraviolet Erasable Programmable Read Only Memory. It is organized

as 64K words by 8 bits per word, operates from a single

+5volt supply, has a static standby mode, and features

fast single address location programming. All programming signals are TTL levels, requiring a single pulse. For

programming outside from the system, existing EPROM

PIN CONFIGURATIONS

PDIP

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

Q0

Q1

Q2

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

MX27C512

19

18

17

16

15

VCC

A14

A13

A8

A9

A11

OE/VPP

A10

CE

Q7

Q6

Q5

Q4

Q3

PLCC

A7

A12

4

5

A6

A5

A4

A3

9

A2

A1

A0

NC

Q0

MX27C512

13

14 17 20

A15NCVCC

1

32

A14

A13

30

29

25

21

• Operating current: 30mA

• Standby current: 100uA

• Package type:

- 28 pin plastic DIP

- 32 pin PLCC

- 28 pin 8 x 13.4 mm TSOP(I)

programmers may be used. The MX27C512 supports

intelligent fast programming algorithm which can result

in programming time of less than fifteen seconds.

This EPROM is packaged in industry standard 28 pin

dual-in-line packages 32 lead PLCC, and 28 lead

TSOP(I) packages.

BLOCK DIAGRAM

A8

A9

A11

NC

OE/VPP

A10

CE

Q7

Q6

8 x 13.4mm 28TSOP(I)

A11

A9

A8

A13

A14

A15

A12

A7

A6

A5

A4

A3

22

23

24

25

26

27

28

1

2

3

4

5

6

7

OE/VPP

VCC

P/N: PM0235

MX27C512

Q1

Q2

GND

Q3Q4Q5

NC

PIN DESCRIPTION

21

A10

20

CE

19

Q7

18

Q6

17

Q5

16

Q4

15

Q3

14

GND

13

Q2

12

Q1

11

Q0

10

A0

9

A1

8

A2

SYMBOL PIN NAME

A0~A15 Address Input

Q0~Q7 Data Input/Output

CE Chip Enable Input

OE/VPP Output Enable Input/Program Supply

Voltage

NC No Internal Connection

VCC Power Supply Pin (+5V)

GND Ground Pin

1

REV. 4.5, NOV. 09, 2001

MX27C512

FUNCTIONAL DESCRIPTION

THE PROGRAMMING OF THE MX27C512

When the MX27C512 is delivered, or it is erased, the

chip has all 512K bits in the "ONE" or HIGH state.

"ZEROs" are loaded into the MX27C512 through the

procedure of programming.

For programming, the data to be programmed is applied

with 8 bits in parallel to the data pins.

Vcc must be applied simultaneously or before Vpp, and

removed simultaneously or after Vpp. When

programming an MXIC EPROM, a 0.1uF capacitor is

required across Vpp and ground to suppress spurious

voltage transients which may damage the device.

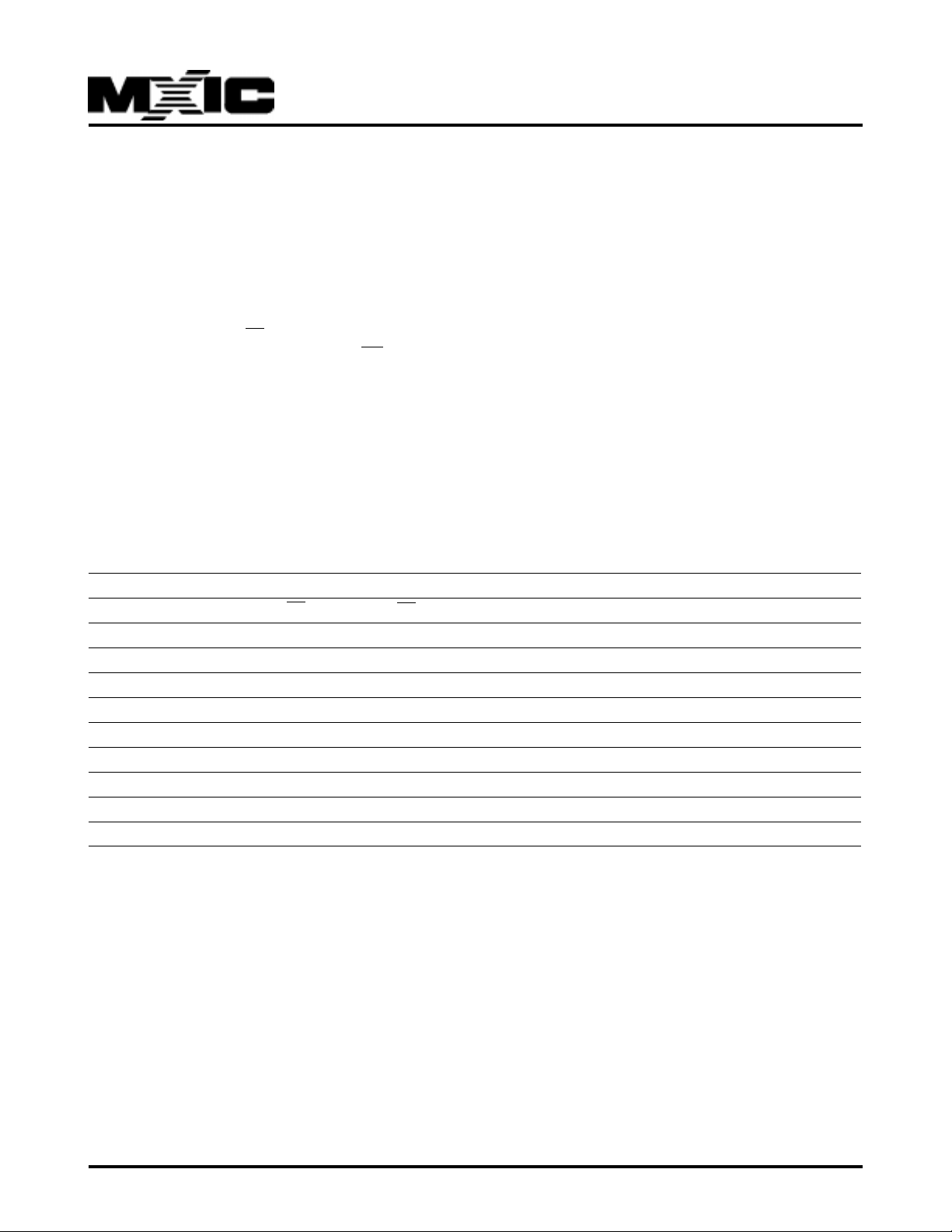

FAST PROGRAMMING

The device is set up in the fast programming mode when

the programming voltage OE/VPP = 12.75V is applied,

with VCC = 6.25 V, (Algorithm is shown in Figure 1). The

programming is achieved by applying a single TTL low

level 100us pulse to the CE input after addresses and

data line are stable. If the data is not verified, an

additional pulse is applied for a maximum of 25 pulses.

This process is repeated while sequencing through

each address of the device. When the programming

mode is completed, the data in all address is verified at

VCC = 5V ± 10%.

PROGRAM INHIBIT MODE

Programming of multiple MX27C512s in parallel with

different data is also easily accomplished by using the

Program Inhibit Mode. Except for CE and OE, all like

inputs of the parallel MX27C512 may be common. A

TTL low-level program pulse applied to an MX27C512

CE input with OE/VPP = 12.5 ± 0.5V will program that

MX27C512. A high-level CE input inhibits the other

MX27C512s from being programmed.

PROGRAM VERIFY MODE

Verification should be performed on the programmed

bits to determine that they were correctly programmed.

The verification should be performed with OE/VPP and

CE, at VIL. Data should be verified tDV after the falling

edge of CE.

AUTO IDENTIFY MODE

The auto identify mode allows the reading out of a binary

code from an EPROM that will identify its manufacturer

and device type. This mode is intended for use by

programming equipment for the purpose of

automatically matching the device to be programmed

with its corresponding programming algorithm. This

mode is functional in the 25°C ± 5°C ambient

temperature range that is required when programming

the MX27C512.

To activate this mode, the programming equipment

must force 12.0 ± 0.5(VH) on address line A9 of the

device. Two identifier bytes may then be sequenced

from the device outputs by toggling address line A0 from

VIL to VIH. All other address lines must be held at VIL

during auto identify mode.

Byte 0 ( A0 = VIL) represents the manufacturer code,

and byte 1 (A0 = VIH), the device identifier code. For the

MX27C512, these two identifier bytes are given in the

Mode Select Table. All identifiers for manufacturer and

device codes will possess odd parity, with the MSB (Q7)

defined as the parity bit.

READ MODE

The MX27C512 has two control functions, both of which

must be logically satisfied in order to obtain data at the

outputs. Chip Enable (CE) is the power control and

should be used for device selection. Output Enable

(OE) is the output control and should be used to gate

data to the output pins, independent of device selection.

Assuming that addresses are stable, address access

time (tACC) is equal to the delay from CE to output (tCE).

Data is available at the outputs tOE after the falling edge

of OE, assuming that CE has been LOW and addresses

have been stable for at least tACC - tOE.

STANDBY MODE

The MX27C512 has a CMOS standby mode which

reduces the maximum VCC current to 100uA . It is

placed in CMOS standby when CE is at VCC ± 0.3 V.

The MX27C512 also has a TTL-standby mode which

reduces the maximum VCC current to 1.5 mA. It is

placed in TTL-standby when CE is at VIH. When in

standby mode, the outputs are in a high-impedance

state, independent of the OE input.

P/N:PM0235

2

REV. 4.5, NOV. 09, 2001

MX27C512

TWO-LINE OUTPUT CONTROL FUNCTION

To accommodate multiple memory connections, a twoline control function is provided to allow for:

SYSTEM CONSIDERATIONS

During the switch between active and standby

conditions, transient current peaks are produced on the

rising and falling edges of Chip Enable. The magnitude

1. Low memory power dissipation,

2. Assurance that output bus contention will not

occur.

of these transient current peaks is dependent on the

output capacitance loading of the device. At a minimum,

a 0.1 uF ceramic capacitor (high frequency, low inherent

inductance) should be used on each device between

It is recommended that CE be decoded and used as the

primary device-selecting function, while OE be made a

common connection to all devices in the array and

connected to the READ line from the system control bus.

This assures that all deselected memory devices are in

their low-power standby mode and that the output pins

are only active when data is desired from a particular

VCC and GND to minimize transient effects. In addition,

to overcome the voltage drop caused by the inductive

effects of the printed circuit board traces on EPROM

arrays, a 4.7 uF bulk electrolytic capacitor should be

used between VCC and GND for each eight devices.

The location of the capacitor should be close to where

the power supply is connected to the array.

memory device.

MODE SELECT TABLE

PINS

MODE CE OE/VPP A0 A9 OUTPUTS

Read VIL VIL X X DOUT

Output Disable VIL VIH X X High Z

Standby (TTL) VIH X X X High Z

Standby (CMOS) VCC±0.3V X X X High Z

Program VIL VPP X X DIN

Program Verify VIL VIL X X DOUT

Program Inhibit VIH VPP X X High Z

Manufacturer Code(3) VIL VIL VIL VH C2H

Device Code(3) VIL VIL V IH VH 91H

NOTES: 1. VH = 12.0 V ± 0.5 V

2. X = Either VIH or VIL

P/N:PM0235

3. A1 - A8 = A10 - A15 = VIL(For auto select)

4. See DC Programming Characteristics for VPP voltage during

programming.

3

REV. 4.5, NOV. 09, 2001

Figure1. FAST PROGRAMMING FLOW CHART

ADDRESS = FIRST LOCATION

OE/VPP = 12.75V

PROGRAM ONE 100us PULSE

MX27C512

START

VCC = 6.25V

INCREMENT ADDRESS

INCREMENT ADDRESS

NO

LAST

ADDRESS ?

YES

PASS

NO

ADDRESS = FIRST LOCATION

PROGRAM ONE 100us PULSE

LAST

ADDRESS ?

X = 0

VERIFY BYTE

VCC = 5.25V

OE/VPP = VIL

COMPARE

ALL BYTES

TO ORIGINAL

DATA

DEVICE PASSED

YES

PASS

FAIL

NO

FAIL

INCREMENT X

X = 25 ?

YES

DEVICE FAILED

P/N:PM0235

4

REV. 4.5, NOV. 09, 2001

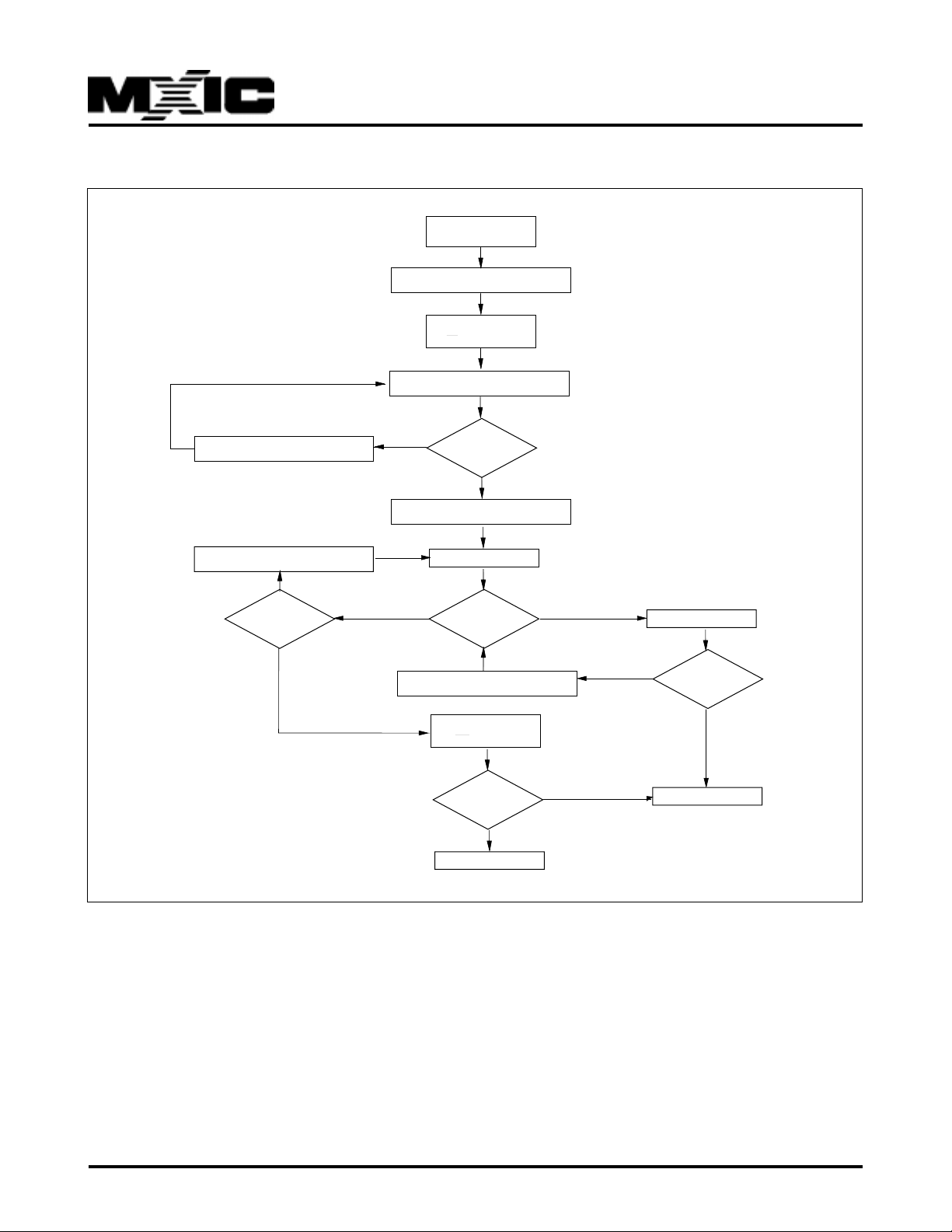

SWITCHING TEST CIRCUITS

MX27C512

DEVICE

UNDER

TEST

CL = 100 pF including jig capacitance (30pF for 45/55/70 ns parts)

SWITCHING TEST WAVEFORMS

AC driving levels

AC TESTING: AC driving levels are 2.4V/0.4V for commercial grade, 3.0V/0V for industrial grade.

Input pulse rise and fall times are < 10ns.

INPUT

CL

2.0V

0.8V

6.2K ohm

TEST POINTS

1.8K ohm

+5V

DIODES = IN3064

OR EQUIVALENT

2.0V

0.8V

OUTPUT

P/N:PM0235

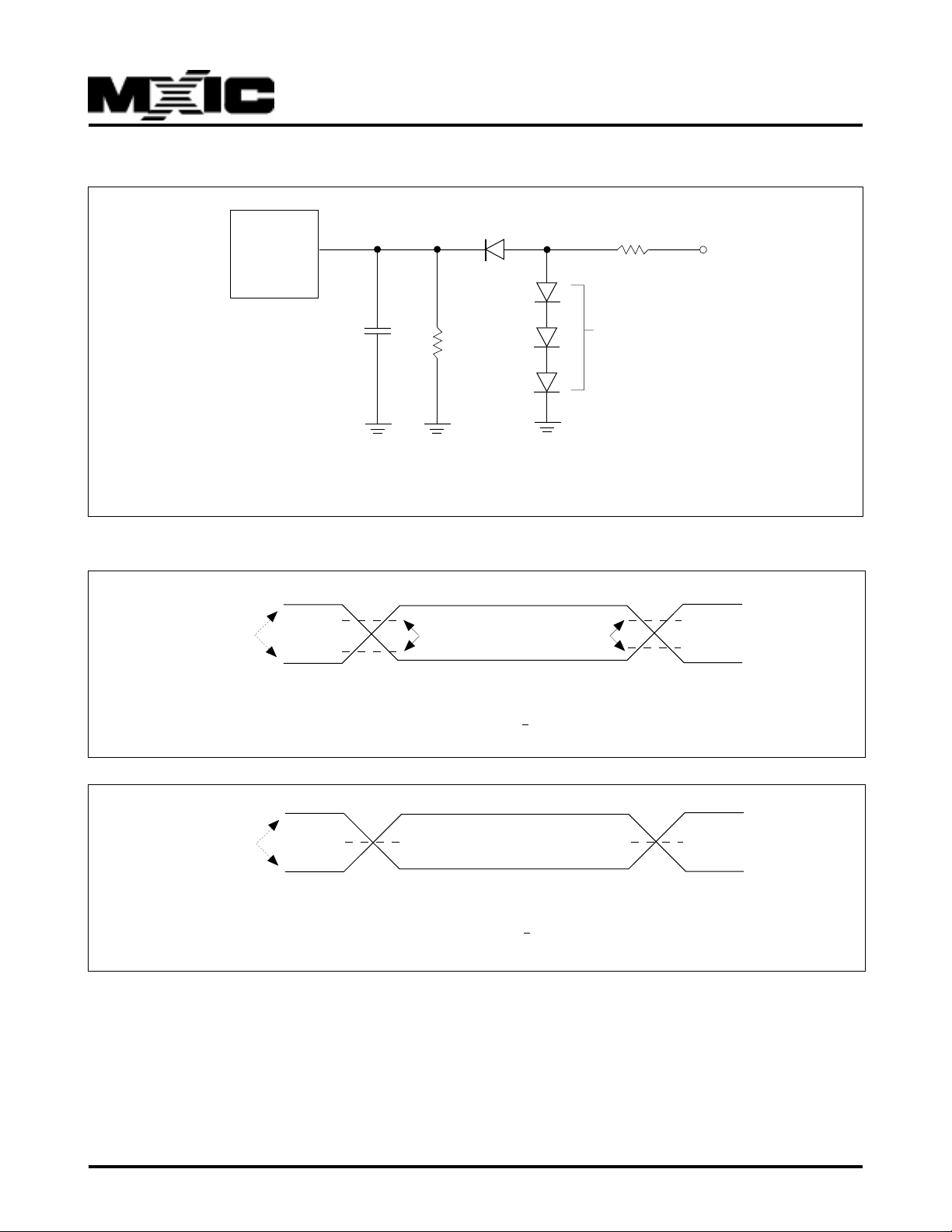

AC driving levels

1.5V

INPUT

AC TESTING: (1) AC driving levels are 3.0V/0V for both commercial grade and industrial grade.

Input pulse rise and fall times are < 10ns.

(2) For MX27C1000-45, MX27C1000/1001-55, MX27C1000/1001-70.

TEST POINTS

OUTPUT

5

1.5V

REV. 4.5, NOV. 09, 2001

Loading...

Loading...