MX COM Inc MX019TN, MX019P, MX019DW Datasheet

DATA BULLETIN

MX019

1998 MX-COM, INC. www.mxcom.com Tel: 800 638 5577 910 744 5050 Fax: 910 744 5054 Doc. # 20480077.006

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service marks are held by their respective companies

Quad Digital Control Amplifier

FEATURES APPLICATIONS

4 Digitally Controlled Amplifiers

15 Gain/Attenuation Steps

3 Amplifiers

± 3dB Range in 0.43dB Steps

1 'Volume' Amplifier

±14dB Range in 2dB Steps

8-Bit Serial Data Control

Output Mute Function

Gain Control Applications

Audio

Data

Telecommunications, Radio, & Industrial

Applications

2

3

3

3

4

4

SERIAL DATA

INPUT

LOAD/LATCH

LOAD/LATCH

CHIP ADDRESS

1

1

2

2

Ch1

Ch2

Ch4

Ch3

V

DD

V

BIAS

SERIAL CLOCK

INPUT

V

SS

8-BIT SERIAL DATA INPUT

CONTROLLED A UDIO OUTPUT LINES

VOLUME

The MX019 Digitally Adjustable Amplifier Array replaces trimmer potentiometers and volume controls in

Cellular, LMR, Telephony and Communication applications where voice or data signals need adjustment.

The MX019 is a single-chip LSI consisting of four digitally controlled amplifier stages, each with 15 distinct

gain/attenuation steps. Control of each individual amplifier is by an 8-bit serial data stream. Three of the

amplifier stages offer a 3dB range in steps of 0.43dB, while the remaining amplifier offers a 14dB range in

steps of 2dB, and is suggested for volume control applications. Each amplifier includes a 16th 'Off' state

which, when applied, mutes the output audio from that channel. This array uses a Chip Select input to select

one of two MX019s in a system. The MX019 uses the host microprocessor to digitally control the set-up of all

audio levels during development, production/calibration, and operation. Such applications include:

1. Control, adjustment, and set-up of communications equipment by an Intelligent ATE without manual

intervention – eg. Deviation, Microphone and L/S Levels, RX Audio Level etc.

2. Automatic Dynamic Compensation of drift caused by variations in temperature, linearity, etc.

3. Fully automated servicing and re-alignment.

The MX019 is a low-power, single 5-volt CMOS device available in 24-pin TSSOP (MX019TN), 16-pin SOIC

(MX019DW), 16-pin CDIP (MX019J) and 16-pin PDIP (MX019P) package versions.

Quad Digital Control Amplifier 2 MX019

1998 MX-COM, INC. www.mxcom.com Tel: 800 638 5577 910 744 5050 Fax: 910 744 5054 Doc. # 20480077.006

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service marks are held by their respective companies

CONTENTS

Section Page

1. Block Diagram 3

2. Signal List 4

3. External Components 5

4. General Description 5

4.1 Control Data and Timing 5

4.1.1 Data Loading 5

4.1.2 Timing 7

5. Application 8

6. Performance Specification 8

6.1 Electrical Performance 8

6.1.1 Absolute Maximum Ratings 8

6.1.2 Operating Limits 8

6.1.3 Operating Characteristics 9

6.2 Packaging 10

MX-COM, Inc. reserves the right to change specifications at any time and without notice.

Quad Digital Control Amplifier 3 MX019

1998 MX-COM, INC. www.mxcom.com Tel: 800 638 5577 910 744 5050 Fax: 910 744 5054 Doc. # 20480077.006

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service marks are held by their respective companies

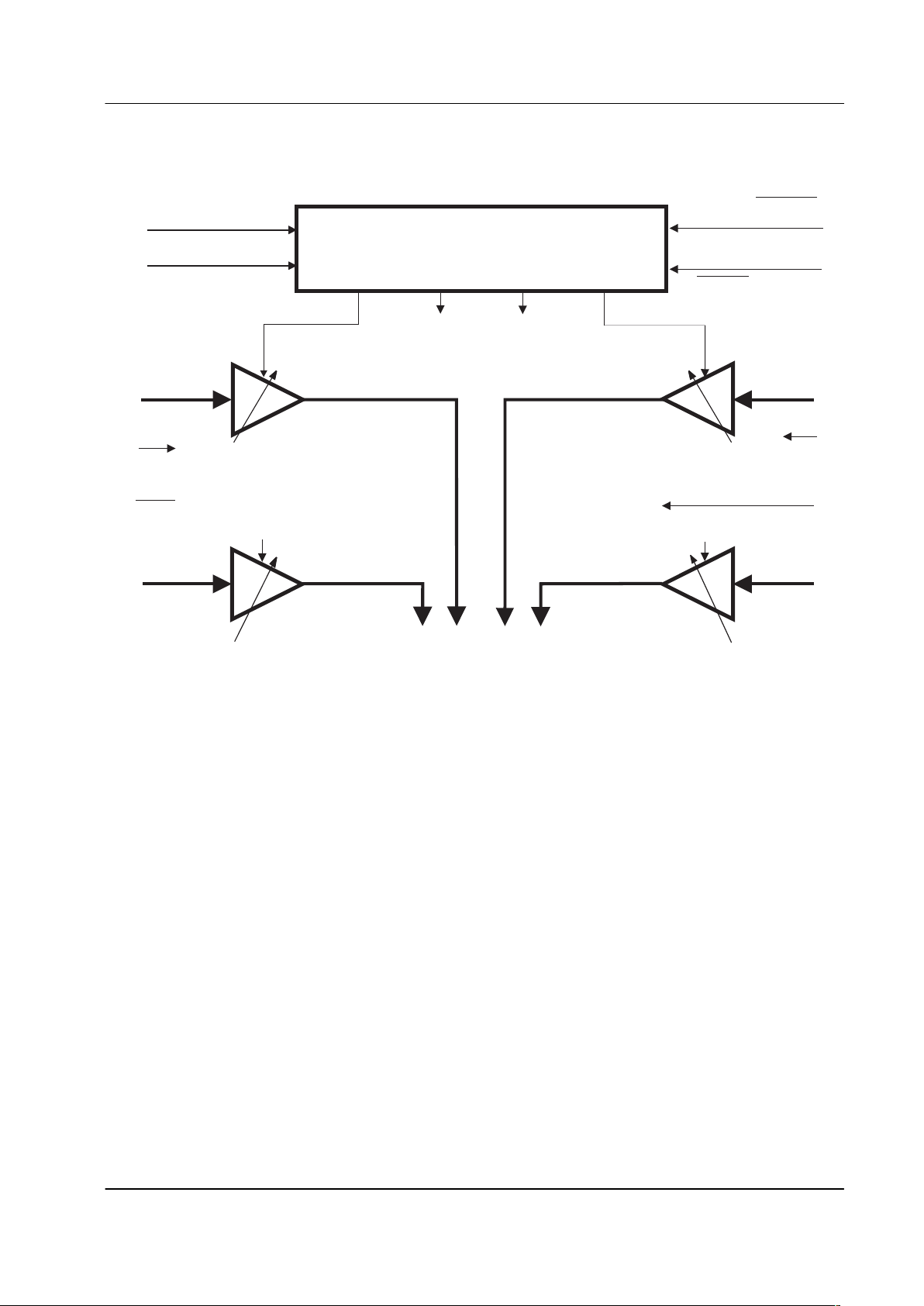

1. Block Diagram

2

3

3

3

4

4

SERIAL DATA

INPUT

LOAD/LATCH

LOAD/LATCH

CHIP ADDRESS

1

1

2

2

Ch1

Ch2

Ch4

Ch3

V

DD

V

BIAS

SERIAL CLOCK

INPUT

V

SS

8-BIT SERIAL DATA INPUT

CONTROLLED AUDIO OUTPUT LINES

VOLUME

Figure 1: Device Block Diagram

Quad Digital Control Amplifier 4 MX019

1998 MX-COM, INC. www.mxcom.com Tel: 800 638 5577 910 744 5050 Fax: 910 744 5054 Doc. # 20480077.006

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service marks are held by their respective companies

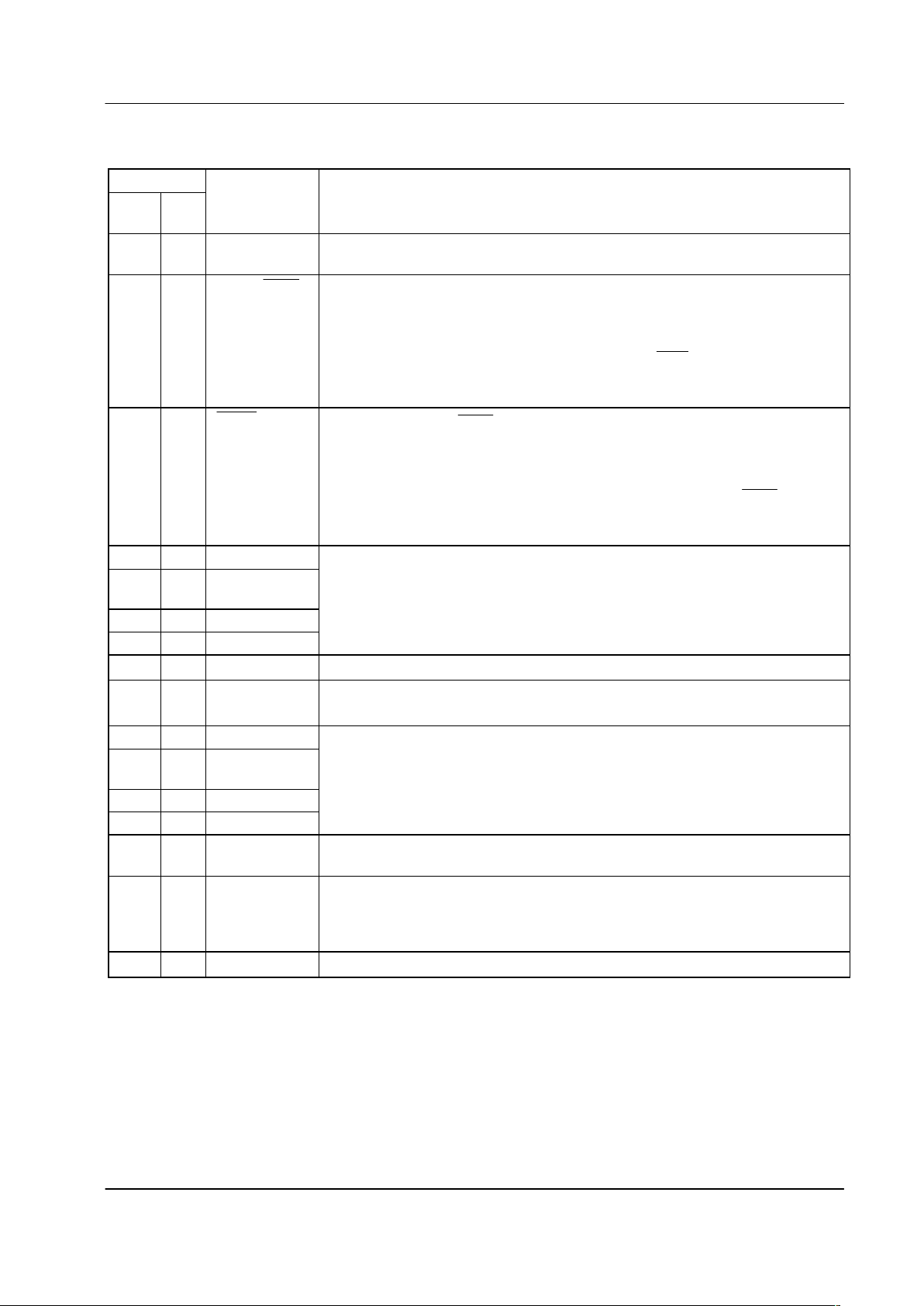

2. Signal List

Pin No.

J/PDWTN

Name Description

1 1 Serial Clock This external clock pulse input is used to “clock in” the Control Data. See

Figure 3. This input has an internal 1M pullup resistor.

22

Load/

Latch

This input governs the loading and execution of the control data. During

serial data loading this input should be kept at a logical '0' to ensure that data

rippling past the latches has no effect. When all 8 bits have been loaded,

this input should be strobed '0 - 1 - 0' to latch the new data in. Data is

executed on the falling edge of the strobe. If the

Load

/Latch input is used

this pin should be left open circuit. This input has an internal 1M pullup

resistor.

34

LATCH/LOAD

This inverted Load/

Latch

input governs the loading and execution of control

data. During serial data loading this input should be kept at a logical '1' to

ensure that data rippling past the latches has no effect. When all 8 bits have

been loaded, this input should be strobed '1' - '0' - '1' to latch the new data in.

Data is executed on the rising edge of the strobe. If the Load/

Latch

input is

used this pin should be left open circuit. This input has an internal 1M

pulldown resistor.

4 5 Ch1 Input

Analog Inputs :

5 6 Ch2 Input These individual amplifier inputs are self-biasing; AC input analog signals

must be capacitively coupled to these pins, as shown in Figure 2.

6 7 Ch3 Input Note that amplifiers Ch1 to Ch4 are 'inverting amplifiers.'

7 8 Ch4 Input

812 V

SS

Negative supply rail (GND).

913 V

BIAS

The output of the on-chip bias circuitry, held at VDD/2. This pin should be

decoupled to V

SS

as shown in Figure 2.

10 14 Ch4 Output

Controlled Analog Outputs :

11 17 Ch3 Output These are individual "Gain Controlled" amplifier outputs. Ch1 to Ch3 range

from -3dB to +3dB in 0.43dB steps, Ch4 can be utilized as a volume control,

12 18 Ch2 Output ranging from -14dB to +14dB in 2.0dB steps. In the “OFF” mode there is no

13 19 Ch1 Output output from the selected amplifier.

14 20 Chip Address A logic input to select one of two MX019 ICs in a system (see Table 1). This

input has an internal 1M pulldown resistor.

15 23 Control Data

Input

Operation of the 4 amplifier channels (Ch1 – Ch4) is controlled by the 8 bits

of data entered serially at this pin. The data is entered (bit 7 to bit 0) on the

rising edge of the external Serial Clock. The data format is described in

Table 1, Table 2 and Figure 3. This input has an internal 1M pullup resistor.

16 24 V

DD

Positive supply rail. A single +5V power supply is required.

Loading...

Loading...