MX COM Inc CMX631AD4, CMX631AP3, CMX631AD5 Datasheet

DATA BULLETIN

CMX631A

© 1999 MX

•COM Inc. www.mxcom.com Tele: 800 638-5577 336 744-5050 Fax: 336 744-5054 Doc. # 20480177.004

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service marks are held by their respective companies.

Low Voltage

SPM Detector

PRELIMINARY INFORMATION

Features Applications

•

Detects 12kHz or 16kHz SPM

Frequencies

•

Tone Follower and Packet Mode

Outputs

•

High Speech-Band Rejection

Properties

•

Low Power Operation (3.0V < 0.8mA)

•

Call Charge Applications on PABX Line

Cards

•

Complex and/or Simple telephone

Systems

•

Remote Telephone/Payphones

+

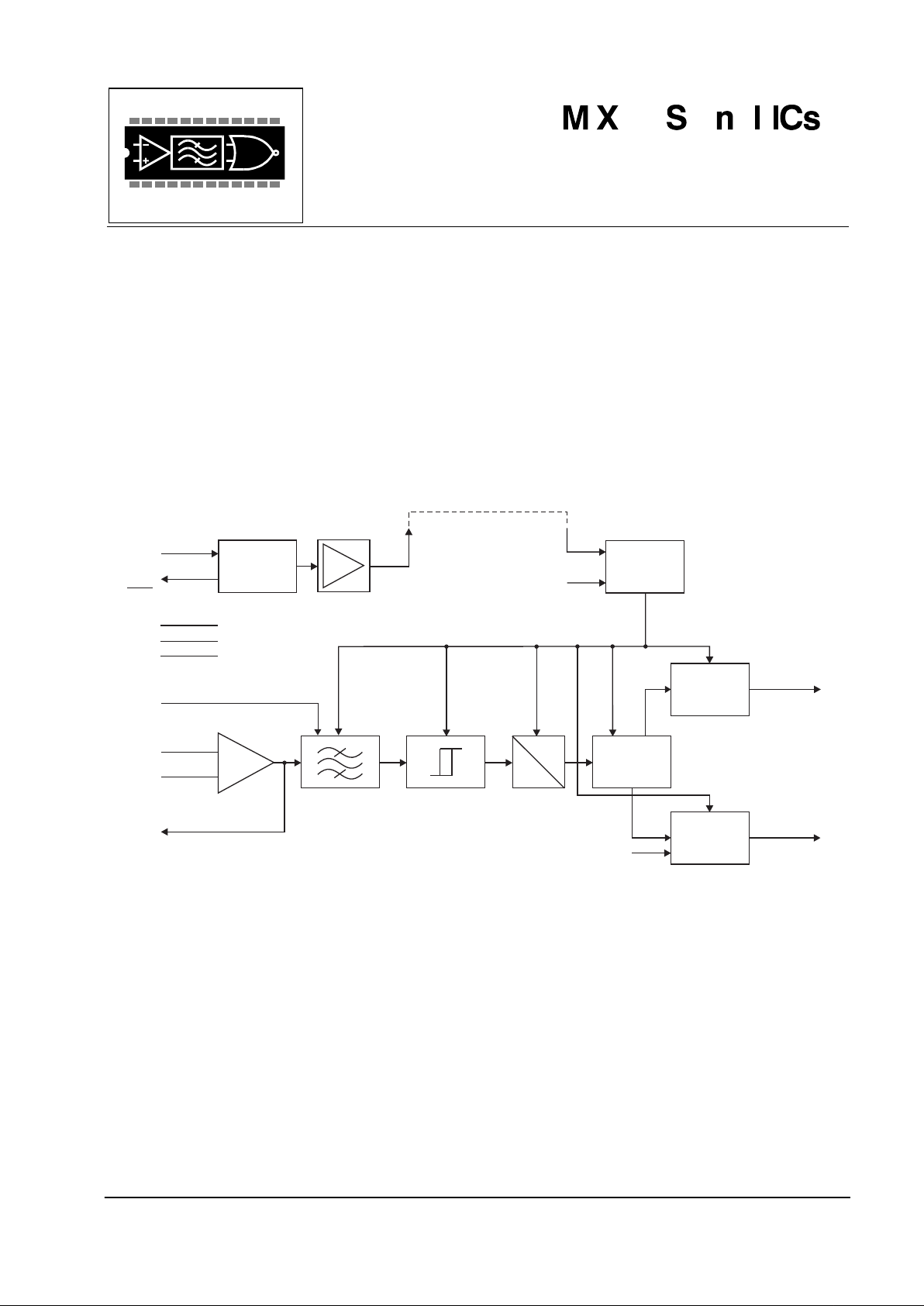

-

1

32

PERIOD

MEASURE

TONE

FOLLOWER

LOGIC

PACKET

TONE

LOGIC

DIVIDER

SIGNAL IN (-)

AMP OUT

XTAL/CLOCK

SYSTEM (12kHz/16kHz)

SYSTEM

SYSTEM

CLOCK IN

CLOCK OUT

TONE FOLLOWER

OUTPUT

V

SS

V

DD

V

BIAS

P ACKET MODE

OUTPUT

SIGNAL IN (+)

LEVEL DETECTOR

+20dB

12kHz/16kHz

XTAL

CLOCK

DIVIDERS

INPUT AM P

XTAL/CLOCK

OSCILLATOR

The CMX631A is a low-power, system-selectable Subscriber Pulse Metering (SPM) detector that indicates the

presence of both 12kHz or 16kHz telephone call-charge frequencies on a telephone line.

Deriving its input directly from the telephone line, input amplitude/sensitivities are component adjustable to the

user's national ‘Must/Must-Not Decode’ specifications via an on-chip input amplifier. The 12kHz and 16kHz

frequency limits are accurately defined by the use of an external 3.579545MHz telephone-system Xtal or

clock-pulse input.

The CMX631A demonstrates exceptional 12kHz and 16kHz performance in the presence of both voice and

noise. This device may operate from a single or differential analog signal input, from which two individual

logic outputs will be produced; a Tone Follower Output or a Packet Mode Output.

This system (12kHz/16kHz) selectable integrated circuit, requires a 2.7V to 5.5V power supply, which may be

line-powered, is available in the following packages: 24-pin SSOP (CMX631AD5), 16-pin SOIC

(CMX631AD4), and 16-pin PDIP (CMX631AP3). Additional package styles may be available to meet specific

design requirements.

Low Voltage SPM Detector 2 CMX631A PRELIMINARY INFORMATION

© 1999 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 336 744-5050 Fax: 336 744-5054 Doc. # 20480177.004

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service marks are held by their respective companies.

CONTENTS

Section Page

1 Block Diagram................................................................................................................3

2 Signal List.......................................................................................................................4

3 External Components....................................................................................................5

4 General Description.......................................................................................................6

4.1 Tone Follower Mode............................................................................................................ 6

4.2 Packet Mode........................................................................................................................ 6

4.3 Sensitivity Setting ................................................................................................................ 6

4.3.1 Input Gain Calculation............................................................................................................6

4.3.2 Input Gain Components .........................................................................................................8

4.4 ‘WILL’/’WILL-NOT’ Detect Frequencies............................................................................... 8

5 Applications ...................................................................................................................8

5.1 Input Configurations ............................................................................................................ 8

5.1.1 Protection Against High Voltages...........................................................................................8

5.1.2 Aliasing...................................................................................................................................9

6 Performance Specification............................................................................................9

6.1 Electrical Specifications....................................................................................................... 9

6.1.1 Absolute Maximum Ratings....................................................................................................9

6.1.2 Operating Limits...................................................................................................................10

6.1.3 Operating Characteristics.....................................................................................................10

6.2 Packages........................................................................................................................... 11

MX-COM, Inc. reserves the right to change specifications at any time and without notice.

Low Voltage SPM Detector 3 CMX631A PRELIMINARY INFORMATION

© 1999 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 336 744-5050 Fax: 336 744-5054 Doc. # 20480177.004

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service marks are held by their respective companies.

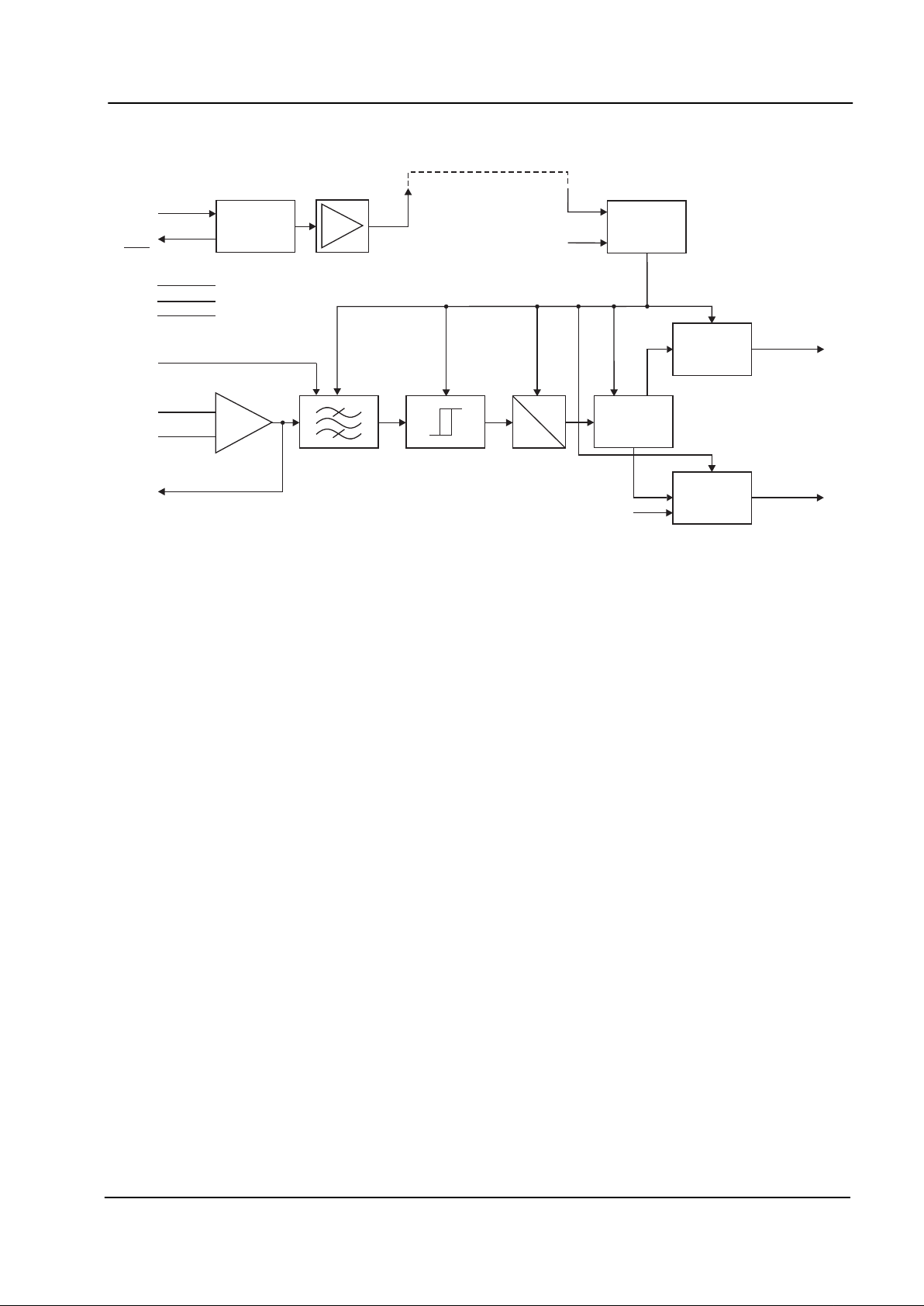

1 Block Diagram

+

-

1

32

PERIOD

MEASURE

TONE

FOLLOWER

LOGIC

PACKET

TONE

LOGIC

DIVIDER

SIGNAL IN (-)

AMP OUT

XTAL/CLOCK

SYSTEM (12kHz/16kHz)

SYSTEM

SYSTEM

CLOCK IN

CLOCK OUT

TONE FOLLOWER

OUTPUT

V

SS

V

DD

V

BIAS

P ACKET MODE

OUTPUT

SIGNAL IN (+)

LEVEL DETECTOR

+20dB

12kHz/16kHz

XTAL

CLOCK

DIVIDERS

INPUT AM P

XTAL/CLOCK

OSCILLATOR

Figure 1: Block Diagram

Low Voltage SPM Detector 4 CMX631A PRELIMINARY INFORMATION

© 1999 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 336 744-5050 Fax: 336 744-5054 Doc. # 20480177.004

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service marks are held by their respective companies.

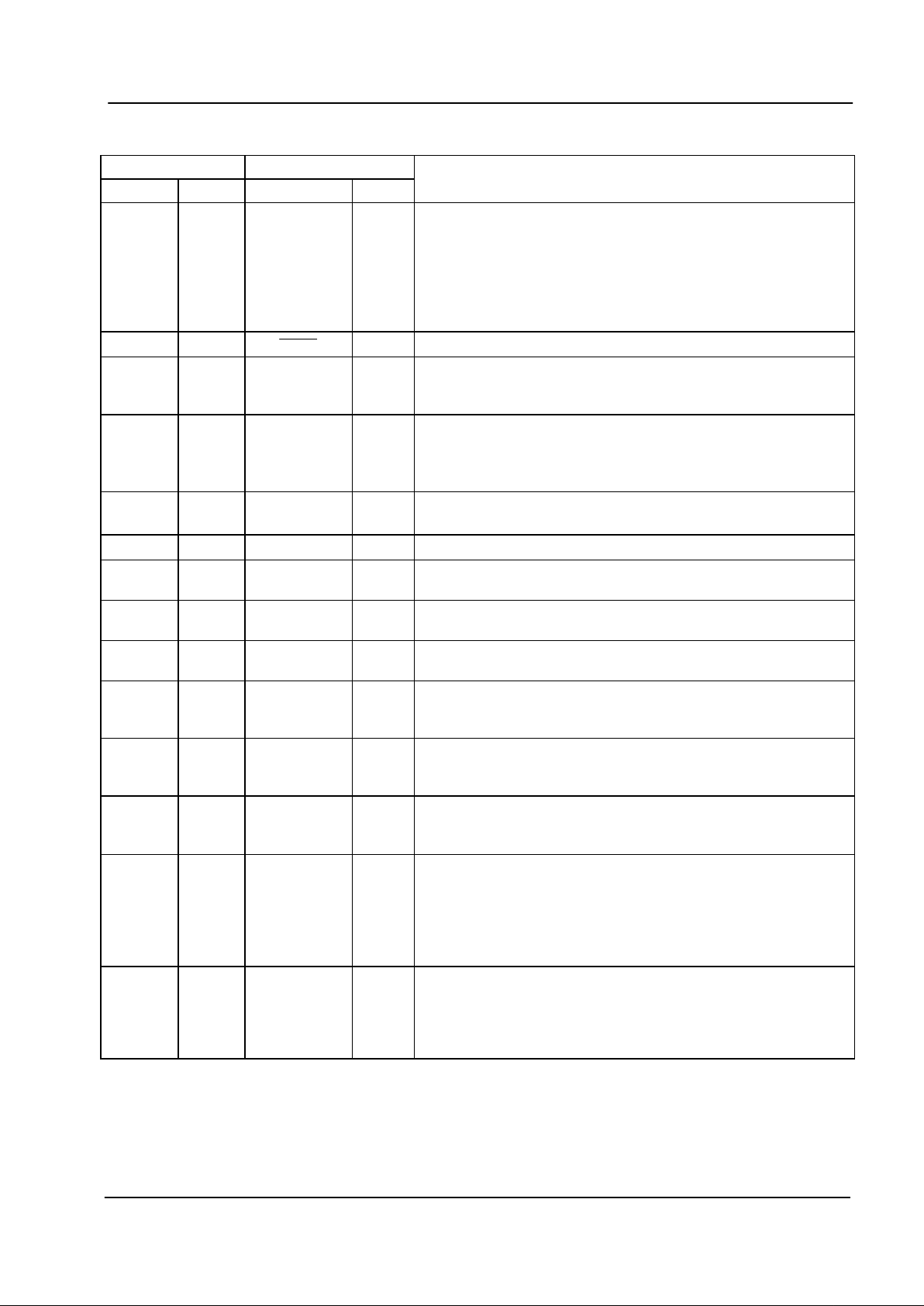

2 Signal List

Packages Signal

D5 D4/P3 Name Type

Description

1 1 Xtal/Clock input The input to the on-chip clock oscillator; for use with a

3.579545MHz Xtal in conjunction with the Xtal output; circuit

components are on-chip. When using a Xtal input, the Clock

Out pin should be connected directly to the Clock In pin. If a

clock pulse input is used at the Clock In pin, this (Xtal/Clock)

pin must be connected directly to V

DD

See Figure 2 and

Section 3.

42

XTAL

output The output of the on-chip clock oscillator inverter.

5 3 Clock Out output The buffered output of the on-chip-clock oscillator inverter. If a

Xtal input is used, this output should be connected directly to

the Clock In pin.

6 4 Clock In input The 3.579545MHz clock pulse input to the internal clock

dividers. If an externally generated clock pulse is used, the

Xtal/Clock input pin should be connected to V

DD

. Reference

Section 3.

87V

BIAS

power The output of the on-chip analog bias circuitry. Held internally

at V

DD

/2, this pin should be bypassed to VSS. See Figure 2.

12 8 V

SS

power Negative supply (GND).

13 9 Signal In + input The positive input to the input gain adjusting signal amplifier.

Reference Section 4.3 and 4.4.

17 10 Signal In - input The negative input to the input gain adjusting signal amplifier.

Reference Section 4.3 and 4.4.

18 11 Amp Out input The output of the input gain adjusting signal amplifier.

Reference Section 4.3 and 4.4.

19 13 Tone

Follower

Mode

output This output provides a logic 0 for the period of a detected tone

and a logic 1 for a NOTONE detection. See Section 4.1 and

Figure 3.

20 14 Packet Mode output This output provides a logic 0 for a detected tone and a logic 1

for NOTONE detection and will ignore a small fluctuation or

fade during the tone signal. See Section 4.2 and Figure 3.

21 15 System input This logic input selects the device operation to either 12kHz

(logic 1) or 16kHz (logic 0) SPM systems. This input has an

internal 1MΩ pull-up resistor (12kHz).

24 16 V

DD

power Positive supply. A single, stable power supply is required.

Critical levels and voltages within the CMX631A are dependent

upon this supply. This pin should be bypassed to V

SS

by a

capacitor mounted close to the pin. Note: If this device is line

powered, the resulting power supply must be stable. See

Section 5.1.1.

2, 3, 7,

9, 10,

11, 14,

15, 16,

22, 23

5,6,12 N/C No internal connection; leave open circuit.

Table 1: Signal List

Loading...

Loading...