MUSIC MU9C4K64-90TDC, MU9C4K64-90TDI, MU9C4K64-70TDC, MU9C4K64-12TDI, MU9C4K64-35TDC Datasheet

...

Data Sheet

MUSIC Semiconductors, the MUSIC logo, and the phrase “MUSIC Semiconductors” are

June 1 2002 Rev. 6

Registered trademarks of MUSIC Semiconductors. MUSIC is a trademark of

MUSIC Semiconductors.

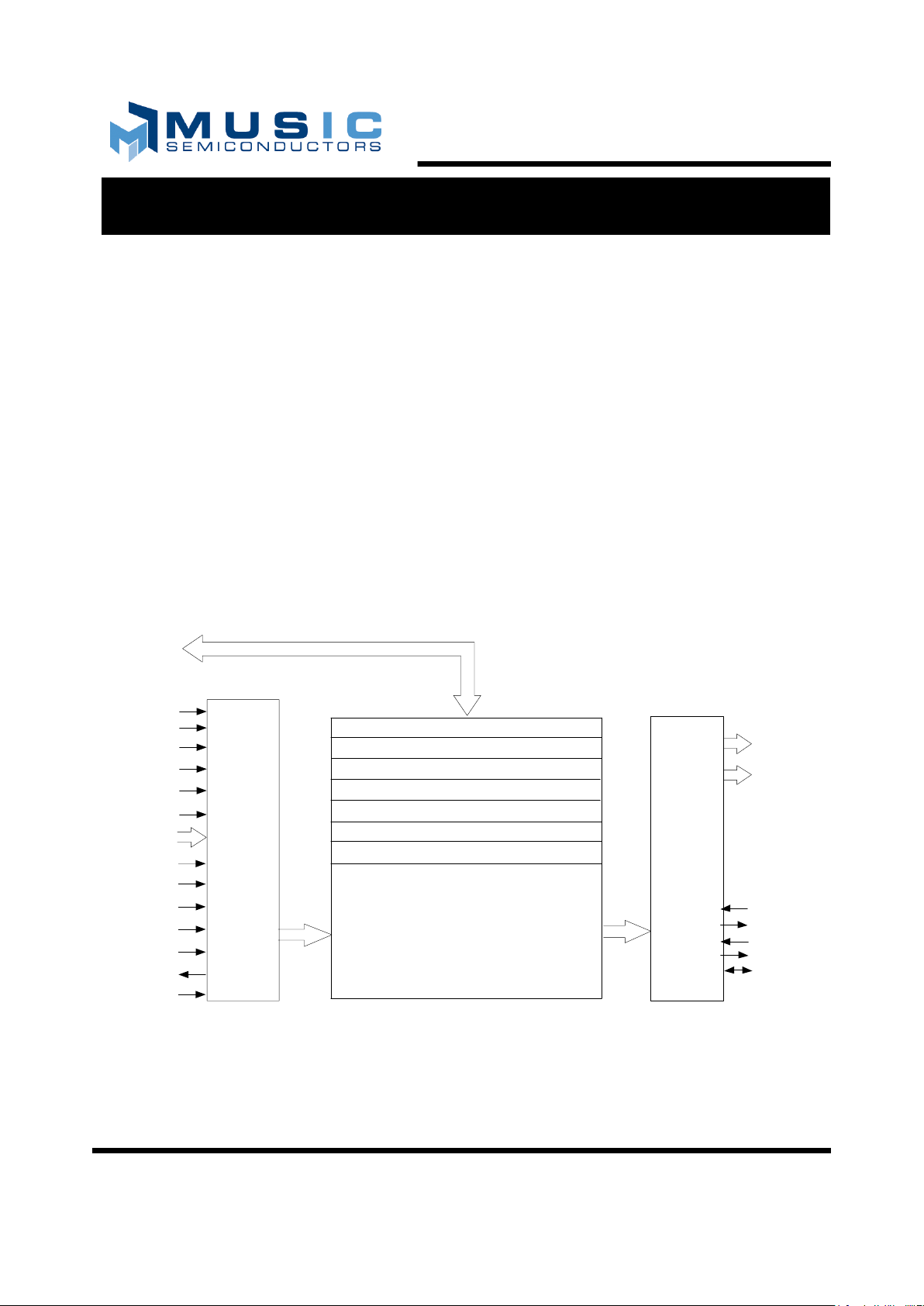

DQ31–0

/VB

AA Bus

PA3–0

/MM

/RESET

TCLK

TMS

TDI

TDO

/TRST

CONTROL

AND

ADDRESS

DECODER

PRIORITY

ENCODER

AND

FLAG

LOGIC

/E

/CS1

/CS2

/W

/OE

/AV

AC Bus

/DSC

INSTRUCTION REGISTER

DEVICE SELECT REGISTER

STATUS REGISTER

CONFIGURATION REGISTER

ADDRESS REGISTER

MASK REGISTERS 1–7

COMPARAND REGISTER

4 K x 64 Word

(MU9C4K64)

8 K x 64 Word

(MU9C8K64)

Address Database

/M F

/M I

/FF

/FI

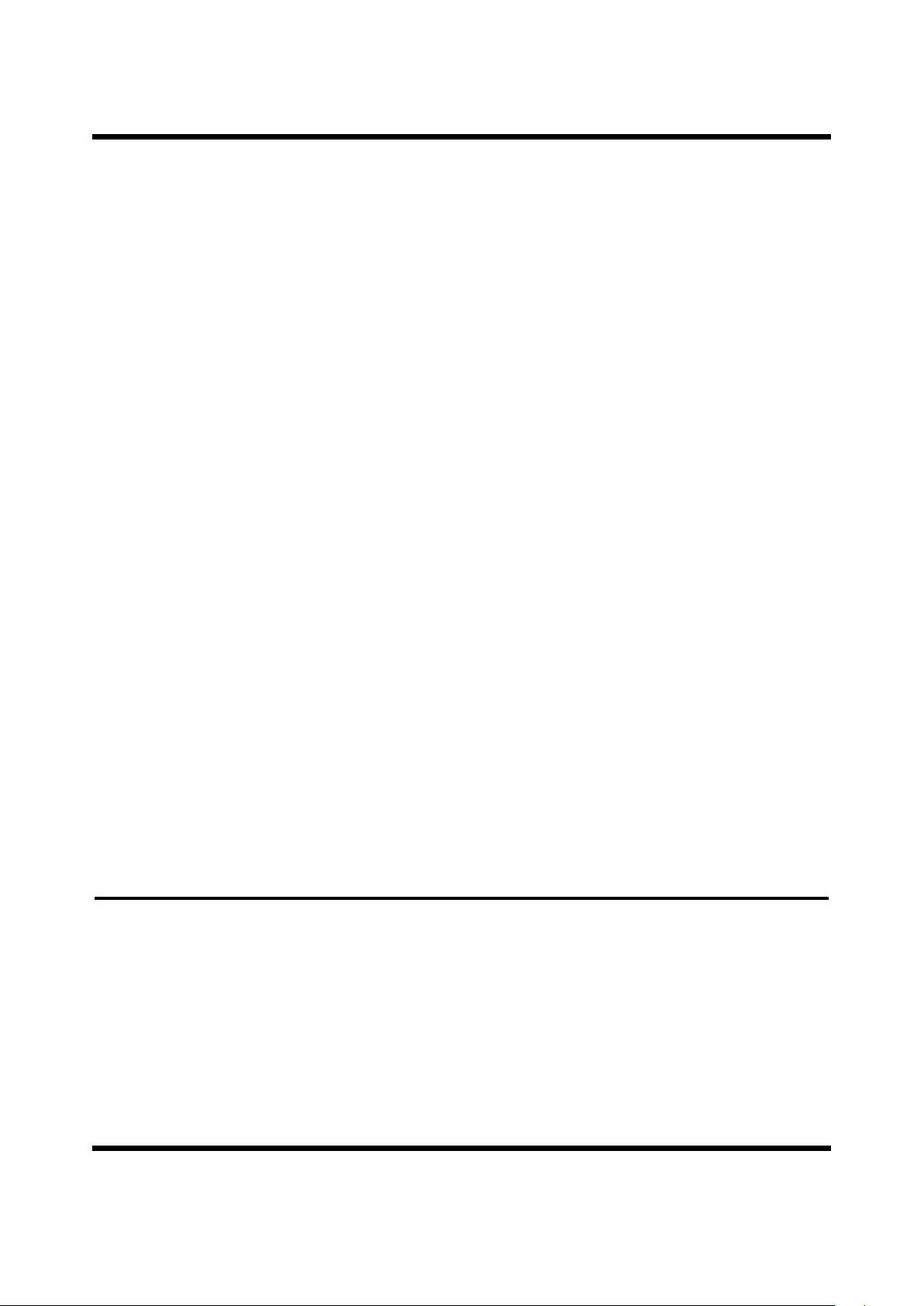

Figure 1: Block Diagram

APPLICATION BENEFITS

• 28 million IPv4 packets per second supports up to 18

Gb Ethernet or 7 OC-48 ATM ports at wire speed

• Exact match on MAC addresses

• Processes DA and SA within 190 ns, supporting three ports

of 1 Gb or 34 ports of 100 Mb Ethernet at wire

speed

• Mixed mode L3 and L2 single search engine for two ports

at 1 Gb or 29 ports of 100 Mb Ethernet at wire

speed

• Directly addresses external RAM containing

associated data of any width

• Hardware control states directly address memory and

registers; Instruction and Status registers for optional

software control

DISTINCTIVE CHARACTERISTICS

• 4K and 8K x 64-bit words

• 64-bit binary compares

• 35 ns deterministic compare and output time

• 32-bit Data I/O port

• 16-bit Match Address Output port

• Address/Control bus directly controls device operations for

faster operation or higher throughput

• Seven selectable mask registers

• Synchronous operation

• Cascadable for increased depth

• Extensive set of control states for flexibility

• JTAG interface

• 100-pin LQFP package; 3.3 Volt operation

MU9C Routing Coprocessor (RCP) Family

MU9C Binary Routing Coprocessor (RCP) Family General Description

2

Rev. 6

GENERAL DESCRIPTION

The MU9C RCP family consists of 4K and 8K x 64-bit

Routing Coprocessors (RCPs) with a 32-bit wide data

interface. The device is designed for use in layer 2

switches to provide very high throughput address

translation using tables held in external RAM. The MU9C

RCP has a fully deterministic search time, independent of

the size of the list and the position of the data in the list.

This unique feature guarantees that the wire speed address

recognition does not impact the latency or induce some

jitter on the latency of the global system. Address fields

from the packet header are compared against a list of

entries stored in the array. As a result of the comparison,

the MU9C RCP generates an index that is used to access

an external RAM where port mapping data and other

associated information is stored.

A set of control states provides a powerful and flexible

control interface to the MU9C RCP. This control structure

allows memory read and write, register read and write,

data move, comparison, validity control, addressing

control, and initialization operations.

The MU9C RCP architecture uses direct hardware control

of the device and an independent bus for returning match

results. Software control is also supported for systems

where maximum performance is not needed.

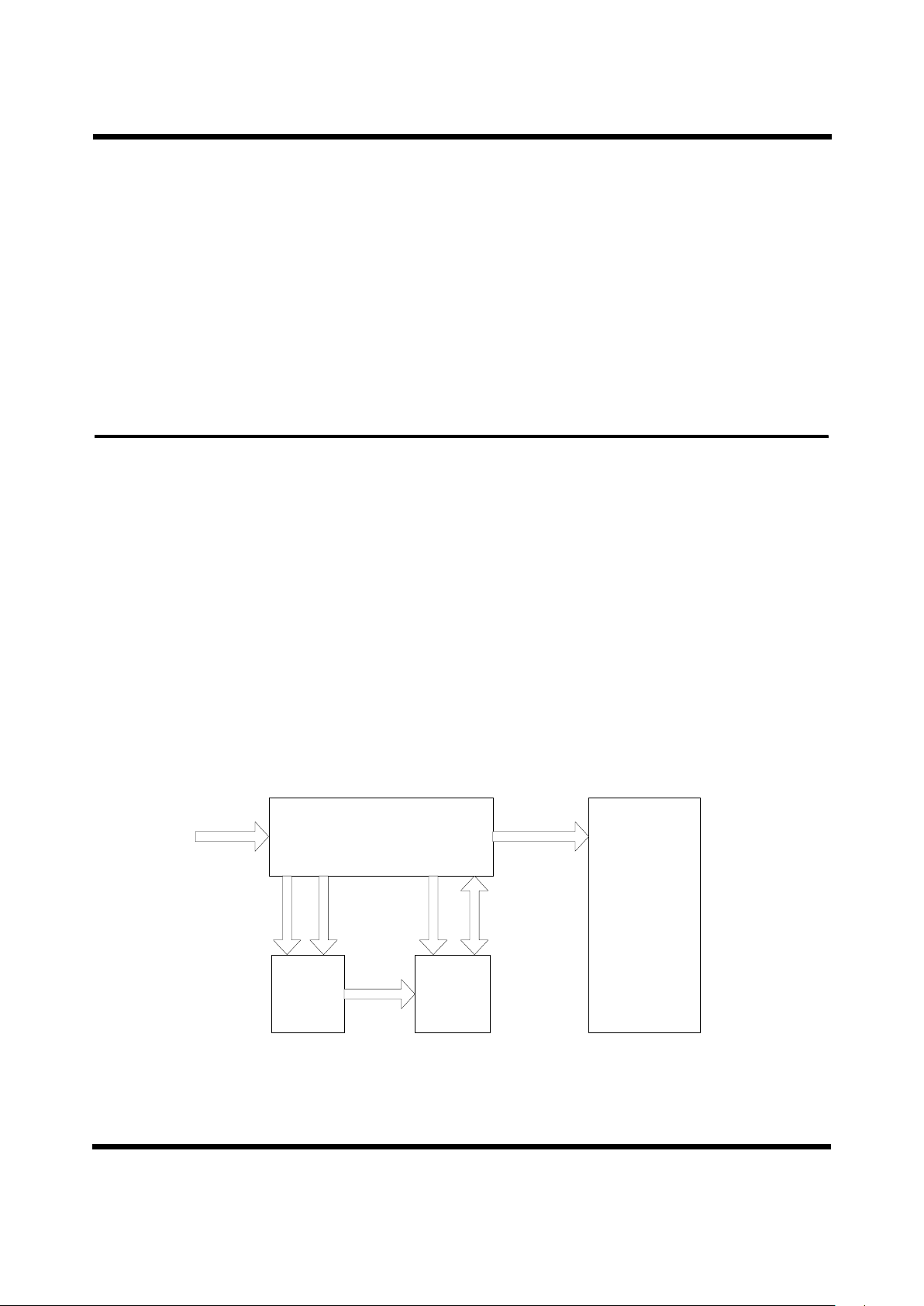

OPERATIONAL OVERVIEW

The MU9C RCP is designed to act as an address translator

for lookup tables in layer 2 switches. Refer to Figure 2 for

a simplified block diagram of a switch. During normal

operation, the controller extracts the address information

from an arriving packet to form the comparand, which is

then compared against the contents of the MU9C RCP.

The MU9C RCP generates an index that is used to access

the data in an external RAM, which holds the destination

port for accessing the network. The controller reads the

data from the RAM and forwards the packet.

The validity of a location in the Address Database is

determined by an extra bit called the Validity bit. This bit is

set and reset either with an index or an associative match.

Therefore, when a new entry is written to the database, its

Validity bit is set valid.

The index at which a write takes

place is driven onto the PA:AA bus, so that output port

data can be written simultaneously into the external RAM

at the correct index.

When a database location is deleted, the Validity bit for that

entry is reset, and the index of the location is driven onto

the Active Address bus. This simple mechanism allows

easy maintenance of the tables in both the database and the

external RAM.

The MU9C RCP supports simple daisy chained vertical

cascading that serves to prioritize multiple devices and

provides system-level match and full indication. If the

slight timing overhead associated with the daisy chain is

unacceptable, the MU9C RCP is designed to facilitate

external prioritization across multiple devices.

Figure 2: Switch Block Diagram

Controller

RAM

Switch

Fabric

MU9C

Switch Control

and Packet Data

Network

Address

Data

RCP

Control

Packet Stream

RAM

Address

Pin Descriptions MU9C Binary Routing Coprocessor (RCP) Family

Rev. 6 3

PIN DESCRIPTIONS

Note: Signal names that start with a slash (“/”) are active LOW.

All signals are 3.3V CMOS level. Never leave inputs floating.

The CAM architecture draws large currents during compare

operations, mandating the use of good layout and bypassing

techniques. Refer to the Electrical Characteristics section for

more information.

DQ31–0 (Data Bus, Three-state, Common Input/

Output)

The DQ31–0 lines convey data to and from the MU9C

RCP. When the /E input is HIGH the DQ31–0 lines are

held in their high-impedance state. The /W input

determines whether data flows to or from the device on the

DQ31–0 lines. The source or destination of the data is

determined by the AC bus, DSC, and the /AV line. During

a Write cycle, data on the DQ31–0 lines is registered by

the falling edge of /E.

AC12–0/AC11–0 (Address/Control Bus, Input)

When Hardware control is selected, the AC bus conveys

address or control information to the MU9C RCP,

depending on the state of the /AV input. When /AV is

LOW then the AC bus carries an address; when /AV is

HIGH the AC bus carries control information. Data on the

AC bus is registered by the falling edge of /E. When

software control is selected, the state of the AC bus does

not affect the operation of the device.

DSC (Data Segment Control, Input)

When DQ bus access to a 64 bit register or memory word

is performed, the DSC input determines whether bits 31–0

(DSC LOW) or bits 63–32 (DSC HIGH) are accessed.

Access to 32 bit registers require that DSC be held LOW.

AA12–0/AA11–0 (Active Address, Output)

The AA bus conveys the Match address, the Next Free

address, or Random Access address, depending on the

most recent memory cycle. The /OE input enables the AA

bus; when the /OE input is HIGH, the AA bus is in its

high-impedance state; when /OE is LOW the AA bus is

active. In a vertically cascaded system after a Comparison

cycle, Write at Next Free Address cycle or Read/Write at

Highest-Priority match, only the highest-priority device

will enable its AA bus, regardless of the state of the /OE

input. In the event of a mismatch in the Address Database

after a Compare cycle, or after a Write at Next Free

Address cycle into an already full system, the

lowest-priority device will drive the AA bus with all 1s.

The AA bus is latched when /E is LOW, and are free to

change only when /E is HIGH.

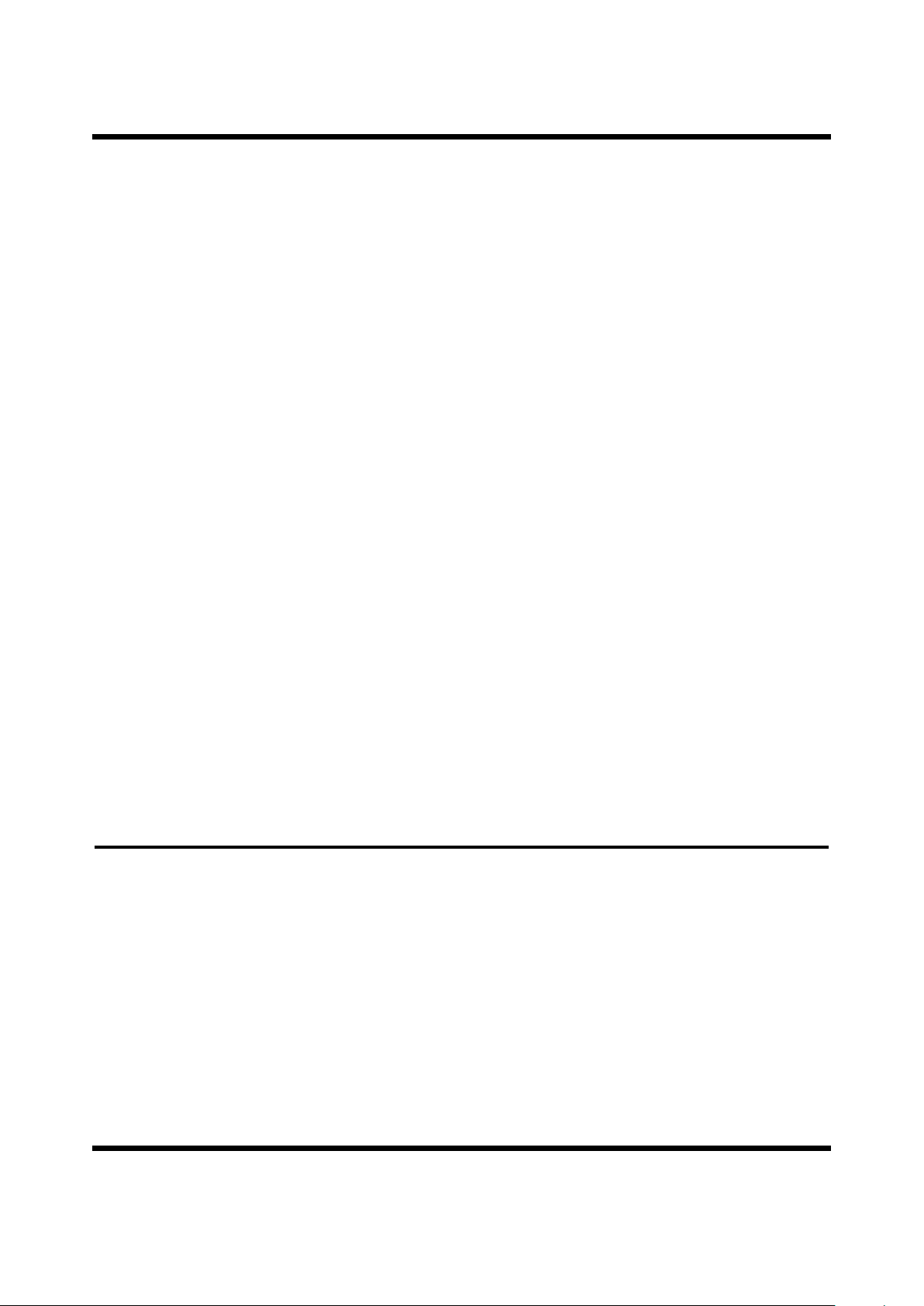

Figure 3: MU9C RCP Pinout

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

81

31

10 0

99

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

32

TCLK

TMS

TDI

DQ0

DQ1

DQ2

DQ3

VDD

DQ4

DQ5

DQ6

DQ7

VSS

DQ8

DQ9

DQ10

DQ11

VDD

DQ12

DQ13

DQ14

DQ15

VSS

VSS

VSS

AC11

AC10

AC9

AC8

AC7

AC6

VDD

AC5

AC4

AC3

AC2

AC1

AC0

TDO

AA12/NC*

8

0

7

9

7

8

7

7

7

6

7

5

7

4

7

3

7

2

7

1

7

0

6

9

6

8

6

7

6

6

6

5

6

4

6

3

6

2

6

1

6

0

5

9

5

8

5

7

5

6

5

5

5

4

5

3

5

2

5

1

D

Q

1

6

D

Q

1

7

D

Q

1

8

D

Q

1

9

V

D

D

D

Q

2

0

D

Q

2

1

D

Q

2

2

D

Q

2

3

V

S

S

D

Q

2

4

D

Q

2

5

D

Q

2

6

D

Q

2

7

V

D

D

D

Q

2

8

D

Q

2

9

D

Q

3

0

D

Q

3

1

V

S

S

/

E

/

W

/

C

S

1

/

C

S

2

/

O

E

V

S

S

/

A

V

/

V

B

/

R

E

S

E

T

/

T

R

S

T

1

2

3

4

5

6

7

8

9

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

V

S

S

V

S

S

A

A

1

2

/

N

C

*

A

A

8

V

S

S

A

A

7

A

A

6

A

A

5

A

A

4

V

D

D

A

A

3

A

A

2

A

A

1

A

A

0

V

S

S

/

M

F

/

F

F

V

D

D

/

M

I

/

F

I

V

S

S

/

M

M

D

S

C

P

A

3

P

A

2

P

A

1

P

A

0

A

A

1

0

A

A

9

A

A

1

1

MU9CxK64

100-Pin LQFP

(Top View)

* NC on MU9C4K64

MU9C Binary Routing Coprocessor (RCP) Family Pin Descriptions

4

Rev. 6

PA3–0 (Page Address, Output)

The PA3–0 lines convey Page Address information. When

the /OE input is HIGH, the PA3–0 outputs are in their

high-impedance state; when /OE is LOW the PA3–0 lines

carry the Page Address value held in the Configuration

register. The PA3–0 lines are latched when /E is LOW, and

are free to change only when /E is HIGH. The Page

Address value of the currently active or highest-priority

responding device is output at the same time, and under

the same conditions, as the AA bus is active.

/E (Chip Enable, Input)

The /E input is the main chip enable and synchronizing

control for the MU9C RCP. When /E is HIGH, the chip is

disabled and the DQ31–0 lines are held in their

high-impedance state. The falling edge of /E registers the

/W, /CS1, /CS2, /AV, /AC bus, DSC, and the /VB and

DQ31–0 lines for a Write cycle. /E being LOW causes the

results of the previous comparison or memory access to be

latched on the PA:AA bus; when /E goes HIGH the latches

opens allowing the new comparison results or random

access memory address to flow to the PA:AA bus.

/CS1, /CS2 (Chip Select 1, Chip Select 2, Inputs)

The /CS1 and /CS2 inputs enable the MU9C RCP. If

either /CS1 or /CS2 are LOW, the device is selected for a

Read, Write, or Compare cycle through the DQ31–0 lines,

or for an internal data transfer. The /CS1 and /CS2 lines do

not have any effect on the PA:AA bus. The state of the

/CS1 and /CS2 lines is registered by the falling edge of /E.

/W (Write Enable, Input)

The /W input determines the direction of data transfer on

the DQ31–0 lines during Read, Write, and Data Move

cycles. When /W is LOW, data flows into the DQ31–0

lines; when /W is HIGH, data flows out. The /W line also

conditions the control state present on the AC bus and

DSC lines. The state of the /W line is registered by the

falling edge of /E.

/OE (Output Enable, Input)

The /OE input enables the PA:AA bus. When /OE is

HIGH, PA:AA bus are in their high-impedance state.

When /OE is LOW, PA:AA bus are active, and convey the

results of the last Comparison Cycle Match address or

Memory Access address. In a vertically cascaded system,

only the PA:AA bus of the highest-priority device will be

activated by /OE being LOW; in lower-priority devices,

the PA:AA bus remains in high-impedance regardless of

the state of /OE.

/AV (Address Valid, Input)

When Hardware control is selected, the /AV input

determines whether the AC bus carries address or control

information. When /AV is LOW, the AC bus conveys a

memory address; when /AV is HIGH, the AC bus conveys

control information. The state of the /AV line is registered

by the falling edge of /E. When software control is

selected, the /AV line distinguishes between instructions

and data on the DQ31–0 lines; when /AV is LOW, data is

present on the DQ31–0 lines; when /AV is HIGH, an

instruction is present on the DQ11–0 lines.

/VB (Validity Bit, Three-state, Common

Input/Output)

During accesses over the DQ31–0 lines, the /VB line

conveys validity information to and from the MU9C RCP.

During a Write cycle (/W=LOW), when /VB is LOW the

addressed location is set valid; when /VB is HIGH it is set

empty. During a Read cycle (/W=HIGH), the validity of

the addressed location is read on the /VB line. During a

Write cycle, the state of the /VB line is registered by the

falling edge of /E.

/MF (Match Flag, Output)

The /MF output indicates whether a valid match has

occurred during the previous Comparison cycle. If the /MF

output is HIGH at the end of a Comparison cycle, then no

match occurred; if it is LOW then either a match occurred

within the device, or the /MI input is LOW, conditioned by

the /MF output from a higher-priority device in the system.

The state of the /MF line will not change until after the

rising edge of /E during the Comparison cycle. Note that

/MF indicates the results of the most recent Comparison

cycle; it will not change when the PA:AA bus carry an

address other than the Match address.

/MI (Match Input, Input)

The /MI input receives match information from the next

higher-priority MU9C RCP in a vertically cascaded

system to provide system-level prioritization. When the

/MI input is HIGH, the /MF output will only go LOW if

there is a match during a Comparison cycle; when the /MI

input is LOW, the /MF output will go LOW. The /MF

output from one device is connected to the /MI input of the

next lower-priority device. The /MI pin of the

highest-priority device must be tied HIGH.

/FF (Full Flag, Output)

The /FF output indicates when all the memory locations

have their Validity bits set valid (LOW). When there is at

least one location with its Validity bit set HIGH, the /FF

output will be HIGH; when all locations have their Validity

bits set LOW, and the /FI input is LOW, the /FF output will

MU9C Binary Routing Coprocessor (RCP) Family

Rev. 6 5

be LOW. If the /FI input is HIGH, the /FF output will be

HIGH. The state of the /FF line will not change until after

the rising edge of /E during a Write cycle.

/FI (Full Input, Input)

The /FI input receives full information from the next

higher-priority MU9C RCP in a vertically cascaded

system to provide system-level full information. When the

/FI input is LOW the /FF output will be HIGH if there is at

least one location whose Validity bit is set invalid; when

all locations have their Validity bits set valid, the /FF

output goes LOW. When the /FI input is HIGH, the /FF

output will remain HIGH. The /FF output from one device

is connected to the /FI input of the next lower-priority

device to give system-full indication. The /FI pin of the

highest-priority device must be tied LOW.

/MM (Multiple Match, Open Drain Output)

The /MM line indicates that there is a multiple match

within the system. When the /MI input is HIGH, the /MM

line is pulled LOW if there are at least two matches within

the MU9C RCP as a result of the previous Comparison

cycle; when there are less than two matches, the /MM line

floats HIGH. When the /MI input is LOW, the /MM line is

pulled LOW if there are one or more matches within the

MU9C RCP as a result of the previous Comparison cycle;

when there are no matches, the /MM line floats HIGH.

The /MM lines have open-drain outputs, so all /MM lines

within the system are connected together to give

system-level multiple match indication. The state of the

/MM line will not change until after the rising edge of /E

during a Comparison cycle.

/RESET

The /RESET input is used to reset the MU9C RCP to a

known state. When the /RESET line is pulled LOW it

causes the MU9C RCP to enter its reset state. After power

is applied to the MU9C RCP, the /RESET line must be

held LOW for a time equal to or greater than the minimum

RESET pulse width before the device can operate

correctly. This pin is internally pulled up.

TCLK (JTAG Test Clock, Input)

The TCLK input is the Test Clock input. This pin is

internally pulled up.

TMS (JTAG Test Mode Select, Input)

The TMS input is the Test Mode Select input. This pin is

internally pulled up.

TDI (JTAG Test Data Input, Input)

The TDI input is the Test Data input. This pin is internally

pulled up.

TDO (JTAG Test Data Output, Output)

The TCLK output is the Test Data Output. This pin is

internally pulled up.

/TRST (JTAG Reset, Input)

The /TRST input is the Reset input, and serves to reset the

Test Access Port circuitry to its reset condition. This pin is

internally pulled up.

VDD, VSS (Positive Power Supply, Ground)

These pins are the main power supply connections to the

MU9C RCP. VDD must be held at +3.3 Volts and ± 0.3

Volts relative to the VSS pin, which is at 0 Volts, system

reference potential, for correct operation of the device.

Note: The TCLK, TMS, TDI, TDO, and /TRST lines are defined

in the IEEE Standard Test Access Port and Boundary-scan

Architecture IEEE Standard. 1149.1-1990 and IEEE Standard.

1149.1a-1993.

FUNCTIONAL DESCRIPTION

Data is read from and written to the MU9C RCP through

the DQ31–0 lines. The Control bus, which is comprised of

Chip Enable (/E), two Chip Selects (/CS1, /CS2), Write

Enable (/W), Output Enable (/OE), Validity Bit Control

(/VB), Address Valid (/AV), Data Segment Control (DSC),

and the Address/Control inputs (AC bus) controls the

MU9C RCP. When the /AV line is LOW, the AC bus

carries an address for random access into the Memory

array; when it is HIGH, the AC bus conveys control

information. The MU9C RCP control states perform

Register Read/Write, Memory Read/Write, Data Move,

Comparison, Validity Bit Control, Initialization, and

Address Register Control. These functions are

summarized in Control State Overview on page 15.

Random access to memory locations occurs when the /AV

line is LOW; during a Write cycle, the validity of the

location is set by the /VB input. When the /AV line is

HIGH the control states allow read and write access to the

register set comprising Comparand register, seven mask

registers, a Configuration register, a Status register, an

Address register, a Device Select register, and an

Instruction register. The Configuration register sets the

persistent operating conditions of the device: the Page

address of the device, selection of mask register for

directly addressed memory writes, and selection between

hardware and software control.

MU9C Binary Routing Coprocessor (RCP) Family Functional Description

6

Rev. 6

When Hardware control is selected, control is through the

AC bus and DSC line. When Software control is selected,

control is through the Instruction register, which is loaded

from the DQ bus. Under software control the /AV line is

used to distinguish between data and an instruction on the

DQ bus. Therefore, in Software Control mode, random

access to the Memory array can take place only using

indirect addressing through the Address register.

The two Chip Select lines /CS1, /CS2 enable the device and

simplify access to a multi-chip system, if either Chip Select

line is LOW the device is selected. The MU9C RCP also

can be selected through the Device Select register when its

value is set to that of the Page address of the device, and the

enable bit in the Device Select register is set LOW. The /OE

input enables the output signal and is used to synchronize

devices in a multi-chip system, and to prevent race

conditions among devices during priority resolution.

The output signals comprise the Active address (AA bus),

and the Page address (PA bus). The PA:AA bus provides

the current Active address, which is either the Match

address, Next Free address, or the Random Access

address, concatenated with the Device Page address. The

source of Active address is dependent on the previous

control state, allowing access to associated data in the

external RAM at the same location as an access in the

MU9C RCP for all types of cycles.

The Output enable, /OE, controls the PA:AA bus: when it is

LOW after a Compare cycle, the highest-priority

responding device outputs its Page and Match addresses on

PA:AA bus. Only the highest-priority responding device is

enabled, all other lower-priority devices will have their

PA:AA bus in the high-impedance state, regardless of the

state of their respective /OE lines: when /OE is HIGH, the

PA:AA remain in the high-impedance state.

When a mismatch occurs in the system, the lowest-priority

device, as defined in the Configuration register, will drive

the PA:AA bus with all 1s. When any Read or Write cycle

occurs, the address of the accessed location is output on

the PA:AA bus. The address output on the PA:AA bus is

persistent, and is held latched until /E goes HIGH during

the next cycle that changes the Active address. The PA:AA

bus is free to change only while /E is HIGH. Once /E goes

LOW, the state of the PA:AA bus is latched.

After a Compare cycle, the /MF and /MM flags are free to

change after /E has gone HIGH. Once the Match Flag

daisy chain has resolved device prioritization, the /OE

lines can be asserted to enable the PA:AA bus from the

highest-priority matching device.

In a multi-chip system, when a device remains deselected

during a Compare cycle through /CS1 and /CS2 being

HIGH and there being no match between the Device

Select register and the Page Address register, that device

will clear any previous positive match results. In other

words, if it had previously been indicating a match from

an earlier Comparison cycle, it will now be set to indicate

a mismatch, even though it was not selected during the

most recent Compare cycle.

For pure software control of the MU9C RCP, instructions

can be loaded into the Instruction register, and results read

from the Status register. The Status register holds the

results of comparison: PA:AA bus, /MF, /FF, and /MM

plus two PA:AA Validation bits that indicate the type of

cycle that generated the PA:AA bus value.

Vertical cascading is supported through a daisy chain

architecture. There are two daisy chains, one each for the

Match flag and the Full flag; the Multiple Match flag is

connected between devices through an open-drain line.

The Match flag (/MF) from a higher-priority device is

connected to the Match input (/MI) of the next

lower-priority device to provide prioritization throughout

a multiple device system. The /MF output from the

lowest-priority device provides a system Match flag. If the

delay through the daisy chain is unacceptable, the /OE

input can be used by external priority-resolution circuitry

to enable the highest-priority responder in the system.

The match conditions on the Match and Multiple Match

flag lines are persistent indicating the results of the most

recent Compare cycle. The Match flags are free to change

after the rising edge of /E during a Compare cycle, at

which time the daisy chain starts to resolve device

prioritization. Once the daisy chain has settled, the /OE

lines can be pulled LOW to access the Highest-Priority

Match address on the PA:AA bus.

The Multiple Match open-drain output (/MM) provides

multiple match indication when there are two or more

matches in a single device, or a device has its /MI input

LOW and has a match; the /MM flags of all devices in the

system are wire-ORed. Multiple responders can be

accessed sequentially by resetting the Highest-Priority

Match latch with the control state Advance to Next

Matching Location.

The Full flag (/FF) is cascaded from one device to the Full

Flag input (/FI) of the next lower-priority device in the

system. The /FF output from the lowest-priority device

provides a system Full flag. The Full flag is free to change

after the rising edge of /E during a Write cycle. The daisy

chains are persistent and are not conditioned by the /OE

input.

The MU9C RCP supports JTAG boundary-scan testing

through the pins TCK, TMS, TDI, TDO, and /TRST,

according to the IEEE 1149 Standard: Test Access Port

and Boundary-scan Architecture.

Operational Characteristics MU9C Binary Routing Coprocessor (RCP) Family

Rev. 6 7

OPERATIONAL CHARACTERISTICS

Processor Interface

The processor interface is through a 32-bit data bus

DQ31–0 and control signals comprised of Chip Enable

(/E), two Chip Selects (/CS1, /CS2), Write Enable (/W),

Output Enable (/OE), Validity Bit Control (/VB), Address

Valid (/AV), Data Segment Control (DSC), and

Address/Control inputs (AC bus). When the /AV line is

LOW, the DSC and AC bus carries an address for random

access into the Memory array; when it is HIGH, the AC

bus conveys control information.

Most of the functionality of the MU9C RCP is accessed

through the control states on DSC and AC bus when /AV

is HIGH. The processor maps the control structure into

memory space and controls the MU9C RCP through

memory Read and Write cycles. Using this memory

mapping scheme, the /AV line should be driven from logic

that generates a HIGH level within the mapped range of

the control states, and a LOW level outside it. Other

control inputs /E, /W, /CS1, and /CS2 are analogous to

SRAM control inputs.

The /VB line acts like an extra data bit during memory

Read and Write cycles and is used to read and write the

validity of any memory location.

The MU9C RCP is enabled either through hardware

through /CS1 or /CS2 being LOW, or it is enabled by the

value written to the Device Select register matching with

the Page Address field of the Configuration register. One

extra bit in the Device Select register enables the

comparison between the Page Address value and the

Device Select register. These Chip Select mechanisms

operate in parallel. If any one is active, the device is

enabled.

The MU9C RCP can be controlled directly through

software. The Software Control mode is selected through

settings in the Configuration register.

When the Software Control mode is selected, control states

are written to the Instruction register from DQ11–0 during a

Write cycle with the /AV line held HIGH. DQ12 acts as the

DSC input. If the control state does not involve any data

transaction on the DQ31–0 lines, the instruction is executed

during the same cycle; the state of DQ13 modifies the

instruction, its state is equivalent to the /W input.

Note: It is up to the system designer to ensure that the correct

cycle type follows the loading of an instruction in Software

Control mode. If the instruction expects a Read cycle, and a

Write cycle is executed, or vice versa, the function of the MU9C

RCP is undefined. Such an error may lead to data loss, but will

not damage the device physically.

A Read cycle with the /AV line HIGH will access the

Status register, allowing results to be read back without

loading a new instruction. After a Comparison cycle,

Write at Next Free Address cycle or Read/Write at

Highest-Priority match in a vertically cascaded system,

only the highest-priority device will enable its DQ31–0

lines and output the contents of its Status register. After a

Comparison cycle, in the event of a mismatch in the

MU9C, the DQ31–0 lines of the lowest-priority device

will be enabled. After a random access Read or Write

cycle, the Status register of any selected device will be

enabled. Under these circumstances, it is up to the user to

ensure that only a single device is enabled through /CS1,

/CS2, or the Device Select register.

The instruction is persistent, so that all subsequent data

transactions will be executed according to the control state

held in the Instruction register. The results of a

Comparison cycle can be read back from the Status

register, and include PA:AA bus, /MF, /MM, and /FF. The

following sequence of events provides the fastest

operation of the MU9C RCP in Software Control mode:

Note: It is up to the system designer to ensure that the correct

cycle type follows the loading of an instruction in Software

Control mode. If the instruction expects a Read cycle, and a

Write cycle is executed, or vice versa, the function of the MU9C

RCP is undefined. Such an error may lead to data loss, but will

not damage the device physically.

Hardware Control

Direct hardware control using the AC bus and DSC line

enhances performance of the MU9C RCP. The AC bus

inputs determine which CAM location is accessed, and the

DSC determines whether bits 31–0 (DSC LOW) or bits

63–32 (DSC HIGH) are active. The Hardware Control

mode is selected when Configuration Register bits

FR27–26 are set LOW. The AC bus inputs are qualified by

/W, /AV, and /VB. When /AV is LOW, the AC bus and

DSC line carry the address for a random Read or Write

cycle, depending on the state of /W, and /VB carries the

validity of the location. During a Write cycle, /VB is

written to the Validity bit of the addressed location; during

a Read cycle, the validity of the location is read on the /VB

line. When /VB is LOW, the location contains valid data;

when /VB is HIGH the location is empty.

When /AV is HIGH, the AC bus and DSC line carry

address and control information. The DSC line selects

whether bits 31–0 (DSC LOW) or bits 63–32 (DSC

/AV Operation

1 Load ‘Compare DQ with CAM’ instruction

0 Comparand on DQ31–0

1 Read Status register

0 Next Comparand on DQ31–0

1 Read Status register, etc.

MU9C Binary Routing Coprocessor (RCP) Family Operational Characteristics

8

Rev. 6

HIGH) participate in the operation. The AC8–6 lines

select the mask register and the AC5–0 lines provide the

Op-Code. If masking is not used, and all random

addressing of the memory is indirect through the Address

register, then only the DSC and AC5–0 lines are needed

for full control of the device.

In applications where a restricted number of control lines

are available, or where speed is not critical, the MU9C

RCP can be controlled in Software Control mode where

the control states are loaded into the Instruction register

through the DQ31–0 lines. The control states are identical

in both Hardware and Software Control modes, although

DQ12 and DQ13 take on special significance in Software

mode.

Software Control

For optimum performance, the AC bus and DSC line

control the MU9C RCP, allowing data transactions

through the DQ31–0 lines during a control cycle. In cases

where the overhead of a separate data load cycle can be

accommodated, the MU9C RCP can be operated through

the Instruction register. The AC bus and DSC line are not

used.

Control through the Instruction register is selected by the

FR27–26 bits of the Configuration register being set

HIGH. The instruction is loaded from the DQ11–0 lines

(with DSC on DQ12) into the Instruction register during a

Write cycle with the /AV line HIGH. The instructions are

directly analogous to the control states for any operation

that does not involve data transfer on the DQ31–0 lines, in

which case the instruction is executed during the same

cycle as the instruction is loaded. To distinguish between

Read and Write control states, DQ13 is used to indicate

which type of instruction should be executed. When DQ13

is LOW at the beginning of the cycle, the instruction

executed is the Write Cycle instruction (/W = LOW when

control state is conveyed on AC bus and DSC); when

DQ13 is HIGH at the beginning of the cycle, the

instruction executed is the Read Cycle instruction (/W =

HIGH when control state is conveyed on the AC bus).

When the instruction calls for data to be written or read

from the DQ31–0 lines, the instruction is loaded into the

Instruction register during the cycle, and the next Data Read

or Write cycle with /AV LOW executes the instruction

using the DQ31–0 bus for the data transaction. The

instruction is persistent; for example, if no other instruction

is loaded into the Instruction Register, subsequent data

transactions with the /AV line LOW will be executed

according to the instruction currently loaded in the

Instruction register. When there is a data access to a

memory location on DQ31–0 associated with the

instruction, the /VB line carries the validity of that location.

Instructions that involve data transactions on DQ31–0, and

are therefore executed on a subsequent Read or Write

cycle with the /AV line LOW, are all Read/Write Memory

and Read/Write Register instructions, Read Validity, Write

PA3-0. All other instructions are executed in a single cycle

with the state of DQ13 being interpreted as the state of the

/W line during the equivalent hardware control state.

For Read Cycles with the /AV line HIGH, there is a

Software Control mode. This mode is selected through the

Configuration bits FR27–26. In Software Control mode

(FR27–26 = 0b11) a Read cycle with /AV HIGH accesses

the Status register.

Active Address Interface PA:AA Bus

The Active Address interface PA:AA bus carries the

currently active address. The address source depends on

the most recent control state that caused it to change. The

possible address sources that are output on PA:AA bus are:

Highest-Priority Match address, Next Free address, Read

address, and Write address.

PA:AA Bus After a Comparison Cycle

After a Comparison cycle, or access to the

Highest-Priority address, the PA:AA bus carries one of the

following two possible results:

• The Match address if the Comparison cycle resulted

in a match in the MU9C. Only the device containing

the highest-priority match enables its PA:AA bus. All

other devices with either no match or a lower-priority

match, as indicated by the Match Flag daisy chain,

keep their PA:AA bus in high-impedance regardless

of the state of their /OE inputs.

• All 1s if there was no match in the MU9C. The

lowest-priority device, as indicated by bit FR25 in the

Configuration register, enables its PA:AA bus and

provides the source of all 1s. All other devices will

keep their PA:AA bus in high-impedance regardless

of the state of their /OE inputs.

PA:AA Bus After a Write at Next Free Address Cycle

After a Write at Next Free Address cycle the PA:AA

carries the address that was written to during that cycle.

Only the device in which the write occurred enables its

PA:AA bus. All other devices keep their PA:AA bus in

high-impedance regardless of the state of their /OE inputs.

In the event that the system was full prior to the Write at

Next Free Address cycle being executed, so that the write

operation was suppressed, the PA:AA carries all 1s. The

lowest-priority device, as indicated by bit FR25 in the

Configuration register, enables its PA:AA bus and

provides the source of all 1s. All other devices keep their

PA:AA in high-impedance regardless of the state of their

/OE inputs.

Register Descriptions MU9C Binary Routing Coprocessor (RCP) Family

Rev. 6 9

PA:AA Bus After a Random Access Read or Write to the

CAM

After a random Read or Write cycle to the MU9C, the

PA:AA bus carries the address that was accessed during

that cycle. Only the device in which the access occurred

enables its PA:AA bus. All other devices keep their

PA:AA bus in high-impedance regardless of the state of

their /OE inputs. Note that the access to the PA:AA bus

differs in this respect from the operation of the Status

register, which is accessible in any selected device under

this particular circumstance.

In the event that the Write cycle was broadcast to multiple

devices, all devices that have their /OE lines held LOW will

enable their PA:AA bus. Under this circumstance, it is up to

the system designer to ensure that only one /OE line is

driven LOW to prevent bus contention on the PA:AA bus.

PA:AA Bus Conditions of Operation

• During a control state that does not have any effect on

the device address, such as a Write Register cycle, the

PA:AA bus remains unchanged. In other words, the

state of the PA:AA bus persists until another cycle

causes it to change.

• When enabled by /OE being LOW, the PA:AA bus is

only free to change while /E is HIGH. When /E goes

LOW the PA:AA bus is latched.

• The PA:AA bus is enabled when /OE is LOW

provided that the previous cycle causes them to be

active. When /OE is HIGH, the PA:AA bus is in

high-impedance. Note that /OE is asynchronous with

respect to /E, and is independent of Chip Select from

either /CS1, /CS2, or through the Device Select

register, except in the case of non-broadcast random

Read and Write cycles to the MU9C.

PA:AA Bus and the Match Flags

The Match flags /MF and /MM reflect the results of the

most recent Comparison cycle. During a Comparison

cycle, they do not change until after /E has gone HIGH

after which they are free to change combinatorially; their

state is latched when /E is LOW. This condition allows

some pipelining to occur and is useful in systems with

long daisy chains. A Comparison cycle can be followed by

another cycle that does not affect the PA:AA bus before

the daisy chain is resolved. For example:

The WRL CR control state can be executed before the

daisy chain has resolved device prioritization after the

CMP CR control state. The /OE then is asserted at a

suitable time, depending on the length of the daisy chain.

The Match address of the highest-priority responding

device then is driven onto the PA:AA bus.

The /MF, /MM lines continue to indicate the results of the

most recent match, even when the PA:AA bus carries an

address other than the Match address. This condition

allows rapid return to the Match address value on the

PA:AA bus lines through a RDL[HPM] cycle, without the

daisy chain having to re-resolve device-level prioritization.

PA:AA Bus and the Status Register

The Status Register bits SR15–0 reflect the PA:AA bus

under all conditions. The Status Register flags /MF, /MM,

and /FF represent the local conditions within the device,

and are not conditioned by the /MI and /FI inputs.

After a Comparison cycle, Write at Next Free address, or

access to the Highest-Priority Matching device, a Status

Register Read cycle is executed in the same device as the

active PA:AA bus. In the case of a random access Read or

Write cycle, the Status register of any selected device can

be accessed by a Read Status Register cycle. The system

designer must ensure that a Status Register Read cycle

after a random Read or Write cycle is into a single device

using Chip Select /CS1, /CS2, or the Device Select

register to prevent bus contention on the DQ31–0 bus.

REGISTER DESCRIPTIONS

The Comparand register, seven mask registers, Address

register, Configuration register, Status register, Next Free

Address register, Device Select register, and Instruction

register comprise the register set. Note that all

RESERVED bits can be read and written without affecting

the operation of the device.

However, for forward compatibility with future product

enhancements, system designers should not rely on any

particular RESERVED bit having no effect on the

operation of the device in future revisions. Therefore all

RESERVED bits should be set to logical zero.

The Register Set

Comparand Register

The 64-bit Comparand register holds the value to be

compared with the valid contents of the Address Database

array, although the DQ lines can be compared directly, and

then optionally written into the Comparand register.

CMP CR

WR CR

Loading...

Loading...