MUSIC MU9C8328-RDC Datasheet

Preliminary Data Sheet

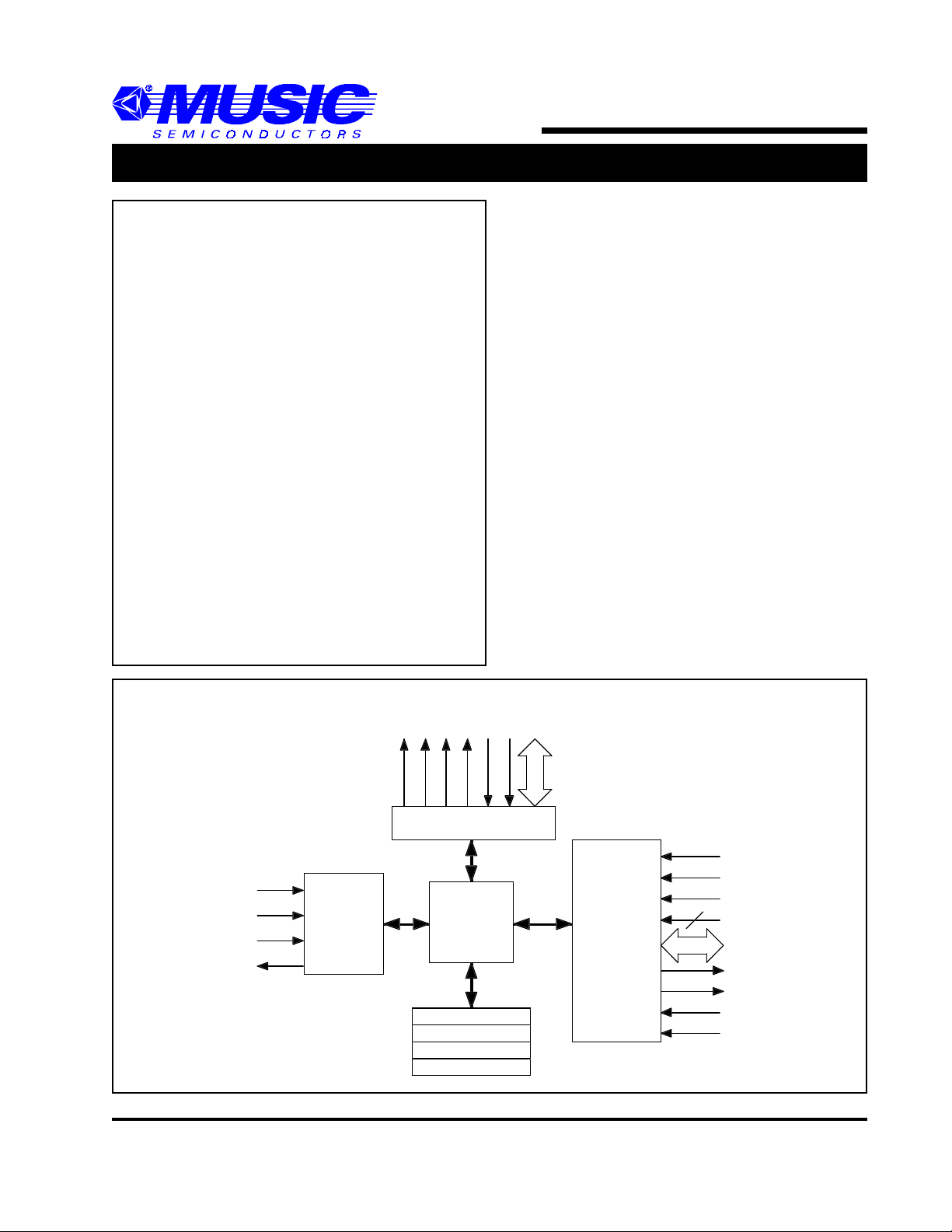

MU9C8328 Ethernet Interface

APPLICA TION BENEFITS

Ø Single port 10 MHz Ethernet address parsing,

filtering, and learning state machine at wire

speed

Ø Glue-free interface between the MUSIC

LANCAM® Family and AMD, National,

Motorola, or similar Ethernet Controllers

having an NRZ serial data port

Ø Selectable filtering and learning decisions

on DA and SA compares

Ø Supports cascaded MUSIC LANCAM series

for long station lists

Ø Host processor port for LANCAM

initialization and housekeeping activities

Ø Supports system clock rates from 20 MHz to

33 MHz

Ø 100-pin PQFP package

Ø 5 Volt operation

GENERAL DESCRIPTION

The MU9C8328 speeds up bridging operations using

Ethernet controller chips with serial NRZ data outputs,

such as AMD’s MACE™, National’s SONIC™, and

Motorola’s QUICC™ controllers, by parsing the Ethernet

frame independently of the Ethernet controller device, and

notifying it whether to accept or reject the incoming frame.

The MU9C8328 supports both positive and negative

filtering on the Destination address and learning of new

Source addresses, by efficiently controlling the compare

activities of the MUSIC LANCAM Family. Filtering and

learning routines are user configurable. These routines

are automatically invoked by the internal state machine

based on the contents of the incoming frame and the

configuration settings. For aging and other housekeeping

routines, the MU9C8328 provides the proper sequencing

and timing of LANCAM accesses for an external

processor.

The MU9C8328 receives serial NRZ data from the

Ethernet controller chip, finds the Start delimiter, and

loads the DA and SA into registers. The DA is sent to the

LANCAM for filtering and, depending on the filter action

/E

/CM

/W

/EC

/M F

DQ(15-0)

PROCESSOR

INTERFACE

SERCLK

SERDAT

/N E TRD Y

/REJ ECT

NETW OR K

INTERFACE

/FF

LANC AM IN TER FACE

STATE

MACHINE

CO NT RO L

STAT US

OP-C ODE

ASS OCIATED D ATA

Block Diagram

MUSIC Semiconductors, the MUSIC logo, the phrase “MUSIC Semiconductors”, and LANCAM are registered trademarks of MUSIC

Semiconductors. All other trademarks are registered by their respective owners. MUSIC is a trademark of MUSIC Semiconductors.

/CS

/AS

/W E

3

A(2-0)

D(15-0)

READY

/INT

SYSCLK

/RESET

11 February 1999 Rev. 4a

MU9C8328 Ethernet Interface

GENERAL DESCRIPTION

selected, notifies the controller whether to copy or purge

the frame. The SA is then sent to the LANCAM for

comparison, and if no match is found, can be learned

to the Next Free address in the LANCAM. Scheduling

is done within the MU9C8328 so that each filtering

action completes in the time of a minimum length

frame. The filtering and learning routines are

preprogrammed in the MU9C8328, with decision

options set in the control register. A Status register is

provided so the host processor can determine the results

of activities. The specific Op-Code for the LANCAM

Continued

learning instruction is by default a MOV NF , CR, V, but it

can be overridden by writing a value to the Op-Code

register. Aging and purging activity is directly controlled

by the host processor. The READY signal notifies the host

processor that processor operations are complete. The /

INT signal notifies the processor that a network frame

has been processed and the result stored in the Status

register. The processor can turn off the network filtering

activity to have total control of the LANCAM; during this

time the controller can be notified to accept or reject

all frames.

PIN DESCRIPTIONS

All signals are implemented in CMOS technology with TTL levels. Signal names that start with a slash (“/”) are active

LOW. Inputs should never be left floating. Refer to the Electrical Characteristics section for more information.

NETWORK INTERFACE

SERCLK (Serial Clock, Input, TTL)

SERCLK is the nominally 10 MHz clock from the Ethernet

controller chip to the MU9C8328. Frame parsing begins

only after the internal clock detector determines that

SERCLK is valid. Internally pulled down with nominal

50K resistor.

SERDAT (Serial Data, Input, TTL)

SERDAT is the NRZ data from the 10 MHz Ethernet

controller chip. The MU9C8328 uses SERCLK to strobe

SERDAT looking for a Start Frame delimiter (SFD), at

which point it begins filtering and learning activity on

the Destination Address (DA) and Source Address (SA).

/REJECT (Reject, Output, TTL)

The MU9C8328 takes /REJECT LOW to notify the

Ethernet controller chip to reject a frame under conditions

set in the Filter Control register.

/NETRDY (Network Ready, Input, TTL)

If /NETRDY is LOW, the MU9C8328 begins parsing

frame data received on the SERDAT input if SERCLK is

valid. The Ethernet controller chip, or the user, takes

/NETRDY HIGH to indicate that SERCLK or SERDAT

is invalid or is transmitting. The MU9C8328 frame parser

and internal state machines are returned to an idle state

after safely completing any LANCAM activity, while

ignoring any compare results. Internally pulled down with

nominal 50K resistor.

PROCESSOR INTERFACE

SYSCLK (System Clock, Input, TTL)

SYSCLK is a 20 MHz to 33 MHz continuous

clock provided by the host system and is the master clock

within the MU9C8328. It is used to determine the presence

of a valid clock on the SERCLK input, operate the three

internal state machines, and provide the proper timing of

the signals on the LANCAM port. If SYSCLK is below

30 MHz, a LANCAM speed grade of 120 ns is acceptable.

Above 30 MHz, a LANCAM speed grade of 90 ns or better

is required.

/CS (Chip Select, Input, TTL)

/CS is taken LOW by the host processor to gain access to

the registers of the MU9C8328 or to directly access the

LANCAM through the MU9C8328 internal

LANCAM registers. The state of /CS becomes effective

on the rising edge of SYSCLK. When /CS goes HIGH,

the MU9C8328 continues filtering and learning based on

conditions set in the Filter Control register and the frame

activity on the network interface.

/AS (Address Strobe, Input, TTL)

The falling edge of /AS latches the A(2–0) bus, and when

both /AS and /CS are LOW, the processor state machine

is enabled by first rising edge of the SYSCLK to begin

writes into or reads out of the MU9C8328.

Rev . 4a 2

MU9C8328 Ethernet Interface

/

PIN DESCRIPTIONS

/WE (Write Enable, Input, TTL)

/WE determines the direction of data flow into or out of

the MU9C8328’s processor interface. It also determines

the state of /W to the LANCAM when the processor is

accessing the MU9C8328’s internal LANCAM registers.

If /WE is LOW , the data is written into the register selected

by the A(2–0) bus. If /WE is HIGH, then data is read

out of the register selected by the A(2–0) bus.

A(2–0) (Address Bus, Input, TTL)

A(2–0) select the internal register in the MU9C8328

accessed by the host processor as shown in Table 1.

A(2–0) are latched by the falling edge of /AS.

D(15–0) (Data Bus, I/O, Three-state TTL)

D(15–0) is the processor data bus into and out of the

MU9C8328, and is demuxed to the internal registers as

selected by the A(2–0) bus. If the register selected is the

Control, Status or Op-Code register, when /WE is LOW,

D(15–0) is loaded on the second rising edge of SYSCLK

after both /AS and /CS are LOW. When /WE is HIGH,

data from the selected register is output to the D(15–0)

Continued

bus on the second rising edge of SYSLCK after both /AS

and /CS are LOW. For CAM access, the write or read

operation is completed when READY returns HIGH. If

/CS is HIGH, or if data is not being read out of the

MU9C8328, the output buffers go to HIGH-Z. Internally

pulled down with nominal 50K resistor.

READY (Ready, Output, Three-state, TTL)

When writing to the Control, Status, or Op-Code register,

READY goes LOW on the first rising edge of SYSCLK

after both /AS and /CS are LOW and returns HIGH on the

next rising edge of SYSCLK. For a read cycle from those

registers, READY may only show a negative-going spike

at the first rising edge of SYSCLK after both /AS and /CS

are LOW. The data will be valid before the next rising

edge of SYSCLK. When writing or reading to/from the

CAM registers, READY will go LOW on the first rising

edge of SYSCLK after both /CS and /AS are LOW.

READY returns HIGH four SYSCLK cycles later,

indicating that the CAM write cycle will complete after

the next rising edge of SYSCLK.

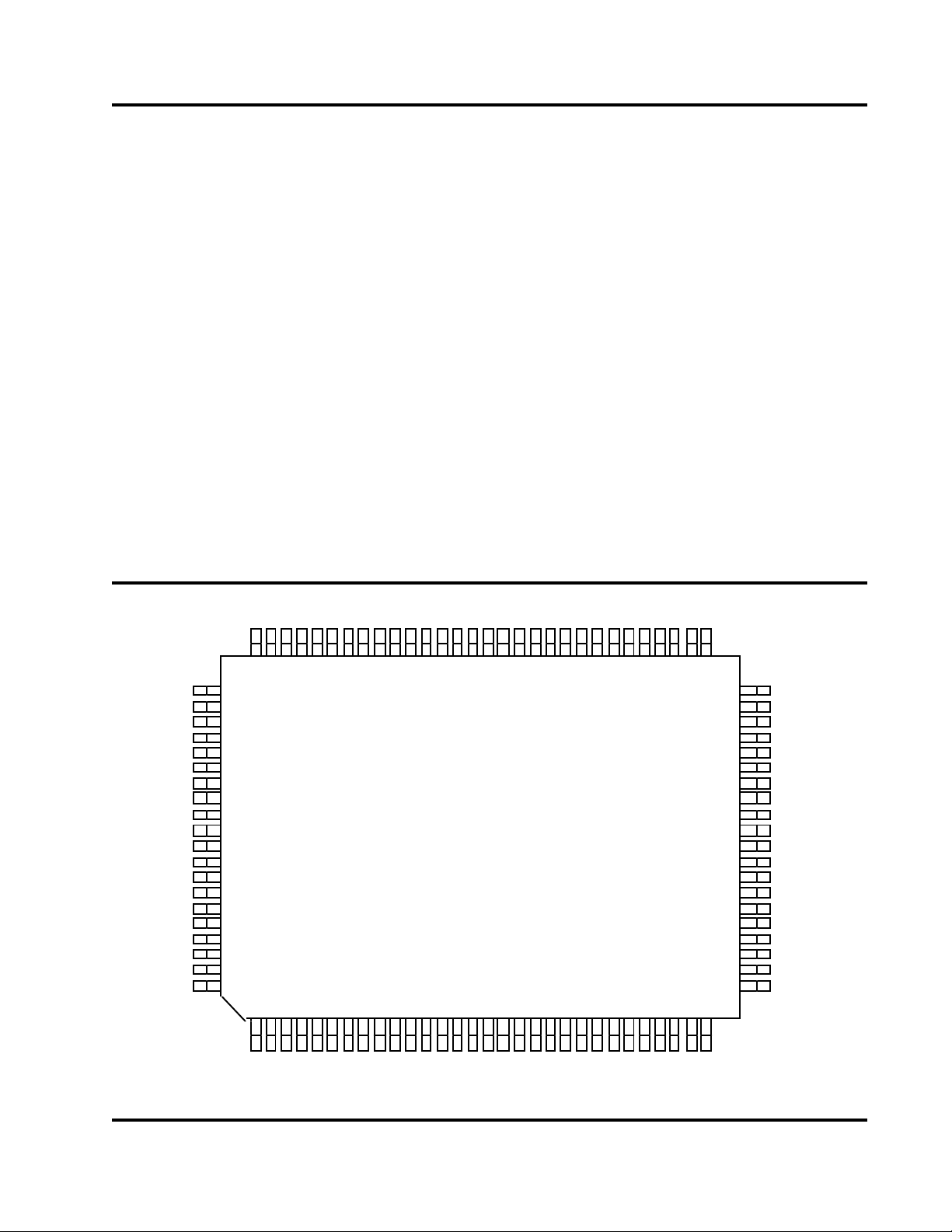

/FF

/M F

/E C

/CM

GND

VCC

RESET

READY

/INT

/W E

/AS

/CS

DQ15

DQ13

DQ12

8

A2

DQ11

73

72

71

9

10

D15

D14

GND

VCC

80

79

77

78

81

82

83

84

85

86

/E

/W

87

88

89

90

91

92

93

94

95

96

97

98

99

100

2

4

3

1

VCC

GND

SYSCLK

A1

DQ14

75

76

74

7

5

6

A0

GND

DQ10

70

69

68

67

DQ7

DQ9

DQ8

VCC

65

66

64

63

MU9C8328-RDC

100-pin PQFP

(Top View)

17

14

11

12

13

15

16

18

D9

D13

D12

D11

GND

D8

D10

VCC

PINOUT DIAGRAM

DQ6

19

D7

DQ5

DQ4

60

62

61

20

21

D6

D5

59

22

D4

DQ1

DQ2

DQ0

VCC

DQ3

58

57

56

23

24

25

D3

D2

GND

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

27

26

28

29

30

D1

VCC

GND

SERCLK

SE RDAT

/REJECT

NTE ST OUT

NTEST_ E N

GND

VCC

/NE TRDY

D0

3

Rev . 4a

MU9C8328 Ethernet Interface

PIN DESCRIPTIONS

/INT (Interrupt, Output, Three-state TTL)

/INT goes LOW to signal the processor that a frame has

been processed, and the results loaded into the Status

register. /INT returns HIGH when the Status register is read.

/RESET (Reset, Input, TTL)

When /RESET is taken LOW, all the internal state

machines are reset to their initial state. Any data stored in

the input address parser is cleared, and the Control, Status,

and Learn Op-Code registers are reset to their default

values. /RESET is synchronous and should be held LOW

for a minimum of two SYSCLK cycles. The user must set

the LANCAM Segment Control register after asserting

/RESET.

LANCAM INTERF ACE

DQ(15–0) (CAM Data Bus, I/O, Three-state TTL)

The DQ(15–0) bus communicates 16-bit data or

instructions between the MU9C8328 and the

LANCAM. When no data is being transmitted by either,

the bus goes HIGH-Z. Internally pulled down with nominal

50K resistor.

Continued

MU9C8328 is outputting data for the LANCAM to place

in its data registers or memory. If /CM is HIGH while /W

is HIGH, the LANCAM is outputting data from one of its

data registers or memory to the MU9C8328.

/EC (Enable Daisy Chain, Output, TTL)

The MU9C8328 takes /EC LOW to control a daisy chain

of LANCAMs by generating the /MF output from the

LANCAM in the case of a match between the contents of

its Comparand register and its memory . When /EC is LOW ,

only the LANCAM containing the match will respond to

write cycles, or output read data. When /EC is HIGH, all

LANCAMs will respond to write cycles.

/MF (Match Flag, Input, TTL)

The LANCAM takes /MF LOW to indicate to the

MU9C8328 that a match was found in its memory with

the contents of its Comparand register. /MF returns HIGH

after the MU9C8328 takes /EC HIGH, or the match

condition is no longer valid. In a daisy chain of

LANCAMs, the /MF signal comes from the /MF output

of the last LANCAM in the string. Internally pulled down

with nominal 50K resistor.

/E (Chip Enable, Output, TTL)

The MU9C8328 takes /E LOW to initiate LANCAM

activity by registering the /W, /CM, /EC, and DQ(15–0)

signals into the LANCAM. /E is taken HIGH to register

returning data into the MU9C8328.

/W (Write Gate, Output, TTL)

The MU9C8328 outputs /W to control the direction of

data flow between the MU9C8328 and the LANCAM. If

/W is LOW at the falling edge of /E, the MU9C8328 is

outputting data to the DQ(15–0) bus for the LANCAM to

input. When /W is HIGH at the falling edge of /E, the

LANCAM outputs data to the DQ(15–0) bus for input to

the MU9C8328.

/CM (Data/Command Select, Output, TTL)

The MU9C8328 outputs /CM to control whether

the LANCAM interprets the DQ(15–0) bus as containing

command information or data. If both /CM and /W are

LOW at the falling edge of /E, the MU9C8328 is outputting

an instruction for the LANCAM to execute, or a value for

one of the LANCAM configuration registers. If /CM is

LOW while /W is HIGH, then the LANCAM will be

outputting data from one of its configuration registers to

the MU9C8328. If /CM is HIGH while /W is LOW, the

/FF (Full Flag, Input, TTL)

The LANCAM takes /FF LOW to indicate to the

MU9C8328 that the LANCAM has no empty locations

remaining. /FF is taken HIGH when the LANCAM has

one or more locations still empty. In a daisy chain of

LANCAMs, the /FF signal comes from the /FF output pin

of the last LANCAM in the string. Internally pulled down

with nominal 50K resistor.

POWER AND GROUND

VCC, GND (Positive Power Supply, Ground)

The VCC pins must be connected externally to a power

source regulated to 5.0 ± 0.25 volts, and should be

adequately bypassed to the Ground pins through

both high and low frequency capacitors. The Ground pins

should all be connected to a common ground plane.

NTTESTOUT

Reserved - Do not connect.

NTEST_EN

Reserved - Tie low.

Rev . 4a 4

MU9C8328 Ethernet Interface

FUNCTIONAL DESCRIPTION

The MU9C8328 works with the MUSIC LANCAMs to

provide a complementary and versatile 10 MHz Ethernet

filtering solution for bridges, routers, and switches. Using

the serial NRZ data stream and clock available from many

Ethernet controller chips, the MU9C8328 parses the

incoming frame, finds the Start Delimiter, and forms the

Destination and Source addresses into 16-bit words for

relay to the LANCAM. After all three 16-bit DA segments

have been loaded into the LANCAM, an automatic

compare occurs between the incoming DA and the 48-bit

MAC addresses stored in the LANCAM. If a match is

found, the MU9C8328 is notified, and if Control Register

bit 5 is set for negative filtering, the /REJECT line will be

asserted if Control Register bit 3 is set. An interrupt can

also be generated over the /INT pin if Control Register bit

8 is set. Also, if Control Register bit 0 is set, the Associated

data in segment 0 of the matching entry in the LANCAM

will be retrieved and stored in the Associated Data register

for reading by the host processor. If a match is not found

on the DA, and Control Register bit 5 was set for positive

filtering, the /REJECT line will be asserted. An interrupt

can also be enabled for a no-match on a DA using Control

Register bit 10.

After the DA filtering, the Source Address is loaded

into the LANCAM in three segments. Upon the last

SA load, an automatic compare again takes place. If

there is a match between the SA and an entry in the

CAM, and Control Register bit 7 was set, an interrupt

is asserted. Positive and negative filtering on the SA is

also possible, set by Control Register bit 4, and the /INT

pin may be asserted as well. In the case of a no-match

on an SA, the SA can be automatically “learned” (i.e.,

moved to the first empty location in the LANCAM) if

Control Register bit 1 is set.

If a Loss of Carrier is detected by SERCLK staying LOW

for more than 16 SYSCLK cycles, an interrupt is triggered

if Control Register bit 12 is set. This interrupt also activates

if a collision is detected.

The host processor can access the MU9C8328, shown in

T able 1, at any time, even when a frame is being processed.

Access to the LANCAM through the LANCAM access

registers (04H to 07H) is arbitrated, however, with the

network having precedence. The host processor can have

control of the LANCAM by setting the Network Enable

bit in the Control register (bit 13) to a 0, which will disable

network filtering until it is returned to a 1. While disabled,

bit 14 in the Control register sets the MU9C8328 to accept

all frames by keeping /REJECT HIGH, or to reject all

frames by keeping /REJECT LOW.

Registers 04H through 07H allow the host processor access

to the LANCAM for Command and Data Write and Read

cycles, with /EC HIGH or LOW. This is often needed for

housekeeping activities, such as preventing the LANCAM

from becoming full by aging out old entries based on

timestamps stored in the Associated data (Segment 0) of

the LANCAM memory.

The /INT pin will go LOW at the end of the SA field to

indicate an interrupt for any of the reasons set in the

Control register. Reading the Status register to discover

the nature of the interrupt will take the /INT pin HIGH

again. The READY signal goes LOW after a host processor

write to a register or the LANCAM to indicate that the

Write cycle has begun and return HIGH after a fixed

number of SYSCLK cycles. It will also go LOW during a

read from the LANCAM and return HIGH when the data

from the LANCAM is valid. Since a network compare

activity has precedence over a host process access to the

LANCAM, READY will stay LOW until the network

activity is complete and the host-induced LANCAM read

has completed.

Figure 1 shows a typical network filtering sequence, where

the MU9C8328’s Control register was set to 2109H. This

setting enables network filtering, enables an interrupt for

a match found on the DA, enables negative filtering on

the DA (reject if a DA match is found), enables asserting

the /REJECT pin for compares on the DA, and enables

retrieving the Associated Data field from the matching

location in the LANCAM.

5

Rev . 4a

Loading...

Loading...