Multi-Tech Systems MT5600SMI-PL34, MT5600SMI-P92, MT5600SMI-L34, MT5600SMI-PL92, MT5600SMI-L92 User Manual

...Page 1

SocketModem

Embedded Modem

MT5600SMI Family

MT5600SMI-32

MT5600SMI-L32

MT5600SMI-P32

MT5600SMI-34

MT5600SMI-L34

MT5600SMI-XL34

MT5600SMI-P34

MT5600SMI-PL34

MT5600SMI-92

MT5600SMI-L92

MT5600SMI-XL92

MT5600SMI-P92

MT5600SMI-PL92

Ô

Developer’s Guide

Page 2

Copyright and Technical Support

SocketModemÔ Developer's Guide

MT5600SMI

MT5600SMI-XL34, MT5600SMI-P34, MT5600SMI-PL34, MT5600SMI-92, MT5600SMI-L92, MT5600SMI-XL92,

MT5600SMI-P92, MT5600SMI-PL92)

(MT5600SMI-32, MT5600SMI-L32, MT5600SMI-P32, MT5600SMI-34, MT5600SMI-L34,

PN S000306A, Version A

Copyright

This publication may not be reproduced, in whole or in part, without prior expressed written permission

from Multi-Tech Systems, Inc. All rights reserved.

Copyright © 2002-2003, by Multi-Tech Systems, Inc.

Multi-Tech Systems, Inc. makes no representations or warranties with respect to the contents hereof and

specifically disclaims any implied warranties of merchantability or fitness for any particular purpose.

Furthermore, Multi-Tech Systems, Inc. reserves the right to revise this publication and to make changes

from time to time in the content hereof without obligation of Multi-Tech Systems, Inc. to notify any person

or organization of such revisions or changes.

Revisions

Revision Level Date Description

A 09/04/03 First release.

Patents

This device covered by one or more of the following patents: 6,219,708; 6,031,867; 6,012,113; 6,009,082;

5,905,794; 5,864,560; 5,815,567; 5,815,503; 5,812,534; 5,809,068; 5,790,532; 5,764,628; 5,764,627;

5,754,589; 5,724,356; 5,673,268; 5,673,257; 5,644,594; 5,628,030; 5,619,508; 5,617,423; 5,600,649;

5,592,586; 5,577,041; 5,574,725; 5,559,793; 5,546,448; 5,546,395; 5,535,204; 5,500,859; 5,471,470;

5,463,616; 5,453,986; 5,452,289; 5,450,425; 5,355,365; 5,309,562; 5,301,274

Other Patents Pending.

Trademarks

Trademarks of Multi-Tech Systems, Inc. are SocketModem and the Multi-Tech logo.

Microsoft and Windows are registered trademarks or trademarks of Microsoft Corporation in the United

States and/or other countries. All other trademarks are owned by their respective companies.

World Headquarters

Multi-Tech Systems, Inc.

2205 Woodale Drive

Mounds View, Minnesota 55112

Phone: 763-785-3500 or 800-328-9717

Fax: 763-785-9874

Technical Support

Country By Email By Phone

France: support@multitech.fr (33) 1-64 61 09 81

India: support@multitechindia.com 91 (124) 6340778

U.K.: support@multitech.co.uk (44) 118 959 7774

U.S. and Canada: oemsales@multitech.com (800) 972-2439

Rest of the World: oemsales@multitech.com (763) 717-5863

Internet Address: http://www.multitech.com

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 2

Page 3

Table of Contents

Contents

Chapter 1 – Product Description and Specifications................................................................................ 5

Introduction ................................................................................................................................................ 5

Product Description ................................................................................................................................... 5

Features..................................................................................................................................................... 6

Technical Specifications ............................................................................................................................ 7

Sources of Additional Information.............................................................................................................. 7

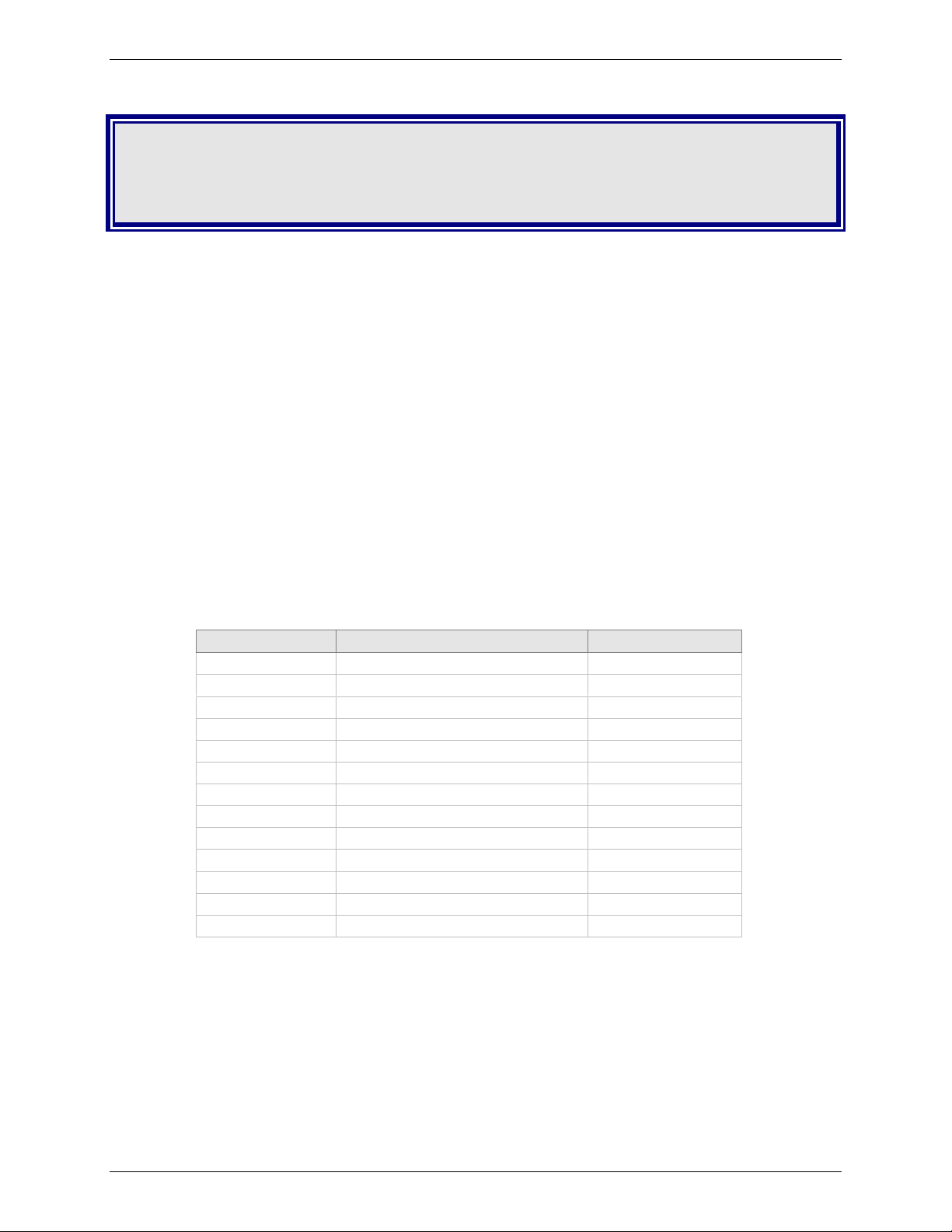

Chapter 2 – Mechanical Specifications ...................................................................................................... 8

Physical Dimensions ................................................................................................................................. 8

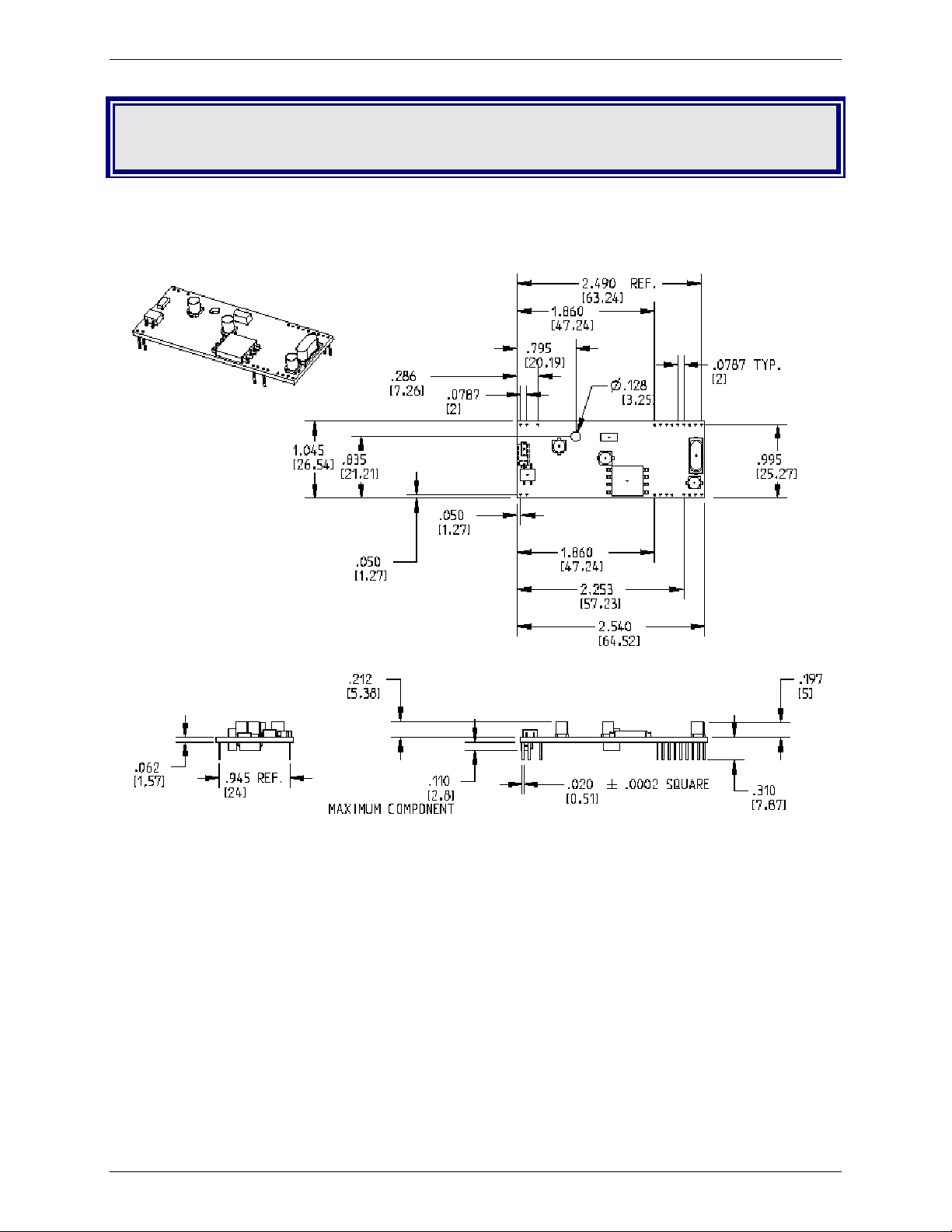

Serial Pin Configurations ........................................................................................................................... 9

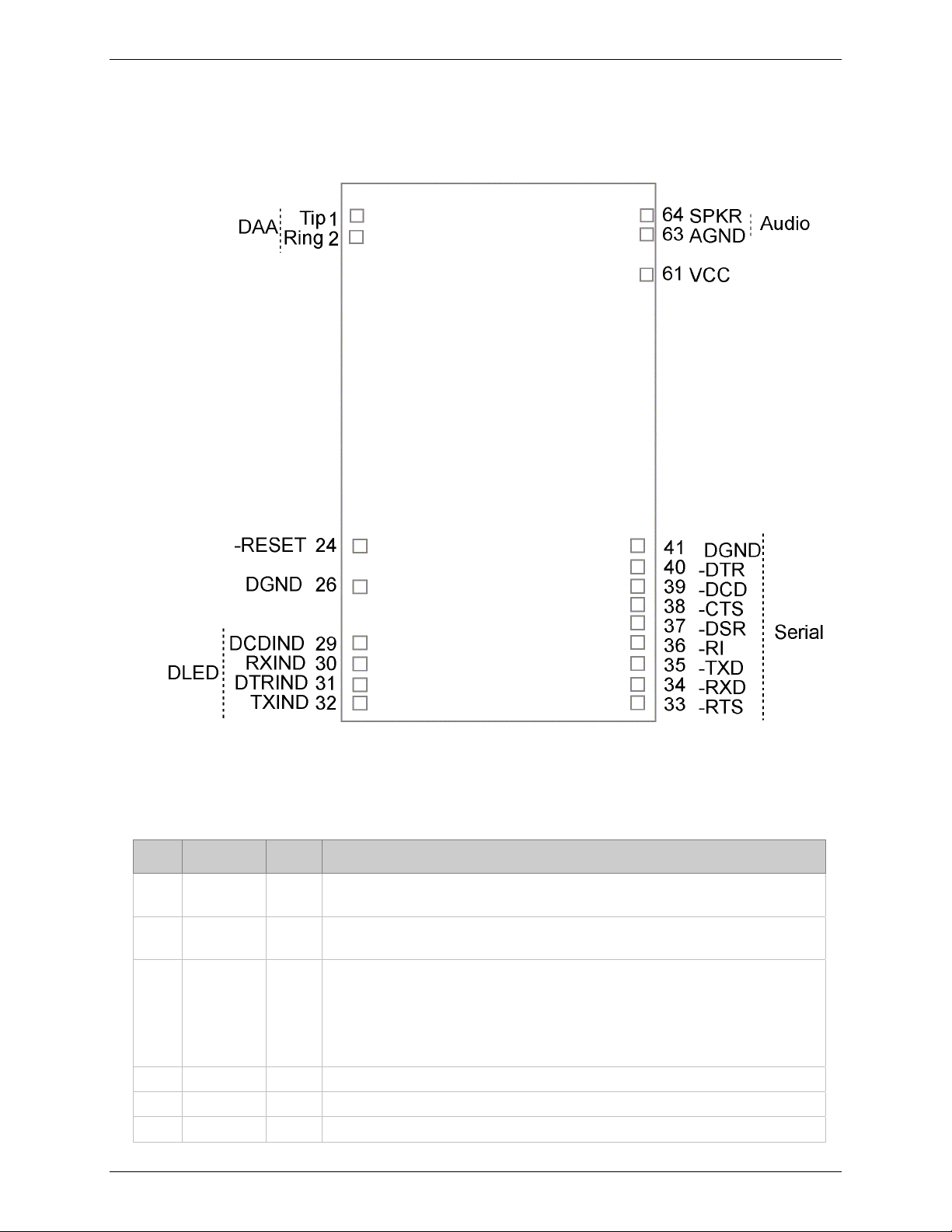

Parallel Pin Configurations ...................................................................................................................... 11

Chapter 3 – Electrical Characteristics ...................................................................................................... 13

Handling Precautions .............................................................................................................................. 13

I/O Electrical Characteristics ................................................................................................................... 13

3.3V Serial SocketModem ................................................................................................................... 13

3.3V Parallel SocketModem................................................................................................................. 13

5V Serial SocketModem ...................................................................................................................... 14

5V Parallel SocketModem.................................................................................................................... 14

Operating Conditions ............................................................................................................................... 14

Absolute Maximum Ratings..................................................................................................................... 14

Current and Power Requirements........................................................................................................... 15

Parallel Host Bus Timing ......................................................................................................................... 16

Parallel Host Bus Timing Table ........................................................................................................... 16

Parallel Host Bus - Read...................................................................................................................... 17

Parallel Host Bus - Write...................................................................................................................... 17

Chapter 4 – SocketModem Parallel Interface – A Programmer’s Description...................................... 18

SocketModem Parallel Interface.............................................................................................................. 18

Overview.................................................................................................................................................. 18

Register Signal Definitions ...................................................................................................................... 20

IER – Interrupt Enable Register (Addr = 1, DLAB = 0) ........................................................................ 20

FCR – FIFO Control Register (Addr = 2, Write Only) ..........................................................................21

IIR – Interrupt Identifier Register (Addr = 2) ........................................................................................ 22

LCR – Line Control Register (Addr = 3)............................................................................................... 23

MCR – Modem Control Register (Addr = 4) ........................................................................................ 24

LSR – Line Status Register (Addr = 5) ................................................................................................25

MSR – Modem Status Register (Addr = 6) ..........................................................................................26

RBX – RX Buffer (Receiver Buffer Register) (Addr = 0, DLAB = 0) .................................................... 26

THR – TX Buffer (Transmitter Holding Register) (Addr = 0, DLAB = 0) .............................................. 26

SCR – Scratch Register (Addr = 7)...................................................................................................... 27

Receiver FIFO Interrupt Operation.......................................................................................................... 28

Receiver Data Available Interrupt ........................................................................................................ 28

Receiver Character Timeout Interrupts................................................................................................ 28

Transmitter FIFO Interrupt Operation...................................................................................................... 28

Transmitter Empty Interrupt .................................................................................................................28

Chapter 5 – AT Commands, S-Registers, and Result Codes ................................................................. 29

Introduction .............................................................................................................................................. 29

Data Commands...................................................................................................................................... 30

Generic Modem Control Commands ...................................................................................................30

DTE-Modem Interface Commands ...................................................................................................... 36

Call Control Commands....................................................................................................................... 41

Modulation Control Commands ...........................................................................................................51

Error Control Commands..................................................................................................................... 55

Data Compression Commands............................................................................................................ 60

V.8/V.8bis Commands .........................................................................................................................63

Diagnostic Commands......................................................................................................................... 65

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 3

Page 4

Table of Contents

Compatibility Commands..................................................................................................................... 70

FastConnect Commands .....................................................................................................................71

V.92 +P and –Q Commands................................................................................................................ 71

S-Registers .............................................................................................................................................. 75

Result Codes ........................................................................................................................................... 83

Chapter 6 – Fax Class 1 and Class 1.0 Commands ................................................................................ 86

Fax I/O Processing .................................................................................................................................. 86

DTE-to-Modem Transmit Data Stream ................................................................................................86

Modem-to-DTE Receive Data Stream .................................................................................................86

Fax Mode Selection ............................................................................................................................. 87

Fax Origination..................................................................................................................................... 87

Fax Answering ..................................................................................................................................... 87

Fax Control Transmission ....................................................................................................................87

Fax Control Reception .........................................................................................................................88

Fax Data Transmission ........................................................................................................................89

Fax Data Reception .............................................................................................................................89

Commands and Parameters.................................................................................................................... 90

Mode Entry Commands .......................................................................................................................90

Mode Commands................................................................................................................................. 90

Service Class 1 Commands................................................................................................................. 94

Examples ................................................................................................................................................. 98

Chapter 7 – Voice Commands ................................................................................................................. 100

Voice Commands Overview .................................................................................................................. 100

<DLE> Shielded Event Codes Sent to the DTE ................................................................................101

<DLE> Shielded Codes Sent to the Modem (DCE)........................................................................... 102

Voice Configuration Commands............................................................................................................ 103

Basic Voice Commands ........................................................................................................................ 104

Chapter 8 – Setting Country Codes ........................................................................................................ 114

Appendix A – Mechanical Details ........................................................................................................... 115

Test/Demo Board Components............................................................................................................. 115

5V / 3.3V Jumper – JP6 ..................................................................................................................... 116

Serial Test/Demo Board Block Diagram................................................................................................ 116

Parallel Test/Demo Board Block Diagram ............................................................................................. 117

Appendix B - Safety/EMC Approvals, Design Considerations, and Regulatory Compliance........... 118

Approvals – Product Safety and EMC ................................................................................................... 118

Telecom Certifications .......................................................................................................................118

Regulatory Design Considerations ........................................................................................................ 119

Hardware Considerations .................................................................................................................. 119

EMC ...................................................................................................................................................120

Other Design Considerations ................................................................................................................ 121

PC Board Layout Guidelines.............................................................................................................. 121

Electromagnetic Interference (EMI) Considerations.......................................................................... 122

Safety ................................................................................................................................................. 122

5V Tolerant Inputs for 3.3V Modules .................................................................................................123

Regulatory Compliance ......................................................................................................................... 124

Regulatory Requirements for the United States ................................................................................ 124

Regulatory Requirements for Canada ...............................................................................................127

New Zealand Telecom Warning Notice ............................................................................................. 129

South African Statement ....................................................................................................................129

International Modem Restrictions ......................................................................................................130

EMC, Safety, and R&TTE Directive Compliance............................................................................... 130

Index........................................................................................................................................................... 131

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 4

Page 5

Chapter 1 – Product Description and Specifications

Chapter 1 – Product Description and

Specifications

Introduction

The Multi-Tech SocketModem creates communication-ready devices by integrating data functionality into

a single product design. The SocketModem is a space-efficient (1" × 2.5"), embedded modem that

provides V.92 or V.34/33.6K data communication. The complete, ready-to-integrate modem dramatically

reduces development time and costs for system designers. The SocketModem complies with telecom

requirements, can be shipped worldwide, and is globally configurable.

This guide provides the hardware, software, and troubleshooting information needed to effectively

integrate the SocketModem into your equipment. This guide also provides:

· commands that the developer can use to configure and control a data modem and

· Result codes that the modem issues in response to the commands.

Product Description

The MT5600SMI SocketModem is a standard 64-pin modem used for integrating data communications.

· It is a single-port 3.3V modem, which integrates the controller, DSP, and DAA in a 1" x 2.5" form

factor and communicates to a host controller via an asynchronous serial interface.

· It is available with an 8-bit parallel interface.

This Developer's Guide covers all of the MT5600SMI products:

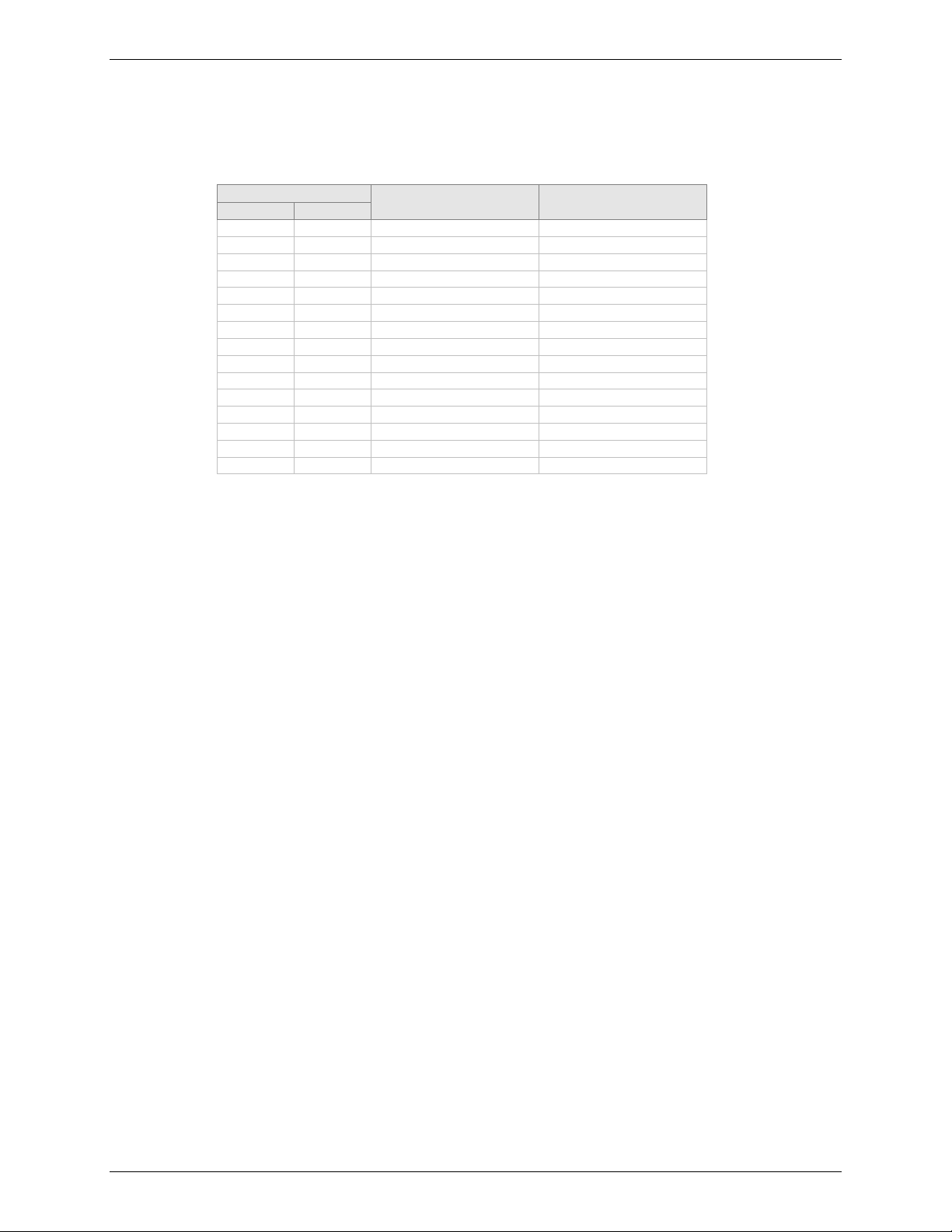

Product Description Region

MT5600SMI-32 V.32bis Serial Data/Fax 5V Global

MT5600SMI-L32 V.32bis Serial Data/Fax 3.3V Global

MT5600SMI-P32 V.32bis Parallel Data/Fax 5V Global

MT5600SMI-34 V.34 Serial Data/Fax 5V Global

MT5600SMI-L34 V.34 Serial Data/Fax 3.3V Global

MT5600SMI-XL34 V.34 Serial Data/Fax 3.3V Global

MT5600SMI-P34 V.34 Parallel Data/Fax 5V Global

MT5600SMI-PL34 V.34 Parallel Data/Fax 3.3V Global

MT5600SMI-92 V.92 Serial Data/Fax 5V Global

MT5600SMI-L92 V.92 Serial Data/Fax 3.3V Global

MT5600SMI-XL92 V.92 Serial Data/Fax 3.3V Global

MT5600SMI-P92 V.92 Parallel Data/Fax 5V Global

MT5600SMI-PL92 V.92 Parallel Data/Fax 3.3V Global

How to Read the Product Codes in the Table Above:

32 V.32bis/14.4K data rate

34 V.34/33.6K data rate

92 V.92/56K data rate

L 3.3 volt power input (default is 5V)

P Parallel interface (serial is default)

X Exclude LED pinouts

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 5

Page 6

Chapter 1 – Product Description and Specifications

Developer's Kit

A Developer's Kit is available. The serial kit allows you to plug in the SocketModem and use it as a serial

modem for testing, programming, and evaluation. The parallel kit turns the parallel module into an ISA

modem. Each kit includes one SocketModem, one development board with an RS-232 DB-25 connector,

wall power adapter, RJ-11 jack, and RS-232 cable.

Features

· Integrates the controller, data pump, and data access arrangement (DAA) in one module.

· V.92/56K, V.34/33.6K, or V.32bis/14.4Kdata rates

· Backward compatibility with lower speed data standards

· 3.3 Volt or 5 Volt power input options

· Serial or parallel interface

· V.17, V.21, V.27, V.29 Fax

· Fax Class 1 and 1.0

· V.22bis Fast Connect

· FastPOS (V.29)

· Voice send and receive functions

· LED pin output option

· Industry-standard error correction and data compression

· DTMF detection and distinctive ring

· Audio circuit outputs for audio call-progress monitoring

· Three-number storage for automatic dialing capabilities and non-volatile memory (NoVRAM) to

store user profiles

· Speaker interface for call progress monitoring

· Full-duplex data transmission over dial-up lines

· Line quality monitoring and retrain

· Line protection circuitry included

· Auto-dial, redial, and auto-answer

· Pulse or tone dial

· Call status display

· Extension pickup detection

· Caller ID detection

· Remote hang-up detection

· Digital PBX detection and protection

· 60-character command line buffering

· AT command compatibility

· Global approvals with a single module design

· Intelligent DAA technology detects line status

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 6

Page 7

Chapter 1 – Product Description and Specifications

Technical Specifications

The SocketModem meets the following specifications:

Data Format Serial or parallel interface

Data

Error Correction V.42 (LAP-M or MNP 2–4)

Data Compression V.42bis, MNP 5

Fax V.17, V.29, V.27ter, V.21 ch.2

Modes of Operation Full duplex over dial-up lines; data mode, command mode, online command mode

Advanced Extension pickup detection, remote hang-up detection, line-in-use detection,

Flow Control XON/XOFF (software), RTS/CTS (hardware)

Command Buffer 60 characters

Interface Serial or 8-bit parallel interface

Telephony/TAM V.253 commands: V.253

Weight 0.6 oz. (0.017 kg.)

Dimensions 1.045" × 2.541" × 0.680" (2.65 x 6.45 x 1.7 cm)

Power Consumption Typical: 115 mA (.38W @ 3.3 V DC); Maximum: 116 mA (.41 W @ 3.47 V DC)

V.92; V.90, V.34, V.32bis, V.32, V.22bis, V.22, V.23, V.21,Bell 212A & Bell 103

Class 1 and 1.0 commands

digital PBX detection and protection

2-bit and 4-bit ADPCM, 8-bit linear PCM, and 4-bit IMA coding

8 kHz sample rate

Concurrent DTMF, ring, and Caller ID detection

Typical: 117 mA (.58 W @ 5 V DC); Maximum: 118 mA (.61 W @ 5.25 V DC)

Operational

Temperature

Storage Temperature -10 to +85° C

0 to +70° C

Humidity Range: 20 to 90% (non-condensing)

Sources of Additional Information

For information on Multi-Tech modem installation, AT commands, S-Registers, and testing refer to the

applicable user manual that came with your Multi-Tech modem. Multi-Tech manuals and other resources

are on the Multi-Tech web page at http://www.multitech.com.

For additional Multi-Tech information, contact:

http://www.multitech.com for News, Products, Solutions, Support, Manuals and more.

ftp://ftp.multitech.com for Modem Firmware, Modem INFs, Utilities, etc.

oemsales@multitech.com for email technical support.

The Global Engineering Documents Web site manages a collection of more than one million documents

from over 460 organizations worldwide: http://global.ihs.com

Phone: 800-854-7179

Fax: 303-792-2192

ITU is the leading publisher of telecommunication technology, regulatory and standard information, with

over 4,000 titles in printed form, on CD-ROM and online at http://www.itu.int/publications/

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 7

Page 8

Chapter 2 – Mechanical Specifications

Chapter 2 – Mechanical Specifications

Physical Dimensions

Figure 2–1. Maximum Component Height

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 8

Page 9

Chapter 2 – Mechanical Specifications

Serial Pin Configurations

The serial interface use an 16-pin interface to provide an on-board DAA with tip and ring connections,

audio circuit for call-progress monitoring and serial interface via logic level signals.

Figure 2–2. Serial SocketModems Pins

Available with or without LED Pins

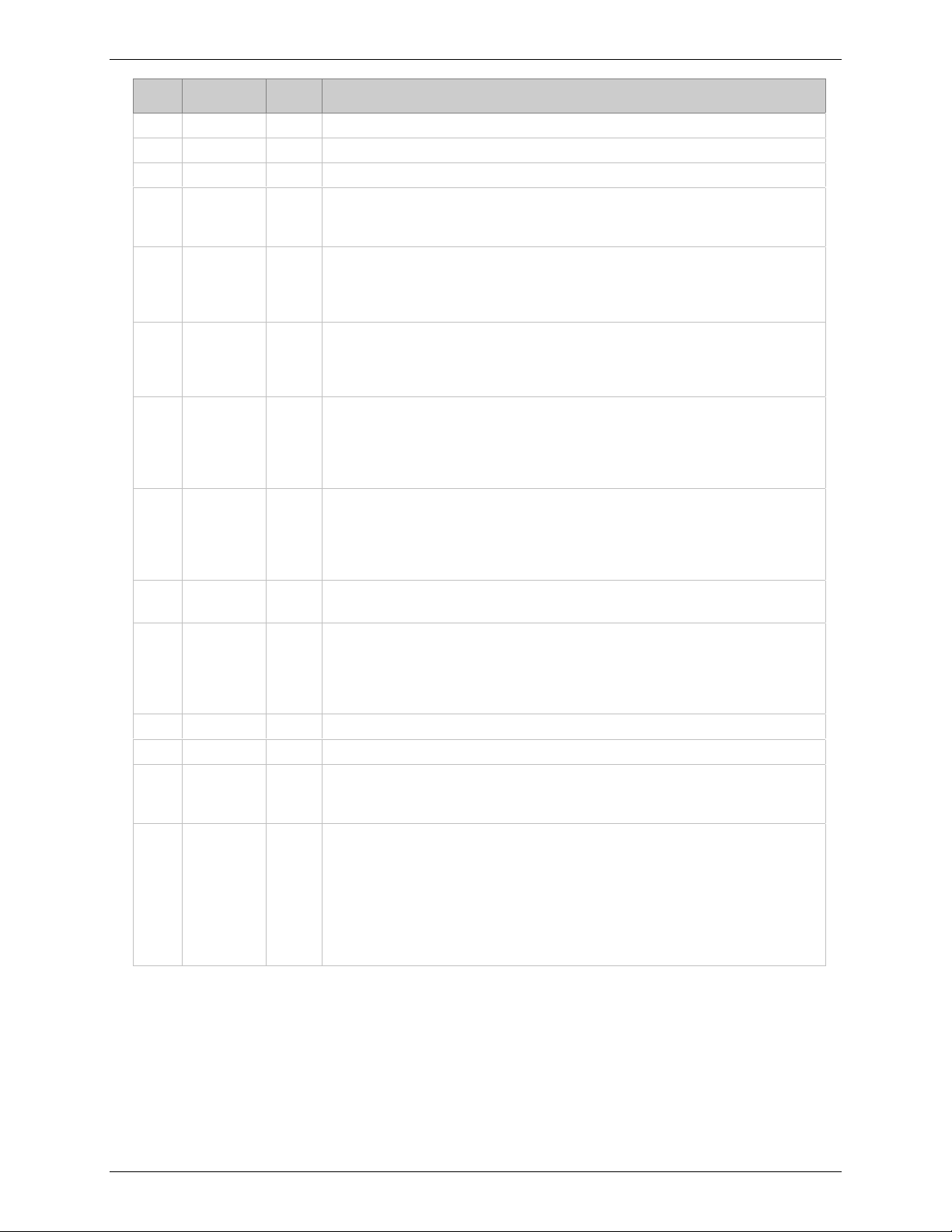

Pin Descriptions for Serial SocketModem Devices

Pin#Signal

Name

1 Tip I/O

2 Ring I/O

24 –RESET I

26 DGND

29 DCDIND

30 RXIND

I/O

Type

Description

Tip Signal from Telco. Tip connection to the phone line (RJ11 Pin 3).

SocketModem is Tip/Ring is polarity insensitive.

Ring Signal from Telco. Ring connection to the phone line (RJ11 Pin 4).

SocketModem is Tip/Ring is polarity insensitive.

Modem Reset (with weak pull-up). The active low –RESET input resets the

SocketModem logic and returns the AT command set to the original factory

default values or to "stored values" in NVRAM. –RESET is tied to VCC

through a 400ms time constant circuit for "Power-on-Reset" functionality. The

modem is ready to accept commands within 6.5 seconds of power-on or reset.

Reset must be asserted for a minimum of 300 ns.

Ground

DCD LED. Output from 74AC05 with 1500 Ohms pull-up.

RX LED. Output from 74AC05 with 1500 Ohms pull-up.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 9

Page 10

Chapter 2 – Mechanical Specifications

Pin#Signal

Name

31 DTRIND

32 TXIND

33 –RTS I

34 –RXD O

35 –TXD I

36 –RI O

37 –DSR O

38 –CTS O

39 –DCD O

40 –DTR I

41 DGND

61 VCC

63 AGND

64 SPKR

I/O

Type

Description

DTR LED. Output from 74AC05 with 1500 Ohms pull-up.

TX LED. Output from 74AC05 with 1500 Ohms pull-up.

Request to Send. RTS signal is used for hardware flow control.

Received Data. Used to send data received from the telephone line and also

modem responses to the DTE. Modem response take priority over incoming

data. When no data is transmitted, the signal is held in mark condition.

Transmit Data. The DTE uses this line to send data to the modem for

transmission over the telephone line or to transmit commands to the modem.

The DTE should hold this circuit in the mark state when no data is being

transmitted or during intervals between characters.

Ring Indicate. –RI output ON (low) indicates the presence of an ON segment

of a ring signal on the telephone line.

The modem will not go off-hook when –RI is active; the modem waits for –RI

to go inactive before going off-hook.

Data Set Ready. –DSR indicates modem status to the DTE. –DSR OFF

(high) indicates that the DTE is to disregard all signals appearing on the

interchange circuits except Ring Indicator (–RI). It reflects the status of the

local data set, and does not indicate an actual link with any remote data

equipment.

Clear To Send. –CTS is controlled by the modem to indicate whether or not

the modem is ready to transmit data. –CTS ON, indicates to the DTE that

signals presented on TXD will be transmitted to the telephone line. –CTS OFF

indicates to the DTE that it should not transfer data across the interface on

TXD.

Data Carrier Detect. –DCD output is ON (low) when a carrier is detected on

the telephone line or OFF (high) when carrier is not detected.

Data Terminal Ready (Active Low). The –DTR input is turned ON (low) by

the DTE when the DTE is ready to transmit or receive data. –DTR ON

prepares the modem to be connected to the telephone line, and, once

connected, maintains the connection. –DTR OFF places the modem in the

disconnect state.

Ground.

3.3V DC Power.

Analog Ground. Analog ground is tied common with DGND on the

SocketModem. To minimize potential ground noise issues, connect audio

circuit return to AGND.

Speaker Output. SPKR is a single ended-output. SPKR is tied directly to the

CODEC. One side of a differential AC output coupled through a 6.8K ohm

resistor and capacitor.

The call progress speaker interface signal is:

· Digital speaker output (DSPKOUT); output

DSPKOUT is a square wave output in data mode used for call progress or

carrier monitoring. This output can be optionally connected to a low-cost onboard speaker, e.g., a sounducer, or to an analog speaker circuit.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 10

Page 11

Chapter 2 – Mechanical Specifications

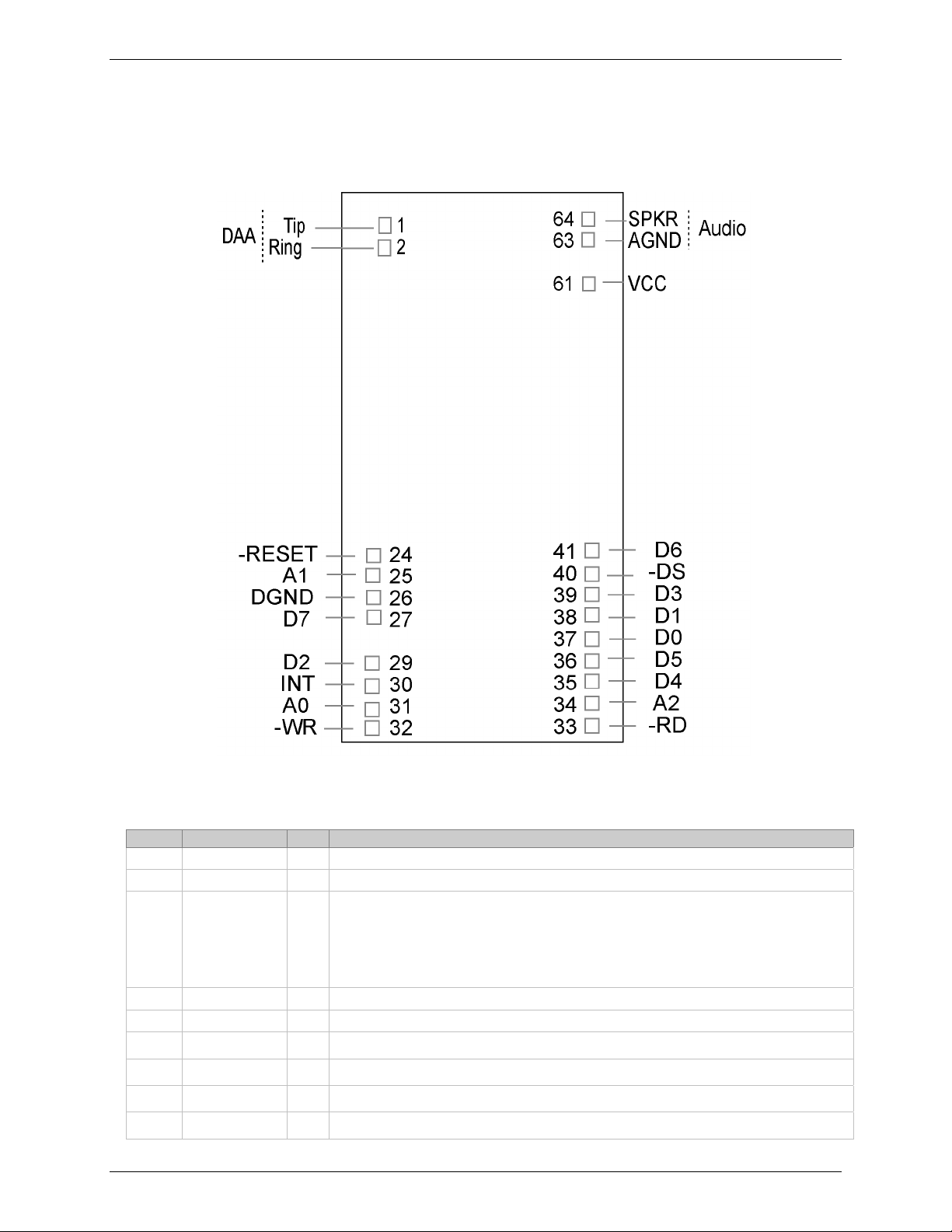

Parallel Pin Configurations

The parallel interface SocketModem uses a 22-pin interface to provide an on-board DAA with tip and ring

connections, audio circuit for call-progress monitoring, and parallel interface.

Figure 2–3. Parallel SocketModem Pins

Pin Descriptions for a Parallel SocketModem Device

Pin # Signal Name I/O Description

1 Tip I/O

2 Ring I/O

24 –RESET I

25 A1

26 DGND GND

27 D7 O

29 D2 O

30 INT O

31 A0 I

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 11

Telephone Line Interface – TIP

Telephone Line Interface – RING

Modem Reset (CMOS input with weak pull-up). The active low –RESET input

resets the SocketModem logic and returns the AT command set to the original

factory default values or to "stored values" in NVRAM.

The modem is ready to accept commands within 6.5 seconds of power-on or

reset. Reset must be asserted for a minimum of 300 ns.

Host Bus Address Line 1

Digital Ground

Host Bus Data Line 7

Host Bus Data Line 2

Host Bus Interrupt Line, Active High, Resets on Low

Host Bus Address Line 0

Page 12

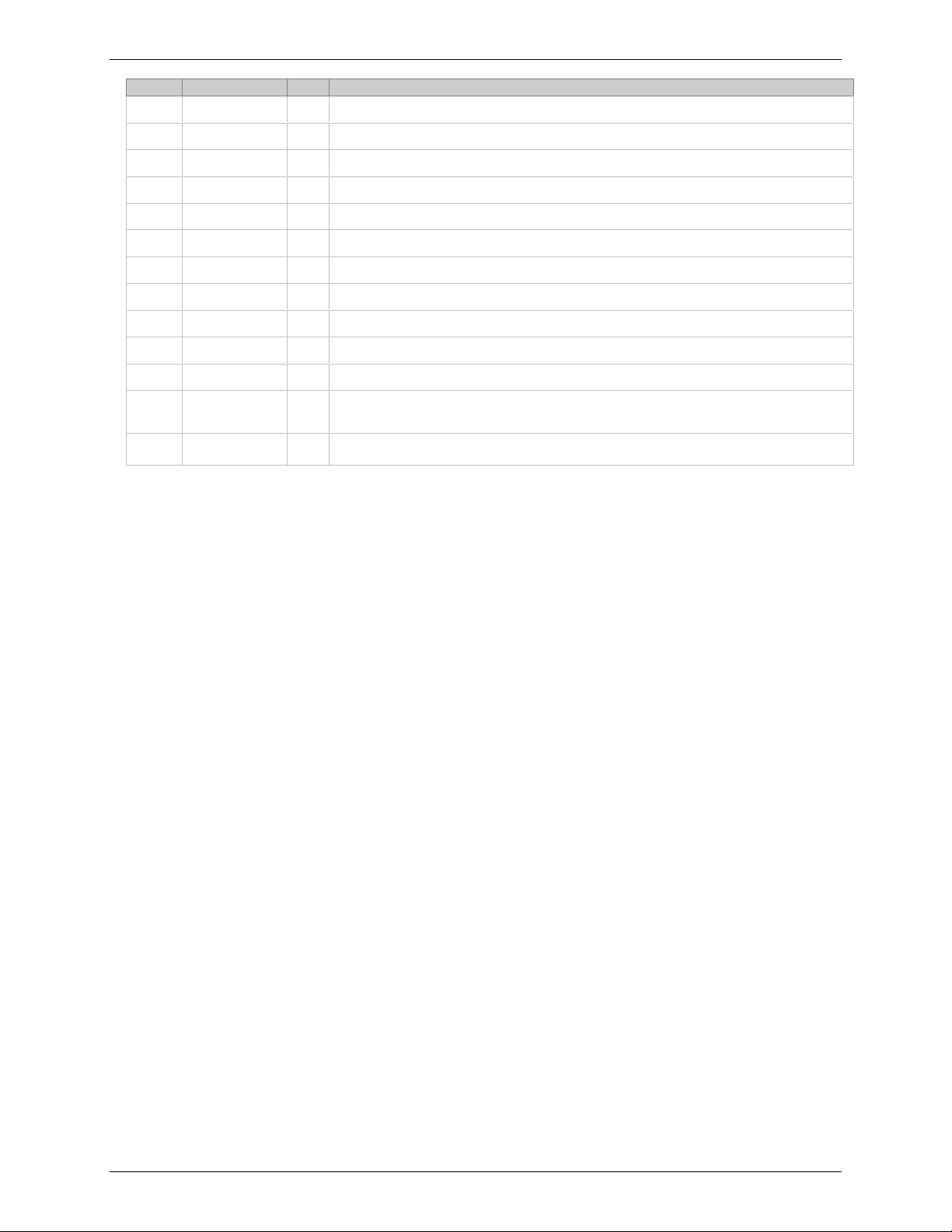

Pin # Signal Name I/O Description

32 –WT I

33 –RD I

34 A2 I

35 D4 O

36 D5 O

37 D0 O

38 D1 O

39 D3 O

40 –CS I

41 D6 O

61 VCC PWR

63 AGND GND

Host Bus Write. When low, allows host to write to SocketModem.

Host Bus Read. When low, allows host to read from SocketModem.

Host Bus Address Line 2

Host Bus Data Line 4

Host Bus Data Line 5

Host Bus Data Line 0

Host Bus Data Line 1

Host Bus Data Line 3

Host Bus Chip Select; active low

Host Bus Data Line 6

3.3V or 5V Supply (depends upon model).

Analog Ground. This is tied common with DGND on the SocketModem. To

minimize potential ground noise issues, connect audio circuit return to AGND.

Chapter 2 – Mechanical Specifications

64 SPKR O

Speaker, Call Monitor

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 12

Page 13

Chapter 3 – Electrical Characteristics

Chapter 3 – Electrical Characteristics

Handling Precautions

All electronic devices should be handled with certain precautions to avoid damage due to the

accumulation of static charge. Although input protection circuitry has been incorporated into the devices

to minimize the effect of this static buildup, proper precautions should be taken to avoid exposure to

electrostatic discharge during handling and mounting.

I/O Electrical Characteristics

3.3V Serial SocketModem

3.3V DC Characteristics (TA = 0°C to 70°C; VDD = 3.3 V ± 0.3 V) VDDMAX = 3.6 V

Inputs

–DTR (40), –TXD (35), –RTS (33), –RESET (24)

Inputs

–DCD (39), –CTS (38), –DSR (37), –RI (36), –RXD (34)

2mA, Z INT = 120

Digital Input Capacitance 50pF

W

Input High

Min 2.0 V

Output High

Min 2.4 V

Input Low

Max 0.8 V

Output Low

Max 0.5 V

3.3V Parallel SocketModem

Electrical characteristics for Parallel SocketModem devices are presented below.

3.3V DC Characteristics (TA = 0°C to 70°C; VDD = 3.3 V ± 0.3 V)

Digital Inputs

–DS (40)

Digital Inputs (hysteresis input buffer)

A0 (31), A1 (25), A2 (34), –WR (32), –RD (33)

8mA Z

Digital Input/Output

DO (37), D1 (38), D2 (29), D3 (39), D4 (35), D5

(36), D6 (41), D7 (27)

2mA, Z

= 50W 2mA Z

INT

= 120 W

INT

= 120 W

INT

Input High

Min 2.0 V

Input High

Min 2.0 V

Input High

Min 2.0 V

Output High

Min 2.4 V

VDDMAX = 3.6 V

Input Low

Max 0.8 V

Input Low

Max 0.8 V

Input Low

Max 0.8 V

Output Low

Max 0.5 V

Digital Output

INT (30)

2mA, Z

Digital Input Capacitance 50pF

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 13

= 120 W

INT

Output High

Min 2.4 V

Output Low

Max 0.5 V

Page 14

Chapter 3 – Electrical Characteristics

5V Serial SocketModem

5 Vdc Characteristics (TA = 0 °C to 50 °C; VDD = 5 V ± 0.25 V) VDDMAX = 5.25 V

Digital Inputs

–DTR (40), –TXD (35), –RTS (33), –RESET (24)

Digital Outputs

–DCD (39), –CTS (38), –DSR (37), –RI (36), –RXD (34)

Digital Input Capacitance 5 PF

Input High

Min 3.5 V

Output High

Min 4 V

Input Low

Max .8 V

Output Low

Max 0.5 V

Current Drive

15 ma

5V Parallel SocketModem

5 Vdc Characteristics (TA = 0 °C to 50 °C; VDD = 5 V ± 0.25 V) VDDMAX = 5.25 V

Digital Inputs

–DS (40)

Digital Inputs (hysteresis input buffer)

A0 (31), A1 (25), –WR (32), –RD (33)

Digital Input / Output

DO (37), D1 (38), D2 (29), D3 (39), D4 (35), D5 (36),

D6 (41), D7 (27)

Digital Output

INT (30)

Input High

Min 2 V

Input High

Min 2 V

Input High

Min 2 V

Output High

Min 2.4 V

Input Low

Max .8 V

Input Low

Max .8 V

Input Low

Max .8 V

Output Low

Max 0.5 V

Current Drive

8 ma

Current Drive

8 ma

Digital Input Capacitance 5 PF

Operating Conditions

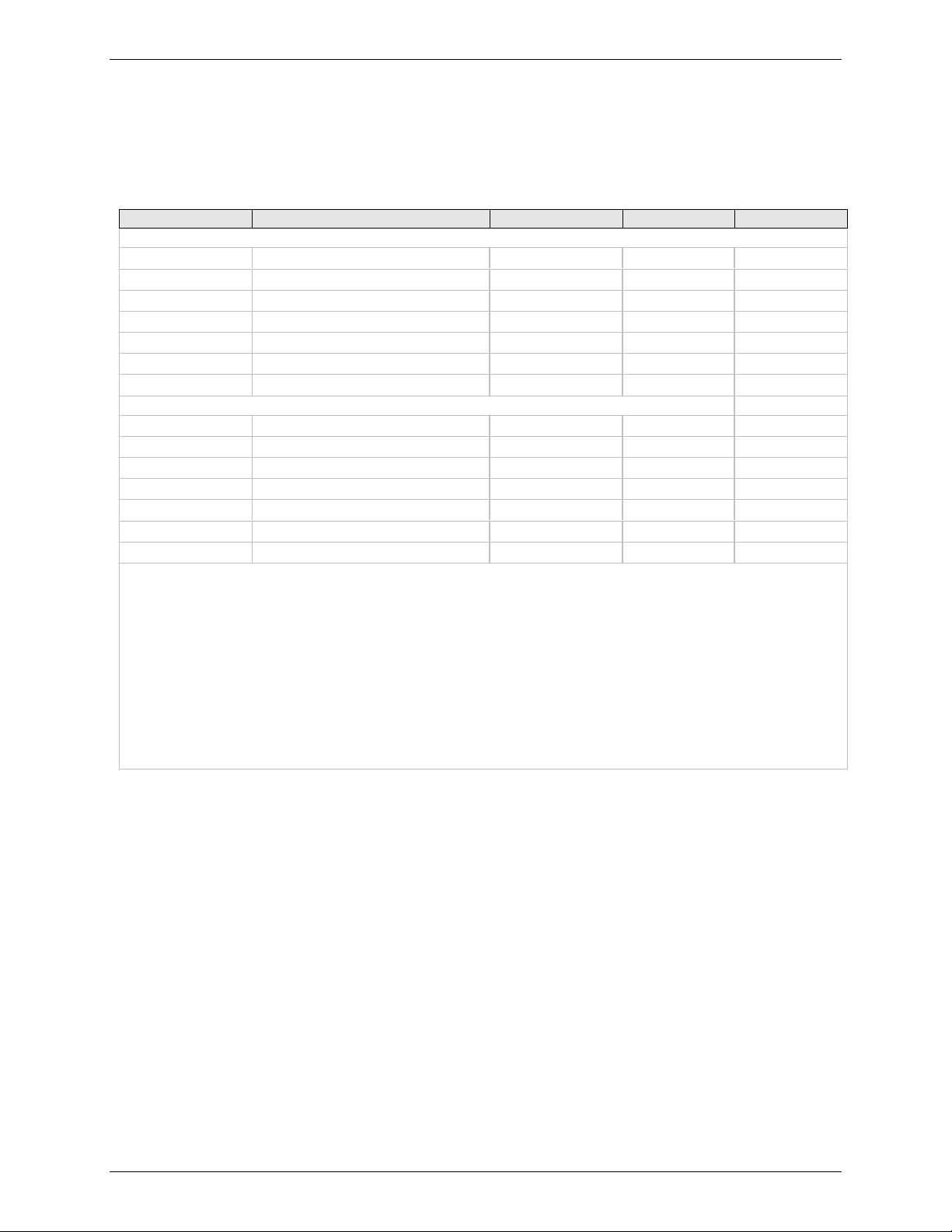

Parameter Symbol Limits Units

+3.3 V Configuration

Supply voltage (Pin 61 = +3.3 V) VDD +3.13 to +3.47 VDC

Operating ambient temperature T

+5 V Configuration

Supply voltage (Pin 61 = +5 V) VDD +4.75 to +5.25 VDC

Operating ambient temperature

A

T

A

0 to +70 °C

0 to +70 °C

Absolute Maximum Ratings

Parameter Symbol Limits Units

Supply voltage (Pin 61 = +3.3 V) VDD -0.5 to +4.0 VDC

Supply voltage (Pin 61 = +5 V)

Input voltage V

Voltage applied to outputs in high impedance (Off) state V

Storage temperature T

VDD -0.5 to +7.0 VDC

IN

OUT

STG

-0.5 to (VDD +0.5) VDC

+3.13 to +3.47

-40 to +80 °C

VDC

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 14

Page 15

Chapter 3 – Electrical Characteristics

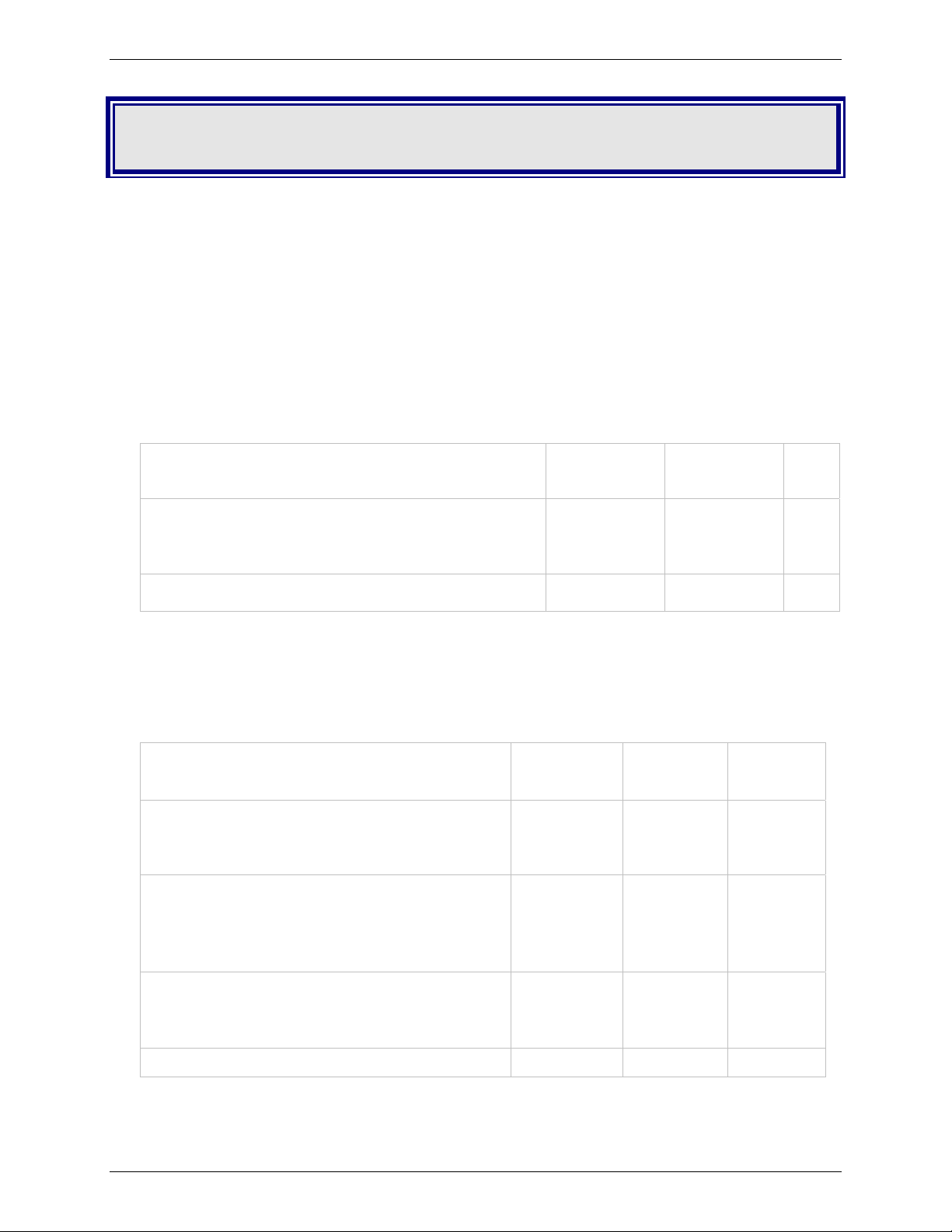

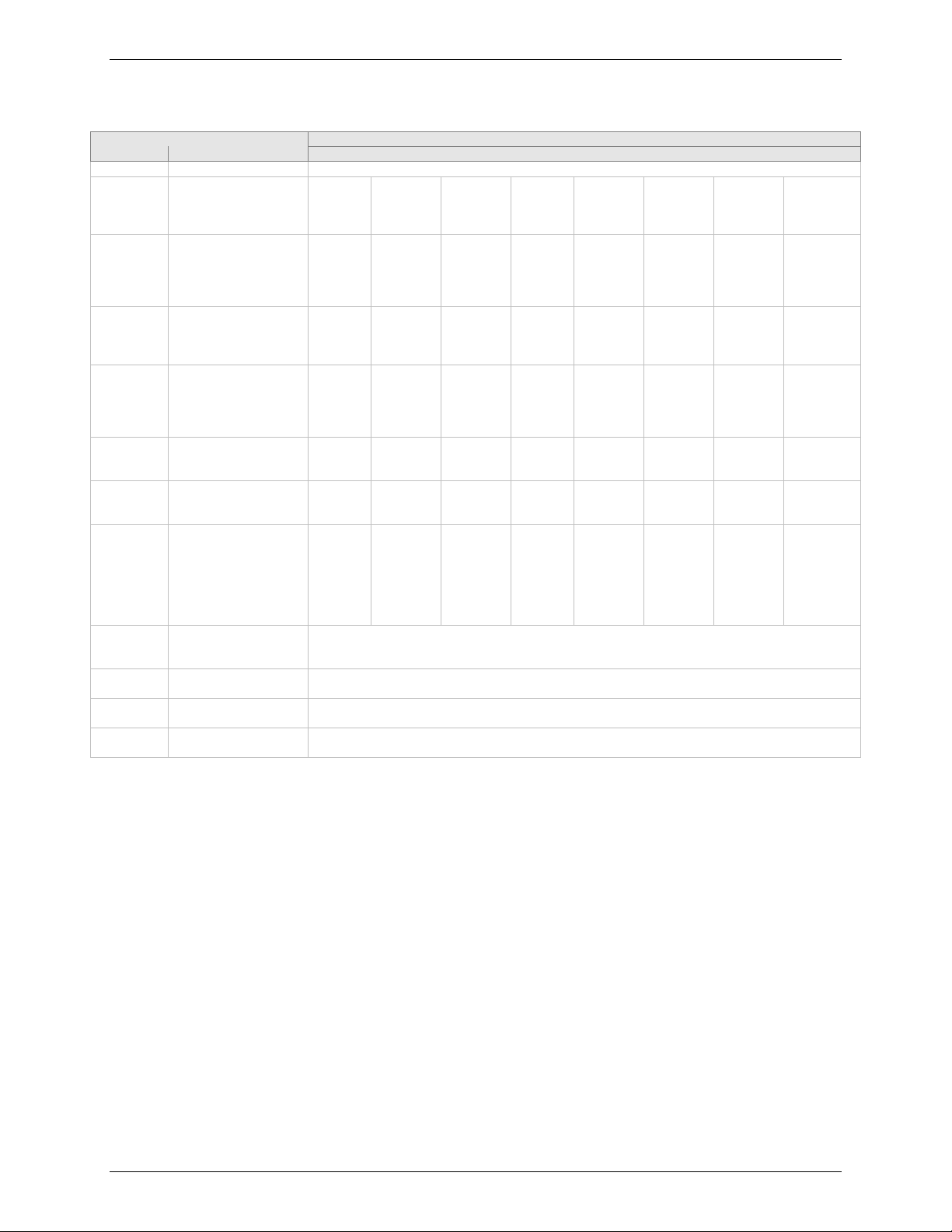

Current and Power Requirements

Typ.

Mode

Normal Mode (Serial interface) 115 116 0.38 0.41

Normal Mode (Serial interface) 117 118 0.58 0.61

Normal Mode (Parallel interface) 117 118 0.58 0.61

Test conditions:

For Pin 61 = +5 V, VDD = +5 V for typical values; VDD = +5.25 V for maximum values.

For Pin 61 = +3.3 V, VDD = +3.3 V for typical values; VDD = +3.47 V for maximum values.

Current (mA)

+3.3 V Configuration (VDD = +3.3 V)

+5 V Configuration (VDD = +5 V)

Max.

Current (mA)

Typ.

Power (mW)

Max.

Power (mW)

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 15

Page 16

Chapter 3 – Electrical Characteristics

Parallel Host Bus Timing

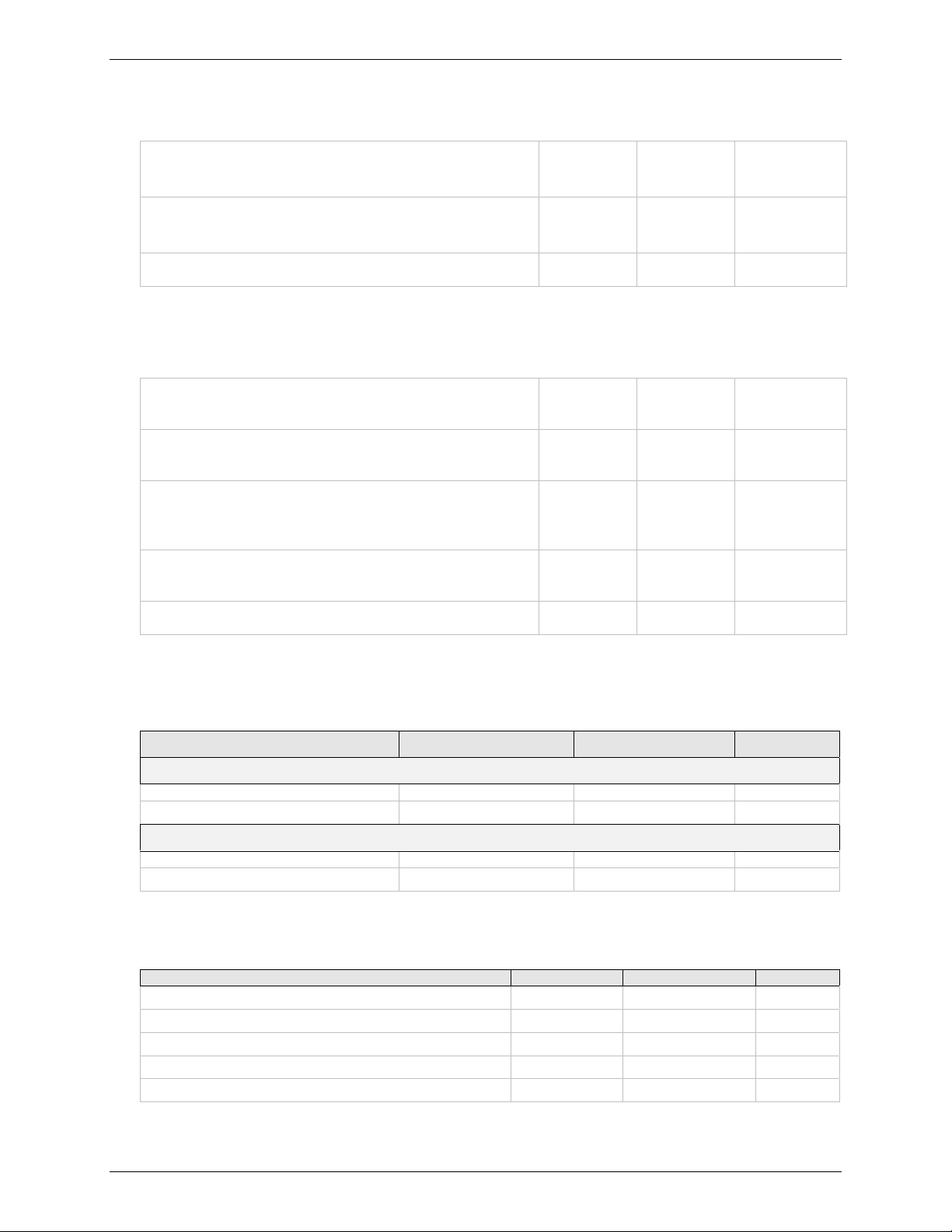

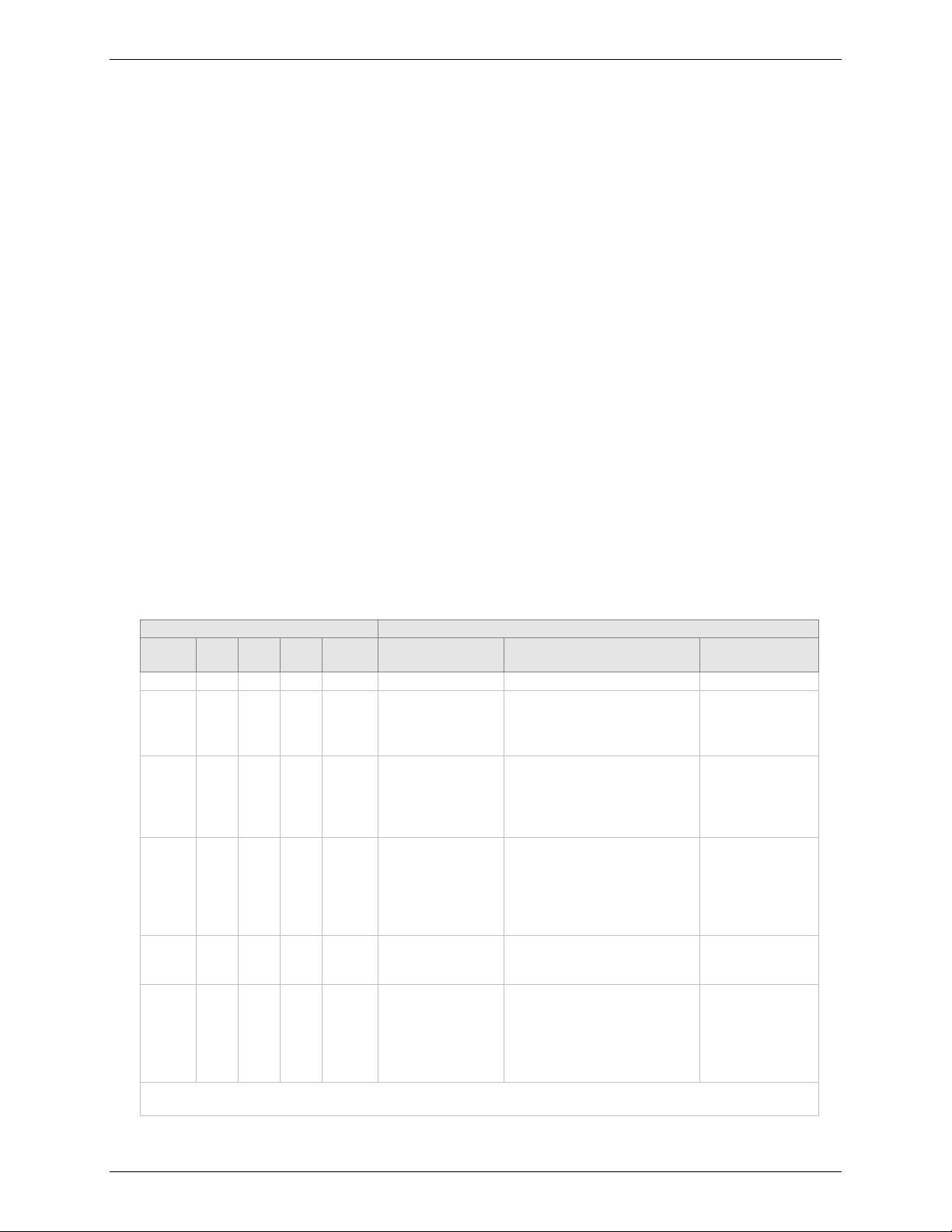

Parallel Host Bus Timing Table

Symbol Parameter Min Max Units

t

AS

t

AH

t

CS

t

CH

t

RD

t

DD

t

DRH

Address Setup 5 - ns

Address Hold 10 - ns

Chip Select Setup 0 - ns

Chip Select Hold 10 - ns

RD Strobe Width 45 - ns

Read Data Delay - 25 ns

Read Data Hold 5 - ns

WRITE (See Notes)

t

AS

t

AH

t

CS

t

CH

t

WT

t

DS

t

DWH

Address Setup 5 - ns

Address Hold 15 - ns

Chip Select Setup 0 - ns

Chip Select Hold 10 - ns

WT Strobe Width 75 - ns

Write Data Setup (see Note 4) - 20 ns

Write Data Hold (see Note 5) 5 - ns

Notes:

1. When the host executes consecutive Rx FIFO reads, a minimum delay of 2 times the internal CPU

clock cycle plus 15 ns (85.86 ns at 28.224 MHz) is required from the falling edge of RD to the falling

edge of the next Host Rx FIFO RD clock.

2. When the host executes consecutive Tx FIFO writes, a minimum delay of 2 times the internal CPU

clock cycle plus 15 ns (85.86 ns at 28.224 MHz) is required from the falling edge of WT to the

falling edge of the next Host Tx FIFO WT clock.

t

3.

RD' tWT

4.tDS is measured from the point at which both CS and WT are active.

t

5

.

DWH is measured from the point at which either CS and WT become active.

t

=

CYC

+ 15 ns.

6. Clock Frequency = 28.224 MHz clock.

READ (See Notes)

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 16

Page 17

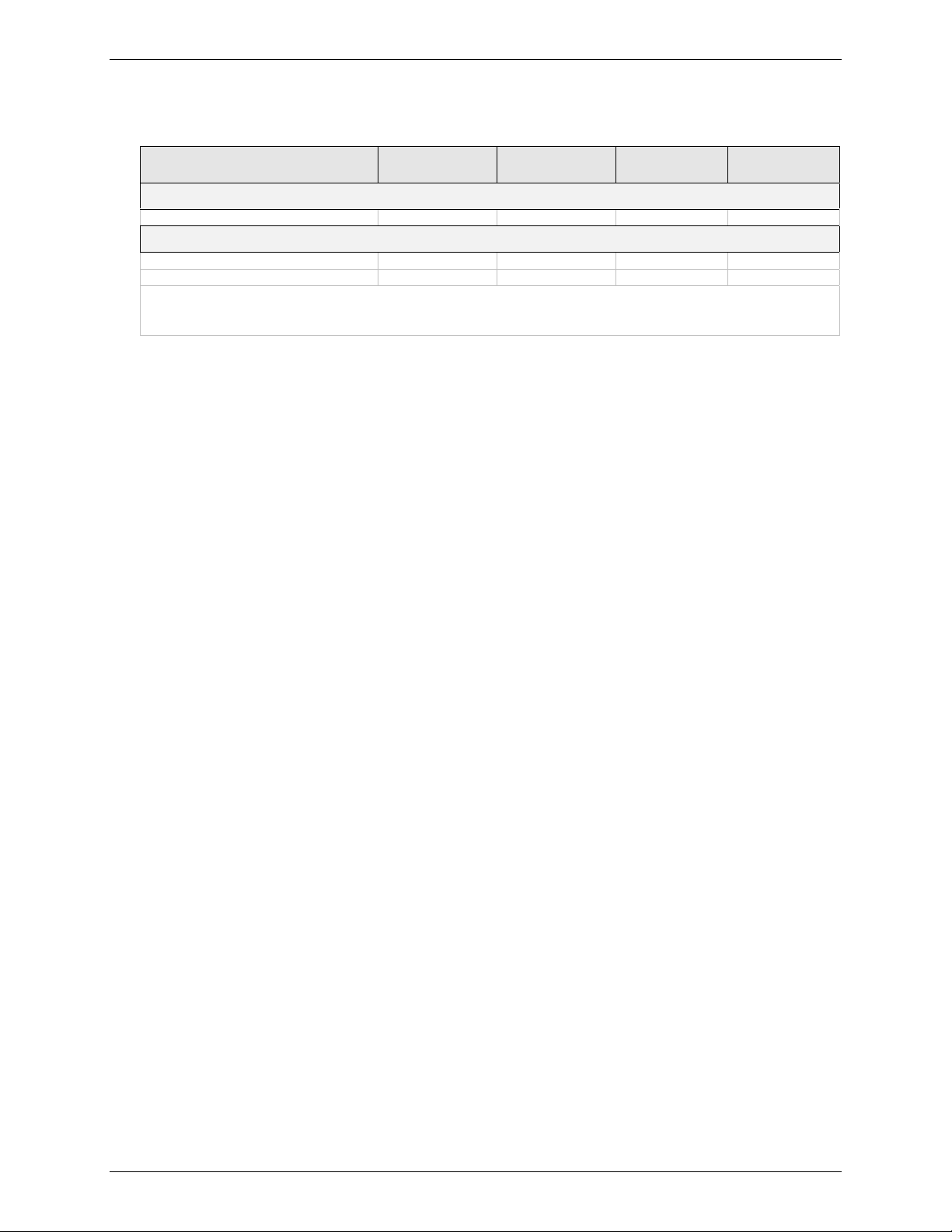

Parallel Host Bus - Read

Chapter 3 – Electrical Characteristics

Parallel Host Bus - Write

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 17

Page 18

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

Chapter 4 – SocketModem Parallel

Interface – A Programmer’s

Description

SocketModem Parallel Interface

The modem supports a 16550A interface in parallel interface versions. The 16550A interface can operate

in FIFO mode or non-FIFO mode. Non-FIFO mode is the same as the 16450 interface operation. FIFO

mode’s unique operations are described in this chapter.

Overview

The modem emulates the 16450/16550A interface and includes both a 16-byte receiver data first-in firstout buffer (RX FIFO) and a 16-byte transmit data first-in first-out buffer (TX FIFO).

FIFO Mode Selected

When FIFO mode is selected in the FIFO Control Register (FCR0 = 1), both FIFOs are operative.

Furthermore, when FIFO mode is selected, DMA operation of the FIFO can also be selected (FCR3 = 1).

FIFO Mode Not Selected

When FIFO mode is not selected, operation is restricted to a 16450 interface operation.

Receive Data

Received Data is read by the host from the Receiver Buffer (RX Buffer). The RX Buffer corresponds to

the Receiver Buffer Register in a 16550A device. In FIFO mode, the RX FIFO operates transparently

behind the RX Buffer. Interface operation is described with reference to the RX Buffer in FIFO and nonFIFO modes.

Transmit Data

Transmit Data is loaded by the host into the Transmit Buffer (TX Buffer). The TX Buffer corresponds to

the Transmit Holding Register in a 16550A device. In FIFO mode, the TX FIFO operates transparently

behind the TX Buffer. Interface operation is described with reference to the TX Buffer in both FIFO and

non-FIFO modes.

Note

The parallel interface registers and the corresponding bit assignments are shown in Table 4–1.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 18

Page 19

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

Table 4–1. Parallel Interface Registers

Register

No.

7 Scratch Register (SCR) Scratch Register

6 Modem Status Register

5 Line Status Register

4 Modem Control

3 Line Control Register

2 Interrupt Identify

2 FIFO Control Register

1

(DLAB = 0)

0

(DLAB = 0)

0

(DLAB = 0)

1

(DLAB = 1)

0

(DLAB = 1)

Register

Name

(MSR)

(LSR)

Register (MCR)

(LCR)

Register (IIR)

(Read Only)

(FCR)

(Write Only)

Interrupt Enable

Register (ER)

Transmitter Buffer

Register

(THR)

Receiver Buffer

Register (RBR)

Divisor Latch MSB

Register (DLM)

Divisor Latch LSB

Register (DLL)

7 6 5 4 3 2 1 0

Data

Carrier

Detect

(DCD)

RX

FIFO

Error

0 0 0 Local

Divisor

Latch

Access Bit

(DLAB)

FIFOs

Enabled

Receiver

Trigger

MSB

0 0 0 0 Enable

Ring

Indicator

(RI)

Transmitter

Empty

(TEMT)

Set

Break

FIFOs

Enabled

Receiver

Trigger

LSB

Data Set

Ready

(DSR)

Transmitter

Buffer

Register

Empty

(THRE)

Stick

Parity

Reserved Reserved DMA

Transmitter FIFO Buffer Register (Write Only)

Send CTS)

Loopback

0 0 Pending

Receiver FIFO Buffer Register (Read Only)

BIT No.

Clear to

Break

Interrupt

(BI)

Even

Parity

Select

(EPS)

Divisor Latch MSB

Divisor Latch LSB

Delta Data

Carrier

Detect

(DDCD)

Framing

Error

(FE)

Out 2 Out 1 Request

Parity

Enable

(PEN)

Interrupt ID

Bit 2

Mode

Select

Modem

Status

Interrupt

(EDSSI)

Trailing

dge of Ring

Indicator

(TERI)

Parity

Error

(PE)

Number

of Stop

Bits

(STB)

Pending

Interrupt ID

Bit 1

TX FIFO

Reset

Enable

Receiver

Line Status

Interrupt

(ELSI)

Delta Data

Set Ready

Interrupt ID

Transmitter

(DDSR)

Overrun

Error

(OE)

to Send

(RTS)

Word

Length

Select

Bit 1

(WLS1)

Pending

Bit 0

RX FIFO

Reset

Enable

Holding

Register

Empty

Interrupt

(ETBEI)

Delta Clear

to Send

(DCTS)

Receiver

Data

Ready

(DR)

Data

Terminal

Ready

(DTR)

Word Length

Select

Bit 0

(WLSO)

“0” if

Interrupt

Pending

FIFO

Enable

Enable

Received

Data

Available

Interrupt

(ERBFI)

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 19

Page 20

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

Register Signal Definitions

IER – Interrupt Enable Register (Addr = 1, DLAB = 0)

The IER enables five types of interrupts that can separately assert the HINT output signal (Table 4–

2.). A selected interrupt can be enabled by setting the corresponding enable bit to a 1, or disabled by

setting the corresponding enable bit to a 0. Disabling an interrupt in the IER prohibits setting the

corresponding indication in the IIR and assertion of HINT. Disabling all interrupts (resetting IER0 –

IER3 to a 0) inhibits setting of any Interrupt Identifier Register (IIR) bits and inhibits assertion of the

HINT output. All other system functions operate normally, including the setting of the Line Status

Register (LSR) and the Modem Status Register (MSR).

The IER enables five types of interrupts that can separately assert the HINT output signal. A selected

interrupt can be enabled by setting the corresponding enable bit to a 1, or disabled by setting the

corresponding enable bit to a 0. Disabling an interrupt in the IER prohibits setting the corresponding

indication in the IIR and assertion of HINT. Disabling all interrupts (resetting IER0 - IER3 to a 0)

inhibits setting of any Interrupt Identifier Register (IIR) bits and inhibits assertion of the HINT output.

All other system functions operate normally, including the setting of the Line Status Register (LSR)

and the Modem Status Register (MSR).

Bits 7-4 Not used.

Always 0.

Bit 3 Enable Modem Status Interrupt (EDSSI).

This bit, when a 1, enables assertion of the HINT output whenever the Delta CTS

(MSR0), Delta DSR (MSR1), Delta TER (MSR2), or Delta DCD (MSR3) bit in the

Modem Status Register (MSR) is a 1. This bit, when a 0, disables assertion of

HINT due to setting of any of these four MSR bits.

Bit 2 Enable Receiver Line Status Interrupt (ELSI).

This bit, when a 1, enables assertion of the HINT output whenever the Overrun

Error (LSR1), Parity Error (LSR2), Framing Error (LSR3), or Break Interrupt

(LSR4) receiver status bit in the Line Status Register (LSR) changes state. This

bit, when a 0, disables assertion of HINT due to change of the receiver LSR bits

1-4.

Bit 1 Enable Transmitter Holding Register Empty Interrupt (ETBEI).

This bit, when a 1, enables assertion of the HINT output when the Transmitter

Empty bit in the Line Status Register (LSR5) is a 1. This bit, when a 0, disables

assertion of HINT due to LSR5.

Bit 0 Enable Receiver Data Available Interrupt (ERBFI) and Character Timeout in

FIFO Mode.

This bit, when a 1, enables assertion of the HINT output when the Receiver Data

Ready bit in the Line Status Register (LSR0) is a1 or character timeout occurs in

the FIFO mode. This bit, when a 0, disables assertion of HINT due to the LSR0

or character timeout.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 20

Page 21

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

FCR – FIFO Control Register (Addr = 2, Write Only)

The FCR is a write-only register used to enable FIFO mode, clear the RX FIFO and TX FIFO, enable

DMA mode, and set the RX FIFO trigger level.

Bits 7-6 RX FIFO Trigger Level

FCR7 and FCR6 set the trigger level for the RX FIFO (Receiver Data Available) interrupt.

FCR7 FCR6 RX FIFO Trigger Level (Bytes)

0001

0104

1008

1114

Bits 5-4

Bit 3 DMA Mode Select

Not used

When FIFO mode is selected (FCR0 = 1), FCR3 selects non-DMA operation (FCR3 = 0) or DMA

operation (FCR3 = 1). When FIFO mode is not selected (FCR0 = 0), this bit is not used (the

modem operates in non-DMA mode in 16450 operation).

DMA Operation in FIFO Mode

RXRDY will be asserted with the number of characters in the RX FIFO us equal to or greater

than the value in the RX FIFO Trigger Level (IIR0-IIR3 = 4h) or the received character

timeout (IIRO-IIR3 = Ch) has occurred. RXTDY will go inactive when there are no more

characters in the RX FIFO.

TXRDY will be asserted when there are one or more empty (unfilled) locations in the TX

FIFO. TXRDY will go inactive when the TX FIFO is completely full.

Non-DMA Operation in FIFO Mode

RXRDY will be asserted when there are one or more characters in the RX FIFO. RXRDY will

go inactive when there are no more characters in the RX FIFO.

TXRDY will be asserted when there are no characters in the TX FIFO. TXRDY will go

inactive when the character is loaded into the TX FIFO Buffer.

Bit 2 TX FIFO Reset

When FCR2 is a 1, all bytes in the TX FIFO are cleared. This bit is cleared automatically by the

modem.

Bit 1 RX FIFO Reset

When FCR1 is a 1, all bytes in the RX FIFO are cleared. This bit is cleared automatically by the

modem.

Bit 0 FIFO Enable

When FCR0 is a 0, 16450 mode is selected and all bits are cleared in both FIFOs. When FCR0

is a 1, FIFO mode (16550A) is selected and both FIFOs are enabled. FCR0 must be a 1 when

other bits in the FCR are written or they will not be acted upon.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 21

Page 22

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

IIR – Interrupt Identifier Register (Addr = 2)

The Interrupt Identifier Register (IIR) identifies the existence and type of up to five prioritized pending

interrupts. Four priority levels are set to assist interrupt processing in the host. The four levels, in

order of decreasing priority, are Highest: Receiver Line Status, 2: Receiver Data Available or

Receiver Character Timeout. 3: TX Buffer Empty, and 4: Modem Status.

When the IIR is accessed, the modem freezes all interrupts and indicates the highest priority interrupt

pending to the host. Any change occurring in interrupt conditions are not indicated until this access is

complete.

Bits 7-6 FIFO Mode

These two bits copy FCR0.

Bits 5-4 Not Used

Always 0.

Bits 3-1 Highest Priority Pending Interrupt

These three bits identify the highest priority pending interrupt (Table 4-2). Bit 3 is applicable

only when FIFO mode is selected; otherwise, bit 3 is a 0.

Bit 0 Interrupt Pending

When this bit is a 0, an interrupt is pending; IIR bits 1-3 can be used to determine the source

of the interrupt. When this bit is a 1, an interrupt is not pending.

Table 4–2. Interrupt Sources and Reset Control

Interrupt Identification Register Interrupt Set and Reset Functions

Bit 3

(Note 1)

Bit 2 Bit 1 Bit 0 Priority

Level

Interrupt Type Interrupt Source Interrupt Reset

Control

0 0 0 1 — None None —

0 1 1 0 Highest Receiver Line

Status

0 1 0 0 2 Received Data

Available

1 1 0 0 2 Character Timeout

Indication

0 0 1 0 3 TX Buffer Empty TX Buffer Empty Reading the IIR

0 0 0 0 4 Modem Status Delta CTS (DCTS) (MSR0),

1

Overrun Error (OE) (LSR1),

Parity Error (PE) (LSR2),

Framing Error (FE) (LSR3),

or Break Interrupt (BI) (LSR4)

Received Data Available

(LSR0)

or RX FIFO Trigger Level

(FCR6-FCR7)

Reached

The RX FIFO contains at

least 1 character and no

characters have been

removed from or input to the

RX FIFO during the last 4

character times.

Delta DSR (DDST) (MSR1),

Trailing Edge Ring Indicator

(TERI) (MSR3), or Delta

DCD (DCD) (MSR4)

1

Reading the LSR

Reading the RX

Buffer or the RX

FIFO drops

below the

Trigger Level

Reading the RX

Buffer

or writing to the

TX Buffer

Reading the

MSR

Notes:

1. FIFO Mode only.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 22

Page 23

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

LCR – Line Control Register (Addr = 3)

The Line Control Register (LCR) specifies the format of the asynchronous data communications

exchange.

Bit 7 Divisor Latch Access Bit (DLAB)

This bit must be set to a 1 to access the Divisor Latch Registers during a read or write operation.

It must be reset to a 0 to access the Receiver Buffer, the Transmitter Buffer, or the Interrupt

Enable Register.

Bit 6 Set Break

When bit 6 is a 1, the Transmit data is forced to the break condition, i.e., space (0) is sent. When

bit 6 is a 0, break is not sent. The Set Break bit acts only on the Transmit data and has no effect

on the serial in logic.

Bit 5 Stick Parity

When Parity is enabled (LCR3 = 1) and stick parity is selected (LCR5 = 1), the parity bit is

transmitted and checked by the receiver as a 0 if even parity is selected (LCR4 – 1) or a 1 if odd

parity is selected (LCR4 = 0). When the stick parity is not selected (LCR3 = 0), parity is transmit

and checked as determined by the LCR3 and LCR4 bits.

Bit 4 Even Parity Select (EPS)

When parity is enabled (LCR3 = 1) and stick parity is not selected (LCR5 = 0), the number of 1s

transmitted or checked by the receiver in the data word bits and parity bit is either even (LCR4 =

1) or odd (LCR4 = 0).

Bit 3 Enable Parity (PEN)

When bit 3 is a 1, a parity bit is generated in the serial out (transmit) data stream and checked in

the serial in (receive) data stream as determined by the LCR4 and LCR5 bits. The parity bit is

located between the last data bit and the first stop bit.

Bit 2 Number of Stop GBITS (STB)

This bit specifies the number of stop bits in each serial out character. If bit 2 is a 0, one stop bit is

generated regardless of word length. If bit 2 is a 1 and 5-bit word length is selected, one and

one-half stop bits are generated. If bit 2 is a 1 and 6-, 7-, or 8-bit word length is selected, two

stop bits are generated. The serial in logic checks the first stop bit only, regardless of the number

of stop bits selected.

Bit 1-0 Word Length Select (WLS0 and WLS1)

These two bits specify the number of bits in each serial in or serial out character. The encoding

of bits 0 and 1 is:

Bit 1 Bit 0 Word Length

0 0 5 Bits (Not supported)

0 1 6 Bits (Not supported)

10 7 Bits

11 8 Bits

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 23

Page 24

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

MCR – Modem Control Register (Addr = 4)

The Modem Control Register (MCR) controls the interface with modem or data set.

Bit 7-5 Not used

Always 0

Bit 4 Local Loopback

When this bit is set to a 1, the diagnostic mode is selected and the following occurs:

1. Data written to the Transmit Buffer is looped back to the Receiver Buffer.

2. The DTS (MCR0), RTS (MCR1), Out1 (MCR2), and Out2 (MCR3) modem control register

bits are internally connected to the DSR (MSR5), CTS (MSR4), RI (MSR6), and DCD

(MSR7) modem status register bits, respectively.

Bit 3 Output 2

When this bit is a 1, HINT is enabled. When this bit is a 0, HINT is in the high impedance state.

Bit 2 Output 1

This bit is used in local loopback (see MCR4).

Bit 1 Request to Send (RTS)

This bit controls the Request to Send (RTS) function. When this bit is a 1, RTS is on. When this

bit is a 0, RTS is off.

Bit 0 Data Terminal Ready (DTR)

This bit controls the Data Terminal Ready (DTR) function. When this bit is a 1, DTR is on. When

this bit is a 0, DTR is off.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 24

Page 25

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

LSR – Line Status Register (Addr = 5)

This 8-bit register provides status information to the host concerning data transfer.

Bit 7 RX FIFO Error

In the 16450 mode, this bit is not used and is always 0.

In the FIFO mode, this bit is set if there are one or more characters in the RX FIFO with parity

error, framing error, or break indication detected. This bit is reset to a 0 when the host reads the

LSR and note of the above conditions exist in the RX FIFO.

Bit 6 Transmitter Empty (TEMT)

This bit is set to a 1 whenever the TX Buffer (THR) and equivalent of the Transmitter Shift

Register (TRS) are both empty. It is reset to a 0 whenever either the THR or the equivalent of the

TSR contains a character.

In the FIFO mode, this bit is set to a 1 whenever the TX FIFO and the equivalent of the TSR are

both empty

Bit 5 Transmitter Holding Register Empty (THRE) [TX Buffer Empty]

This bit, when set, indicates that the TX Buffer is empty and the modem can accept a new

character for transmission. In addition, this bit causes the modem to issue an interrupt to the host

when the Transmit Holding Register Empty Interrupt Enable bit (IIR1) is set to 1. The THRE bit is

set to a 1 when a character is transferred from the TX Buffer. The bit is reset to 0 when a byte is

written into the TX Buffer by the host.

In the FIFO mode, this bit is set when the TX FIFO is empty; it is cleared when at lease one byte

is in the TX FIFO.

Bit 4 Break Interrupt (BI)

This bit is set to a 1 whenever the received data input is a space (logic 0) for longer than two full

word lengths plus 3 bits. The BI is reset when the host reads the LSR.

Bit 3 Framing Error (FE)

This bit indicates that the received character did not have a valid stop bit. The FE bit is set to a 1

whenever the stop bit following the last data bit or parity bit is detected as a logic o (space). The

FE bit is reset to a 0 when the host reads the LSR.

In the FIFO mode, the error indication is associated with the particular character in the FIFO it

applies to. The FE bit set to a 1 when this character is loaded into the RX Buffer.

Bit 2 Parity Error (PE)

This bit indicates that the received data character in the RX Buffer does not have the correct

even or odd parity, as selected by the Even Parity Select bit (LCR4) and the Stick Parity bit

(LCR5). The PE bit is reset to a 0 when the host reads the LSR.

In the FIFO mode, the error indication is associated with the particular character in the FIFO it

applies to. The PE bit set to a 1 when this character is loaded into the RX Buffer.

Bit 1 Overrun Error (OE)

This bit is set to a 1 whenever received data is loaded into the RX Buffer before the host has

read the previous data from the RX Buffer. The OE is reset to a 0 when the host reads the LSR.

In the FIFO mode, if data continues to fill beyond the trigger level, an overrun condition will occur

only if the RX FIFO is full and the next character has been completely received.

Bit 0 Receiver Data Ready (DR)

This bit is set to a 1 whenever a complete incoming character has been received and transferred

into the RX Buffer. The DR bit is reset to a 0 when the host reads the RX Buffer.

In the FIFO mode, the DR bit is set when the number of received data bytes in the RX FIFO

equals or exceeds the trigger level specified in the FCR0-FCR1.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 25

Page 26

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

MSR – Modem Status Register (Addr = 6)

The Modem Status Register (MSR) reports current state and change information of the modem. Bits

4-7 supply current state, and bits 0-3 supply change information. The change bits are set to a 1

whenever a control input form the modem changes state from the last MSR read by the host. Bits 0-3

are reset to 0 when the host reads the MSR or upon reset.

Whenever bits 0, 1, 2, or 3 are set to a 1, a Modem Status Interrupt (IIR0-IIR3 = 0) is generated.

Bit 7 Data Carrier Detect (DCD)

This bit indicates the logic state of the DCH# (RLSD#) output. If Loopback is selected (MCR4 =

1), this bit reflects the state of the Out2 bit in the MCR (MCR3).

Bit 6 Ring Indicator (RI)

This bit indicates the logic state of the RI# output. If Loopback is selected (MCR4 = 1), this bit

reflects the state of the Out1 bit in the MCR (MCR2).

Bit 5 Data Set Ready (DSR)

This bit indicates the logic state of the DSR# output. If Loopback is selected (MCR4 = 1), this bit

reflects the state of the DTR in the MCR (MCR0).

Bit 4 Clear to Send (CTS)

This bit indicates the logic state of the CTS# output. If Loopback is selected (MCR4 = 1), this bit

reflects the state of the RTS bit in the MCR (MCR1).

Bit 3 Delta Data Carrier Detect (DDCD)

This bit is set to a 1 when the DCD bit changes state since the host last read the MSR.

Bit 2 Trailing Edge of Ring Indicator (TERI)

This bit is set to a 1 when the RI bit changes from a 1 to a 0 state since the host last read the

MSR.

Bit 1 Delta Data Set Ready (DDSR)

This bit is set to a 1 when the DSR bit has changed since the host last read the MSR.

Bit 0 Delta Clear to Send (DCTS)

This bit is set to a 1 when the CTS bit has changed since the MSR the host last read the MSR.

RBX – RX Buffer (Receiver Buffer Register) (Addr = 0,

DLAB = 0)

The RX Buffer (RBR) is a read-only register at location 0 (with DLAB = 0). Bit 0 is the least significant

bit of the data and is the first bit received.

THR – TX Buffer (Transmitter Holding Register) (Addr = 0,

DLAB = 0)

The TX Buffer (THR) is a write-only register at address 0 when DLAB = 0. Bit 0 is the least significant

bit and the first bit sent.

Divisor Registers (Addr = 0 and 1, DLAB = 1)

The Divisor Latch LS (least significant byte) and Divisor Latch MS (most significant byte) are two

read-write registers at locations 0 and 1 when DLAB = 1, respectively.

The baud rate is selected by loading each divisor latch with the appropriate hex value.

Programmable values corresponding to the desired baud rate are listed in Table 4-3.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 26

Page 27

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

SCR – Scratch Register (Addr = 7)

The Scratchpad Register is a read-write register at location 7. This register is not used by the modem

and can be used by the host for temporary storage.

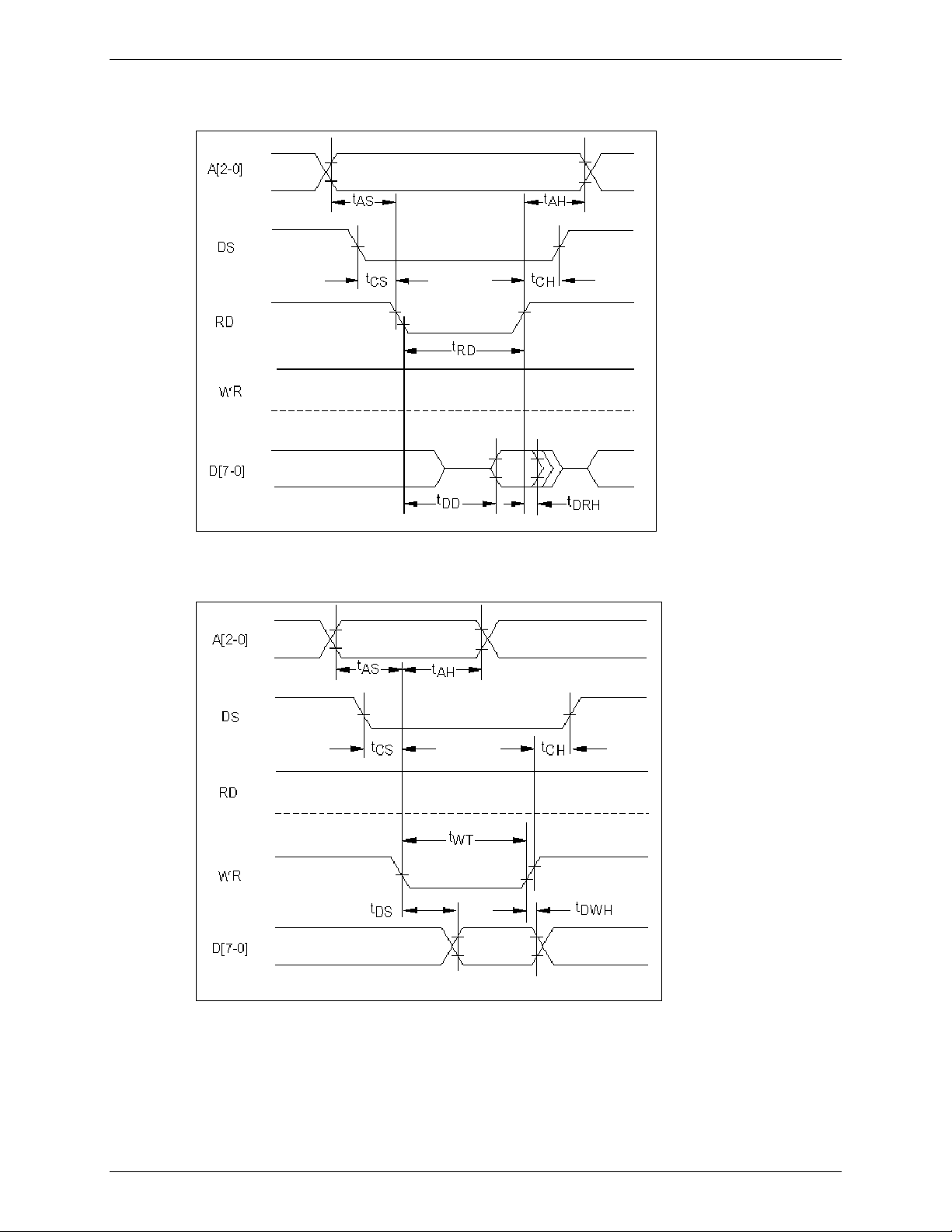

Divisor Latch (Hex)

MS LS Divisor (Decimal) Baud Rate

06 00 1536 75

04 17 1047 110

03 00 768 150

01 80 384 300

00 C0 192 600

00 60 96 1200

00 30 48 2400

00 18 24 4800

00 0C 12 9600

00 06 6 19200

00 04 4 28800

00 03 3 38400

00 02 2 57600

00 01 1 115600

00 00 NA 230400

Table 4–3. Programmable Baud Rates

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 27

Page 28

Chapter 4 – SocketModem Parallel Interface – A Programmer's Description

Receiver FIFO Interrupt Operation

Receiver Data Available Interrupt

When the FIFO mode is enabled (FCR0 = 1) and receiver interrupt (RX Data Available) is enabled

(IER0 = 1), receiver interrupt operation is as follows:

1.

The Receiver Data Available Flag (LSR0) is set as soon as a received data character is

available in the RX FIFO. LSR0 is cleared when RX FIFO is empty.

The Receiver Data Available Interrupt code (IIR0-IIR4 = 4h) is set whenever the number of

2.

received data bytes in the RX FIFO reaches the trigger level specified by FCR6-FCR7 bits. It

is cleared whenever the number of received data bytes in the RX FIFO drops below the

trigger level specified by FCR6-FCR7 bits.

The HINT interrupt is asserted whenever the number of received data bytes in the RX FIFO

3.

reaches the trigger level specified by FCR6-FCR7 bits. HINT interrupt is de-asserted when

the number of received data bytes in the RX FIFO drops below the trigger level specified by

FCR6-FCR7 bits.

Receiver Character Timeout Interrupts

When the FIFO mode is enabled (FCR0 = 1) and receiver interrupt (Receiver Data Available) is

enabled (IER0 = 1), receiver character timeout interrupt operation is as follows:

A Receiver character timeout interrupt code (IIR0-IIR3 = Ch) is set if at least one received

1.

character is in the RX FIFO, the most recent received serial character was longer than four

continuous character times ago (if 2 stop bits are specified, the second stop bit is included in

this time period), and the most recent host read of the RX FIFO was longer than four

continuous character times ago.

Transmitter FIFO Interrupt Operation

Transmitter Empty Interrupt

When the FIFO mode is enabled (FCR0 = 1) and transmitter interrupt (TX Buffer Empty) is enabled

(IER0 =1), transmitter interrupt operation is as follows:

1.

The TX Buffer Empty interrupt code (IIR0-IIR3 = 2h) will occur when the TX Buffer is empty. It

is cleared when the TX Buffer is written to (1 to 16 characters) or the IIR is read.

The TX Buffer Empty indications will be delayed 1 character time minus the last stop bit time

2.

whenever the following occur: THRE = 1 and there have not been at least two bytes at the

same time in the TX FIFO Buffer since the last setting of THRE was set. The first transmitter

interrupt after setting FCR0 will be immediate.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 28

Page 29

Chapter 5 – AT Commands, S-Registers, and Result Codes

Chapter 5 – AT Commands, S-

Registers, and Result Codes

Introduction

The AT commands are used to control the operation of your modem. They are called AT commands

because the characters AT must precede each command to get the ATtention of the modem.

AT commands can be issued only when the modem is in command mode or online command mode. The

modem is in command mode whenever it is not connected to another modem. The modem is in data

mode whenever it is connected to another modem and ready to exchange data. Online command mode is

a temporary state in which you can issue commands to the modem while connected to another modem.

To put the modem into online command mode from data mode, you must issue an escape sequence

(+++) followed immediately by the AT characters and the command, e.g., +++ to hang up the modem. To

return to data mode from online command mode, you must issue the command ATO.

To send AT commands to the modem you must use a communications program, such as the

HyperTerminal applet in Windows 98/95 and NT 4.0, or some other available terminal program. You can

issue commands to the modem either directly, by typing them in the terminal window of the

communications program, or indirectly, by configuring the operating system or communications program

to send the commands automatically. Fortunately, communications programs make daily operation of

modems effortless by hiding the commands from the user. Most users, therefore, need to use AT

commands only when reconfiguring the modem, e.g., to turn autoanswer on or off.

The format for entering an AT command is ATXn, where X is the command, and n is the specific value for

the command, sometimes called the command parameter. The value is always a number. If the value is

zero, you can omit it from the command; thus, AT&W is equivalent to AT&W0. Most commands have a

default value, which is the value that is set at the factory. The default values are shown in the “AT

Command Summary” (See below).

You must press ENTER (depending on the terminal program it could be some other key) to send the

command to the modem. Any time the modem receives a command, it sends a response known as a

result code. The most common result codes are OK, ERROR, and the CONNECT messages that the

modem sends to the computer when it is connecting to another modem. See “Result Codes” at the end of

this chapter for a table of valid result codes.

You can issue several commands in one line, in what is called a command string. The command string

begins with AT and ends when you press ENTER. Spaces to separate the commands are optional; the

command interpreter ignores them. The most familiar command string is the initialization string, which is

used to configure the modem when it is turned on or reset, or when your communications software calls

another modem.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 29

Page 30

Chapter 5 – AT Commands, S-Registers, and Result Codes

Data Commands

The modem will respond to the commands detailed below. Parameters applicable to each command are

listed with the command description.

Generic Modem Control Commands

Command: Z Soft Reset and Restore Profile

Description: Causes the modem to perform a soft reset and restore (recall) the

configuration profile. If no value is specified, zero is assumed.

Default: None

Values: Number corresponding to the selected profile:

Z0 Soft reset and restore stored profile 0.

Z1 Soft reset and restores stored profile 1.

Result Codes: OK

Otherwise ERROR

Command: +FCLASS Select Active Service Class

Description: Selects the active service class (mode).

Default: 0

Defined Values: +FCLASS=0 Select Data Mode (Section 3) (Default).

+FCLASS=1 Select Facsimile Class 1 Mode.

+FCLASS=1.0 Select Facsimile Class 1.0 Mode.

+FCLASS=8 Select Voice Mode.

+FCLASS=10 Reserved.

Result Codes: OK

Otherwise ERROR

Report Commands: +FCLASS? Reports Current or Selected Values

+FCLASS=? Reports Range of Parameters

Command: +VCID Caller ID (CID)

Description: Controls the reporting and presentation of data associated with the Caller

ID services in the Incoming Call Line ID (ICLID) data format for the next

call. (U.S. only)

Default: 0

Defined Values: +VCID0 Disable Caller ID reporting.

+VCID1 Enables Caller ID with formatted presentation to the DTE. The

modem presents the data items in a <Tag><Value> pair

format. The expected pairs are date, time, name, and caller

code (telephone number).

+VCID2 Enables Caller ID with unformatted presentation to the DTE.

Report Commands: +VCID? Reports the Mode

+VCID=? Reports Range of Parameters

Command: +VRID Report Retrieved Caller ID (CID)

Description: Reports the data associated with the Caller ID services in the Incoming

Caller Line (ICLID) data format for the last received call. U.S. only

Default: None

Defined Values: +VRID0 Reports Caller ID with formatted presentation to the DTE. The

modem presents the data items in a <Tag><Value> pair

format. The expected pairs are date, time, name, and caller

code (telephone number).

+VRID1 Reports Caller ID with unformatted presentation to the DTE.

Report Commands: +VRID? Reports the Mode

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 30

Page 31

Chapter 5 – AT Commands, S-Registers, and Result Codes

Command: \N Operating Mode - Error Correction

Description: Controls the preferred error-correcting mode to be negotiated in a

subsequent data connection. This command is affected by the OEM

firmware configuration.

Default: 5

Defined Values: \N0 Selects normal speed buffered mode (disables error-correction

mode). (Forces &Q6.)

\N1 Serial interface selected: Selects direct mode and is equivalent to

&M0, Q0 mode of operation. (Forces &Q0.) Parallel interface

selected: Same as \N0.

\N2 Selects reliable (error-correction) mode. The modem will first attempt

a LAPM connection and then an MNP connection. Failure to make a

reliable connection results in the modem hanging up. (Forces &Q5,

S36=4, and S48=7.)

\N3 Selects auto-reliable mode. This operates the same as \N2 except

failure to make a reliable connection results in the modem falling

back to the speed buffered normal mode. (Forces &Q5, S36=7, and

S48=7.)

\N4 Selects LAPM error-correction mode. Failure to make an LAPM

error-correction connection results in the modem hanging up.

(Forces &Q5 and S48=0.) Note: The -K1 command can override the

\N4 command.

\N5 Selects MNP error-correction mode. Failure to make an MNP error-

correction connection results in the modem hanging up. (Forces

&Q5, S36=4, and S48=128.)

Result Codes: OK

Otherwise ERROR

Command I Identification

Description: Causes the modem to reports the requested result according to the

command parameter.

Default: 4

Defined Values: I0 Reports product code (e.g., 56000).

I1 Reports the least significant byte of the stored checksum (e.g.,

12AB).

I2 Checks ROM and verifies the checksum. Reports OK or ERROR.

I3 Reports ROM Code Revision-Modulation (e.g., 2109-V90).

I4 Reports OEM defined identifier string in binary format (default) or

ASCII formats. (e.g.: a007040284C6002F bC60000000

r1005111151012000 3000111170000000).

I5 Reports Country Code parameter (see +GCI).

I6 Reports modem data pump model and internal code revision.

Result Codes: OK

Otherwise ERROR

Command: +GMI Request Manufacturer Identification

Description: Causes the modem to report the modem product manufacturer.

Typical Response: +GMI: Multi-Tech

OK

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 31

Page 32

Chapter 5 – AT Commands, S-Registers, and Result Codes

Command +GMM Request Model Identification

Description: Causes the modem to report the modem product.

Typical Response: +GMM: V92

Command: +GMR Request Revision Identification

Description: Causes the modem to report the modem version, revision level, or date.

This is the same as the I3 command.

Typical Response: +GMR: P2109-V90

OK

Command: +GCAP Request Complete Capabilities List

Description: This extended-format command causes the modem to transmit one or

more lines of information text listing additional capabilities command

+<name>s, which is intended to permit the user to identify the overall

capabilities of the modem. In particular, if the modem implements a

particular modem control standard that uses Extended Syntax Commands,

and if that modem control standard includes command(s) that indicate

general capabilities, the +<names>(s) of those commands will be reported

to the modem in response to a +GCAP command.

Example Responses: +GCAP: +FCLASS, +MS, +ES, +DS, for a data modem that supports all

capabilities listed. Where:

+MS +M commands (Modulation Control: +MS and +MR commands)

+ES +E commands (Error Control: +ES, +EB, +ER, +EFCS, +ETBM)

+DS +D commands (Data Compression: +DS and +DR). Manual

Command: +GCI Country of Installation

Description: This extended syntax command selects and indicates the country of

installation for the modem. This parameter selects the settings for any

operational parameters that need to be adjusted for national regulations or

telephone networks. The chapter Setting Country Codes for more

information.

Default: If the modem is specified for use in only one country, that country code is

the default. Otherwise, the default is defined by the OEM. Factory default is

B5 (United States).

Report Commands: +GCI? Reports the current country code.

+GCI=? Displays the list of available country codes.

Command: &F Restore Factory Configuration (Profile)

Description: The modem loads the factory default configuration (profile). The factory

defaults are identified for each command and in the S-Parameter

descriptions. A configuration (profile) consists of a subset of S-Parameters.

Default: None

Values: &F0 Restore factory configuration 0.

&F Restore factory configuration 1.

Result Codes: OK

ERROR if the modem is connected.

Multi-Tech Systems, Inc. SocketModem MT5600SMI Developer’s Guide 32

Page 33

Chapter 5 – AT Commands, S-Registers, and Result Codes

Command: &T Local Analog Loopback Test

Description: The modem will perform the local analog loopback test if &T1 is selected.

The test can be run only when in an asynchronous operation in non-errorcorrection mode (normal), e.g., AT&Q6. To terminate the test in progress,

the escape sequence must be entered first.

Default: None

Defined Values: &T0 Terminates test in progress. Clears S16.

&T1 Initiates local analog loopback, V.54 Loop 3. Sets S16 bit 0. If a

connection exists when this command is issued, the modem hangs

up. The CONNECT XXXX message is displayed upon the start of

the test.

Command: &Y Designate a Default Reset Profile