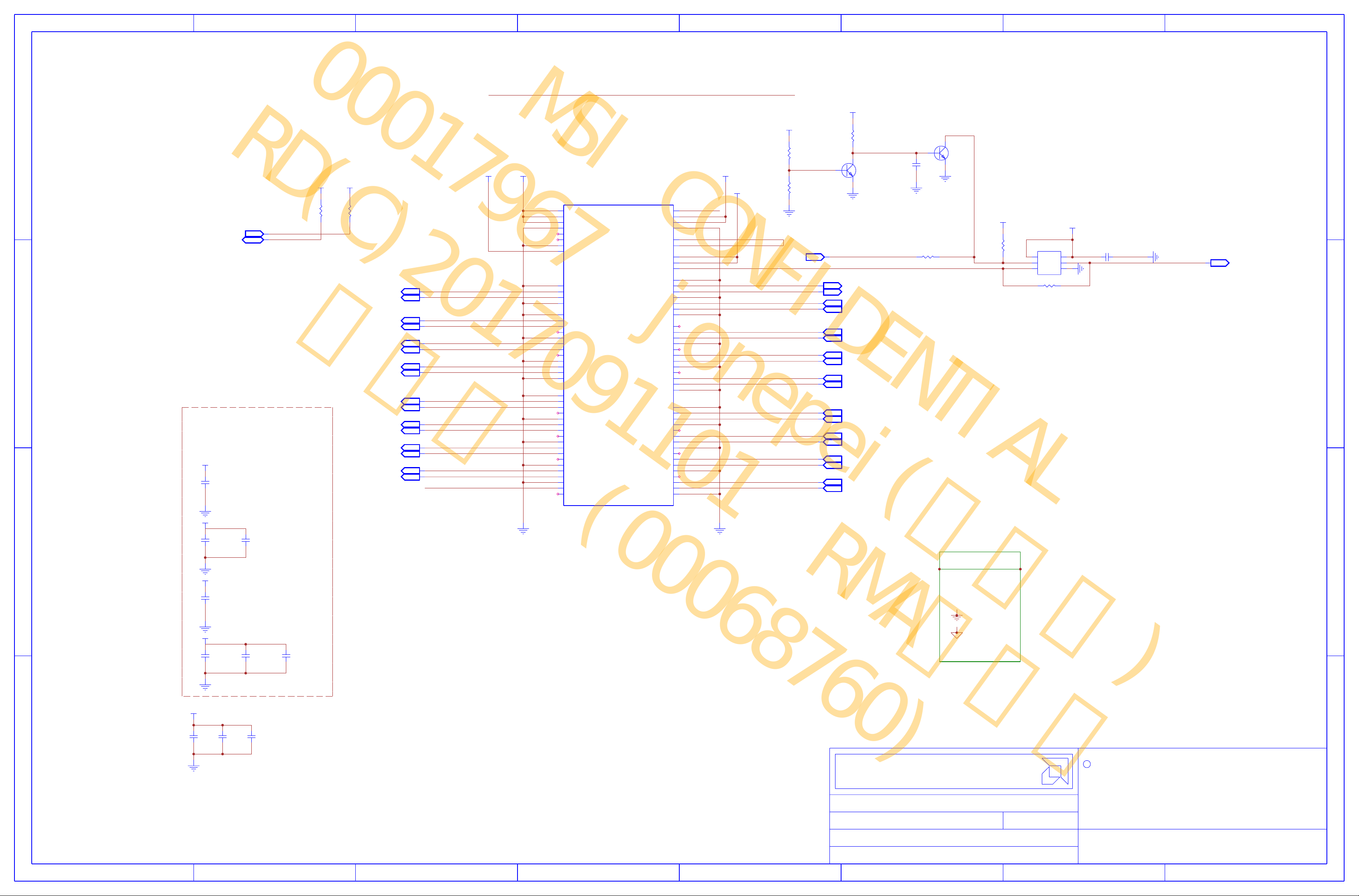

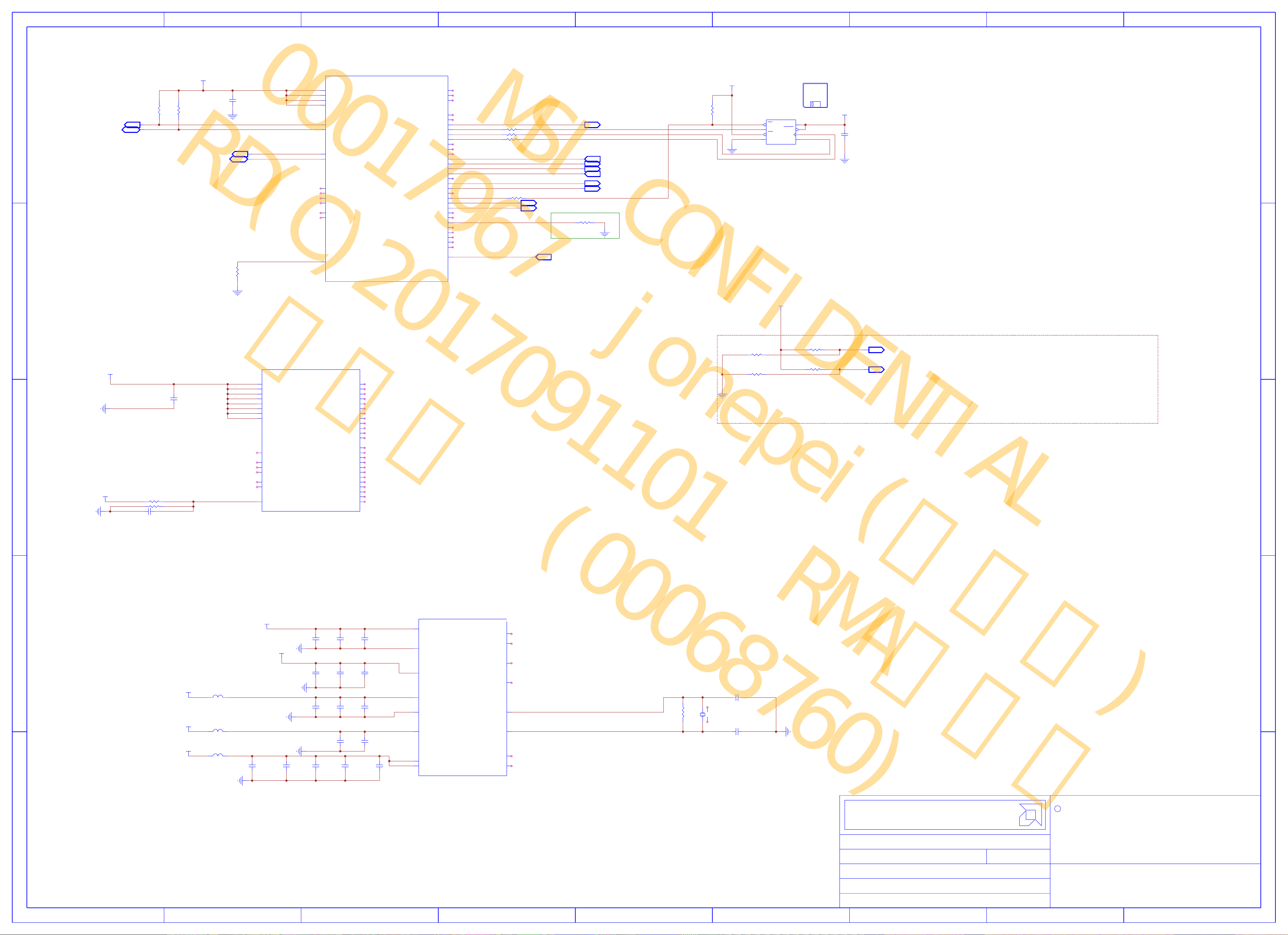

Page 1

This AMD Board schematic and design is the exclusive property of AMD, and

DATE:

SHEET:

Advanced Micro Devices

2

3

345

6

6

7

7

8

8

C

5

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

C

BB

A

1

DD

C

A

4

REV:

SHEET NUMBER:

DOCUMENT NUMBER:

OF

1

prohibited. Use of this schematic and design for any purpose other than

for evaluation purposes. Further distribution or disclosure is strictly

is provided only to entities under a non-disclosure agreement with AMD

2

schematic and design, including, not limited to, any implied warranty

AMD makes no representations or warranties of any kind regarding this

evaluation requires a Board Technology License Agreement with AMD.

of merchantability or fitness for a particular purpose, and disclaims

responsibility for any consequences resulting from use of the

information included herein.

TITLE:

OUT

OUTININININININININININININININININ

Mechanical Key

PERn0

GND

PRSNT2_B48

GND

PETn7

PETp7

GND

GND

PETn6

PETp6

GND

GND

PETn5

PETp5

GND

GND

PETn4

PETp4

GND

GND

PETn3

PETp3

GND

GND

PETn2

PETp2

GND

GND

PETn1

PETp1

GND

GND

PETn0

PETp0

GND

+3.3V

GND

SMDAT

SMCLK

GND

+12V

+12V

+12V

GND

PERn7

PERp7

GND

GND

PERn6

PERp6

GND

GND

PERn5

PERp5

GND

GND

PERn4

PERp4

GND

GND

PERn3

PERp3

GND

GND

PERn2

PERp2

GND

GND

PERn1

PERp1

GND

GND

PERp0

GND

REFCLK-

REFCLK+

GND

PERST_

+3.3V

+3.3V

JTAG4

JTAG3

GND

+12V

+12V

PRSNT1_A1

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTBIININOUT

C

VCC

Y

A

GND

B

8

MSI CONFIDENTIAL

00017967 jonepei(裴亮樂)

RD(C)2017091101 RMA工程課

石阿鋒 (00068760)

7

6

345

2

1

PCI-EXPRESS EDGE CONNECTOR

PCI-EXPRESS EDGE CONNECTOR

+1.8V

+1.8V

PRESENCE

PRESENCE

+12V_BUS

+12V_BUS

+3.3V_BUS

+3.3V_BUS

1

1

JTDIO_LOOP

JTDIO_LOOP

PCIE_REFCLKP

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_REFCLKN

PERP0

PERP0

PERN0

PERN0

PERP1

PERP1

PERN1

PERN1

PERP2

PERP2

PERN2

PERN2

PERP3

PERP3

PERN3

PERN3

PERP4

PERP4

PERN4

PERN4

PERP5

PERP5

PERN5

PERN5

PERP6

PERP6

PERN6

PERN6

PERP7

PERP7

PERN7

PERN7

+12V_BUS+3.3V_BUS

+12V_BUS+3.3V_BUS

+3.3V_BUS

+3.3V_BUS

SMBCLK

IN

BI

SMBCLK

SMBDATA

SMBDATA

5

5

5

5

C

Place these caps as close to the PCIE

Place these caps as close to the PCIE

CAP CER 10UF 20% 16V X5R

CAP CER 10UF 20% 16V X5R

connector as possible

connector as possible

(1206)1.8MM H MAX

(1206)1.8MM H MAX

+12V_BUS

+12V_BUS

1

+12V_BUS

1

+12V_BUS

C1001

C1001

10uF

10uF

16V

16V

2 1

2 1

R1

45.3K

45.3K

1%

1%

2 1

2 1

+3.3V_BUS

+3.3V_BUS

R2

R2R1

45.3K

45.3K

1%

1%

2 1

2 1

MPCIE1

B1

B1

+12V

B2

B2

+12V

B3

B3

+12V

B4

B4

GND

B5

B5

SMCLK

B6

B6

SMDAT

B7

B7

GND

B8

B8

+3.3V

B13

B13

GND

B14

PETP0_GFXRP0

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

2

2

OUT

1

1

PETP0_GFXRP0

PETN0_GFXRN0

PETN0_GFXRN0

PETP1_GFXRP1

PETP1_GFXRP1

PETN1_GFXRN1

PETN1_GFXRN1

PETP2_GFXRP2

PETP2_GFXRP2

PETN2_GFXRN2

PETN2_GFXRN2

PETP3_GFXRP3

PETP3_GFXRP3

PETN3_GFXRN3

PETN3_GFXRN3

PETP4_GFXRP4

PETP4_GFXRP4

PETN4_GFXRN4

PETN4_GFXRN4

PETP5_GFXRP5

PETP5_GFXRP5

PETN5_GFXRN5

PETN5_GFXRN5

PETP6_GFXRP6

PETP6_GFXRP6

PETN6_GFXRN6

PETN6_GFXRN6

PETP7_GFXRP7

PETP7_GFXRP7

PETN7_GFXRN7

PETN7_GFXRN7

PRESENCE

PRESENCE

B14

B15

B15

B16

B16

B18

B18

B19

B19

B20

B20

B21

B21

B22

B22

B23

B23

B24

B24

B25

B25

B26

B26

B27

B27

B28

B28

B29

B29

B32

B32

B33

B33

B34

B34

B35

B35

B36

B36

B37

B37

B38

B38

B39

B39

B40

B40

B41

B41

B42

B42

B43

B43

B44

B44

B45

B45

B46

B46

B47

B47

B48

B48

B49

B49

PETp0

PETn0

GND

GND

PETp1

PETn1

GND

GND

PETp2

PETn2

GND

GND

PETp3

PETn3

GND

GND

PETp4

PETn4

GND

GND

PETp5

PETn5

GND

GND

PETp6

PETn6

GND

GND

PETp7

PETn7

GND

PRSNT2_B48

GND

MPCIE1

Mechanical Key

PRSNT1_A1

+12V

+12V

GND

JTAG3

JTAG4

+3.3V

+3.3V

PERST_

GND

REFCLK+

REFCLK-

GND

PERp0

PERn0

GND

GND

PERp1

PERn1

GND

GND

PERp2

PERn2

GND

GND

PERp3

PERn3

GND

GND

PERp4

PERn4

GND

GND

PERp5

PERn5

GND

GND

PERp6

PERn6

GND

GND

PERp7

PERn7

GND

A1

A1

A2

A2

A3

A3

A4

A4

A6

A6

A7

A7

A9

A9

A10

A10

A11

A11

A12

A12

A13

A13

A14

A14

A15

A15

A16

A16

A17

A17

A18

A18

A20

A20

A21

A21

A22

A22

A23

A23

A24

A24

A25

A25

A26

A26

A27

A27

A28

A28

A29

A29

A30

A30

A31

A31

A34

A34

A35

A35

A36

A36

A37

A37

A38

A38

A39

A39

A40

A40

A41

A41

A42

A42

A43

A43

A44

A44

A45

A45

A46

A46

A47

A47

A48

A48

A49

A49

R3

R3

10K

10K

1%

1%

DNI

DNI

2 1

2 1

1.8V_IN

1.8V_IN

R4

R4

10K

10K

DNI

DNI

2 1

2 1

15 14

15 14

IN

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

2

2

+3.3V_BUS

+3.3V_BUS

2 11 6

2 1

1 6

+1.8V_EN

+1.8V_EN

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

R50

R50

10K

10K

1%

1%

DNI

DNI

Q1

Q1

MMDT3904-7

MMDT3904-7

DNI

DNI

PWR_IN

PWR_IN

R23

C50

C50

0.1uF

0.1uF

10V

10V

2 1

2 1

DNI

DNI

PWR_RST

PWR_RST

5

5

Q1

Q1

MMDT3904-7

MMDT3904-7

DNI

DNI

4 3

4 3

0R

0R

21R23

21

PERST#

PERST#

+3.3V_BUS

+3.3V_BUS

21

21

10K

10K

R1005

R1005

DNI

DNI

U4

U4

3

3

A

1

1

B

C

74AUP1G57GM

74AUP1G57GM

R1007

Place R1007 in U4

Place R1007 in U4

+3.3V_BUS

+3.3V_BUS

VCC

Y

GND

21R1007

21

6.3V

0.1uF

0.1uF

6.3V

PERST#_BUF

PERST#_BUF

OUT

2 16

2 16

5

C1011

5

4

4

26

26

0RDNI

0RDNI

21C1011

21

DD

C

A

+12V_BUS

+12V_BUS

1

+12V_BUS

1

+12V_BUS

C1002

0.15uF

0.15uF

16V

16V

2 1

2 12 1

+3.3V_BUS

+3.3V_BUS

+3.3V_BUS

1

+3.3V_BUS

1

C1004

C1004

10uF

10uF

6.3V

6.3V

2 1

+3.3V_BUS

+3.3V_BUS

1

+3.3V_BUS

1

+3.3V_BUS

C1005

C1005

0.1uF

0.1uF

6.3V

6.3V

2 1

2 1

+12V_BUS

+12V_BUS

+12V_BUS

1

+12V_BUS

1

C1008

C1008

0.1uF

0.1uF

16V

16V

2 1

2 1

2 1

2 1

8

C1003

C1003C1002

0.15uF

0.15uF

16V

16V

2 1

2 1

CAP CER 10UF 10% 6.3V X5R

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

(0805)1.4MM MAX THICK

21

21

C1006

1uF

1uF

6.3V

C1009

0.1uF

0.1uF

16V

16V

6.3V

2 1

2 1

C1010

C1010C1009

0.1uF

0.1uF

16V

16V

2 1

2 1

7

C1007

C1007C1006

0.01uF

0.01uF

10V

10V

6

x8 PCIe

x8 PCIe

SYMBOL LEGEND

SYMBOL LEGEND

DNI

DNI

BUO

BUO

AMD - PLATFORM HARDWARE ENG

AMD - PLATFORM HARDWARE ENG

#48, No.1387, ZHANGDONG ROAD

#48, No.1387, ZHANGDONG ROAD

SHANGHAI, CHINA 201203

SHANGHAI, CHINA 201203

SHEET:

DATE:

SHEET NUMBER:

DOCUMENT NUMBER:

5

4

PCI-E Edge Connector

PCI-E Edge Connector

Fri Oct 28 17:09:42 2016

Fri Oct 28 17:09:42 2016 1.0

1 21

1 21

OF

105_CXXX00_00A

105_CXXX00_00A

3

DO NOT

DO NOT

INSTALL

INSTALL

# ACTIVE

# ACTIVE

LOW

LOW

DIGITAL

DIGITAL

GROUND

GROUND

ANALOG

ANALOG

GROUND

GROUND

BRING UP

BRING UP

ONLY

ONLY

REV:

1.0

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

2016

2016

C

This AMD Board schematic and design is the exclusive property of AMD, and

is provided only to entities under a non-disclosure agreement with AMD

for evaluation purposes. Further distribution or disclosure is strictly

prohibited. Use of this schematic and design for any purpose other than

evaluation requires a Board Technology License Agreement with AMD.

AMD makes no representations or warranties of any kind regarding this

schematic and design, including, not limited to, any implied warranty

of merchantability or fitness for a particular purpose, and disclaims

responsibility for any consequences resulting from use of the

information included herein.

TITLE:

2

Advanced Micro Devices

TITLE

TITLE

1

BB

A

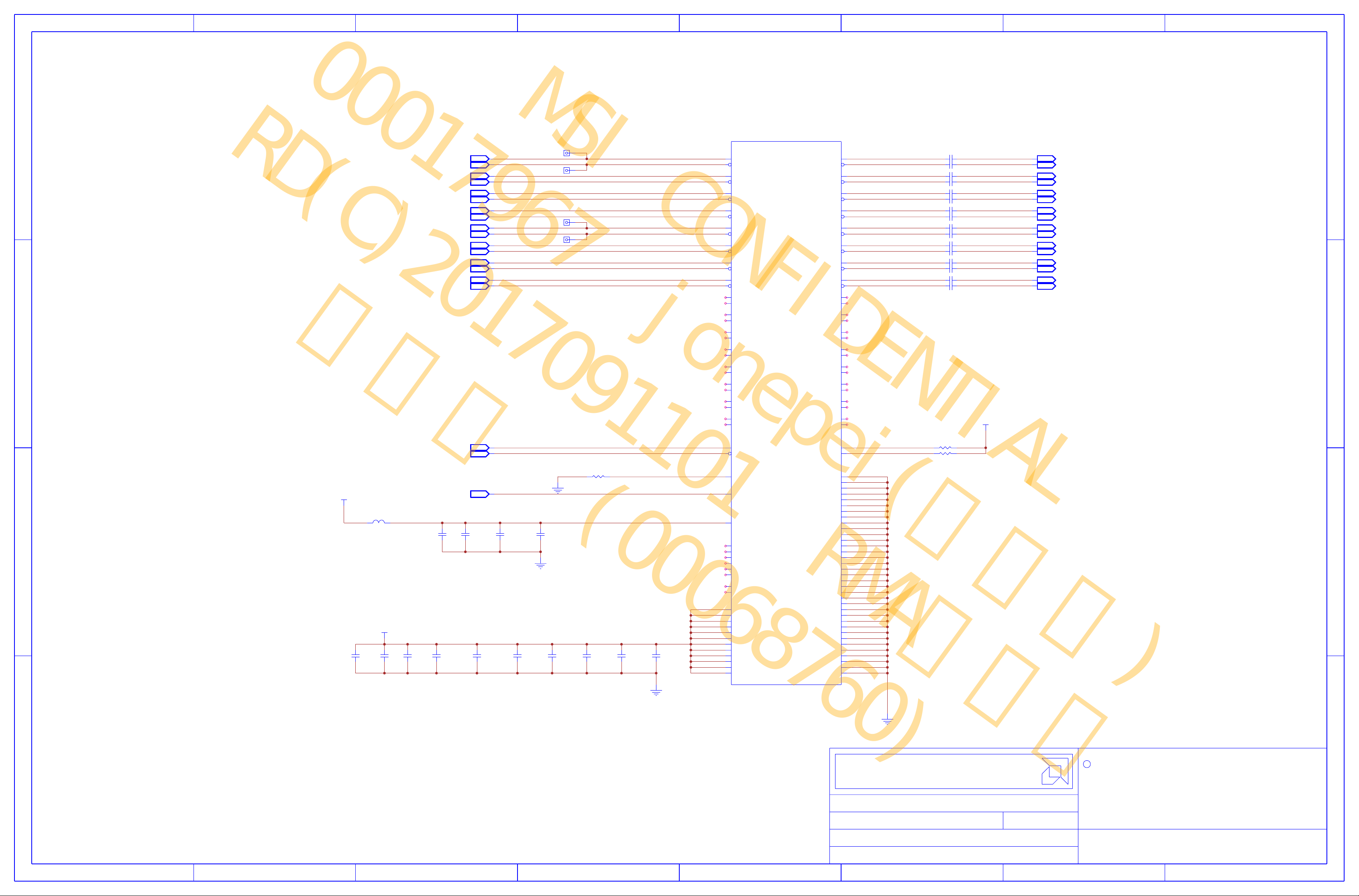

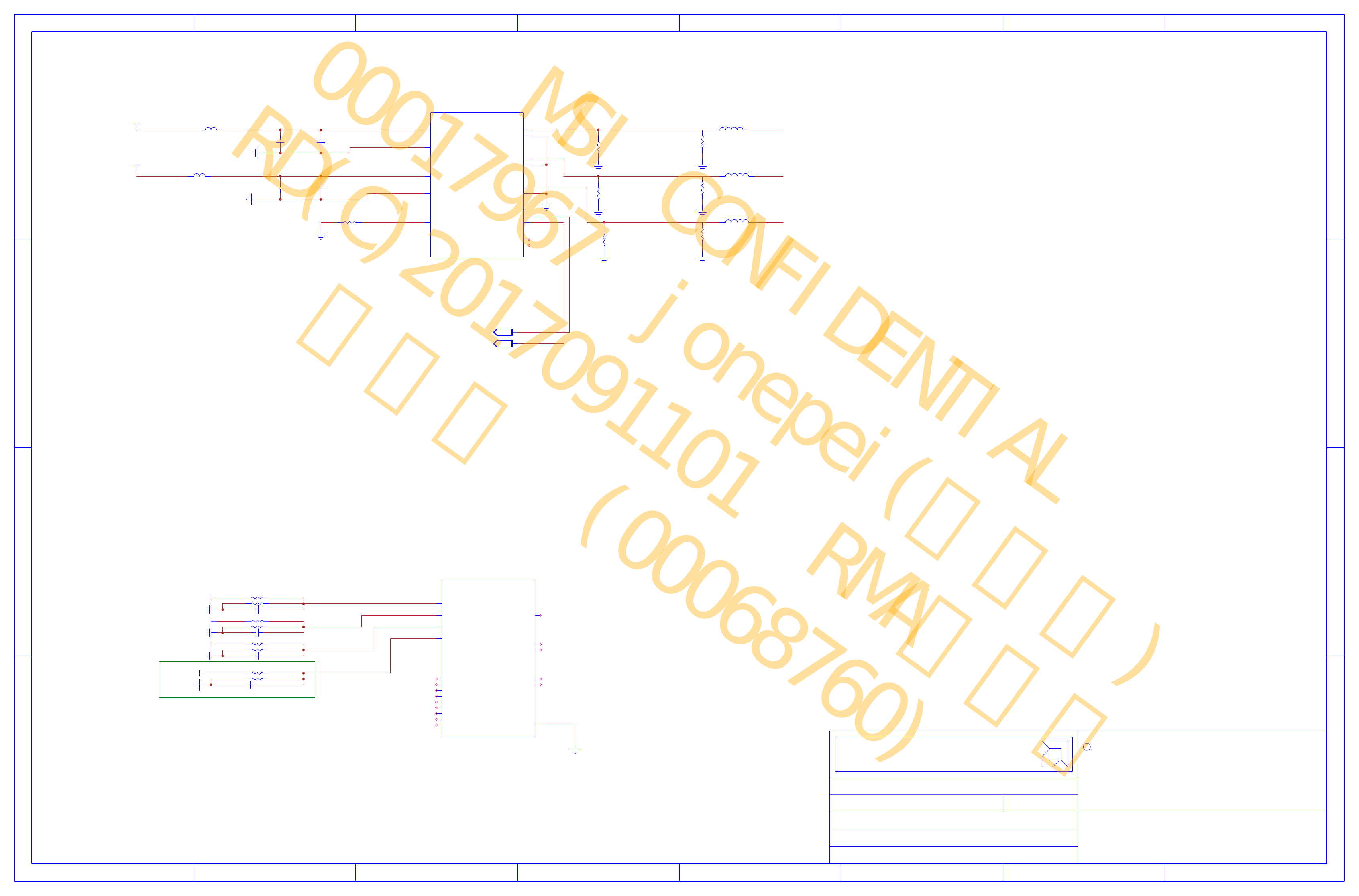

Page 2

This AMD Board schematic and design is the exclusive property of AMD, and

DATE:

SHEET:

Advanced Micro Devices

2

3

345

6

6

7

7

8

8

C

5

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

C

BB

A

1

DD

C

A

4

REV:

SHEET NUMBER:

DOCUMENT NUMBER:

OF

1

prohibited. Use of this schematic and design for any purpose other than

for evaluation purposes. Further distribution or disclosure is strictly

is provided only to entities under a non-disclosure agreement with AMD

2

schematic and design, including, not limited to, any implied warranty

AMD makes no representations or warranties of any kind regarding this

evaluation requires a Board Technology License Agreement with AMD.

of merchantability or fitness for a particular purpose, and disclaims

responsibility for any consequences resulting from use of the

information included herein.

TITLE:

INININININININININININ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSPX_EN

PERSTB

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

PCIE_VDDC

NC#N30

NC#N29

NC#N33

NC#N32

PCIE_TX7P

PCIE_TX7N

PCIE_TX6P

PCIE_TX6N

PCIE_TX5P

PCIE_TX5N

PCIE_TX4P

PCIE_TX4N

PCIE_TX3P

PCIE_TX3N

PCIE_TX2P

PCIE_TX2N

PCIE_TX1P

PCIE_TX1N

NC#H33

NC#H32

NC#K30

NC#K29

NC#J33

NC#J32

NC#K33

NC#K32

NC#L30

NC#L29

NC#L33

NC#L32

PCIE_TX0P

PCIE_TX0N

NC#M35

NC#L36

NC#N38

NC#M37

PCIE_RX7P

PCIE_RX7N

PCIE_RX6P

PCIE_RX6N

PCIE_RX5P

PCIE_RX5N

PCIE_RX4P

PCIE_RX4N

PCIE_RX3P

PCIE_RX3N

PCIE_RX2P

PCIE_RX2N

PCIE_RX1P

PCIE_RX1N

NC#F35

NC#E37

NC#G38

NC#F37

NC#H35

NC#G36

NC#J38

NC#H37

NC#K35

NC#J36

NC#L38

NC#K37

PCIE_RX0P

PCIE_RX0N

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_PVDD

PCIE_CALR_TX

PCIE_CALR_RX

NC_BIF_VDDC

NC_BIF_VDDC

NC#38

NC#37

NC#36

NC#35

NC#34

NC#33

PCIE_VDDC

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTININININININININ

8

MSI CONFIDENTIAL

00017967 jonepei(裴亮樂)

RD(C)2017091101 RMA工程課

石阿鋒 (00068760)

7

6

345

2

1

C

Oland PCIe Interface

Oland PCIe Interface

+1.8V

+1.8V

2 1

2 1

C1161

1uF

1uF

6.3V

6.3V

B11

B11

+0.95V

+0.95V

120R

120R

2 1

2 1

21

21

C1160

10uF

10uF

6.3V

6.3V

PCIE_TX0P

PCIE_TX0P

PCIE_TX0N

PCIE_TX0N

PCIE_TX1P

PCIE_TX1P

PCIE_TX1N

PCIE_TX1N

PCIE_TX2P

PCIE_TX2P

PCIE_TX2N

PCIE_TX2N

PCIE_TX3P

PCIE_TX3P

PCIE_TX3N

PCIE_TX3N

PCIE_TX4P

PCIE_TX4P

PCIE_TX4N

PCIE_TX4N

PCIE_TX5P

PCIE_TX5P

PCIE_TX5N

PCIE_TX5N

PCIE_TX6P

PCIE_TX6P

PCIE_TX6N

PCIE_TX6N

PCIE_TX7P

PCIE_TX7P

PCIE_TX7N

PCIE_TX7N

R1013

R1014

C1101

C1102

C1103

C1104

C1105

C1106

C1107

C1108

C1109

C1110

C1111

C1112

C1113

C1114

C1115

C1116

220nF for GEN3

220nF for GEN3

21C1101

21

0.22uF

0.22uF

21C1102

21

0.22uF

0.22uF

21C1103

21

0.22uF

0.22uF

21C1104

21

0.22uF

0.22uF

21C1105

21

0.22uF

0.22uF

21C1106

21

0.22uF

0.22uF

21C1107

21

0.22uF

0.22uF

21C1108

21

0.22uF

0.22uF

21C1109

21

0.22uF

0.22uF

21C1110

21

0.22uF

0.22uF

21C1111

21

0.22uF

0.22uF

21C1112

21

0.22uF

0.22uF

21C1113

21

0.22uF

0.22uF

21C1114

21

0.22uF

0.22uF

21C1115

21

0.22uF

0.22uF

21C1116

21

0.22uF

0.22uF

+0.95V

+0.95V

21R1013

21

21R1014

21

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V

1%1.69K

1%1.69K

1%1K

1%1K

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

1

1

IN

17 1

17 1

IN

+PCIE_PVDD

+PCIE_PVDD

2 1

2 1

C1159

10uF

10uF

6.3V

6.3V

C1143

C1143U1C1189

10uF

10uF

6.3V

6.3V

2 1

2 1

C1158

C1158C1159C1161 C1160

10uF

10uF

6.3V

6.3V

2 1

2 1

C1189

1uF

1uF

6.3V

6.3V

2 1

2 1

2 1

2 1

C1150

C1150

1uF

1uF

6.3V

6.3V

2 1

2 1

C1173

C1173

1uF

1uF

6.3V

6.3V

2 1

2 1

C1151

C1151

1uF

1uF

6.3V

6.3V

2 1

2 1

NOTE: Some of the PCIE testpoints will

NOTE: Some of the PCIE testpoints will

be available through vias on traces.

be available through vias on traces.

TP110

TP110

TP109

TP109

TP107

TP107

TP108

TP108

C1175

C1175

0.1uF

0.1uF

6.3V

6.3V

2 1

2 1

R1015

C1152

1uF

1uF

6.3V

6.3V

1K

DNI

21R1015

DNI

1K

21

PERST#_BUF

PERST#_BUF

1.8V 200mA

1.8V 200mA

C1153

C1153C1152

1uF

1uF

6.3V

6.3V

2 1

2 1

2 1

2 1

PETP1_GFXRP1

PETP1_GFXRP1

PETN1_GFXRN1

PETN1_GFXRN1

PETP3_GFXRP3

PETP3_GFXRP3

PETN3_GFXRN3

PETN3_GFXRN3

PETP4_GFXRP4

PETP4_GFXRP4

PETN4_GFXRN4

PETN4_GFXRN4

PETP5_GFXRP5

PETP5_GFXRP5

PETN5_GFXRN5

PETN5_GFXRN5

PETP7_GFXRP7

PETP7_GFXRP7

PETN7_GFXRN7

PETN7_GFXRN7

PCIE_REFCLKN PCIE_CALRN

PCIE_REFCLKN PCIE_CALRN

C1154

C1154

1uF

1uF

6.3V

6.3V

PETP0_GFXRP0

PETP0_GFXRP0

PETN0_GFXRN0

PETN0_GFXRN0

PETP2_GFXRP2

PETP2_GFXRP2

PETN2_GFXRN2

PETN2_GFXRN2

PETP6_GFXRP6

PETP6_GFXRP6

PETN6_GFXRN6

PETN6_GFXRN6

PX_EN

PX_EN

C1155

C1155

1uF

1uF

6.3V

6.3V

2 1

2 1

U1

AA38

AA38

PCIE_RX0P

Y37

Y37

PCIE_RX0N

Y35

Y35

PCIE_RX1P

W36

W36

PCIE_RX1N

W38

W38

PCIE_RX2P

V37

V37

PCIE_RX2N

V35

V35

PCIE_RX3P

U36

U36

PCIE_RX3N

U38

U38

PCIE_RX4P

T37

T37

PCIE_RX4N

T35

T35

PCIE_RX5P

R36

R36

PCIE_RX5N

R38

R38

PCIE_RX6P

P37

P37

PCIE_RX6N

P35

P35

PCIE_RX7P

N36

N36

PCIE_RX7N

N38 N33

N38 N33

NC#N38

M37

M37

NC#M37

M35

M35

NC#M35

L36

L36

NC#L36

L38

L38

NC#L38

K37

K37

NC#K37

K35

K35

NC#K35

J36

J36

NC#J36

J38

J38

NC#J38

H37

H37

NC#H37

H35

H35

NC#H35

G36

G36

NC#G36

G38

G38

NC#G38

F37

F37

NC#F37

F35

F35

NC#F35

E37

E37

NC#E37

AB35

AB35

PCIE_REFCLKP

AA36

AA36

PCIE_REFCLKN

AA30

AA30

PERSTB

AB37

AB37

PCIE_PVDD

AA31

AA31

NC#33

AA32

AA32

NC#34

AA33

AA33

NC#35

AA34

AA34

NC#36

W30

W30

NC#37

Y31

Y31

NC#38

V28

V28

NC_BIF_VDDC

W29

W29

NC_BIF_VDDC

G30

G30

PCIE_VDDC

G31

G31

PCIE_VDDC

H29

H29

PCIE_VDDC

H30

H30

PCIE_VDDC

J29

J29

PCIE_VDDC

J30

J30

PCIE_VDDC

L28

L28

PCIE_VDDC

M28

M28

PCIE_VDDC

N28

N28

PCIE_VDDC

R28

R28

PCIE_VDDC

T28

T28

PCIE_VDDC

U28

U28

PCIE_VDDC

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

NC#N33

NC#N32

NC#N30

NC#N29

NC#L33

NC#L32

NC#L30

NC#L29

NC#K33

NC#K32

NC#J33

NC#J32

NC#K30

NC#K29

NC#H33

NC#H32

PCIE_CALR_TX

PCIE_CALR_RX

VSSPX_EN

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y33

Y33

Y32

Y32

W33

W33

W32

W32

U33

U33

U32

U32

U30

U30

U29

U29

T33

T33

T32

T32

T30

T30

T29

T29

P33

P33

P32

P32

P30

P30

P29

P29

N32

N32

N30

N30

N29

N29

L33

L33

L32

L32

L30

L30

L29

L29

K33

K33

K32

K32

J33

J33

J32

J32

K30

K30

K29

K29

H33

H33

H32

H32

Y30

Y30

Y29

Y29

AB39AL21

AB39AL21

E39

E39

F34

F34

F39

F39

G33

G33

G34

G34

H31

H31

H34

H34

H39

H39

J31

J31

J34

J34

K31

K31

K34

K34

K39

K39

L31

L31

L34

L34

M34

M34

M39

M39

N31

N31

N34

N34

P31

P31

P34

P34

P39

P39

R34

R34

T31

T31

T34

T34

T39

T39

U31

U31

U34

U34

V34

V34

Y39

Y39

V39

V39

W31

W31

W34

W34

Y34

Y34

PCIE_CALRPPCIE_REFCLKP

PCIE_CALRPPCIE_REFCLKP

PERP0

PERP0

PERN0

PERN0

PERP1

PERP1

PERN1

PERN1

PERP2

PERP2

PERN2

PERN2

PERP3

PERP3

PERN3

PERN3

PERP4

PERP4

PERN4

PERN4

PERP5

PERP5

PERN5

PERN5

PERP6

PERP6

PERN6

PERN6

PERP7

PERP7

PERN7

PERN7

PCIE_CALR_TX 1.69k pull up for Oland

PCIE_CALR_TX 1.69k pull up for Oland

PCIE_CALR_RX 1k pull up for Oland

PCIE_CALR_RX 1k pull up for Oland

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

DD

C

BB

A

8

7

6

5

4

OLAND M2 GDDR5

OLAND M2 GDDR5

AMD - PLATFORM HARDWARE ENG

AMD - PLATFORM HARDWARE ENG

#48, No.1387, ZHANGDONG ROAD

#48, No.1387, ZHANGDONG ROAD

SHANGHAI, CHINA 201203

SHANGHAI, CHINA 201203

SHEET:

DATE:

SHEET NUMBER:

DOCUMENT NUMBER:

Oland PCIE Interface

Oland PCIE Interface

Fri Oct 28 17:09:40 2016

Fri Oct 28 17:09:40 2016 1.0

2 21

2 21

OF

105_CXXX00_00A

105_CXXX00_00A

3

REV:

1.0

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

2016

2016

C

This AMD Board schematic and design is the exclusive property of AMD, and

is provided only to entities under a non-disclosure agreement with AMD

for evaluation purposes. Further distribution or disclosure is strictly

prohibited. Use of this schematic and design for any purpose other than

evaluation requires a Board Technology License Agreement with AMD.

AMD makes no representations or warranties of any kind regarding this

schematic and design, including, not limited to, any implied warranty

of merchantability or fitness for a particular purpose, and disclaims

responsibility for any consequences resulting from use of the

information included herein.

TITLE:

2

Advanced Micro Devices

TITLE

TITLE

1

A

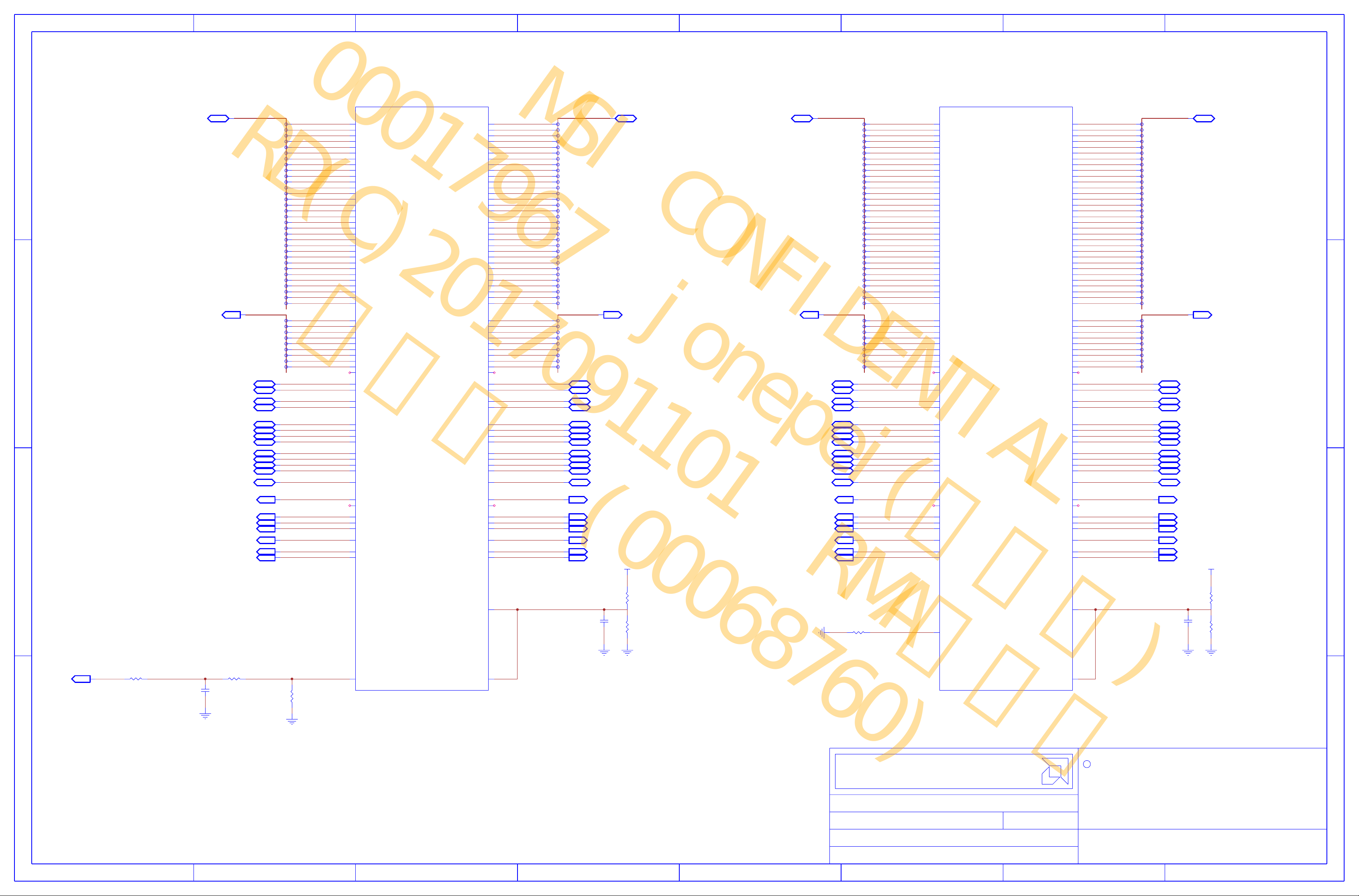

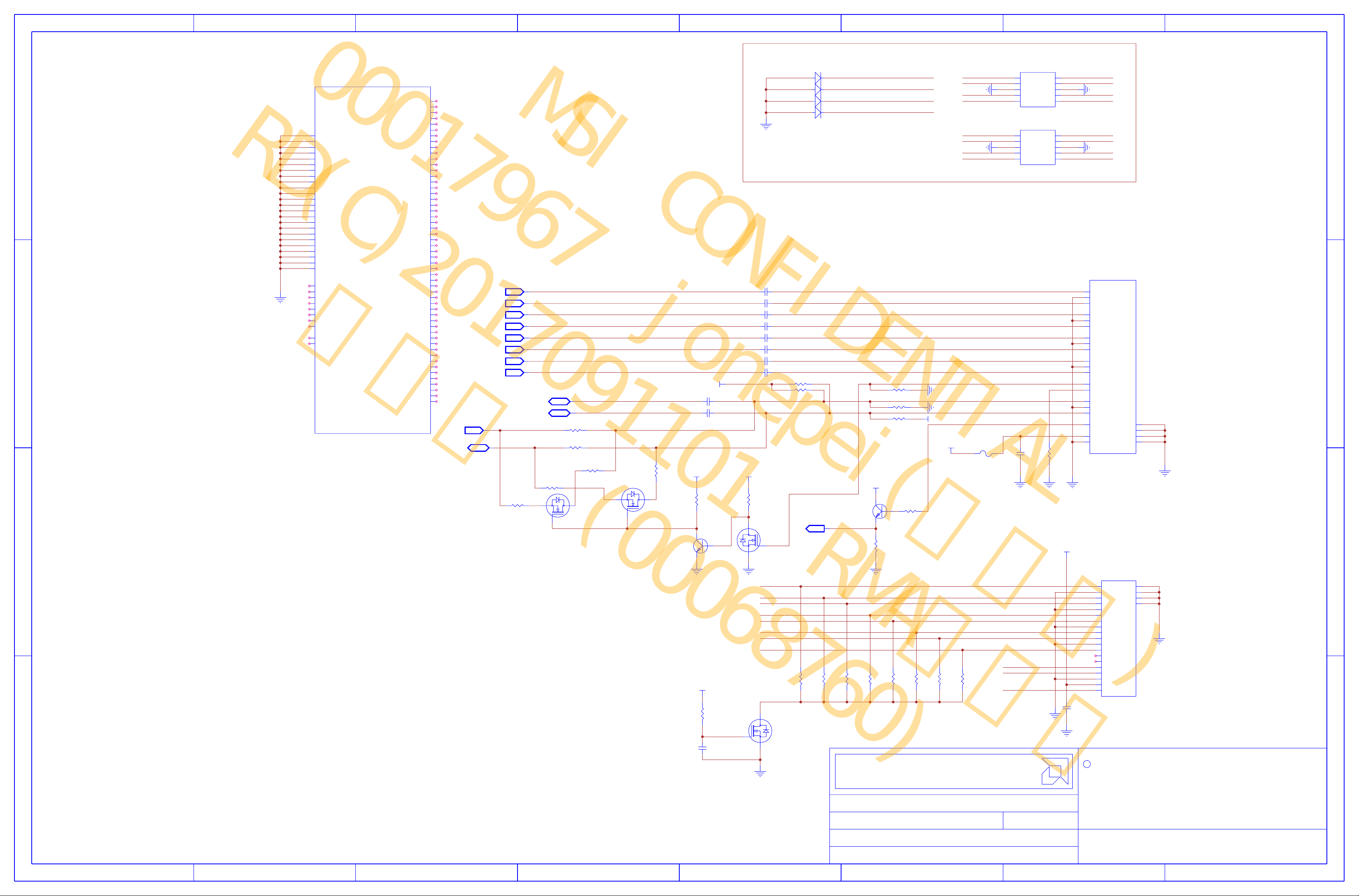

Page 3

This AMD Board schematic and design is the exclusive property of AMD, and

DATE:

SHEET:

Advanced Micro Devices

2

3

345

6

6

7

7

8

8

C

5

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

C

BB

A

1

DD

C

A

4

REV:

SHEET NUMBER:

DOCUMENT NUMBER:

OF

1

prohibited. Use of this schematic and design for any purpose other than

for evaluation purposes. Further distribution or disclosure is strictly

is provided only to entities under a non-disclosure agreement with AMD

2

schematic and design, including, not limited to, any implied warranty

AMD makes no representations or warranties of any kind regarding this

evaluation requires a Board Technology License Agreement with AMD.

of merchantability or fitness for a particular purpose, and disclaims

responsibility for any consequences resulting from use of the

information included herein.

TITLE:

WEB1BWEB0B

WCKB1B_1

WCKB1B_0

WCKB1_1

WCKB1_0

WCKB0B_1

WCKB0B_0

WCKB0_1

WCKB0_0

RASB1BRASB0B

MVREFSB

MVREFDB

MEM_CALRP0

MAB1_9

MAB1_8

MAB1_7

MAB1_6

MAB1_5

MAB1_4

MAB1_3

MAB1_2

MAB1_1

MAB1_0

MAB0_9

MAB0_8

MAB0_7

MAB0_6

MAB0_5

MAB0_4

MAB0_3

MAB0_2

MAB0_1

MAB0_0

EDCB1_3

EDCB1_2

EDCB1_1

EDCB1_0

EDCB0_3

EDCB0_2

EDCB0_1

EDCB0_0

DQB1_9

DQB1_8

DQB1_7

DQB1_6

DQB1_5

DQB1_4

DQB1_31

DQB1_30

DQB1_3

DQB1_29

DQB1_28

DQB1_27

DQB1_26

DQB1_25

DQB1_24

DQB1_23

DQB1_22

DQB1_21

DQB1_20

DQB1_2

DQB1_19

DQB1_18

DQB1_17

DQB1_16

DQB1_15

DQB1_14

DQB1_13

DQB1_12

DQB1_11

DQB1_10

DQB1_1

DQB1_0

DQB0_9

DQB0_8

DQB0_7

DQB0_6

DQB0_5

DQB0_4

DQB0_31

DQB0_30

DQB0_3

DQB0_29

DQB0_28

DQB0_27

DQB0_26

DQB0_25

DQB0_24

DQB0_23

DQB0_22

DQB0_21

DQB0_20

DQB0_2

DQB0_19

DQB0_18

DQB0_17

DQB0_16

DQB0_15

DQB0_14

DQB0_13

DQB0_12

DQB0_11

DQB0_10

DQB0_1

DQB0_0

DDBIB1_3

DDBIB1_2

DDBIB1_1

DDBIB1_0

DDBIB0_3

DDBIB0_2

DDBIB0_1

DDBIB0_0

CSB1B_1

CSB1B_0

CSB0B_1

CSB0B_0

CLKB1B

CLKB1

CLKB0B

CLKB0

CKEB1CKEB0

CASB1BCASB0B

ADBIB1ADBIB0

WEA1BWEA0B

WCKA1B_1

WCKA1B_0

WCKA1_1

WCKA1_0

WCKA0B_1

WCKA0B_0

WCKA0_1

WCKA0_0

RASA1BRASA0B

MVREFSA

MVREFDA

MAA1_9

MAA1_8

MAA1_7

MAA1_6

MAA1_5

MAA1_4

MAA1_3

MAA1_2

MAA1_1

MAA1_0

MAA0_9

MAA0_8

MAA0_7

MAA0_6

MAA0_5

MAA0_4

MAA0_3

MAA0_2

MAA0_1

MAA0_0

EDCA1_3

EDCA1_2

EDCA1_1

EDCA1_0

EDCA0_3

EDCA0_2

EDCA0_1

EDCA0_0

DRAM_RST

DQA1_9

DQA1_8

DQA1_7

DQA1_6

DQA1_5

DQA1_4

DQA1_31

DQA1_30

DQA1_3

DQA1_29

DQA1_28

DQA1_27

DQA1_26

DQA1_25

DQA1_24

DQA1_23

DQA1_22

DQA1_21

DQA1_20

DQA1_2

DQA1_19

DQA1_18

DQA1_17

DQA1_16

DQA1_15

DQA1_14

DQA1_13

DQA1_12

DQA1_11

DQA1_10

DQA1_1

DQA1_0

DQA0_9

DQA0_8

DQA0_7

DQA0_6

DQA0_5

DQA0_4

DQA0_31

DQA0_30

DQA0_3

DQA0_29

DQA0_28

DQA0_27

DQA0_26

DQA0_25

DQA0_24

DQA0_23

DQA0_22

DQA0_21

DQA0_20

DQA0_2

DQA0_19

DQA0_18

DQA0_17

DQA0_16

DQA0_15

DQA0_14

DQA0_13

DQA0_12

DQA0_11

DQA0_10

DQA0_1

DQA0_0

DDBIA1_3

DDBIA1_2

DDBIA1_1

DDBIA1_0

DDBIA0_3

DDBIA0_2

DDBIA0_1

DDBIA0_0

CSA1B_1

CSA1B_0

CSA0B_1

CSA0B_0

CLKA1B

CLKA1

CLKA0B

CLKA0

CKEA1CKEA0

CASA1BCASA0B

ADBIA1ADBIA0

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTBIBIBIBIBIBIBIBIBIBIBIBIBIOUT

OUT

OUT

OUT

OUT

OUT

OUTBIBIBIBIBIBIBIBIBIBIBIBI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUTBIBIBIBIBIBIBIBIBIBIBIBIBIOUT

OUT

OUT

OUT

OUT

OUT

OUTBIBIBIBIBIBIBIBIBIBIBIBIBIOUT

OUT

OUT

OUTBIBIBIBI

8

MSI CONFIDENTIAL

00017967 jonepei(裴亮樂)

RD(C)2017091101 RMA工程課

石阿鋒 (00068760)

7

6

345

2

1

C

A

(3) Oland MEM Interface Ch A&B

(3) Oland MEM Interface Ch A&B

U1

DQA0_<31..0>

3 4 3 4 3 4 3 4

3 4 3 4 3 4 3 4

3 4

3 4

DRAM_RST DRAM_RST_RR

4

4

DRAM_RST DRAM_RST_RR

OUT

R3630

R3630

49.9R

49.9R

1%

1%

21

21

C3607

C3607

120pF

120pF

50V

50V

2 1

2 1

DQA0_<31..0>

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

21

21

R3615

R3615

10R

10R

1%

1%

0

0

4 3

4 3

1

1

4 3

4 3

2

2

4 3

4 3

3

3

4 3

4 3

4

4

4 3

4 3

5

5

4 3

4 3

6

6

4 3

4 3

7

7

4 3

4 3

8

8

4 3

4 3

9

9

4 3

4 3

10

10

4 3

4 3

11

11

4 3

4 3

12

12

4 3

4 3

13

13

4 3

4 3

14

14

4 3

4 3

15

15

4 3

4 3

16

16

4 3

4 3

17

17

4 3

4 3

18

18

4 3

4 3

19

19

4 3

4 3

20

20

4 3

4 3

21

21

4 3

4 3

22

22

4 3

4 3

23

23

4 3

4 3

24

24

4 3

4 3

25

25

4 3

4 3

26

26

4 3

4 3

27

27

4 3

4 3

28

28

4 3

4 3

29

29

4 3

4 3

30

30

4 3

4 3

31

31

0

0

4 3

4 3

1

1

4 3

4 3

2

2

4 3

4 3

3

3

4 3

4 3

4

4

4 3

4 3

5

5

4 3

4 3

6

6

4 3

4 3

7

7

4 3

4 3

8

8

DRAM_RST_R

DRAM_RST_R

21

21

4

4

DQA0_<0>

DQA0_<0>

3

3

DQA0_<1>

DQA0_<1>

DQA0_<2>

DQA0_<2>

DQA0_<3>

DQA0_<3>

DQA0_<4>

DQA0_<4>

DQA0_<5>

DQA0_<5>

DQA0_<6>

DQA0_<6>

DQA0_<7>

DQA0_<7>

DQA0_<8>

DQA0_<8>

DQA0_<9>

DQA0_<9>

DQA0_<10>

DQA0_<10>

DQA0_<11>

DQA0_<11>

DQA0_<12>

DQA0_<12>

DQA0_<13>

DQA0_<13>

DQA0_<14>

DQA0_<14>

DQA0_<15>

DQA0_<15>

DQA0_<16>

DQA0_<16>

DQA0_<17>

DQA0_<17>

DQA0_<18>

DQA0_<18>

DQA0_<19>

DQA0_<19>

DQA0_<20>

DQA0_<20>

DQA0_<21>

DQA0_<21>

DQA0_<22>

DQA0_<22>

DQA0_<23>

DQA0_<23>

DQA0_<24>

DQA0_<24>

DQA0_<25>

DQA0_<25>

DQA0_<26>

DQA0_<26>

DQA0_<27>

DQA0_<27>

DQA0_<28>

DQA0_<28>

DQA0_<29>

DQA0_<29>

DQA0_<30>

DQA0_<30>

DQA0_<31>

DQA0_<31>

4

4

3

3

MAA0_<0>

MAA0_<0>

MAA0_<1>

MAA0_<1>

MAA0_<2>

MAA0_<2>

MAA0_<3>

MAA0_<3>

MAA0_<4>

MAA0_<4>

MAA0_<5>

MAA0_<5>

MAA0_<6>

MAA0_<6>

MAA0_<7>

MAA0_<7>

MAA0_<8>

MAA0_<8>

WCKA0_0

WCKA0_0

WCKA0B_0

WCKA0B_0

WCKA0_1

WCKA0_1

WCKA0B_1

WCKA0B_1

EDCA0_0

EDCA0_0

EDCA0_1

EDCA0_1

EDCA0_2

EDCA0_2

EDCA0_3

EDCA0_3

DDBIA0_1

DDBIA0_1

DDBIA0_2

DDBIA0_2

DDBIA0_3

DDBIA0_3

ADBIA0 ADBIA1

ADBIA0 ADBIA1

CSA0B_0

CSA0B_0

CASA0B

CASA0B

RASA0B

RASA0B

WEA0B

WEA0B

CKEA0 CKEA1

CKEA0 CKEA1

CLKA0 CLKA1

CLKA0 CLKA1

CLKA0B

CLKA0B

R3612

R3612

5.1K

5.1K

1%

1%

C37

C37

C35

C35

A35

A35

E34

E34

G32

G32

D33

D33

F32

F32

E32

E32

D31

D31

F30

F30

C30

C30

A30

A30

F28

F28

C28

C28

A28

A28

E28

E28

D27

D27

F26

F26

C26

C26

A26

A26

F24

F24

C24

C24

A24

A24

E24

E24

C22

C22

A22

A22

F22

F22

D21

D21

A20

A20

F20

F20

D19

D19

E18

E18

G24

G24

J23

J23

H24

H24

J24

J24

H26

H26

J26

J26

H21

H21

G21

G21

H23

H23

M21

M21

A32

A32

C32

C32

D23

D23

E22

E22

C34

C34

D29

D29

D25

D25

E20

E20

A34

A34

E30

E30

E26

E26

C20

C20

K24

K24

K27

K27

H27

H27

G27

G27

AH11

AH11

DQA0_0

DQA0_1

DQA0_2

DQA0_3

DQA0_4

DQA0_5

DQA0_6

DQA0_7

DQA0_8

DQA0_9

DQA0_10

DQA0_11

DQA0_12

DQA0_13

DQA0_14

DQA0_15

DQA0_16

DQA0_17

DQA0_18

DQA0_19

DQA0_20

DQA0_21

DQA0_22

DQA0_23

DQA0_24

DQA0_25

DQA0_26

DQA0_27

DQA0_28

DQA0_29

DQA0_30

DQA0_31

MAA0_0

MAA0_1

MAA0_2

MAA0_3

MAA0_4

MAA0_5

MAA0_6

MAA0_7

MAA0_8

MAA0_9

WCKA0_0

WCKA0B_0

WCKA0_1

WCKA0B_1

EDCA0_0

EDCA0_1

EDCA0_2

EDCA0_3

DDBIA0_0

DDBIA0_1

DDBIA0_2

DDBIA0_3

CSA0B_0

CSA0B_1

CLKA0

CLKA0B

DRAM_RST

OLAND M2 GDDR5

OLAND M2 GDDR5

DQA1_0

DQA1_1

DQA1_2

DQA1_3

DQA1_4

DQA1_5

DQA1_6

DQA1_7

DQA1_8

DQA1_9

DQA1_10

DQA1_11

DQA1_12

DQA1_13

DQA1_14

DQA1_15

DQA1_16

DQA1_17

DQA1_18

DQA1_19

DQA1_20

DQA1_21

DQA1_22

DQA1_23

DQA1_24

DQA1_25

DQA1_26

DQA1_27

DQA1_28

DQA1_29

DQA1_30

DQA1_31

MAA1_0

MAA1_1

MAA1_2

MAA1_3

MAA1_4

MAA1_5

MAA1_6

MAA1_7

MAA1_8

MAA1_9

WCKA1_0

WCKA1B_0

WCKA1_1

WCKA1B_1

EDCA1_0

EDCA1_1

EDCA1_2

EDCA1_3

DDBIA1_0

DDBIA1_1

DDBIA1_2

DDBIA1_3

ADBIA1ADBIA0

CSA1B_0

CSA1B_1

CASA1BCASA0B

RASA1BRASA0B

WEA1BWEA0B

CKEA1CKEA0

CLKA1

CLKA1B

MVREFDA

MVREFSA

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

C18

C18

A18

A18

F18

F18

D17

D17

A16

A16

F16

F16

D15

D15

E14

E14

F14

F14

D13

D13

F12

F12

A12

A12

D11

D11

F10

F10

A10

A10

C10

C10

G13

G13

H13

H13

J13

J13

H11

H11

G10

G10

G8

G8

K9

K9

K10

K10

G9

G9

A8

A8

C8

C8

E8

E8

A6

A6

C6

C6

E6

E6

A5

A5

H19

H19

H20

H20

L13

L13

G16

G16

J16

J16

H16

H16

J17

J17

H17

H17

J19

J19

M20

M20

C14

C14

A14

A14

E10

E10

D9

D9

E16

E16

E12

E12

J10

J10

D7

D7

C16

C16

C12

C12

J11

J11

F8

F8

G19J21

G19J21

M13

M13

K16

K16

K17K20

K17K20

K19K23

K19K23

L15K26

L15K26

J20K21

J20K21

J14

J14

H14

H14

L18

L18

L20

L20

DQA1_<0>

DQA1_<0>

DQA1_<1>

DQA1_<1>

DQA1_<2>

DQA1_<2>

DQA1_<3>

DQA1_<3>

DQA1_<4>

DQA1_<4>

DQA1_<5>

DQA1_<5>

DQA1_<6>

DQA1_<6>

DQA1_<7>

DQA1_<7>

DQA1_<8>

DQA1_<8>

DQA1_<9>

DQA1_<9>

DQA1_<10>

DQA1_<10>

DQA1_<11>

DQA1_<11>

DQA1_<12>

DQA1_<12>

DQA1_<13>

DQA1_<13>

DQA1_<14>

DQA1_<14>

DQA1_<15>

DQA1_<15>

DQA1_<16>

DQA1_<16>

DQA1_<17>

DQA1_<17>

DQA1_<18>

DQA1_<18>

DQA1_<19>

DQA1_<19>

DQA1_<20>

DQA1_<20>

DQA1_<21>

DQA1_<21>

DQA1_<22>

DQA1_<22>

DQA1_<23>

DQA1_<23>

DQA1_<24>

DQA1_<24>

DQA1_<25>

DQA1_<25>

DQA1_<26>

DQA1_<26>

DQA1_<27>

DQA1_<27>

DQA1_<28>

DQA1_<28>

DQA1_<29>

DQA1_<29>

DQA1_<30>

DQA1_<30>

DQA1_<31>

DQA1_<31>

MAA1_<0>

MAA1_<0>

MAA1_<1>

MAA1_<1>

MAA1_<2>

MAA1_<2>

MAA1_<3>

MAA1_<3>

MAA1_<4>

MAA1_<4>

MAA1_<5>

MAA1_<5>

MAA1_<6>

MAA1_<6>

MAA1_<7>

MAA1_<7>

MAA1_<8>

MAA1_<8>

WCKA1_0

WCKA1_0

WCKA1B_0

WCKA1B_0

WCKA1_1

WCKA1_1

WCKA1B_1

WCKA1B_1

EDCA1_0

EDCA1_0

EDCA1_1

EDCA1_1

EDCA1_2

EDCA1_2

EDCA1_3

EDCA1_3

DDBIA1_0DDBIA0_0

DDBIA1_0DDBIA0_0

DDBIA1_1

DDBIA1_1

DDBIA1_2

DDBIA1_2

DDBIA1_3

DDBIA1_3

CSA1B_0

CSA1B_0

CASA1B

CASA1B

RASA1B

RASA1B

WEA1B

WEA1B

CLKA1B

CLKA1B

MVREFD/S =0.7*

MVREFD/S =0.7*

VDDR1

VDDR1

(GDDR3/4/5)

(GDDR3/4/5)

0

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

MAA1_<8..0>

MAA1_<8..0>

0

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

MVREFD_A

MVREFD_A

DQA1_<31..0>

DQA1_<31..0>

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

BI BIBIBI

3 4

OUT OUTOUTOUT

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

2 1

2 1

3 4

+MVDD +MVDD

+MVDD +MVDD

R3602

R3602

40.2R

40.2R

1%

1%

1%

1%

2 1

2 1

C3602

C3602

1uF

1uF

R3606

R3606

6.3V

6.3V

100R

100R

1%

1%

1%

1%

2 1

2 1

3 4

3 4

DQB0_<31..0>

DQB0_<31..0>

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

3

4 3

4

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

MAB0_<8..0>MAA0_<8..0>

MAB0_<8..0>MAA0_<8..0>

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

BI

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

4

4

OUT

R3601

R3601

AMD - PLATFORM HARDWARE ENG

AMD - PLATFORM HARDWARE ENG

#48, No.1387, ZHANGDONG ROAD

#48, No.1387, ZHANGDONG ROAD

SHANGHAI, CHINA 201203

SHANGHAI, CHINA 201203

SHEET:

DATE:

SHEET NUMBER:

DOCUMENT NUMBER:

4

4

DQB0_<0>

DQB0_<0>

3

3

0

0

DQB0_<1>

DQB0_<1>

1

1

DQB0_<2>

DQB0_<2>

2

2

DQB0_<3>

DQB0_<3>

3

3

DQB0_<4>

DQB0_<4>

4

4

DQB0_<5>

DQB0_<5>

5

5

DQB0_<6>

DQB0_<6>

6

6

DQB0_<7>

DQB0_<7>

7

7

DQB0_<8>

DQB0_<8>

8

8

DQB0_<9>

DQB0_<9>

9

9

DQB0_<10>

DQB0_<10>

10

10

DQB0_<11>

DQB0_<11>

11

11

DQB0_<12>

DQB0_<12>

12

12

DQB0_<13>

DQB0_<13>

13

13

DQB0_<14>

DQB0_<14>

14

14

DQB0_<15>

DQB0_<15>

15

15

DQB0_<16>

DQB0_<16>

16

16

DQB0_<17>

DQB0_<17>

17

17

DQB0_<18>

DQB0_<18>

18

18

DQB0_<19>

DQB0_<19>

19

19

DQB0_<20>

DQB0_<20>

20

20

DQB0_<21>

DQB0_<21>

21

21

DQB0_<22>

DQB0_<22>

22

22

DQB0_<23>

DQB0_<23>

23

23

DQB0_<24>

DQB0_<24>

24

24

DQB0_<25>

DQB0_<25>

25

25

DQB0_<26>

DQB0_<26>

26

26

DQB0_<27>

DQB0_<27>

27

27

DQB0_<28>

DQB0_<28>

28

28

DQB0_<29>

DQB0_<29>

29

29

DQB0_<30>

DQB0_<30>

30

30

DQB0_<31>

DQB0_<31>

31

31

4

4

MAB0_<0>

MAB0_<0>

3

3

0

0

MAB0_<1>

MAB0_<1>

1

1

MAB0_<2>

MAB0_<2>

2

2

MAB0_<3>

MAB0_<3>

3

3

MAB0_<4>

MAB0_<4>

4

4

MAB0_<5>

MAB0_<5>

5

5

MAB0_<6>

MAB0_<6>

6

6

MAB0_<7>

MAB0_<7>

7

7

MAB0_<8>

MAB0_<8>

8

8

WCKB0_0

WCKB0_0

WCKB0B_0

WCKB0B_0

WCKB0_1

WCKB0_1

WCKB0B_1

WCKB0B_1

EDCB0_0

EDCB0_0

EDCB0_1

EDCB0_1

EDCB0_2

EDCB0_2

EDCB0_3

EDCB0_3

DDBIB0_0

DDBIB0_0

DDBIB0_1

DDBIB0_1

DDBIB0_2

DDBIB0_2

DDBIB0_3

DDBIB0_3

ADBIB0 ADBIB1

ADBIB0 ADBIB1

CSB0B_0

CSB0B_0

CASB0B

CASB0B

RASB0B

RASB0B

WEB0B

WEB0B

CKEB0 CKEB1

CKEB0 CKEB1

CLKB0 CLKB1

CLKB0 CLKB1

CLKB0B

CLKB0B

243R

243R

21

21

MEM_CALRP0

MEM_CALRP0

1%

1%

Oland MEMORY INTERFACE

Oland MEMORY INTERFACE

Fri Oct 28 17:09:40 2016

Fri Oct 28 17:09:40 2016

C5

C5

DQB0_0

C3

C3

DQB0_1

E3

E3

DQB0_2

E1

E1

DQB0_3

F1

F1

DQB0_4

F3

F3

DQB0_5

F5

F5

DQB0_6

G4

G4

DQB0_7

H5

H5

DQB0_8

H6

H6

DQB0_9

J4

J4

DQB0_10

K6

K6

DQB0_11

K5

K5

DQB0_12

L4

L4

DQB0_13

M6

M6

DQB0_14

M1

M1

DQB0_15

M3

M3

DQB0_16

M5

M5

DQB0_17

N4

N4

DQB0_18

P6

P6

DQB0_19

P5

P5

DQB0_20

R4

R4

DQB0_21

T6

T6

DQB0_22

T1

T1

DQB0_23

U4

U4

DQB0_24

V6

V6

DQB0_25

V1

V1

DQB0_26

V3

V3

DQB0_27

Y6

Y6

DQB0_28

Y1

Y1

DQB0_29

Y3

Y3

DQB0_30

Y5

Y5

DQB0_31

P8

P8

MAB0_0

T9

T9

MAB0_1

P9

P9

MAB0_2

N7

N7

MAB0_3

N8

N8

MAB0_4

N9

N9

MAB0_5

U9

U9

MAB0_6

U8

U8

MAB0_7

T8

T8

MAB0_8

U12

U12

MAB0_9

H3

H3

WCKB0_0

H1

H1

WCKB0B_0

T3

T3

WCKB0_1

T5

T5

WCKB0B_1

F6

F6

EDCB0_0

K3

K3

EDCB0_1

P3

P3

EDCB0_2

V5

V5

EDCB0_3

G7

G7

DDBIB0_0

K1

K1

DDBIB0_1

P1

P1

DDBIB0_2

W4

W4

DDBIB0_3

P10

P10

CSB0B_0

L10

L10

CSB0B_1

L9

L9

CLKB0

L8

L8

CLKB0B

M27

M27

MEM_CALRP0

3

3

OF

105_CXXX00_00A

105_CXXX00_00A

21

21

U1

U1U1

OLAND M2 GDDR5

OLAND M2 GDDR5

REV:

1.0

1.0

DQB1_<31..0>

AA4

AA4

DQB1_<0>

DQB1_0

DQB1_1

DQB1_2

DQB1_3

DQB1_4

DQB1_5

DQB1_6

DQB1_7

DQB1_8

DQB1_9

DQB1_10

DQB1_11

DQB1_12

DQB1_13

DQB1_14

DQB1_15

DQB1_16

DQB1_17

DQB1_18

DQB1_19

DQB1_20

DQB1_21

DQB1_22

DQB1_23

DQB1_24

DQB1_25

DQB1_26

DQB1_27

DQB1_28

DQB1_29

DQB1_30

DQB1_31

MAB1_0

MAB1_1

MAB1_2

MAB1_3

MAB1_4

MAB1_5

MAB1_6

MAB1_7

MAB1_8

MAB1_9

WCKB1_0

WCKB1B_0

WCKB1_1

WCKB1B_1

EDCB1_0

EDCB1_1

EDCB1_2

EDCB1_3

DDBIB1_0

DDBIB1_1

DDBIB1_2

DDBIB1_3

ADBIB1ADBIB0

CSB1B_0

CSB1B_1

CASB1BCASB0B

RASB1BRASB0B

WEB1BWEB0B

CKEB1CKEB0

CLKB1

CLKB1B

MVREFDB

MVREFSB

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

DQB1_<0>

AB6

AB6

DQB1_<1>

DQB1_<1>

AB1

AB1

DQB1_<2>

DQB1_<2>

AB3

AB3

DQB1_<3>

DQB1_<3>

AD6

AD6

DQB1_<4>

DQB1_<4>

AD1

AD1

DQB1_<5>

DQB1_<5>

AD3

AD3

DQB1_<6>

DQB1_<6>

AD5

AD5

DQB1_<7>

DQB1_<7>

AF1

AF1

DQB1_<8>

DQB1_<8>

AF3

AF3

DQB1_<9>

DQB1_<9>

AF6

AF6

DQB1_<10>

DQB1_<10>

AG4

AG4

DQB1_<11>

DQB1_<11>

AH5

AH5

DQB1_<12>

DQB1_<12>

AH6

AH6

DQB1_<13>

DQB1_<13>

AJ4

AJ4

DQB1_<14>

DQB1_<14>

AK3

AK3

DQB1_<15>

DQB1_<15>

AF8

AF8

DQB1_<16>

DQB1_<16>

AF9

AF9

DQB1_<17>

DQB1_<17>

AG8

AG8

DQB1_<18>

DQB1_<18>

AG7

AG7

DQB1_<19>

DQB1_<19>

AK9

AK9

DQB1_<20>

DQB1_<20>

AL7

AL7

DQB1_<21>

DQB1_<21>

AM8

AM8

DQB1_<22>

DQB1_<22>

AM7

AM7

DQB1_<23>

DQB1_<23>

AK1

AK1

DQB1_<24>

DQB1_<24>

AL4

AL4

DQB1_<25>

DQB1_<25>

AM6

AM6

DQB1_<26>

DQB1_<26>

AM1

AM1

DQB1_<27>

DQB1_<27>

AN4

AN4

DQB1_<28>

DQB1_<28>

AP3

AP3

DQB1_<29>

DQB1_<29>

AP1

AP1

DQB1_<30>

DQB1_<30>

AP5

AP5

DQB1_<31>

DQB1_<31>

Y9

Y9

MAB1_<0>

MAB1_<0>

W9

W9

MAB1_<1>

MAB1_<1>

AC8

AC8

MAB1_<2>

MAB1_<2>

AC9

AC9

MAB1_<3>

MAB1_<3>

AA7

AA7

MAB1_<4>

MAB1_<4>

AA8

AA8

MAB1_<5>

MAB1_<5>

Y8

Y8

MAB1_<6>

MAB1_<6>

AA9

AA9

MAB1_<7>

MAB1_<7>

W8

W8

MAB1_<8>

MAB1_<8>

V12

V12

WCKB1_0

AE4

AE4

WCKB1_0

AF5

WCKB1B_0

AF5

WCKB1B_0

WCKB1_1

AK6

AK6

WCKB1_1

AK5

WCKB1B_1

AK5

WCKB1B_1

AB5

AB5

EDCB1_0

EDCB1_0

AH1

AH1

EDCB1_1

EDCB1_1

AJ9

AJ9

EDCB1_2

EDCB1_2

AM5

AM5

EDCB1_3

EDCB1_3

AC4

AC4

DDBIB1_0

DDBIB1_0

AH3

AH3

DDBIB1_1

DDBIB1_1

AJ8

AJ8

DDBIB1_2

DDBIB1_2

AM3

AM3

DDBIB1_3

DDBIB1_3

W7T7

W7T7

AD10

AD10

CSB1B_0

CSB1B_0

AC10

AC10

AA10W10

AA10W10

CASB1B

CASB1B

Y10T10

RASB1B

Y10T10

RASB1B

AB11N10

WEB1B

AB11N10

WEB1B

AA11U10

AA11U10

AD8

AD8

AD7

AD7

CLKB1B

CLKB1B

Y12

Y12

MVREFD/S =0.7* 1%

MVREFD/S =0.7* 1%

VDDR1

VDDR1

(GDDR3/4/5)

(GDDR3/4/5)

AA12

AA12

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

2016

2016

C

This AMD Board schematic and design is the exclusive property of AMD, and

is provided only to entities under a non-disclosure agreement with AMD

for evaluation purposes. Further distribution or disclosure is strictly

prohibited. Use of this schematic and design for any purpose other than

evaluation requires a Board Technology License Agreement with AMD.

AMD makes no representations or warranties of any kind regarding this

schematic and design, including, not limited to, any implied warranty

of merchantability or fitness for a particular purpose, and disclaims

responsibility for any consequences resulting from use of the

information included herein.

TITLE:

DQB1_<31..0>

0

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

MAB1_<8..0>

MAB1_<8..0>

0

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

MVREFD_B

MVREFD_B

Advanced Micro Devices

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

C3603

C3603

1uF

1uF

6.3V

6.3V

2 1

2 1

TITLE

TITLE

R3603

R3603

40.2R

40.2R

1%

1%

2 1

2 1

R3607

R3607

100R

100R

1%

1%

2 1

2 1

1%

1%

DD

3 4

3 4

C

BB

A

8

7

6

5

4

3

2

1

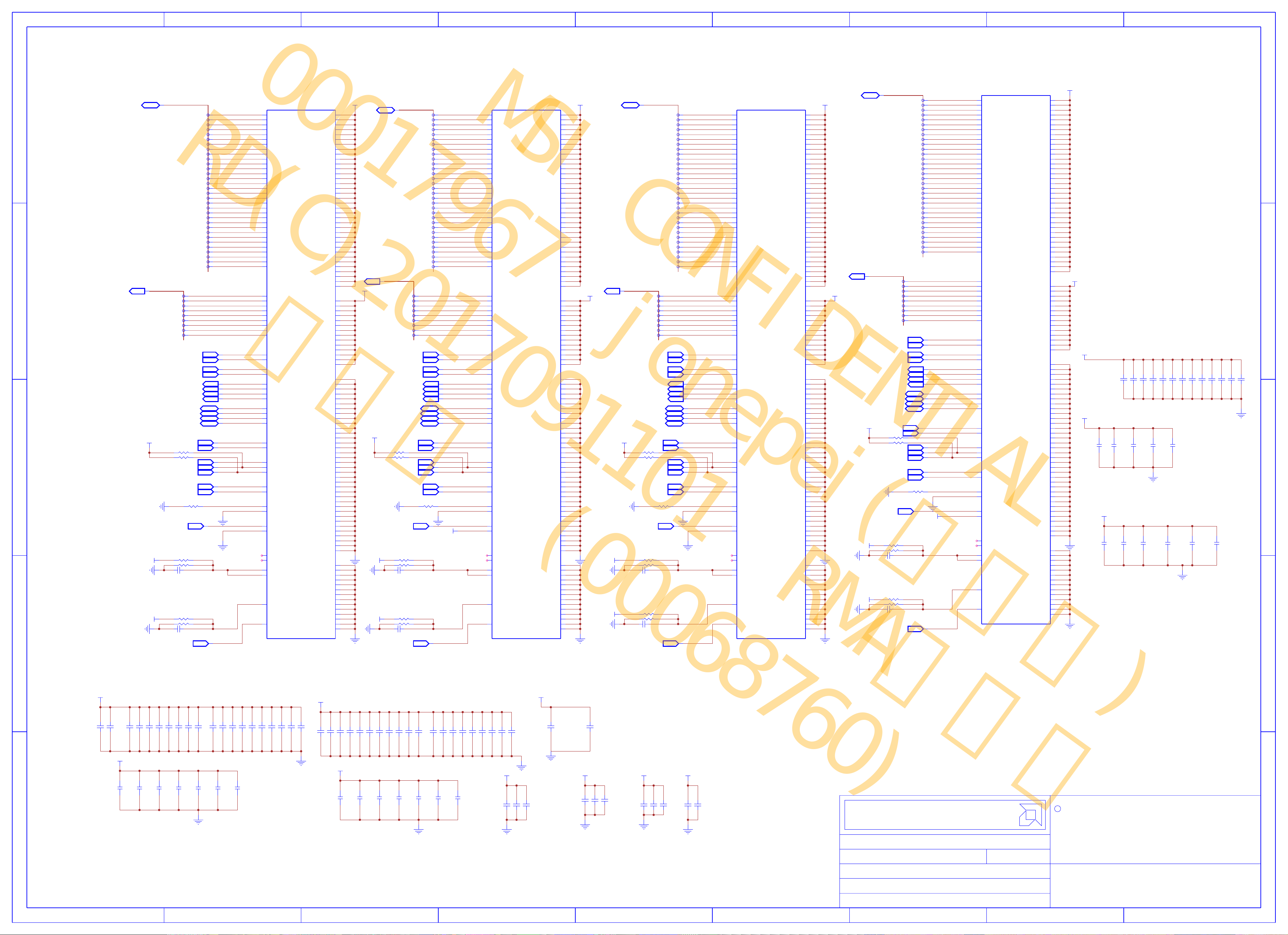

Page 4

9

9

A

B

C

D

E

8

7

7 46 5 123

DOCUMENT NUMBER:

TITLE:

C

is provided only to entities under a non-disclosure agreement with AMD

NOTES:

2

OF

REV:

4

D

1

A

B

58 6 3

SHEET:

SHEET NUMBER:

DATE:

This AMD Board schematic and design is the exclusive property of AMD, and

Advanced Micro Devices

CONFIDENTIAL AND PROPRIETARY TO ADVANCED MICRO DEVICES INC.

information included herein.

responsibility for any consequences resulting from use of the

of merchantability or fitness for a particular purpose, and disclaims

schematic and design, including, not limited to, any implied warranty

AMD makes no representations or warranties of any kind regarding this

evaluation requires a Board Technology License Agreement with AMD.

prohibited. Use of this schematic and design for any purpose other than

for evaluation purposes. Further distribution or disclosure is strictly

C

E

OUTININININ

OUT

OUT

OUT

OUTBIBIBIBIINININININININBIBIBIBIINININININ

OUT

OUT

OUT

OUTBIBIBIBIININININININININ

VSS_B5

VSS_B10

VSS_D10

VSS_G5

VSS_G10

VSS_H1

VSS_H14

VSS_K1

VSS_K14

VSS_L5

VSS_L10

VSS_P10

VSS_T5

VSS_T10

SEN

VSSQ_V14

VSSQ_V12

VSSQ_V3

VSSQ_V1

VSSQ_R14

VSSQ_R12

VSSQ_R11

VSSQ_R4

VSSQ_R3

VSSQ_R1

VSSQ_N1

VSSQ_N14

VSSQ_N12

VSSQ_N3

VSSQ_M10

VSSQ_M5

VSSQ_K13

VSSQ_K2

VSSQ_H13

VSSQ_H2

VSSQ_F10

VSSQ_F5

VSSQ_E14

VSSQ_E12

VSSQ_E3

VSSQ_E1

VSSQ_C14

VSSQ_C12

VSSQ_C11

VSSQ_C4

VSSQ_C3

VSSQ_C1

VSSQ_A14

VSSQ_A12

VSSQ_A3

VSSQ_A1

ZQ

VREFC

VDD_R10

VDD_R5

VDD_P11

VDD_L14

VDDQ_T14

VDDQ_T12

VDDQ_T3

VDDQ_T1

VDDQ_P14

VDDQ_P12

VDDQ_P3

VDDQ_P1

VDDQ_N10

VDDQ_N5

VDDQ_M14

VDDQ_M12

VDDQ_M3

VDDQ_M1

Vpp_NC1

Vpp_NC

WCK23#__WCK01#

WCK23__WCK01

WCK01#__WCK23#

WCK01__WCK23

RFU_A12_NC

VREFD2

VREFD1

MF

VDD_L11

VDD_L4

VDDQ_L13

VDDQ_L2

VDDQ_K12

VDDQ_K3

VDDQ_H12

VDDQ_H3

WE#__CS#

VDD_L1

VDD_G14

VDD_G11

VDD_G4

VDD_G1

VDD_D11

VDD_C10

VDD_C5

VDDQ_G13

VDDQ_G2

VDDQ_F14

VDDQ_F12

VDDQ_E10

DBI3#__DBI0#

DBI2#__DBI1#

DBI1#__DBI2#

DBI0#__DBI3#

EDC3__EDC0

EDC2__EDC1

EDC1__EDC2

EDC0__EDC3

VDDQ_E5

VDDQ_D14

VDDQ_D12

VDDQ_D3

VDDQ_D1

VDDQ_B14

VDDQ_B12

VDDQ_B3

VDDQ_B1

A5_BA1__A3_BA3

CK#

CK

VDDQ_F1

A1_A9__A6_A11

CKE#

RESET#

A2_BA0__A4_BA2

RAS#__CAS#

A6_A11__A1_A9

A7_A8__A0_A10

A4_BA2__A2_BA0

A0_A10__A7_A8

A3_BA3__A5_BA1

CS#__WE#

CAS#__RAS#

DQ0__DQ24

DQ1__DQ25

DQ2__DQ26

DQ3__DQ27

DQ4__DQ28

DQ5__DQ29

DQ6__DQ30

DQ7__DQ31

DQ8__DQ16

DQ9__DQ17

DQ10__DQ18

DQ11__DQ19

DQ12__DQ20

DQ13__DQ21

DQ14__DQ22

DQ15__DQ23

DQ16__DQ8

DQ17__DQ9

DQ18__DQ10

DQ19__DQ11

DQ20__DQ12

DQ21__DQ13

DQ22__DQ14

DQ23__DQ15

DQ24__DQ0

DQ25__DQ1

DQ26__DQ2

DQ27__DQ3

DQ28__DQ4

DQ29__DQ5

DQ30__DQ6

DQ31__DQ7

ABI#

VDDQ_F3

IN

OUTINOUTININININ

OUT

OUT

OUT

OUTBIBIBIBIININININININ

IN

VSS_B5

VSS_B10

VSS_D10

VSS_G5

VSS_G10

VSS_H1

VSS_H14

VSS_K1

VSS_K14

VSS_L5

VSS_L10

VSS_P10

VSS_T5

VSS_T10

SEN

VSSQ_V14

VSSQ_V12

VSSQ_V3

VSSQ_V1

VSSQ_R14

VSSQ_R12

VSSQ_R11

VSSQ_R4

VSSQ_R3

VSSQ_R1

VSSQ_N1

VSSQ_N14

VSSQ_N12

VSSQ_N3

VSSQ_M10

VSSQ_M5

VSSQ_K13

VSSQ_K2

VSSQ_H13

VSSQ_H2

VSSQ_F10

VSSQ_F5

VSSQ_E14

VSSQ_E12

VSSQ_E3

VSSQ_E1

VSSQ_C14

VSSQ_C12

VSSQ_C11

VSSQ_C4

VSSQ_C3

VSSQ_C1

VSSQ_A14

VSSQ_A12

VSSQ_A3

VSSQ_A1

ZQ

VREFC

VDD_R10

VDD_R5

VDD_P11

VDD_L14

VDDQ_T14

VDDQ_T12

VDDQ_T3

VDDQ_T1

VDDQ_P14

VDDQ_P12

VDDQ_P3

VDDQ_P1

VDDQ_N10

VDDQ_N5

VDDQ_M14

VDDQ_M12

VDDQ_M3

VDDQ_M1

Vpp_NC1

Vpp_NC

WCK23#__WCK01#

WCK23__WCK01

WCK01#__WCK23#

WCK01__WCK23

RFU_A12_NC

VREFD2

VREFD1

MF

VDD_L11

VDD_L4

VDDQ_L13

VDDQ_L2

VDDQ_K12

VDDQ_K3

VDDQ_H12

VDDQ_H3

WE#__CS#

VDD_L1

VDD_G14

VDD_G11

VDD_G4

VDD_G1

VDD_D11

VDD_C10

VDD_C5

VDDQ_G13

VDDQ_G2

VDDQ_F14

VDDQ_F12

VDDQ_E10

DBI3#__DBI0#

DBI2#__DBI1#

DBI1#__DBI2#

DBI0#__DBI3#

EDC3__EDC0

EDC2__EDC1

EDC1__EDC2

EDC0__EDC3

VDDQ_E5

VDDQ_D14

VDDQ_D12

VDDQ_D3

VDDQ_D1

VDDQ_B14

VDDQ_B12

VDDQ_B3

VDDQ_B1

A5_BA1__A3_BA3

CK#

CK

VDDQ_F1

A1_A9__A6_A11

CKE#

RESET#

A2_BA0__A4_BA2

RAS#__CAS#

A6_A11__A1_A9

A7_A8__A0_A10

A4_BA2__A2_BA0

A0_A10__A7_A8

A3_BA3__A5_BA1

CS#__WE#

CAS#__RAS#

DQ0__DQ24

DQ1__DQ25

DQ2__DQ26

DQ3__DQ27

DQ4__DQ28

DQ5__DQ29

DQ6__DQ30

DQ7__DQ31

DQ8__DQ16

DQ9__DQ17

DQ10__DQ18

DQ11__DQ19

DQ12__DQ20

DQ13__DQ21

DQ14__DQ22

DQ15__DQ23

DQ16__DQ8

DQ17__DQ9

DQ18__DQ10

DQ19__DQ11

DQ20__DQ12

DQ21__DQ13

DQ22__DQ14

DQ23__DQ15

DQ24__DQ0

DQ25__DQ1

DQ26__DQ2

DQ27__DQ3

DQ28__DQ4

DQ29__DQ5

DQ30__DQ6

DQ31__DQ7

ABI#

VDDQ_F3

IN

IN

VSS_B5

VSS_B10

VSS_D10

VSS_G5

VSS_G10

VSS_H1

VSS_H14

VSS_K1

VSS_K14

VSS_L5

VSS_L10

VSS_P10

VSS_T5

VSS_T10

SEN

VSSQ_V14

VSSQ_V12

VSSQ_V3

VSSQ_V1

VSSQ_R14

VSSQ_R12

VSSQ_R11

VSSQ_R4

VSSQ_R3

VSSQ_R1

VSSQ_N1

VSSQ_N14

VSSQ_N12

VSSQ_N3

VSSQ_M10

VSSQ_M5

VSSQ_K13

VSSQ_K2

VSSQ_H13

VSSQ_H2

VSSQ_F10

VSSQ_F5

VSSQ_E14

VSSQ_E12

VSSQ_E3

VSSQ_E1

VSSQ_C14

VSSQ_C12

VSSQ_C11

VSSQ_C4

VSSQ_C3

VSSQ_C1

VSSQ_A14

VSSQ_A12

VSSQ_A3

VSSQ_A1

ZQ

VREFC

VDD_R10

VDD_R5

VDD_P11

VDD_L14

VDDQ_T14

VDDQ_T12

VDDQ_T3

VDDQ_T1

VDDQ_P14

VDDQ_P12

VDDQ_P3

VDDQ_P1

VDDQ_N10

VDDQ_N5

VDDQ_M14

VDDQ_M12

VDDQ_M3

VDDQ_M1

Vpp_NC1

Vpp_NC

WCK23#__WCK01#

WCK23__WCK01

WCK01#__WCK23#

WCK01__WCK23

RFU_A12_NC

VREFD2

VREFD1

MF

VDD_L11

VDD_L4

VDDQ_L13

VDDQ_L2

VDDQ_K12

VDDQ_K3

VDDQ_H12

VDDQ_H3

WE#__CS#

VDD_L1

VDD_G14

VDD_G11

VDD_G4

VDD_G1

VDD_D11

VDD_C10

VDD_C5

VDDQ_G13

VDDQ_G2

VDDQ_F14

VDDQ_F12

VDDQ_E10

DBI3#__DBI0#

DBI2#__DBI1#

DBI1#__DBI2#

DBI0#__DBI3#

EDC3__EDC0

EDC2__EDC1

EDC1__EDC2

EDC0__EDC3

VDDQ_E5

VDDQ_D14

VDDQ_D12

VDDQ_D3

VDDQ_D1

VDDQ_B14

VDDQ_B12

VDDQ_B3

VDDQ_B1

A5_BA1__A3_BA3

CK#

CK

VDDQ_F1

A1_A9__A6_A11

CKE#

RESET#

A2_BA0__A4_BA2

RAS#__CAS#

A6_A11__A1_A9

A7_A8__A0_A10

A4_BA2__A2_BA0

A0_A10__A7_A8

A3_BA3__A5_BA1

CS#__WE#

CAS#__RAS#

DQ0__DQ24

DQ1__DQ25

DQ2__DQ26

DQ3__DQ27

DQ4__DQ28

DQ5__DQ29

DQ6__DQ30

DQ7__DQ31

DQ8__DQ16

DQ9__DQ17

DQ10__DQ18

DQ11__DQ19

DQ12__DQ20

DQ13__DQ21

DQ14__DQ22

DQ15__DQ23

DQ16__DQ8

DQ17__DQ9

DQ18__DQ10

DQ19__DQ11

DQ20__DQ12

DQ21__DQ13

DQ22__DQ14

DQ23__DQ15

DQ24__DQ0

DQ25__DQ1

DQ26__DQ2

DQ27__DQ3

DQ28__DQ4

DQ29__DQ5

DQ30__DQ6

DQ31__DQ7

ABI#

VDDQ_F3

IN

OUT

IN

VSS_B5

VSS_B10

VSS_D10

VSS_G5

VSS_G10

VSS_H1

VSS_H14

VSS_K1

VSS_K14

VSS_L5

VSS_L10

VSS_P10

VSS_T5

VSS_T10

SEN

VSSQ_V14

VSSQ_V12

VSSQ_V3

VSSQ_V1

VSSQ_R14

VSSQ_R12

VSSQ_R11

VSSQ_R4

VSSQ_R3

VSSQ_R1

VSSQ_N1

VSSQ_N14

VSSQ_N12

VSSQ_N3

VSSQ_M10

VSSQ_M5

VSSQ_K13

VSSQ_K2

VSSQ_H13

VSSQ_H2

VSSQ_F10

VSSQ_F5

VSSQ_E14

VSSQ_E12

VSSQ_E3

VSSQ_E1

VSSQ_C14

VSSQ_C12

VSSQ_C11

VSSQ_C4

VSSQ_C3

VSSQ_C1

VSSQ_A14

VSSQ_A12

VSSQ_A3

VSSQ_A1

ZQ

VREFC

VDD_R10

VDD_R5

VDD_P11

VDD_L14

VDDQ_T14

VDDQ_T12

VDDQ_T3

VDDQ_T1

VDDQ_P14

VDDQ_P12

VDDQ_P3

VDDQ_P1

VDDQ_N10

VDDQ_N5

VDDQ_M14

VDDQ_M12

VDDQ_M3

VDDQ_M1

Vpp_NC1

Vpp_NC

WCK23#__WCK01#

WCK23__WCK01

WCK01#__WCK23#

WCK01__WCK23

RFU_A12_NC

VREFD2

VREFD1

MF

VDD_L11

VDD_L4

VDDQ_L13

VDDQ_L2

VDDQ_K12

VDDQ_K3

VDDQ_H12

VDDQ_H3

WE#__CS#

VDD_L1

VDD_G14

VDD_G11

VDD_G4

VDD_G1

VDD_D11

VDD_C10

VDD_C5

VDDQ_G13

VDDQ_G2

VDDQ_F14

VDDQ_F12

VDDQ_E10

DBI3#__DBI0#

DBI2#__DBI1#

DBI1#__DBI2#

DBI0#__DBI3#

EDC3__EDC0

EDC2__EDC1

EDC1__EDC2

EDC0__EDC3

VDDQ_E5

VDDQ_D14

VDDQ_D12

VDDQ_D3

VDDQ_D1

VDDQ_B14

VDDQ_B12

VDDQ_B3

VDDQ_B1

A5_BA1__A3_BA3

CK#

CK

VDDQ_F1

A1_A9__A6_A11

CKE#

RESET#

A2_BA0__A4_BA2

RAS#__CAS#

A6_A11__A1_A9

A7_A8__A0_A10

A4_BA2__A2_BA0

A0_A10__A7_A8

A3_BA3__A5_BA1

CS#__WE#

CAS#__RAS#

DQ0__DQ24

DQ1__DQ25

DQ2__DQ26

DQ3__DQ27

DQ4__DQ28

DQ5__DQ29

DQ6__DQ30

DQ7__DQ31

DQ8__DQ16

DQ9__DQ17

DQ10__DQ18

DQ11__DQ19

DQ12__DQ20

DQ13__DQ21

DQ14__DQ22

DQ15__DQ23

DQ16__DQ8

DQ17__DQ9

DQ18__DQ10

DQ19__DQ11

DQ20__DQ12

DQ21__DQ13

DQ22__DQ14

DQ23__DQ15

DQ24__DQ0

DQ25__DQ1

DQ26__DQ2

DQ27__DQ3

DQ28__DQ4

DQ29__DQ5

DQ30__DQ6

DQ31__DQ7

ABI#

VDDQ_F3

INININ

OUT

OUT

OUT

OUTBIBIBIINBIINININININININ

9

MSI CONFIDENTIAL

00017967 jonepei(裴亮樂)

RD(C)2017091101 RMA工程課

石阿鋒 (00068760)

8

7 46 5 123

E

D

C

B

A

(4) GDDR5 Memory Channel A&B

(4) GDDR5 Memory Channel A&B

4 3

4 3

4 3

4 3

+MVDD

+MVDD

C2007

C2008

C2008

C2007

6.3V

6.3V

6.3V

6.3V

2 1

2 1

2 1

2 1

2 1

2 1

0.1uF

0.1uF

0.1uF

0.1uF

+MVDD

+MVDD

4.7uF4V4.7uF

4.7uF4V4.7uF

4V

4V

9

GDDR5

C2022

C2022

6.3V

6.3V

2 1

2 1

1uF

1uF

GDDR5

23CNOPN001

23CNOPN001

U2000

U2000

C2024

C2023

C2024

C2023

6.3V

6.3V

6.3V

6.3V

2 1

2 1

2 1

2 1

1uF

1uF

1uF

1uF

C2025

C2025

6.3V

6.3V

1uF

1uF

VDDQ_B1

VDDQ_B3

VDDQ_B12

VDDQ_B14

VDDQ_D1

VDDQ_D3

VDDQ_D12

VDDQ_D14

VDDQ_E5

VDDQ_E10

VDDQ_F1

VDDQ_F3

VDDQ_F12

VDDQ_F14

VDDQ_G2

VDDQ_G13

VDDQ_H3

VDDQ_H12

VDDQ_K3

VDDQ_K12

VDDQ_L2

VDDQ_L13

VDDQ_M1

VDDQ_M3

VDDQ_M12

VDDQ_M14

VDDQ_N5

VDDQ_N10

VDDQ_P1

VDDQ_P3

VDDQ_P12

VDDQ_P14

VDDQ_T1

VDDQ_T3

VDDQ_T12

VDDQ_T14

VDD_C5

VDD_C10

VDD_D11

VDD_G1

VDD_G4

VDD_G11

VDD_G14

VDD_L1

VDD_L4

VDD_L11

VDD_L14

VDD_P11

VDD_R5

VDD_R10

VSSQ_A1

VSSQ_A3

VSSQ_A12

VSSQ_A14

VSSQ_C1

VSSQ_C3

VSSQ_C4

VSSQ_C11

VSSQ_C12

VSSQ_C14

VSSQ_E1

VSSQ_E3

VSSQ_E12

VSSQ_E14

VSSQ_F5

VSSQ_F10

VSSQ_H2

VSSQ_H13

VSSQ_K2

VSSQ_K13

VSSQ_M5

VSSQ_M10

VSSQ_N1

VSSQ_N3

VSSQ_N12

VSSQ_N14

VSSQ_R1

VSSQ_R3

VSSQ_R4

VSSQ_R11

VSSQ_R12

VSSQ_R14

VSSQ_V1

VSSQ_V3

VSSQ_V12

VSSQ_V14

VSS_B5

VSS_B10

VSS_D10

VSS_G5

VSS_G10

VSS_H1

VSS_H14

VSS_K1

VSS_K14

VSS_L5

VSS_L10

VSS_P10

VSS_T5

VSS_T10

+MVDD

+MVDD

C2145

C2145

6.3V

6.3V

2 1

2 1

1uF

1uF

2 1

2 1

+MVDD

+MVDD

DQA0_<31..0>

BI

OUT

DQA0_<31..0>

MAA0_<8..0>

MAA0_<8..0>

4

4

DQA0_<30>

DQA0_<30>

3

3

30 17

30 17

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

4 3

8

8

4 3

4 3

7

7

4 3

4 3

6

6

4 3

4 3

5

5

4 3

4 3

4

4

4 3

4 3

3

3

4 3

4 3

2

2