Page 1

A B

D

HGFEC

PG401 A02

4GB GDDR5, 256b, 128Mx32

1

Tall DVI-I + DP + DP + DP/HDMI + DP

TABLE OF CONTENTS

Page

2

3

Description

Table of Contents

1

Block Diagram

2

PCI Express

3

MEMORY: GPU Partition A/B

4

MEMORY: FBA[31:0]

5

MEMORY: FBA[63:32]

6

MEMORY: FBB[31:0]

7

MEMORY: FBB[63:32]

8

MEMORY: GPU Partition C/D

9

MEMORY: FBC[31:0]

10

MEMORY: FBC[63:32]

11

MEMORY: FBD[31:0]

12

MEMORY: FBD[63:32]

13

GPU PWR and GND

14

GPU Decoupling

15

DACA Interface

16

17

IFPAB DVI-I-DL

18

IFPEF with IFPE DP

IFPF DP

19

Page

20 IFPC HDMI/DP

IFPD DP

21

MIOA/B Interface and Frame Lock

22

MISC1: Fan, Thermal, JTAG, GPIO, Stereo

23

MISC2: ROM, XTAL, Straps

24

PS: 5V, PEX_VDD

4

25

Description

PS: FBVDD/Q

26

PS: NVVDD Controller

27

28

PS: NVVDD Phase 1,2

PS: NVVDD Phase 3,4

29

PS: NVVDD Phase 5, 6

30

31

PS: Dynamic Power Balance Logic

32 PS: Dynamic Power Balance Phases

PS: Inputs, Filtering, and Monitoring

33

PS: Shutdown

34

PS: 12V Current Steering PSI Control and LED

35

MECH: Bracket/Thermal

36

MICROCONTROLLER

37

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY

Table of Contents

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-V317

MS-V317

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Wednesday, August 20, 2014

Wednesday, August 20, 2014

Wednesday, August 20, 2014

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-1G401-BASE-QS1

PG401-A02

PCB REV

A

EC

BOM REV

G

MS-V317

Table of contents

Table of contents

Table of contents

Sheet ofDate:

137

Sheet ofDate:

137

Sheet ofDate:

137

PAGE

DATE

1 OF 37

04-AUG-2014

5

1.0

1.0

1.0

Page 2

A B C D E F G H

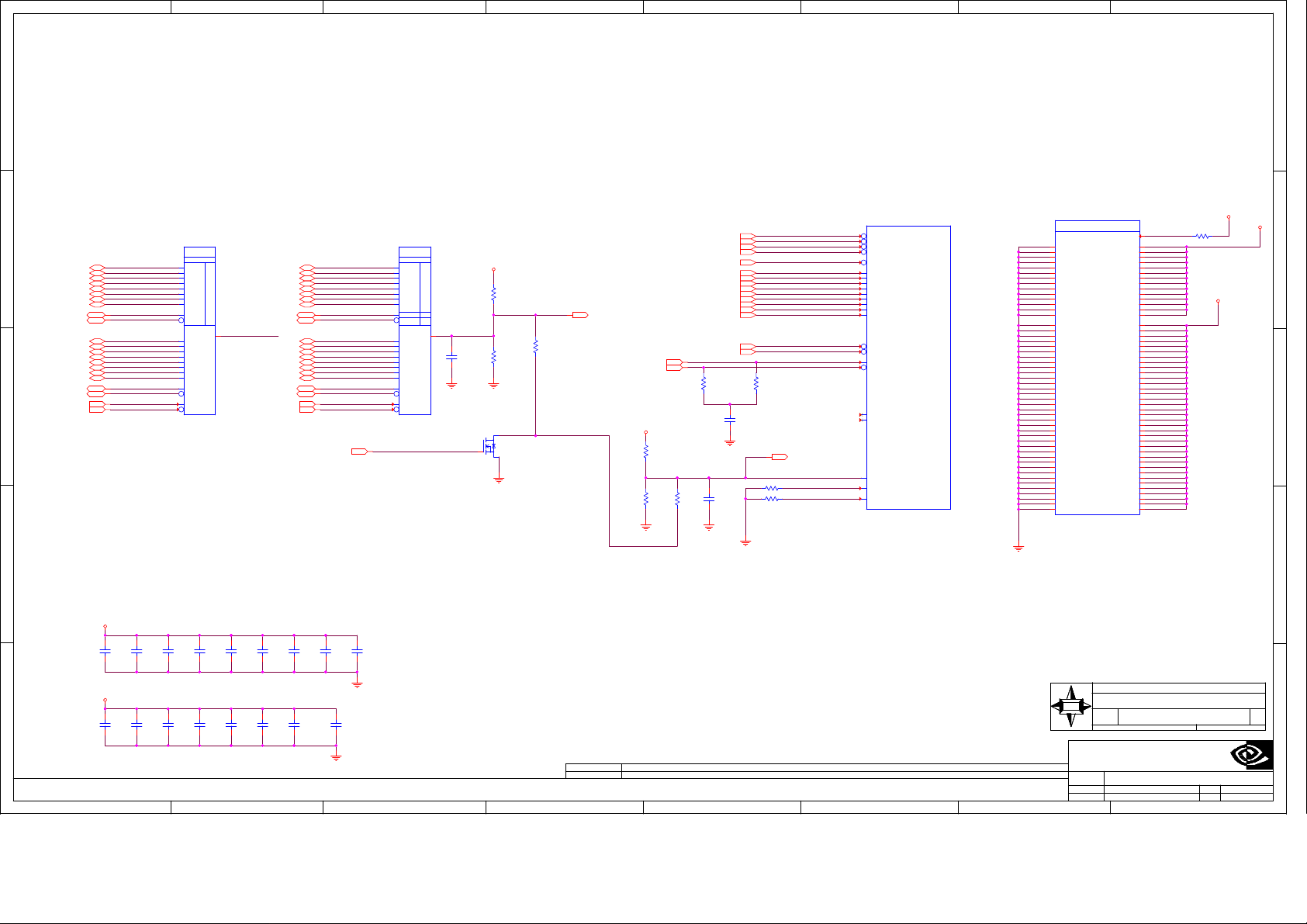

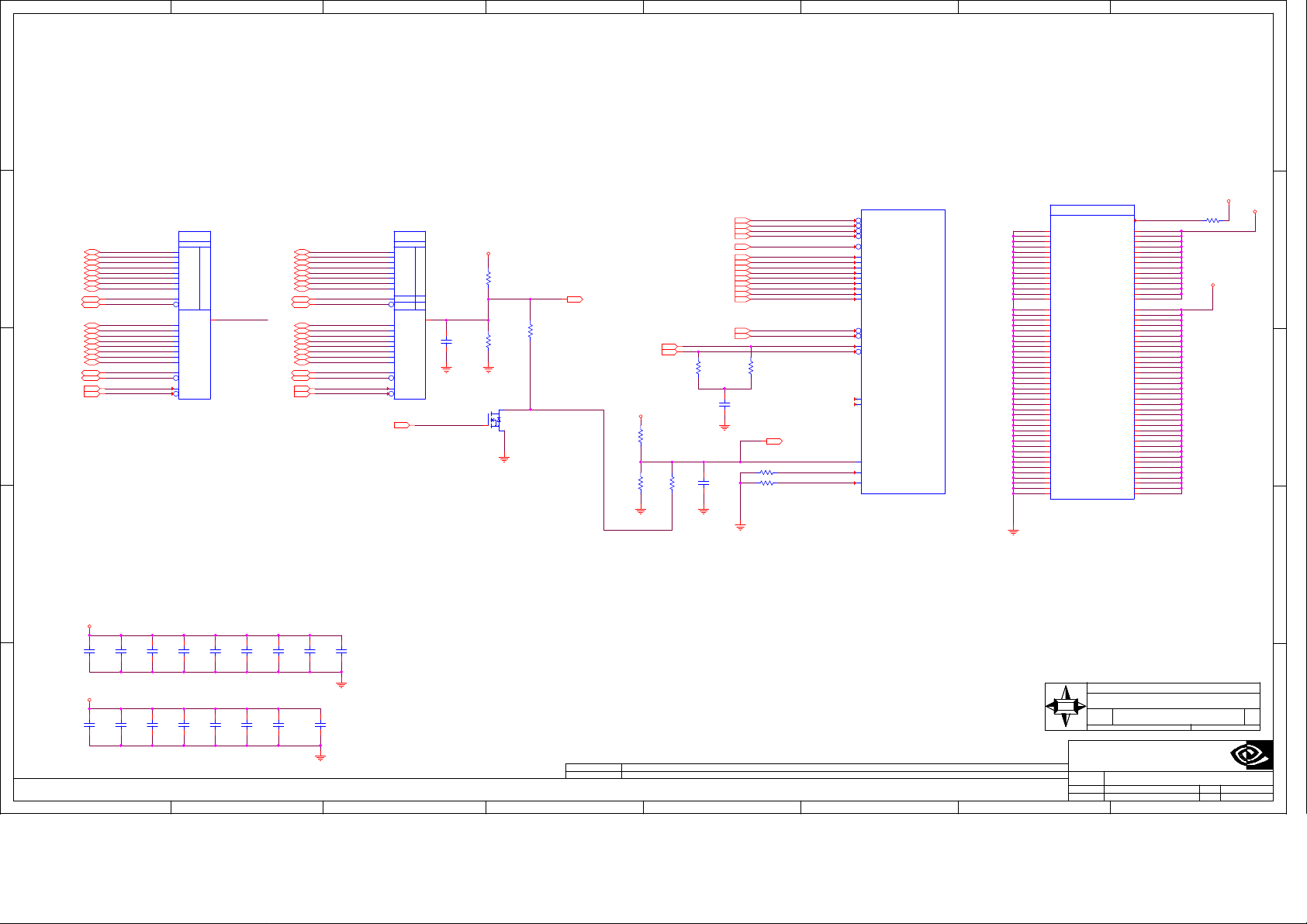

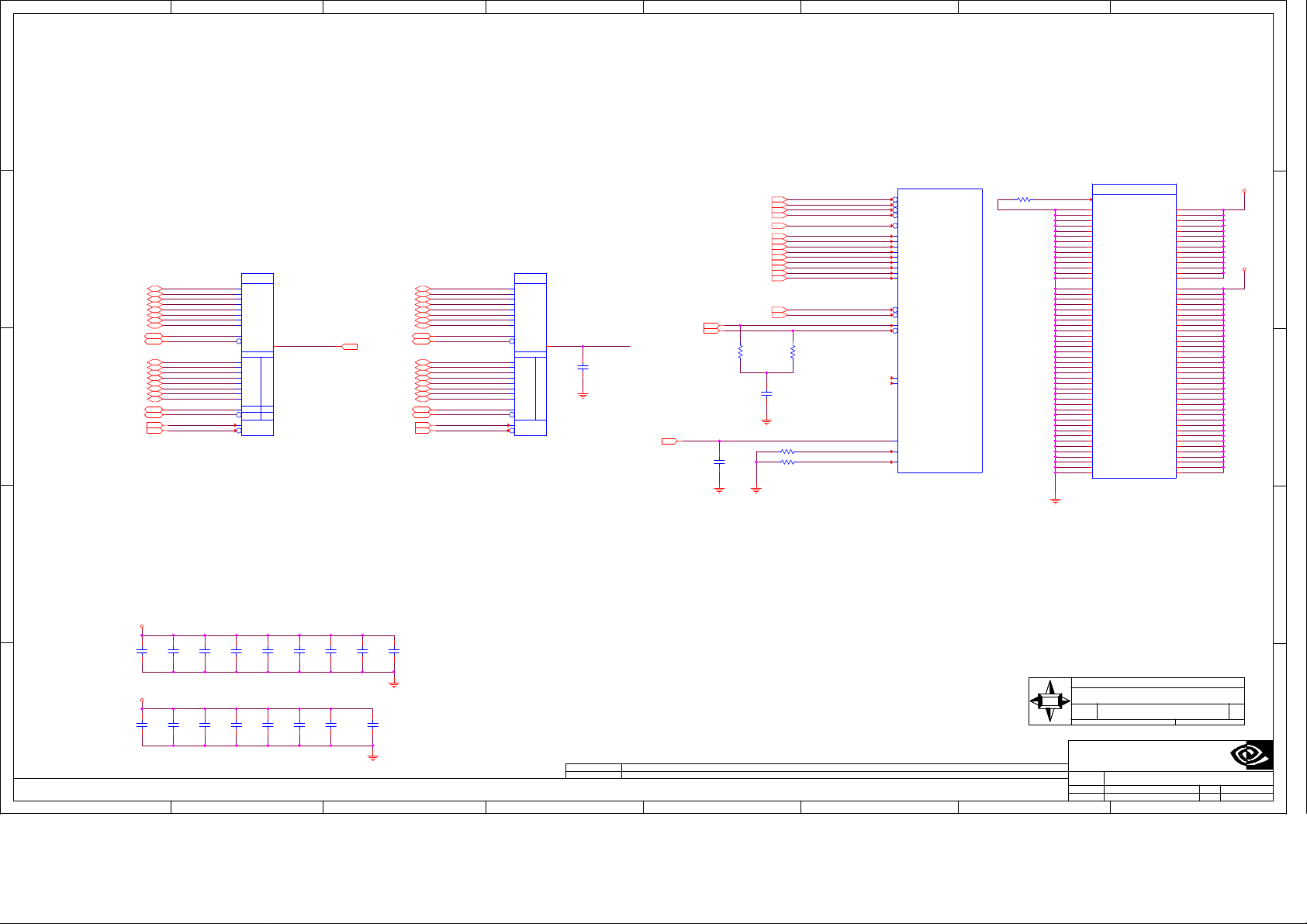

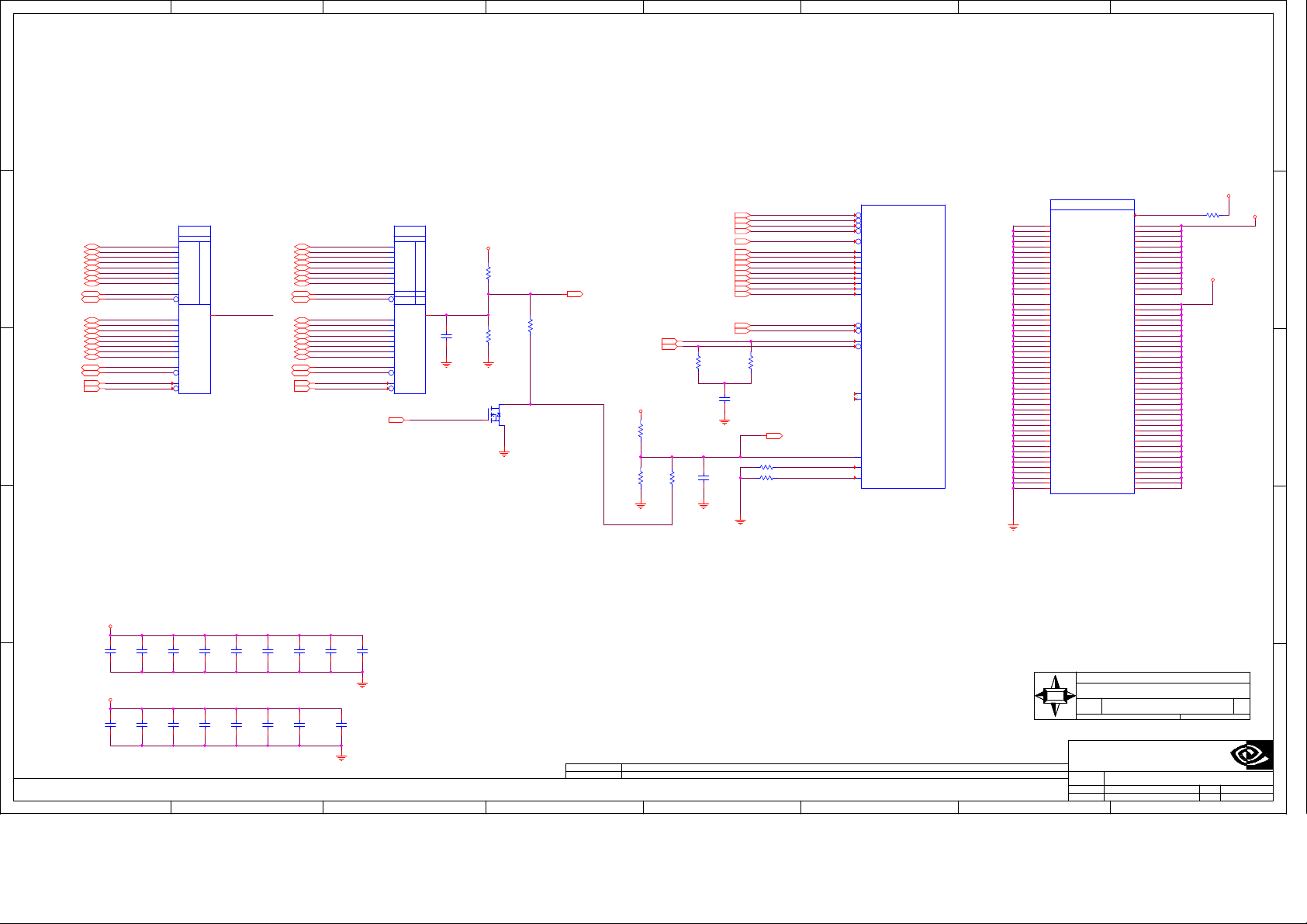

Page2: Block Diagram

1

Power Supply

NVVDD-PH3

EXT_12V 2x3 PWR 1

(NORTH)

1

Power Supply

NVVDD-PH4

4-WAY SLI/

2

DPDP

QD:2-WAY SLI with FRAME LOCK

Power Supply

NVVDD-PH1

Power Supply

NVVDD-PH2

MEM

MEM

D

MEM

HI

QD:DP

HDMI/

MEM

3

D

LO

DP

C

LO

FB X32

GM204

C

HI

MEM

LO

B

Power Supply

NVVDD-PH5

MEM

MEM

B

HI

Power Supply

NVVDD-PH6

A

LO

Power Supply

5V Linear

Power Supply

FBVDD/FBVDDQ

DVI-I

MEM

A

HI

EXT_12V 2x3 PWR 2/

EXT_12V 2x4 PWR 2

(NORTH)

DYNAMIC OPTION

PEX_12V Finger

DYNAMIC OPTION

EXT_12V 2x3 PWR 2/

EXT_12V 2x4 PWR 2

(NORTH)

QD:EXT_12V 2x4 PWR 2

(EAST)

PEX_12V Finger

PEX_12V 2x4 PWR

2

3

4

QD:STEREO

QUADRO OPTIONS SHOWN IN YELLOW

and prefix "QD:"

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C E

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY

Block Diagram

PEX_VDD

Open_Vreg option

Fan

PEX_3V3 Finger

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-V317

MS-V317

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Wednesday, August 20, 2014

Wednesday, August 20, 2014

Wednesday, August 20, 2014

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-1G401-BASE-QS1

PG401-A02

PCB REV

A

FDBA

BOM REV

G

Block Diagram

Block Diagram

Block Diagram

MS-V317

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

PAGE

DATE

H

237

237

237

2 OF 37

04-AUG-2014

4

1.0

1.0

1.0

5

Page 3

A B C D E F G H

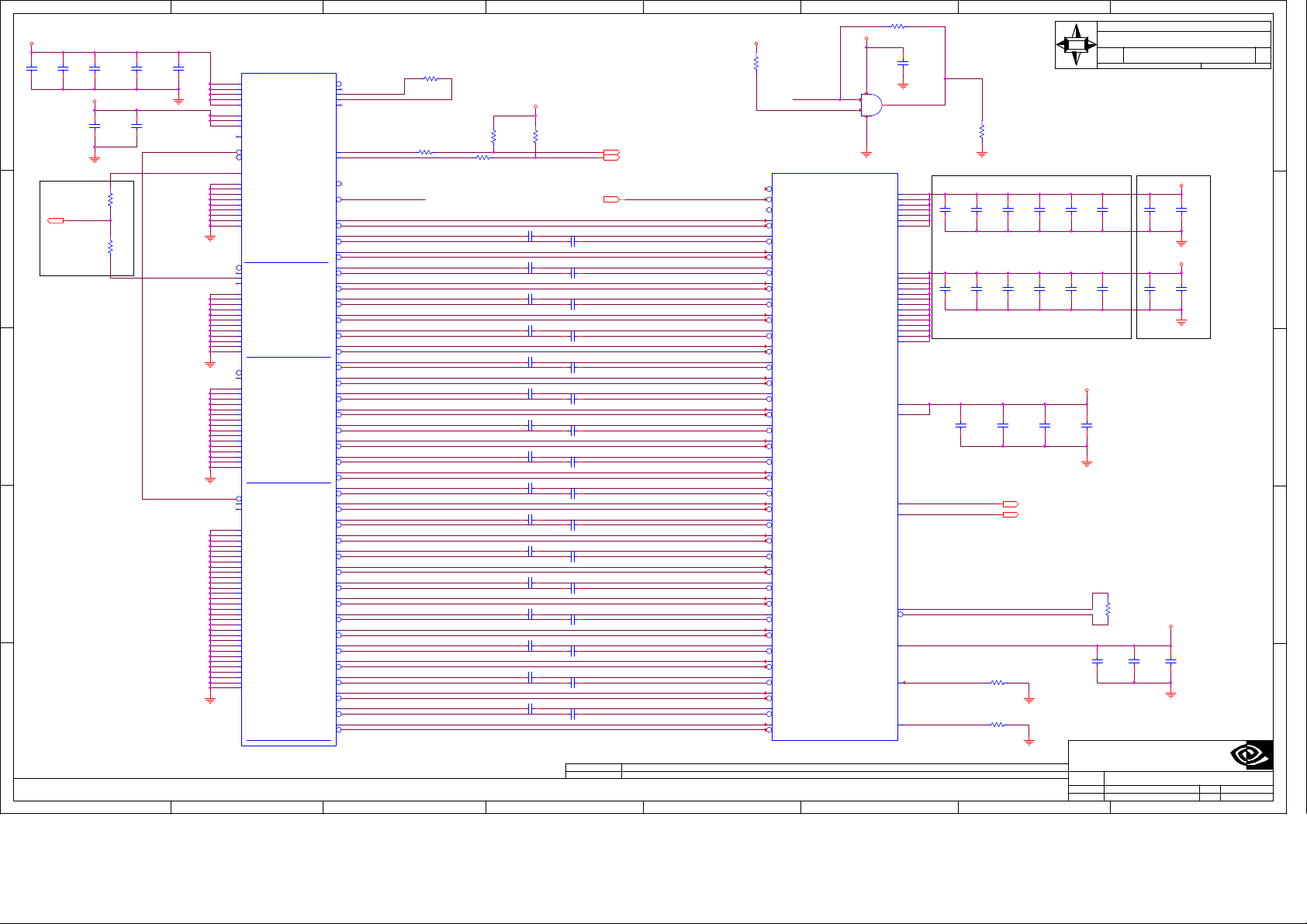

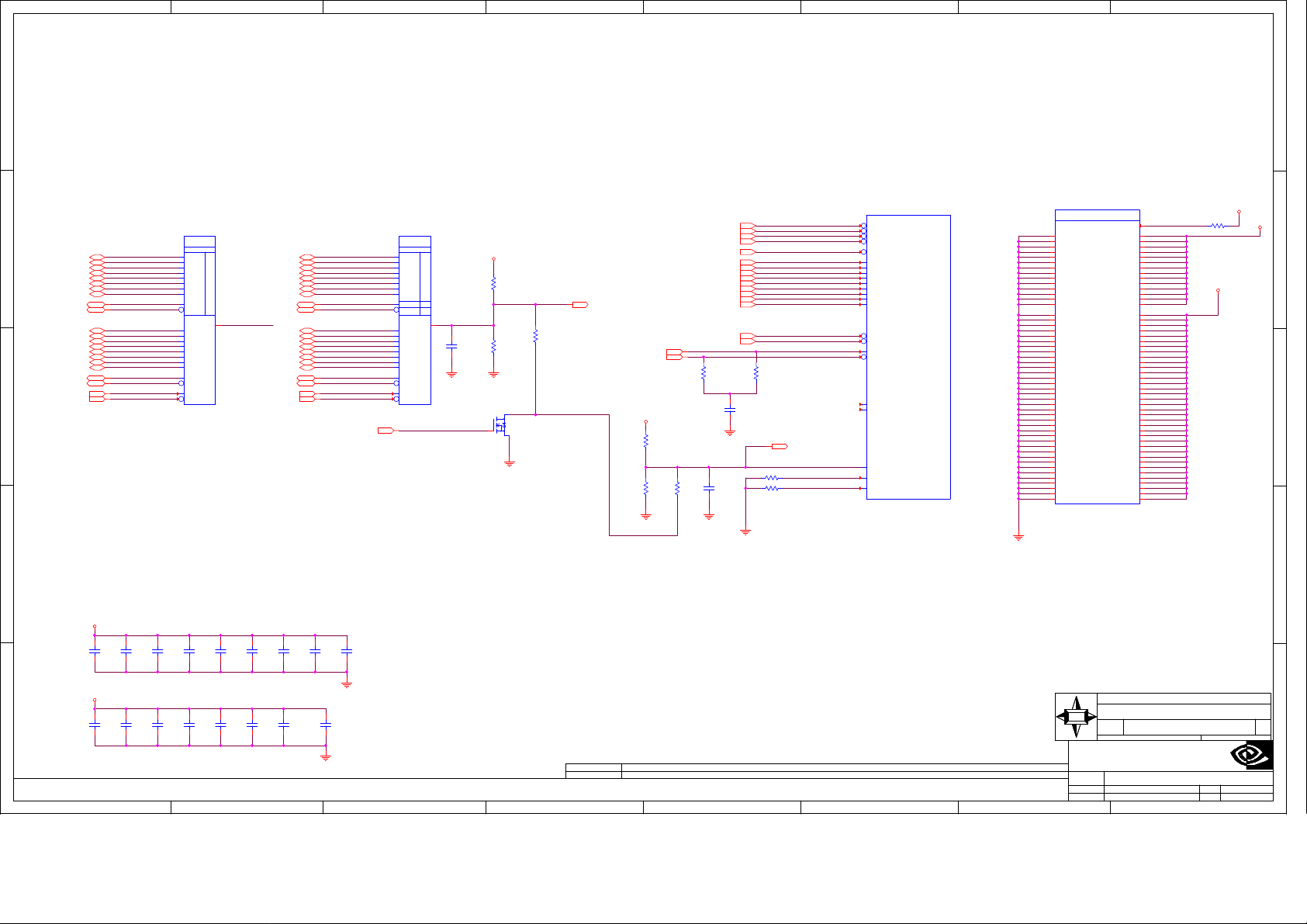

Page3: PCI Express

12V

C223

4.7uF

16V

10%

X5R

0603

DNI

1

OUT

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C908

4.7uF

16V

10%

X5R

0603

DNI

STUFF FOR

TESLA ONLY

POWER_BRAKE*

UNSTUFF FOR

DT/QUADRO

PLACE 0603 4.7UF FOOTPRINT

ON TOP OF 0805 FOOTPRINT

C50

4.7uF

16V

10%

X5R

0805

COMMON

3V3

C843

4.7uF

6.3V

20%

X5R

0603

COMMON

GND

R109

0ohm

0.05 ohm

0402

DNI

R110

0ohm

0.05 ohm

0402

DNI

C857

4.7uF

16V

10%

X5R

0805LP

COMMON

C842

0.1uF

16V

10%

X7R

0402

COMMON

RSVD2_POWER_BRAKE

RSVD4_POWER_BRAKE

GND

C850

0.1uF

16V

10%

X7R

0402

COMMON

PEX_PRSNT*

CN2NONPHY-X16

CON_X16

COMMON

@electro_mechanic.con_pci_express(sym_1):page3_i662

B1

+12V

B2

+12V

A2

+12V

A3

+12V

B3

+12V/RSVD

B8

+3V3

A9

+3V3

A10

+3V3

B10

+3V3AUX

A1

PRSNT1

B17

PRSNT2

B12

RSVD

B4

GND

A4

GND

B7

GND

A12

GND

B13

GND

A15

GND

B16

GND

B18

GND

A18

GND

GND

GND

GND

GND

END OF X1

B31

PRSNT2

A19

RSVD

B30

RSVD

A32

RSVD

A20

GND

B21

GND

B22

GND

A23

GND

A24

GND

B25

GND

B26

GND

A27

GND

A28

GND

B29

GND

A31

GND

B32

GND

END OF X4

B48

PRSNT2

A33

RSVD

A34

GND

B35

GND

B36

GND

A37

GND

A38

GND

B39

GND

B40

GND

A41

GND

A42

GND

B43

GND

B44

GND

A45

GND

A46

GND

B47

GND

B49

GND

A49

GND

END OF X8

B81

PRSNT2

A50

RSVD

B82

RSVD

A51

GND

B52

GND

B53

GND

A54

GND

A55

GND

B56

GND

B57

GND

A58

GND

A59

GND

B60

GND

B61

GND

A62

GND

A63

GND

B64

GND

B65

GND

A66

GND

A67

GND

B68

GND

B69

GND

A70

GND

A71

GND

B72

GND

B73

GND

A74

GND

A75

GND

B76

GND

B77

GND

A78

GND

A79

GND

B80

GND

A82

GND

END OF X16

TRST* JTAG1

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

SMCLK

SMDAT

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

R709

0ohm

B9

A5

A6

PEX_TDO

A7

A8

PEX_SMCLK

B5

PEX_SMDAT

B6

B11

WAKE

PEX_RST* PEX_RST_BUF*

A11

PEX_REFCLK

A13

PEX_REFCLK*

A14

PEX_TXX0

A16

PEX_TXX0*

A17

PEX_RX0

B14

PEX_RX0*

B15

PEX_TXX1

A21

PEX_TXX1*

A22

PEX_RX1

B19

PEX_RX1*

B20

PEX_TXX2

A25

PEX_TXX2*

A26

PEX_RX2

B23

PEX_RX2*

B24

PEX_TXX3

A29

PEX_TXX3*

A30

PEX_RX3

B27

PEX_RX3*

B28

PEX_TXX4

A35

PEX_TXX4*

A36

PEX_RX4

B33

PEX_RX4*

B34

PEX_TXX5

A39

PEX_TXX5*

A40

PEX_RX5

B37

PEX_RX5*

B38

PEX_TXX6

A43

PEX_TXX6*

A44

PEX_RX6

B41

PEX_RX6*

B42

PEX_TXX7

A47

PEX_TXX7*

A48

PEX_RX7

B45

PEX_RX7*

B46

PEX_TXX8

A52

PEX_TXX8*

A53

PEX_RX8

B50

PEX_RX8*

B51

PEX_TXX9

A56

PEX_TXX9*

A57

PEX_RX9

B54

PEX_RX9*

B55

PEX_TXX10

A60

PEX_TXX10*

A61

PEX_RX10

B58

PEX_RX10*

B59

PEX_TXX11

A64

PEX_TXX11*

A65

PEX_RX11

B62

PEX_RX11*

B63

PEX_TXX12

A68

PEX_TXX12*

A69

PEX_RX12

B66

PEX_RX12*

B67

PEX_TXX13

A72

PEX_TXX13*

A73

PEX_RX13

B70

PEX_RX13*

B71

PEX_TXX14

A76

PEX_TXX14*

A77

PEX_RX14

B74

PEX_RX14*

B75

PEX_TXX15

A80

PEX_TXX15*

A81

PEX_RX15

B78

PEX_RX15*

B79

0402

COMMON

R61

0402

0.05 ohm

PEX_REFCLK

PEX_REFCLK

PEX_TXX0

PEX_TXX0

PEX_RX0

PEX_RX0

PEX_TXX1

PEX_TXX1

PEX_RX1

PEX_RX1

PEX_TXX2

PEX_TXX2

PEX_RX2

PEX_RX2

PEX_TXX3

PEX_TXX3

PEX_RX3

PEX_RX3

PEX_TXX4

PEX_TXX4

PEX_RX4

PEX_RX4

PEX_TXX5

PEX_TXX5

PEX_RX5

PEX_RX5

PEX_TXX6

PEX_TXX6

PEX_RX6

PEX_RX6

PEX_TXX7

PEX_TXX7

PEX_RX7

PEX_RX7

PEX_TXX8

PEX_TXX8

PEX_RX8

PEX_RX8

PEX_TXX9

PEX_TXX9

PEX_RX9

PEX_RX9

PEX_TXX10

PEX_TXX10

PEX_RX10

PEX_RX10

PEX_TXX11

PEX_TXX11

PEX_RX11

PEX_RX11

PEX_TXX12

PEX_TXX12

PEX_RX12

PEX_RX12

PEX_TXX13

PEX_TXX13

PEX_RX13

PEX_RX13

PEX_TXX14

PEX_TXX14

PEX_RX14

PEX_RX14

PEX_TXX15

PEX_TXX15

PEX_RX15

PEX_RX15

0.05 ohm

3V3_F

R65

R66

2.2k

2.2k

5 %

5 %

0402

0402

COMMON

0ohm

DNI

COMMON

R62

0ohm

DNI

0402

0.05 ohm

I2CS_SCL

I2CS_SDA

34

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

C815 0.22uF

6.3V

0402

10%

X7R

C796

0.22uF

6.3V0402

10%

X7R

C792 0.22uF

6.3V0402

10%

X7R

C776 0.22uF

6.3V0402

10%

X7R

C750 0.22uF

6.3V0402

10%

X7R

C738 0.22uF

6.3V

0402

10%

X7R

C727 0.22uF

6.3V0402

10%

X7R

C714 0.22uF

6.3V

0402

10%

X7R

C699 0.22uF

6.3V

0402

10%

X7R

C688 0.22uF

6.3V

0402

10%

X7R

C674 0.22uF

6.3V

0402

10%

X7R

C655 0.22uF

6.3V

0402

10%

X7R

C649 0.22uF

6.3V

0402

10%

X7R

C647 0.22uF

6.3V

0402

10%

X7R

C645 0.22uF

6.3V0402

10%

X7R

C641 0.22uF

6.3V

0402

10%

X7R

C816

0402

C797

C793

C777

0402

C748 0.22uF

C731

0402

C722

C710

C697

0402

C683

0402

C669

C652

0402

C648

0402

C646

C643

0402

C640

0402

C E

0.22uF

6.3V

0.22uF

6.3V0402

0.22uF

6.3V0402

0.22uF

6.3V

6.3V0402

0.22uF

6.3V

0.22uF

6.3V0402

0.22uF

6.3V0402

0.22uF

6.3V

0.22uF

6.3V

0.22uF

6.3V0402

0.22uF

6.3V

0.22uF

6.3V

0.22uF

6.3V0402

0.22uF

6.3V

0.22uF

6.3V

ASSEMBLY

PAGE DETAIL

OUT

OUT

IN

PEX_TX0

PEX_TX0*

10%

COMMON

X7R

PEX_TX1

PEX_TX1*

10%

COMMON

X7R

PEX_TX2

PEX_TX2*

10%

COMMON

X7R

PEX_TX3

PEX_TX3*

10%

COMMON

X7R

PEX_TX4

PEX_TX4*

10%

COMMON

X7R

PEX_TX5

PEX_TX5*

10%

COMMON

X7R

PEX_TX6

PEX_TX6*

10%

COMMON

X7R

PEX_TX7

PEX_TX7*

10%

COMMON

X7R

PEX_TX8

PEX_TX8*

10%

COMMON

X7R

PEX_TX9

PEX_TX9*

10%

COMMON

X7R

PEX_TX10

PEX_TX10*

10%

COMMON

X7R

PEX_TX11

PEX_TX11*

10%

COMMON

X7R

PEX_TX12

PEX_TX12*

10%

COMMON

X7R

PEX_TX13

PEX_TX13*

10%

COMMON

X7R

PEX_TX14

PEX_TX14*

10%

COMMON

X7R

PEX_TX15

PEX_TX15*

10%

COMMON

X7R

23

23

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

BASE LEVEL GENERIC SCHEMATIC ONLY

PCI Express

3V3_F

R1132

10k

5 %

0402

DNI

G1A

@digital.u_gpu_gb3b_256(sym_1):page3_i849

BGA1745

COMMON

1/21 PCI_EXPRESS

BJ21

PEX_WAKE

BE20

PEX_RST

BB20

PEX_CLKREQ

BD20

PEX_REFCLK

BC20

PEX_REFCLK

BC21

PEX_TX0

BD21

PEX_TX0

BH21

PEX_RX0

BG21

PEX_RX0

BE22

PEX_TX1

BE23

PEX_TX1

BG23

PEX_RX1

BH23

PEX_RX1

BD23

PEX_TX2

BC23

PEX_TX2

BJ23

PEX_RX2

BJ24

PEX_RX2

BC24

PEX_TX3

BD24

PEX_TX3

BH24

PEX_RX3

BG24

PEX_RX3

BE26

PEX_TX4

BE25

PEX_TX4

BG26

PEX_RX4

BH26

PEX_RX4

BD26

PEX_TX5

BC26

PEX_TX5

BJ26

PEX_RX5

BJ27

PEX_RX5

BC27

PEX_TX6

BD27

PEX_TX6

BH27

PEX_RX6

BG27

PEX_RX6

BE28

PEX_TX7

BE29

PEX_TX7

BG29

PEX_RX7

BH29

PEX_RX7

BD29

PEX_TX8

BC29

PEX_TX8

BJ29

PEX_RX8

BJ30

PEX_RX8

BC30

PEX_TX9

BD30

PEX_TX9

BH30

PEX_RX9

BG30

PEX_RX9

BE31

PEX_TX10

BE32

PEX_TX10

BG32

PEX_RX10

BH32

PEX_RX10

BD32

PEX_TX11

BC32

PEX_TX11

BJ32

PEX_RX11

BJ33

PEX_RX11

BC33

PEX_TX12

BD33

PEX_TX12

BH33

PEX_RX12

BG33

PEX_RX12

BE34

PEX_TX13

BE35

PEX_TX13

BG35

PEX_RX13

BH35

PEX_RX13

BD35

PEX_TX14

BC35

PEX_TX14

BJ35

PEX_RX14

BJ36

PEX_RX14

BC36

PEX_TX15

BD36

PEX_TX15

BH36

PEX_RX15

BG36

PEX_RX15

PEX_RST*

PEX_RST_MCU*

3V3_F

5

1

2

3

GND

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_PLL_HVDD

PEX_SVDD_3V3

NVVDD_SENSE

GND_SENSE

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_PLLVDD

TESTMODE

PEX_TERMP

R1146

FDBA

0402

0.05 ohm

U52

INS16823418

4

SC70-5

DNI

0ohm

COMMON

MSI

MSI

C715

4.7uF

6.3V

20%

X5R

0603

COMMON

C718

4.7uF

6.3V

20%

X5R

0603

COMMON

MSI

C1189

0.1uF

16V

10%

X7R

PEX_RST_BUF*

0402

DNI

GND

R1152

10k

5 %

0402

DNI

GND

Place near balls

AW33

AY32

C709

C694

AY33

1uF

AY35

6.3V

BA33

10%

BA35

X5R

BB33

0402

COMMON

AY24

AY26

C707

AY27

1uF

AY29

6.3V

AY30

10%

BA24

X5R

BA26

0402

COMMON

BA27

BA29

BA30

BA32

BB24

BB27

BB30

1uF

6.3V

10%

X5R

0402

COMMON

C684

1uF

6.3V

10%

X5R

0402

COMMON

C696

1uF

6.3V

10%

X5R

0402

COMMON

C682

1uF

6.3V

10%

X5R

0402

COMMON

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-V317

MS-V317

PCIE

PCIE

PCIE

Place between

GPU and PS

MS-V317

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Wednesday, August 20, 2014

Wednesday, August 20, 2014

Wednesday, August 20, 2014

PEX_VDD

C102

10uF

6.3V

20%

X5R

0805

COMMON

C634

10uF

6.3V

20%

X5R

0805LP

COMMON

C108

22uF

6.3V

20%

X5R

0805

COMMON

C630

22uF

6.3V

20%

X5R

0805LP

COMMON

C109

10uF

6.3V

20%

X5R

0805

COMMON

C100

10uF

6.3V

20%

X5R

0805

COMMON

GND

PEX_VDD

GND

C642

22uF

6.3V

20%

X5R

0805LP

COMMON

C633

22uF

6.3V

20%

X5R

0805LP

COMMON

1.0

1.0

1.0

337

337

337

1

2

3V3_RUN

AW30

AW32

AY23

AW23

NVVDD_SENSE

GND_SENSE

C687

0.1uF

16V

10%

X7R

0402

COMMON

C693

C808

4.7uF

6.3V

20%

X5R

0603

COMMON

C822

4.7uF

6.3V

20%

X5R

0603

COMMON

GND

27

27

0.1uF

16V

10%

X7R

0402

COMMON

OUT

OUT

3

4

R631

BH38

BG38

AW26

BA23

BJ38

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT*

GPU_TESTMODE

PEX_TERMP

PEX_PLL_CLK

PEX_PLL_CLK

PLLVDD now requires decap only

R83 10k

COMMON

0402

5 %

R630 2.49k

COMMON

0402

1 %

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

GND

GND

G

200ohm

5 %

0402

DNI

C85

C84

1uF

0.1uF

16V

6.3V

10%

10%

X7R

X5R

0402

0402

COMMON

COMMON

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-1G401-BASE-QS1

PG401-A02

PCB REV

A

BOM REV

PEX_VDD

GND

C91

4.7uF

6.3V

20%

X5R

0603

COMMON

5

3 OF 37

PAGE

DATE

04-AUG-2014

H

Page 4

A B C D E F G H

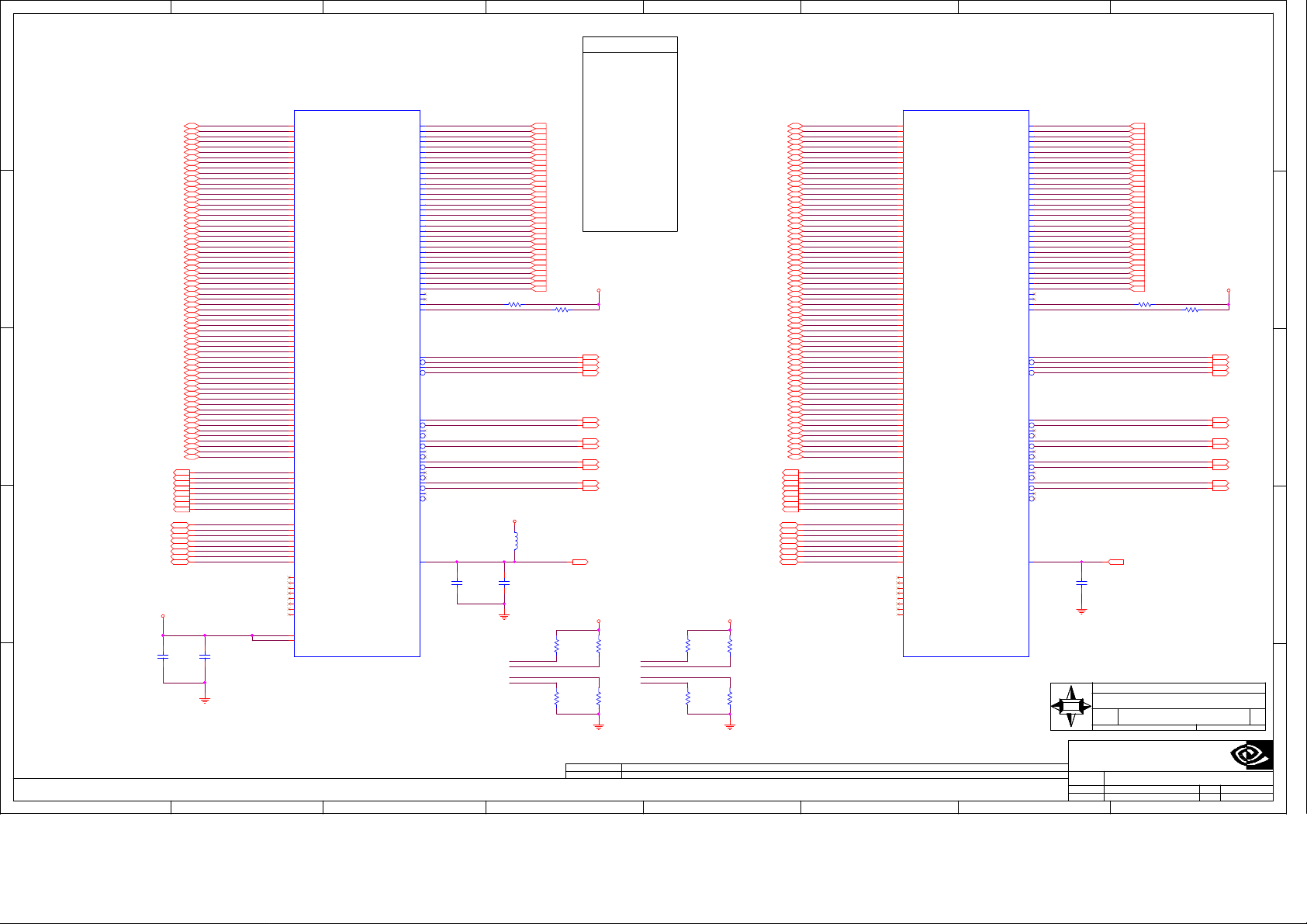

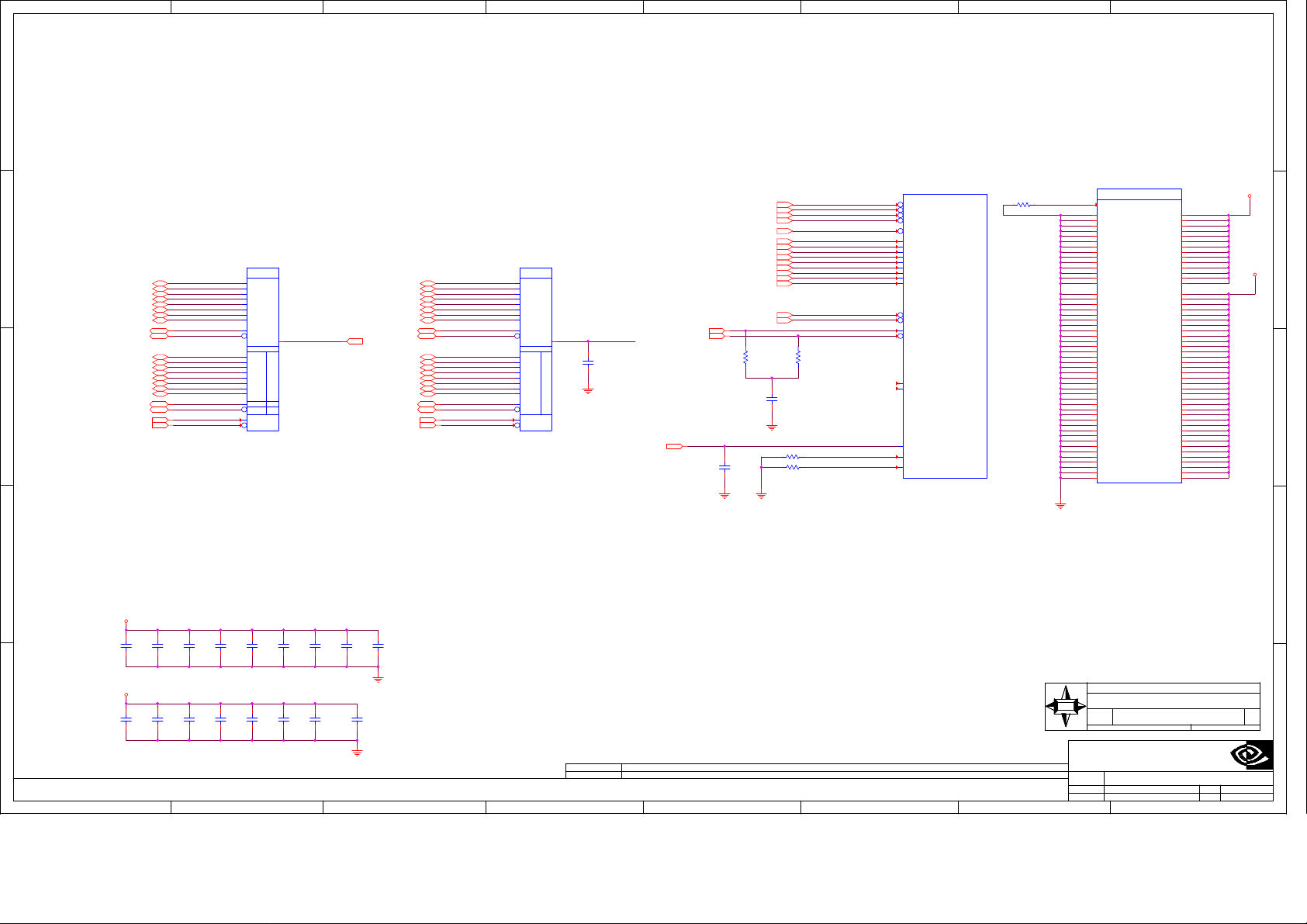

Page4: MEMORY: GPU Partition A/B

1

5

Fba_D<0>

5

Fba_D<1>

5

Fba_D<2>

5

Fba_D<3>

5

Fba_D<4>

5

Fba_D<5>

5

Fba_D<6>

5

Fba_D<7>

5

Fba_D<8>

5

Fba_D<9>

5

Fba_D<10>

5

Fba_D<11>

5

Fba_D<12>

5

Fba_D<13>

5

Fba_D<14>

5

Fba_D<15>

5

Fba_D<16>

5

Fba_D<17>

5

Fba_D<18>

5

Fba_D<19>

5

Fba_D<20>

5

Fba_D<21>

5

2

3

5

5

5

5

06

06

4

06

06

Fba_D<22>

5

Fba_D<23>

5

Fba_D<24>

5

Fba_D<25>

5

Fba_D<26>

5

Fba_D<27>

5

Fba_D<28>

5

Fba_D<29>

5

Fba_D<30>

5

Fba_D<31>

06

Fba_D<32>

06

Fba_D<33>

06

Fba_D<34>

06

Fba_D<35>

06

Fba_D<36>

06

Fba_D<37>

06

Fba_D<38>

06

Fba_D<39>

06

Fba_D<40>

06

Fba_D<41>

06

Fba_D<42>

06

Fba_D<43>

06

Fba_D<44>

06

Fba_D<45>

06

Fba_D<46>

06

Fba_D<47>

06

Fba_D<48>

06

Fba_D<49>

06

Fba_D<50>

06

Fba_D<51>

06

Fba_D<52>

06

Fba_D<53>

06

Fba_D<54>

06

Fba_D<55>

06

Fba_D<56>

06

Fba_D<57>

06

Fba_D<58>

06

Fba_D<59>

06

Fba_D<60>

06

Fba_D<61>

06

Fba_D<62>

06

Fba_D<63>

5

5

5

5

06

06

06

06

1V_PLL

C653

0.1uF

16V

10%

X7R

0402

COMMON

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

FBA_D<0>

0

FBA_D<1>

1

FBA_D<2>

2

FBA_D<3>

3

FBA_D<4>

4

FBA_D<5>

5

FBA_D<6>

6

FBA_D<7>

7

FBA_D<8>

8

FBA_D<9>

9

FBA_D<10>

10

FBA_D<11>

11

FBA_D<12>

12

FBA_D<13>

13

FBA_D<14>

14

FBA_D<15>

15

FBA_D<16>

16

FBA_D<17>

17

FBA_D<18>

18

FBA_D<19>

19

FBA_D<20>

20

FBA_D<21>

21

FBA_D<22>

22

FBA_D<23>

23

FBA_D<24>

24

FBA_D<25>

25

FBA_D<26>

26

FBA_D<27>

27

FBA_D<28>

28

FBA_D<29>

29

FBA_D<30>

30

FBA_D<31>

31

FBA_D<32>

32

FBA_D<33>

33

FBA_D<34>

34

FBA_D<35>

35

FBA_D<36>

36

FBA_D<37>

37

FBA_D<38>

38

FBA_D<39>

39

FBA_D<40>

40

FBA_D<41>

41

FBA_D<42>

42

FBA_D<43>

43

FBA_D<44>

44

FBA_D<45>

45

FBA_D<46>

46

FBA_D<47>

47

FBA_D<48>

48

FBA_D<49>

49

FBA_D<50>

50

FBA_D<51>

51

FBA_D<52>

52

FBA_D<53>

53

FBA_D<54>

54

FBA_D<55>

55

FBA_D<56>

56

FBA_D<57>

57

FBA_D<58>

58

FBA_D<59>

59

FBA_D<60>

60

FBA_D<61>

61

FBA_D<62>

62

FBA_D<63>

63

FBA_DBI<0>

0

FBA_DBI<1>

1

FBA_DBI<2>

2

FBA_DBI<3>

3

FBA_DBI<4>

4

FBA_DBI<5>

5

FBA_DBI<6>

6

FBA_DBI<7>

7

FBA_EDC<0>

0

FBA_EDC<1>

1

FBA_EDC<2>

2

FBA_EDC<3>

3

FBA_EDC<4>

4

FBA_EDC<5>

5

FBA_EDC<6>

6

FBA_EDC<7>

7

C725

0.1uF

16V

10%

X7R

0402

COMMON

GND

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

G1B

@digital.u_gpu_gb3b_256(sym_2):page4_i1879

BGA1745

COMMON

2/21 FBA

V43

FBA_D0

V41

FBA_D1

V44

FBA_D2

V42

FBA_D3

U43

FBA_D4

U44

FBA_D5

U41

FBA_D6

U42

FBA_D7

AA46

FBA_D8

AC46

FBA_D9

AA45

FBA_D10

AA47

FBA_D11

Y46

FBA_D12

Y49

FBA_D13

Y45

FBA_D14

Y48

FBA_D15

AJ46

FBA_D16

AG47

FBA_D17

AG46

FBA_D18

AG45

FBA_D19

AF44

FBA_D20

AF45

FBA_D21

AD46

FBA_D22

AD45

FBA_D23

AD44

FBA_D24

AD43

FBA_D25

AD42

FBA_D26

AC42

FBA_D27

AA44

FBA_D28

AA43

FBA_D29

AA42

FBA_D30

AA40

FBA_D31

AT48

FBA_D32

AT46

FBA_D33

AT49

FBA_D34

AT47

FBA_D35

AW47

FBA_D36

AW48

FBA_D37

BA47

FBA_D38

AW46

FBA_D39

AR46

FBA_D40

AN45

FBA_D41

AR49

FBA_D42

AR48

FBA_D43

AT45

FBA_D44

AR44

FBA_D45

AN41

FBA_D46

AN42

FBA_D47

AG40

FBA_D48

AG43

FBA_D49

AG41

FBA_D50

AJ43

FBA_D51

AJ40

FBA_D52

AK40

FBA_D53

AK42

FBA_D54

AK41

FBA_D55

AK45

FBA_D56

AK43

FBA_D57

AK48

FBA_D58

AK49

FBA_D59

AM45

FBA_D60

AM44

FBA_D61

AK44

FBA_D62

AM43

FBA_D63

U40

FBA_DQM0

AC45

FBA_DQM1

AG44

FBA_DQM2

AA41

FBA_DQM3

AV45

FBA_DQM4

AR45

FBA_DQM5

AG42

FBA_DQM6

AM46

FBA_DQM7

U45

FBA_DQS_WP0

Y43

FBA_DQS_WP1

AF42

FBA_DQS_WP2

AC44

FBA_DQS_WP3

AV47

FBA_DQS_WP4

AN43

FBA_DQS_WP5

AJ42

FBA_DQS_WP6

AK47

FBA_DQS_WP7

U46

FBA_DQS_RN0

Y44

FBA_DQS_RN1

AF43

FBA_DQS_RN2

AC43

FBA_DQS_RN3

AV46

FBA_DQS_RN4

AN44

FBA_DQS_RN5

AJ41

FBA_DQS_RN6

AK46

FBA_DQS_RN7

AC39

FB_REFPLL_DLL_AVDD0

L21

FB_REFPLL_DLL_AVDD1

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CMD31

FBA_CMD32

FBA_CMD33

FBA_CMD34

FBA_CMD35

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_WCK01

FBA_WCK01

FBA_WCKB01

FBA_WCKB01

FBA_WCK23

FBA_WCK23

FBA_WCKB23

FBA_WCKB23

FBA_WCK45

FBA_WCK45

FBA_WCKB45

FBA_WCKB45

FBA_WCK67

FBA_WCK67

FBA_WCKB67

FBA_WCKB67

U48

U49

V48

V49

V47

AA49

AA48

AC48

AC49

AC47

AD49

AD48

AD47

AF47

AF48

BB49

BA48

BA49

AW49

AV48

AV49

AN48

AN49

AM47

AM49

AM48

AJ47

AJ49

AJ48

AG48

AG49

AF49

AF46

Y47

AR47

AF41

AF40

AJ44

AJ45

V46

V45

Y42

Y41

AD41

AD40

AC41

AC40

AT44

AT43

AR43

AR42

AM42

AM41

AN47

AN46

FBA_CMD<1>

FBA_CMD<2>

FBA_CMD<3>

FBA_CMD<4>

FBA_CMD<5>

FBA_CMD<6>

FBA_CMD<7>

FBA_CMD<8>

FBA_CMD<9>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<12>

FBA_CMD<13>

FBA_CMD<14>

FBA_CMD<15>

FBA_CMD<16>

FBA_CMD<17>

FBA_CMD<18>

FBA_CMD<19>

FBA_CMD<20>

FBA_CMD<21>

FBA_CMD<22>

FBA_CMD<23>

FBA_CMD<24>

FBA_CMD<25>

FBA_CMD<26>

FBA_CMD<27>

FBA_CMD<28>

FBA_CMD<29>

FBA_CMD<30>

FBA_CMD<31>

FBA_DEBUG0

FBA_DEBUG1

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBA_WCK01

FBA_WCK01*

FBA_WCK23

FBA_WCK23*

FBA_WCK45

FBA_WCK45*

FBA_WCK67

FBA_WCK67*

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

R622 60.4ohm

0402 DNI

1 %

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_WCK01

FBA_WCK01

FBA_WCK23

FBA_WCK23

FBA_WCK45

FBA_WCK45

FBA_WCK67

FBA_WCK67

FB_CLK

FB_CLK

FB_CLK

FB_CLK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FBA_CMD<0>

FBA_CMD<1>

FBA_CMD<2>

FBA_CMD<3>

FBA_CMD<4>

FBA_CMD<5>

FBA_CMD<6>

FBA_CMD<7>

FBA_CMD<8>

FBA_CMD<9>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<12>

FBA_CMD<13>

FBA_CMD<14>

FBA_CMD<15>

FBA_CMD<16>

FBA_CMD<17>

FBA_CMD<18>

FBA_CMD<19>

FBA_CMD<20>

FBA_CMD<21>

FBA_CMD<22>

FBA_CMD<23>

FBA_CMD<24>

FBA_CMD<25>

FBA_CMD<26>

FBA_CMD<27>

FBA_CMD<28>

FBA_CMD<29>

FBA_CMD<30>

FBA_CMD<31>

R623

0402

1 %

60.4ohm

DNI

FBA_CMD<0>

U47

3V3_RUN

LB501

30ohm

COMMON

BEAD_0603

FBA_PLL_AVDD

AJ39

C820

0.1uF

16V

10%

X7R

0402

COMMON

3V3_PLL 3V3_PLL

C823

22uF

6.3V

20%

X5R

0805LP

COMMON

GND

R596

10k

5 %

0402

FBA_CMD<1>

FBA_CMD<17>

FBA_CMD<2>

FBA_CMD<18>

COMMON

R616

10k

5 %

0402

COMMON

C E

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

ASSEMBLY

PAGE DETAIL

GDDR5 CMD Mapping

CMD0

CMD1

CMD2

CMD3

CMD4

CMD5

CMD6

CMD8

CMD9

CMD10 WE*

CMD11

CMD12

5

CMD13

5

CMD14

5

CMD15

5

CMD16

5

CMD17

5

CMD18

5

CMD19

5

CMD20

5

CMD21

5

CMD22

5

CMD23

5

CMD24

5

CMD25

5

CMD26

5

CMD27

5

CMD28

06

CMD29

06

CMD30

06

CMD31

06

06

06

06

06

06

06

06

06

06

06

06

FBVDDQ

06

FBVDDQ

R595

10k

5 %

0402

COMMON

R614

10k

5 %

0402

COMMON

GND

CAS*

CKE*

RST*

RAS*

A1_A9

A0_A10

A12_RFU

ABI*CMD7

A6_A11

A7_A8

A5_BA1

A4_BA2

A2_BA0

A3_BA3

CS*

32..630..31CMD

CAS*

CKE*

RST*

RAS*

A1_A9

A0_A10

A12_RFU

ABI*

A6_A11

A7_A8

WE*

A5_BA1

A4_BA2

A2_BA0

A3_BA3

CS*

5

5

06

06

5

5

5

5

06

06

06

06

4,09,16,17,18,20,21

R635

10k

5 %

0402

FBB_CMD<1>

FBB_CMD<17>

FBB_CMD<2>

FBB_CMD<18>

BASE LEVEL GENERIC SCHEMATIC ONLY

MEMORY: GPU Partition A/B

COMMON

R617

10k

5 %

0402

COMMON

G1C

@digital.u_gpu_gb3b_256(sym_3):page4_i1880

BGA1745

COMMON

07

Fbb_D<0>

07

Fbb_D<1>

07

Fbb_D<2>

07

Fbb_D<3>

07

Fbb_D<4>

07

Fbb_D<5>

07

Fbb_D<6>

07

Fbb_D<7>

07

Fbb_D<8>

07

Fbb_D<9>

07

Fbb_D<10>

07

Fbb_D<11>

07

Fbb_D<12>

07

Fbb_D<13>

07

Fbb_D<14>

07

Fbb_D<15>

07

Fbb_D<16>

07

Fbb_D<17>

07

Fbb_D<18>

07

Fbb_D<19>

07

Fbb_D<20>

07

Fbb_D<21>

07

Fbb_D<22>

07

Fbb_D<23>

07

Fbb_D<24>

07

Fbb_D<25>

07

Fbb_D<26>

07

Fbb_D<27>

07

Fbb_D<28>

07

Fbb_D<29>

07

Fbb_D<30>

07

Fbb_D<31>

8

Fbb_D<32>

8

Fbb_D<33>

8

Fbb_D<34>

8

Fbb_D<35>

8

Fbb_D<36>

8

Fbb_D<37>

8

Fbb_D<38>

8

Fbb_D<39>

8

Fbb_D<40>

8

Fbb_D<41>

8

Fbb_D<42>

8

Fbb_D<43>

8

Fbb_D<44>

8

Fbb_D<45>

8

Fbb_D<46>

8

Fbb_D<47>

8

Fbb_D<48>

8

Fbb_D<49>

8

Fbb_D<50>

8

Fbb_D<51>

8

Fbb_D<52>

8

Fbb_D<53>

8

Fbb_D<54>

8

Fbb_D<55>

8

Fbb_D<56>

8

Fbb_D<57>

8

Fbb_D<58>

8

Fbb_D<59>

8

Fbb_D<60>

8

Fbb_D<61>

8

Fbb_D<62>

8

Fbb_D<63>

07

07

07

07

8

8

8

8

07

07

07

07

8

8

8

8

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

FBB_D<0>

0

FBB_D<1>

1

FBB_D<2>

2

FBB_D<3>

3

FBB_D<4>

4

FBB_D<5>

5

FBB_D<6>

6

FBB_D<7>

7

FBB_D<8>

8

FBB_D<9>

9

FBB_D<10>

10

FBB_D<11>

11

FBB_D<12>

12

FBB_D<13>

13

FBB_D<14>

14

FBB_D<15>

15

FBB_D<16>

16

FBB_D<17>

17

FBB_D<18>

18

FBB_D<19>

19

FBB_D<20>

20

FBB_D<21>

21

FBB_D<22>

22

FBB_D<23>

23

FBB_D<24>

24

FBB_D<25>

25

FBB_D<26>

26

FBB_D<27>

27

FBB_D<28>

28

FBB_D<29>

29

FBB_D<30>

30

FBB_D<31>

31

FBB_D<32>

32

FBB_D<33>

33

FBB_D<34>

34

FBB_D<35>

35

FBB_D<36>

36

FBB_D<37>

37

FBB_D<38>

38

FBB_D<39>

39

FBB_D<40>

40

FBB_D<41>

41

FBB_D<42>

42

FBB_D<43>

43

FBB_D<44>

44

FBB_D<45>

45

FBB_D<46>

46

FBB_D<47>

47

FBB_D<48>

48

FBB_D<49>

49

FBB_D<50>

50

FBB_D<51>

51

FBB_D<52>

52

FBB_D<53>

53

FBB_D<54>

54

FBB_D<55>

55

FBB_D<56>

56

FBB_D<57>

57

FBB_D<58>

58

FBB_D<59>

59

FBB_D<60>

60

FBB_D<61>

61

FBB_D<62>

62

FBB_D<63>

63

FBB_DBI<0>

0

FBB_DBI<1>

1

FBB_DBI<2>

2

FBB_DBI<3>

3

FBB_DBI<4>

4

FBB_DBI<5>

5

FBB_DBI<6>

6

FBB_DBI<7>

7

FBB_EDC<0>

0

FBB_EDC<1>

1

FBB_EDC<2>

2

FBB_EDC<3>

3

FBB_EDC<4>

4

FBB_EDC<5>

5

FBB_EDC<6>

6

FBB_EDC<7>

7

FBVDDQ

R594

10k

5 %

0402

COMMON

R634

10k

5 %

0402

COMMON

GND

3/21 FBB

D30

G30

E30

F30

G29

F29

J29

H29

C33

E33

F33

D33

C30

K33

E32

D32

H39

G39

F39

D41

F38

G38

D38

E38

F36

K35

E36

D36

G35

F35

D35

E35

M44

P42

M43

P43

R45

R46

R43

R44

M47

P44

M46

M45

P47

P49

P45

P46

F46

E47

D47

D48

F48

H46

H47

H48

L45

L44

J46

H49

L47

J49

L48

L49

E29

G33

H38

C36

P41

P48

F47

L46

J30

H33

D39

J35

R42

M48

F49

J47

H30

J33

E39

H35

R41

M49

E49

J48

FBB_D0

FBB_D1

FBB_D2

FBB_D3

FBB_D4

FBB_D5

FBB_D6

FBB_D7

FBB_D8

FBB_D9

FBB_D10

FBB_D11

FBB_D12

FBB_D13

FBB_D14

FBB_D15

FBB_D16

FBB_D17

FBB_D18

FBB_D19

FBB_D20

FBB_D21

FBB_D22

FBB_D23

FBB_D24

FBB_D25

FBB_D26

FBB_D27

FBB_D28

FBB_D29

FBB_D30

FBB_D31

FBB_D32

FBB_D33

FBB_D34

FBB_D35

FBB_D36

FBB_D37

FBB_D38

FBB_D39

FBB_D40

FBB_D41

FBB_D42

FBB_D43

FBB_D44

FBB_D45

FBB_D46

FBB_D47

FBB_D48

FBB_D49

FBB_D50

FBB_D51

FBB_D52

FBB_D53

FBB_D54

FBB_D55

FBB_D56

FBB_D57

FBB_D58

FBB_D59

FBB_D60

FBB_D61

FBB_D62

FBB_D63

FBB_DQM0

FBB_DQM1

FBB_DQM2

FBB_DQM3

FBB_DQM4

FBB_DQM5

FBB_DQM6

FBB_DQM7

FBB_DQS_WP0

FBB_DQS_WP1

FBB_DQS_WP2

FBB_DQS_WP3

FBB_DQS_WP4

FBB_DQS_WP5

FBB_DQS_WP6

FBB_DQS_WP7

FBB_DQS_RN0

FBB_DQS_RN1

FBB_DQS_RN2

FBB_DQS_RN3

FBB_DQS_RN4

FBB_DQS_RN5

FBB_DQS_RN6

FBB_DQS_RN7

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD28

FBB_CMD29

FBB_CMD30

FBB_CMD31

FBB_CMD32

FBB_CMD33

FBB_CMD34

FBB_CMD35

FBB_CLK0

FBB_CLK0

FBB_CLK1

FBB_CLK1

FBB_WCK01

FBB_WCK01

FBB_WCKB01

FBB_WCKB01

FBB_WCK23

FBB_WCK23

FBB_WCKB23

FBB_WCKB23

FBB_WCK45

FBB_WCK45

FBB_WCKB45

FBB_WCKB45

FBB_WCK67

FBB_WCK67

FBB_WCKB67

FBB_WCKB67

FBB_PLL_AVDD

FDBA

FBB_CMD<0>

C29

FBB_CMD<1>

B29

FBB_CMD<2>

A29

FBB_CMD<3>

A30

FBB_CMD<4>

B30

FBB_CMD<5>

B32

FBB_CMD<6>

A32

FBB_CMD<7>

C32

FBB_CMD<8>

A33

FBB_CMD<9>

B33

FBB_CMD<10>

B35

FBB_CMD<11>

A35

FBB_CMD<12>

C35

FBB_CMD<13>

A36

FBB_CMD<14>

B36

FBB_CMD<15>

B38

FBB_CMD<16>

D49

FBB_CMD<17>

C48

FBB_CMD<18>

B46

FBB_CMD<19>

A46

FBB_CMD<20>

A45

FBB_CMD<21>

C44

FBB_CMD<22>

A44

FBB_CMD<23>

B44

FBB_CMD<24>

C42

FBB_CMD<25>

B42

FBB_CMD<26>

A42

FBB_CMD<27>

A41

FBB_CMD<28>

B41

FBB_CMD<29>

C39

FBB_CMD<30>

B39

FBB_CMD<31>

A39

A38

C38

FBB_DEBUG0

D29

FBB_DEBUG1

C41

FBB_CLK0

E41

FBB_CLK0*

F41

FBB_CLK1

E42

FBB_CLK1*

D42

FBB_WCK01

F32

FBB_WCK01*

G32

H32

J32

FBB_WCK23

G36

FBB_WCK23*

H36

K36

J36

FBB_WCK45

M42

FBB_WCK45*

M41

L42

L43

FBB_WCK67

H45

FBB_WCK67*

H44

J45

J44

L36

GND

MSI

MSI

MSI

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

PCB REV

BOM REV

G

Fbb_Cmd<0>

Fbb_Cmd<1>

Fbb_Cmd<2>

Fbb_Cmd<3>

Fbb_Cmd<4>

Fbb_Cmd<5>

Fbb_Cmd<6>

Fbb_Cmd<7>

Fbb_Cmd<8>

Fbb_Cmd<9>

Fbb_Cmd<10>

Fbb_Cmd<11>

Fbb_Cmd<12>

Fbb_Cmd<13>

Fbb_Cmd<14>

Fbb_Cmd<15>

Fbb_Cmd<16>

Fbb_Cmd<17>

Fbb_Cmd<18>

Fbb_Cmd<19>

Fbb_Cmd<20>

Fbb_Cmd<21>

Fbb_Cmd<22>

Fbb_Cmd<23>

Fbb_Cmd<24>

Fbb_Cmd<25>

Fbb_Cmd<26>

Fbb_Cmd<27>

Fbb_Cmd<28>

Fbb_Cmd<29>

Fbb_Cmd<30>

Fbb_Cmd<31>

1 %

FB_CLK

FB_CLK

FB_CLK

FB_CLK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

MS-V317

MS-V317

MS-V317

07

07

07

07

07

07

07

07

07

07

07

07

07

07

07

07

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

R629 60.4ohm

0402 DNI

1 %

4,09,16,17,18,20,21

H

FBVDDQ

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

Sheet ofDate:

437

Sheet ofDate:

437

Sheet ofDate:

437

PAGE

DATE

4 OF 37

04-AUG-2014

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

R641 60.4ohm

0402 DNI

FBB_CLK0

FBB_CLK0

FBB_CLK1

FBB_CLK1

FBB_WCK01

FBB_WCK01

FBB_WCK23

FBB_WCK23

FBB_WCK45

FBB_WCK45

FBB_WCK67

FBB_WCK67

IN

C654

0.1uF

16V

10%

X7R

0402

COMMON

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

MEMORY: GPU Partition A/B

MEMORY: GPU Partition A/B

MEMORY: GPU Partition A/B

Wednesday, August 20, 2014

Wednesday, August 20, 2014

Wednesday, August 20, 2014

600-1G401-BASE-QS1

PG401-A02

A

1

2

07

07

8

8

3

07

07

07

07

8

8

8

8

4

1.0

1.0

1.0

5

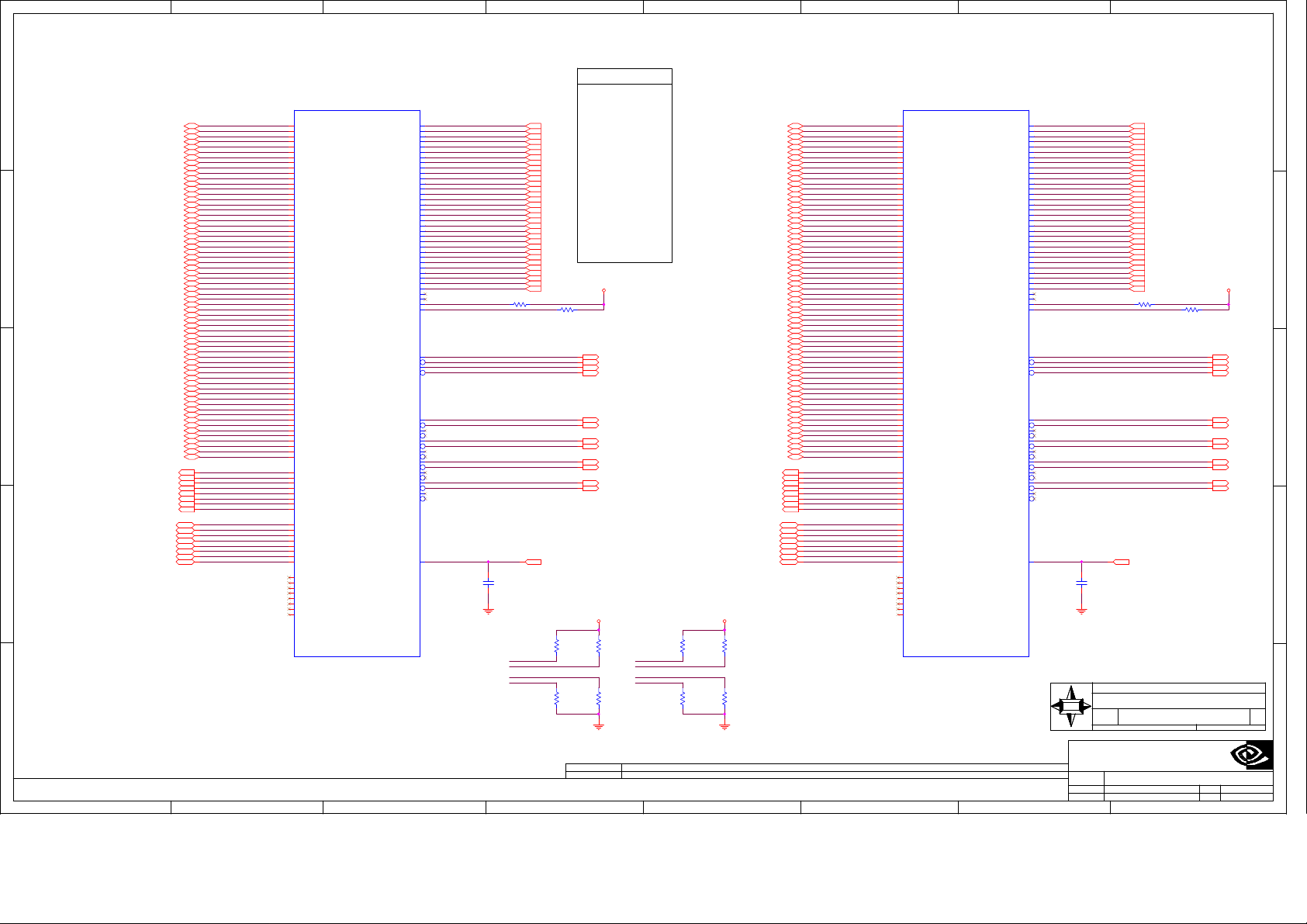

Page 5

A B C D E F G H

Page5: MEMORY: FBA Partition 31..0

1

GND

M7C

@memory.u_mem_sd_ddr5_x32(sym_7):page5_i361

BGA170_MIRR

COMMON

Mirrored

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

SOE*/MF_VDD

add 1k to VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

FBVDDQ

R600

FBA_MF1_A

J1

C10

VDD

C5

VDD

D11

VDD

G1

VDD

G11

VDD

G14

VDD

G4

VDD

L1

VDD

L11

VDD

L14

VDD

L4

VDD

P11

VDD

R10

VDD

R5

VDD

B1

B12

B14

B3

D1

D12

D14

D3

E10

E5

F1

F12

F14

F3

G13

G2

H12

H3

K12

K3

L13

L2

M1

M12

M14

M3

N10

N5

P1

P12

P14

P3

T1

T12

T14

T3

1k

0402 COMMON

1 %

FBVDDQ

M7B

@memory.u_mem_sd_ddr5_x32(sym_5):page5_i360

BGA170_MIRR

M7D

@memory.u_mem_sd_ddr5_x32(sym_2):page5_i358

BGA170_MIRR

2

4

Fba_D<0>

4

Fba_D<1>

4

Fba_D<2>

4

Fba_D<3>

4

Fba_D<4>

4

Fba_D<5>

4

Fba_D<6>

4

Fba_D<7>

4

4

4

Fba_D<8>

4

Fba_D<9>

4

Fba_D<10>

4

Fba_D<11>

4

Fba_D<12>

4

Fba_D<13>

4

Fba_D<14>

4

Fba_D<15>

4

4

3

4

4

FBA_D<0>

0

FBA_D<1>

1

FBA_D<2>

2

FBA_D<3>

3

FBA_D<4>

4

FBA_D<5>

5

FBA_D<6>

6

FBA_D<7>

7

FBA_EDC<0>

BI

FBA_DBI<0>

BI

FBA_D<8>

8

FBA_D<9>

9

FBA_D<10>

10

FBA_D<11>

11

FBA_D<12>

12

FBA_D<13>

13

FBA_D<14>

14

FBA_D<15>

15

FBA_EDC<1>

BI

FBA_DBI<1>

BI

FBA_WCK01

IN

FBA_WCK01*

IN

COMMON

MIRRORED

x16x32

V4

DQ0

NC

4

V2

DQ1

NC

T4

DQ2

NC

T2

DQ3

NC

N4

DQ4

NC

N2

DQ5

NC

M4

DQ6

NC

M2

DQ7

NC

R2

EDC0

NC

P2

DBI0

NC

V10

VREFD

V11

DQ8

V13

DQ9

T11

DQ10

T13

DQ11

N11

DQ12

N13

DQ13

M11

DQ14

M13

DQ15

R13

EDC1

P13

DBI1

P4

WCK01

P5

WCK01

Fba_D<16>

4

Fba_D<17>

4

Fba_D<18>

4

Fba_D<19>

4

Fba_D<20>

4

Fba_D<21>

4

Fba_D<22>

4

Fba_D<23>

4

4

FBA_VREFD

4

Fba_D<24>

4

Fba_D<25>

4

Fba_D<26>

4

Fba_D<27>

4

Fba_D<28>

4

Fba_D<29>

4

Fba_D<30>

4

Fba_D<31>

4

4

4

4

FBA_D<16>

16

FBA_D<17>

17

FBA_D<18>

18

FBA_D<19>

19

FBA_D<20>

20

FBA_D<21>

21

FBA_D<22>

22

FBA_D<23>

23

FBA_EDC<2>

BI

FBA_DBI<2>

BI

FBA_D<24>

24

FBA_D<25>

25

FBA_D<26>

26

FBA_D<27>

27

FBA_D<28>

28

FBA_D<29>

29

FBA_D<30>

30

FBA_D<31>

31

FBA_EDC<3>

BI

FBA_DBI<3>

BI

FBA_WCK23

IN

FBA_WCK23*

IN

07,10,12,23

IN

M7A

@memory.u_mem_sd_ddr5_x32(sym_4):page5_i359

BGA170_MIRR

COMMON

MIRRORED

x32 x16

A11

DQ16

A13

DQ17

B11

DQ18

B13

DQ19

E11

DQ20

E13

DQ21

F11

DQ22

F13

DQ23

C13

EDC2

D13

DBI2

A4

DQ24

A2

DQ25

B4

DQ26

B2

DQ27

E4

DQ28

E2

DQ29

F4

DQ30

F2

DQ31

C2

EDC3

D2

DBI3

D4

WCK23

D5

WCK23

GPIO10_FBVREF_SEL

VREFD

NC

NC

NC

NC

NC

NC

NC

NC

GND

NC

A10

GND GND

C137

820pF

50V

10%

X7R

0402

COMMON

0.140A1.05V

1G1D1S

FBVDDQ

R103

549ohm

1 %

0402

COMMON

R104

1.33k

1 %

0402

COMMON

3

D

Q15

@discrete.q_fet_n_enh(sym_2):page5_i328

SOT23_1G1D1S

G

1

COMMON

S

2

60V

0.26A

3000mohm@10V / 3000mohm@4.5V / 3000mohm@2.5V

0.31A

0.3W

20V

GND

FBA_VREFD

R102

931ohm

1 %

0402

COMMON

FBA_CMD<3>

4

C116

820pF

50V

10%

X7R

0402

COMMON

3

FBA_CMD<0>

4

0

FBA_CMD<10>

4

10

FBA_CMD<15>

4

15

FBA_CMD<7>

4

7

FBA_CMD<5>

4

5

FBA_CMD<4>

4

4

FBA_CMD<13>

4

13

FBA_CMD<14>

4

14

FBA_CMD<12>

4

12

FBA_CMD<11>

4

11

FBA_CMD<8>

4

8

FBA_CMD<9>

4

9

FBA_CMD<6>

4

6

FBA_CMD<2>

4

2

FBA_CMD<1>

4

1

R615

40.2ohm

1 %

0402

COMMON

C609

10nF

16V

10%

X7R

0402

COMMON

GND

OUT

FBA_VREFC

R605

0402 COMMON

R591

0402 COMMON

FBA_ZQ_1_B

121ohm

1 %

FBA_SEN_1

1k

1 %

GND

FBA_CMD<3>

FBA_CMD<0>

FBA_CMD<10>

FBA_CMD<15>

FBA_CMD<7>

FBA_CMD<5>

FBA_CMD<4>

FBA_CMD<13>

FBA_CMD<14>

FBA_CMD<12>

FBA_CMD<11>

FBA_CMD<8>

FBA_CMD<9>

FBA_CMD<6>

FBA_CMD<2>

FBA_CMD<1>

FBA_CLK0

IN

FBA_CLK0*

IN

R611

40.2ohm

1 %

0402

COMMON

FBA_CLK0_RC

0.350 1.05V

R94

931ohm

1 %

0402

COMMON

GND

4

4

FBA_VREF_Q

06

FBVDDQ

R93

549ohm

1 %

0402

COMMON

R89

1.33k

1 %

0402

COMMON

GND

OUT

1.05V

0.350

COMMON

L3

RAS

G3

CAS

G12

WE

L12

CS

J4

ABI

K4

A0_A10

K5

A1_A9

K11

A2_BA0

K10

A3_BA3

H11

A4_BA2

H10

A5_BA1

H5

A6_A11

H4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

06

J14

VREFC

J13

ZQ

J10

SEN

4

1

FBVDDQ

2

3

4

FBVDDQ

C601

C603

C586

C596

C624

10uF

4.7uF

6.3V

6.3V

20%

20%

X5R

X5R

0805LP

0603

COMMON

COMMON

FBVDDQ

C587

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

10uF

6.3V

20%

X5R

0805LP

COMMON

C130

4.7uF

6.3V

20%

X5R

0603

COMMON

4.7uF

6.3V

20%

X5R

0603

COMMON

C127

4.7uF

6.3V

20%

X5R

0603

COMMON

1uF

6.3V

10%

X5R

0402

COMMON

C120

1uF

6.3V

10%

X5R

0402

COMMON

1uF

6.3V

10%

X5R

0402

COMMON

C125

1uF

6.3V

10%

X5R

0402

COMMON

C619

1uF

6.3V

10%

X5R

0402

COMMON

C113

1uF

6.3V

10%

X5R

0402

COMMON

C613

1uF

6.3V

10%

X5R

0402

COMMON

C110

1uF

6.3V

10%

X5R

0402

COMMON

C614

1uF

6.3V

10%

X5R

0402

COMMON

GND

C592

1uF

6.3V

10%

X5R

0402

COMMON

GND

C916

47uF

4V

20%

X5R

0805LP

DNI

C E

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY

MEMORY: FBA[31:0]

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-V317

MS-V317

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Wednesday, August 20, 2014

Wednesday, August 20, 2014

Wednesday, August 20, 2014

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

600-1G401-BASE-QS1

PG401-A02

PCB REV

A

FDBA

BOM REV

G

MS-V317

5: MEMORY: FBA Partition 31..0

5: MEMORY: FBA Partition 31..0

5: MEMORY: FBA Partition 31..0

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

H

537

537

537

5 OF 37

PAGE

DATE

04-AUG-2014

10

10

10

5

Page 6

A B C D E F G H

Page6: MEMORY: FBA Partition 63..32

1

GND

M8C

@memory.u_mem_sd_ddr5_x32(sym_6):page6_i109

BGA170

COMMON

Normal

J1

MF_VSS/SOE*

add 1k to VSS

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

C10

VDD

C5

VDD

D11

VDD

G1

VDD

G11

VDD

G14

VDD

G4

VDD

L1

VDD

L11

VDD

L14

VDD

L4

VDD

P11

VDD

R10

VDD

R5

VDD

B1

VDDQ

B12

VDDQ

B14

VDDQ

B3

VDDQ

D1

VDDQ

D12

VDDQ

D14

VDDQ

D3

VDDQ

E10

VDDQ

E5

VDDQ

F1

VDDQ

F12

VDDQ

F14

VDDQ

F3

VDDQ

G13

VDDQ

G2

VDDQ

H12

VDDQ

H3

VDDQ

K12

VDDQ

K3

VDDQ

L13

VDDQ

L2

VDDQ

M1

VDDQ

M12

VDDQ

M14

VDDQ

M3

VDDQ

N10

VDDQ

N5

VDDQ

P1

VDDQ

P12

VDDQ

P14

VDDQ

P3

VDDQ

T1

VDDQ

T12

VDDQ

T14

VDDQ

T3

VDDQ

M8B

@memory.u_mem_sd_ddr5_x32(sym_5):page6_i55

BGA170

2

M8D

@memory.u_mem_sd_ddr5_x32(sym_1):page6_i11

BGA170

COMMON

4

Fba_D<32>

4

Fba_D<33>

4

Fba_D<34>

4

Fba_D<35>

4

Fba_D<36>

4

Fba_D<37>

4

Fba_D<38>

4

Fba_D<39>

4

4

4

Fba_D<40>

4

Fba_D<41>

4

Fba_D<42>

4

Fba_D<43>

4

Fba_D<44>

4

3

Fba_D<45>

4

Fba_D<46>

4

Fba_D<47>

4

4

4

4

FBA_D<32>

32

FBA_D<33>

33

FBA_D<34>

34

FBA_D<35>

35

FBA_D<36>

36

FBA_D<37>

37

FBA_D<38>

38

FBA_D<39>

39

FBA_EDC<4>

BI

FBA_DBI<4>

BI

FBA_D<40>

40

FBA_D<41>

41

FBA_D<42>

42

FBA_D<43>

43

FBA_D<44>

44

FBA_D<45>

45

FBA_D<46>

46

FBA_D<47>

47

FBA_EDC<5>

BI

FBA_DBI<5>

BI

FBA_WCK45

IN

FBA_WCK45*

IN

NORMAL

A4

DQ0

A2

DQ1

B4

DQ2

B2

DQ3

E4

DQ4

E2

DQ5

F4

DQ6

F2

DQ7

C2

EDC0

D2

DBI0

VREFD

x16

x32

A11

DQ8

A13

DQ9

B11

DQ10

B13

DQ11

E11

DQ12

E13

DQ13

F11

DQ14

F13

DQ15

C13

EDC1

D13

DBI1

D4

WCK01

D5

WCK01

FBA_VREFD FBA_VREFD

A10

NC

NC

NC

NC

NC

NC

NC

NC

GND

NC

4

Fba_D<48>

4

Fba_D<49>

4

Fba_D<50>

4

Fba_D<51>

4

Fba_D<52>

4

Fba_D<53>

4

Fba_D<54>

4

Fba_D<55>

4

4

IN

4

4

5

4

Fba_D<56>

4

Fba_D<57>

4

Fba_D<58>

4

Fba_D<59>

4

Fba_D<60>

4

Fba_D<61>

4

Fba_D<62>

4

Fba_D<63>

4

4

FBA_D<48>

48

FBA_D<49>

49

FBA_D<50>

50

FBA_D<51>

51

FBA_D<52>

52

FBA_D<53>

53

FBA_D<54>

54

FBA_D<55>

55

FBA_EDC<6>

BI

FBA_DBI<6>

BI

FBA_D<56>

56

FBA_D<57>

57

FBA_D<58>

58

FBA_D<59>

59

FBA_D<60>

60

FBA_D<61>

61

FBA_D<62>

62

FBA_D<63>

63

FBA_EDC<7>

BI

FBA_DBI<7>

BI

FBA_WCK67

IN

FBA_WCK67*

IN

M8A

@memory.u_mem_sd_ddr5_x32(sym_3):page6_i51

BGA170

COMMON

NORMAL

V11

DQ16

V13

DQ17

T11

DQ18

T13

DQ19

N11

DQ20

N13

DQ21

M11

DQ22

M13

DQ23

R13

EDC2

P13

DBI2

VREFD

x16

x32

V4

DQ24

V2

DQ25

T4

DQ26

T2

DQ27

N4

DQ28

N2

DQ29

M4

DQ30

M2

DQ31

R2

EDC3

P2

DBI3

P4

WCK23

P5

WCK23

V10

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

C138

820pF

50V

4

10%

X7R

4

0402

COMMON

GND

5

IN

4

IN

IN

C119

820pF

50V

10%

X7R

0402

COMMON

GND GND

FBA_CMD<19>

FBA_CMD<16>

FBA_CMD<26>

FBA_CMD<31>

FBA_CMD<23>

FBA_CMD<21>

FBA_CMD<20>

FBA_CMD<29>

FBA_CMD<30>

FBA_CMD<28>

FBA_CMD<27>

FBA_CMD<24>

FBA_CMD<25>

FBA_CMD<22>

FBA_CMD<18>

FBA_CMD<17>

FBA_CLK1

FBA_CLK1*

R613

40.2ohm

1 %

0402

COMMON

FBA_CLK1_CM

GND

R604 121ohm

R593

C608

10nF

16V

10%

X7R

0402

COMMON

FBA_CMD<19>

4

19

FBA_CMD<16>

4

16

FBA_CMD<26>

4

26

FBA_CMD<31>

4

31

FBA_CMD<23>

4

23

FBA_CMD<21>

4

21

FBA_CMD<20>

4

20

FBA_CMD<29>

4

29

FBA_CMD<30>

4

30

FBA_CMD<28>

4

28

FBA_CMD<27>

4

27

FBA_CMD<24>

4

24

FBA_CMD<25>

4

25

FBA_CMD<22>

4

22

FBA_CMD<18>

4

18

FBA_CMD<17>

4

17

R610

40.2ohm

1 %

0402

COMMON

FBA_VREFC

FBA_ZQ_2B

COMMON0402

1 %

1 %

FBA_SEN_2

1k

COMMON0402

COMMON

G3

RAS

L3

CAS

L12

WE

G12

CS

J4

ABI

H4

A0_A10

H5

A1_A9

H11

A2_BA0

H10

A3_BA3

K11

A4_BA2

K10

A5_BA1

K5

A6_A11

K4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

J14

VREFC

J13

ZQ

J10

SEN

FBA_MF2_A

R602

1k

COMMON0402

1 %

FBVDDQ

FBVDDQ

1

2

3

4

FBVDDQ

C620

C615

C606

GND

1uF

6.3V

10%

X5R

0402

COMMON

C126

1uF

6.3V

10%

X5R

0402

COMMON

GND

C915

47uF

4V

20%

X5R

0805LP

DNI

C E

C600

C589

10uF

6.3V

20%

X5R

0805LP

COMMON

FBVDDQ

C588

10uF

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

6.3V

20%

X5R

0805LP

COMMON

4.7uF

6.3V

20%

X5R

0603

COMMON

C135

4.7uF

6.3V

20%

X5R

0603

COMMON

C625

4.7uF

6.3V

20%

X5R

0603

COMMON

C132

4.7uF

6.3V

20%

X5R

0603

COMMON

C604

1uF

6.3V

10%

X5R

0402

COMMON

C112

1uF

6.3V

10%

X5R

0402

COMMON

C595

1uF

6.3V

10%

X5R

0402

COMMON

C129

1uF

6.3V

10%

X5R

0402

COMMON

1uF

6.3V

10%

X5R

0402

COMMON

C123

1uF

6.3V

10%

X5R

0402

COMMON

1uF

6.3V

10%

X5R

0402

COMMON

C115

1uF

6.3V

10%

X5R

0402

COMMON

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY

MEMORY: FBA[63:32]

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-V317

MS-V317

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Wednesday, August 20, 2014

Wednesday, August 20, 2014

Wednesday, August 20, 2014

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NV_PN

PCB REV

FDBA

BOM REV

G

MS-V317

6: MEMORY: FBA Partition 63..32

6: MEMORY: FBA Partition 63..32

6: MEMORY: FBA Partition 63..32

600-1G401-BASE-QS1

PG401-A02

A

1.0

1.0

1.0

Sheet ofDate:

06 37

Sheet ofDate:

06 37

Sheet ofDate:

06 37

6 OF 37

PAGE

DATE

04-AUG-2014

H

5

Page 7

A B C D E F G H

Page7: MEMORY: FBB Partition 31..0

1

GND

M5C

@memory.u_mem_sd_ddr5_x32(sym_7):page7_i381

BGA170_MIRR

COMMON

Mirrored

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

SOE*/MF_VDD

add 1k to VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

FBB_MF1_A

J1

C10

VDD

C5

VDD

D11

VDD

G1

VDD

G11

VDD

G14

VDD

G4

VDD

L1

VDD

L11

VDD

L14

VDD

L4

VDD

P11

VDD

R10

VDD

R5

VDD

B1

B12

B14

B3

D1

D12

D14

D3

E10

E5

F1

F12

F14

F3

G13

G2

H12

H3

K12

K3

L13

L2

M1

M12

M14

M3

N10

N5

P1

P12

P14

P3

T1

T12

T14

T3

R636 1k

1 %

FBVDDQ

COMMON0402

M5B

@memory.u_mem_sd_ddr5_x32(sym_5):page7_i380

BGA170_MIRR

M5D

@memory.u_mem_sd_ddr5_x32(sym_2):page7_i378

BGA170_MIRR

COMMON

2

4

Fbb_D<0>

4

Fbb_D<1>

4

Fbb_D<2>

4

Fbb_D<3>

4

Fbb_D<4>

4

Fbb_D<5>

4

Fbb_D<6>

4

Fbb_D<7>

4

4

4

Fbb_D<8>

4

Fbb_D<9>

4

Fbb_D<10>

4

Fbb_D<11>

4

Fbb_D<12>

4

Fbb_D<13>

4

Fbb_D<14>

4