Page 1

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

ASSEMBLYNVPNVARIANT

B

1

2

SKU

3

4

5

6

12

13

14

7

8

9

10

11

15

P817_A02: G92M, G3-256, MXM V3.0

LVDS, DVI-D,DisplayPort,VGA,HDCP,SLI

32Mx32 GDDR3, 256Bit, 1024MB

Table of Contents:

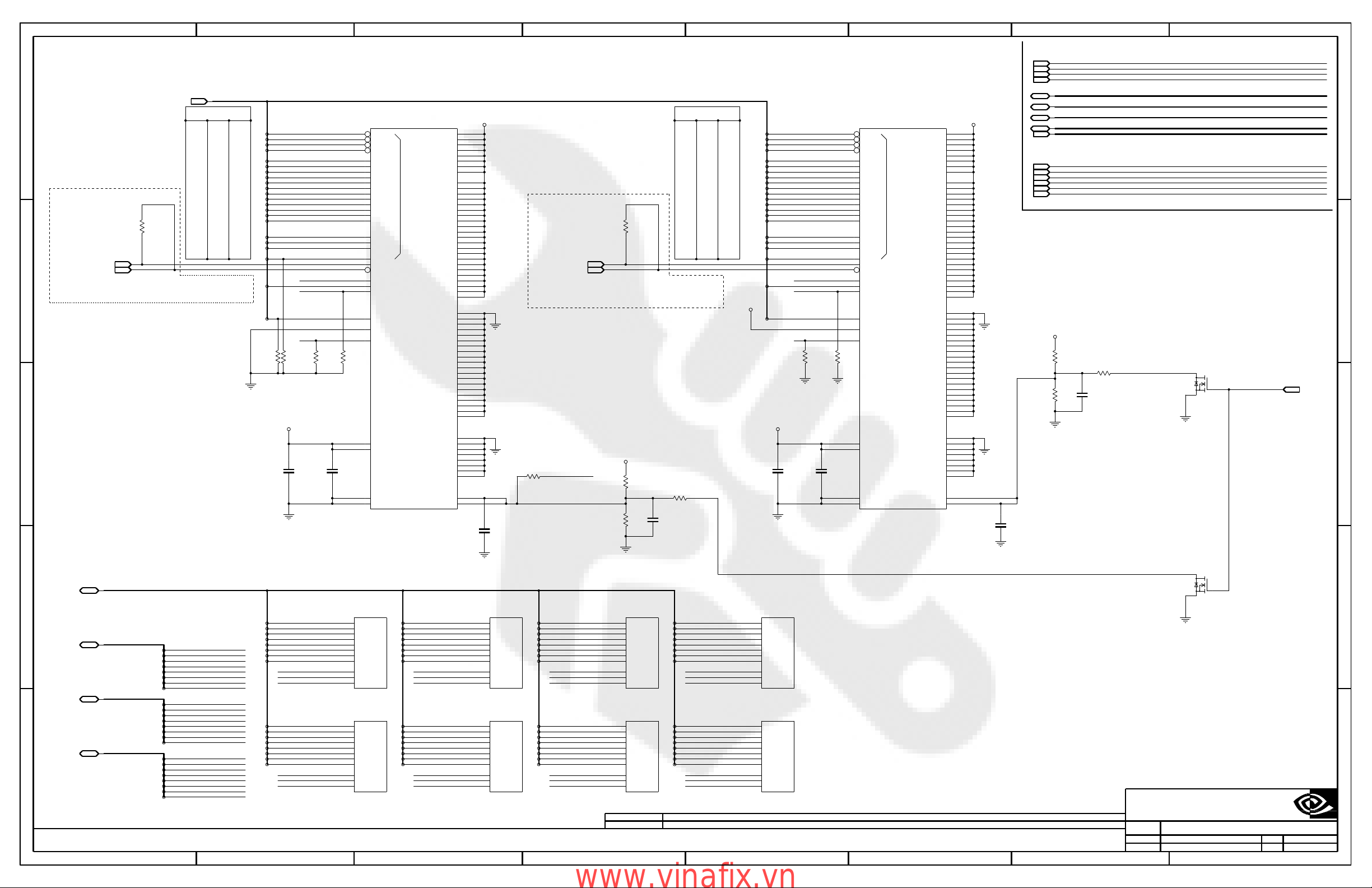

Page 1: Title Page

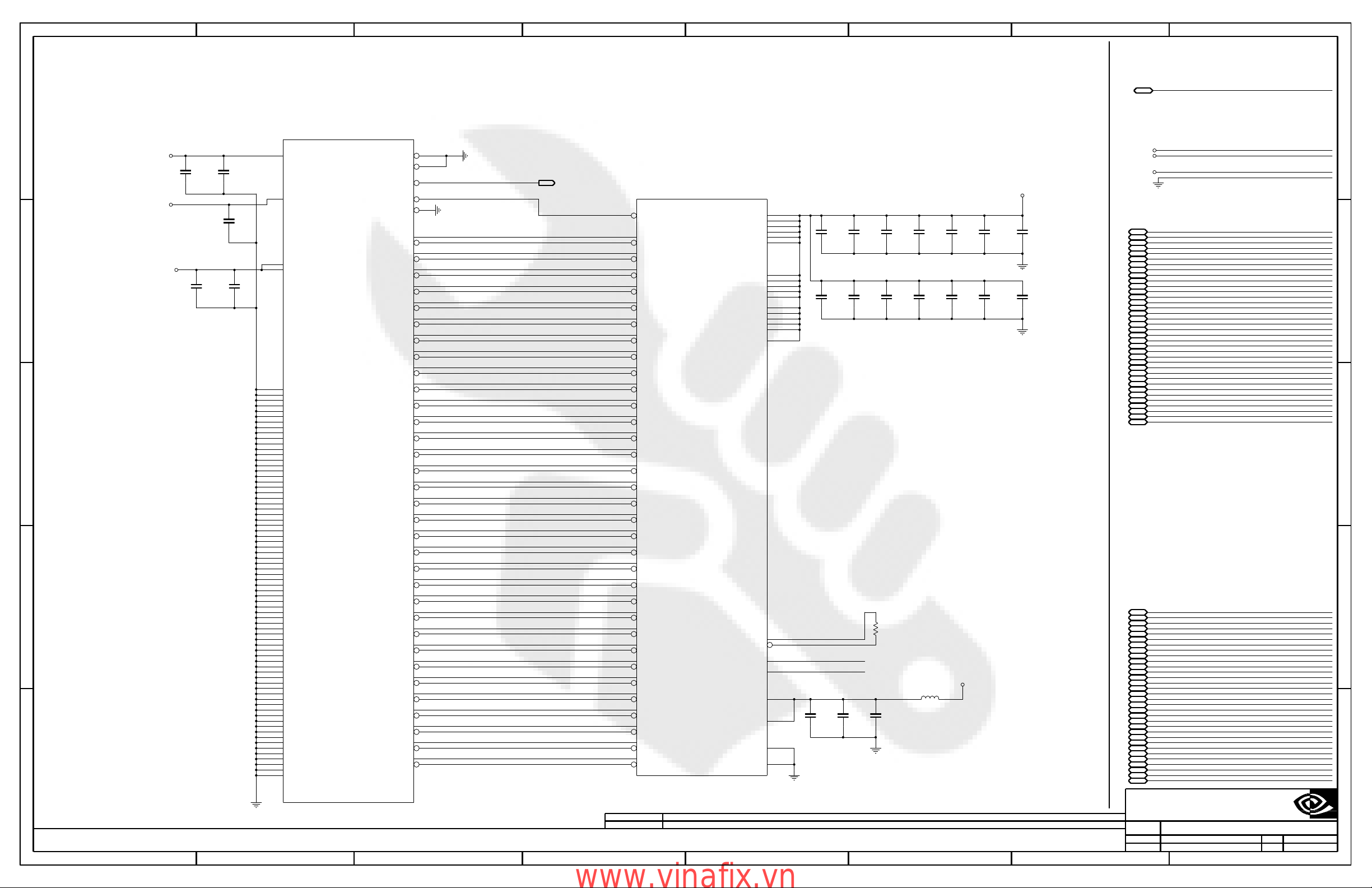

Page 2: MXM-III Connector and GPU PCI-EX Interface

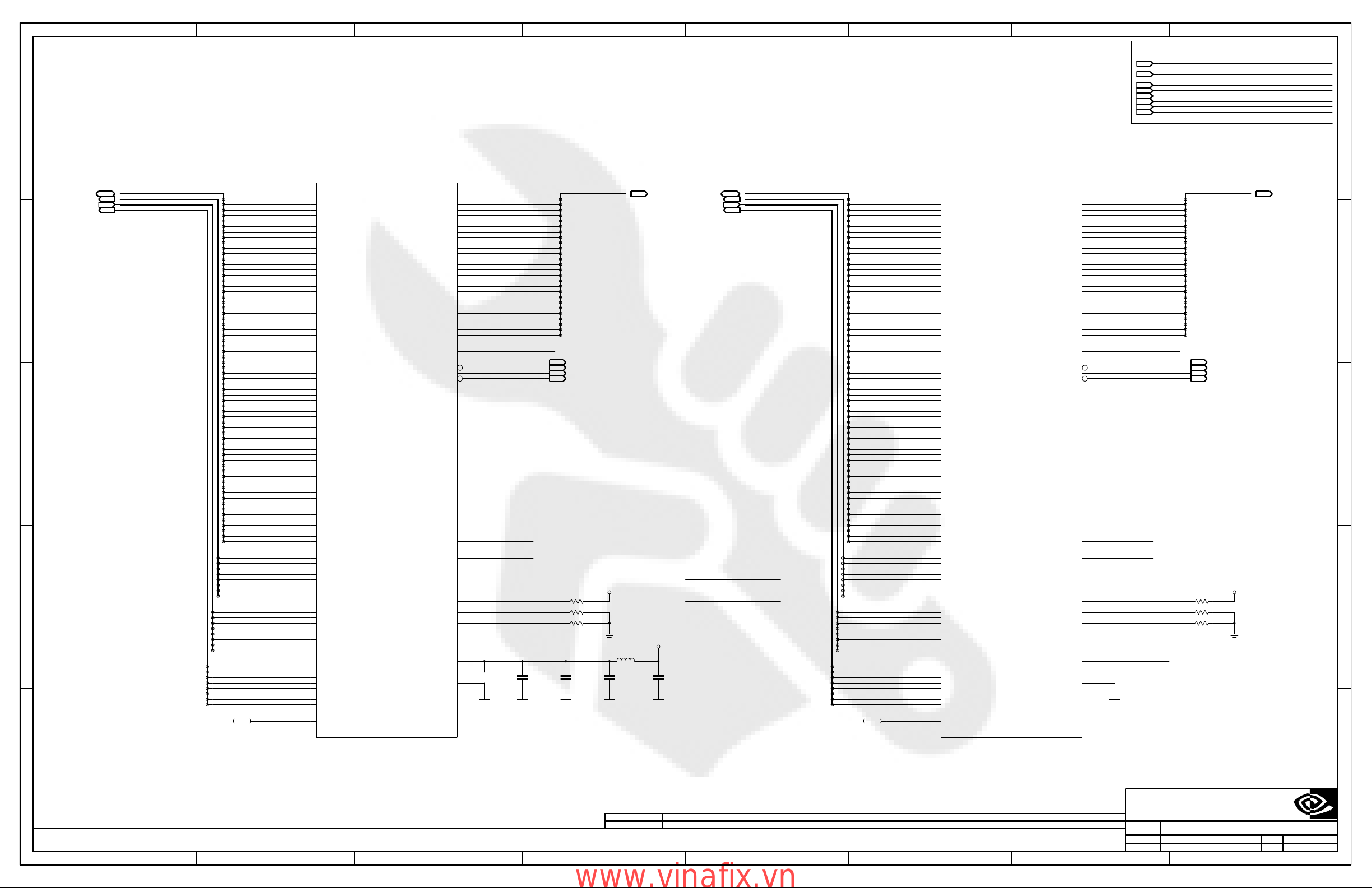

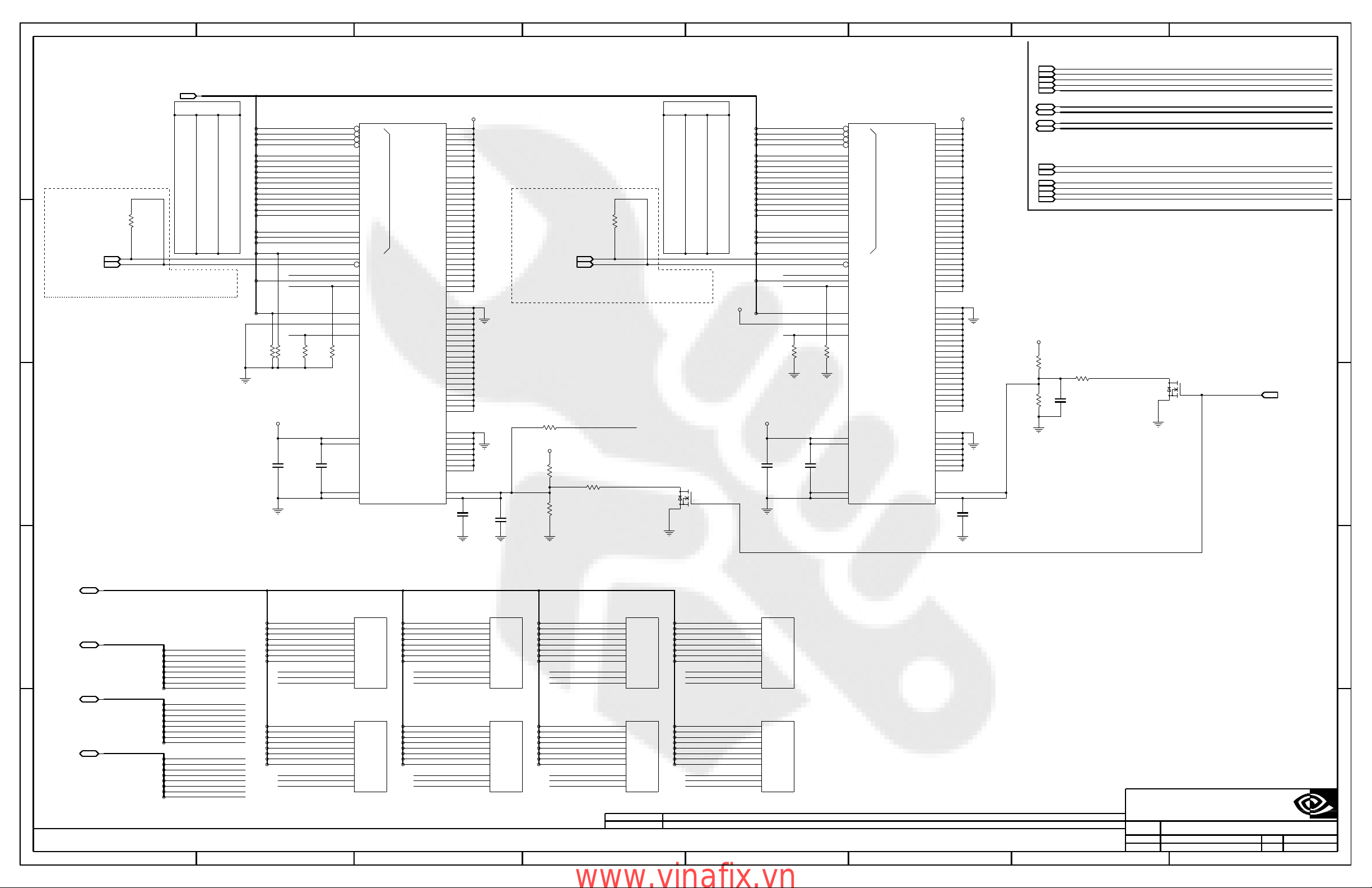

Page 3: FrameBuffer - GPU Partition A/B

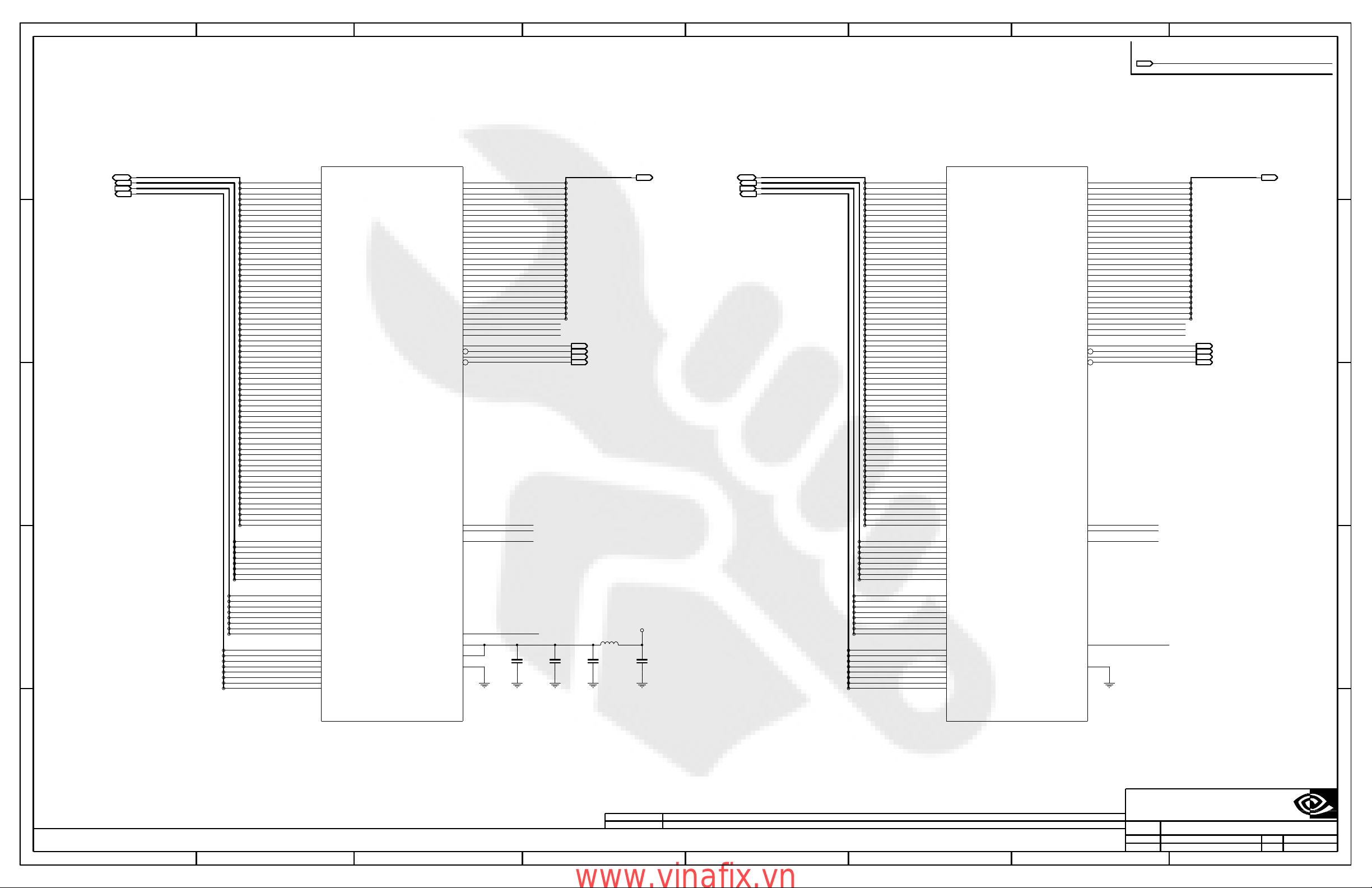

Page 4: FrameBuffer - GPU Partition C/D

Page 5: FrameBuffer - Partition A 16/32Mx32 BGA136 GDDR3

Page 6: FrameBuffer - Partition B 16/32Mx32 BGA136 GDDR3

Page 7: FrameBuffer - Partition C 16/32Mx32 BGA136 GDDR3

Page 8: FrameBuffer - Partition D 16/32Mx32 BGA136 GDDR3

Page 9: FrameBuffer - Memory Decoupling

Page 10: GPU GPIO, MIOA, MIOB Interface; GPU XTAL and Spread Spectrum Clock

Page 11: GPU DACA, DACB, and DACC Interface

Page 12: GPU IFP A/B LVDS and IFP C/D TMDS Interface

Page 13: DisplayPort Transmitter and External Thermal Sensor

Page 14: MXM Connector; GPU Temp Sensor and JTAG; VBIOS and HDCP ROM

Page 15: GPU PLLVDD Power and GND, GPU Decoupling

Page 16: Power Supply I - NVVDD

Page 17: Power Supply II - FBVDDQ, PEX_VDD

Page 18: GPU Strap Configuration

Page 19: BASENET REPORT

Page 20: BASENET REPORT

Page 21: BASENET REPORT

BASE

SKU0000

SKU0002

SKU0003

SKU0004

SKU0005

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

602-10817-BASE-SCH

602-10817-0001-200

602-10817-0002-200

602-10817-0003-200

602-10817-0004-200

602-10817-0005-200

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

NB9E-GTX/G92-750,1024MB, 8pcs32Mx32 GDDR3, SLI.

NB9E-GTX/G92-750,1024MB, 8pcs32Mx32 GDDR3, SLI. SKU2

NB9E-GTX/G92-750-B1,55nm SKU4 1024MB, 8pcs32Mx32 GDDR3, SLI.

NB9E-GTX/G92-760-B1,55nm SKU3 1024MB, 8pcs32Mx32 GDDR3, SLI.

NB9E-GTX/G92-740-A2,65nm SKU3 1024MB, 8pcs32Mx32 GDDR3, SLI.

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

NB9E-GTX/G92-760-B1,55nm SKU3 1024MB, 8pcs32Mx32 GDDR3, SLI.

Title Page

www.vinafix.vn

602-10817-0004-200 A

p817_a02

phchan

1 OF 21

22-AUG-2008

Page 2

Page2: MXM-III Connector and GPU PCI-EX Interface

BIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBI

OUT

1/24 PCI EXPRESS

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

RFU

RFU

PEX_PLLAVDD

PEX_PLLDGND

PEX_PLLAGND

PEX_PLLDVDD

PEX_TEST_PLL_CLK_OUT

PEX_TEST_PLL_CLK_OUT

PEX_TX0

PEX_REFCLK

PEX_REFCLK

PEX_RST

PEX_TX0

PEX_RX1

PEX_TX1

PEX_RX0

PEX_TX2

PEX_TX2

PEX_RX2

PEX_TX3

PEX_RX1

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX1

PEX_RX0

PEX_RX2

PEX_RX5

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX4

PEX_TX4

PEX_RX4

PEX_TX6

PEX_RX5

PEX_RX4

PEX_TX5

PEX_TX5

PEX_TX7

PEX_TX9

PEX_RX8

PEX_TX8

PEX_RX9

PEX_RX7

PEX_TX9

PEX_TX10

PEX_RX7

PEX_TX8

PEX_TX10

PEX_RX9

PEX_RX8

PEX_RX10

PEX_RX11

PEX_RX10

PEX_TX12

PEX_TX12

PEX_RX11

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX11

PEX_TX11

PEX_TX14

PEX_RX15

PEX_RX15

PEX_TX15

PEX_TX15

PEX_RX14

PEX_RX14

PEX_TX14

1/2 PCI-Express, Power

CLK_REQ

PEX_STD_SW

PEX_RST

PEX_REFCLK

PEX_REFCLK

PEX_RX0

PRSNT_R

PRSNT_L

PEX_RX0

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_RX3

PEX_TX0

PEX_TX0

PEX_RX1

PEX_RX1

PEX_TX1

PEX_TX1

PEX_RX3

PEX_TX3

PEX_RX5

PEX_RX4

PEX_RX4

PEX_TX6

PEX_TX5

PEX_TX5

PEX_RX6

PEX_TX6

PEX_TX3

PEX_TX4

PEX_TX4

PEX_RX5

PEX_RX6

PEX_RX7

PEX_RX7

PEX_TX7

PEX_TX7

PEX_RX8

PEX_RX8

PEX_TX8

PEX_TX8

PEX_RX9

PEX_RX9

PEX_TX9

PEX_TX9

PEX_RX10

PEX_RX10

PEX_TX12

PEX_RX12

PEX_TX10

PEX_TX10

PEX_RX11

PEX_TX11

PEX_RX11

PEX_TX11

PEX_TX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_RX15

PEX_RX15

PEX_RX14

PEX_RX14

PEX_TX14

PEX_TX15

PEX_TX15

(2.5A)

5V

(1A)

3V3

PWR_SRC

PWR_SRC

(10A)

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

POWER NET RULES

MAX_CURRENT

VOLTAGE

NET

0.25A

PEX_PLLVDD

1.1V

MIN_LINE_WIDTH

16MIL

CN1

CON_MXM3_EDGE

NPHY

NPHY

COMMON

2

281

19

156

154

155

153

149

147

150

148

143

141

144

142

137

135

138

136

123

121

122

120

117

115

116

114

111

109

110

108

105

103

104

102

99

97

98

96

93

91

92

90

87

85

86

84

81

79

80

78

75

73

74

72

69

67

68

66

63

61

62

60

57

55

56

54

51

49

50

48

GND

GND

PEX_PRSNT_STDSW*

PEX_RST*

PEX_REFCLK

PEX_REFCLK*

PEX_TX0

PEX_TX0*

PEX_RX0

PEX_RX0*

PEX_TX1

PEX_TX1*

PEX_RX1

PEX_RX1*

PEX_TX2

PEX_TX2*

PEX_RX2

PEX_RX2*

PEX_TX3

PEX_TX3*

PEX_RX3

PEX_RX3*

PEX_TX4

PEX_TX4*

PEX_RX4

PEX_RX4*

PEX_TX5

PEX_TX5*

PEX_RX5

PEX_RX5*

PEX_TX6

PEX_TX6*

PEX_RX6

PEX_RX6*

PEX_TX7

PEX_TX7*

PEX_RX7

PEX_RX7*

PEX_TX8

PEX_TX8*

PEX_RX8

PEX_RX8*

PEX_TX9

PEX_TX9*

PEX_RX9

PEX_RX9*

PEX_TX10

PEX_TX10*

PEX_RX10

PEX_RX10*

PEX_TX11

PEX_TX11*

PEX_RX11

PEX_RX11*

PEX_TX12

PEX_TX12*

PEX_RX12

PEX_RX12*

PEX_TX13

PEX_TX13*

PEX_RX13

PEX_RX13*

PEX_TX14

PEX_TX14*

PEX_RX14

PEX_RX14*

PEX_TX15

PEX_TX15*

PEX_RX15

PEX_RX15*

18.4C>

G1

G92-750-A2

BGA1148

COMMON

AR9

AK10

AL10

AM11

AM10

AP9

AP10

AN10

AN11

AR10

AR11

AN12

AM12

AT11

AT12

AL12

AK12

AP12

AP13

AM14

AM13

AR13

AR14

AN13

AN14

AT14

AT15

AN15

AM15

AP15

AP16

AL15

AK15

AR16

AR17

AM16

AN16

AT17

AT18

AN17

AN18

AP18

AP19

AM18

AM17

AR19

AR20

AL18

AK18

AT20

AT21

AM19

AN19

AP21

AP22

AN20

AN21

AR22

AR23

AM21

AM20

AT23

AT24

AL21

AK21

AR24

AR25

NB9E-GTX/G92-760-B1,55nm SKU3 1024MB, 8pcs32Mx32 GDDR3, SLI.

MXM-III Connector and GPU PCI-EX Interface

www.vinafix.vn

AH21

AJ21

AH22

AJ22

AH23

AJ23

AH16

AF17

AH17

AF18

AH18

AF19

AH19

AE20

AF20

AH20

AJ20

AM9

AN9

AK19

AK20

AE15

AE17

AF15

AE16

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT*

SNN_PEX_CAL_PD_VDDQ

SNN_PEX_CAL_PD_GND

PEX_PLLVDD

GND

C675

.1UF

16V

10%

X7R

0402

COMMON

C537

.1UF

16V

10%

X7R

0402

COMMON

C504

0.22UF

25V

10%

X7R

0603

COMMON

GND

278

100

101

106

107

112

113

118

119

124

125

133

134

139

140

145

146

151

152

157

166

173

174

179

180

185

186

191

192

197

198

203

204

209

210

215

216

221

222

228

244

250

251

256

257

262

263

268

269

275

1

E1

E2

11

36

37

46

47

52

53

58

59

64

65

70

71

76

77

82

83

88

89

94

95

E3

E4

3V3_RUN

C768

1UF

6.3V

10%

X5R

0402

COMMON

C775

.1UF

16V

10%

X7R

0402

COMMON

5V

PWR_SRC

C101

0.22UF

25V

10%

X7R

0603

COMMON

C633

C609

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C637

C653

.1UF .1UF

16V

16V

10%

10%

X7RX7R

0402

0402

COMMON

COMMON

C670

2.2UF

6.3V

20%

X5R

0402

COMMON

C644C659

1UF

.1UF

6.3V

16V

10%

10%

X5R

X7R

0402

0402

COMMON

COMMON

C646

C626

1UF.1UF 1UF

6.3V

16V

10%

10%

X7R

0402

0402

COMMON

COMMON

DNI

R580

200

Place to the bottom side for test usage.

1%

NO STUFF FOR PRODUCTION.

0402

COMMON

PEX_VDD

10nH

LB3

C58

4.7UF

6.3V

20%

X5R

0603

COMMON

COMMON0603

GND

C619

1UF

6.3V

10%

X5R

0402

COMMON

C618

6.3V

10%

X5RX5R

0402

COMMON

C636

1UF

6.3V

10%

X5R

0402

COMMON

C654

1UF

6.3V

10%

X5R

0402

COMMON

PEX_VDD

GND

GND

C660

4.7UF

6.3V

20%

X5R

0603

COMMON

C74

4.7UF

6.3V

20%

X5R

0603

COMMON

PLATFORM POWER

NET RULES

NV_NET_MAX_

CURRENT

VOLTAGE

NET

20V

PWR_SRC

5V

3V3_RUN

PWR_SRC

5V

3V3_RUN

GND

5V

3.3V

16A

3A

1.5A

0V

GND

NET RULES

NET

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT*

PEX_REFCLK

PEX_REFCLK*

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

PEX_RX0

PEX_RX0*

PEX_RX1

PEX_RX1*

PEX_RX2

PEX_RX2*

PEX_RX3

PEX_RX3*

PEX_RX4

PEX_RX4*

PEX_RX5

PEX_RX5*

PEX_RX6

PEX_RX6*

PEX_RX7

PEX_RX7*

PEX_RX8

PEX_RX8*

PEX_RX9

PEX_RX9*

PEX_RX10

PEX_RX10*

PEX_RX11

PEX_RX11*

PEX_RX12

PEX_RX12*

PEX_RX13

PEX_RX13*

PEX_RX14

PEX_RX14*

PEX_RX15

PEX_RX15*

602-10817-0004-200 A

p817_a02

phchan

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

NV_SOURCE_MIN_LINE_

WIDTH

16MIL

16MIL

16MIL

16MIL

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_TX1

PEX_TX1

PEX_TX2

PEX_TX2

PEX_TX3

PEX_TX3

PEX_TX4

PEX_TX5

PEX_TX5

PEX_TX6

PEX_TX6

PEX_TX7

PEX_TX7

PEX_TX8

PEX_TX8

PEX_TX9

PEX_TX9

PEX_TX10

PEX_TX10

PEX_TX11

PEX_TX11

PEX_TX12

PEX_TX12

PEX_TX13

PEX_TX13

PEX_TX14

PEX_TX14 90DIFF

PEX_TX15

PEX_TX15

PEX_RX0

PEX_RX0

PEX_RX1

PEX_RX1

PEX_RX2

PEX_RX2

PEX_RX3

PEX_RX3

PEX_RX4

PEX_RX4

PEX_RX5

PEX_RX5

PEX_RX6

PEX_RX6

PEX_RX7

PEX_RX7

PEX_RX8

PEX_RX8

PEX_RX9

PEX_RX9

PEX_RX10

PEX_RX10

PEX_RX11

PEX_RX11

PEX_RX12 90DIFF

PEX_RX12

PEX_RX13

PEX_RX13

PEX_RX14

PEX_RX14

PEX_RX15

PEX_RX15

POWER_NET

NV_IMPEDANCEDIFFPAIRNV_CRITICAL_NET

2 OF 21

22-AUG-2008

TRUE

TRUE

TRUE

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFFPEX_TX4

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

Page 3

Page3: FrameBuffer - GPU Partition A/B

ININININININININOUT

OUT

OUT

OUT

OUT

3/24 MEM_B

FBB_CMD6

FBB_CMD4

FBB_CMD5

FBB_CMD3

FBB_CMD1

FBB_CMD2

FBB_CMD0

FBB_CMD7

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD19

FBB_CMD18

FBB_CMD17

FBB_CMD16

FBB_CMD14

FBB_CMD15

FBB_CMD13

FBB_CMD12

FBB_CMD11

FBB_CMD9

FBB_CMD10

FBB_CMD8

FBB_CLK1

FBB_CLK0

FBB_CLK0

FBB_CMD28

FBB_CLK1

RFU

RFU

FBB_DEBUG

FBCAL1_PD_VDDQ

FBCAL1_PU_GND

FBB_PLLVDD_NC

FBCAL1_TERM_GND

FBB_PLLGND

FBBD6

FBBD4

FBBD5

FBBD3

FBBD2

FBBD1

FBBD0

FBBD7

FBBD27

FBBD26

FBBD25

FBBD24

FBBD23

FBBD22

FBBD21

FBBD19

FBBD20

FBBD17

FBBD16

FBBD15

FBBD13

FBBD12

FBBD11

FBBD9

FBBD10

FBBD8

FBBD14

FBBD18

FBBD47

FBBD46

FBBD45

FBBD44

FBBD42

FBBD43

FBBD41

FBBD40

FBBD39

FBBD37

FBBD38

FBBD36

FBBD35

FBBD34

FBBD32

FBBD33

FBBD31

FBBD30

FBBD29

FBBD28

FBBD48

FBBDQM2

FBBDQM1

FBBDQM0

FBBD62

FBBD63

FBBD60

FBBD61

FBBD59

FBBD57

FBBD58

FBBD55

FBBD56

FBBD54

FBBD53

FBBD52

FBBD50

FBBD51

FBBD49

FBBDQS_RN6

FBBDQS_WP2

FBBDQS_WP1

FBBDQS_WP0

FBBDQS_RN7

FBBDQS_RN4

FBBDQS_RN5

FBBDQS_RN3

FBBDQS_RN2

FBBDQS_RN1

FBBDQS_RN0

FBBDQM7

FBBDQM6

FBBDQM4

FBBDQM5

FBBDQM3

FBBDQS_WP3

FB_VREF2

FBBDQS_WP7

FBBDQS_WP6

FBBDQS_WP5

FBBDQS_WP4

OUT

OUTBIIN

OUT

OUT

OUT

OUT

OUT

OUTINOUT

BI

2/24 MEM_A

FBA_CMD6

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD7

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD19

FBA_CMD18

FBA_CMD17

FBA_CMD16

FBA_CMD14

FBA_CMD15

FBA_CMD13

FBA_CMD12

FBA_CMD11

FBA_CMD9

FBA_CMD10

FBA_CMD8

FBA_CMD22

FBA_CMD21

FBA_CMD20

FBA_CMD28

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

RFU

RFU

FBA_DEBUG

FBCAL0_PU_GND

FBCAL0_TERM_GND

FBCAL0_PD_VDDQ

FBA_PLLAVDD

FBA_DLLAVDD

FBA_PLLGND

FBAD6

FBAD4

FBAD5

FBAD3

FBAD2

FBAD1

FBAD0

FBAD7

FBAD20

FBAD21

FBAD26

FBAD25

FBAD24

FBAD23

FBAD22

FBAD19

FBAD17

FBAD15

FBAD12

FBAD13

FBAD11

FBAD9

FBAD10

FBAD8

FBAD27

FBAD14

FBAD16

FBAD18

FBAD45

FBAD44

FBAD42

FBAD41

FBAD37

FBAD38

FBAD36

FBAD35

FBAD32

FBAD33

FBAD31

FBAD30

FBAD29

FBAD28

FBAD46

FBAD40

FBAD39

FBAD43

FBAD34

FBAD47

FBAD48

FBAD60

FBADQM2

FBADQM1

FBAD61

FBAD58

FBAD57

FBAD55

FBAD56

FBAD54

FBAD53

FBAD52

FBAD51

FBAD50

FBAD49

FBAD59

FBADQM0

FBAD63

FBAD62

FBADQS_WP2

FBADQS_RN7

FBADQS_RN5

FBADQS_RN3

FBADQS_RN2

FBADQM4

FBADQM3

FBADQS_RN6

FBADQS_RN4

FBADQM7

FBADQM6

FBADQM5

FBADQS_RN1

FBADQS_RN0

FBADQS_WP0

FBADQS_WP1

FBADQS_WP3

FBADQS_WP5

FBADQS_WP4

FBADQS_WP7

FBADQS_WP6

FB_VREF1

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

FB_VREF

FB_CAL_PD_VDDQ0

FB_CAL_PU_GND0

FB_CAL_TERM_GND0

FB_CAL_PD_VDDQ1

FB_CAL_PU_GND1

FB_CAL_TERM_GND1

0.25A

1.2VFBAB_PLLAVDD

MIN_LINE_WIDTHMAX_CURRENTVOLTAGENET

16MIL

12MIL

12MIL

12MIL

12MIL

12MIL

12MIL

12MIL

G1

G92-750-A2

BGA1148

COMMON

5.1G<>

5.4A<>

5.1G<>

5.4A<>

5.1G<>

5.5A<>

5.1G<>

5.5A<>

FBA_D<63..0>

FBA_DQM<7..0>

FBA_DQS_RN<7..0>

FBA_DQS_WP<7..0>

FBA_CMD<0>

FBA_D<0>

0

FBA_D<1>

1

FBA_D<2>

2

FBA_D<3>

3

FBA_D<4>

4

FBA_D<5>

5

FBA_D<6>

6

FBA_D<7>

7

FBA_D<8>

8

FBA_D<9>

9

FBA_D<10>

10

FBA_D<11>

11

FBA_D<12>

12

FBA_D<13>

13

FBA_D<14>

14

FBA_D<15>

15

FBA_D<16>

16

FBA_D<17>

17

FBA_D<18>

18

FBA_D<19>

19

FBA_D<20>

20

FBA_D<21>

21

FBA_D<22>

22

FBA_D<23>

23

FBA_D<24>

24

FBA_D<25>

25

FBA_D<26>

26

FBA_D<27>

27

FBA_D<28>

28

FBA_D<29>

29

FBA_D<30>

30

FBA_D<31>

31

FBA_D<32>

32

FBA_D<33>

33

FBA_D<34>

34

FBA_D<35>

35

FBA_D<36>

36

FBA_D<37>

37

FBA_D<38>

38

FBA_D<39>

39

FBA_D<40>

40

FBA_D<41>

41

FBA_D<42>

42

FBA_D<43>

43

FBA_D<44>

44

FBA_D<45>

45

FBA_D<46>

46

FBA_D<47>

47

FBA_D<48>

48

FBA_D<49>

49

FBA_D<50>

50

FBA_D<51>

51

FBA_D<52>

52

FBA_D<53>

53

FBA_D<54>

54

FBA_D<55>

55

FBA_D<56>

56

FBA_D<57>

57

FBA_D<58>

58

FBA_D<59>

59

FBA_D<60>

60

FBA_D<61>

61

FBA_D<62>

62

FBA_D<63>

63

FBA_DQM<0>

0

FBA_DQM<1>

1

FBA_DQM<2>

2

FBA_DQM<3>

3

FBA_DQM<4>

4

FBA_DQM<5>

5

FBA_DQM<6>

6

FBA_DQM<7>

7

FBA_DQS_RN<0>

0

FBA_DQS_RN<1>

1

FBA_DQS_RN<2>

2

FBA_DQS_RN<3>

3

FBA_DQS_RN<4>

4

FBA_DQS_RN<5>

5

FBA_DQS_RN<6>

6

FBA_DQS_RN<7>

7

FBA_DQS_WP<0>

0

FBA_DQS_WP<1>

1

FBA_DQS_WP<2>

2

FBA_DQS_WP<3>

3

FBA_DQS_WP<4>

4

FBA_DQS_WP<5>

5

FBA_DQS_WP<6>

6

FBA_DQS_WP<7>

7

FB_VREF1

TP501

AH35

AH36

AH34

AJ34

AK36

AJ36

AK34

AL34

AH32

AK33

AJ33

AH33

AL33

AN32

AN33

AN31

AE32

AF30

AF32

AE30

AE31

AC30

AC32

AD30

AG36

AG34

AG35

AF36

AD36

AD34

AD35

AE34

AP36

AN35

AM34

AP35

AP34

AP33

AT34

AR34

AM22

AM25

AN26

AN24

AK24

AL22

AK23

AM23

AT32

AT33

AR33

AP31

AR30

AT30

AP30

AT29

AP26

AP27

AT25

AP25

AR28

AP28

AT28

AP29

AK35

AM33

AF33

AF34

AN34

AM24

AP32

AR27

AL35

AK32

AG33

AE36

AM36

AN22

AR31

AT27

AL36

AL32

AG32

AE35

AN36

AN23

AT31

AT26

J29

AK28

FBA_CMD<1>

AK29

FBA_CMD<2>

AN30

FBA_CMD<3>

AM27

FBA_CMD<4>

AN28

FBA_CMD<5>

AL29

FBA_CMD<6>

AM30

FBA_CMD<7>

AJ31

FBA_CMD<8>

AK31

FBA_CMD<9>

AH31

FBA_CMD<10>

AK25

FBA_CMD<11>

AM26

FBA_CMD<12>

AL31

FBA_CMD<13>

AN29

FBA_CMD<14>

AK27

FBA_CMD<15>

AK26

FBA_CMD<16>

AN27

FBA_CMD<17>

AL25

FBA_CMD<18>

AJ30

FBA_CMD<19>

AM31

FBA_CMD<20>

AH30

FBA_CMD<21>

AL30

FBA_CMD<22>

AH29

FBA_CMD<23>

AL28

FBA_CMD<24>

AH28

FBA_CMD<25>

AM28

SNN_FBA_CMD<26>

AG30

SNN_FBA_CMD<27>

AG28

SNN_FBA_CMD<28>

AF28

FBA_CLK0

AH26

FBA_CLK0*

AH27

FBA_CLK1

AJ29

FBA_CLK1*

AJ28

SNN_FBA_RFU0

AJ24

SNN_FBA_RFU1

AH24

SNN_FBA_DEBUG

AH25

ADD A SMALL TESTPOINT ON THIS SNN NET IN BOARD FILE

FB_CAL_PD_VDDQ0

J28

FB_CAL_PU_GND0

H28

FB_CAL_TERM_GND0

H29

FBAB_PLLAVDDAC29

AD29

AE29

GND

GND

C62

.1UF

16V

10%

X7R

0402

COMMON

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

R538

R548

R547

FBA_CMD<28..0>

5.1G<

5.1G<

5.1G<

5.1G<

0402

1%

0402

1%

0402

1%

C57

1UF

6.3V

10%

X5R

0402

COMMON

GND

5.2A<

5.2A<

5.2D<

5.2D<

FBVDDQ

51.1

COMMON

28

COMMON

34.8

COMMON

GND

BEAD_0402

GND

240R@100MHzLB4

C68

4.7UF

6.3V

20%

X5R

0603

COMMON

PEX_VDD

COMMON

6.4A<> 6.1G<>

5.1G< 5.1A<

6.4A<> 6.1G<>

6.5A<> 6.1G<>

6.5A<> 6.1G<>

FB_CALx_PD_VDDQ

FB_CALx_PU_GND

FB_CALx_TERM_GND

VREF RATIO GPIO10 low

VREF RATIO GPIO10 high

(0.5 ratio needed only when FBVDD can be 2.0V)

C60

4.7UF

6.3V

20%

X5R

0603

COMMON

GND

NB9E-GTX/G92-760-B1,55nm SKU3 1024MB, 8pcs32Mx32 GDDR3, SLI.

FrameBuffer - GPU Partition A/B

www.vinafix.vn

FBB_D<63..0>

FBB_DQM<7..0>

FBB_DQS_RN<7..0>

FBB_DQS_WP<7..0>

DDR3CALIBRATION PIN

51.1

28

34.8

0.667 FBVDDQ

0.5 FBVDDQ

G1

G92-750-A2

BGA1148

COMMON

FBB_CMD<0>

P33

FBB_CMD<1>

N33

FBB_CMD<2>

R31

FBB_CMD<3>

U33

FBB_CMD<4>

V30

FBB_CMD<5>

T33

FBB_CMD<6>

T30

FBB_CMD<7>

N32

FBB_CMD<8>

R32

FBB_CMD<9>

P32

FBB_CMD<10>

U32

FBB_CMD<11>

U30

FBB_CMD<12>

P30

FBB_CMD<13>

V31

FBB_CMD<14>

T28

FBB_CMD<15>

W30

FBB_CMD<16>

V32

FBB_CMD<17>

T32

FBB_CMD<18>

N30

FBB_CMD<19>

P28

FBB_CMD<20>

P29

FBB_CMD<21>

U29

FBB_CMD<22>

N28

FBB_CMD<23>

R30

FBB_CMD<24>

M30

FBB_CMD<25>

T29

SNN_FBB_CMD<26>

N29

SNN_FBB_CMD<27>

AA30

SNN_FBB_CMD<28>

Y29

FBB_CLK0

M28

FBB_CLK0*

L28

FBB_CLK1

W31

FBB_CLK1*

W32

SNN_FBB_RFU0

R28

SNN_FBB_RFU1

K29

SNN_FBB_DEBUG

C34

ADD A SMALL TESTPOINT ON THIS SNN NET IN BOARD FILE

FB_CAL_PD_VDDQ1

H27

FB_CAL_PU_GND1

H26

FB_CAL_TERM_GND1

J26

SNN_FBB_PLLVDD

AB28

AC28

GND

FB_VREF2

G36

G35

H36

H34

J35

J34

K34

K35

J31

K32

J30

H30

L32

K30

M31

L30

G31

J32

J33

F33

H31

E33

F31

F32

F35

G34

F36

F34

C35

D34

C36

D35

N35

M34

L34

N36

P36

P34

R36

R34

AC33

Y33

Y30

AB30

AA32

AD32

AD33

AA33

T36

R35

T34

U36

W35

U34

V34

W36

AC36

AA36

AC34

AB34

AA35

Y34

Y36

W34

J36

M32

H33

E34

N34

Y32

T35

AA34

L36

K33

G32

E36

M36

AB32

V35

AB35

K36

L33

G33

D36

M35

AB31

V36

AB36

J27

FBB_D<0>

0

FBB_D<1>

1

FBB_D<2>

2

FBB_D<3>

3

FBB_D<4>

4

FBB_D<5>

5

FBB_D<6>

6

FBB_D<7>

7

FBB_D<8>

8

FBB_D<9>

9

FBB_D<10>

10

FBB_D<11>

11

FBB_D<12>

12

FBB_D<13>

13

FBB_D<14>

14

FBB_D<15>

15

FBB_D<16>

16

FBB_D<17>

17

FBB_D<18>

18

FBB_D<19>

19

FBB_D<20>

20

FBB_D<21>

21

FBB_D<22>

22

FBB_D<23>

23

FBB_D<24>

24

FBB_D<25>

25

FBB_D<26>

26

FBB_D<27>

27

FBB_D<28>

28

FBB_D<29>

29

FBB_D<30>

30

FBB_D<31>

31

FBB_D<32>

32

FBB_D<33>

33

FBB_D<34>

34

FBB_D<35>

35

FBB_D<36>

36

FBB_D<37>

37

FBB_D<38>

38

FBB_D<39>

39

FBB_D<40>

40

FBB_D<41>

41

FBB_D<42>

42

FBB_D<43>

43

FBB_D<44>

44

FBB_D<45>

45

FBB_D<46>

46

FBB_D<47>

47

FBB_D<48>

48

FBB_D<49>

49

FBB_D<50>

50

FBB_D<51>

51

FBB_D<52>

52

FBB_D<53>

53

FBB_D<54>

54

FBB_D<55>

55

FBB_D<56>

56

FBB_D<57>

57

FBB_D<58>

58

FBB_D<59>

59

FBB_D<60>

60

FBB_D<61>

61

FBB_D<62>

62

FBB_D<63>

63

FBB_DQM<0>

0

FBB_DQM<1>

1

FBB_DQM<2>

2

FBB_DQM<3>

3

FBB_DQM<4>

4

FBB_DQM<5>

5

FBB_DQM<6>

6

FBB_DQM<7>

7

FBB_DQS_RN<0>

0

FBB_DQS_RN<1>

1

FBB_DQS_RN<2>

2

FBB_DQS_RN<3>

3

FBB_DQS_RN<4>

4

FBB_DQS_RN<5>

5

FBB_DQS_RN<6>

6

FBB_DQS_RN<7>

7

FBB_DQS_WP<0>

0

FBB_DQS_WP<1>

1

FBB_DQS_WP<2>

2

FBB_DQS_WP<3>

3

FBB_DQS_WP<4>

4

FBB_DQS_WP<5>

5

FBB_DQS_WP<6>

6

FBB_DQS_WP<7>

7

TP502

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

R554

R551

R556

FBB_CMD<28..0>

0402

1%

0402

1%

0402

1%

6.1G<

6.1G<

6.1G<

6.1G<

51.1

COMMON

28

COMMON

34.8

COMMON

6.2A<

6.2A<

6.2D<

6.2D<

FBVDDQ

GND

6.1G< 6.1A<

602-10817-0004-200 A

p817_a02

phchan

3 OF 21

22-AUG-2008

Page 4

Page4: FrameBuffer - GPU Partition C/D

OUTINOUT

OUT

OUT

OUT

5/24 MEM_D

FBD_CMD0

FBD_CMD1

FBD_CMD2

FBD_CMD3

FBD_CMD5

FBD_CMD4

FBD_CMD6

FBD_CMD7

FBD_CMD21

FBD_CMD20

FBD_CMD19

FBD_CMD8

FBD_CMD10

FBD_CMD9

FBD_CMD11

FBD_CMD12

FBD_CMD13

FBD_CMD14

FBD_CMD15

FBD_CMD16

FBD_CMD17

FBD_CMD18

FBD_CMD23

FBD_CMD22

FBD_CMD27

FBD_CMD26

FBD_CMD25

FBD_CMD24

FBD_CLK1

FBD_CLK1

FBD_CLK0

FBD_CLK0

FBD_CMD28

RFU

RFU

FBD_DEBUG

FBD_PLLVDD_NC

FBD_PLLGND

FBDD0

FBDD1

FBDD2

FBDD3

FBDD4

FBDD5

FBDD6

FBDD7

FBDD9

FBDD21

FBDD25

FBDD8

FBDD10

FBDD11

FBDD12

FBDD13

FBDD15

FBDD14

FBDD16

FBDD17

FBDD18

FBDD20

FBDD19

FBDD22

FBDD23

FBDD24

FBDD26

FBDD27

FBDD28

FBDD29

FBDD30

FBDD31

FBDD33

FBDD32

FBDD36

FBDD35

FBDD38

FBDD37

FBDD40

FBDD41

FBDD39

FBDD42

FBDD43

FBDD44

FBDD45

FBDD46

FBDD47

FBDD34

FBDD48

FBDD57

FBDD58

FBDD59

FBDD60

FBDD49

FBDD50

FBDD51

FBDD52

FBDD53

FBDD54

FBDD56

FBDD55

FBDD61

FBDD62

FBDD63

FBDDQM0

FBDDQM2

FBDDQM1

FBDDQM3

FBDDQM5

FBDDQM4

FBDDQM6

FBDDQM7

FBDDQS_RN0

FBDDQS_RN1

FBDDQS_RN2

FBDDQS_RN3

FBDDQS_RN6

FBDDQS_RN4

FBDDQS_RN7

FBDDQS_WP0

FBDDQS_WP1

FBDDQS_WP2

FBDDQS_RN5

FBDDQS_WP3

FBDDQS_WP4

FBDDQS_WP5

FBDDQS_WP6

FBDDQS_WP7

BI

OUTINOUT

OUT

OUT

OUT

OUT

OUTBIOUT

OUT

IN

4/24 MEM_C

FBC_CMD6

FBC_CMD5

FBC_CMD4

FBC_CMD3

FBC_CMD2

FBC_CMD1

FBC_CMD0

FBC_CMD7

FBC_CMD24

FBC_CMD25

FBC_CMD21

FBC_CMD22

FBC_CMD23

FBC_CMD20

FBC_CMD19

FBC_CMD18

FBC_CMD17

FBC_CMD16

FBC_CMD15

FBC_CMD14

FBC_CMD13

FBC_CMD12

FBC_CMD11

FBC_CMD10

FBC_CMD9

FBC_CMD8

FBC_CMD26

FBC_CMD27

FBC_CMD28

FBC_CLK1

FBC_CLK1

FBC_CLK0

FBC_CLK0

RFU

RFU

FBC_DEBUG

FBC_DLLAVDD

FBC_PLLAVDD

FBC_PLLVDD_NC

FBC_PLLGND

FBCD5

FBCD3

FBCD1

FBCD6

FBCD4

FBCD2

FBCD0

FBCD7

FBCD16

FBCD19

FBCD27

FBCD26

FBCD25

FBCD22

FBCD23

FBCD20

FBCD13

FBCD9

FBCD8

FBCD14

FBCD15

FBCD17

FBCD12

FBCD24

FBCD21

FBCD18

FBCD11

FBCD10

FBCD29

FBCD28

FBCD33

FBCD35

FBCD47

FBCD45

FBCD46

FBCD44

FBCD43

FBCD42

FBCD39

FBCD41

FBCD40

FBCD37

FBCD32

FBCD30

FBCD36

FBCD34

FBCD31

FBCD38

FBCD48

FBCD60

FBCD63

FBCDQM0

FBCDQM2

FBCDQM1

FBCD62

FBCD61

FBCD57

FBCD58

FBCD59

FBCD55

FBCD56

FBCD53

FBCD54

FBCD51

FBCD50

FBCD49

FBCD52

FBCDQM5

FBCDQM4

FBCDQM6

FBCDQM7

FBCDQS_RN0

FBCDQS_RN1

FBCDQS_RN2

FBCDQS_RN4

FBCDQS_RN5

FBCDQS_RN6

FBCDQS_RN7

FBCDQS_WP0

FBCDQS_WP1

FBCDQS_WP2

FBCDQS_RN3

FBCDQM3

FBCDQS_WP3

FBCDQS_WP4

FBCDQS_WP5

FBCDQS_WP6

FBCDQS_WP7

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

MAX_CURRENT MIN_LINE_WIDTHVOLTAGENET

0.25A

1.2VFBCD_PLLAVDD

16MIL

FBC_D<63..0>

FBC_DQM<7..0>

FBC_DQS_RN<7..0>

FBC_DQS_WP<7..0>

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBC_D<0>

FBC_D<1>

FBC_D<2>

FBC_D<3>

FBC_D<4>

FBC_D<5>

FBC_D<6>

FBC_D<7>

FBC_D<8>

FBC_D<9>

FBC_D<10>

FBC_D<11>

FBC_D<12>

FBC_D<13>

FBC_D<14>

FBC_D<15>

FBC_D<16>

FBC_D<17>

FBC_D<18>

FBC_D<19>

FBC_D<20>

FBC_D<21> E14

FBC_D<22>

FBC_D<23>

FBC_D<24>

FBC_D<25>

FBC_D<26>

FBC_D<27>

FBC_D<28>

FBC_D<29>

FBC_D<30>

FBC_D<31>

FBC_D<32>

FBC_D<33>

FBC_D<34>

FBC_D<35>

FBC_D<36>

FBC_D<37>

FBC_D<38>

FBC_D<39>

FBC_D<40>

FBC_D<41>

FBC_D<42>

FBC_D<43>

FBC_D<44>

FBC_D<45>

FBC_D<46>

FBC_D<47>

FBC_D<48>

FBC_D<49>

FBC_D<50>

FBC_D<51>

FBC_D<52>

FBC_D<53>

FBC_D<54>

FBC_D<55>

FBC_D<56>

FBC_D<57>

FBC_D<58>

FBC_D<59>

FBC_D<60>

FBC_D<61>

FBC_D<62> A31

FBC_D<63>

FBC_DQM<0>

FBC_DQM<1>

FBC_DQM<2>

FBC_DQM<3>

FBC_DQM<4>

FBC_DQM<5>

FBC_DQM<6>

FBC_DQM<7>

FBC_DQS_RN<0>

FBC_DQS_RN<1>

FBC_DQS_RN<2>

FBC_DQS_RN<3>

FBC_DQS_RN<4>

FBC_DQS_RN<5>

FBC_DQS_RN<6>

FBC_DQS_RN<7>

FBC_DQS_WP<0>

FBC_DQS_WP<1>

FBC_DQS_WP<2>

FBC_DQS_WP<3>

FBC_DQS_WP<4>

FBC_DQS_WP<5>

FBC_DQS_WP<6>

FBC_DQS_WP<7>

7.1G<>

7.4A<>

7.1G<>

7.4A<>

7.1G<>

7.5A<>

7.1G<>

7.5A<>

C18

C17

A17

B16

C14

A16

C15

A14

A18

A19

B19

B18

B21

C19

B22

C21

E15

D16

D17

G16

E16

G13

D13

A22

C22

C23

A23

A24

C24

C25

B24

C28

B27

C27

B28

C29

A29

B30

A30

E31

E28

D28

F29

F30

D33

D32

D31

G27

F25

G26

D26

G29

G28

E27

F28

A34

C32

B34

C33

C31

B31

C30

C16

C20

G14

C26

A28

D29

D27

B33

B15

A21

D14

B25

A27

E30

E25

A33

A15

A20

E13

A25

A26

D30

E26

A32

G1

G92-750-A2

BGA1148

COMMON

H20

E18

E20

D23

G24

D24

G23

D20

E22

J21

E21

G20

F22

H21

E17

E19

D21

E23

F19

E24

G19

G25

G18

G22

G17

F15

G15

H17

J16

J24

H23

H24

J25

H16

J11

J12

J13

GND

FBC_CMD<0>F18

FBC_CMD<1>

FBC_CMD<2>

FBC_CMD<3>

FBC_CMD<4>

FBC_CMD<5>

FBC_CMD<6>

FBC_CMD<7>

FBC_CMD<8>

FBC_CMD<9>

FBC_CMD<10>

FBC_CMD<11>

FBC_CMD<12>

FBC_CMD<13>

FBC_CMD<14>

FBC_CMD<15>

FBC_CMD<16>

FBC_CMD<17>

FBC_CMD<18>

FBC_CMD<19>

FBC_CMD<20>

FBC_CMD<21>G21

FBC_CMD<22>

FBC_CMD<23>

FBC_CMD<24>

FBC_CMD<25>

SNN_FBC_CMD<26>

SNN_FBC_CMD<27>

SNN_FBC_CMD<28>

FBC_CLK0

FBC_CLK0*

FBC_CLK1

FBC_CLK1*

SNN_FBC_RFU0

SNN_FBC_RFU1

SNN_FBC_DEBUG

SNN_FBC_PLLVDDH13

FBCD_PLLAVDD

GND

C703

.1UF

16V

10%

X7R

0402

COMMON

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

FBC_CMD<28..0>

7.1G<

7.1G<

7.1G<

7.1G<

7.2A<

7.2A<

7.2D<

7.2D<

7.1A<

8.4A<> 7.1G<

8.4A<>

8.5A<>

8.5A<>

8.1G<>

8.1G<>

8.1G<>

8.1G<>

PEX_VDD

240R@100MHz

C32

1UF

6.3V

10%

X5R

0402

COMMON

LB2

BEAD_0402

C27

4.7UF

6.3V

20%

X5R

0603

COMMON

GNDGND

COMMON

C34

4.7UF

6.3V

20%

X5R

0603

COMMON

GND

NB9E-GTX/G92-760-B1,55nm SKU3 1024MB, 8pcs32Mx32 GDDR3, SLI.

FrameBuffer - GPU Partition C/D

www.vinafix.vn

FBD_D<63..0>

FBD_DQM<7..0>

FBD_DQS_RN<7..0>

FBD_DQS_WP<7..0>

G1

G92-750-A2

BGA1148

COMMON

FBD_CMD<0>

FBD_D<0>

0

FBD_D<1>

1

FBD_D<2>

2

FBD_D<3>

3

FBD_D<4>

4

FBD_D<5>

5

FBD_D<6>

6

FBD_D<7>

7

FBD_D<8>

8

FBD_D<9>

9

FBD_D<10>

10

FBD_D<11>

11

FBD_D<12>

12

FBD_D<13>

13

FBD_D<14>

14

FBD_D<15>

15

FBD_D<16>

16

FBD_D<17>

17

FBD_D<18>

18

FBD_D<19>

19

FBD_D<20>

20

FBD_D<21>

21

FBD_D<22>

22

FBD_D<23>

23

FBD_D<24>

24

FBD_D<25>

25

FBD_D<26>

26

FBD_D<27>

27

FBD_D<28>

28

FBD_D<29>

29

FBD_D<30>

30

FBD_D<31>

31

FBD_D<32>

32

FBD_D<33>

33

FBD_D<34>

34

FBD_D<35>

35

FBD_D<36>

36

FBD_D<37>

37

FBD_D<38>

38

FBD_D<39>

39

FBD_D<40>

40

FBD_D<41>

41

FBD_D<42>

42

FBD_D<43>

43

FBD_D<44>

44

FBD_D<45>

45

FBD_D<46>

46

FBD_D<47>

47

FBD_D<48>

48

FBD_D<49>

49

FBD_D<50>

50

FBD_D<51>

51

FBD_D<52>

52

FBD_D<53>

53

FBD_D<54>

54

FBD_D<55>

55

FBD_D<56>

56

FBD_D<57>

57

FBD_D<58>

58

FBD_D<59>

59

FBD_D<60>

60

FBD_D<61>

61

FBD_D<62>

62

FBD_D<63>

63

FBD_DQM<0>

0

FBD_DQM<1>

1

FBD_DQM<2>

2

FBD_DQM<3>

3

FBD_DQM<4>

4

FBD_DQM<5>

5

FBD_DQM<6>

6

FBD_DQM<7>

7

FBD_DQS_RN<0>

0

FBD_DQS_RN<1>

1

FBD_DQS_RN<2>

2

FBD_DQS_RN<3>

3

FBD_DQS_RN<4>

4

FBD_DQS_RN<5>

5

FBD_DQS_RN<6>

6

FBD_DQS_RN<7>

7

FBD_DQS_WP<0>

0

FBD_DQS_WP<1>

1

FBD_DQS_WP<2>

2

FBD_DQS_WP<3>

3

FBD_DQS_WP<4>

4

FBD_DQS_WP<5>

5

FBD_DQS_WP<6>

6

FBD_DQS_WP<7>

7

J3 G5

J1

J2

M3

K3

L3

M1

H1

G3

G1

G2

F3

E1

D1

D2

P4

N7

M7

N5

P5

R7

T7

P7

C1

C5

C2

B4

A3

B3

C4

C3

A8

C6

C7

A7

C8

C9

A9

B9

E12

E9

F9

G10

D10

G12

F12

D11

F4

E4

D4

D5

D8

E7

D7

D9

B13

C11

A13

C13

A11

A10

B10

C10

K2

E3

N4

D3

B7

G11

F5

C12

K1

F2

R6

A4

B6

E10

E6

A12

L1

F1

R5

A5

A6

E11

D6

B12

M6H3

FBD_CMD<1>

FBD_CMD<2>

L7

FBD_CMD<3>

K5

FBD_CMD<4>

J10

FBD_CMD<5>

G8

FBD_CMD<6>

F8

FBD_CMD<7>

G6

FBD_CMD<8>

H6

FBD_CMD<9>

F6

FBD_CMD<10>

K8

FBD_CMD<11>

L5

FBD_CMD<12>

H4

FBD_CMD<13>

G4

FBD_CMD<14>

K9

FBD_CMD<15>

L4

FBD_CMD<16>

K4

FBD_CMD<17>

K7

FBD_CMD<18>

G7

FBD_CMD<19>

J4

FBD_CMD<20>

F7

FBD_CMD<21>

J5

FBD_CMD<22>

J6

FBD_CMD<23>

H7

FBD_CMD<24>

L8

FBD_CMD<25>

J7

SNN_FBD_CMD<26>

M5

SNN_FBD_CMD<27>

H9

SNN_FBD_CMD<28>

G9

FBD_CLK0

L9

FBD_CLK0*

M9

FBD_CLK1

J9

FBD_CLK1*

J8

H10

L11

N8

H11

H12

GND

SNN_FBD_RFU0

SNN_FBD_RFU1

SNN_FBD_DEBUG

ADD A SMALL TESTPOINT ON THIS SNN NET IN BOARD FILEADD A SMALL TESTPOINT ON THIS SNN NET IN BOARD FILE

SNN_FBD_PLLVDD

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

FBD_CMD<28..0>

8.1G<

8.1G<

8.1G<

8.1G<

8.2A<

8.2A<

8.2D<

8.2D<

8.1A< 8.1G<

602-10817-0004-200 A

p817_a02

phchan

4 OF 21

22-AUG-2008

Page 5

Page5: FrameBuffer - Partition A 32Mx32 BGA136 GDDR3

IN

S

D

G

INININININBIBIBIINBIINININININ

IN

MIRRORED

VDD

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSS

VREF

VREF

VSS

VSSA (GND)

VSSA (GND)

VDDA (VDD)

VDDA (VDD)

A12 (32Mx32)

RAS

CS0

CAS

A0

WE

A3

A2

A1

A5

A4

A11

A10

A8/AP

BA1

BA0

A9

A6

A7

BA2

CLK

CLK

NC/RFU

SEN (GND)

CKE

MF (VDDQ)

RESET

ZQ

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

IN

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

INININ

NONMIRRORED

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSSQ

VSS

VSS

VSS

VSS

VSS

VREF

VREF

A12 (32Mx32)

VDDA (VDD)

VSSA (GND)

VSSA (GND)

VDDA (VDD)

RAS

CAS

CS0

WE

A0

A2

A3

A4

A5

A1

BA1

A11

A10

A8/AP

BA0

A9

A7

A6

BA2

NC/RFU

SEN (GND)

CLK

CLK

CKE

RESET

MF (GND)

ZQ

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

BIBIBI

BI

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

5.1G< 3.1D>

R509

475

1%

0402

COMMON

3.3D> 5.1G<

3.3D> 5.1G<

MUST BE PLACED as close as possible to

the BGA memory on the line AFTER the

MEMORY pin!!

Minimize the stub length!!

CMD-Addr Mapping

144 136 ADDR

CMD15 CMD1 RAS*

CMD25 CMD10 CAS*

CMD9 CMD11 WE*

CMD8 CMD8 CS0*

CMD7 CMD7 BA2

CMD1 CMD19 A<0>

CMD3 CMD25 A<1>

CMD2 CMD22 0A<2>

CMD0 CMD24 0A<3>

CMD24 CMD0 0A<4>

CMD22 CMD2 0A<5>

CMD13 CMD4 1A<2>

CMD4 CMD6 1A<3>

CMD5 CMD5 1A<4>

CMD6 CMD13 1A<5>

CMD21 CMD21 A<6>

CMD23 CMD16 A<7>

CMD19 CMD23 A<8>

CMD20 CMD20 A<9>

CMD17 CMD17 A<10>

CMD16 CMD9 A<11>

CMD10 CMD12 BA0

CMD18 CMD3 BA1

CMD11 CMD18 CKE

CMD12 CMD15 RST

FBA_CMD<28..0>

*

M7

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

H11

K10

K11

H10

J11

J10

H3

F4

H9

F9

K4

H2

K3

M4

K9

L9

M9

K2

L4

G4

G9

H4

J2

J3

V4

1

10

11

8

19

25

22

24

0

2

21

16

23

20

17

9

12

3

7

18

14

FBA_CMD<1>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<8>

FBA_CMD<19>

FBA_CMD<25>

FBA_CMD<22>

FBA_CMD<24>

FBA_CMD<0>

FBA_CMD<2>

FBA_CMD<21>

FBA_CMD<16>

FBA_CMD<23>

FBA_CMD<20>

FBA_CMD<17>

FBA_CMD<9>

FBA_CMD<12>

FBA_CMD<3>

FBA_CMD<7>

FBA_CMD<18>

FBA_CLK0

FBA_CLK0*

SNN_FBA0_NC

FBA_CMD<14>

FBA_SEN0

15

FBA_CMD<15>

V9

A9

R506

10K

0402

COMMON

FBA_ZQ0

R49

R52

243

10K

1%

5%

5%

0402

COMMON

0402

COMMON

R504

1K

1%

0402

COMMON

A4

GND

FBVDDQ

F1

M1

A2

V2

A11

V11

F12

M12

A1

C1

E1

N1

R1

V1

C4

E4

J4

N4

R4

C9

E9

J9

N9

R9

A12

C12

E12

N12

R12

V12

B1

D1

P1

T1

G2

L2

B4

D4

P4

T4

B9

D9

P9

T9

G11

L11

B12

D12

P12

T12

GND

5.1G<

5.1G<

MUST BE PLACED as close as possible to

the BGA memory on the line AFTER the

MEMORY pin!!

Minimize the stub length!!

FBVDDQ

G1

FBA_D<8>

8

FBA_D<9>

9

FBA_D<10>

10

FBA_D<11>

11

FBA_D<12>

12

FBA_D<13>

13

FBA_D<14>

14

FBA_D<15>

15

FBA_DQM<1>

FBA_DQS_RN<1>

FBA_DQS_WP<1>

FBA_D<40>

40

FBA_D<41>

41

FBA_D<42>

42

FBA_D<43>

43

FBA_D<44>

44

FBA_D<45>

45

FBA_D<46>

46

FBA_D<47>

47

FBA_DQM<5>

FBA_DQS_RN<5>

FBA_DQS_WP<5>

L1

A3

V3

A10

V10

G12

L12

H1

H12

GND

FBA_VREF0

GND

FBB_VREF0

C91

.01UF

16V

10%

X7R

0402

COMMON

*

M7

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

G3

B3

C3

F3

C2

E2

B2

F2

E3

D3

D2

*

M8

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

C2

F3

G3

B2

C3

F2

E2

B3

E3

D3

D2

GND

C79

.01UF

16V

10%

X7R

0402

COMMON

K1

K12

C515C532

FBA_D<0>

FBA_D<1>

FBA_D<2>

FBA_D<3>

FBA_D<4>

FBA_D<5>

FBA_D<6>

FBA_D<7>

FBA_DQM<0>

FBA_DQS_RN<0>

FBA_DQS_WP<0>

FBA_D<32>

FBA_D<33>

FBA_D<34>

FBA_D<35>

FBA_D<36>

FBA_D<37>

FBA_D<38>

FBA_D<39>

FBA_DQM<4>

FBA_DQS_RN<4>

.047UF

16V

10%

X7R

0402

COMMON

J12

J1

T3

T2

R3

R2

L3

M3

M2

N2

N3

P3

P2

L10

T11

N11

M11

M10

R10

T10

R11

N10

P10

P11FBA_DQS_WP<4>

*

M7

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

*

M8

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

GND

.047UF

16V

10%

X7R

0402

COMMON

0

1

2

3

4

5

6

7

32

33

34

35

36

37

38

39

5.1G<> 3.1A<>

5.1G<> 3.2A>

5.1G<> 3.2A<

5.1G<> 3.2A>

FBA_D<63..0>

FBA_DQM<7..0>

FBA_DQS_RN<7..0>

FBA_DQS_WP<7..0>

FBA_DQM<0>

0

FBA_DQM<1>

1

FBA_DQM<2>

2

FBA_DQM<3>

3

FBA_DQM<4>

4

FBA_DQM<5>

5

FBA_DQM<6>

6

FBA_DQM<7>

7

FBA_DQS_RN<0>

0

FBA_DQS_RN<1>

1

FBA_DQS_RN<2>

2

FBA_DQS_RN<3>

3

FBA_DQS_RN<4>

4

FBA_DQS_RN<5>

5

FBA_DQS_RN<6>

6

FBA_DQS_RN<7>

7

FBA_DQS_WP<0>

0

FBA_DQS_WP<1>

1

FBA_DQS_WP<2>

2

FBA_DQS_WP<3>

3

FBA_DQS_WP<4>

4

FBA_DQS_WP<5>

5

FBA_DQS_WP<6>

6

FBA_DQS_WP<7>

7

CMD-Addr Mapping

144 136 ADDR

CMD15 CMD1 RAS*

CMD25 CMD10 CAS*

CMD9 CMD11 WE*

CMD8 CMD8 CS0*

CMD7 CMD7 BA2

CMD1 CMD19 A<0>

CMD3 CMD25 A<1>

CMD2 CMD22 0A<2>

CMD0 CMD24 0A<3>

CMD24 CMD0 0A<4>

CMD22 CMD2 0A<5>

CMD13 CMD4 1A<2>

CMD4 CMD6 1A<3>

CMD5 CMD5 1A<4>

CMD6 CMD13 1A<5>

CMD21 CMD21 A<6>

CMD23 CMD16 A<7>

CMD19 CMD23 A<8>

CMD20 CMD20 A<9>

CMD17 CMD17 A<10>

CMD16 CMD9 A<11>

CMD10 CMD12 BA0

CMD18 CMD3 BA1

CMD11 CMD18 CKE

CMD12 CMD15 RST

3.3D>

3.3D>

R513

475

0402

COMMON

1%

FBVDDQ

6.1G<

*

M7

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

16

FBA_D<17>

17

FBA_D<18>

18

FBA_D<19>

19

FBA_D<20>

20

FBA_D<21>

21

FBA_D<22>

22

FBA_D<23>

23

FBA_DQM<2>

FBA_DQS_RN<2>

FBA_DQS_WP<2>

FBA_D<48>

48

FBA_D<49>

49

FBA_D<50> E11

50

FBA_D<51>

51

FBA_D<52>

52

FBA_D<53>

53

FBA_D<54>

54

FBA_D<55>

55

FBA_DQM<6>

FBA_DQS_RN<6>

FBA_DQS_WP<6>

B10FBA_D<16>

F10

C10

B11

G10

E11

F11

C11

E10

D10

D11

*

M8

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

B11

F11

C11

F10

C10

B10

G10

E10

D10

D11

24

FBA_D<25>

25

FBA_D<26>

26

FBA_D<27>

27

FBA_D<28>

28

FBA_D<29>

29

FBA_D<30>

30

FBA_D<31>

31

FBA_DQM<3>

FBA_DQS_RN<3>

FBA_DQS_WP<3>

FBA_D<56>

56

FBA_D<57>

57

FBA_D<58> N2

58

FBA_D<59>

59

FBA_D<60>

60

FBA_D<61>

61

FBA_D<62>

62

FBA_D<63>

63

FBA_DQM<7>

FBA_DQS_RN<7>

FBA_DQS_WP<7>

NB9E-GTX/G92-760-B1,55nm SKU3 1024MB, 8pcs32Mx32 GDDR3, SLI.

FrameBuffer - Partition A 32Mx32 BGA136 GDDR3

www.vinafix.vn

1

10

11

8

19

25

4

6

5

13

21

16

23

20

17

9

12

3

7

18

14

15

FBVDDQ

GND

R10FBA_D<24>

T10

L10

M10

R11

T11

N11

M11

N10

P10

P11

R2

L3

M2

T2

T3

R3

M3

N3

P3

P2

FBA_CMD<4>

FBA_CMD<6>

FBA_CMD<5>

FBA_CMD<13>

R525

COMMON

C510

.047UF

16V

10%

X7R

0402

COMMON

FBA_CMD<1>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<8>

FBA_CMD<19>

FBA_CMD<25>

FBA_CMD<21>

FBA_CMD<16>

FBA_CMD<23>

FBA_CMD<20>

FBA_CMD<17>

FBA_CMD<9>

FBA_CMD<12>

FBA_CMD<3>

FBA_CMD<7>

FBA_CMD<18>

FBA_CLK1

FBA_CLK1*

SNN_FBA1_NC

FBA_CMD<14>

FBA_SEN1

FBA_CMD<15>

FBA_ZQ1

R507

243

0402

1K

1%

1%

0402

COMMON

GND

C569

.047UF

16V

10%

X7R

0402

COMMON

*

M7

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

*

M8

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

GND

*

M8

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

H10

F9

H4

F4

K9

H11

K10

M9

K4

H2

K3

L4

K2

M4

K11

L9

G9

G4

H3

H9

J11

J10

J2

J3

V4

V9

A9

A4

K1

K12

J1

J12

F1

M1

A2

V2

A11

V11

F12

M12

A1

C1

E1

N1

R1

V1

C4

E4

J4

N4

R4

C9

E9

J9

N9

R9

A12

C12

E12

N12

R12

V12

B1

D1

P1

T1

G2

L2

B4

D4

P4

T4

B9

D9

P9

T9

G11

L11

B12

D12

P12

T12

G1

L1

A3

V3

A10

V10

G12

L12

H1

H12

FBVDDQ

FBA_VREF0

GND

GND

GND

5.2A<

5.2A<

5.2D<

5.2D<

5.1A<

5.4A<>

5.4A<>

5.5A<>

5.5A<>

C96

.01UF

16V

10%

X7R

0402

COMMON

3.3D>

3.3D>

3.3D>

3.3D>

3.1D>

3.1A<>

3.2A>

3.2A<

3.2A>

FBVDDQ

R526

549

1%

0402

COMMON

R528

1.1K

1% 16V

0402

COMMON

GND

NET

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBA_CMD<25..0>

FBA_D<63..0>

FBA_DQM<7..0>

FBA_DQS_RN<7..0>

FBA_DQS_WP<7..0>

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

1

1

1

1

1

1

1

1

1

NV_IMPEDANCENV_CRITICALDIFFPAIR

80DIFF

80DIFF

80DIFF

80DIFF

40OHM

40OHM

40OHM

40OHM

40OHM

NET

FBA_VREF0

FBAB_VREF

FBA_VREF_CTL0

FBA_ZQ0

FBA_ZQ1

MIN_LINE_WIDTH

10MIL

10MIL

10MIL

10MIL

10MIL

R1

FBA_VREF_CTL0

1.1K

R42

COMMON

0402

1%

C550

.01UF

R2

10%

X7R

0402

COMMON

CONTINUOUS_CURRENT=0.115A

2N7002

SOT23_1G1D1S

COMMON

MAX_VOLTAGE=60V

R_DS_ON=7.5R

MAX_CURRENT=0.8A

MAX_WATTAGE=0.2W

V_BE_GS=20V

Q12

3

1G1D1S

GPIO10_FB_VREF_SW

1

2

6.3H< 7.3H< 8.3H<

10.2D>

GND

602-10817-0004-200 A

p817_a02

phchan

5 OF 21

22-AUG-2008

Page 6

IN

S

D

G

ININININBIBIBIININININBIINININ

S

D

G

IN

IN

MIRRORED

VDD

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSS

VREF

VREF

VSS

VSSA (GND)

VSSA (GND)

VDDA (VDD)

VDDA (VDD)

A12 (32Mx32)

RAS

CS0

CAS

A0

WE

A3

A2

A1

A5

A4

A11

A10

A8/AP

BA1

BA0

A9

A6

A7

BA2

CLK

CLK

NC/RFU

SEN (GND)

CKE

MF (VDDQ)

RESET

ZQ

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

INININ

NONMIRRORED

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSSQ

VSS

VSS

VSS

VSS

VSS

VREF

VREF

A12 (32Mx32)

VDDA (VDD)

VSSA (GND)

VSSA (GND)

VDDA (VDD)

RAS

CAS

CS0

WE

A0

A2

A3

A4

A5

A1

BA1

A11

A10

A8/AP

BA0

A9

A7

A6

BA2

NC/RFU

SEN (GND)

CLK

CLK

CKE

RESET

MF (GND)

ZQ

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

BIBIBI

BI

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

Page6: FrameBuffer - Partition B 32Mx32 BGA136 GDDR3

R510

475

1%

0402

COMMON

3.3H>

6.1G<

3.3H>

6.1G<

MUST BE PLACED as close as possible to

the BGA memory on the line AFTER the

MEMORY pin!!

Minimize the stub length!!

3.1H> 6.1G<

CMD-Addr Mapping

144 136 ADDR

CMD15 CMD1 RAS*

CMD25 CMD10 CAS*

CMD9 CMD11 WE*

CMD8 CMD8 CS0*

CMD7 CMD7 BA2

CMD1 CMD19 A<0>

CMD3 CMD25 A<1>

CMD2 CMD22 0A<2>

CMD0 CMD24 0A<3>

CMD24 CMD0 0A<4>

CMD22 CMD2 0A<5>

CMD13 CMD4 1A<2>

CMD4 CMD6 1A<3>

CMD5 CMD5 1A<4>

CMD6 CMD13 1A<5>

CMD21 CMD21 A<6>

CMD23 CMD16 A<7>

CMD19 CMD23 A<8>

CMD20 CMD20 A<9>

CMD17 CMD17 A<10>

CMD16 CMD9 A<11>

CMD10 CMD12 BA0

CMD18 CMD3 BA1

CMD11 CMD18 CKE

CMD12 CMD15 RST

FBB_CMD<28..0>

1

10

11

8

19

25

22

24

0

2

21

16

23

20

17

9

12

3

7

18

14

15

FBB_CMD<1>

FBB_CMD<10>

FBB_CMD<11>

FBB_CMD<8>

FBB_CMD<19>

FBB_CMD<25>

FBB_CMD<22>

FBB_CMD<24>

FBB_CMD<0>

FBB_CMD<2>

FBB_CMD<21>

FBB_CMD<16>

FBB_CMD<23>

FBB_CMD<20>

FBB_CMD<17>

FBB_CMD<9>

FBB_CMD<12>

FBB_CMD<3>

FBB_CMD<7>

FBB_CMD<18>

FBB_CLK0

FBB_CLK0*

SNN_FBB0_NC

FBB_CMD<14>

FBB_SEN0

FBB_CMD<15>

*

M5

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

H3

F4

H9

F9

K4

H2

K3

M4

K9

H11

K10

L9

K11

M9

K2

L4

G4

G9

H10

H4

J11

J10

J2

J3

V4

V9

A9

R505

10K

0402

COMMON

FBB_ZQ0

R44

R514

243

10K

1%

5%

5%

0402

COMMON

0402

COMMON

R502

1K

1%

0402

COMMON

A4

GND

FBVDDQ

F1

M1

A2

V2

A11

V11

F12

M12

A1

C1

E1

N1

R1

V1

C4

E4

J4

N4

R4

C9

E9

J9

N9

R9

A12

C12

E12

N12

R12

V12

B1

D1

P1

T1

G2

L2

B4

D4

P4

T4

B9

D9

P9

T9

G11

L11

B12

D12

P12

T12

GND

6.1G<

6.1G<

MUST BE PLACED as close as possible to

the BGA memory on the line AFTER the

MEMORY pin!!

Minimize the stub length!!

FBVDDQ

G1

L1

A3

V3

A10

V10

G12

L12

H1

H12

C78

.01UF

0402

COMMON

16V

10%

X7R

GND

GND

*

M5

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

F2

E2

F3

G3

B3

C2

B2

C3

E3

D3

D2

*

M6

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

C2

F3

G3

B2

C3

F2

E2

B3

E3

D3

D2

R48

0402

FBB_VREF1

0

COMMON

5%

16

17

18

19

20

21

22

23

48

49

50

51

52

53

54

55

FBB_VREF0

FBB_D<17>

FBB_D<18>

FBB_D<19>

FBB_D<20>

FBB_D<21>

FBB_D<22>

FBB_D<23>

FBB_DQM<2>

FBB_DQS_RN<2>

FBB_DQS_WP<2>

FBB_D<48>

FBB_D<49>

FBB_D<50>

FBB_D<51> M3

FBB_D<52>

FBB_D<53>

FBB_D<54>

FBB_D<55>

FBB_DQM<6>

FBB_DQS_RN<6>

FBB_DQS_WP<6>

3.1E<> 6.1G<>

3.2E>

6.1G<>

3.2E<

6.1G<>

3.2E> 6.1G<>

FBB_D<63..0>

FBB_DQM<7..0>

FBB_DQS_RN<7..0>

FBB_DQS_WP<7..0>

K1

K12

C90

.047UF

16V

10%

X7R

0402

COMMON

C540

.047UF

16V

10%

X7R

0402

COMMON

J12

J1

GND

*

M5

DDR3BGA136

PACK_TYPE=BGA136_V2

VERSION=BGA136

COMMON

FBB_D<0>

0

FBB_D<1>

1

FBB_D<2>

2

FBB_D<3>

3

FBB_D<4>

4

FBB_DQM<0>

0

FBB_DQM<1>

1

FBB_DQM<2>

2

FBB_DQM<3>

3

FBB_DQM<4>

4

FBB_DQM<5>

5

FBB_DQM<6>

6

FBB_DQM<7>

7

FBB_DQS_RN<0>

0

FBB_DQS_RN<1>

1

FBB_DQS_RN<2>

2

FBB_DQS_RN<3>

3

FBB_DQS_RN<4>

4

FBB_DQS_RN<5>

5

FBB_DQS_RN<6>

6

FBB_DQS_RN<7>

7

FBB_DQS_WP<0>

0

FBB_DQS_WP<1>

1

FBB_DQS_WP<2>

2

FBB_DQS_WP<3>

3