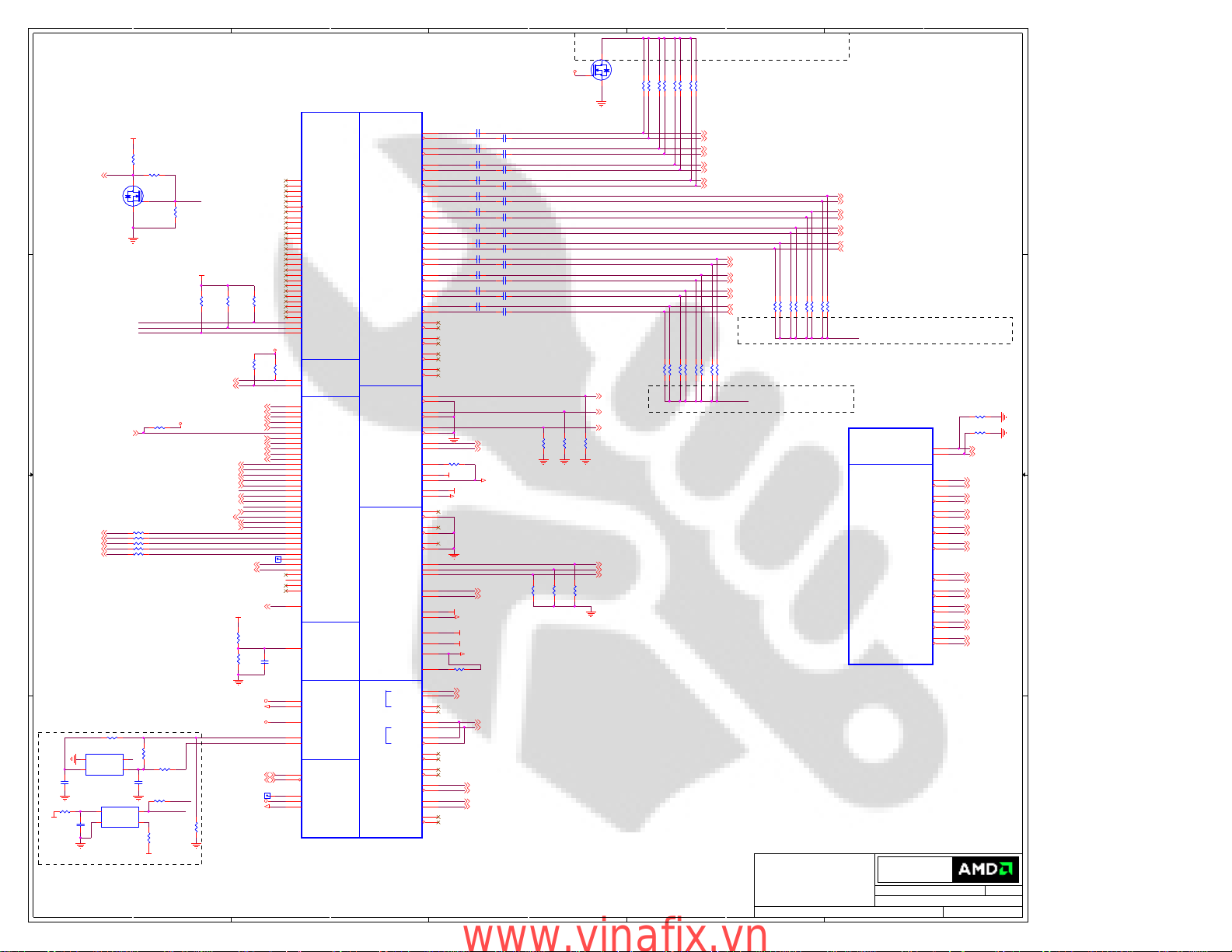

Page 1

5

U1A

U1A

4

3

2

1

PCIE_RXP0

C1401

C1401

220nF

220nF

PCIE_RXN0

PCIE_RXP1

PCIE_RXN1

PCIE_RXP2

PCIE_RXN2

PCIE_RXP3

PCIE_RXN3

PCIE_RXP4

PCIE_RXN4

PCIE_RXP5

PCIE_RXN5

PCIE_RXP6

PCIE_RXN6

PCIE_RXP7

PCIE_RXN7

PCIE_RXP8

PCIE_RXN8

PCIE_RXP9

PCIE_RXN9

PCIE_RXP10

PCIE_RXN10

PCIE_RXP11

PCIE_RXN11

PCIE_RXP12

PCIE_RXN12

PCIE_RXP13

PCIE_RXN13

PCIE_RXP14

PCIE_RXN14

PCIE_RXP15

PCIE_RXN15

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_RST#

D D

C C

B B

MVDDC_GOOD10,12

A A

For M97 Only

R13120RR1312

5

0R

DNI

DNI

AA38

PCIE_RX0P

Y37

PCIE_RX0N

Y35

PCIE_RX1P

W36

PCIE_RX1N

W38

PCIE_RX2P

V37

PCIE_RX2N

V35

PCIE_RX3P

U36

PCIE_RX3N

U38

PCIE_RX4P

T37

PCIE_RX4N

T35

PCIE_RX5P

R36

PCIE_RX5N

R38

PCIE_RX6P

P37

PCIE_RX6N

P35

PCIE_RX7P

N36

PCIE_RX7N

N38

PCIE_RX8P

M37

PCIE_RX8N

M35

PCIE_RX9P

L36

PCIE_RX9N

L38

PCIE_RX10P

K37

PCIE_RX10N

K35

PCIE_RX11P

J36

PCIE_RX11N

J38

PCIE_RX12P

H37

PCIE_RX12N

H35

PCIE_RX13P

G36

PCIE_RX13N

G38

PCIE_RX14P

F37

PCIE_RX14N

F35

PCIE_RX15P

E37

PCIE_RX15N

CLOCK

CLOCK

AB35

PCIE_REFCLKP

AA36

PCIE_REFCLKN

AJ21

NC#1

AK21

NC#2

AH16

NC_PWRGOOD

AA30

PERSTB

M96 A11 HF MVD SLT B1

M96 A11 HF MVD SLT B1

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCI EXPRESS INTERFACE

PCI EXPRESS INTERFACE

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

CALIBRATION

CALIBRATION

PCIE_CALRP

PCIE_CALRN

4

Y33

Y32

W33

W32

U33

U32

U30

U29

T33

T32

T30

T29

P33

P32

P30

P29

N33

N32

N30

N29

L33

L32

L30

L29

K33

K32

J33

J32

K30

K29

H33

H32

Y30

Y29

PCIE_TXP0

PCIE_TXN0

PCIE_TXP1

PCIE_TXN1

PCIE_TXP2

PCIE_TXN2

PCIE_TXP3

PCIE_TXN3

PCIE_TXP4

PCIE_TXN4

PCIE_TXP5

PCIE_TXN5

PCIE_TXP6

PCIE_TXN6

PCIE_TXP7

PCIE_TXN7

PCIE_TXP8

PCIE_TXN8

PCIE_TXP9

PCIE_TXN9

PCIE_TXP10

PCIE_TXN10

PCIE_TXP11

PCIE_TXN11

PCIE_TXP12

PCIE_TXN12

PCIE_TXP13

PCIE_TXN13

PCIE_TXP14

PCIE_TXN14

PCIE_TXP15

PCIE_TXN15

R1

1.27KR11.27K

R2

2.0KR22.0K

1.1V_REG

3

PCIE_RST#10

PCIE_REFCLKP10

PCIE_REFCLKN10

PCIE_RXP[15..0]10

PCIE_RXN[15..0]10

PCIE_TXP[15..0]10

PCIE_TXN[15..0]10

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH M92/M96 M package MXM2.1A DDR2

RH M92/M96 M package MXM2.1A DDR2

RH M92/M96 M package MXM2.1A DDR2

2

PCIE_RST#

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_RXP[15..0]

PCIE_RXN[15..0]

PCIE_TXP[15..0]

PCIE_TXN[15..0]

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Wednesday, August 27, 2008

Wednesday, August 27, 2008

Wednesday, August 27, 2008

Sheet

Sheet

Sheet

of

1 14

of

1 14

of

1 14

Doc No.

Doc No.

Doc No.

105-B80631-00A

105-B80631-00A

105-B80631-00A

1

RevDate:

RevDate:

RevDate:

0

0

0

www.vinafix.vn

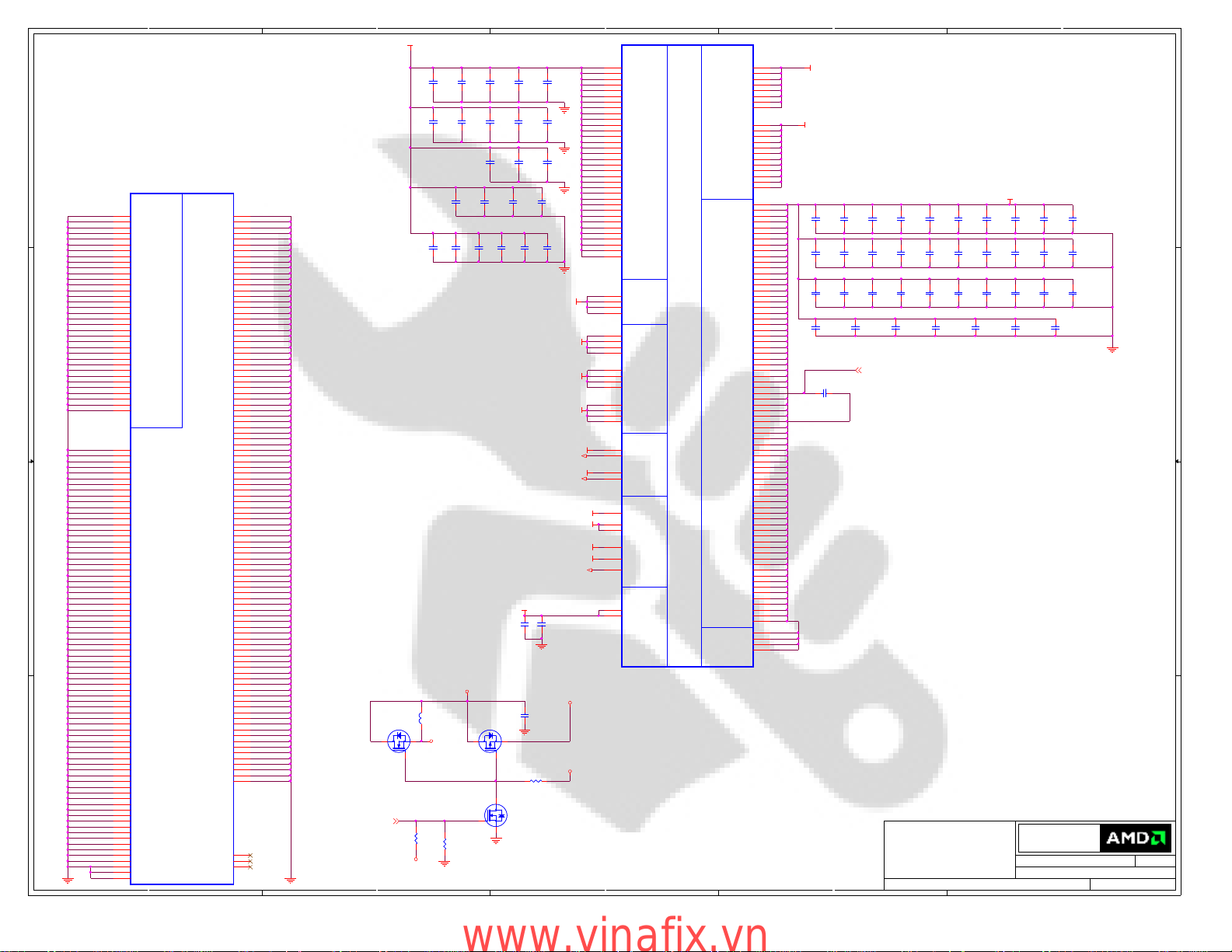

Page 2

5

CTFb10,11

GND2

XTAL11XTAL2

XGND

4

2

C1213

C1213

1uF

1uF

R1147 0RR1147 0R

DNI

+3VRUN_BUS

R24

R24

10K

10K

32

Q1

1

2N7002_NLQ12N7002_NL

MEM_ID0

MEM_ID1

MEM_ID2

R1130 10KR1130 10K

AC_BAT#10

R1285 0RR1285 0R

RP1A 33RRP1A 33R

81

RP1B 33RRP1B 33R

72

RP1C 33RRP1C 33R

63

RP1D

RP1D

54

PLACE VREFG DIVIDER AND CAP

CLOSE TO ASIC

DPLL_PVDD: Display PLL Analog Power

(DPLL_PVDD: 1.8V@ 120mA)

DPLL_VDDC: Display PLL Digital Power

(DPLL_VDDC: 1.1V@300mA)

DNI

R999

R999

61.9R

61.9R

Y1

XGND

4

GND4

XOUTXIN

R1150 0RR1150 0R

3

27MHzY127MHz

DNI

C328

C328

18pF_50V

18pF_50V

Y2

3

VCC

OUT

XIN

1

GND

E/D

27.000MHzY227.000MHz

OSC

+3VRUN

33R

33R

DNI

R11510RR1151

R11551KR1155

1K

R260RR26

0R

DNI

0R

R27

R27

10K

10K

+3VRUN

GPIO16_SS

XOUT

CTF

1.8V_REG

R444

R444

R445

R445

R446

10K

10K

I2C_CLK10

I2C_DAT10

MB_ALERTB11

P1

TSVDD: Temperature sensor power

R1153

R1153

75R

75R

R446

10K

10K C1211 100nF_6.3VC1211 100nF_6.3V

10K

10K

+3VRUN

R6

R5

4.7KR64.7K

4.7KR54.7K

GPIO010,11

GPIO111

GPIO211

PBAT_SMBDAT10,11

PBAT_SMBCLK10,11

GPIO613

GPIO7_BLON10

SOUT11

SIN11

SCLK11

GPIO1111

GPIO1211

GPIO1311

HPD_210

GPIO1513

GPIO16_SS

HPD_310

CTF

GPIO2013

BB_EN3

SCS#11

CLKREQB10

TP68TP68

GENERICB

GENERICC11

HPD_110

1.8V_REG

R18

R18

499R

499R

R20

R20

249R

249R C1

100nFC1100nF

DPLL_PVDD

GND_PVSS

DPLL_VDDC

XIN_A

XOUT_A

GPU_DPLUS11

GPU_DMINUS11

TP44TP44

TSVDD

TSVSS

(TSVDD: 1.8V@20mA)

D D

C C

JTAG_RSTb10

JTAG_TDI10

JTAG_TCK10

JTAG_TMS10

JTAG_TDO10

B B

2

C327

C327

CRY

DNI

18pF_50V

18pF_50V

A A

R12840RR1284

0R

+3VRUN

USE OVERLAP FOOT PRINT

5

U1B

U1B

AR8

DVPCNTL_MVP_0

AU8

DVPCNTL_MVP_1

AP8

DVPCNTL_0

AW8

DVPCNTL_1

AR3

DVPCNTL_2

AR1

DVPCLK

AU1

DVPDATA_0

AU3

DVPDATA_1

AW3

DVPDATA_2

AP6

DVPDATA_3

AW5

DVPDATA_4

AU5

DVPDATA_5

AR6

DVPDATA_6

AW6

DVPDATA_7

AU6

DVPDATA_8

AT7

DVPDATA_9

AV7

DVPDATA_10

AN7

DVPDATA_11

AV9

DVPDATA_12

AT9

DVPDATA_13

AR10

DVPDATA_14

AW10

DVPDATA_15

AU10

DVPDATA_16

AP10

DVPDATA_17

AV11

DVPDATA_18

AT11

DVPDATA_19

AR12

DVPDATA_20

AW12

DVPDATA_21

AU12

DVPDATA_22

AP12

DVPDATA_23

AK26

SCL

AJ26

SDA

GENERAL PURPOSE I/O

GENERAL PURPOSE I/O

AH20

GPIO_0

AH18

GPIO_1

AN16

GPIO_2

AH23

GPIO_3_SMBDATA

AJ23

GPIO_4_SMBCLK

AH17

GPIO_5_AC_BATT

AJ17

GPIO_6

AK17

GPIO_7_BLON

AJ13

GPIO_8_ROMSO

AH15

GPIO_9_ROMSI

AJ16

GPIO_10_ROMSCK

AK16

GPIO_11

AL16

GPIO_12

AM16

GPIO_13

AM14

GPIO_14_HPD2

AM13

GPIO_15_PWRCNTL_0

AK14

GPIO_16_SSIN

AG30

GPIO_17_THERMAL_INT

AN14

GPIO_18_HPD3

AM17

GPIO_19_CTF

AL13

GPIO_20_PWRCNTL_1

AJ14

GPIO_21_BB_EN

AK13

GPIO_22_ROMCSB

AN13

GPIO_23_CLKREQB

AM23

JTAG_TRSTB

AN23

JTAG_TDI

AK23

JTAG_TCK

AL24

JTAG_TMS

AM24

JTAG_TDO

AJ19

GENERICA

AK19

GENERICB

AJ20

GENERICC

AK20

GENERICD

AJ24

GENERICE_HPD4

AH26

GENERICF

AH24

GENERICG

AK24

HPD1

AH13

VREFG

AM32

DPLL_PVDD

AN32

DPLL_PVSS

AN31

DPLL_VDDC

AV33

XTALIN

AU34

XTALOUT

AF29

DPLUS

AG29

DMINUS

AK32

TS_FDO

AJ32

TSVDD

AJ33

TSVSS

4

MUTI GFX

MUTI GFX

I2C

I2C

PLL/CLOCK

PLL/CLOCK

THERMAL

THERMAL

M96 A11 HF MVD SLT B1

M96 A11 HF MVD SLT B1

4

TXCAP_DPA3P

TXCAM_DPA3N

TX0P_DPA2P

TX0M_DPA2N

DPA

DPA

TX1P_DPA1P

TX1M_DPA1N

TX2P_DPA0P

TX2M_DPA0N

TXCBP_DPB3P

TXCBM_DPB3N

TX3P_DPB2P

TX3M_DPB2N

DPB

DPB

TX4P_DPB1P

TX4M_DPB1N

TX5P_DPB0P

TX5M_DPB0N

TXCCP_DPC3P

TXCCM_DPC3N

TX0P_DPC2P

TX0M_DPC2N

DPC

DPC

TX1P_DPC1P

TX1M_DPC1N

TX2P_DPC0P

TX2M_DPC0N

TXCDP_DPD3P

TXCDM_DPD3N

TX3P_DPD2P

TX3M_DPD2N

DPD

DPD

TX4P_DPD1P

TX4M_DPD1N

TX5P_DPD0P

TX5M_DPD0N

DAC1

DAC1

DAC2

DAC2

DDC/AUX

DDC/AUX

DDC1DATA

DDC2DATA

DDCCLK_AUX3P

DDCDATA_AUX3N

DDCCLK_AUX4P

DDCDATA_AUX4N

DDCCLK_AUX5P

DDCDATA_AUX5N

DDC6DATA

NC_DDCCLK_AUX7P

NC_DDCDATA_AUX7N

HSYNC

VSYNC

RSET

AVDD

AVSSQ

VDD1DI

VSS1DI

COMP

H2SYNC

V2SYNC

VDD2DI

VSS2DI

A2VDD

A2VDDQ

A2VSSQ

R2SET

DDC1CLK

AUX1P

AUX1N

DDC2CLK

AUX2P

AUX2N

DDC6CLK

3

+5VRUN

DVI_GND

32

Q29

Q29

1

SI2304DS

SI2304DS

R1003499RR1003499R

R1002499RR1002499R

R1004499RR1004499R

R1006499RR1006499R

R1005499RR1005499R

2

Add a Solid plane to these pads

R1008499R R1008499R

R1009499R R1009499R

R1007499R R1007499R

1

P1

C610 100nF_6.3VC610 100nF_6.3V

AU24

AV23

AT25

AR24

AU26

AV25

AT27

AR26

AR30

AT29

AV31

AU30

AR32

AT31

AT33

AU32

AU14

AV13

AT15

AR14

AU16

AV15

AT17

AR16

AU20

AT19

AT21

AR20

AU22

AV21

AT23

AR22

AD39

R

AD37

RB

AE36

G

AD35

GB

AF37

B

AE38

BB

AC36

AC38

AB34

AD34

AE34

AC33

AC34

AC30

R2

AC31

R2B

AD30

G2

AD31

G2B

AF30

B2

AF31

B2B

AC32

C

AD32

Y

AF32

AD29

AC29

AG31

AG32

AG33

AD33

AF33

AA29

AM26

AN26

AM27

AL27

AM19

AL19

AN20

AM20

AL30

AM30

AL29

AM29

AN21

AM21

AJ30

AJ31

AK30

AK29

C616 100nF_6.3VC616 100nF_6.3V

C611 100nF_6.3VC611 100nF_6.3V

C612 100nF_6.3VC612 100nF_6.3V

C617 100nF_6.3VC617 100nF_6.3V

C618 100nF_6.3VC618 100nF_6.3V

C619 100nF_6.3VC619 100nF_6.3V

C620 100nF_6.3VC620 100nF_6.3V

C613 100nF_6.3VC613 100nF_6.3V

C621 100nF_6.3VC621 100nF_6.3V

C614 100nF_6.3VC614 100nF_6.3V

C622 100nF_6.3VC622 100nF_6.3V

C623 100nF_6.3VC623 100nF_6.3V

C624 100nF_6.3VC624 100nF_6.3V

C625 100nF_6.3VC625 100nF_6.3V

C626 100nF_6.3VC626 100nF_6.3V

C1205 100nF_6.3VC1205 100nF_6.3V

C1206 100nF_6.3VC1206 100nF_6.3V

C1207 100nF_6.3VC1207 100nF_6.3V

C1208 100nF_6.3VC1208 100nF_6.3V

C1209 100nF_6.3VC1209 100nF_6.3V

C1210 100nF_6.3VC1210 100nF_6.3V

C1212 100nF_6.3VC1212 100nF_6.3V

VGA_RED

VGA_GRN

VGA_BLU

HSYNC 10,11

VSYNC 10,11

R1135

R1135

499R

499R

AVDD

VDD1DI

VSS1DI

VDD2DI

AVDD: DAC1 Analog Power

AVSSQ

AVDD: 1.8V@70mA)

VDD1DI: DAC1 Digital Power

(VDD1DI: 1.8V@42mA)

H2SYNC 11

V2SYNC 11

(VDD2DI: 1.8V@40mA)

VDD2DI: DAC2 Digital Power

VSS2DI

A2VDD:CRT for DAC2

A2VDD

(A2VDD:3.3V@65mA)

A2VDDQ

A2VDDQ: DAC2 Band Gap (clean) power supply

A2VDDQ: 1.8V@ 1mA)

A2VSSQ

R1144

R1144

715R

715R

DDC1CLK 10

DDC1DAT 10

DDC2CLK 10

DDC2DAT 10

DDC5CLK 10

DDC5DAT 10

DDC6CLK 10,11

DDC6DAT 10,11

PLACE RGB TERMINATION

RESISTORS CLOSE TO ASIC

R1132

R1132

150R

150R

PLACE RGB TERMINATION

RESISTORS CLOSE TO ASIC

R1141

R1141

R1142

R1142

150R

150R

150R

150R

3

R1133

R1133

150R

150R

R1143

R1143

150R

150R

VGA_RED 10

VGA_GRN 10

VGA_BLU 10

R1134

R1134

150R

150R

TV_CR_PR 10

TV_Y_G 10

TV_COMP_B_PB 10

DPA3P 10

DPA3N 10

DPA2P 10

DPA2N 10

DPA1P 10

DPA1N 10

DPA0P 10

DPA0N 10

DPC3P 10

DPC3N 10

DPC2P 10

DPC2N 10

DPC1P 10

DPC1N 10

DPC0P 10

R1010499RR1010499R

R1012499RR1012499R

R1013499RR1013499R

R1011499RR1011499R

DPC0N 10

R1128499RR1128499R

R1126499RR1126499R

R1121499RR1121499R

R1127499RR1127499R

R1122499RR1122499R

R1125499RR1125499R

R1123499RR1123499R

R1124499RR1124499R

P1

Add a Solid plane to

these pads

DVI_GND

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

M96 GDDR3 MXMII 2.1A Crossfire

M96 GDDR3 MXMII 2.1A Crossfire

M96 GDDR3 MXMII 2.1A Crossfire

2

TXBCP 10

TXBCM 10

TXB0P 10

TXB0M 10

TXB1P 10

TXB1M 10

TXB2P 10

TXB2M 10

P4

R1014499RR1014499R

R1017499RR1017499R

R1016499RR1016499R

R1015499RR1015499R

Add a Solid plane to these pads

DVI_GND

R4

10KR410K

R1303

AK27

AJ27

AK35

AL36

AJ38

AK37

AH35

AJ36

AG38

AH37

AF35

AG36

AP34

AR34

AW37

AU35

AR37

AU39

AP35

AR35

AN36

AP37

Doc No.

Doc No.

Doc No.

R1303

10K

10K

BLON_PWM 10

DIGON 10

TXCLK_U+ 10

TXCLK_U- 10

TXOUT_U0+ 10

TXOUT_U0- 10

TXOUT_U1+ 10

TXOUT_U1- 10

TXOUT_U2+ 10

TXOUT_U2- 10

TXOUT_U3+ 10

TXOUT_U3- 10

TXCLK_L+ 10

TXCLK_L- 10

TXOUT_L0+ 10

TXOUT_L0- 10

TXOUT_L1+ 10

TXOUT_L1- 10

TXOUT_L2+ 10

TXOUT_L2- 10

TXOUT_L3+ 10

TXOUT_L3- 10

RevDate:

RevDate:

RevDate:

105-B786xx-00A

105-B786xx-00A

105-B786xx-00A

0

0

0

U1G

U1G

LVDS CONTROL

LVDS CONTROL

TXOUT_U0P_DPF2P

TXOUT_U0N_DPF2N

TXOUT_U1P_DPF1P

TXOUT_U1N_DPF1N

TXOUT_U2P_DPF0P

TXOUT_U2N_DPF0N

LVTMDP

LVTMDP

TXOUT_L0P_DPE2P

TXOUT_L0N_DPE2N

TXOUT_L1P_DPE1P

TXOUT_L1N_DPE1N

TXOUT_L2P_DPE0P

TXOUT_L2N_DPE0N

M96 A11 HF MVD SLT B1

M96 A11 HF MVD SLT B1

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Sheet

Sheet

Sheet

VARY_BL

DIGON

TXCLK_UP_DPF3P

TXCLK_UN_DPF3N

TXOUT_U3P

TXOUT_U3N

TXCLK_LP_DPE3P

TXCLK_LN_DPE3N

TXOUT_L3P

TXOUT_L3N

Wednesday, September 03, 2008

Wednesday, September 03, 2008

Wednesday, September 03, 2008

of

2 14

of

2 14

of

2 14

1

www.vinafix.vn

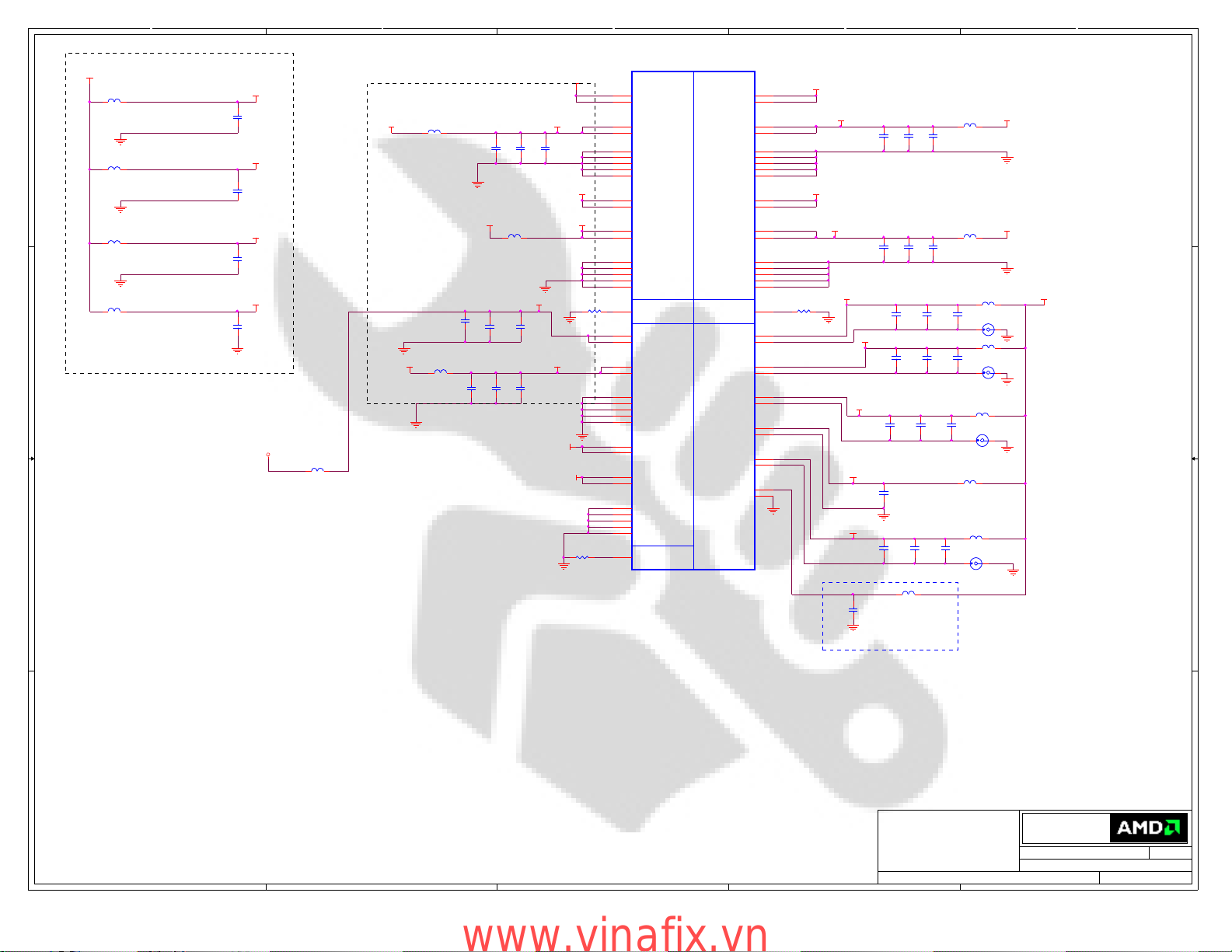

Page 3

5

D D

M96 A11 HF MVD SLT B1U1F

M96 A11 HF MVD SLT B1U1F

AB39

PCIE_VSS#1

E39

PCIE_VSS#2

F34

PCIE_VSS#3

F39

PCIE_VSS#4

G33

PCIE_VSS#5

G34

PCIE_VSS#6

H31

PCIE_VSS#7

H34

PCIE_VSS#8

H39

PCIE_VSS#9

J31

PCIE_VSS#10

J34

PCIE_VSS#11

K31

PCIE_VSS#12

K34

PCIE_VSS#13

K39

PCIE_VSS#14

L31

PCIE_VSS#15

L34

PCIE_VSS#16

M34

PCIE_VSS#17

M39

PCIE_VSS#18

N31

PCIE_VSS#19

N34

PCIE_VSS#20

P31

PCIE_VSS#21

P34

PCIE_VSS#22

P39

PCIE_VSS#23

R34

PCIE_VSS#24

T31

C C

B B

A A

T34

T39

U31

U34

V34

V39

W31

W34

Y34

Y39

F15

F17

F19

F21

F23

F25

F27

F29

F31

F33

J27

K14

L11

L17

L22

L24

M17

M22

M24

N16

N18

N21

N23

N26

R15

R17

R20

R22

R24

R27

T11

T13

T16

T18

T21

T23

T26

U15

U17

U20

U22

U24

U27

V11

V16

V18

V21

V23

V26

W2

W6

Y15

Y17

Y20

Y22

Y24

Y27

U13

V13

F7

F9

G2

G6

H9

J2

J6

J8

K7

L2

L6

N2

N6

R2

R6

U2

U6

PCIE_VSS#25

PCIE_VSS#26

PCIE_VSS#27

PCIE_VSS#28

PCIE_VSS#29

PCIE_VSS#30

PCIE_VSS#31

PCIE_VSS#32

PCIE_VSS#33

PCIE_VSS#34

PCIE_VSS#35

GND#101

GND#102

GND#103

GND#104

GND#105

GND#106

GND#107

GND#108

GND#109

GND#110

GND#111

GND#112

GND#113

GND#114

GND#115

GND#116

GND#117

GND#118

GND#119

GND#120

GND#121

GND#122

GND#123

GND#124

GND#125

GND#126

GND#127

GND#128

GND#129

GND#130

GND#131

GND#132

GND#133

GND#134

GND#135

GND#136

GND#137

GND#138

GND#139

GND#140

GND#141

GND#142

GND#143

GND#144

GND#145

GND#146

GND#147

GND#148

GND#149

GND#150

GND#151

GND#152

GND#153

GND#154

GND#155

GND#156

GND#157

GND#158

GND#159

GND#160

GND#161

GND#162

GND#163

GND#164

GND#165

GND#166

GND#167

GND#168

GND#169

GND#170

GND#171

GND#172

GND#173

GND#174

GND#175

GND#176

5

GND

GND

GND#1

GND#2

GND#3

GND#4

GND#5

GND#6

GND#7

GND#8

GND#9

GND#10

GND#11

GND#12

GND#13

GND#14

GND#15

GND#16

GND#17

GND#18

GND#19

GND#20

GND#21

GND#22

GND#23

GND#24

GND#25

GND#26

GND#27

GND#28

GND#29

GND#30

GND#31

GND#32

GND#33

GND#34

GND#35

GND#36

GND#37

GND#38

GND#39

GND#40

GND#41

GND#42

GND#43

GND#44

GND#45

GND#46

GND#47

GND#48

GND#49

GND#50

GND#51

GND#52

GND#53

GND#54

GND#55

GND#56

GND#57

GND#58

GND#59

GND#60

GND#61

GND#62

GND#63

GND#64

GND#65

GND#66

GND#67

GND#68

GND#69

GND#70

GND#71

GND#72

GND#73

GND#74

GND#75

GND#76

GND#77

GND#78

GND#79

GND#80

GND#81

GND#82

GND#83

GND#84

GND#85

GND#86

GND#87

GND#88

GND#89

GND#90

GND#91

GND#92

GND#93

GND#94

GND#95

GND#96

GND#97

GND#98

GND#99

GND#100

VSS_MECH#1

VSS_MECH#2

VSS_MECH#3

A3

A37

AA16

AA18

AA2

AA21

AA23

AA26

AA28

AA6

AB12

AB15

AB17

AB20

AB22

AB24

AB27

AC11

AC13

AC16

AC18

AC2

AC21

AC23

AC26

AC28

AC6

AD15

AD17

AD20

AD22

AD24

AD27

AD9

AE2

AE6

AF10

AF16

AF18

AF21

AG17

AG2

AG20

AG22

AG6

AG9

AH21

AH29

AJ10

AJ11

AJ2

AJ28

AJ6

AK11

AK31

AK7

AL11

AL14

AL17

AL2

AL20

AL21

AL23

AL26

AL32

AL6

AL8

AM11

AM31

AM9

AN11

AN2

AN30

AN6

AN8

AP11

AP7

AP9

AR5

AW34

B11

B13

B15

B17

B19

B21

B23

B25

B27

B29

B31

B33

B7

B9

C1

C39

E35

E5

F11

F13

A39

AW1

AW39

4

MVDDC

C6

1uFC61uF

C11

C11

1uF

1uF

C2

10uF_6.3VC210uF_6.3V

(+1.8V 0R VDDC @ 120MA BBP)

Q18

Q18

2N7002E

2N7002E

**

L39

L39

A

DNI

VDDC

BLM15BD121SN1

BLM15BD121SN1

3 2

1

BB_EN2

R1162

R1162

10K

10K

+3VRUN

4

C8

C7

1uFC81uF

1uFC71uF

C13

C13

C12

C12

1uF

1uF

1uF

1uF

C16

C16

1uF

1uF

C1217

C1217

C1215

C1215

100nF

100nF

100nF

100nF

C3

C4

10uF_6.3VC510uF_6.3V

10uF_6.3VC310uF_6.3V

10uF_6.3VC410uF_6.3V

VDD_CT:Level translation between core and I/O

(VDD_CT: 1.8V@ 136mA)

VDDR3:ROM+Sync+DDC

(VDDR3: 3.3V@60mA)

VDDR4_5:Power for DVP control pins

(VDDR4_5: 1.8V@ 20/170mA)

C10

C10

C9

1uF

1uF

1uFC91uF

C14

C14

C15

C15

1uF

1uF

1uF

1uF

C17

C17

C1214

C1214

1uF

1uF

1uF

1uF

C1216

C1216

C1218

C1218

100nF

100nF

100nF

100nF

C5

C1225

C1225

C1226

C1226

10uF_6.3V

10uF_6.3V C1228

10uF_6.3V

10uF_6.3V C1220

VDD_CT

VDDR3

VDDR4_5

VDDR4 for DVPDATA[12..23]

VDDR4_5

VDDR5 for DVPDATA[0..11]

VDDRHA:MCLK PAD Power

(VDDRHA: 1.8V@20mA?)

VDDRHB:MCLK PAD Power

(VDDRHB: 1.8V@20mA?)

PCIE_PVDD:PCI-E PLL power.

(PCIE_PVDD: 1.8V@ 68mA)

SPV10: Dedicated power pin for memory

and engine PLLs.

(SPV10: VDDC@414mA)

+BBP

Q19

Q19

Si2301BDS

Si2301BDS

C1241

C1241

1uF

1uF

+BBP

C405

C405

1uF_6.3V

1uF_6.3V

GND_VSSRHA

GND_VSSRHB

PCIE_PVDD

C1242

C1242

100nF

100nF

1.8V_REG

23

FET BFET C

1

32

Q20

Q20

1

2N7002_NL

2N7002_NL

FET A

R657

R657

10K

10K

R655 100KR655 100K

+5VRUN

OR R1= (Vout/1.24-1)*R2

3

U1E

U1E

MEM I/O

MEM I/O

AC7

VDDR1#1

AD11

VDDR1#2

AF7

VDDR1#3

AG10

VDDR1#4

AJ7

VDDR1#5

AK8

VDDR1#6

AL9

VDDR1#7

G11

VDDR1#8

G14

VDDR1#9

G17

VDDR1#10

G20

VDDR1#11

G23

VDDR1#12

G26

VDDR1#13

G29

VDDR1#14

H10

VDDR1#15

J7

VDDR1#16

J9

VDDR1#17

K11

VDDR1#18

K13

VDDR1#19

K8

VDDR1#20

L12

VDDR1#21

L16

VDDR1#22

L21

VDDR1#23

L23

VDDR1#24

L26

VDDR1#25

L7

VDDR1#26

M11

VDDR1#27

N11

VDDR1#28

P7

VDDR1#29

R11

VDDR1#30

U11

VDDR1#31

U7

VDDR1#32

Y11

VDDR1#33

Y7

VDDR1#34

LEVEL

LEVEL

TRANSLATION

TRANSLATION

AF26

VDD_CT#1

AF27

VDD_CT#2

AG26

VDD_CT#3

AG27

VDD_CT#4

I/O

I/O

AF23

VDDR3#1

AF24

VDDR3#2

AG23

VDDR3#3

AG24

VDDR3#4

AF13

VDDR5#1

AF15

VDDR5#2

AG13

VDDR5#3

AG15

VDDR5#4

AD12

VDDR4#1

AF11

VDDR4#2

AF12

VDDR4#3

AG11

VDDR4#4

MEM CLK

MEM CLK

M20

VDDRHA

VDDRHB

MPV18

SPV18

SPV10

SPVSS

USE R1 to change +BBP

VOUT= 1.24 X( 1+R1/R2)

VDDRHA

M21

VSSRHA

V12

VDDRHB

U12

VSSRHB

AB37

PCIE_PVDD

H7

NC_MPV18#1

H8

NC_MPV18#2

AM10

NC_SPV18

AN9

SPV10

AN10

SPVSS

BACK BIAS

BACK BIAS

AA13

BBP#1

Y13

BBP#2

M96 A11 HF MVD SLT B1

M96 A11 HF MVD SLT B1

3

PLL

PLL

PCIE

PCIE

AA31

PCIE_VDDR#1

AA32

PCIE_VDDR#2

AA33

PCIE_VDDR#3

AA34

PCIE_VDDR#4

V28

PCIE_VDDR#5

W29

PCIE_VDDR#6

W30

PCIE_VDDR#7

Y31

PCIE_VDDR#8

G30

PCIE_VDDC#1

G31

PCIE_VDDC#2

H29

PCIE_VDDC#3

H30

PCIE_VDDC#4

J29

PCIE_VDDC#5

J30

PCIE_VDDC#6

L28

PCIE_VDDC#7

M28

PCIE_VDDC#8

N28

PCIE_VDDC#9

R28

PCIE_VDDC#10

T28

PCIE_VDDC#11

U28

PCIE_VDDC#12

AA15

VDDC#1

CORE

CORE

POWER

POWER

ISOLATED

ISOLATED

CORE I/O

CORE I/O

BB_ENA = 0V FOR BACK BIASING DISABLED

N FET A = OFF, P FET B = OFF, N FET C = ON

+BBP = VDD_CORE

BB_ENA = +3.3V FOR BACK BIASING ENABLED

N FET A = ON, P FET B = ON, N FET C = OFF

+BBP = +1.8V

** FOR NO BACK BIASING

DO NOT INSTALL FETS

AND INSTALL BEAD A

VDDC#2

VDDC#3

VDDC#4

VDDC#5

VDDC#6

VDDC#7

VDDC#8

VDDC#9

VDDC#10

VDDC#11

VDDC#12

VDDC#13

VDDC#14

VDDC#15

VDDC#16

VDDC#17

VDDC#18

VDDC#19

VDDC#20

VDDC#21

VDDC#22

VDDC#23

VDDC#24

VDDC#25

VDDC#26

VDDC#27

VDDC#28

VDDC#29

VDDC#30

VDDC#31

VDDC#32

VDDC#33

VDDC#34

VDDC#35

VDDC#36

VDDC#37

VDDC#38

VDDC#39

VDDC#40

VDDC#41

VDDC#42

VDDC#43

VDDC#44

VDDC#45

VDDC#46

VDDC#47

VDDC#48

VDDC#49

VDDC#50

VDDC#51

VDDC#52

VDDC#53

VDDC#54

VDDC#55

VDDC#56

VDDC#57

VDDC#58

VDDC#59

VDDC#60

VDDC#61

VDDC#62

VDDC#63

VDDC#64

VDDC#65

VDDC#66

VDDC#67

VDDC#68

VDDC#69

VDDC#70

VDDC#71

VDDC#72

VDDC#73

VDDC#74

VDDCI#1

VDDCI#2

VDDCI#3

VDDCI#4

AA17

AA20

AA22

AA24

AA27

AB13

AB16

AB18

AB21

AB23

AB26

AB28

AC12

AC15

AC17

AC20

AC22

AC24

AC27

AD13

AD16

AD18

AD21

AD23

AD26

AF17

AF20

AF22

AG16

AG18

AG21

AH22

M16

M18

M23

M26

N15

N17

N20

N22

N24

N27

R13

R16

R18

R21

R23

R26

T15

T17

T20

T22

T24

T27

U16

U18

U21

U23

U26

V15

V17

V20

V22

V24

V27

Y16

Y18

Y21

Y23

Y26

Y28

AH27

AH28

M15

N13

R12

T12

PCIE_VDDR

PCIE_VDDR:PCI-E I/O power.

(PCIE_VDDR: 1.8V@ 500mA)

PCIE_VDDC

PCIE_VDDC: PCI-E Digital Power Supply

(PCIE_VDDC: 1.1V@2.0A)

C19

C19

1uF_6.3V

1uF_6.3V

C31

C31

1uF_6.3V

1uF_6.3V

C1229

C1229

1uF_6.3V

1uF_6.3V

C18

C18

10uF_4V

10uF_4V

C1335

C1335

1uF

1uF

(0.95V-1.1V@?A VDDCI)

(VDDCI : VDDC@~2A)

VDDCI: Isolated (clean) core power for the l/O logic

2

C20

C20

1uF_6.3V

1uF_6.3V

C32

C32

1uF_6.3V

1uF_6.3V

C1230

C1230

1uF_6.3V

1uF_6.3V

C21

C21

1uF_6.3V

1uF_6.3V

C1219

C1219

1uF_6.3V

1uF_6.3V

C1231

C1231

1uF_6.3V

1uF_6.3V

C23

C23

10uF_4V

10uF_4V

VSENSE 13

C22

C22

1uF_6.3V

1uF_6.3V

C1220

1uF_6.3V

1uF_6.3V

C1232

C1232

1uF_6.3V

1uF_6.3V

C28

C28

10uF_4V

10uF_4V

C24

C24

1uF_6.3V

1uF_6.3V

C1221

C1221

1uF_6.3V

1uF_6.3V

C1233

C1233

1uF_6.3V

1uF_6.3V

C37

C37

10uF_4V

10uF_4V

replace with 0R if VSENSE is not used

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

M96 GDDR3 MXMII 2.1A Crossfire

M96 GDDR3 MXMII 2.1A Crossfire

2

M96 GDDR3 MXMII 2.1A Crossfire

C25

C25

1uF_6.3V

1uF_6.3V

C1222

C1222

1uF_6.3V

1uF_6.3V

C1234

C1234

1uF_6.3V

1uF_6.3V

C42

C42

10uF_4V

10uF_4V

C26

C26

1uF_6.3V

1uF_6.3V

C1223

C1223

1uF_6.3V

1uF_6.3V

C1235

C1235

1uF_6.3V

1uF_6.3V

VDDC

C27

C27

1uF_6.3V

1uF_6.3V

C1224

C1224

1uF_6.3V

1uF_6.3V

C1236

C1236

1uF_6.3V

1uF_6.3V

C1239

C1239

10uF_4V

10uF_4V

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Wednesday, August 27, 2008

Wednesday, August 27, 2008

Wednesday, August 27, 2008

Sheet

Sheet

Sheet

3 14

3 14

3 14

C29

C29

1uF_6.3V

1uF_6.3V

C1227

C1227

1uF_6.3V

1uF_6.3V

C1237

C1237

1uF_6.3V

1uF_6.3V

of

of

of

1

C1240

C1240

10uF_4V

10uF_4V

1

C30

C30

1uF_6.3V

1uF_6.3V

C1228

1uF_6.3V

1uF_6.3V

C1238

C1238

1uF_6.3V

1uF_6.3V

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

0

0

0

105-B786xx-00A

105-B786xx-00A

105-B786xx-00A

www.vinafix.vn

Page 4

5

4

3

2

1

1.8V_REG

D D

C C

B B

For M97 Only

(1.8V@???mA DPA_VDD18)

B9

B9

BLM15BD121SN1

BLM15BD121SN1

(1.8V@???mA DPB_VDD18)

B12

B12

BLM15BD121SN1

BLM15BD121SN1

P4

(1.8V@???mA DPC_VDD18)

B13

B13

BLM15BD121SN1

BLM15BD121SN1

(1.8V@???mA DPD_VDD18)

B16

B16

BLM15BD121SN1

BLM15BD121SN1

P4

P4

P4

DPA_VDD18

C1243

C1243

1uF

1uF

DPB_VDD18

C1250

C1250

1uF

1uF

DPC_VDD18

C1251

C1251

1uF

1uF

DPD_VDD18

C1256

C1256

1uF

1uF

1.8V_REG

(DPE_VDD18: 1.8V@ 200mA)

DPE_VDD18: Output Driver

Analog Power Supply.

(DPE_VDD10: 1.1V@ 100mA)

DPE_VDD10: Output Driver Analog

Power Supply.

B17

B17

BLM15BD121SN1

BLM15BD121SN1

1.1V_REG

(DPC_VDD10: 1.1V@ 200mA)

DPC_VDD10: Transmitter Power 1.1V +/-3%

(DPD_VDD10: 1.1V@ 200mA)

DPD_VDD10: Transmitter Power 1.1V +/-3%

B11 BLM15BD121SN1B11 BLM15BD121SN1

(1.8V@40mA DPE_VDDC)

C1260

C1260

10uF_6.3V

10uF_6.3V

BLM15BD121SN1

BLM15BD121SN1

B20

B20

C1266

C1266

1uF

1uF

10uF_6.3V

10uF_6.3V

(DPF_VDD18: 1.8V@ 200mA)

DPF_VDD18: Output Driver Analog Power Supply.

(DPF_VDD10: 1.1V@ 100mA)

DPF_VDD10: Output Driver Analog Power Supply.

C1247

C1247

10uF_6.3V

10uF_6.3V

1.1V_REG

BLM15BD121SN1

BLM15BD121SN1

C1261

C1261

1uF

1uF

C1267

C1267

100nF

100nF

C1268

C1268

C1248

C1248

1uF

1uF

B15

B15

DPE_VDD18

C1262

C1262

100nF

100nF

DPE_VDD18

DPC_VDD10

C1249

C1249

100nF

100nF

DPE_VDD101.1V_REG

DPE_VDD10

DPC_VDD18

DPD_VDD18

DPD_VDD10

R1165150RR1165150R

R1163

R1163

150R

150R

U1H

U1H

AP20

NC_DPC_VDD18#1

AP21

NC_DPC_VDD18#2

AP13

DPC_VDD10#1

AT13

DPC_VDD10#2

AN17

DPC_VSSR#1

AP16

DPC_VSSR#2

AP17

DPC_VSSR#3

AW14

DPC_VSSR#4

AW16

DPC_VSSR#5

AP22

NC_DPD_VDD18#1

AP23

NC_DPD_VDD18#2

AP14

DPD_VDD10#1

AP15

DPD_VDD10#2

AN19

DPD_VSSR#1

AP18

DPD_VSSR#2

AP19

DPD_VSSR#3

AW20

DPD_VSSR#4

AW22

DPD_VSSR#5

AW18

DPCD_CALR

AH34

DPE_VDD18#1

AJ34

DPE_VDD18#2

AL33

DPE_VDD10#1

AM33

DPE_VDD10#2

AN34

DPE_VSSR#1

AP39

DPE_VSSR#2

AR39

DPE_VSSR#3

AU37

DPE_VSSR#4

AW35

DPE_VSSR#5

AF34

DPF_VDD18#1

AG34

DPF_VDD18#2

AK33

DPF_VDD10#1

AK34

DPF_VDD10#2

AF39

DPF_VSSR#1

AH39

DPF_VSSR#2

AK39

DPF_VSSR#3

AL34

DPF_VSSR#4

AM34

DPF_VSSR#5

AM39

DPEF_CALR

M96 A11 HF MVD SLT B1

M96 A11 HF MVD SLT B1

DP E/F POWER

DP E/F POWER

DP A/B POWERDP C/D POWER

DP A/B POWERDP C/D POWER

NC_DPA_VDD18#1

NC_DPA_VDD18#2

DPA_VDD10#1

DPA_VDD10#2

DPA_VSSR#1

DPA_VSSR#2

DPA_VSSR#3

DPA_VSSR#4

DPA_VSSR#5

NC_DPB_VDD18#1

NC_DPB_VDD18#2

DPB_VDD10#1

DPB_VDD10#2

DPB_VSSR#1

DPB_VSSR#2

DPB_VSSR#3

DPB_VSSR#4

DPB_VSSR#5

DPAB_CALR

DP PLL POWER

DP PLL POWER

DPA_PVDD

DPA_PVSS

DPB_PVDD

DPB_PVSS

DPC_PVDD

DPC_PVSS

DPD_PVDD

DPD_PVSS

DPE_PVDD

DPE_PVSS

NC_DPF_PVDD

NC_DPF_PVSS

AN24

AP24

AP31

AP32

AN27

AP27

AP28

AW24

AW26

AP25

AP26

AN33

AP33

AN29

AP29

AP30

AW30

AW32

AW28

AU28

AV27

AV29

AR28

AU18

AV17

AV19

AR18

AM37

AN38

AL38

AM35

DPA_VDD18

DPB_VDD18

R1164

R1164

150R

150R

DPA_VDD10: Transmitter Power 1.1V +/-3%

DPA_VDD10

(DPA_VDD10: 1.1V@ 200mA)

C1245

C1245

C1244

C1244

10uF_6.3V

10uF_6.3V

DPB_VDD10: Transmitter Power 1.1V +/-3%

DPB_VDD10

(DPB_VDD10: 1.1V@ 200mA)

C1253

C1253

C1252

C1252

10uF_6.3V

10uF_6.3V

100nF

100nF

DPA_PVDD: DP PLL Power 1.8V +/-3%

DPA_PVDD

(DPA_PVDD: 1.8V@ 20mA)

C1257

C1257

100nF

100nF

DPB_PVDD

(DPB_PVDD: 1.8V@ 20mA)

C1263

C1263

100nF

100nF

DPB_PVDD: DP PLL Power 1.8V +/-3%

DPC_PVDD

(DPC_PVDD: 1.8V@ 20mA)

C1269

C1269

100nF

100nF

DPC_PVDD: DP PLL Power 1.8V +/-3%

DPD_PVDD

(DPD_PVDD: 1.8V@ 20mA)

C1272

C1272

DPD_PVDD: DP PLL Power 1.8V +/-3%

100nF

100nF

DPE_PVDD

(DPE_PVDD: 1.8V@ 20mA)

C1273

C1273

100nF

100nF

DPE_PVDD: DP PLL Power 1.8V +/-3%

BLM15BD121SN1

BLM15BD121SN1

For M97 Only

100nF

100nF

C1276

C1276

1uF

1uF

C1274

C1274

1uF

1uF

C1270

C1270

1uF

1uF

100nF

100nF

C1258

C1258

1uF

1uF

C1264

C1264

1uF

1uF

C1246

C1246

C1254

C1254

1uF

1uF

B24

B24

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

C1259

C1259

10uF_6.3V

10uF_6.3V

BLM15BD121SN1

BLM15BD121SN1

C1265

C1265

10uF_6.3V

10uF_6.3V

BLM15BD121SN1

BLM15BD121SN1

C1271

C1271

10uF_6.3V

10uF_6.3V

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

C1275

C1275

10uF_6.3V

10uF_6.3V

B10

B10

B14

B14

B22

B22

12

1.1V_REG

1.1V_REG

12

12

B21

B21

12

B23

B23

1.8V_REG

B18

B18

B19

B19

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

M96 GDDR3 MXMII 2.1A Crossfire

M96 GDDR3 MXMII 2.1A Crossfire

5

4

3

2

M96 GDDR3 MXMII 2.1A Crossfire

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Wednesday, August 27, 2008

Wednesday, August 27, 2008

Wednesday, August 27, 2008

Sheet

Sheet

Sheet

of

4 14

of

4 14

of

4 14

RevDate:

RevDate:

RevDate:

0

0

0

Doc No.

Doc No.

Doc No.

105-B786xx-00A

105-B786xx-00A

1

105-B786xx-00A

www.vinafix.vn

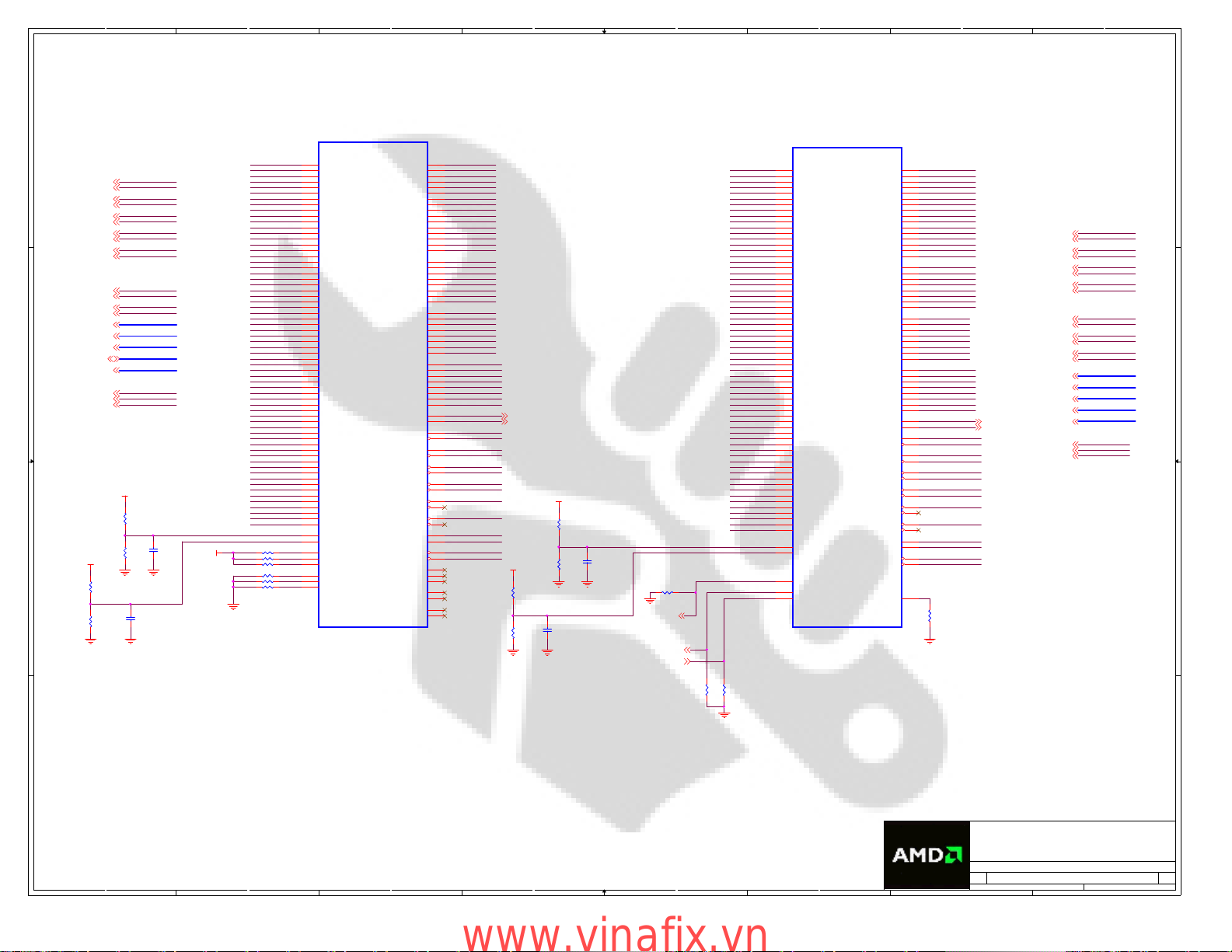

Page 5

1

A A

MVDDC

QSA#[7..0]

QSA[7..0]

DQMA#[7..0]

MDA[63..0]

MAA[12..0]

R64

R64

100R

100R

R66

R66

100R

100R

C301

C301

100nF

100nF

RASA0#

RASA1#

CASA0#

CASA1#

WEA0#

WEA1#

CKEA0

CKEA1

CSA0#_0

CSA1#_0

CLKA0

CLKA0#

CLKA1

CLKA1#

A_BA0

A_BA1

A_BA2

C298

C298

100nF

100nF

MVDDC

RASA0#6

RASA1#7

CASA0#6

CASA1#7

WEA0#6

WEA1#7

CKEA06

CKEA17

CSA0#_06

CSA1#_07

CLKA06

CLKA0#6

CLKA17

CLKA1#7

QSA#[7..0]6,7

QSA[7..0]6,7

B B

C C

DQMA#[7..0]6,7

MDA[63..0]6,7

MAA[12..0]6,7

A_BA06,7

A_BA16,7

A_BA26,7

MVDDC

R72

R72

100R

100R R76

R78

R78

100R

100R

2

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

R67 243RR67 243R

R70 243RR70 243R

R68 243RR68 243R

R71 243RR71 243R

R73 243RR73 243R

R75 243RR75 243R

U1C

U1C

C37

DQA_0

C35

DQA_1

A35

DQA_2

E34

DQA_3

G32

DQA_4

D33

DQA_5

F32

DQA_6

E32

DQA_7

D31

DQA_8

F30

DQA_9

C30

DQA_10

A30

DQA_11

F28

DQA_12

C28

DQA_13

A28

DQA_14

E28

DQA_15

D27

DQA_16

F26

DQA_17

C26

DQA_18

A26

DQA_19

F24

DQA_20

C24

DQA_21

A24

DQA_22

E24

DQA_23

C22

DQA_24

A22

DQA_25

F22

DQA_26

D21

DQA_27

A20

DQA_28

F20

DQA_29

D19

DQA_30

E18

DQA_31

C18

DQA_32

A18

DQA_33

F18

DQA_34

D17

DQA_35

A16

DQA_36

F16

DQA_37

D15

DQA_38

E14

DQA_39

F14

DQA_40

D13

DQA_41

F12

DQA_42

A12

DQA_43

D11

DQA_44

F10

DQA_45

A10

DQA_46

C10

DQA_47

G13

DQA_48

H13

DQA_49

J13

DQA_50

H11

DQA_51

G10

DQA_52

G8

DQA_53

K9

DQA_54

K10

DQA_55

G9

DQA_56

A8

DQA_57

C8

DQA_58

E8

DQA_59

A6

DQA_60

C6

DQA_61

E6

DQA_62

A5

DQA_63

L18

MVREFDA

L20

MVREFSA

L27

NC_MEM_CALRN0

N12

NC_MEM_CALRN1

AG12

NC_MEM_CALRN2

M12

MEM_CALRP1

M27

NC_MEM_CALRP0

AH12

NC_MEM_CALRP2

M96 A11 HF MVD SLT B1

M96 A11 HF MVD SLT B1

3

MAA_10

MAA_11

MAA_12

MAA_13/BA2

MAA_14/BA0

MAA_15/BA1

DQMA_0

DQMA_1

DQMA_2

DQMA_3

DQMA_4

DQMA_5

DQMA_6

MEMORY INTERFACE A

MEMORY INTERFACE A

DQMA_7

QSA_0/RDQSA_0

QSA_1/RDQSA_1

QSA_2/RDQSA_2

QSA_3/RDQSA_3

QSA_4/RDQSA_4

QSA_5/RDQSA_5

QSA_6/RDQSA_6

QSA_7/RDQSA_7

QSA_0B/WDQSA_0

QSA_1B/WDQSA_1

QSA_2B/WDQSA_2

QSA_3B/WDQSA_3

QSA_4B/WDQSA_4

QSA_5B/WDQSA_5

QSA_6B/WDQSA_6

QSA_7B/WDQSA_7

ODTA0

ODTA1

CLKA0B

CLKA1B

RASA0B

RASA1B

CASA0B

CASA1B

CSA0B_0

CSA0B_1

CSA1B_0

CSA1B_1

WEA0B

WEA1B

RSVD#1

RSVD#2

RSVD#3

RSVD#5

RSVD#6

RSVD#9

RSVD#11

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

CLKA0

CLKA1

CKEA0

CKEA1

G24

J23

H24

J24

H26

J26

H21

G21

H19

H20

L13

G16

J16

H16

J17

H17

A32

C32

D23

E22

C14

A14

E10

D9

C34

D29

D25

E20

E16

E12

J10

D7

A34

E30

E26

C20

C16

C12

J11

F8

J21

G19

H27

G27

J14

H14

K23

K19

K20

K17

K24

K27

M13

K16

K21

J20

K26

L15

AF28

AG28

AL31

H23

J19

T8

W8

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

A_BA2

A_BA0

A_BA1

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

QSA0

QSA1

QSA2

QSA3

QSA4

QSA5

QSA6

QSA7

QSA#0

QSA#1

QSA#2

QSA#3

QSA#4

QSA#5

QSA#6

QSA#7

ODTA0

ODTA1

CLKA0

CLKA0#

CLKA1

CLKA1#

RASA0#

RASA1#

CASA0#

CASA1#

CSA0#_0

CSA1#_0

CKEA0

CKEA1

WEA0#

WEA1#

ODTA0 6

ODTA1 7

MVDDC

4

MVDDC

R65

R65

100R

100R

C299

C299

R69

R69

100nF

100nF

100R

100R

R76

100R

100R

C303

C303

R83

R83

100nF

100nF

100R

100R

5

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

R77

R77

5.11K

5.11K

TESTEN10

TEST_MCLK10

TEST_YCLK10

TEST_MCLK

TEST_YCLK

U1D

U1D

C5

DQB_0

C3

DQB_1

E3

DQB_2

E1

DQB_3

F1

DQB_4

F3

DQB_5

F5

DQB_6

G4

DQB_7

H5

DQB_8

H6

DQB_9

J4

DQB_10

K6

DQB_11

K5

DQB_12

L4

DQB_13

M6

DQB_14

M1

DQB_15

M3

DQB_16

M5

DQB_17

N4

DQB_18

P6

DQB_19

P5

DQB_20

R4

DQB_21

T6

DQB_22

T1

DQB_23

U4

DQB_24

V6

DQB_25

V1

DQB_26

V3

DQB_27

Y6

DQB_28

Y1

DQB_29

Y3

DQB_30

Y5

DQB_31

AA4

DQB_32

AB6

DQB_33

AB1

DQB_34

AB3

DQB_35

AD6

DQB_36

AD1

DQB_37

AD3

DQB_38

AD5

DQB_39

AF1

DQB_40

AF3

DQB_41

AF6

DQB_42

AG4

DQB_43

AH5

DQB_44

AH6

DQB_45

AJ4

DQB_46

AK3

DQB_47

AF8

DQB_48

AF9

DQB_49

AG8

DQB_50

AG7

DQB_51

AK9

DQB_52

AL7

DQB_53

AM8

DQB_54

AM7

DQB_55

AK1

DQB_56

AL4

DQB_57

AM6

DQB_58

AM1

DQB_59

AN4

DQB_60

AP3

DQB_61

AP1

DQB_62

AP5

DQB_63

Y12

MVREFDB

AA12

MVREFSB

AD28

TESTEN

AK10

CLKTESTA

AL10

CLKTESTB

M96 A11 HF MVD SLT B1

M96 A11 HF MVD SLT B1

6

MAB_10

MAB_11

MAB_12

MAB_13/BA2

MAB_14/BA0

MAB_15/BA1

DQMB_0

DQMB_1

DQMB_2

DQMB_3

DQMB_4

DQMB_5

DQMB_6

MEMORY INTERFACE B

MEMORY INTERFACE B

DQMB_7

QSB_0/RDQSB_0

QSB_1/RDQSB_1

QSB_2/RDQSB_2

QSB_3/RDQSB_3

QSB_4/RDQSB_4

QSB_5/RDQSB_5

QSB_6/RDQSB_6

QSB_7/RDQSB_7

QSB_0B/WDQSB_0

QSB_1B/WDQSB_1

QSB_2B/WDQSB_2

QSB_3B/WDQSB_3

QSB_4B/WDQSB_4

QSB_5B/WDQSB_5

QSB_6B/WDQSB_6

QSB_7B/WDQSB_7

ODTB0

ODTB1

CLKB0B

CLKB1B

RASB0B

RASB1B

CASB0B

CASB1B

CSB0B_0

CSB0B_1

CSB1B_0

CSB1B_1

WEB0B

WEB1B

DRAM_RST

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

CLKB0

CLKB1

CKEB0

CKEB1

P8

T9

P9

N7

N8

N9

U9

U8

Y9

W9

AC8

AC9

AA7

AA8

Y8

AA9

H3

H1

T3

T5

AE4

AF5

AK6

AK5

F6

K3

P3

V5

AB5

AH1

AJ9

AM5

G7

K1

P1

W4

AC4

AH3

AJ8

AM3

T7

W7

L9

L8

AD8

AD7

T10

Y10

W10

AA10

P10

L10

AD10

AC10

U10

AA11

N10

AB11

AH11

7

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

B_BA2

B_BA0

B_BA1

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

QSB0

QSB1

QSB2

QSB3

QSB4

QSB5

QSB6

QSB7

QSB#0

QSB#1

QSB#2

QSB#3

QSB#4

QSB#5

QSB#6

QSB#7

ODTB0

ODTB0 8

ODTB1

CLKB0

CLKB0#

CLKB1

CLKB1#

RASB0#

RASB1#

CASB0#

CASB1#

CSB0#_0

CSB1#_0

CKEB0

CKEB1

WEB0#

WEB1#

R1346

R1346

DNI

4.7K

4.7K

ODTB1 9

RASB0#8

RASB1#9

CASB0#8

CASB1#9

WEB0#8

WEB1#9

CSB0#_08

CSB1#_09

CKEB08

CKEB19

CLKB08

CLKB0#8

CLKB19

CLKB1#9

QSB#[7..0]8,9

QSB[7..0]8,9

DQMB#[7..0]8,9

MDB[63..0]8,9

MAB[12..0]8,9

B_BA08,9

B_BA18,9

B_BA28,9

8

RASB0#

RASB1#

CASB0#

CASB1#

WEB0#

WEB1#

CSB0#_0

CSB1#_0

CKEB0

CKEB1

CLKB0

CLKB0#

CLKB1

CLKB1#

QSB#[7..0]

QSB[7..0]

DQMB#[7..0]

MDB[63..0]

MAB[12..0]

B_BA0

B_BA1

B_BA2

R80

R80

R79

R79

4.7K

4.7K

4.7K

4.7K

D D

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

RH M92/M96 M package MXM2.1A DDR2

RH M92/M96 M package MXM2.1A DDR2

RH M92/M96 M package MXM2.1A DDR2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

1

2

3

4

5

6

Date: Sheet of

7

105-B80631-00A

105-B80631-00A

105-B80631-00A

0

0

5 14Wednesday, August 27, 2008

5 14Wednesday, August 27, 2008

5 14Wednesday, August 27, 2008

8

0

www.vinafix.vn

Page 6

5

A_BA0

A_BA1

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

D D

C C

MVDDC

R201

R201

4.99K

4.99K

R202

R202

4.99K

4.99K

C413

C413

100nF

100nF

B B

PLACE VREF DIVIDER COMPONENTS

AS CLOSE TO MEMORY AS POSSIBLE

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

CLKA0#

CLKA0

CKEA0

CSA0#_0

WEA0#

RASA0#

CASA0#

DQMA#3 DQMA#1

ODTA0

QSA3 QSA1

QSA#3 QSA#1

QSA0

QSA#0

A_BA2

U20

U20

L2

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

R3

R7

R8

23BC1147SP02

23BC1147SP02

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

CK

CKE

CS

WE

RAS

CAS

LDM

UDM

ODT

LDQS

LDQS

UDQS

UDQS

VREF

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSS1

VSS2

VSS3

VSS4

VSS5

B9

B1

D9

D1

D3

D7

C2

C8

F9

F1

H9

H1

H3

H7

G2

G8

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

MDA2

MDA4

MDA1

MDA7

MDA5

MDA3

MDA6

MDA0

MDA27

MDA31

MDA24

MDA29

MDA30

MDA25

MDA28

MDA26

C784

C784

100nF

100nF

4

MVDDC

B46 BLM15BD121SN1B46 BLM15BD121SN1

C785

C785

1uF_6.3V

1uF_6.3V

MVDDC

R204

R204

4.99K

4.99K

PLACE VREF DIVIDER COMPONENTS

AS CLOSE TO MEMORY AS POSSIBLE

R203

R203

4.99K

4.99K

C438

C438

100nF

100nF

A_BA0

A_BA1

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

CLKA0#

CLKA0

CKEA0

CSA0#_0

WEA0#

RASA0#

CASA0#

DQMA#2DQMA#0

ODTA0

QSA2

QSA#2

A_BA2

3

U21

U21

L2

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

R3

R7

R8

23BC1147SP02

23BC1147SP02

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

CK

CKE

CS

WE

RAS

CAS

LDM

UDM

ODT

LDQS

LDQS

UDQS

UDQS

VREF

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSS1

VSS2

VSS3

VSS4

VSS5

B9

B1

D9

D1

D3

D7

C2

C8

F9

F1

H9

H1

H3

H7

G2

G8

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

MDA21

MDA18

MDA23

MDA17

MDA16

MDA20

MDA19

MDA22

MDA12

MDA10

MDA15

MDA8

MDA11

MDA14

MDA9

MDA13

C786

C786

100nF

100nF

2

MVDDC

B47 BLM15BD121SN1B47 BLM15BD121SN1

C787

C787

1uF_6.3V

1uF_6.3V

1

R555

R555

MAA[12..0]

DQMA#[7..0]

QSA#[7..0]

QSA[7..0]

CLKA0

CLKA0#

56R

56R

A_BA0

A_BA1

A_BA2

CKEA0

CSA0#_0

WEA0#

RASA0#

CASA0#

ODTA0

MDA[63..0]

C788

C788

470pF

470pF

R556

R556

56R

56R

A_BA05,7

A_BA15,7

A_BA25,7

MAA[12..0]5,7

CKEA05

CSA0#_05

WEA0#5

RASA0#5

CASA0#5

DQMA#[7..0]5,7

ODTA05

QSA#[7..0]5,7

QSA[7..0]5,7

MDA[63..0]5,7

CLKA05

CLKA0#5

MVDDC

C409

C408

C408

1uF_6.3V

1uF_6.3V

402402 402 402402402 402 402402402

10uF_6.3V

10uF_6.3V

4

C493

C493

C409

1uF_6.3V

1uF_6.3V

C407

C407

C406

C406

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

MVDDC

C492

C490

A A

5

C490

10uF_6.3V

10uF_6.3V

C492

10uF_6.3V

10uF_6.3V

C410

C410

1uF_6.3V

1uF_6.3V

C494

C494

10uF_6.3V

10uF_6.3V

MVDDC

C1412

C1412

1uF_6.3V

1uF_6.3V

MVDDC

C1413

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

DNI

C791 100nF_6.3VC791 100nF_6.3V

C790 100nF_6.3VC790 100nF_6.3V

C789 100nF_6.3VC789 100nF_6.3V

C792 100n F_6.3VC 792 100nF_6 .3V

3

1uF_6.3V

1uF_6.3V

C435

C435

1uF_6.3V

1uF_6.3V

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

RH M92/M96 M package MXM2.1A DDR2

RH M92/M96 M package MXM2.1A DDR2

RH M92/M96 M package MXM2.1A DDR2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

105-B80631-00A

105-B80631-00A

105-B80631-00A

1

0

0

6 14Wednesday, September 03, 2008

6 14Wednesday, September 03, 2008

6 14Wednesday, September 03, 2008

0

C434

C434

C1414

C1414

C1413

www.vinafix.vn

Page 7

5

A_BA0

A_BA1

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

D D

C C

MVDDC

R205

R205

4.99K

4.99K

R206

R206

4.99K

4.99K

C463

C463

100nF

100nF

B B

PLACE VREF DIVIDER COMPONENTS

AS CLOSE TO MEMORY AS POSSIBLE

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

CLKA1#

CLKA1

CKEA1

CSA1#_0

WEA1#

RASA1#

CASA1# CASA1#

DQMA#6 DQMA#5

ODTA1 ODTA1

QSA#4

QSA6

QSA#6 QSA#5

A_BA2

U22

U22

L2

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

R3

R7

R8

23BC1147SP02

23BC1147SP02

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

CK

CKE

CS

WE

RAS

CAS

LDM

UDM

ODT

LDQS

LDQS

UDQS

UDQS

VREF

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSS1

VSS2

VSS3

VSS4

VSS5

B9

B1

D9

D1

D3

D7

C2

C8

F9

F1

H9

H1

H3

H7

G2

G8

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

MDA48

MDA52

MDA50

MDA55

MDA54

MDA51

MDA53

MDA49

MDA35

MDA36

MDA33

MDA38

MDA39

MDA32

MDA37

MDA34

4

C793

C793

100nF

100nF

MVDDC

B48 BLM15BD121SN1B48 BLM15BD121SN1

C794

C794

1uF_6.3V

1uF_6.3V

3

A_BA0

A_BA1

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

CLKA1#

CLKA1

CKEA1 CASA1#

CSA1#_0

WEA1#

RASA1#

DQMA#7DQMA#4

QSA7QSA4

MVDDC

R207

R207

4.99K

4.99K

R208

R208

4.99K

4.99K

C448

C448

100nF

100nF

PLACE VREF DIVIDER COMPONENTS

AS CLOSE TO MEMORY AS POSSIBLE

QSA#7

QSA5

A_BA2

U23

U23

L2

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

R3

R7

R8

23BC1147SP02

23BC1147SP02

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

CK

CKE

CS

WE

RAS

CAS

LDM

UDM

ODT

LDQS

LDQS

UDQS

UDQS

VREF

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSS1

VSS2

VSS3

VSS4

VSS5

2

MDA46

B9

MDA43

B1

MDA47

D9

MDA41

D1

MDA42

D3

MDA44

D7

MDA40

C2

MDA45

C8

MDA60

F9

MDA58

F1

MDA63

H9

MDA56

H1

MDA59

H3

MDA62

H7

MDA57

G2

MDA61

G8

A9

C1

C3

C7

C9