Page 1

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

ASSEMBLYNVPNVARIANT

B

1

2

SKU

3

4

5

6

12

13

14

7

8

9

10

11

15

G94-P547-A00 - GDDR3, DVI/VGA + DVI/VGA + HDTV/SDTV-Out

BASE

sku0011

<UNDEFINED

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

600-10547-base-000

600-10547-0011-000

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

P547 BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

G94-400 650MHz/900MHz 512MB 16Mx32 BGA136 GDDR3, DVI-I-DL+DVI-I-DL

<UNDEFINED

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

Table of Contents:

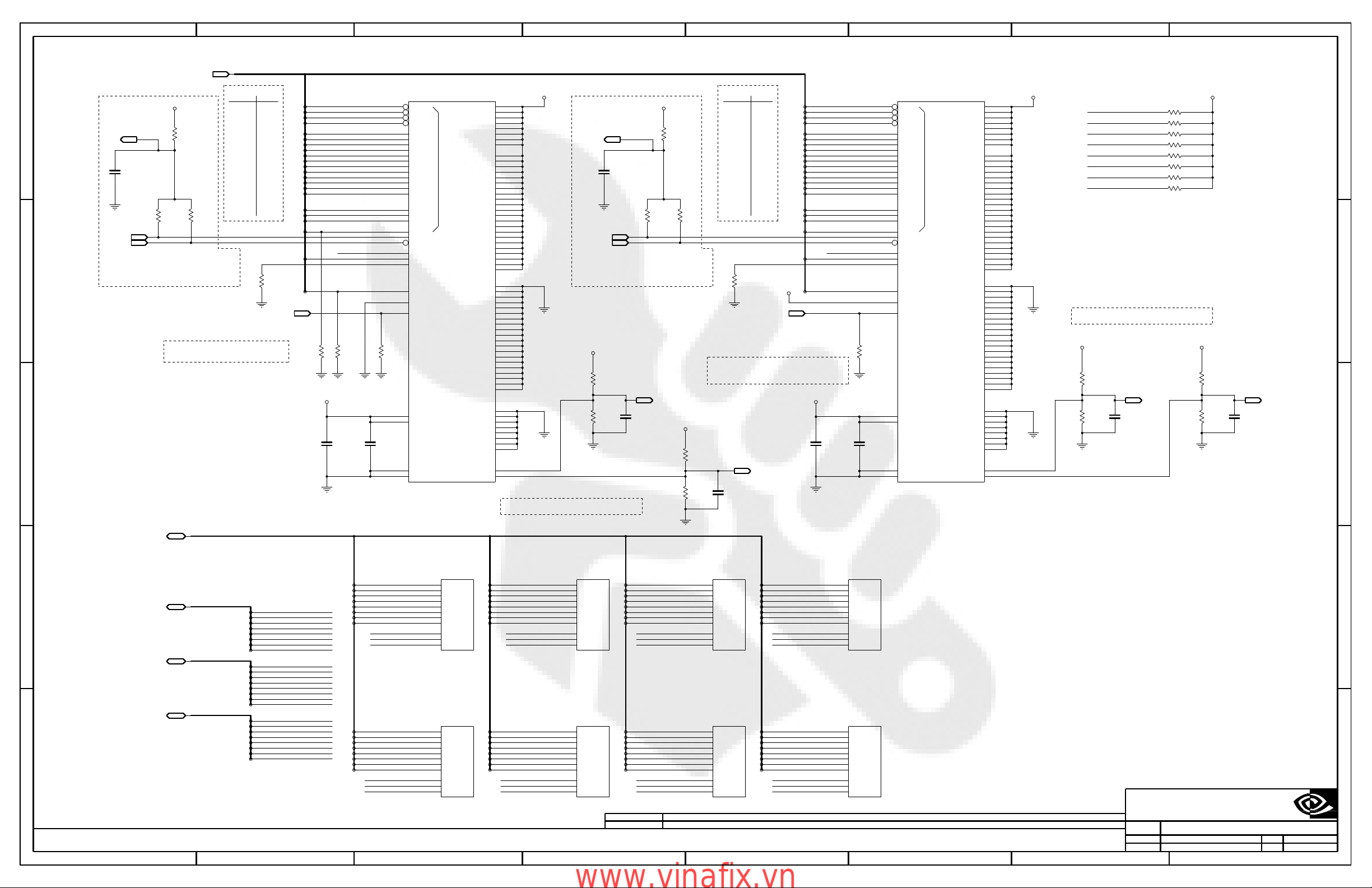

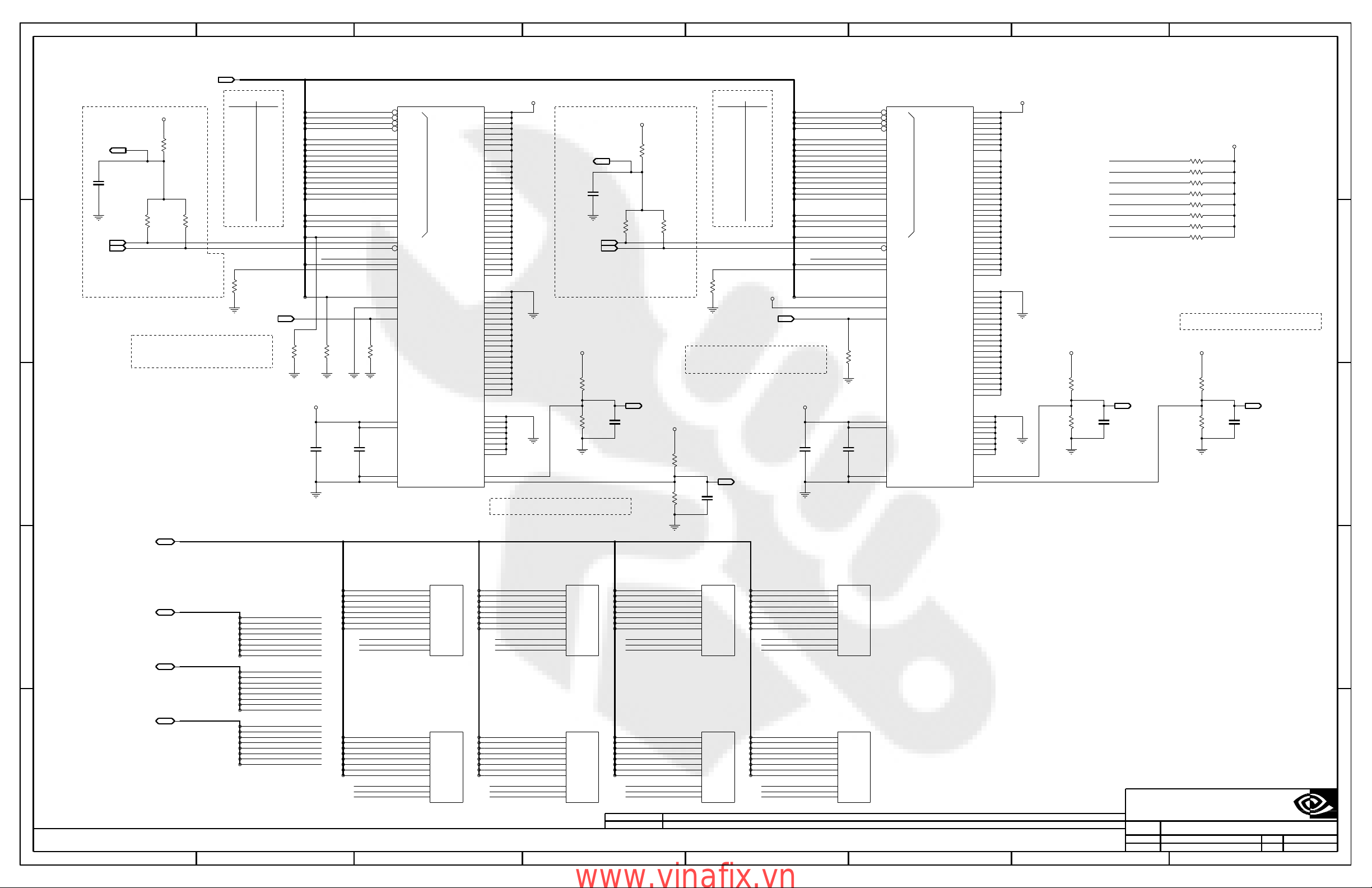

Page 1: Overview

Page 2: PCI Express

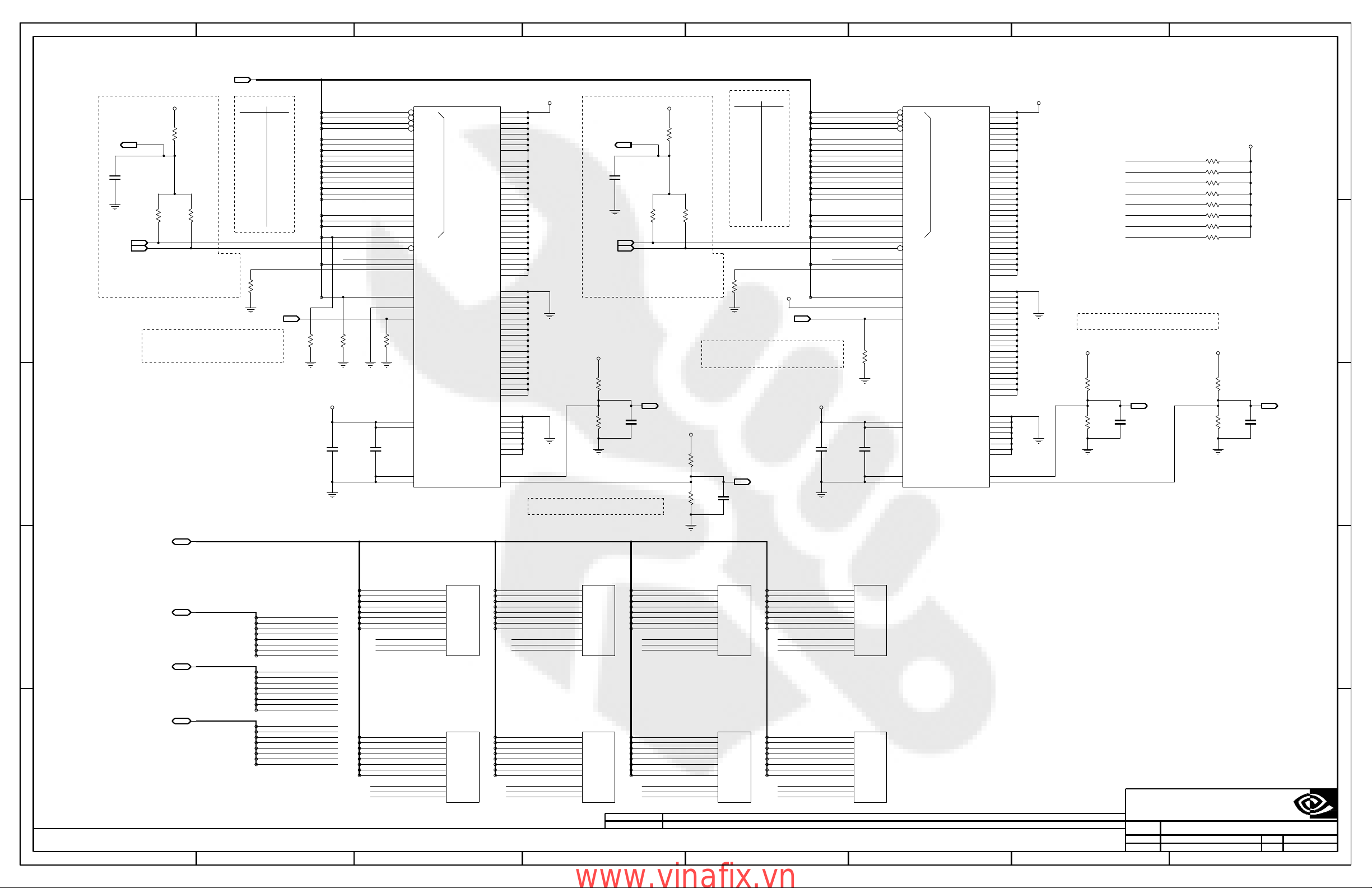

Page 3: MEMORY: GPU Partition A/B

Page 4: MEMORY: GPU Partition C/D

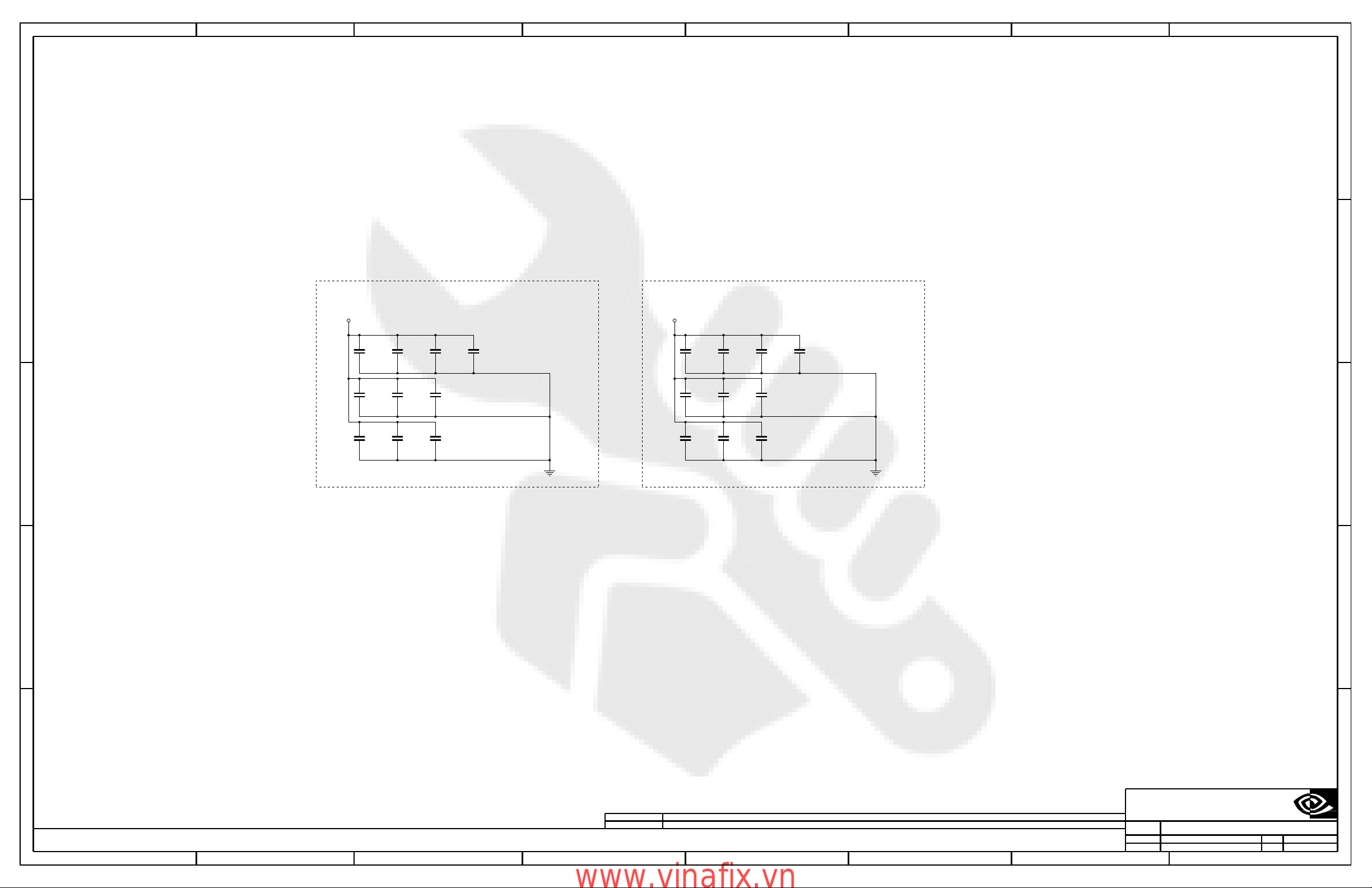

Page 5: FBA Partition

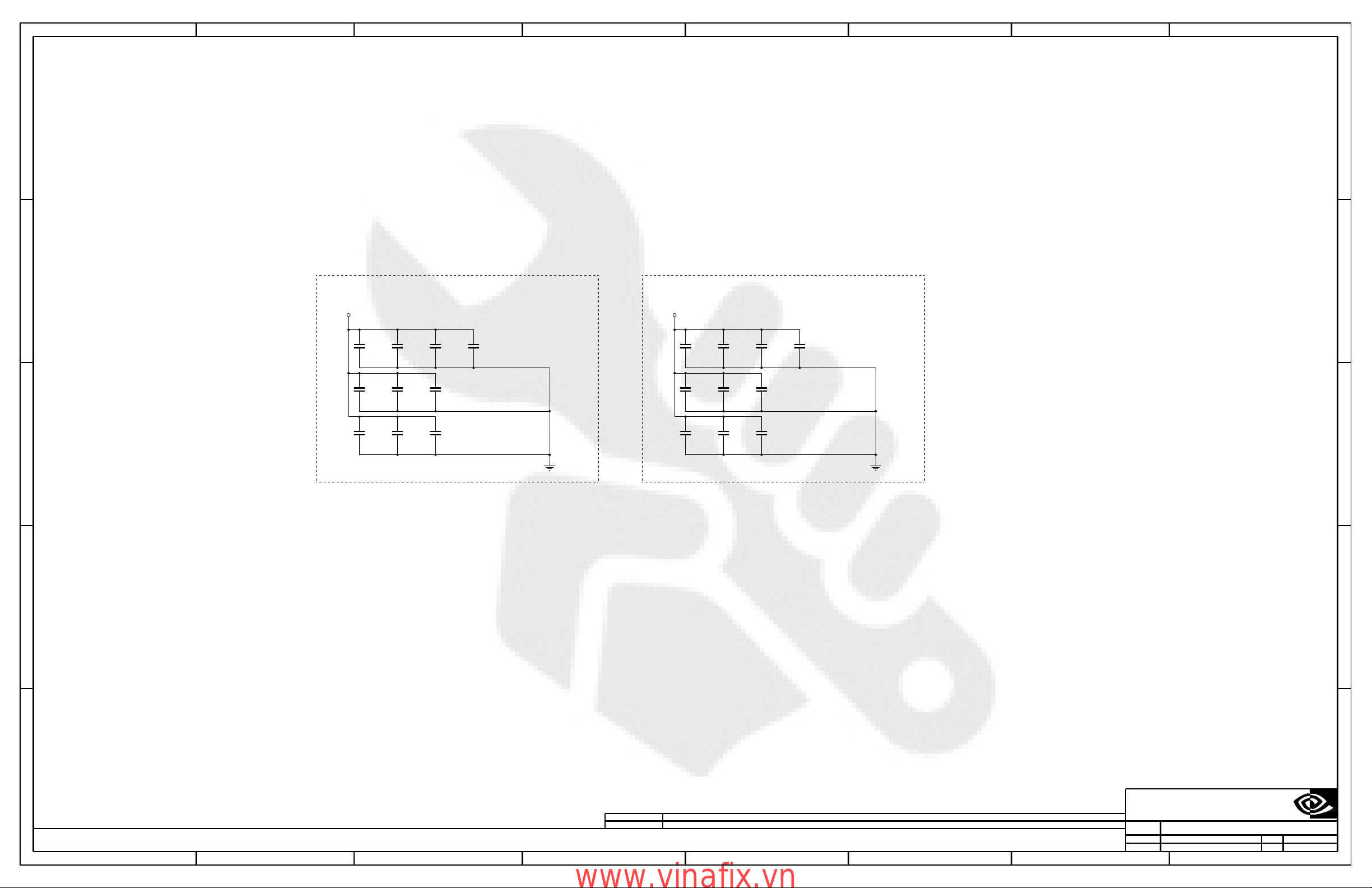

Page 6: FBA Partition Decoupling

REVISION HISTORY:

Page 7: FBB Partition

Page 8: FBB Partion Decoupling

Page 9: FBC Partition

Page 10: FBC Partition Decoupling

Page 11: FBD Partition

Page 12: FBD Partition Decoupling

Page 13: FB Net Properties

Page 14: DACA Interface

Page 15: DACC Interface

Page 16: IFP A/B Interface -- DVI Connector South

Page 17: IFP C/D Interface -- DVI Connector MID

Page 18: IFP E/F Interface -- Unused

Page 19: DACB and HDTV/SDTV-Out

Page 20: MIO A/B Interface

Page 21: MISC: GPIO, I2C, ROM, HDCP, and XTAL

Page 22: Strap Configuration

Page 23: PWR and GND Signals

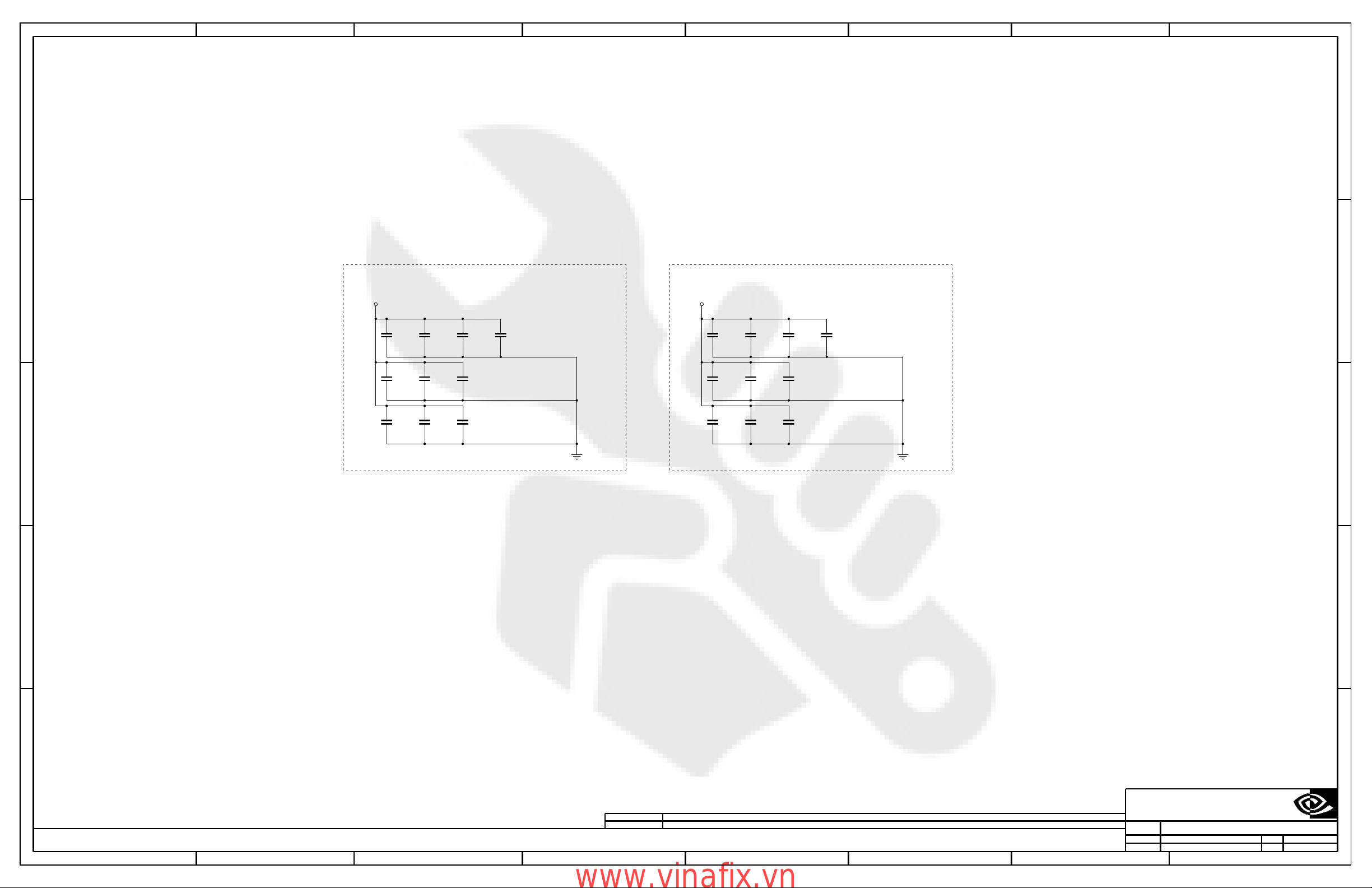

Page 24: NVVDD and FBVDDQ Decoupling

Page 25: SPDIF Input, Backdrive Protection, and IFP_IOVDD Power Supply

Page 26: PS I: 12V and 12V_EXT Power Supply Filter

Page 27: PS II: IFP_PLLVDD, 2V5, 5V, and DDC_5V Power Supply

Page 28: PS III: FBVDDQ Power Supply

Page 29: PS IV: NVVDD Power Supply

Page 30: BLANK

Page 31: Fan Connector

Page 32: Thermal, Mechanical, and Bracket

Overview

www.vinafix.vn

600-10547-0011-000 A

design

rachen

1 OF 32

07-AUG-2008

Page 2

J501

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTINOUT

OUTINOUT

OUT

KEY

TRST*

TCK

GND

TMS

TDO

VCC

TDI

OUT

1/19 PCI_EXPRESS

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

VDD33

VDD33

VDD33

VDD33

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

VDD33

GND_SENSE

VDD_SENSE

PEX_PLLVDD

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_CAL_PU_GND

PEX_TERMP

TESTMODE

PEX_CAL_PD_VDDQ

PEX_TX0

PEX_CLKREQ

PEX_REFCLK

PEX_REFCLK

PEX_RST

PEX_TX0

PEX_TX3

PEX_TX3

PEX_TX2

PEX_TX2

PEX_TX1

PEX_TX1

PEX_RX3

PEX_RX3

PEX_RX2

PEX_RX2

PEX_RX1

PEX_RX1

PEX_RX0

PEX_RX0

PEX_TX7

PEX_TX6

PEX_TX6

PEX_TX5

PEX_TX5

PEX_TX4

PEX_TX4

PEX_RX6

PEX_RX6

PEX_RX5

PEX_RX5

PEX_RX4

PEX_RX4

PEX_TX7

PEX_TX10

PEX_TX10

PEX_TX9

PEX_TX9

PEX_TX8

PEX_TX8

PEX_RX10

PEX_RX9

PEX_RX9

PEX_RX8

PEX_RX8

PEX_RX7

PEX_RX7

PEX_TX13

PEX_TX13

PEX_TX12

PEX_TX12

PEX_TX11

PEX_TX11

PEX_RX13

PEX_RX13

PEX_RX12

PEX_RX10

PEX_RX11

PEX_RX11

PEX_RX12

PEX_TX14

PEX_TX15

PEX_TX15

PEX_TX14

PEX_RX15

PEX_RX15

PEX_RX14

PEX_RX14

OUT

OUT

OUT

END OF X8

END OF X16

END OF X1

END OF X4

TCLK JTAG2

TMS JTAG5

TDO JTAG4

TDI JTAG3

WAKE

SMDAT

SMCLK

PERN0

PERP0

REFCLK

PERST

REFCLK

PETN1

PERP2

PETN0

PERP1

PERN1

PETP0

PETP1

PERN3

PETP3

PETN3

PETP2

PERP3

PETN2

PERN2

PERP4

PERN4

PETN4

PERP5

PETP4

PERN5

PETP5

PETP6

PERN6

PERP6

PETN5

PERP7

PETN6

PERN7

PETN8

PETP8

PERP8

PETN7

PETP7

PERN8

PERN9

PERP9

PERP10

PERN10

PETP10

PETP9

PETN9

PETN10

PETN11

PERP12

PERN12

PERP11

PERN11

PETP11

PETN12

PETP12

PETN13

PERP13

PERN13

PETP13

PERP14

PERN15

PETP15

PETN15

PERN14

PETN14

PETP14

PERP15

TRST* JTAG1+12V

+12V/RSVD

+3V3AUX

+12V

+12V

+12V

+3V3

+3V3

+3V3

PRSNT2

PRSNT1

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

GND

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

1

3

5

7

HDR_2F4

FEMALE

1.274MM

0

KEY6_JTAG_SMALL

NO STUFF

AT18

AT24

AT25

AU15

AU16

AU19

AU22

AM17

AM18

AM19

AM20

AM24

AM25

AM26

AM27

AM28

AP18

AP19

AP21

AP22

AP24

AP25

AP27

AR15

AR16

AR18

AR19

AR21

AR22

AR24

AR25

AR27

AT15

AT16

AT19

AT21

AT22

L11

L12

L13

M11

N11AW21

NVVDD_SENSE_GPU

AJ22

NVVDD_GND_SENSE_GPU

AJ21

PEX_PLL_CLK_OUT

AP16

PEX_PLL_CLK_OUT*

AP17

12MIL

PEX_PLLVDD

AM16

GPU_TESTMODE

BB27

12MIL

PEX_CAL_PD_VDDQ

AM21

PEX_CAL_PU_GND

AM22

12MIL

PEX_TERMP

AM23

12MIL

PCI Express

2

4

8

Place near balls

Place near balls

3V3

www.vinafix.vn

.1UF

10V

10%

.1UF

10%

.1UF

10V

10%

.1UF

10V

10%

.1UF

10V

10%

.1UF

10V

10%

.1UF

10V

10%

.1UF

10V

10%

.1UFC696

10V

10%

.1UF

10V

10%

.1UF

10V

10%

.1UF

10V

10%

.1UF

10V

10%

.1UF

10V

10%

.1UF

10V

10%

.1UF

10V

10%

21>

21>

C796

0402

C782

0402

C773

0402

C756

0402

C741

0402

C726

0402 10V

C706

C686

0402

C661

0402

C638

0402

C624

0402

C614

0402

C604

0402

C601

25<

2>

SNN_PEX_CLKREQ*

.1UF

10%

10V0402

X5R

.1UF

10V

.1UF

10%

10V

X5R

.1UF

10%

10V

X5R

.1UF

10%

10V

X5R

.1UF

10%

10V

X5R

.1UF

10%

X5R

.1UF

10%

10V0402

X5R

.1UF

10%

10V

X5R

.1UF

10%

10V

X5R

.1UF

10%

10V

X5R

.1UF

10%

10V

X5R

.1UF

10%

10V0402

X5R

.1UFC606

10%

10V

X5R

.1UF

10%

10V

X5R

.1UF

10%

10V0402

X5R

R703

0402

R691

0402

R711

0402

R713

0402

R714

0402

PEX_TX0

PEX_TX0*

COMMON

PEX_TX1

PEX_TX1* AW14

10%

COMMON

X5R

PEX_TX2

PEX_TX2*

COMMON

PEX_TX3

PEX_TX3*

COMMON

PEX_TX4

PEX_TX4*

COMMON

PEX_TX5

PEX_TX5*

COMMON

PEX_TX6

PEX_TX6*

COMMON

PEX_TX7

PEX_TX7*

COMMON

PEX_TX8 AV21

PEX_TX8*

COMMON

PEX_TX9

PEX_TX9*

COMMON

PEX_TX10

PEX_TX10*

COMMON

PEX_TX11

PEX_TX11*

COMMON

PEX_TX12

PEX_TX12*

COMMON

PEX_TX13

PEX_TX13*

COMMON

PEX_TX14

PEX_TX14*

COMMON

PEX_TX15

PEX_TX15*

COMMON

5%

5%

5%

5%

5%

0

NO STUFF

0

NO STUFF

0

NO STUFF

0

NO STUFF

0

NO STUFF

AW10

AY10

AW11

AW12

AU13

AV13

AY12

BA12

AW13

BB12

BB13

AW15

AV15

BA13

AY13

AV16

AW16

AY15

BA15

AW17

AW18

BB15

BB16

AV18

AU18

BA16

AY16

AV19

AW19

AY18

BA18

AW20

BB18

BB19

AU21

BA19

AY19

AV22

AW22

AY21

BA21

AW23

AW24

BB21

BB22

AV24

AU24

BA22

AY22

AU25

AV25

AY24

BA24

AW25

AW26

BB24

BB25

AW27

AV27

BA25

AY25

AU27

AT27

AY27

BA27

JTAG_TRST*

JTAG_TCLK

JTAG_TDI

JTAG_TDO

JTAG_TMS

G1

G94-400-A1

BGA1504

COMMON

C834

4.7UF

16V

10%

X7R

1206

COMMON

C823

.1UF

16V

10%

X7R

0402

COMMON

C33

0402

NO STUFF

C835

4.7UF

16V

10%

X7R

1206

COMMON

GND

3V3_AUX

.1UF

10V

10%

X5R

PEX_PRSNT*

SNN_PE_PRSNT2_A

SNN_PE_RSVD1

SNN_PE_PRSNT2_B

SNN_PE_RSVD2

SNN_PE_RSVD3

SNN_PE_RSVD4

GND

SNN_PE_PRSNT2_C

SNN_PE_RSVD5

PEX_PRSNT*

SNN_PE_RSVD6

SNN_PE_RSVD7

C836

.1UF

16V

10%

X7R

0402

COMMON

CN2

CON_X16

NO STUFF

CON_PCIEXP_X16_EDGE

B1

B2

A2

A3

B3

B8

A9

A10

B10

A1

B17

B12

B4

A4

B7

A12

B13

A15

B16

B18

A18

GND

B31

A19

B30

A32

A20

B21

B22

A23

A24

B25

B26

A27

A28

B29

A31

B32

B48

A33

A34

B35

B36

A37

A38

B39

B40

A41

A42

B43

B44

A45

A46

B47

B49

A49

GND

B81

A50

B82

A51

B52

B53

A54

A55

B56

B57

A58

A59

B60

B61

A62

A63

B64

B65

A66

A67

B68

B69

A70

A71

B72

B73

A74

A75

B76

B77

A78

A79

B80

A82

GND

B9

A5

A6

A7

A8

B5

B6

B11

A11

A13

A14

A16

A17

B14

B15

A21

A22

B19

B20

A25

A26

B23

B24

A29

A30

B27

B28

A35

A36

B33

B34

A39

A40

B37

B38

A43

A44

B41

B42

A47

A48

B45

B46

A52

A53

B50

B51

A56

A57

B54

B55

A60

A61

B58

B59

A64

A65

B62

B63

A68

A69

B66

B67

A72

A73

B70

B71

A76

A77

B74

B75

A80

A81

B78

B79

PEX_TRST*

PEX_TCLK

PEX_TDI

PEX_TDO

PEX_TMS

PEX_SMCLK

PEX_SMDAT

SNN_PEX_WAKE*

PEX_RST*

PEX_REFCLK

PEX_REFCLK*

PEX_TXX0

PEX_TXX0*

PEX_RX0

PEX_RX0*

PEX_TXX1

PEX_TXX1*

PEX_RX1

PEX_RX1*

PEX_TXX2

PEX_TXX2*

PEX_RX2

PEX_RX2*

PEX_TXX3

PEX_TXX3*

PEX_RX3

PEX_RX3*

PEX_TXX4

PEX_TXX4*

PEX_RX4

PEX_RX4*

PEX_TXX5

PEX_TXX5*

PEX_RX5

PEX_RX5*

PEX_TXX6

PEX_TXX6*

PEX_RX6

PEX_RX6*

PEX_TXX7

PEX_TXX7*

PEX_RX7

PEX_RX7*

PEX_TXX8

PEX_TXX8*

PEX_RX8

PEX_RX8*

PEX_TXX9

PEX_TXX9*

PEX_RX9

PEX_RX9*

PEX_TXX10

PEX_TXX10*

PEX_RX10

PEX_RX10*

PEX_TXX11

PEX_TXX11*

PEX_RX11

PEX_RX11*

PEX_TXX12

PEX_TXX12*

PEX_RX12

PEX_RX12*

PEX_TXX13

PEX_TXX13*

PEX_RX13

PEX_RX13*

PEX_TXX14

PEX_TXX14*

PEX_RX14

PEX_RX14*

PEX_TXX15

PEX_TXX15*

PEX_RX15

PEX_RX15*

C800

0402

COMMON

X5R

C795

0402 10V C794

COMMON

X5R

C784

0402

COMMON

X5R

C778

0402

COMMON

X5R

C761

0402

COMMON

X5R

C745

0402

COMMON

X5R

C734

0402

COMMON

X5R

C714

0402

COMMON

X5R

0402

COMMON

X5R

C665

0402

COMMON

X5R

C642

0402

COMMON

X5R

C625

0402

COMMON

X5R

C617

0402

COMMON

X5R

C608

0402

COMMON

X5R

C605

0402

COMMON

X5R

C603

0402

COMMON

X5R

R712

0

5%

0402

NO STUFF

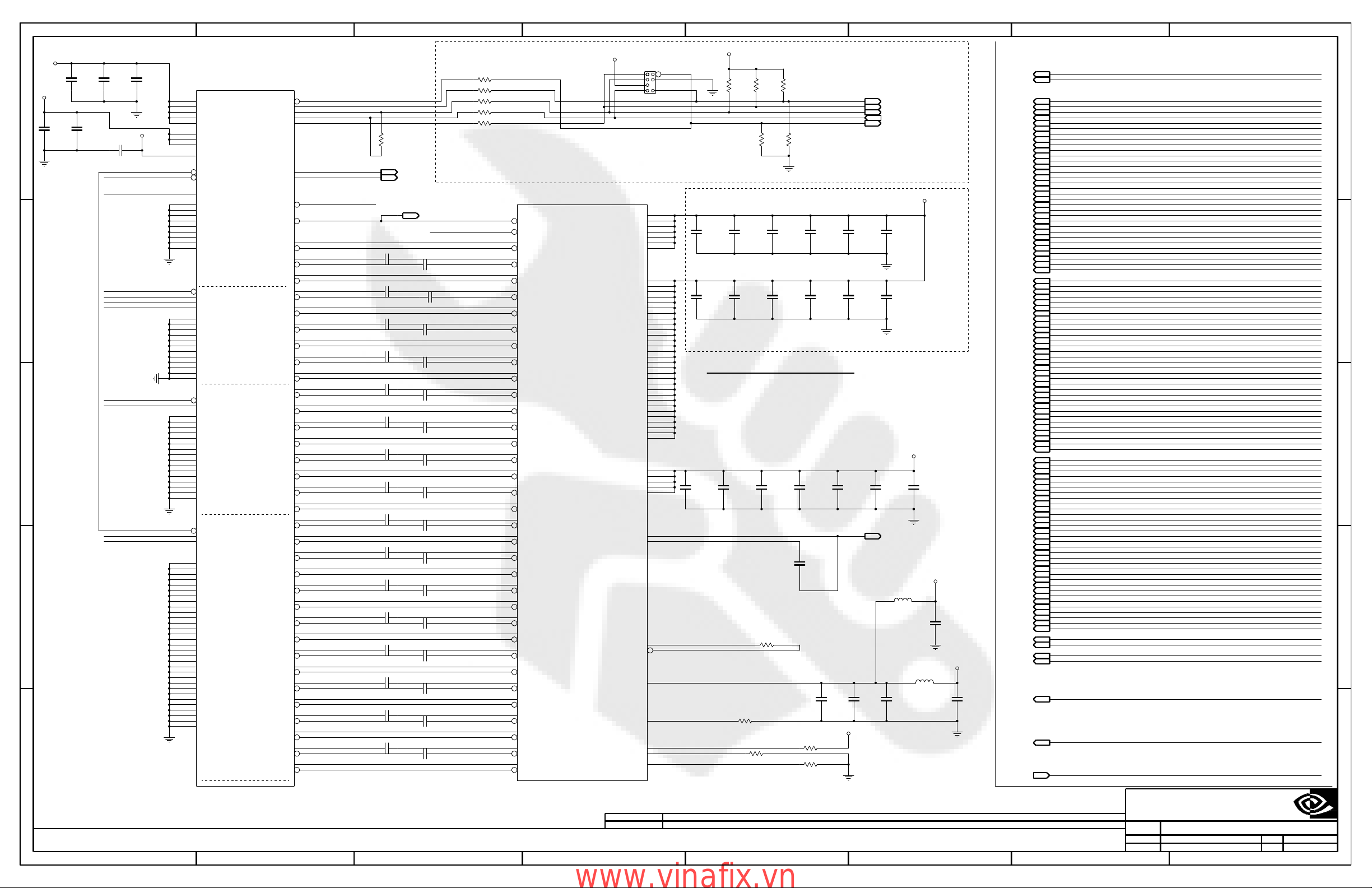

Page2: PCI Express

12V

3V3

C824

4.7UF

6.3V

10%

X5R

0603

COMMON

GND

3V3

R690

R715

GND

C656

.1UF

10V

10%

X5R

0402

COMMON

C668

10V

10%

X5R

0402

COMMON

R710

10K

5%

0402

COMMON

C682

.1UF

10V

10%

X5R

0402

COMMON

C689

.1UF.1UF

10V

10%

X5R

0402

COMMON

10K

5%

0402

COMMON

R702

10K

5%

0402

COMMON

GND

C666

1UF

6.3V

10%

X5R

0603

COMMON

C681

1UF

6.3V

10%

X5R

0603

COMMON

180

5%

0402

COMMON

R687

270

5%

0402

COMMON

JTAG_TCLK

JTAG_TMS

JTAG_TDI

JTAG_TDO

JTAG_TRST*

C659

1UF

6.3V

10%

X5R

0603

C653

6.3V

10%

X5R

0603

Matching Rule of Thumb

4 inch from Top of Gold Fingers to GPU

*2 inch Lane to Lane Skew

*No real Skew rule, but reducing the skew will minimize latency

VDD33

R620

0402

R619

0402

C725

.47UF

6.3V

10%

X5R

0402

COMMON

C673

.1UF

10V

10%

X5R

0402

COMMON

1%

1%

2.49K

COMMON

2.49K

COMMON

C716

.47UF

6.3V

10%

X5R

0402

COMMON

C718

1UF

6.3V

10%

X5R

0402

COMMON

SHOULD BE PLACED ON THE BOTTOM LAYER

R623

0402

10K

R616

COMMON

0402

5%

R618

0402

C768

.1UF

10V

10%

X5R

0402

COMMON

200

COMMON

5%

2.49K

COMMON

1%

C698

.1UF

6.3V

10%

X7R

0402

COMMON

PEX_VDD

JTAG

C693

4.7UF

6.3V

10%

X5R

0603

COMMONCOMMON

C708

4.7UF1UF

6.3V

10%

X5R

0603

COMMONCOMMON

C717

1UF

6.3V

10%

X5R

0402

COMMON

GND

C669

1UF

6.3V

10%

X5R

0402

COMMON

GND

GND

L501

2>

2>

2>

2<

2>

C731

.1UF

10V

10%

X5R

0402

COMMON

2>

0402

21<

21<

21<

21>

21<

C650

10UF

10V

10%

X5R

0805

COMMON

C651

10UF

10V

10%

X5R

0805

COMMON

29<

LB502

C690

1UF

6.3V

10%

X5R

0402

COMMON

2>

2>

2>

2<

2>

PEX_VDD

3V3

C723

1UF

6.3V

10%

X5R

0603

COMMON

GND

10nH

NO STUFF

0402 COMMON

21<

21<

21<

21>

21<

1V1_PLL

GND

10nH

C695

4.7UF

6.3V

10%

X5R

0603

NO STUFF

PEX_VDD

GND

C654

4.7UF

6.3V

10%

X5R

0603

COMMON

2> 25<

29< 2>

PEX_REFCLK

PEX_REFCLK*

PEX_TXX0

PEX_TXX0*

PEX_TXX1

PEX_TXX1*

PEX_TXX2

PEX_TXX2*

PEX_TXX3

PEX_TXX3*

PEX_TXX4

PEX_TXX4*

PEX_TXX5

PEX_TXX5*

PEX_TXX6

PEX_TXX6*

PEX_TXX7

PEX_TXX7*

PEX_TXX8

PEX_TXX8*

PEX_TXX9

PEX_TXX9*

PEX_TXX10

PEX_TXX10*

PEX_TXX11

PEX_TXX11*

PEX_TXX12

PEX_TXX12*

PEX_TXX13

PEX_TXX13*

PEX_TXX14

PEX_TXX14*

PEX_TXX15

PEX_TXX15*

PEX_RX0

PEX_RX0*

PEX_RX1

PEX_RX1*

PEX_RX2

PEX_RX2*

PEX_RX3

PEX_RX3*

PEX_RX4

PEX_RX4*

PEX_RX5

PEX_RX5*

PEX_RX6

PEX_RX6*

PEX_RX7

PEX_RX7*

PEX_RX8

PEX_RX8*

PEX_RX9

PEX_RX9*

PEX_RX10

PEX_RX10*

PEX_RX11

PEX_RX11*

PEX_RX12

PEX_RX12*

PEX_RX13

PEX_RX13*

PEX_RX14

PEX_RX14*

PEX_RX15

PEX_RX15*

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT*

PEX_RST*

PEX_PRSNT*

GPU_TESTMODE

NVVDD_SENSE_GPU

PEX_PLLVDD

90DIFF1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1 90DIFF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1 90DIFF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

3

3

3

1.1V

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

50OHM

50OHM

50OHM

0.16A

600-10547-0011-000 A

design

rachen

DIFFPAIRNV_IMPEDANCENV_CRITICALNET

PEX_REFCLK

PEX_REFCLK

PEX_TXX0

PEX_TXX0

PEX_TXX1

PEX_TXX1

PEX_TXX2

PEX_TXX2

PEX_TXX3

PEX_TXX3

PEX_TXX4

PEX_TXX4

PEX_TXX5

PEX_TXX5

PEX_TXX6

PEX_TXX6

PEX_TXX7

PEX_TXX7

PEX_TXX8

PEX_TXX8

PEX_TXX9

PEX_TXX9

PEX_TXX10

PEX_TXX10

PEX_TXX11

PEX_TXX11

PEX_TXX12

PEX_TXX12

PEX_TXX13

PEX_TXX13

PEX_TXX14

PEX_TXX14

PEX_TXX15

PEX_TXX15

PEX_RX0

PEX_RX0

PEX_RX1

PEX_RX1

PEX_RX2

PEX_RX2

PEX_RX3

PEX_RX3

PEX_RX4

PEX_RX4

PEX_RX5

PEX_RX5

PEX_RX6

PEX_RX6

PEX_RX7

PEX_RX7

PEX_RX8

PEX_RX8

PEX_RX9

PEX_RX9

PEX_RX10

PEX_RX10

PEX_RX11

PEX_RX11

PEX_RX12

PEX_RX12

PEX_RX13

PEX_RX13

PEX_RX14

PEX_RX14

PEX_RX15

PEX_RX15

PEX_TX0

PEX_TX0

PEX_TX1

PEX_TX1

PEX_TX2

PEX_TX2

PEX_TX3

PEX_TX3

PEX_TX4

PEX_TX4

PEX_TX5

PEX_TX5

PEX_TX6

PEX_TX6

PEX_TX7

PEX_TX7

PEX_TX8

PEX_TX8

PEX_TX9

PEX_TX9

PEX_TX10

PEX_TX10

PEX_TX11

PEX_TX11

PEX_TX12

PEX_TX12

PEX_TX13

PEX_TX13

PEX_TX14

PEX_TX14

PEX_TX15

PEX_TX15

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT

MIN_WIDTHMAX_CURRENTVOLTAGENET

12MIL

2 OF 32

07-AUG-2008

Page 3

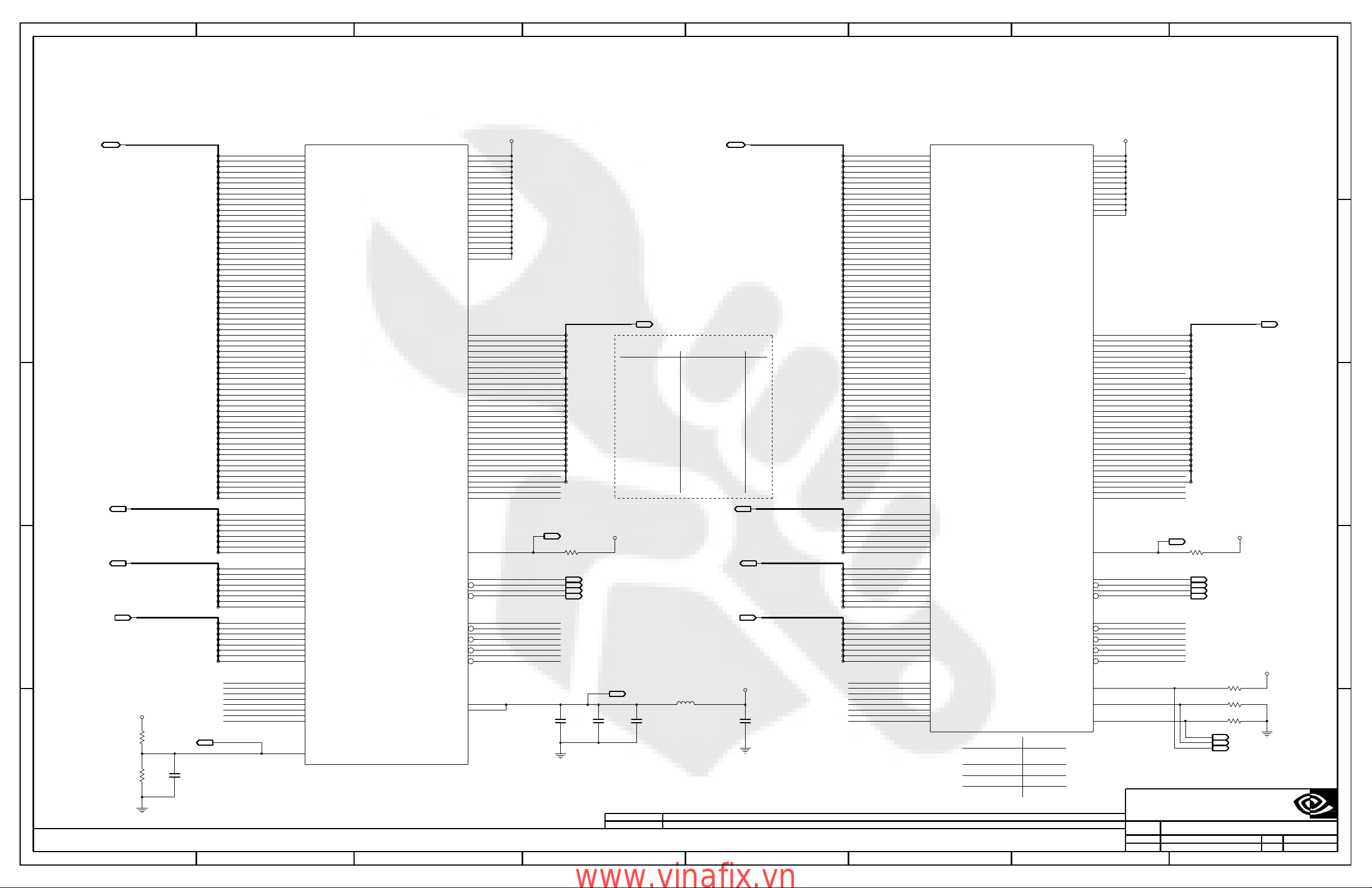

Page3: MEMORY: GPU Partition A/B

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

3/19 FBB

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD30

FBB_CMD29

FBB_CMD28

FBB_CMD27

FBB_CMD26

FBB_CMD25

FBB_CLK0

FBB_CLK0

FBB_WCK3

FBB_WCK2

FBB_WCK2

FBB_WCK1

FBB_WCK1

FBB_WCK0

FBB_WCK0

FBB_DEBUG

FBB_CLK1

FBB_CLK1

FBB_WCK3

FB_CAL_TERM_GND

FB_CAL_PU_GND

FB_CAL_PD_VDDQ

FBB_D0

FBB_D1

FBB_D2

FBB_D3

FBB_D4

FBB_D5

FBB_D6

FBB_D7

FBB_D8

FBB_D9

FBB_D10

FBB_D11

FBB_D12

FBB_D13

FBB_D14

FBB_D15

FBB_D16

FBB_D17

FBB_D18

FBB_D19

FBB_D20

FBB_D21

FBB_D22

FBB_D23

FBB_D24

FBB_D25

FBB_D26

FBB_D27

FBB_D28

FBB_D29

FBB_D30

FBB_D31

FBB_D32

FBB_D33

FBB_D34

FBB_D35

FBB_D36

FBB_D37

FBB_D38

FBB_D39

FBB_D40

FBB_D41

FBB_D42

FBB_D43

FBB_D44

FBB_D45

FBB_D46

FBB_D47

FBB_D48

FBB_D49

FBB_D50

FBB_D51

FBB_D52

FBB_D53

FBB_D54

FBB_D55

FBB_D56

FBB_D57

FBB_D58

FBB_D59

FBB_D60

FBB_D61

FBB_D62

FBB_D63

FBB_DQM0

FBB_DQM1

FBB_DQM2

FBB_DQM3

FBB_DQM4

FBB_DQM5

FBB_DQM6

FBB_DQM7

FBB_DQS_RN0

FBB_DQS_RN1

FBB_DQS_RN2

FBB_DQS_RN3

FBB_DQS_RN4

FBB_DQS_RN5

FBB_DQS_RN6

FBB_DQS_WP0

FBB_DQS_WP1

FBB_DQS_WP2

FBB_DQS_WP3

FBB_DQS_WP4

FBB_DQS_WP5

FBB_DQS_WP6

FBB_DQS_WP7

FBB_DQS_RN7

FBB_DBI0

FBB_DBI1

FBB_DBI2

FBB_DBI3

FBB_DBI4

FBB_DBI5

FBB_DBI6

FBB_DBI7

BI

OUT

OUT

OUTINOUT

OUT

OUT

OUT

OUT

OUT

BI

2/19 FBA

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBA_CMD0

FBA_CMD1

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBA_CMD21

FBA_CMD20

FBA_CMD19

FBA_CMD18

FBA_CMD17

FBA_CMD16

FBA_CMD15

FBA_CMD14

FBA_CMD13

FBA_CMD12

FBA_CMD11

FBA_CMD10

FBA_CMD9

FBA_CMD8

FBA_CMD7

FBA_CMD6

FBA_CMD5

FBA_CMD4

FBA_CMD3

FBA_CMD2

FBA_CMD22

FBA_DEBUG

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_WCK3

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_WCK0

FBA_WCK0

FBA_WCK1

FBA_WCK1

FBA_WCK2

FBA_WCK2

FBA_WCK3

FB_DLLAVDD0

FB_PLLAVDD0

FBA_D13

FBA_D12

FBA_D11

FBA_D10

FBA_D9

FBA_D8

FBA_D7

FBA_D6

FBA_D5

FBA_D4

FBA_D3

FBA_D2

FBA_D1

FBA_D0

FBA_D14

FBA_D34

FBA_D33

FBA_D32

FBA_D31

FBA_D30

FBA_D29

FBA_D28

FBA_D27

FBA_D26

FBA_D25

FBA_D24

FBA_D23

FBA_D22

FBA_D21

FBA_D20

FBA_D19

FBA_D18

FBA_D17

FBA_D16

FBA_D15

FBA_D54

FBA_D53

FBA_D52

FBA_D51

FBA_D50

FBA_D49

FBA_D48

FBA_D47

FBA_D46

FBA_D45

FBA_D44

FBA_D43

FBA_D42

FBA_D41

FBA_D40

FBA_D39

FBA_D38

FBA_D37

FBA_D36

FBA_D35

FBA_D55

FBA_DQM7

FBA_DQM6

FBA_DQM5

FBA_DQM4

FBA_DQM3

FBA_DQM2

FBA_DQM1

FBA_DQM0

FBA_D63

FBA_D62

FBA_D61

FBA_D60

FBA_D59

FBA_D58

FBA_D57

FBA_D56

FBA_DQS_WP7

FBA_DQS_WP6

FBA_DQS_WP5

FBA_DQS_WP4

FBA_DQS_WP3

FBA_DQS_WP2

FBA_DQS_WP1

FBA_DQS_WP0

FBA_DQS_RN7

FBA_DQS_RN6

FBA_DQS_RN5

FBA_DQS_RN4

FBA_DQS_RN3

FBA_DQS_RN2

FBA_DQS_RN1

FBA_DQS_RN0

FBA_DBI7

FBA_DBI6

FBA_DBI5

FBA_DBI4

FBA_DBI3

FBA_DBI2

FBA_DBI1

FBA_DBI0

FB_VREF

IN

OUT

OUT

OUT

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

G1

G94-400-A1

BGA1504

13<> 5<>

13> 5<>

13> 5<>

13<

5<>

FBA_D<63..0>

FBA_DQM<7..0>

FBA_DQS_WP<7..0>

FBA_DQS_RN<7..0>

FBVDDQ

R598

511

1%

0402

COMMON

R600

1.3K

1%

0402

COMMON

GND

13<>

C613

.1UF

6.3V

10%

X7R

0402

COMMON

FBA_D<0>

0

FBA_D<1>

1

FBA_D<2>

2

FBA_D<3>

3

FBA_D<4>

4

FBA_D<5>

5

FBA_D<6>

6

FBA_D<7>

7

FBA_D<8>

8

FBA_D<9>

9

FBA_D<10>

10

FBA_D<11>

11

FBA_D<12>

12

FBA_D<13>

13

FBA_D<14>

14

FBA_D<15>

15

FBA_D<16>

16

FBA_D<17>

17

FBA_D<18>

18

FBA_D<19>

19

FBA_D<20>

20

FBA_D<21>

21

FBA_D<22>

22

FBA_D<23>

23

FBA_D<24>

24

FBA_D<25>

25

FBA_D<26> AN39

26

FBA_D<27>

27

FBA_D<28>

28

FBA_D<29>

29

FBA_D<30>

30

FBA_D<31>

31

FBA_D<32>

32

FBA_D<33>

33

FBA_D<34>

34

FBA_D<35>

35

FBA_D<36>

36

FBA_D<37>

37

FBA_D<38>

38

FBA_D<39>

39

FBA_D<40>

40

FBA_D<41>

41

FBA_D<42>

42

FBA_D<43>

43

FBA_D<44>

44

FBA_D<45>

45

FBA_D<46>

46

FBA_D<47>

47

FBA_D<48>

48

FBA_D<49>

49

FBA_D<50>

50

FBA_D<51>

51

FBA_D<52>

52

FBA_D<53>

53

FBA_D<54>

54

FBA_D<55>

55

FBA_D<56>

56

FBA_D<57>

57

FBA_D<58>

58

FBA_D<59>

59

FBA_D<60>

60

FBA_D<61>

61

FBA_D<62>

62

FBA_D<63>

63

FBA_DQM<0>

0

FBA_DQM<1> AM39

1

FBA_DQM<2>

2

FBA_DQM<3>

3

FBA_DQM<4>

4

FBA_DQM<5>

5

FBA_DQM<6>

6

FBA_DQM<7>

7

FBA_DQS_WP<0>

0

FBA_DQS_WP<1>

1

FBA_DQS_WP<2>

2

FBA_DQS_WP<3>

3

FBA_DQS_WP<4>

4

FBA_DQS_WP<5>

5

FBA_DQS_WP<6>

6

FBA_DQS_WP<7>

7

0

FBA_DQS_RN<1>

1

FBA_DQS_RN<2>

2

FBA_DQS_RN<3>

3

FBA_DQS_RN<4>

4

FBA_DQS_RN<5>

5

FBA_DQS_RN<6>

6

FBA_DQS_RN<7>

7

SNN_FBA_DBI<0>

SNN_FBA_DBI<1>

SNN_FBA_DBI<2>

SNN_FBA_DBI<3>

SNN_FBA_DBI<4>

SNN_FBA_DBI<5>

SNN_FBA_DBI<6>

SNN_FBA_DBI<7>

AL34

AK35

AK36

AJ34

AH34

AH35

AJ36

AK37

AL39

AL41

AL42

AK42

AJ39

AH39

AH41

AH42

AN35

AP36

AP37

AR37

AM34

AL35

AL36

AL37

AP41

AP42

AN40

AN41

AN42

AR40

AT39

AR31

AP32

AR33

AT31

AT34

AU34

AU35

AU31

BB33

BA33

AY33

BA34

BB34

AW33

AW36

AY35

AU30

AP28

AP31

AR28

AW28

AP29

AR30

AT30

AW31

BA31

BB31

BB30

AW29

BB28

BA28

AY28

AJ37

AP35

AP40

AR34

AY34

AU29

AW32

AH36

AK41

AM36

AP38

AT33

AV34

AT28

AY30

AH37FBA_DQS_RN<0>

AK40

AN36

AP39

AT32

AW34

AU28

BA30

AH38

AL38

AN38

AR39

AV33

AW35

AT29

AV31

L32FB_VREF

COMMON

AA32

AB32

AC32

AD32

AD34

AE32

AF32

AG32

AG34

AK34

AN34

AP30

AP33

J10

J13

J16

J19

J24

J27

J30

AT40

AU38

AT38

BA39

AV37

BB39

AW38

AW42

AW39

AY41

AU39

AV36

BA40

AY39

AU40

BA37

AY36

AY37

AT37

AU36

AV39

AY38

AV40

AU42

AW40

AU41

AW41

BB37

AW37

AY42

BB40

AT36

AT41

AT42

BA36

BB36

AK38

AK39

AM37

AN37

AU32

AU33

AV30

AH32

AJ32

FBVDDQ

FBA_CMD<0>

FBA_CMD<1>

FBA_CMD<2>

FBA_CMD<3>

FBA_CMD<4>

FBA_CMD<5>

FBA_CMD<6>

SNN_FBA_CMD<7>

FBA_CMD<8>

FBA_CMD<9>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<12>

FBA_CMD<13>

FBA_CMD<14>

FBA_CMD<15>

FBA_CMD<16>

FBA_CMD<17>

FBA_CMD<18>

FBA_CMD<19>

FBA_CMD<20>

FBA_CMD<21>

FBA_CMD<22>

FBA_CMD<23>

FBA_CMD<24>

FBA_CMD<25>

SNN_FBA_CMD<26>

FBA_CMD<27>

SNN_FBA_CMD<28>

SNN_FBA_CMD<29>

SNN_FBA_CMD<30>

FBA_DEBUG

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

SNN_FBA_WDS0

SNN_FBA_WDS0*

SNN_FBA_WDS1

SNN_FBA_WDS1*

SNN_FBA_WDS2

SNN_FBA_WDS2*

SNN_FBA_WDS3

SNN_FBA_WDS3*AW30

FB_PLLAVDD0

7<> 13<>

0

1

2

3

4

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

FBA_CMD<27..0>

BGA136[31..0] BGA136[63..32] ADDR

CMD1 CMD1 RAS*

13>

5<

CMD-Addr Map

CMD10 CMD10 CAS*

CMD11 CMD11 WE*

CMD8 CMD8 CS0*

CMD19 CMD19 A<0>

CMD25 CMD25 A<1>

CMD22 A<2>

CMD24 A<3>

CMD0 A<4>

CMD2 A<5>

CMD4 A<2>

CMD6 A<3>

CMD5 A<4>

CMD13 A<5>

CMD21 CMD21 A<6>

CMD16 CMD16 A<7>

CMD23 CMD23 A<8>

CMD20 CMD20 A<9>

CMD17 CMD17 A<10>

CMD9 CMD9 A<11>

CMD12 CMD12 BA0

CMD3 CMD3 BA1

CMD27 CMD27 BA2

CMD18 CMD18 CKE

CMD15 CMD15 RST

7<> 13>

FBVDDQ

60.4

R601

NO STUFF

0402

1%

13>

5<

13>

5<

13>

5<

13>

5<

13>

7<>

7<> 13<

PEX_VDD

GND

GND

.1UF

6.3V

10%

X7R

0402

C635C636

1UF

6.3V

10%

X5R

0402

13<>

C633

1UF

6.3V

10%

X5R

0402

COMMONCOMMONCOMMON

LB501

BEAD_0402

120R@100MHz

COMMON

MEMORY: GPU Partition A/B

www.vinafix.vn

FBB_D<63..0>

FBB_DQM<7..0>

FBB_DQS_WP<7..0>

FBB_DQS_RN<7..0>

C644

4.7UF

6.3V

10%

X5R

0603

COMMON

FBB_D<0>

0

FBB_D<1>

1

FBB_D<2>

2

FBB_D<3>

3

FBB_D<4>

4

FBB_D<5>

5

FBB_D<6>

6

FBB_D<7>

7

FBB_D<8>

8

FBB_D<9>

9

FBB_D<10>

10

FBB_D<11>

11

FBB_D<12>

12

FBB_D<13>

13

FBB_D<14>

14

FBB_D<15>

15

FBB_D<16>

16

FBB_D<17>

17

FBB_D<18>

18

FBB_D<19>

19

FBB_D<20>

20

FBB_D<21>

21

FBB_D<22>

22

FBB_D<23>

23

FBB_D<24>

24

FBB_D<25>

25

FBB_D<26>

26

FBB_D<27>

27

FBB_D<28>

28

FBB_D<29>

29

FBB_D<30>

30

FBB_D<31>

31

FBB_D<32>

32

FBB_D<33>

33

FBB_D<34>

34

FBB_D<35>

35

FBB_D<36>

36

FBB_D<37>

37

FBB_D<38>

38

FBB_D<39>

39

FBB_D<40>

40

FBB_D<41>

41

FBB_D<42>

42

FBB_D<43>

43

FBB_D<44>

44

FBB_D<45>

45

FBB_D<46>

46

FBB_D<47>

47

FBB_D<48>

48

FBB_D<49>

49

FBB_D<50>

50

FBB_D<51>

51

FBB_D<52>

52

FBB_D<53>

53

FBB_D<54>

54

FBB_D<55>

55

FBB_D<56>

56

FBB_D<57>

57

FBB_D<58>

58

FBB_D<59>

59

FBB_D<60>

60

FBB_D<61>

61

FBB_D<62>

62

FBB_D<63>

63

FBB_DQM<0>

0

FBB_DQM<1>

1

FBB_DQM<2>

2

FBB_DQM<3>

3

FBB_DQM<4>

4

FBB_DQM<5>

5

FBB_DQM<6>

6

FBB_DQM<7>

7

FBB_DQS_WP<0>

0

FBB_DQS_WP<1>

1

FBB_DQS_WP<2>

2

FBB_DQS_WP<3>

3

FBB_DQS_WP<4>

4

FBB_DQS_WP<5>

5

FBB_DQS_WP<6>

6

FBB_DQS_WP<7>

7

FBB_DQS_RN<0>

0

FBB_DQS_RN<1>

1

FBB_DQS_RN<2>

2

FBB_DQS_RN<3>

3

FBB_DQS_RN<4>

4

FBB_DQS_RN<5>

5

FBB_DQS_RN<6>

6

FBB_DQS_RN<7>

7

SNN_FBB_DBI<0>

SNN_FBB_DBI<1>

SNN_FBB_DBI<2>

SNN_FBB_DBI<3>

SNN_FBB_DBI<4>

SNN_FBB_DBI<5>

SNN_FBB_DBI<6>

SNN_FBB_DBI<7>

C40

E39

F37

H37

G38

G39

H39

C41

D40

D41

C42

D42

H40

G41

G42

J37

K37

J38

J39

L36

M34

M35

M36

J40

J41

J42

K39

L39

M38

M39

M40

W35

W36

W37

W38

AA34

AA35

AA36

AA37

W40

AA40

AA41

AA42

AB40

AB41

AB42

AD40

AB34

AB35

AB36

AB37

AE35

AE36

AE37

AG36

AD41

AD42

AE38

AF39

AE42

AG40

AG41

AG42

G37

F41

L37

K42

AA38

AC39

AE34

AE41

F39

F40

K35

K41

Y39

AB39

AD36

AE40

F38

E40

K36

K40

W39

AB38

AD35

AE39

H36

F42

L34

K38

AA39

AD39

AG35

AG39

G1

G94-400-A1

BGA1504

COMMON

CALIBRATION PIN

FB_CALx_PD_VDDQ

FB_CALx_PU_GND

FB_CALx_TERM_GND

VREF RATIO

DDR3

60

40

40

0.7 FBVDDQ

FBVDDQ

J33

K34

K9

L17

L18

L19

L20G40

L23

L24

L25

L26

L27

R609

0402

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

0

1

2

3

4

5

6

8

9

1%

FBB_CMD<27..0>

60.4

NO STUFF

FBB_CMD<0>

N41

FBB_CMD<1>

R39

FBB_CMD<2>

N42

FBB_CMD<3>

V37

FBB_CMD<4>

T41

FBB_CMD<5>

T42

FBB_CMD<6>

V38

SNN_FBB_CMD<7>

R38

FBB_CMD<8>

N40

FBB_CMD<9>

U39

FBB_CMD<10>

N39

FBB_CMD<11>

V40

FBB_CMD<12>

R41

FBB_CMD<13>

V39

FBB_CMD<14>

P39

FBB_CMD<15>

V36

FBB_CMD<16>

V41

FBB_CMD<17>

T39

FBB_CMD<18>

T38

FBB_CMD<19>

T35

FBB_CMD<20>

T36

FBB_CMD<21>

T40

FBB_CMD<22>

R37

FBB_CMD<23>

M41

FBB_CMD<24>

T37

FBB_CMD<25>

M42

SNN_FBB_CMD<26>

R36

FBB_CMD<27>

V35

SNN_FBB_CMD<28>

V42

SNN_FBB_CMD<29>

R42

SNN_FBB_CMD<30>

R40

FBB_DEBUG

R34

FBB_CLK0

N37

FBB_CLK0*

N38

FBB_CLK1

U34

FBB_CLK1*

V34

SNN_FBB_WDS0

J35

SNN_FBB_WDS0*

J36

SNN_FBB_WDS1

N35

SNN_FBB_WDS1*

N36

SNN_FBB_WDS2

W41

SNN_FBB_WDS2*

W42

SNN_FBB_WDS3

AD37

SNN_FBB_WDS3*

AD38

FB_CAL_PD_VDDQ

M32

FB_CAL_PU_GND

N32

FB_CAL_TERM_GND

P32

600-10547-0011-000 A

design

rachen

7<

7<

7<

7<

R613

R608

R607

0402

0402

0402

FBVDDQ

13>

13>

13>

13>

13> 7<

FBVDDQ

54.9

COMMON

1%

40.2

COMMON

1%

40.2

COMMON

1%

GND

3 OF 32

07-AUG-2008

Page 4

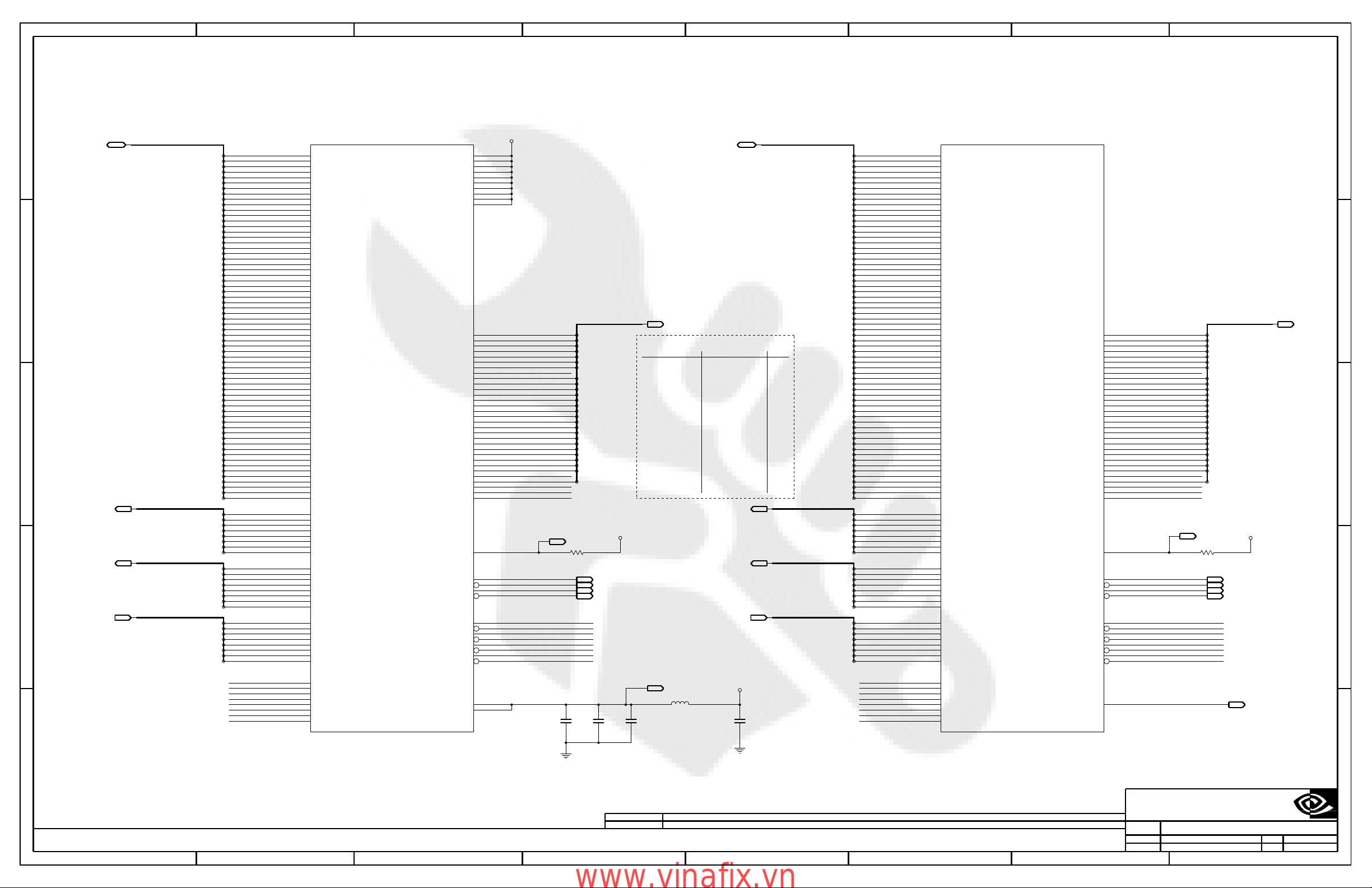

Page4: MEMORY: GPU Partition C/D

OUT

OUT

OUT

OUT

OUT

OUT

OUT

5/19 FBD

FBD_CMD0

FBD_CMD1

FBD_CMD2

FBD_CMD3

FBD_CMD4

FBD_CMD5

FBD_CMD6

FBD_CMD7

FBD_CMD8

FBD_CMD9

FBD_CMD10

FBD_CMD11

FBD_CMD12

FBD_CMD13

FBD_CMD14

FBD_CMD15

FBD_CMD16

FBD_CMD17

FBD_CMD18

FBD_CMD19

FBD_CMD20

FBD_CMD21

FBD_CMD22

FBD_CMD23

FBD_CMD24

FBD_CMD30

FBD_CMD29

FBD_CMD28

FBD_CMD27

FBD_CMD26

FBD_CMD25

FBD_CLK0

FBD_CLK0

FBD_WCK3

FBD_WCK2

FBD_WCK2

FBD_WCK1

FBD_WCK1

FBD_WCK0

FBD_WCK0

FBD_DEBUG

FBD_CLK1

FBD_CLK1

FBD_WCK3

FB_VDDQ_SENSE

FBD_D0

FBD_D1

FBD_D2

FBD_D3

FBD_D4

FBD_D5

FBD_D6

FBD_D7

FBD_D8

FBD_D9

FBD_D10

FBD_D11

FBD_D12

FBD_D13

FBD_D14

FBD_D15

FBD_D16

FBD_D17

FBD_D18

FBD_D19

FBD_D20

FBD_D21

FBD_D22

FBD_D23

FBD_D24

FBD_D25

FBD_D26

FBD_D27

FBD_D28

FBD_D29

FBD_D30

FBD_D31

FBD_D32

FBD_D33

FBD_D34

FBD_D35

FBD_D36

FBD_D37

FBD_D38

FBD_D39

FBD_D40

FBD_D41

FBD_D42

FBD_D43

FBD_D44

FBD_D45

FBD_D46

FBD_D47

FBD_D48

FBD_D49

FBD_D50

FBD_D51

FBD_D52

FBD_D53

FBD_D54

FBD_D55

FBD_D56

FBD_D57

FBD_D58

FBD_D59

FBD_D60

FBD_D61

FBD_D62

FBD_D63

FBD_DQM0

FBD_DQM1

FBD_DQM2

FBD_DQM3

FBD_DQM4

FBD_DQM5

FBD_DQM6

FBD_DQM7

FBD_DQS_RN0

FBD_DQS_RN1

FBD_DQS_RN2

FBD_DQS_RN3

FBD_DQS_RN4

FBD_DQS_RN5

FBD_DQS_RN6

FBD_DQS_WP0

FBD_DQS_WP1

FBD_DQS_WP2

FBD_DQS_WP3

FBD_DQS_WP4

FBD_DQS_WP5

FBD_DQS_WP6

FBD_DQS_WP7

FBD_DQS_RN7

FBD_DBI0

FBD_DBI1

FBD_DBI2

FBD_DBI3

FBD_DBI4

FBD_DBI5

FBD_DBI6

FBD_DBI7

BI

OUT

OUT

OUTINOUT

OUT

OUT

OUT

OUT

OUT

BI

4/19 FBC

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBC_CMD0

FBC_CMD1

FBC_CMD2

FBC_CMD3

FBC_CMD4

FBC_CMD5

FBC_CMD6

FBC_CMD7

FBC_CMD8

FBC_CMD9

FBC_CMD10

FBC_CMD11

FBC_CMD12

FBC_CMD13

FBC_CMD14

FBC_CMD15

FBC_CMD16

FBC_CMD17

FBC_CMD18

FBC_CMD19

FBC_CMD20

FBC_CMD21

FBC_CMD22

FBC_CMD23

FBC_CMD24

FBC_CMD30

FBC_CMD29

FBC_CMD28

FBC_CMD27

FBC_CMD26

FBC_CMD25

FBC_CLK0

FBC_CLK0

FBC_WCK3

FBC_WCK2

FBC_WCK2

FBC_WCK1

FBC_WCK1

FBC_WCK0

FBC_WCK0

FBC_DEBUG

FBC_CLK1

FBC_CLK1

FBC_WCK3

FB_PLLAVDD1

FB_DLLAVDD1

FBC_D0

FBC_D1

FBC_D2

FBC_D3

FBC_D4

FBC_D5

FBC_D6

FBC_D7

FBC_D8

FBC_D9

FBC_D10

FBC_D11

FBC_D12

FBC_D13

FBC_D14

FBC_D15

FBC_D16

FBC_D17

FBC_D18

FBC_D19

FBC_D20

FBC_D21

FBC_D22

FBC_D23

FBC_D24

FBC_D25

FBC_D26

FBC_D27

FBC_D28

FBC_D29

FBC_D30

FBC_D31

FBC_D32

FBC_D33

FBC_D34

FBC_D35

FBC_D36

FBC_D37

FBC_D38

FBC_D39

FBC_D40

FBC_D41

FBC_D42

FBC_D43

FBC_D44

FBC_D45

FBC_D46

FBC_D47

FBC_D48

FBC_D49

FBC_D50

FBC_D51

FBC_D52

FBC_D53

FBC_D54

FBC_D55

FBC_D56

FBC_D57

FBC_D58

FBC_D59

FBC_D60

FBC_D61

FBC_D62

FBC_D63

FBC_DQM0

FBC_DQM1

FBC_DQM2

FBC_DQM3

FBC_DQM4

FBC_DQM5

FBC_DQM6

FBC_DQM7

FBC_DQS_RN0

FBC_DQS_RN1

FBC_DQS_RN2

FBC_DQS_RN3

FBC_DQS_RN4

FBC_DQS_RN5

FBC_DQS_RN6

FBC_DQS_WP0

FBC_DQS_WP1

FBC_DQS_WP2

FBC_DQS_WP3

FBC_DQS_WP4

FBC_DQS_WP5

FBC_DQS_WP6

FBC_DQS_WP7

FBC_DQS_RN7

FBC_DBI0

FBC_DBI1

FBC_DBI2

FBC_DBI3

FBC_DBI4

FBC_DBI5

FBC_DBI6

FBC_DBI7

OUT

OUT

IN

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

G1

G94-400-A1

BGA1504

13<> 9<>

13>

13>

13<

9<>

9<>

9<>

FBC_D<63..0>

FBC_DQM<7..0>

FBC_DQS_WP<7..0>

FBC_DQS_RN<7..0>

FBC_D<0>

0

FBC_D<1>

1

FBC_D<2>

2

FBC_D<3>

3

FBC_D<4>

4

5

FBC_D<6>

6

FBC_D<7>

7

FBC_D<8>

8

FBC_D<9>

9

FBC_D<10>

10

FBC_D<11>

11

FBC_D<12>

12

FBC_D<13>

13

FBC_D<14>

14

FBC_D<15>

15

FBC_D<16>

16

FBC_D<17>

17

FBC_D<18>

18

FBC_D<19>

19

FBC_D<20>

20

FBC_D<21>

21

FBC_D<22>

22

FBC_D<23>

23

FBC_D<24>

24

FBC_D<25>

25

FBC_D<26> B22

26

FBC_D<27>

27

FBC_D<28>

28

FBC_D<29>

29

FBC_D<30>

30

FBC_D<31>

31

FBC_D<32>

32

FBC_D<33>

33

FBC_D<34>

34

FBC_D<35>

35

FBC_D<36>

36

FBC_D<37>

37

FBC_D<38>

38

FBC_D<39>

39

FBC_D<40>

40

FBC_D<41>

41

FBC_D<42>

42

FBC_D<43>

43

FBC_D<44>

44

FBC_D<45>

45

FBC_D<46>

46

FBC_D<47>

47

FBC_D<48>

48

FBC_D<49>

49

FBC_D<50>

50

FBC_D<51>

51

FBC_D<52>

52

FBC_D<53>

53

FBC_D<54>

54

FBC_D<55>

55

FBC_D<56>

56

FBC_D<57>

57

FBC_D<58>

58

FBC_D<59>

59

FBC_D<60>

60

FBC_D<61>

61

FBC_D<62>

62

FBC_D<63>

63

FBC_DQM<0>

0

FBC_DQM<1> B18

1

FBC_DQM<2>

2

FBC_DQM<3>

3

FBC_DQM<4>

4

FBC_DQM<5>

5

FBC_DQM<6>

6

FBC_DQM<7>

7

FBC_DQS_WP<0>

0

FBC_DQS_WP<1>

1

FBC_DQS_WP<2>

2

FBC_DQS_WP<3>

3

FBC_DQS_WP<4>

4

FBC_DQS_WP<5>

5

FBC_DQS_WP<6>

6

FBC_DQS_WP<7>

7

FBC_DQS_RN<0>

0

FBC_DQS_RN<1>

1

FBC_DQS_RN<2>

2

FBC_DQS_RN<3>

3

FBC_DQS_RN<4>

4

FBC_DQS_RN<5>

5

FBC_DQS_RN<6>

6

FBC_DQS_RN<7>

7

SNN_FBC_DBI<0>

SNN_FBC_DBI<1>

SNN_FBC_DBI<2>

SNN_FBC_DBI<3>

SNN_FBC_DBI<4>

SNN_FBC_DBI<5>

SNN_FBC_DBI<6>

SNN_FBC_DBI<7>

J21

H21

G21

F21

F18

G18FBC_D<5>

H18

G16

B16

A16

B19

A19

D17

E18

A18

C16

H24

G24

F24

E24

J22

H22

G22

F22

C24

C22

A22

C21

B21

A21

C19

F34

F33

E34

D34

G32

J31

H31

G31

C34

B34

A34

D33

D32

E31

D31

C31

D39

D38

G36

F35

E36

D36

C36

D35

B40

C39

B39

A40

A39

C35

B36

A36

J18

E22

D20

F32

A33

F36

B37

G19

C18

D23

D21

H33

B33

D37

C37

H19

D18

D24

E21

G33

C33

E37

C38

H16

D16

D22

D19

J32

E33

G35

A37

COMMON

N34

N9

R32

T32

T34

U32

V32

W32

W34

Y32

C25

A27

E25

D30

D28

E28

G27

D27

C30

B28

B25

A30

D26

F27

F25

B31

B30

D29

A28

E27

C27

G28

B27

G25

H27

H25

A25

A31

F28

C28

D25

J28

J26

J25

F30

E30

F19

E19

B24

A24

H30

G30

H34

G34

L21

L22

FBVDDQ

FBC_CMD<0>

FBC_CMD<1>

FBC_CMD<2>

FBC_CMD<3>

FBC_CMD<4>

FBC_CMD<5>

FBC_CMD<6>

SNN_FBC_CMD<7>

FBC_CMD<8>

FBC_CMD<9>

FBC_CMD<10>

FBC_CMD<11>

FBC_CMD<12>

FBC_CMD<13>

FBC_CMD<14>

FBC_CMD<15>

FBC_CMD<16>

FBC_CMD<17>

FBC_CMD<18>

FBC_CMD<19>

FBC_CMD<20>

FBC_CMD<21>

FBC_CMD<22>

FBC_CMD<23>

FBC_CMD<24>

FBC_CMD<25>

SNN_FBC_CMD<26>

FBC_CMD<27>

SNN_FBC_CMD<28>

SNN_FBC_CMD<29>

SNN_FBC_CMD<30>

FBC_DEBUG

FBC_CLK0

FBC_CLK0*

FBC_CLK1

FBC_CLK1*

SNN_FBC_WDS0

SNN_FBC_WDS0*

SNN_FBC_WDS1

SNN_FBC_WDS1*

SNN_FBC_WDS2

SNN_FBC_WDS2*

SNN_FBC_WDS3

SNN_FBC_WDS3*

FB_PLLAVDD1

11<> 13<>

0

1

2

3

4

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

FBC_CMD<27..0>

BGA136[31..0] BGA136[63..32] ADDR

13> 9<

CMD-Addr Map

CMD1 CMD1 RAS*

CMD10 CMD10 CAS*

CMD11 CMD11 WE*

CMD8 CMD8 CS0*

CMD19 CMD19 A<0>

CMD25 CMD25 A<1>

CMD22 A<2>

CMD24 A<3>

CMD0 A<4>

CMD2 A<5>

CMD4 A<2>

CMD6 A<3>

CMD5 A<4>

CMD13 A<5>

CMD21 CMD21 A<6>

CMD16 CMD16 A<7>

CMD23 CMD23 A<8>

CMD20 CMD20 A<9>

CMD17 CMD17 A<10>

CMD9 CMD9 A<11>

CMD12 CMD12 BA0

CMD3 CMD3 BA1

CMD27 CMD27 BA2

CMD18 CMD18 CKE

CMD15 CMD15 RST

11<> 13>

FBVDDQ

60.4

R615

NO STUFF

0402

1%

13>

9<

13>

9<

13>

9<

13>

9<

13>

11<>

11<> 13<

PEX_VDD

GND

C658

4.7UF

6.3V

10%

X5R

0603

COMMON

GND

C688

.1UF

6.3V

10%

X7R

0402

C687

1UF

6.3V

10%

X5R

0402

C675

1UF

6.3V

10%

X5R

0402

COMMONCOMMONCOMMON

LB504

BEAD_0402

13<>

120R@100MHz

COMMON

MEMORY: GPU Partition C/D

www.vinafix.vn

FBD_D<63..0>

FBD_DQM<7..0>

FBD_DQS_WP<7..0>

FBD_DQS_RN<7..0>

FBD_D<0>

0

FBD_D<1>

1

FBD_D<2>

2

FBD_D<3>

3

FBD_D<4>

4

FBD_D<5>

5

FBD_D<6>

6

FBD_D<7>

7

FBD_D<8>

8

FBD_D<9>

9

FBD_D<10>

10

FBD_D<11>

11

FBD_D<12>

12

FBD_D<13>

13

FBD_D<14>

14

FBD_D<15>

15

FBD_D<16>

16

FBD_D<17>

17

FBD_D<18>

18

FBD_D<19>

19

FBD_D<20>

20

FBD_D<21>

21

FBD_D<22>

22

FBD_D<23>

23

FBD_D<24>

24

FBD_D<25>

25

FBD_D<26>

26

FBD_D<27>

27

FBD_D<28>

28

FBD_D<29>

29

FBD_D<30>

30

FBD_D<31>

31

FBD_D<32>

32

FBD_D<33>

33

FBD_D<34>

34

FBD_D<35>

35

FBD_D<36>

36

FBD_D<37>

37

FBD_D<38>

38

FBD_D<39>

39

FBD_D<40>

40

FBD_D<41>

41

FBD_D<42>

42

FBD_D<43>

43

FBD_D<44>

44

FBD_D<45>

45

FBD_D<46>

46

FBD_D<47>

47

FBD_D<48>

48

FBD_D<49>

49

FBD_D<50>

50

FBD_D<51>

51

FBD_D<52>

52

FBD_D<53>

53

FBD_D<54>

54

FBD_D<55>

55

FBD_D<56>

56

FBD_D<57>

57

FBD_D<58>

58

FBD_D<59>

59

FBD_D<60>

60

FBD_D<61>

61

FBD_D<62>

62

FBD_D<63>

63

FBD_DQM<0>

0

FBD_DQM<1>

1

FBD_DQM<2>

2

FBD_DQM<3>

3

FBD_DQM<4>

4

FBD_DQM<5>

5

FBD_DQM<6>

6

FBD_DQM<7>

7

FBD_DQS_WP<0>

0

FBD_DQS_WP<1>

1

FBD_DQS_WP<2>

2

FBD_DQS_WP<3>

3

FBD_DQS_WP<4>

4

FBD_DQS_WP<5>

5

FBD_DQS_WP<6>

6

FBD_DQS_WP<7>

7

FBD_DQS_RN<0>

0

FBD_DQS_RN<1>

1

FBD_DQS_RN<2>

2

FBD_DQS_RN<3>

3

FBD_DQS_RN<4>

4

FBD_DQS_RN<5>

5

FBD_DQS_RN<6>

6

FBD_DQS_RN<7>

7

SNN_FBD_DBI<0>

SNN_FBD_DBI<1>

SNN_FBD_DBI<2>

SNN_FBD_DBI<3>

SNN_FBD_DBI<4>

SNN_FBD_DBI<5>

SNN_FBD_DBI<6>

SNN_FBD_DBI<7>

H12

J11

H10

G12

F12

A10

B10

C10

D10

F13

J15

J12

H15

D15

J14

H13

G13

D12

B12

A12

A13

D14

A15

B15

C15

F14

D11

G10

G15

C13

G11

F15

B13

E10

G14

E12

M9

N8

N7

P9

R9

R8

P7

N6

M4

M2

M1

N1

P4

R4

R2

R1

K8

J7

J6

H6

L9

M8

M7

M6

J2

J1

K4

K3

K2

K1

H3

G4

G9

F9

F8

B9

A9

D7

C8

P6

L4

J8

J3

H9

C9

R7

N2

L7

J5

E9

R6

N3

K7

J4

D9

R5

M5

K5

H4

D8

G1

G94-400-A1

BGA1504

COMMON

R627

0402

0

1

2

3

4

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

1%

FBD_CMD<27..0>

60.4

NO STUFF

FBD_CMD<0>

G3

FBD_CMD<1>

F5

FBD_CMD<2>

G5

FBD_CMD<3>

B4

FBD_CMD<4>

E6

FBD_CMD<5>

A4

FBD_CMD<6>

D5

SNN_FBD_CMD<7>

D1

FBD_CMD<8>

D4

FBD_CMD<9>

C2

FBD_CMD<10>

F4

FBD_CMD<11>

E7

FBD_CMD<12>

B3

FBD_CMD<13>

C4

FBD_CMD<14>

F3

FBD_CMD<15>

B6

FBD_CMD<16>

C7

FBD_CMD<17>

C6

FBD_CMD<18>

G6

FBD_CMD<19>

F7

FBD_CMD<20>

E4

FBD_CMD<21>

C5

FBD_CMD<22>

E3

FBD_CMD<23>

F1

FBD_CMD<24>

D3

FBD_CMD<25>

F2

SNN_FBD_CMD<26>

D2

FBD_CMD<27>

A6

SNN_FBD_CMD<28>

D6

SNN_FBD_CMD<29>

C1

SNN_FBD_CMD<30>

A3

FBD_DEBUG

G7

FBD_CLK0

G1

FBD_CLK0*

G2

FBD_CLK1

B7

FBD_CLK1*

A7

SNN_FBD_WDS0

N5

SNN_FBD_WDS0*

N4

SNN_FBD_WDS1

L6

SNN_FBD_WDS1*

K6

SNN_FBD_WDS2

F11

SNN_FBD_WDS2*

F10

SNN_FBD_WDS3

E13

SNN_FBD_WDS3*

D13

FBVDDQ_SENSE

J34

600-10547-0011-000 A

design

rachen

FBVDDQ

13> 11<

13> 11<

13> 11<

13> 11<

28<

4 OF 32

07-AUG-2008

13> 11<

Page 5

OUT

OUTINOUTININ

OUT

MIRRORED

VDD

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSS

VREF

VREF

VSS

VSSA (GND)

VSSA (GND)

VDDA (VDD)

VDDA (VDD)

A12 (32Mx32)

RAS

CS0

CAS

A0

WE

A3

A2

A1

A5

A4

A11

A10

A8/AP

BA1

BA0

A9

A6

A7

BA2

CLK

CLK

NC/RFU

SEN (GND)

CKE

MF (VDDQ)

RESET

ZQ

OUT

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

ININOUTININ

NONMIRRORED

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSSQ

VSS

VSS

VSS

VSS

VSS

VREF

VREF

A12 (32Mx32)

VDDA (VDD)

VSSA (GND)

VSSA (GND)

VDDA (VDD)

RAS

CAS

CS0

WE

A0

A2

A3

A4

A5

A1

BA1

A11

A10

A8/AP

BA0

A9

A7

A6

BA2

NC/RFU

SEN (GND)

CLK

CLK

CKE

RESET

MF (GND)

ZQ

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

WDQS

RDQS

DQ0

DQ4

DQ1

DQ2

DQ3

DQ5

DQM

DQ7

DQ6

BIBIBI

BI

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

Page5: FBA Partition

13> 3>

CMD-Addr Map

FBVDDQ

R564

0

FBA_CLK0_TERM

1%

R558

121

0402

COMMON

5%

0402

NO STUFF

1%

13>

C557

.01UF

16V

10%

X7R

0402

COMMON

R555

121

GND

0402

COMMON

3>

13>

3>

13>

MUST BE PLACED as close as possible to

the BGA memory on the line AFTER the

MEMORY pin!!

BGA136 ADDR

CMD1 RAS*

CMD10 CAS*

CMD11 WE*

CMD8 CS0*

CMD19 A<0>

CMD25 A<1>

CMD22 A<2>

CMD24 A<3>

CMD0 A<4>

CMD2 A<5>

CMD21 A<6>

CMD16 A<7>

CMD23 A<8>

CMD20 A<9>

CMD17 A<10>

CMD9 A<11>

CMD12 BA0

CMD3 BA1

CMD27 BA2

CMD18 CKE

CMD15 RST

Minimize the stub length!!

ZQ = 6x desired output

DDR3:

impedence of DQ drivers

Impedence = 240 / 6 = 40 ohm

13<>

13>

13<

13>

3<>

3>

3<

3>

FBA_D<63..0>

FBA_DQM<7..0>

FBA_DQS_RN<7..0>

FBA_DQS_WP<7..0>

FBA_CMD<27..0>

R566

0

5%

0402

COMMON

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

13<> GND

FBA_DQM<0>

FBA_DQM<1>

FBA_DQM<2>

FBA_DQM<3>

FBA_DQM<4>

FBA_DQM<5>

FBA_DQM<6>

FBA_DQM<7>

FBA_DQS_RN<0>

FBA_DQS_RN<1>

FBA_DQS_RN<2>

FBA_DQS_RN<3>

FBA_DQS_RN<4>

FBA_DQS_RN<5>

FBA_DQS_RN<6>

FBA_DQS_RN<7>

FBA_DQS_WP<0>

FBA_DQS_WP<1>

FBA_DQS_WP<2>

FBA_DQS_WP<3>

FBA_DQS_WP<4>

FBA_DQS_WP<5>

FBA_DQS_WP<6>

FBA_DQS_WP<7>

R568

10K

0402

COMMON

1

10

11

8

19

25

22

24

0

2

21

16

23

20

17

9

12

3

27

18

14

15

5%

GND

FBVDDQ

GND

CMD7 CMD7 BA2

FBA_CMD<1>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<8>

FBA_CMD<19>

FBA_CMD<25>

FBA_CMD<22>

FBA_CMD<24>

FBA_CMD<0>

FBA_CMD<2>

FBA_CMD<21>

FBA_CMD<16>

FBA_CMD<23>

FBA_CMD<20>

FBA_CMD<17>

FBA_CMD<9>

FBA_CMD<12>

FBA_CMD<3>

FBA_CMD<27>

FBA_CMD<18>

FBA_CLK0

FBA_CLK0*

SNN_FBA0_NC1

FBA_CMD<14>

FBA_CMD_SENA0

FBA_CMD<15>

FBA_ZQ0

R551

10K

5%

0402

COMMON

GND

C575

.047UF

16V

10%

X7R

0402

COMMON

0

1

2

3

4

5

6

7

32

33

34

35

36

37

38

39

M6

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

COMMON

H3

F4

H9

F9

K4

H2

K3

M4

K9

H11

K10

L9

K11

M9

K2

L4

G4

G9

H10

H4

J11

J10

J2

J3

V4

V9

A9

A4

R560

243

1%

0603

COMMON

GNDGND

K1

K12

C549

.047UF

16V

10%

X7R

0402

COMMON

J1

J12

FBA_D<0>

FBA_D<1>

FBA_D<2>

FBA_D<3>

FBA_D<4>

FBA_D<5>

FBA_D<6>

FBA_DQM<0>

FBA_DQS_RN<0>

FBA_DQS_WP<0>

FBA_D<32>

FBA_D<33>

FBA_D<34> R3

FBA_D<35>

FBA_D<36>

FBA_D<37>

FBA_D<38>

FBA_D<39>

FBA_DQM<4>

FBA_DQS_RN<4>

FBA_DQS_WP<4>

G10

F11

E11

B10

B11

C11

C10

F10FBA_D<7>

E10

D10

D11

M6

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

COMMON

M7

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

COMMON

L3

N2

M3

R2

T3

T2

M2

N3

P3

P2

FBVDDQ

F1

M1

A2

V2

A11

V11

F12

M12

A1

C1

E1

N1

R1

V1

C4

E4

J4

N4

R4

C9

E9

J9

N9

R9

A12

C12

E12

N12

R12

V12

B1

D1

P1

T1

G2

L2

B4

D4

P4

T4

B9

D9

P9

T9

G11

L11

B12

D12

P12

T12

G1

L1

A3

V3

A10

V10

G12

L12

H1

H12

8

9

10

11

12

13

14

15

40

41

42

43

44

45

46

47

GND

GND

FBA_VREF0

FBA_VREF2

VREF = FBVDDQ * R2/(R1 + R2)

VREF = 0.70 * FBVDDQ

DDR3:

1.26V = 1.8V * 1.18K/(511 + 1.18K)

FBA_D<8>

FBA_D<9>

FBA_D<10>

FBA_D<11>

FBA_D<12>

FBA_D<13>

FBA_D<14>

FBA_D<15>

FBA_DQM<1>

FBA_DQS_RN<1>

FBA_DQS_WP<1>

FBA_D<40>

FBA_D<41>

FBA_D<42>

FBA_D<43>

FBA_D<44>

FBA_D<45>

FBA_D<46>

FBA_D<47>

FBA_DQM<5>

FBA_DQS_RN<5>

FBA_DQS_WP<5>

FBVDDQ

R580

0

FBA_CLK1_TERM

1%

R579

121

0402

COMMON

5%

0402

NO STUFF

1%

13>

C570

.01UF

16V

10%

X7R

0402

COMMON

R574

121

GND

0402

COMMON

3>

13>

3>

13>

MUST BE PLACED as close as possible to

the BGA memory on the line AFTER the

MEMORY pin!!

Minimize the stub length!!

FBVDDQ

R584

511

R1

1%

0402

COMMON

13<>

C584R583

1.3K

0402

COMMON

R2

1%

GND

.1UF

10V

10%

X5R

0402

COMMON

R60

511

0402

COMMON

R59

1.3K

0402

COMMON

FBVDDQ

1%

1%

R1

R2

GND

M6

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

M10

M11

L10

N11

R11

T11

T10

R10

N10

P10

P11

G3

F3

F2

E2

C2

C3

B2

B3

E3

D3

D2

COMMON

M7

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

COMMON

16

17

18

19

20

21

22

23

48

49

50

51

52

53

54

55

FBA_D<16>

FBA_D<17>

FBA_D<18>

FBA_D<19>

FBA_D<20>

FBA_D<21>

FBA_D<22>

FBA_D<23>

FBA_DQM<2>

FBA_DQS_RN<2>

FBA_DQS_WP<2>

FBA_D<48>

FBA_D<49>

FBA_D<50>

FBA_D<51>

FBA_D<52>

FBA_D<53>

FBA_D<54>

FBA_D<55>

FBA_DQM<6>

FBA_DQS_RN<6>

FBA_DQS_WP<6>

CMD-Addr Map

BGA136 ADDR

CMD1 RAS*

CMD10 CAS*

CMD11 WE*

CMD8 CS0*

CMD19 A<0>

CMD25 A<1>

CMD4 A<2>

CMD6 A<3>

CMD5 A<4>

CMD13 A<5>

CMD21 A<6>

CMD16 A<7>

CMD23 A<8>

CMD20 A<9>

CMD17 A<10>

CMD9 A<11>

CMD12 BA0

CMD3 BA1

CMD27 BA2

CMD18 CKE

CMD15 RST

GND

ZQ = 6x desired output

DDR3:

impedence of DQ drivers

Impedence = 240 / 6 = 40 ohm

C46

.1UF

10V

10%

X5R

0402

COMMON

M6

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

COMMON

R10

T11

T10

R11

N11

L10

M11

M10

N10

P10

P11

M7

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

COMMON

E2

C2

G3

C3

B3

B2

F2

F3