Page 1

5

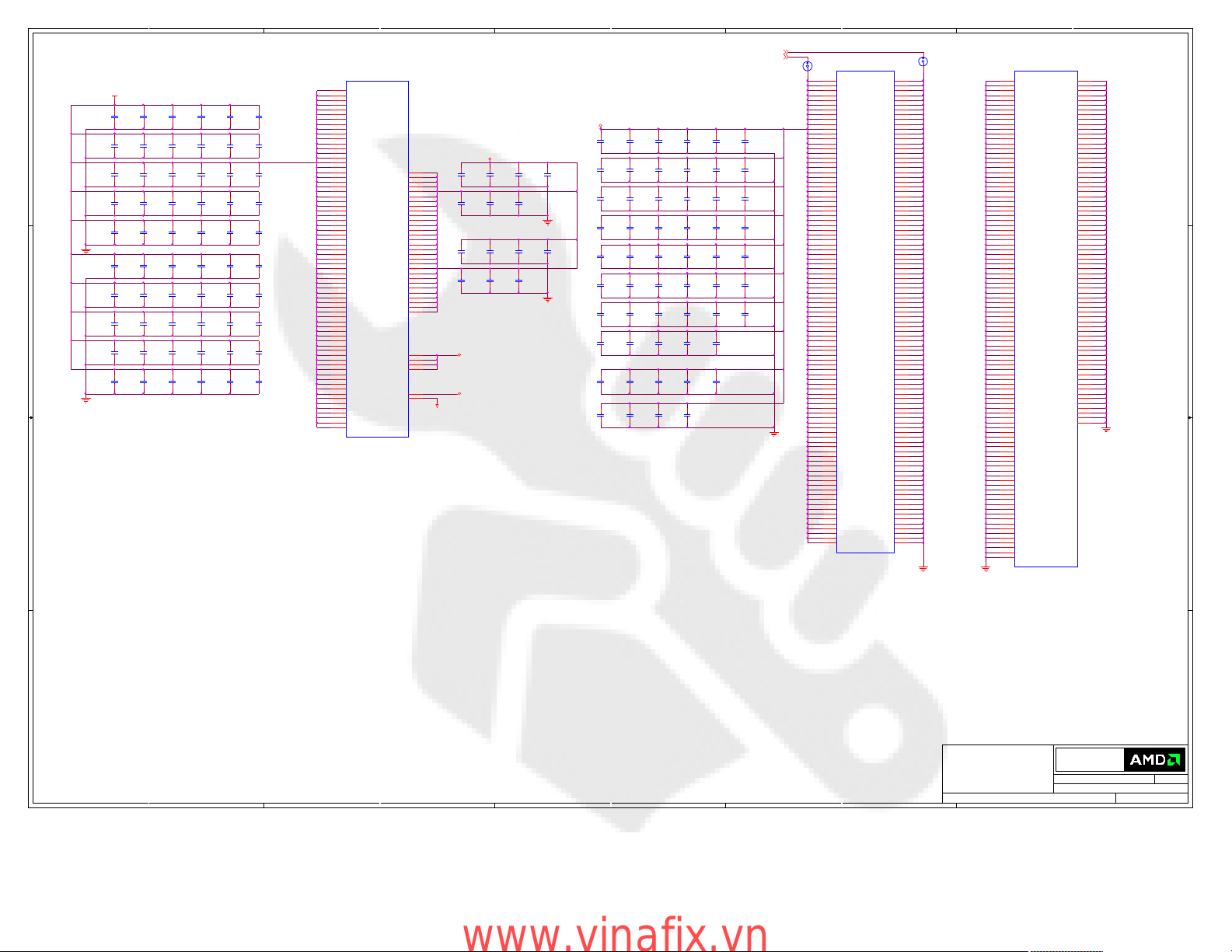

PCIE_REFCLKP(10)

PCIE_REFCLKN(10)

D D

C C

PCIE_RXP[15..0](10)

PCIE_RXN[15..0](10)

PCIE_TXP[15..0](10)

PCIE_TXN[15..0](10)

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_RXP[15..0]

PCIE_RXN[15..0]

PCIE_TXP[15..0]

PCIE_TXN[15..0]

PCIE_VDDC: 1.0V-1.1V,+-5%, 2.5A

B B

A A

5

PCIE_VDDR: 1.8V,+-5%, 700mA

1.1V_REG

4

4

PCIE_RXP0

PCIE_RXN0

PCIE_RXP1

PCIE_RXN1

PCIE_RXP2

PCIE_RXN2

PCIE_RXP3

PCIE_RXN3

PCIE_RXP4

PCIE_RXN4

PCIE_RXP5

PCIE_RXN5

PCIE_RXP6

PCIE_RXN6

PCIE_RXP7

PCIE_RXN7

PCIE_RXP8

PCIE_RXN8

PCIE_RXP9

PCIE_RXN9

PCIE_RXP10

PCIE_RXN10

PCIE_RXP11

PCIE_RXN11

PCIE_RXP12

PCIE_RXN12

PCIE_RXP13

PCIE_RXN13

PCIE_RXP14

PCIE_RXN14

PCIE_RXP15

PCIE_RXN15

PCIE_REFCLKP

PCIE_REFCLKN

R21.27K R21.27K

R12.0K R12.0K

1.1V_REG

PCIE_VDDR

AM48

AK52

AK48

AH52

AH48

AG49

AG51

AF52

AF48

AE49

AE51

AD52

AD48

AC49

AC51

AB52

AB48

AA49

AA51

AM45

AM44

AF39

AF38

AF37

AA38

AA39

AB37

AB38

AB39

AD37

AD38

AD39

AE37

AE38

AE39

AM40

AH37

AK38

AK39

AK37

AM37

AM38

AM39

AN37

AN38

AN39

AR39

AR40

AA40

AA43

AA47

AB50

AB40

AB43

AC53

AC47

AD50

AD40

AD43

AE53

AE40

AE43

AE47

AF50

AF40

AF43

AG53

AG47

AL49

AL51

AJ49

AJ51

Y52

Y48

W49

W51

V52

V48

U49

U51

T52

W38

W39

W40

W41

W42

W43

W44

W45

AJ38

AJ39

AJ37

U1A

U1A

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_CALRP

PCIE_CALRN

PCIE_VDDC#1

PCIE_VDDC#2

PCIE_VDDC#3

PCIE_VDDC#4

PCIE_VDDC#5

PCIE_VDDC#6

PCIE_VDDC#7

PCIE_VDDC#8

PCIE_VDDC#9

PCIE_VDDC#10

PCIE_VDDC#11

PCIE_VDDC#12

PCIE_VDDC#13

PCIE_VDDC#14

PCIE_VDDC#15

PCIE_VDDC#16

PCIE_VDDC#17

PCIE_VDDC#18

PCIE_VDDC#19

PCIE_VDDC#20

PCIE_VDDR#1

PCIE_VDDR#2

PCIE_VDDR#3

PCIE_VDDR#4

PCIE_VDDR#5

PCIE_VDDR#6

PCIE_VDDR#7

PCIE_VDDR#8

PCIE_VDDR#9

PCIE_VDDR#10

PCIE_VDDR#11

PCIE_VDDR#12

PCIE_VDDR#13

PCIE_VDDR#14

PCIE_VDDR#15

PCIE_VDDR#16

PCIE_VSS#1

PCIE_VSS#2

PCIE_VSS#3

PCIE_VSS#4

PCIE_VSS#5

PCIE_VSS#6

PCIE_VSS#7

PCIE_VSS#8

PCIE_VSS#9

PCIE_VSS#10

PCIE_VSS#11

PCIE_VSS#12

PCIE_VSS#13

PCIE_VSS#14

PCIE_VSS#15

PCIE_VSS#16

PCIE_VSS#17

PCIE_VSS#18

PCIE_VSS#19

PCIE_VSS#20

216-0732004-00

216-0732004-00

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

PERSTB

PCIE_PVDD

PCIE_VSS#21

PCIE_VSS#22

PCIE_VSS#23

PCIE_VSS#24

PCIE_VSS#25

PCIE_VSS#26

PCIE_VSS#27

PCIE_VSS#28

PCIE_VSS#29

PCIE_VSS#30

PCIE_VSS#31

PCIE_VSS#32

PCIE_VSS#33

PCIE_VSS#34

PCIE_VSS#35

PCIE_VSS#36

PCIE_VSS#37

PCIE_VSS#38

PCIE_VSS#39

PCIE_VSS#40

PCIE_VSS#41

PCIE_VSS#42

PCIE_VSS#43

PCIE_VSS#44

PCIE_VSS#45

PCIE_VSS#46

PCIE_VSS#47

PCIE_VSS#48

PCIE_VSS#49

PCIE_VSS#50

PCIE_VSS#51

PCIE_VSS#52

PCIE_VSS#53

PCIE_VSS#54

PCIE_VSS#55

PCIE_VSS#56

PCIE_VSS#57

PCIE_VSS#58

PCIE_VSS#59

PCIE_VSS#60

PCIE_VSS#61

PCIE_VSS#62

PCIE_VSS#63

PCIE_VSS#64

PCIE_VSS#65

PCIE_VSS#66

PCIE_VSS#67

PCIE_VSS#68

PCIE_VSS#69

PCIE_VSS#70

PCIE_VSS#71

PCIE_VSS#72

PCIE_VSS#73

PCIE_VSS#74

PCIE_VSS#75

PCIE_VSS#76

PCIE_VSS#77

PCIE_VSS#78

PCIE_VSS#79

PCIE_VSS#80

PCIE_VSS#81

PCIE_VSS#82

3

PCIE_TXP0

AK45

PCIE_TXN0

AK44

PCIE_TXP1

AK42

PCIE_TXN1

AK41

PCIE_TXP2

AJ45

PCIE_TXN2

AJ44

PCIE_TXP3

AJ42

PCIE_TXN3

AJ41

PCIE_TXP4

AH45

PCIE_TXN4

AH44

PCIE_TXP5

AH42

PCIE_TXN5

AH41

PCIE_TXP6

AF45

PCIE_TXN6

AF44

PCIE_TXP7

AF42

PCIE_TXN7

AF41

PCIE_TXP8

AE45

PCIE_TXN8

AE44

PCIE_TXP9

AE42

PCIE_TXN9

AE41

PCIE_TXP10

AD45

PCIE_TXN10

AD44

PCIE_TXP11

AD42

PCIE_TXN11

AD41

PCIE_TXP12

AB45

PCIE_TXN12

AB44

PCIE_TXP13

AB42

PCIE_TXN13

AB41

PCIE_TXP14

AA45

PCIE_TXN14

AA44

PCIE_TXP15

AA42

PCIE_TXN15

AA41

AT39

AR37

PCIE_PVDD

PCIE_PVDD: 1.8V,+-3%, 40mA

AH50

AH40

AH43

AJ53

AJ40

AJ43

AJ47

AK50

AK40

AK43

AL53

AL47

AM50

AA53

AM43

AN53

AN40

AN43

AN47

AP50

AR53

Y50

AR43

AR47

AT50

AT40

AT43

AU53

AU40

AU43

AU47

AV50

AW53

AW40

AW43

AW47

AY50

AY40

AY43

BA53

BA47

BB50

BB43

BC53

BB42

BC47

BD50

BD44

BD45

BF53

BE47

BF50

BJ53

BL45

BN46

W47

BN49

T50

U53

U47

V50

W53

3

PCIE_RST# (10)

2

U1J

U1J

BK49

SP_RX0P

BL51

SP_RX0N

BJ50

SP_RX1P

BG52

SP_RX1N

BF48

SP_RX2P

BE49

SP_RX2N

BE51

SP_RX3P

BD52

SP_RX3N

BD48

SP_RX4P

BC49

SP_RX4N

BC51

SP_RX5P

BB52

SP_RX5N

BB48

SP_RX6P

BA49

SP_RX6N

BA51

SP_RX7P

AY52

SP_RX7N

AY48

SP_RX8P

AW49

SP_RX8N

AW51

SP_RX9P

AV52

SP_RX9N

AV48

SP_RX10P

AU49

SP_RX10N

AU51

SP_RX11P

AT52

SP_RX11N

AT48

SP_RX12P

AR49

SP_RX12N

AR51

SP_RX13P

AP52

SP_RX13N

AP48

SP_RX14P

AN49

SP_RX14N

AN51

SP_RX15P

AM52

SP_RX15N

BM47

SP_REFCLKP

BK46

SP_REFCLKN

216-0732004-00

216-0732004-00

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

M98-L 1GB DDR3 MXM 3.0 CF

M98-L 1GB DDR3 MXM 3.0 CF

M98-L 1GB DDR3 MXM 3.0 CF

2

SP_TX0P

SP_TX0N

SP_TX1P

SP_TX1N

SP_TX2P

SP_TX2N

SP_TX3P

SP_TX3N

SP_TX4P

SP_TX4N

SP_TX5P

SP_TX5N

SP_TX6P

SP_TX6N

SP_TX7P

SP_TX7N

SP_TX8P

SP_TX8N

SP_TX9P

SP_TX9N

SP_TX10P

SP_TX10N

SP_TX11P

SP_TX11N

SP_TX12P

SP_TX12N

SP_TX13P

SP_TX13N

SP_TX14P

SP_TX14N

SP_TX15P

SP_TX15N

SP_CALRP

SP_CALRN

SP_PVDD

1

BH48

BH46

BC45

BC44

BB45

BB44

AY42

AY41

AY45

AY44

AW42

AW41

AW45

AW44

AU42

AU41

AU45

AU44

AT42

AT41

AT45

AT44

AR42

AR41

AR45

AR44

AN42

AN41

AN45

AN44

AM42

AM41

AH39

AH38

AR38

PCIE_PVDD

SP_PVDD: 1.8V,+-5%, 35mA

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Wednesday, May 14, 2008

Wednesday, May 14, 2008

Wednesday, May 14, 2008

Sheet

Sheet

Sheet

of

1 15

of

1 15

of

1 15

Doc No.

Doc No.

Doc No.

1

RevDate:

RevDate:

RevDate:

0

0

0

105-B735xx-00A

105-B735xx-00A

105-B735xx-00A

www.vinafix.vn

Page 2

5

4

3

2

1

DPAVDDR: 1.1V,+-3%, 200mA

D D

DPAVDDR

DPBVDDR

DPBVDDR: 1.1V,+-3%, 200mA

LVDDC: 1.8V,+-3%, 400mA

DPA_PVDD: 1.8V,+-3%, 20mA

DPB_PVDD: 1.8V,+-3%, 20mA

C C

LPVDD: 1.8V,+-3%, 40mA

AVDD: 1.8V,+-5%, 70mA

VDD1DI: 1.8V,+-5%, 50mA

A2VDD: 3.3V,+-5%, 135mA

VDD2DI: 1.8V,+-5%, 40mA

A2VDDQ: 1.8V,+-5%, 1mA

B B

DPLL_VDDC: 1.1V,+-5%, 100mA

DPLL_PVDD: 1.8V,+-3%, 40mA

LVDDC

DPA_PVDD

GND_DPA_PVSS

DPB_PVDD

GND_DPB_PVSS

R22150R R22150R

LPVDD

GND_LPVSS

DAC1_AVDD

VDD1DI

499R

499R

A2VDD

GND_A2VSSQ

VDD2DI

GND_VSS2DI

R30

R30

715R

715R

A2VDDQ

DPLL_VDDC

DPLL_PVDD

XTALIN(14)

DP_CALR

GND_AVSSQ

GND_VSS1DI

R29

R29

GND_PVSS

TP7TP7

XTALIN

U1B

U1B

BD29

DPAVDDR#1

BE29

DPAVDDR#2

BG25

DPAVSSR#1

BN27

DPAVSSR#2

BN25

DPAVSSR#3

BG27

DPAVSSR#4

BK26

DPAVSSR#5

BK28

DPAVSSR#6

BM24

DPAVSSR#7

BD30

DPBVDDR#1

BE30

DPBVDDR#2

BK32

DPBVSSR#1

BG31

DPBVSSR#2

BN29

DPBVSSR#3

BN31

DPBVSSR#4

BH32

DPBVSSR#5

BK30

DPBVSSR#6

BG29

DPBVSSR#7

BG37

T2XVDDC#1

BK38

T2XVDDC#2

BK44

T2VXDDC#3

BM44

T2XVDDC#4

BG35

T2XVSSR#1

BN41

T2XVSSR#2

BM34

T2XVSSR#3

BG39

T2XVSSR#4

BK36

T2XVSSR#5

BJ43

T2XVSSR#6

BN43

T2XVSSR#7

BK40

T2XVSSR#8

BN35

T2XVSSR#9

BN37

T2XVSSR#10

BN39

T2XVSSR#11

BG41

T2XVSSR#12

BH42

T2XVSSR#13

BE26

DPA_PVDD

BD26

DPA_PVSS

BE28

DPB_PVDD

BD28

DPB_PVSS

BC29

DP_CALR

BN33

T2PVDD

BL33

T2PVSS

BC40

AVDD

BB40

AVSSQ

BG45

VDD1DI

BE44

VSS1DI

RSET

BA40

RSET

BD39

A2VDD

BC39

A2VSSQ

BD43

VDD2DI

BE43

VSS2DI

R2SET

BB39

R2SET

BE39

A2VDDQ

BD33

DPLL_VDDC

BG33

DPLL_PVDD

BE33

DPLL_PVSS

AV37

BH44

BJ45

TP922milTP922mil

PLLTEST

XTALIN

XTALOUT

DDC3DATA_DP3_AUXN

DDC3CLK_DP3_AUXP

DDC4CLK_DP4_AUXP

DDC4DATA_DP4_AUXN

216-0732004-00

216-0732004-00

TX0P_DPA2P

TX0M_DPA2N

TX1P_DPA1P

TX1M_DPA1N

TX2P_DPA0P

TX2M_DPA0N

TXCAP_DPA3P

TXCAM_DPA3N

TX3P_DPB2P

TX3M_DPB2N

TX4P_DPB1P

TX4M_DPB1N

TX5P_DPB0P

TX5M_DPB0N

TXCBP_DPB3P

TXCBM_DPB3N

TXOUT_L0P

TXOUT_L0N

TXOUT_L1P

TXOUT_L1N

TXOUT_L2P

TXOUT_L2N

TXOUT_L3P

TXOUT_L3N

TXCLK_LP

TXCLK_LN

TXOUT_U0P

TXOUT_U0N

TXOUT_U1P

TXOUT_U1N

TXOUT_U2P

TXOUT_U2N

TXOUT_U3P

TXOUT_U3N

TXCLK_UP

TXCLK_UN

HPD1

HSYNC

VSYNC

H2SYNC

V2SYNC

COMP

DDC1CLK

DDC1DATA

DDC2CLK

DDC2DATA

BM26

DPA2P (10)

BL25

DPA2N (10)

BJ27

DPA1P (10)

BH26

DPA1N (10)

BM28

DPA0P (10)

BL27

DPA0N (10)

BJ25

DPA3P (10)

BK24

DPA3N (10)

BM30

DPB2P (10)

BL29

DPB2N (10)

BJ31

DPB1P (10)

BH30

DPB1N (10)

BM32

DPB0P (10)

BL31

DPB0N (10)

BJ29

DPB3P (10)

BH28

DPB3N (10)

BJ35

TXOUT_L0+ (10)

BH34

TXOUT_L0- (10)

BM36

TXOUT_L1+ (10)

BL35

TXOUT_L1- (10)

BJ37

TXOUT_L2+ (10)

BH36

TXOUT_L2- (10)

BM38

TXOUT_L3+ (10)

BL37

TXOUT_L3- (10)

BK34

BJ33

BM40

BL39

BJ41

BH40

BM42

BL41

BL43

BK42

BJ39

BH38

AW39

BC42

R

BC43

Rb

BD42

G

BE42

Gb

BE40

B

BD40

Bb

AY39

BA39

BC37

R2

BC36

R2b

BD37

G2

BE37

G2b

BE36

B2

BD36

B2b

AY37

AW37

BB36

BA37

Y

BB37

C

BC32

SCL

BB32

SDA

AU37

AU38

AY36

BA36

BB28

BC28

BB26

BC26

TXCLK_L+ (10)

TXCLK_L- (10)

TXOUT_U0+ (10)

TXOUT_U0- (10)

TXOUT_U1+ (10)

TXOUT_U1- (10)

TXOUT_U2+ (10)

TXOUT_U2- (10)

TXOUT_U3+ (10)

TXOUT_U3- (10)

TXCLK_U+ (10)

TXCLK_U- (10)

HPD1 (10)

VGA_RED

VGA_GRN

VGA_BLU

HSYNC (10,14)

H2SYNC (14)

V2SYNC (14)

DDC1CLK (10)

DDC1DAT (10)

DDC2CLK (10)

DDC2DAT (10)

DPA_AUXN (10)

DPA_AUXP (10)

DPB_AUXP (10)

DPB_AUXN (10)

VSYNC (10,14)

PLACE RGB TERMINATION

RESISTORS CLOSE TO ASIC

R26

R26

150R

150R

+3VRUN

R33

R33

R37

R37

4.7K

4.7K

4.7K

4.7K

VGA_RED (10)

VGA_GRN (10)

VGA_BLU (10)

R28

R28

R27

R27

150R

150R

150R

150R

CON1

I2C_CLK (10)

I2C_DAT (10)

CON1

37

36

20347

20347

GENERICD

35

35

34

34

33

33

32

32

31

31

30

30

29

29

28

28

27

27

26

26

25

25

24

24

23

23

22

22

21

21

20

20

19

19

18

18

GPIO2

17

17

16

16

15

15

14

14

13

13

12

12

11

11

10

10

9

9

8

8

7

7

6

6

5

5

4

4

3

3

2

2

TAB1

CLK_B

11TAB2

ALL DATA AND SIGNAL TRACES

HAVE TO MATCHING WITH CLK_B

WITH IN +/-5 MM

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

DE_A

CLK_A

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

DE_B

1.8V_REG

R11 221RR11 221R

R21 110RR21 110R

C12 100nFC12 100nF

TH_PWM(10)

R20 10KR20 10K

BLON_PWM(10)

TSVDD

TSVSS

FPVCC(10)

+3VRUN

R311KR31

1K

VREFG

R321KR32

1K

VDDR3

VDDR4_5

R465

R465

1K

1K

DNI

DNI

CTF

U1K

U1K

BG21

VREFG

AU29

VDDR3#1

AU30

VDDR3#2

AU32

VDDR3#3

AU33

VDDR3#4

BB24

VDDR5#1

BE24

VDDR5#2

BC24

VDDR5#3

BD24

VDDR5#4

BE25

VDDR4#1

BD25

VDDR4#2

BB25

VDDR4#3

BC25

VDDR4#4

AV36

TS_FDO

AV30

DPLUS

AW30

DMINUS

AU24

TSVDD

AU25

TSVSS

BA30

VARY_BL

BB30

DIGON

AU39

JMODE

R231KR23

1K

BG19

VSSD#1

BA22

VSSD#2

AV28

VSSD#3

BA29

VSSD#4

BA35

VSSD#5

AW36

VSSD#6

BA26

VSSD#7

AY30

VSSD#8

BM22

VSSD#9

BN19

VSSD#10

AU22

VSSD#11

BG43

VSSD#12

AU28

VSSD#13

AU26

VSSD#14

AR19

NC_GPIO_31

AP19

NC_GPIO_32

BA19

TEST_YCLK

AY19

TEST_MCLK

216-0732004-00

216-0732004-00

+3VRUN_BUS

C936

C936

100nF

100nF

2

D

1

C

DVPCNTL_MVP_0

DVPCNTL_MVP_1

GPIO_3_SMBDAT

GPIO_4_SMBCLK

GPIO_8_ROMSO

GPIO_9_ROMSI

GPIO_10_ROMSCK

GPIO_14_HPD2

GPIO_15_PWRCNTL_0

GPIO_16_SSIN

GPIO_17_THERMAL_INT

GPIO_18_HPD3

GPIO_20_PWRCNTL_1

GPIO_22_ROMCSB

GPIO_23_CLKREQB

GPIO_24_TRSTB

R485 1MR485 1M

C937

C937

100nF

100nF

U32

U32

8PR7

NC7SZ74K8X

NC7SZ74K8X

5

Q

Vcc

3

G4CL

Q

6

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPCLK

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

GPIO_0

GPIO_1

GPIO_2

GPIO_5

GPIO_6_TACH

GPIO_7

GPIO_11

GPIO_12

GPIO_13

GPIO_19_CTF

GPIO_21

GPIO_25_TDI

GPIO_26_TCK

GPIO_27_TMS

GPIO_28_TDO

GENERICA

GENERICB

GENERICC

GENERICD

GENERICE

GENERICF

GENERICG

GENERICH

VPCLK0

DVALID

PSYNC

VHAD_0

VHAD_1

VPHCTL

VIPCLK

VIP_0

VIP_1

VIP_2

VIP_3

VIP_4

VIP_5

VIP_6

VIP_7

BH20

BK20

BM20

BJ21

BL21

BN21

BH22

BK22

BG23

BJ23

BN23

BL23

BK18

BM18

BJ19

BL19

AW25

AY24

AV25

AY25

AY26

AW26

BA28

AV26

AY28

AW28

AY29

AW29

AW24

AV24

BA24

AV29

BH24

BD22

BA25

BE22

AY22

BC22

BB22

BA21

BB21

AW22

BE21

BD21

BD19

BB19

BC19

BE19

AY21

BH18

BN17

BG17

BC21

AW21

BL17

BM16

BH16

BK16

BJ17

BC35

BE32

BC33

BA33

BC30

BD35

BB29

BD32

AV35

AW35

AY35

AV33

AW33

AY33

AV32

AW32

AY32

BB33

BE35

AU36

AU35

BB35

BA32

+3VRUN_BUS

Q7

1

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

CLK_B

DE_B

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

DE_A

CLK_A

R292 0RR292 0R

R291 0RR291 0R

R256 0RR256 0R

CTF

JTAG122milJTAG122mil

JTAG222milJTAG222mil

JTAG322milJTAG322mil

JTAG422milJTAG422mil

JTAG522milJTAG522mil

GENERICD

R200

R200

100K

100K

32

2N7002EQ72N7002E

GPIO0 (14)

GPIO1 (14)

GPIO2 (14)

PBAT_SMBDAT (10)

PBAT_SMBCLK (10)

MEM_PP (12)

OPT_BL_ENA (10)

SCLK (14)

GPIO11 (14)

GPIO12 (14)

GPIO13 (14)

HPD2 (10)

GPIO16_SS (14)

HPD3 (10)

GPIO21 (14)

CLKREQB (10)

GENERICA (10)

GENERICB (10)

GENERICC (14)

VGA/TV# (10)

HDTV#/TV (10)

VID_0 (14)

VID_1 (14)

VID_2 (14)

VID_3 (14)

MEM_ID0 (14)

MEM_ID1 (14)

VID_6 (14)

MEM_ID2 (14)

VID1 (11)

DVALID (14)

PSYNC (14)

VHAD0 (14)

VID2 (11)

VID3 (11)

CTFb (10)

R25

R25

10K

10K

+3VRUN

10K

10K

R196

R196

R464 10K

R464 10K

DNI

DNI

100K

100K

R169

R169

SCS# (14)

+3VRUN

DNI

PWR_LEVEL (10,11)

GPIO8 (14)

SOUT (14)

SIN (14)

GPIO9 (14)

+3VRUN

OTEMP# (10)

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

M98-L 1GB DDR3 MXM 3.0 CF

M98-L 1GB DDR3 MXM 3.0 CF

5

4

3

2

M98-L 1GB DDR3 MXM 3.0 CF

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Friday, May 16, 2008

Friday, May 16, 2008

Friday, May 16, 2008

Sheet

Sheet

Sheet

of

2 15

of

2 15

of

2 15

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

0

0

0

105-B735xx-00A

105-B735xx-00A

105-B735xx-00A

www.vinafix.vn

Page 3

5

4

3

2

1

RASB0#

RASB1#

CASB0#

CASB1#

WEB0#

WEB1#

CKEB0

CKEB1

CSB0_0#

CSB1_0#

CSB0_1#

CSB1_1#

CLKB0

CLKB0#

CLKB1

CLKB1#

WDQSB[7..0]

RDQSB[7..0]

DQMB#[7..0]

MDB[63..0]

MAB[11..0]

B_BA0

B_BA1

VDD_MEM

C19

C19

100nF

100nF

VDD_MEM

R48

R48

40.2R

40.2R

1%

PLACE MVREF CAPS

AS CLOSE TO ASIC AS POSSIBLE

R49

R49

C21

C21

100R

100R

100nF

100nF

1%

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

DQMB#0

DQMB#1

DQMB#2

DQMB#3

RDQSB0

RDQSB1

RDQSB2

RDQSB3

WDQSB0

WDQSB1

WDQSB2

WDQSB3

WEB0#

CSB0_0#

CSB0_1# CSB1_1#

CASB0#

RASB0#

CKEB0

CLKB0

CLKB0# CLKB1#

R43 243RR43 243R

R44 243RR44 243R

WDQSB[7..0](7)

RDQSB[7..0](7)

DQMB#[7..0](7)

MDB[63..0](7)

MAB[11..0](7)

VDD_MEM

R39

R39

40.2R

40.2R

1%

R42

R42

100R

100R

1%

RASB0#(7)

RASB1#(7)

CASB0#(7)

CASB1#(7)

WEB0#(7)

WEB1#(7)

CKEB0(7)

CKEB1(7)

CSB0_0#(7)

CSB1_0#(7)

CSB0_1#(7)

CLKB0(7)

CLKB0#(7)

CLKB1(7)

CLKB1#(7)

B_BA0(7)

B_BA1(7)

RASA0#(6)

RASA1#(6)

CASA0#(6)

D D

CASA1#(6)

WEA0#(6)

WEA1#(6)

CKEA0(6)

CKEA1(6)

CSA0_0#(6)

CSA1_0#(6)

CSA0_1#(6) CSB1_1#(7)

CSA1_1#(6)

CLKA0(6)

CLKA0#(6)

CLKA1(6)

CLKA1#(6)

WDQSA[7..0](6)

RDQSA[7..0](6)

DQMA#[7..0](6)

MDA[63..0](6)

MAA[11..0](6)

A_BA0(6)

A_BA1(6) B_BA2(7)

A_BA2(6)

C C

VDD_MEM

B B

R38

R38

40.2R

40.2R

1%

R40

R40

100R

100R

1%

RASA0#

RASA1#

CASA0#

CASA1#

WEA0#

WEA1#

CKEA0

CKEA1

CSA0_0#

CSA1_0#

CSA0_1#

CSA1_1#

CLKA0

CLKA0#

CLKA1

CLKA1#

WDQSA[7..0]

RDQSA[7..0]

DQMA#[7..0]

MDA[63..0]

MAA[11..0]

A_BA0

A_BA1 B_BA2

A_BA2

VDD_MEM

C18

C18

100nF

100nF

VDD_MEM

R47

R47

40.2R

40.2R

1%

PLACE MVREF CAPS

AS CLOSE TO ASIC AS POSSIBLE

R50

R50

C20

C20

100R

100R

100nF

100nF

1%

MEM_RST(6,7,8,9)

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

DQMA#0

DQMA#1 DQMA#5

DQMA#2

DQMA#3

RDQSA0

RDQSA1

RDQSA2

WDQSA0

WDQSA1

WDQSA2

WEA0#

CSA0_0#

CSA0_1# CSA1_1#

CASA0#

RASA0#

CKEA0

CLKA0

CLKA0#

R41 243RR41 243R

R45 243RR45 243R

R46 10KR46 10K

C469 1uF_6.3VC469 1uF_6.3V

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

AW19

V40

R42

V41

R41

V42

V43

U45

P44

M48

M50

L53

L51

P48

P50

P52

N53

L49

J51

K50

K48

G52

H48

F48

C51

C43

F44

E43

D44

A46

D46

F46

B47

L44

M45

P40

M44

R43

P43

J43

K44

M42

K45

R51

R49

E50

D49

U44

N49

J49

C45

U43

N51

H50

E45

U38

R39

R40

J44

P45

L43

U40

U39

U33

U32

T32

P36

U1C

U1C

DQA0_0

DQA0_1

DQA0_2

DQA0_3

DQA0_4

DQA0_5

DQA0_6

DQA0_7

DQA0_8

DQA0_9

DQA0_10

DQA0_11

DQA0_12

DQA0_13

DQA0_14

DQA0_15

DQA0_16

DQA0_17

DQA0_18

DQA0_19

DQA0_20

DQA0_21

DQA0_22

DQA0_23

DQA0_24

DQA0_25

DQA0_26

DQA0_27

DQA0_28

DQA0_29

DQA0_30

DQA0_31

MAA0_0

MAA0_1

MAA0_2

MAA0_3

MAA0_4

MAA0_5

MAA0_6

MAA0_7

MAA0_8

ADBIA0

WCKA0_0

WCKA0B_0

WCKA0_1

WCKA0B_1

EDCA0_0

EDCA0_1

EDCA0_2

EDCA0_3

DDBIA0_0

DDBIA0_1

DDBIA0_2

DDBIA0_3

WEA0B

CSA0B_0

CSA0B_1

CASA0B

RASA0B

CKEA0

CLKA0

CLKA0B

MVREFAS

MVREFAD

MEM_CALRPA

MEM_CALRNA

DRAM_RST

216-0732004-00

216-0732004-00

DQA1_0

DQA1_1

DQA1_2

DQA1_3

DQA1_4

DQA1_5

DQA1_6

DQA1_7

DQA1_8

DQA1_9

DQA1_10

DQA1_11

DQA1_12

DQA1_13

DQA1_14

DQA1_15

DQA1_16

DQA1_17

DQA1_18

DQA1_19

DQA1_20

DQA1_21

DQA1_22

DQA1_23

DQA1_24

DQA1_25

DQA1_26

DQA1_27

DQA1_28

DQA1_29

DQA1_30

DQA1_31

MAA1_0

MAA1_1

MAA1_2

MAA1_3

MAA1_4

MAA1_5

MAA1_6

MAA1_7

MAA1_8

ADBIA1

WCKA1_0

WCKA1B_0

WCKA1_1

WCKA1B_1

EDCA1_0

EDCA1_1

EDCA1_2

EDCA1_3

DDBIA1_0

DDBIA1_1

DDBIA1_2

DDBIA1_3

WEA1B

CSA1B_0

CSA1B_1

CASA1B

RASA1B

CKEA1

CLKA1

CLKA1B

MPVDD#0

MPVDD#1

MPVDD#2

MDA32

D30

MDA33

A31

MDA34

F30

MDA35

E29

MDA36

D32

MDA37

C33

MDA38

E33

MDA39

F32

MDA40

J35

MDA41

L32

MDA42

L35

MDA43

K35

MDA44

M30

MDA45

L33

MDA46

L30

MDA47

J29

MDA48

F34

MDA49

A35

MDA50

E35

MDA51

C35

MDA52

E37

MDA53

C37

MDA54

B38

MDA55

A37

MDA56

F42

MDA57

E41

MDA58

A43

MDA59

D42

MDA60

D40

MDA61

E39

MDA62

C39

MDA63

F40

MAA8

J42

MAA9

K40

MAA10

L37

MAA11

J40

J37

A_BA2

K37

A_BA0

M39

A_BA1

M40

K42

L42

DQMA#4

B34

D34

DQMA#6

D38

DQMA#7

F38

RDQSA4

C31

RDQSA5

J32

RDQSA6

D36

RDQSA7RDQSA3

C41

WDQSA4

E31

WDQSA5

K32

WDQSA6

F36

WDQSA7WDQSA3

A41

WEA1#

N36

CSA1_0#

P37

R37

CASA1#

N39

RASA1#

L39

CKEA1

T37

CLKA1

M36

CLKA1#

L36

J10

K10

K9

MEM_PLL

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

U1D

U1D

P35

P32

T35

P33

N30

P30

R32

R35

M25

M28

N25

T26

K26

J26

R29

N28

A29

C29

F28

D28

A27

D26

E25

F26

E21

D22

C21

A21

C23

E23

F24

D24

J24

L24

L25

P24

L28

P25

N22

P22

L22

M22

K29

L29

C25

A25

N33

L26

E27

F22

M33

M26

C27

A23

T29

P26

R26

R24

K24

T24

P29

P28

T17

U18

T21

R21

216-0732004-00

216-0732004-00

DQB0_0

DQB0_1

DQB0_2

DQB0_3

DQB0_4

DQB0_5

DQB0_6

DQB0_7

DQB0_8

DQB0_9

DQB0_10

DQB0_11

DQB0_12

DQB0_13

DQB0_14

DQB0_15

DQB0_16

DQB0_17

DQB0_18

DQB0_19

DQB0_20

DQB0_21

DQB0_22

DQB0_23

DQB0_24

DQB0_25

DQB0_26

DQB0_27

DQB0_28

DQB0_29

DQB0_30

DQB0_31

MAB0_0

MAB0_1

MAB0_2

MAB0_3

MAB0_4

MAB0_5

MAB0_6

MAB0_7

MAB0_8

ADBIB0

WCKB0_0

WCKB0B_0

WCKB0_1

WCKB0B_1

EDCB0_0

EDCB0_1

EDCB0_2

EDCB0_3

DDBIB0_0

DDBIB0_1

DDBIB0_2

DDBIB0_3

WEB0B

CSB0B_0

CSB0B_1

CASB0B

RASB0B

CKEB0

CLKB0

CLKB0B

MVREFBS

MVREFBD

MEM_CALRPB

MEM_CALRNB

DQB1_0

DQB1_1

DQB1_2

DQB1_3

DQB1_4

DQB1_5

DQB1_6

DQB1_7

DQB1_8

DQB1_9

DQB1_10

DQB1_11

DQB1_12

DQB1_13

DQB1_14

DQB1_15

DQB1_16

DQB1_17

DQB1_18

DQB1_19

DQB1_20

DQB1_21

DQB1_22

DQB1_23

DQB1_24

DQB1_25

DQB1_26

DQB1_27

DQB1_28

DQB1_29

DQB1_30

DQB1_31

MAB1_0

MAB1_1

MAB1_2

MAB1_3

MAB1_4

MAB1_5

MAB1_6

MAB1_7

MAB1_8

ADBIB1

WCKB1_0

WCKB1B_0

WCKB1_1

WCKB1B_1

EDCB1_0

EDCB1_1

EDCB1_2

EDCB1_3

DDBIB1_0

DDBIB1_1

DDBIB1_2

DDBIB1_3

WEB1B

CSB1B_0

CSB1B_1

CASB1B

RASB1B

CKEB1

CLKB1

CLKB1B

MDB32

C3

MDB33

D5

MDB34

B7

MDB35

D8

MDB36

E9

MDB37

F10

MDB38

D10

MDB39

A11

MDB40

K18

MDB41

L18

MDB42

L17

MDB43

M17

MDB44

M12

MDB45

L12

MDB46

K12

MDB47

J12

MDB48

F12

MDB49

D12

MDB50

C13

MDB51MDB19

A13

MDB52

F14

MDB53

C15

MDB54

A15

MDB55

E15

MDB59

F20

MDB57

C17

MDB58

D20

MDB56

C19

MDB60

E19

MDB61

D18

MDB62

E17

MDB63MDB31

A17

MAB8

J18

MAB9

M19

MAB10

P18

MAB11

T18

N17

B_BA2

R18

B_BA0

N19

B_BA1

P21

L19

J21

DQMB#4

C11

DQMB#5

E11

DQMB#6

D16

DQMB#7

F16

RDQSB4

F8

RDQSB5

K15

RDQSB6

E13

RDQSB7

A19

WDQSB4

C9

WDQSB5

J15

WDQSB6

D14

WDQSB7

F18

WEB1#

P15

CSB1_0#

N15

L14

CASB1#

K21

RASB1#

P19

CKEB1

L21

CLKB1

N14

M14

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

M98-L 1GB DDR3 MXM 3.0 CF

M98-L 1GB DDR3 MXM 3.0 CF

5

4

3

M98-L 1GB DDR3 MXM 3.0 CF

2

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markhaml, Ontario

Markhaml, Ontario

Markhaml, Ontario

Wednesday, May 14, 2008

Wednesday, May 14, 2008

Wednesday, May 14, 2008

Sheet

Sheet

Sheet

of

3 15

of

3 15

of

3 15

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

0

0

0

105-B735xx-00A

105-B735xx-00A

105-B735xx-00A

www.vinafix.vn

Page 4

5

RASC0#(8)

RASC1#(8)

CASC0#(8)

D D

CASC1#(8)

WEC0#(8)

WEC1#(8)

CKEC0(8)

CKEC1(8)

CSC0_0#(8)

CSC1_0#(8)

CSC0_1#(8)

CSC1_1#(8)

CLKC0(8)

CLKC0#(8)

CLKC1(8)

CLKC1#(8)

WDQSC[7..0](8)

RDQSC[7..0](8)

DQMC#[7..0](8)

MDC[63..0](8)

MAC[11..0](8)

C_BA0(8)

C_BA1(8)

C C

C_BA2(8)

RASC0#

RASC1#

CASC0#

CASC1#

WEC0#

WEC1#

CKEC0

CKEC1

CSC0_0#

CSC1_0#

CSC0_1#

CSC1_1#

CLKC0

CLKC0#

CLKC1

CLKC1#

WDQSC[7..0]

RDQSC[7..0]

DQMC#[7..0]

MDC[63..0]

MAC[11..0]

C_BA0

C_BA1

C_BA2

DQMC#0

DQMC#1 DQMC#5

DQMC#2

DQMC#3 DQMC#7

RDQSC0

RDQSC1

RDQSC2

RDQSC3

WDQSC0

WDQSC1

WDQSC2

WEC0#

CSC0_1# CSC1_1# CSD0_1# CSD1_1#

CASC0#

VDD_MEM

B B

R51

R51

40.2R

40.2R

R53

R53

100R

100R

1%

C22

100nF

100nF

VDD_MEM

RASC0#

CKEC0

CLKC0

CLKC0#

R55 243RR55 243R

R54 243RR54 243R

VDD_MEM

R59

R59

40.2R

40.2R

1%

R61

R61

C24

C24

100R

100R

100nF

100nF

1%

4

U1E

U1E

MDC0

E4

DQC0_0

H4

DQC0_1

G2

DQC0_2

F6

DQC0_3

J5

DQC0_4

K6

DQC0_5

K4

DQC0_6

L1

DQC0_7

V10

DQC0_8

V11

DQC0_9

U11

DQC0_10

U12

DQC0_11

L11

DQC0_12

M11

DQC0_13

M10

DQC0_14

M9

DQC0_15

M6

DQC0_16

M4

DQC0_17

N3

DQC0_18

N1

DQC0_19

P6

DQC0_20

R3

DQC0_21

R1

DQC0_22

R5

DQC0_23

Y6

DQC0_24

W3

DQC0_25

Y4

DQC0_26

W5

DQC0_27

V4

DQC0_28

U3

DQC0_29

U5

DQC0_30

U1

DQC0_31

V9

MAC0_0

W12

MAC0_1

V14

MAC0_2

V16

MAC0_3

U13

MAC0_4

V15

MAC0_5

W13

MAC0_6

AA14

MAC0_7

W11

MAC0_8

AA9

ADBIC0

L3

WCKC0_0

L5

WCKC0B_0

T4

WCKC0_1

T6

WCKC0B_1

H6

EDCC0_0

R10

EDCC0_1

N5

EDCC0_2

W1

EDCC0_3

J3

DDBIC0_0

R9

DDBIC0_1

P4

DDBIC0_2

V6

DDBIC0_3

R14

WEC0B

R13

CSC0B_0

P11

CSC0B_1

AA10

CASC0B

W14

RASC0B

AA11

CKEC0

P13

CLKC0

P12

CLKC0B

U16

MVREFCS

V17

MVREFCD

AA16

MEM_CALRPC

AA15

MEM_CALRNC

216-0732004-00

216-0732004-00

PLACE MVREF CAPS

AS CLOSE TO ASIC AS POSSIBLE

MAC0

MAC1

MAC2

MAC3

MAC4

MAC5

MAC6

MAC7

MDC1

MDC2

MDC3

MDC4

MDC5

MDC6

MDC7

MDC8

MDC9

MDC10

MDC11

MDC12

MDC13

MDC14

MDC15

MDC16

MDC17

MDC18

MDC19

MDC20

MDC21

MDC22

MDC23

MDC24

MDC25

MDC26

MDC27

MDC28

MDC29

MDC30

MDC31

DQC1_0

DQC1_1

DQC1_2

DQC1_3

DQC1_4

DQC1_5

DQC1_6

DQC1_7

DQC1_8

DQC1_9

DQC1_10

DQC1_11

DQC1_12

DQC1_13

DQC1_14

DQC1_15

DQC1_16

DQC1_17

DQC1_18

DQC1_19

DQC1_20

DQC1_21

DQC1_22

DQC1_23

DQC1_24

DQC1_25

DQC1_26

DQC1_27

DQC1_28

DQC1_29

DQC1_30

DQC1_31

MAC1_0

MAC1_1

MAC1_2

MAC1_3

MAC1_4

MAC1_5

MAC1_6

MAC1_7

MAC1_8

ADBIC1

WCKC1_0

WCKC1B_0

WCKC1_1

WCKC1B_1

EDCC1_0

EDCC1_1

EDCC1_2

EDCC1_3

DDBIC1_0

DDBIC1_1

DDBIC1_2

DDBIC1_3

WEC1B

CSC1B_0

CSC1B_1

CASC1B

RASC1B

CKEC1

CLKC1

CLKC1B

AR16

AN14

AR14

AR15

AM15

AM14

AK13

AK14

AJ15

AH12

AH13

AF10

AF9

AF16

AE13

AE12

AJ3

AJ1

AH4

AH6

AG1

AF4

AE5

AF6

AA5

AB4

AA3

AA1

AC5

AD6

AD4

AC3

AD9

AD11

AE11

AD14

AH11

AE14

AB13

AB14

AB11

AB12

AJ10

AJ11

AE3

AE1

AN13

AF11

AG5

AB6

AN12

AF12

AG3

AC1

AJ16

AF14

AF15

AD15

AD10

AD16

AJ14

AH14

MDC32

MDC33

MDC34

MDC35

MDC36

MDC37

MDC38

MDC39

MDC40

MDC41

MDC42

MDC43

MDC44

MDC45

MDC46

MDC47

MDC48

MDC49

MDC50

MDC51

MDC52

MDC53

MDC54

MDC55

MDC56

MDC57

MDC58

MDC59

MDC60

MDC61

MDC62

MDC63

MAC8

MAC9

MAC10

MAC11

C_BA2

C_BA0

C_BA1

DQMC#4

DQMC#6

RDQSC4

RDQSC5

RDQSC6

RDQSC7

WDQSC4

WDQSC5

WDQSC6

WDQSC7WDQSC3

WEC1#

CSC1_0#CSC0_0#

CASC1#

RASC1#

CKEC1

CLKC1

CLKC1#

3

WDQSD[7..0](9)

RDQSD[7..0](9)

VDD_MEM

R52

R52

40.2R

40.2R

R56

R56

100R

100R

1%

2

U1F

AR11

AK12

AR10

AN11

AK11

AM11

AY10

AU11

AU10

AW12

AY12

BB10

BB11

AM10

AT13

AU14

AU15

AW13

AW11

AU16

AT12

AT11

AM17

AN17

AM16

AT14

AJ5

AK6

AK4

AL1

AM6

AM4

AN5

AN3

AR9

AJ9

AR3

AR1

AP6

AR5

AU1

AU3

AU5

AV2

BB6

BA5

BC1

BB4

AY6

AW5

AW3

AY4

BB9

AY9

AU9

AP2

AP4

AV4

AV6

AL3

AM9

AT4

BA3

AL5

AT6

BA1

U1F

DQD0_0

DQD0_1

DQD0_2

DQD0_3

DQD0_4

DQD0_5

DQD0_6

DQD0_7

DQD0_8

DQD0_9

DQD0_10

DQD0_11

DQD0_12

DQD0_13

DQD0_14

DQD0_15

DQD0_16

DQD0_17

DQD0_18

DQD0_19

DQD0_20

DQD0_21

DQD0_22

DQD0_23

DQD0_24

DQD0_25

DQD0_26

DQD0_27

DQD0_28

DQD0_29

DQD0_30

DQD0_31

MAD0_0

MAD0_1

MAD0_2

MAD0_3

MAD0_4

MAD0_5

MAD0_6

MAD0_7

MAD0_8

ADBID0

WCKD0_0

WCKD0B_0

WCKD0_1

WCKD0B_1

EDCD0_0

EDCD0_1

EDCD0_2

EDCD0_3

DDBID0_0

DDBID0_1

DDBID0_2

DDBID0_3

WED0B

CSD0B_0

CSD0B_1

CASD0B

RASD0B

CKED0

CLKD0

CLKD0B

MVREFDS

MVREFDD

MEM_CALRPD

MEM_CALRND

DQD1_0

DQD1_1

DQD1_2

DQD1_3

DQD1_4

DQD1_5

DQD1_6

DQD1_7

DQD1_8

DQD1_9

DQD1_10

DQD1_11

DQD1_12

DQD1_13

DQD1_14

DQD1_15

DQD1_16

DQD1_17

DQD1_18

DQD1_19

DQD1_20

DQD1_21

DQD1_22

DQD1_23

DQD1_24

DQD1_25

DQD1_26

DQD1_27

DQD1_28

DQD1_29

DQD1_30

DQD1_31

MAD1_0

MAD1_1

MAD1_2

MAD1_3

MAD1_4

MAD1_5

MAD1_6

MAD1_7

MAD1_8

ADBID1

WCKD1_0

WCKD1B_0

WCKD1_1

WCKD1B_1

EDCD1_0

EDCD1_1

EDCD1_2

EDCD1_3

DDBID1_0

DDBID1_1

DDBID1_2

DDBID1_3

WED1B

CSD1B_0

CSD1B_1

CASD1B

RASD1B

CKED1

CLKD1

CLKD1B

BC18

BB18

BA18

AY18

BE17

BA15

BB15

BD14

BH12

BK12

BN11

BL11

BH14

BK14

BM14

BN13

BJ11

BK10

BM7

BL9

BH10

BH8

BH6

BL3

BC5

BD4

BC3

BF1

BD6

BF6

BF4

BG2

BD11

BE12

AY14

BD12

BC15

BC14

BC9

BD10

BC11

BE10

BL15

BJ15

BK5

BJ4

BD17

BJ13

BJ9

BE3

BC17

BL13

BK8

BE5

AV17

AW15

AY15

BD9

BE14

BB12

AY17

AW17

MDD32

MDD33

MDD34

MDD35

MDD36

MDD37

MDD38

MDD39

MDD40

MDD41

MDD42

MDD43

MDD44

MDD45

MDD46

MDD47

MDD48

MDD49

MDD55

MDD51MDD19

MDD52

MDD53

MDD50

MDD54

MDD56

MDD57

MDD58

MDD59

MDD60

MDD61

MDD62

MDD63MDD31

MAD8

MAD9

MAD10

MAD11

D_BA2

D_BA0

D_BA1

DQMD#4

DQMD#5

DQMD#6

DQMD#7

RDQSD4

RDQSD5

RDQSD6

RDQSD7

WDQSD4

WDQSD5

WDQSD6

WDQSD7WDQSD3

WED1#

CSD1_0#

CASD1#

RASD1#

CKED1

CLKD1CLKD0

CLKD1#

RASD0#(9)

RASD1#(9)

CASD0#(9)

CASD1#(9)

WED0#(9)

WED1#(9)

CKED0(9)

CKED1(9)

CSD0_0#(9)

CSD1_0#(9)

CSD0_1#(9)

CSD1_1#(9)

CLKD0(9)

CLKD0#(9)

CLKD1(9)

CLKD1#(9)

RASD0#

RASD1#

CASD0#

CASD1#

WED0#

WED1#

CKED0

CKED1

CSD0_0#

CSD1_0#

CSD0_1#

CSD1_1#

CLKD0

CLKD0#

CLKD1

CLKD1#

WDQSD[7..0]

RDQSD[7..0]

DQMD#[7..0](9)

MDD[63..0](9)

MAD[11..0](9)

D_BA0(9)

D_BA1(9)

D_BA2(9)

DQMD#[7..0]

MDD[63..0]

MAD[11..0]

D_BA0

D_BA1

D_BA2

MAD0

MAD1

MAD2

MAD3

MAD4

MAD5

MAD6

MAD7

DQMD#0

DQMD#1

DQMD#2

DQMD#3

RDQSD0

RDQSD1

RDQSD2

RDQSD3

WDQSD0

WDQSD1

WDQSD2

WED0#

CSD0_0#

CASD0#

RASD0#

MDD0

MDD1

MDD2

MDD3

MDD4

MDD5

MDD6

MDD7

MDD8

MDD9

MDD10

MDD11

MDD12

MDD13

MDD14

MDD15

MDD16

MDD17

MDD18

MDD20

MDD21

MDD22

MDD23

MDD24

MDD25

MDD26

MDD27

MDD28

MDD29

MDD30

CKED0

CLKD0#

C23

100nF

100nFC22

VDD_MEM

R58 243RR58 243RC23

R57 243RR57 243R

1

VDD_MEM

216-0732004-00

R60

R60

40.2R

40.2R

1%

R62

R62

100R

100R

1%

C25

C25

100nF

100nF

216-0732004-00

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

M98-L 1GB DDR3 MXM 3.0 CF

M98-L 1GB DDR3 MXM 3.0 CF

5

4

3

M98-L 1GB DDR3 MXM 3.0 CF

2

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markhaml, Ontario

Markhaml, Ontario

Markhaml, Ontario

Wednesday, May 14, 2008

Wednesday, May 14, 2008

Wednesday, May 14, 2008

Sheet

Sheet

Sheet

of

4 15

of

4 15

of

4 15

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

0

0

0

105-B735xx-00A

105-B735xx-00A

105-B735xx-00A

www.vinafix.vn

Page 5

5

VDD_MEM

C56

C56

C57

C57

2.2UF_2.5V

2.2UF_2.5V

2.2UF_2.5V

C60

C60

2.2UF_2.5V

2.2UF_2.5V

C37

2.2UF_2.5V

2.2UF_2.5V

C79

C79

2.2UF_2.5V

2.2UF_2.5V

C90

C90

2.2UF_2.5V

2.2UF_2.5V

C100

C100

2.2UF_2.5V

2.2UF_2.5V

C114

C114

2.2UF_2.5V

2.2UF_2.5V

C123

C123

2.2UF_2.5V

2.2UF_2.5V

C134

C134

2.2UF_2.5V

2.2UF_2.5V

C140

C140

2.2UF_2.5V

2.2UF_2.5V

2.2UF_2.5V

C61

2.2UF_2.5V

2.2UF_2.5V

C67

C67

2.2UF_2.5V

2.2UF_2.5V

C80

C80

2.2UF_2.5V

2.2UF_2.5V

C91

C91

2.2UF_2.5V

2.2UF_2.5V

C105

C105

2.2UF_2.5V

2.2UF_2.5V

C54

C54

2.2UF_2.5V

2.2UF_2.5V

C124

C124

2.2UF_2.5V

2.2UF_2.5V

C135

C135

2.2UF_2.5V

2.2UF_2.5V

C141

C141

2.2UF_2.5V

2.2UF_2.5V

D D

C C

B B

C33

C33

2.2UF_2.5V

2.2UF_2.5V

C62

C62

2.2UF_2.5V

2.2UF_2.5V

C38

C38

2.2UF_2.5V

2.2UF_2.5V

C39

C39

2.2UF_2.5V

2.2UF_2.5V

C92

C92

2.2UF_2.5V

2.2UF_2.5V

C48

C48

2.2UF_2.5V

2.2UF_2.5V

C115

C115

2.2UF_2.5V

2.2UF_2.5V

C125

C125

2.2UF_2.5V

2.2UF_2.5V

C136

C136

2.2UF_2.5V

2.2UF_2.5V

C142

C142

2.2UF_2.5V

2.2UF_2.5V

C26

C26

2.2UF_2.5V

2.2UF_2.5V

C34

C34

2.2UF_2.5V

2.2UF_2.5V

C55

C55

2.2UF_2.5V

2.2UF_2.5V

C81

C81

2.2UF_2.5V

2.2UF_2.5V

C30

C30

2.2UF_2.5V

2.2UF_2.5V

C106

C106

2.2UF_2.5V

2.2UF_2.5V

C116

C116

2.2UF_2.5V

2.2UF_2.5V

C126

C126

2.2UF_2.5V

2.2UF_2.5V

C137

C137

2.2UF_2.5V

2.2UF_2.5V

C143

C143

2.2UF_2.5V

2.2UF_2.5V

C58

C58

2.2UF_2.5V

2.2UF_2.5V

C35

C35

2.2UF_2.5V

2.2UF_2.5V

C68

C68

2.2UF_2.5V

2.2UF_2.5V

C40

C40

2.2UF_2.5V

2.2UF_2.5V

C43

C43

2.2UF_2.5V

2.2UF_2.5V

C107

C107

2.2UF_2.5V

2.2UF_2.5V

C32

C32

2.2UF_2.5V

2.2UF_2.5V

C127

C127

2.2UF_2.5V

2.2UF_2.5V

C138

C138

2.2UF_2.5V

2.2UF_2.5V

C144

C144

2.2UF_2.5V

2.2UF_2.5V

C59

C59

2.2UF_2.5V

2.2UF_2.5V

C63

C63

10uF_6.3V

10uF_6.3V

C69

C69

10uF_6.3V

10uF_6.3V

C82

C82

10uF_6.3V

10uF_6.3V

C93

C93

10uF_6.3V

10uF_6.3V

C49

C49

2.2UF_2.5V

2.2UF_2.5V

C117

C117

10uF_6.3V

10uF_6.3V

C128

C128

10uF_6.3V

10uF_6.3V

C139

C139

10uF_6.3V

10uF_6.3V

C145

C145

10uF_6.3V

10uF_6.3V

AA12

AD12

AE15

AB15

AH15

AK15

AM12

AN15

AR12

AT15

AU12

AW14

BB14

BE18

BC10

AW18

BE11

BE15

BB17

AB9

AE9

AH9

AJ12

AK9

AN9

AT9

AW9

K11

J14

J17

J30

J33

J36

J19

J22

J25

J28

J39

K43

L45

L10

L15

M18

M21

M24

R22

M29

M32

M35

M37

P14

P17

R19

R25

R28

R30

R33

R36

P39

P42

R11

R45

U14

U42

V12

V39

V45

W9

W15

P9

U9

U1G

U1G

VDDR1#1

VDDR1#2

VDDR1#3

VDDR1#4

VDDR1#5

VDDR1#6

VDDR1#7

VDDR1#8

VDDR1#9

VDDR1#10

VDDR1#11

VDDR1#12

VDDR1#13

VDDR1#14

VDDR1#15

VDDR1#16

VDDR1#17

VDDR1#18

VDDR1#19

VDDR1#20

VDDR1#21

VDDR1#22

VDDR1#23

VDDR1#24

VDDR1#25

VDDR1#26

VDDR1#27

VDDR1#28

VDDR1#29

VDDR1#30

VDDR1#31

VDDR1#32

VDDR1#33

VDDR1#34

VDDR1#35

VDDR1#36

VDDR1#37

VDDR1#38

VDDR1#39

VDDR1#40

VDDR1#41

VDDR1#42

VDDR1#43

VDDR1#44

VDDR1#45

VDDR1#46

VDDR1#47

VDDR1#48

VDDR1#49

VDDR1#50

VDDR1#51

VDDR1#52

VDDR1#53

VDDR1#54

VDDR1#55

VDDR1#56

VDDR1#57

VDDR1#58

VDDR1#59

VDDR1#60

VDDR1#61

VDDR1#62

VDDR1#63

VDDR1#64

VDDR1#65

VDDR1#66

VDDR1#67

VDDR1#68

VDDR1#69

VDDR1#70

VDDR1#71

216-0732004-00

216-0732004-00

4

VDDCI#1

VDDCI#2

VDDCI#3

VDDCI#4

VDDCI#5

VDDCI#6

VDDCI#7

VDDCI#8

VDDCI#9

VDDCI#10

VDDCI#11

VDDCI#12

VDDCI#13

VDDCI#14

VDDCI#15

VDDCI#16

VDDCI#17

VDDCI#18

VDDCI#19

VDDCI#20

VDDCI#21

VDDCI#22

VDDCI#23

VDDCI#24

VDDCI#25

VDDCI#26

VDDCI#27

VDDCI#28

VDDCI#29

VDDCI#30

VDDCT#1

VDDCT#2

VDDCT#3

VDDCT#4

SPVDD

SPVSS

3

VCORE_RTN(11)

VCORE_SEN(11)

VDD_CORE

C28

C28

C36

C27

C27

C64

C64

10nF

10nF

100nF_6.3V

VDD_CORE

AA17

AB17

AD17

AE17

AF17

AH17

AJ17

AK17

AR17

AT17

AU17

AU18

AU19

U17

U19

U21

U22

U24

U25

U26

U28

U29

U30

U35

U36

U37

V37

W37

W17

AA37

AV22

AU21

AV21

AV19

AT37

AT38

C70

C70

2.2UF_2.5V

2.2UF_2.5V

C83

C83

100nF_6.3V

100nF_6.3V

C47

C47

2.2UF_2.5V

2.2UF_2.5V

C110

C110

100nF_6.3V

100nF_6.3V C52

VDD_CT

SPVDD

GND_SPVSS

C71

C71

2.2UF_2.5V

2.2UF_2.5V

C84

C84

100nF_6.3V

100nF_6.3V

C97

C97

2.2UF_2.5V

2.2UF_2.5V

C111

C111

100nF_6.3V

100nF_6.3V

C72

C72

2.2UF_2.5V

2.2UF_2.5V

C85

C85

10nF

10nF

C98

C98

2.2UF_2.5V

2.2UF_2.5V

C50

C50

10nF

10nF

C73

C73

10uF_6.3V

10uF_6.3V

C99

C99

10uF_6.3V

10uF_6.3V

C29

C29

1nF

1nFC37

C41

C41

1nF

1nF

C44

C44

2.2UF_2.5V

2.2UF_2.5V

C101

C101

2.2UF_2.5V

2.2UF_2.5V

C51

C51

100nF_6.3V

100nF_6.3V

C118

C118

10nF

10nF

C129

C129

2.2UF_2.5V

2.2UF_2.5V

C146

C146

10uF_6.3V

10uF_6.3V

C151

C151

10uF_6.3V

10uF_6.3V

100nF_6.3V

C74

C74

1nF

1nF

C86

C86

2.2UF_2.5V

2.2UF_2.5V

C94

C94

2.2UF_2.5V

2.2UF_2.5V

C102

C102

2.2UF_2.5V

2.2UF_2.5V

C52

10nF

10nF

C119

C119

10nF

10nF

C130

C130

100nF_6.3V

100nF_6.3V

C147

C147

10uF_6.3V

10uF_6.3V

C152

C152

10uF_6.3V

10uF_6.3V

C65

C65

2.2UF_2.5V

2.2UF_2.5VC61

C75

C75

2.2UF_2.5V

2.2UF_2.5V

C87

C87

2.2UF_2.5V

2.2UF_2.5V

C45

C45

2.2UF_2.5V

2.2UF_2.5V

C103

C103

1nF

1nF

C31

C31

2.2UF_2.5V

2.2UF_2.5V

C120

C120

2.2UF_2.5V

2.2UF_2.5V

C131

C131

2.2UF_2.5V

2.2UF_2.5V

C148

C148

10uF_6.3V

10uF_6.3V

C153

C153

10uF_6.3V

10uF_6.3V

C66

C66

2.2UF_2.5V

2.2UF_2.5V

C76

C76

2.2UF_2.5V

2.2UF_2.5V

C88

C88

2.2UF_2.5V

2.2UF_2.5V

C95

C95

2.2UF_2.5V

2.2UF_2.5V

C104

C104

100nF_6.3V

100nF_6.3V

C112

C112

2.2UF_2.5V

2.2UF_2.5V

C121

C121

2.2UF_2.5V

2.2UF_2.5V

C132

C132

2.2UF_2.5V

2.2UF_2.5V

C149

C149

10uF_6.3V

10uF_6.3V

C154

C154

10uF_6.3V

10uF_6.3V

100nF_6.3V

100nF_6.3V

C77

C77

2.2UF_2.5V

2.2UF_2.5V

C42

C42

2.2UF_2.5V

2.2UF_2.5V

C46

C46

2.2UF_2.5V

2.2UF_2.5V

C108

C108

1nF

1nF

C113

C113

100nF_6.3V

100nF_6.3V

C122

C122

2.2UF_2.5V

2.2UF_2.5V

C133

C133

2.2UF_2.5V

2.2UF_2.5V

C150

C150

10uF_6.3V

10uF_6.3V

C36

10uF_6.3V

10uF_6.3V

C78

C78

10uF_6.3V

10uF_6.3V

C89

C89

10uF_6.3V

10uF_6.3V

C96

C96

10uF_6.3V

10uF_6.3V

C109

C109

10uF_6.3V

10uF_6.3V

C53

C53

10uF_6.3V

10uF_6.3V

C467

C467

100nF_6.3V

100nF_6.3V

2

U1H

U1H

1 2

AA19

VDDC#1

VDDC#2

VDDC#3

VDDC#4

VDDC#5

VDDC#6

VDDC#7

VDDC#8

VDDC#9

VDDC#10

VDDC#11

VDDC#12

VDDC#13

VDDC#14

VDDC#15

VDDC#16

VDDC#17

VDDC#18

VDDC#19

VDDC#20

VDDC#21

VDDC#22

VDDC#23

VDDC#24

VDDC#25

VDDC#26

VDDC#27

VDDC#28

VDDC#29

VDDC#30

VDDC#31

VDDC#32

VDDC#33

VDDC#34

VDDC#35

VDDC#36

VDDC#37

VDDC#38

VDDC#39

VDDC#40

VDDC#41

VDDC#42

VDDC#43

VDDC#44

VDDC#45

VDDC#46

VDDC#47

VDDC#48

VDDC#49

VDDC#50

VDDC#51

VDDC#52

VDDC#53

VDDC#54

VDDC#55

VDDC#56

VDDC#57

VDDC#58

VDDC#59

VDDC#60

VDDC#61

VDDC#62

VDDC#63

VDDC#64

VDDC#65

VDDC#66

VDDC#67

VDDC#68

VDDC#69

VDDC#70

VDDC#71

VDDC#72

VDDC#73

VDDC#74

VDDC#75

VDDC#76

VDDC#77

VDDC#78

VDDC#79

VDDC#80

VDDC#81

VDDC#82

VDDC#83

VDDC#84

VDDC#85

VDDC#86

VDDC#87

VDDC#88

VDDC#89

VDDC#90

VDDC#91

VDDC#92

VDDC#93

VDDC#94

VDDC#95

VDDC#96

VDDC#97

216-0732004-00

216-0732004-00

VSSC#1

VSSC#2

VSSC#3

VSSC#4

VSSC#5

VSSC#6

VSSC#7

VSSC#8

VSSC#9

VSSC#10

VSSC#11

VSSC#12

VSSC#13

VSSC#14

VSSC#15

VSSC#16

VSSC#17

VSSC#18

VSSC#19

VSSC#20

VSSC#21

VSSC#22

VSSC#23

VSSC#24

VSSC#25

VSSC#26

VSSC#27

VSSC#28

VSSC#29

VSSC#30

VSSC#31

VSSC#32

VSSC#33

VSSC#34

VSSC#35

VSSC#36

VSSC#37

VSSC#38

VSSC#39

VSSC#40

VSSC#41

VSSC#42

VSSC#43

VSSC#44

VSSC#45

VSSC#46

VSSC#47

VSSC#48

VSSC#49

VSSC#50

VSSC#51

VSSC#52

VSSC#53

VSSC#54

VSSC#55

VSSC#56

VSSC#57

VSSC#58

VSSC#59

VSSC#60

VSSC#61

VSSC#62

VSSC#63

VSSC#64

VSSC#65

VSSC#66

VSSC#67

VSSC#68

VSSC#69

VSSC#70

VSSC#71

VSSC#72

VSSC#73

VSSC#74

VSSC#75

VSSC#76

VSSC#77

VSSC#78

VSSC#79

VSSC#80

VSSC#81

VSSC#82

VSSC#83

VSSC#84

VSSC#85

VSSC#86

VSSC#87

VSSC#88

VSSC#89

VSSC#90

VSSC#91

VSSC#92

VSSC#93

VSSC#94

VSSC#95

VSSC#96

VSSC#97

AA21

AA24

AA26

AA29

AA31

AA34

AC20

AC23

AC25

AC28

AC30

AC33

AC35

AD19

AD21

AD24

AD26

AD29

AD31

AD34

AE20

AE23

AE25

AE28

AE30

AE33

AE35

AF19

AF21

AF24

AF26

AF29

AF31

AF34

AH20

AH23

AH25

AH28

AH30

AH33

AH35

AJ19

AJ21

AJ24

AJ26

AJ29

AJ31

AJ34

AK20

AK23

AK25

AK28

AK30

AK33

AK35

AL19

AL21

AL24

AL26

AL29

AL31

AL34

AN20

AN23

AN25

AN28

AN30

AN33

AN35

AP21

AP24

AP26

AP29

AP31

AP34

AR20

AR23

AR25

AR28

AR30

AR33

W19

W21

W24

W26

W29

W31

W34

Y20

Y23

Y25

Y28

Y30

Y33

Y35

AR35

1 2

AA20

AA23

AA25

AA28

AA30

AA33

AA35

AC19

AC21

AC24

AC26

AC29

AC31

AC34

AD20

AD23

AD25

AD28

AD30

AD33

AD35

AE19

AE21

AE24

AE26

AE29

AE31

AE34

AF20

AF23

AF25

AF28

AF30

AF33

AF35

AH19

AH21

AH24

AH26

AH29

AH31

AH34

AJ20

AJ23

AJ25

AJ28

AJ30

AJ33

AJ35

AK19

AK21

AK24

AK26

AK29

AK31

AK34

AL20

AL23

AL25

AL28

AL30

AL33

AL35

AN19

AN21

AN24

AN26

AN29

AN31

AN34

AP20

AP23

AP25

AP28

AP30

AP33

AR21

AR24

AR26

AR29

AR31

AR34

W20

W23

W25

W28

W30

W33

W35

Y19

Y21

Y24

Y26

Y29

Y31

Y34

AP35

AA13

AB10

AB16

AD13

AE10

AE16

AF13

AH10

AH16

AJ13

AK10

AK16

AM13

AN10

AN16

AR13

AT10

AT16

AU13

AW10

AY13

BA14

BA17

AY11

AV18

BD15

BD18

BC12

BG11

BG13

BG15

BM12

BN15

BM10

B14

B18

B22

A39

A49

A5

AA7

AB2

AC7

AD2

AE7

AF2

AG7

AH2

AJ7

AK2

AL7

AM2

AN1

AN7

AR7

AT2

AU7

AW1

AW7

AY2

B10

B16

B26

B30

A33

B42

BA7

BB2

BC7

BD2

BE7

BG9

BJ1

BN8

BN5

B12

B20

B24

B28

B32

B36

B40

B44

A8

E1

E53

G11

G13

G15

G17

G19

G21

G23

G25

G27

G29

G31

G33

G35

G37

U1I

U1I

VSSM#1

VSSM#2

VSSM#3

VSSM#4

VSSM#5

VSSM#6

VSSM#7

VSSM#8

VSSM#9

VSSM#10

VSSM#11

VSSM#12

VSSM#13

VSSM#14

VSSM#15

VSSM#16

VSSM#17

VSSM#18

VSSM#19

VSSM#20

VSSM#21

VSSM#22

VSSM#23

VSSM#24

VSSM#25

VSSM#26

VSSM#27

VSSM#28

VSSM#29

VSSM#30

VSSM#31

VSSM#32

VSSM#33

VSSM#34

VSSM#35

VSSM#36

VSSM#37

VSSM#38

VSSM#39

VSSM#40

VSSM#41

VSSM#42

VSSM#43

VSSM#44

VSSM#45

VSSM#46

VSSM#47

VSSM#48

VSSM#49

VSSM#50

VSSM#51

VSSM#52

VSSM#53

VSSM#54

VSSM#55

VSSM#56

VSSM#57

VSSM#58

VSSM#59

VSSM#60

VSSM#61

VSSM#62

VSSM#63

VSSM#64

VSSM#65

VSSM#66

VSSM#67

VSSM#68

VSSM#69

VSSM#70

VSSM#71

VSSM#72

VSSM#73

VSSM#74

VSSM#75

VSSM#76

VSSM#77

VSSM#78

VSSM#79

VSSM#80

VSSM#81

VSSM#82

VSSM#83

VSSM#84

VSSM#85

VSSM#86

VSSM#87

VSSM#88

VSSM#89

VSSM#90

VSSM#91

VSSM#92

VSSM#93

VSSM#94

VSSM#95

VSSM#96

VSSM#97

VSSM#98

VSSM#99

VSSM#100

216-0732004-00

216-0732004-00

VSSM#101

VSSM#102

VSSM#103

VSSM#104

VSSM#105

VSSM#106

VSSM#107

VSSM#108

VSSM#109

VSSM#110

VSSM#111

VSSM#112

VSSM#113

VSSM#114

VSSM#115

VSSM#116

VSSM#117

VSSM#118

VSSM#119

VSSM#120

VSSM#121

VSSM#122

VSSM#123

VSSM#124

VSSM#125

VSSM#126

VSSM#127

VSSM#128

VSSM#129

VSSM#130

VSSM#131

VSSM#132

VSSM#133

VSSM#134

VSSM#135

VSSM#136

VSSM#137

VSSM#138

VSSM#139

VSSM#140

VSSM#141

VSSM#142

VSSM#143

VSSM#144

VSSM#145

VSSM#146

VSSM#147

VSSM#148

VSSM#149

VSSM#150

VSSM#151

VSSM#152

VSSM#153

VSSM#154

VSSM#155

VSSM#156

VSSM#157

VSSM#158

VSSM#159

VSSM#160

VSSM#161

VSSM#162

VSSM#163

VSSM#164

VSSM#165

VSSM#166

VSSM#167

VSSM#168

VSSM#169

VSSM#170

VSSM#171

VSSM#172

1

G39

G41

G43

G45

G9

H1

J47

H53

J7

J11

K2

L40

K14

K17

K19

K22

K25

K28

K30

K33

K36

K39

L47

K52

L7

P2