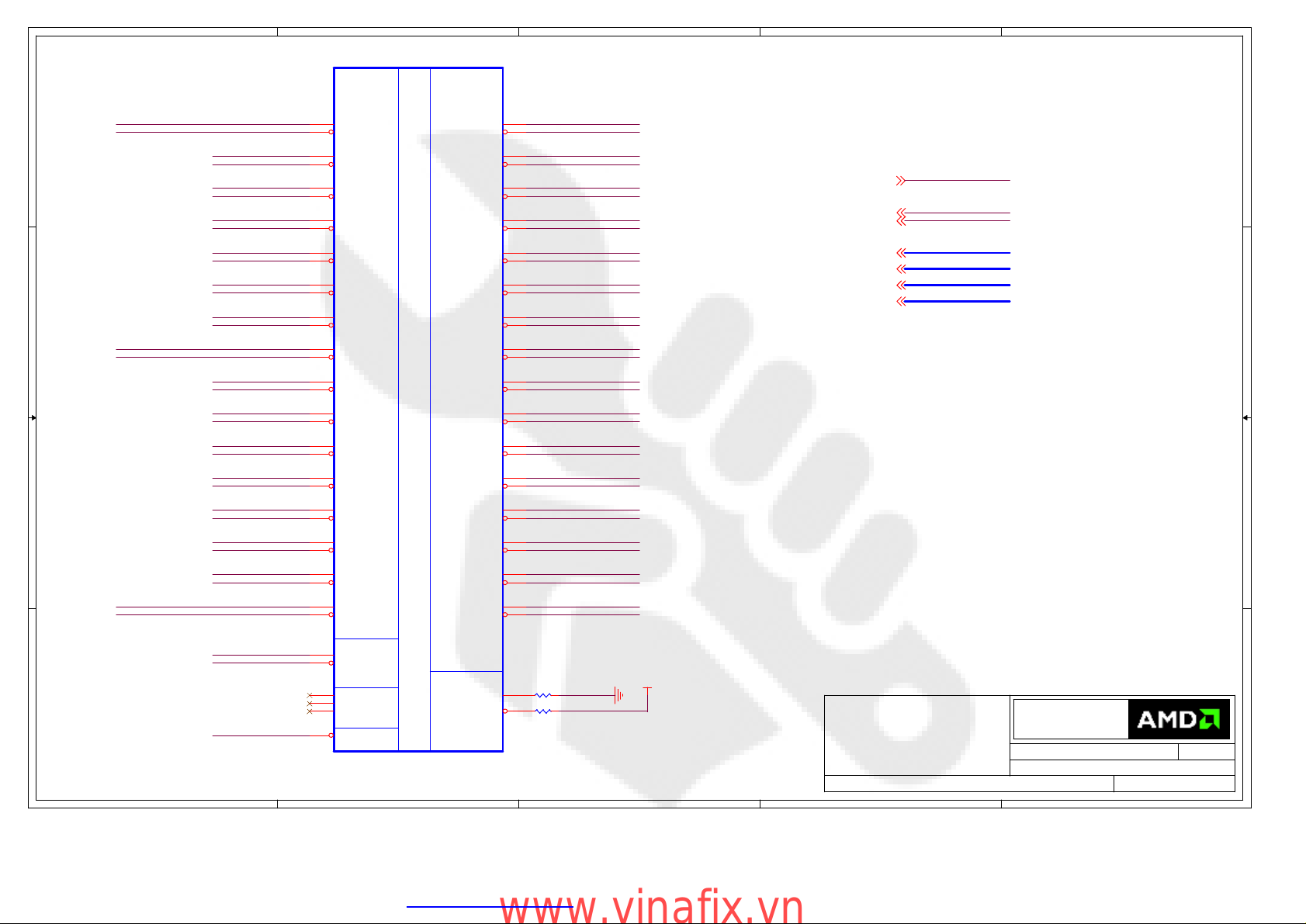

Page 1

5

U1A

4

3

2

1

PCIE_RXP0

D D

C C

B B

PCIE_RXN0

PCIE_RXP1

PCIE_RXN1

PCIE_RXP2

PCIE_RXN2

PCIE_RXP3

PCIE_RXN3

PCIE_RXP4

PCIE_RXN4

PCIE_RXP5

PCIE_RXN5

PCIE_RXP6

PCIE_RXN6

PCIE_RXP7

PCIE_RXN7

PCIE_RXP8

PCIE_RXN8

PCIE_RXP9

PCIE_RXN9

PCIE_RXP10

PCIE_RXN10

PCIE_RXP11

PCIE_RXN11

PCIE_RXP12

PCIE_RXN12

PCIE_RXP13

PCIE_RXN13

PCIE_RXP14

PCIE_RXN14

PCIE_RXP15

PCIE_RXN15

AA38

Y37

Y35

W36

W38

V37

V35

U36

U38

T37

T35

R36

R38

P37

P35

N36

N38

M37

M35

K37

K35

H37

H35

G36

G38

F37

F35

E37

L36

L38

J36

J38

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

PCI EXPRESS INTERFACE

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Y33

Y32

W33

W32

U33

U32

U30

U29

T33

T32

T30

T29

P33

P32

P30

P29

N33

N32

N30

N29

L33

L32

L30

L29

K33

K32

J33

J32

K30

K29

H33

H32

PCIE_TXP0

PCIE_TXN0

PCIE_TXP1

PCIE_TXN1

PCIE_TXP2

PCIE_TXN2

PCIE_TXP3

PCIE_TXN3

PCIE_TXP4

PCIE_TXN4

PCIE_TXP5

PCIE_TXN5

PCIE_TXP6

PCIE_TXN6

PCIE_TXP7

PCIE_TXN7

PCIE_TXP8

PCIE_TXN8

PCIE_TXP9

PCIE_TXN9

PCIE_TXP10

PCIE_TXN10

PCIE_TXP11

PCIE_TXN11

PCIE_TXP12

PCIE_TXN12

PCIE_TXP13

PCIE_TXN13

PCIE_TXP14

PCIE_TXN14

PCIE_TXP15

PCIE_TXN15

PCIE_RST#8

PCIE_REFCLKP8

PCIE_REFCLKN8

PCIE_RXP[15..0]8

PCIE_RXN[15..0]8

PCIE_TXP[15..0]8

PCIE_TXN[15..0]8

PCIE_RST#

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_RXP[15..0]

PCIE_RXN[15..0]

PCIE_TXP[15..0]

PCIE_TXN[15..0]

PCIE_REFCLKP

PCIE_REFCLKN

A A

PCIE_RST#

5

CLOCK

AB35

PCIE_REFCLKP

AA36

PCIE_REFCLKN

AJ21

NC#1

AK21

NC#2

AH16 Y29

NC_PWRGOOD PCIE_CALRN

AA30

PERSTB

216-0729012-00

4

CALIBRATION

PCIE_CALRP

Y30

R11

1.27K

R12

2.0K

1.1V_REG

3

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

?2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

Title

RH M92/M96 M package MXM3.0 DDR3

2

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

Markham, Ontario

Thursday, August 28, 2008

M8X GDDR3

Sheet

1 12

of

Doc No.

1

RevDate:

1

105-B79531-00A

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

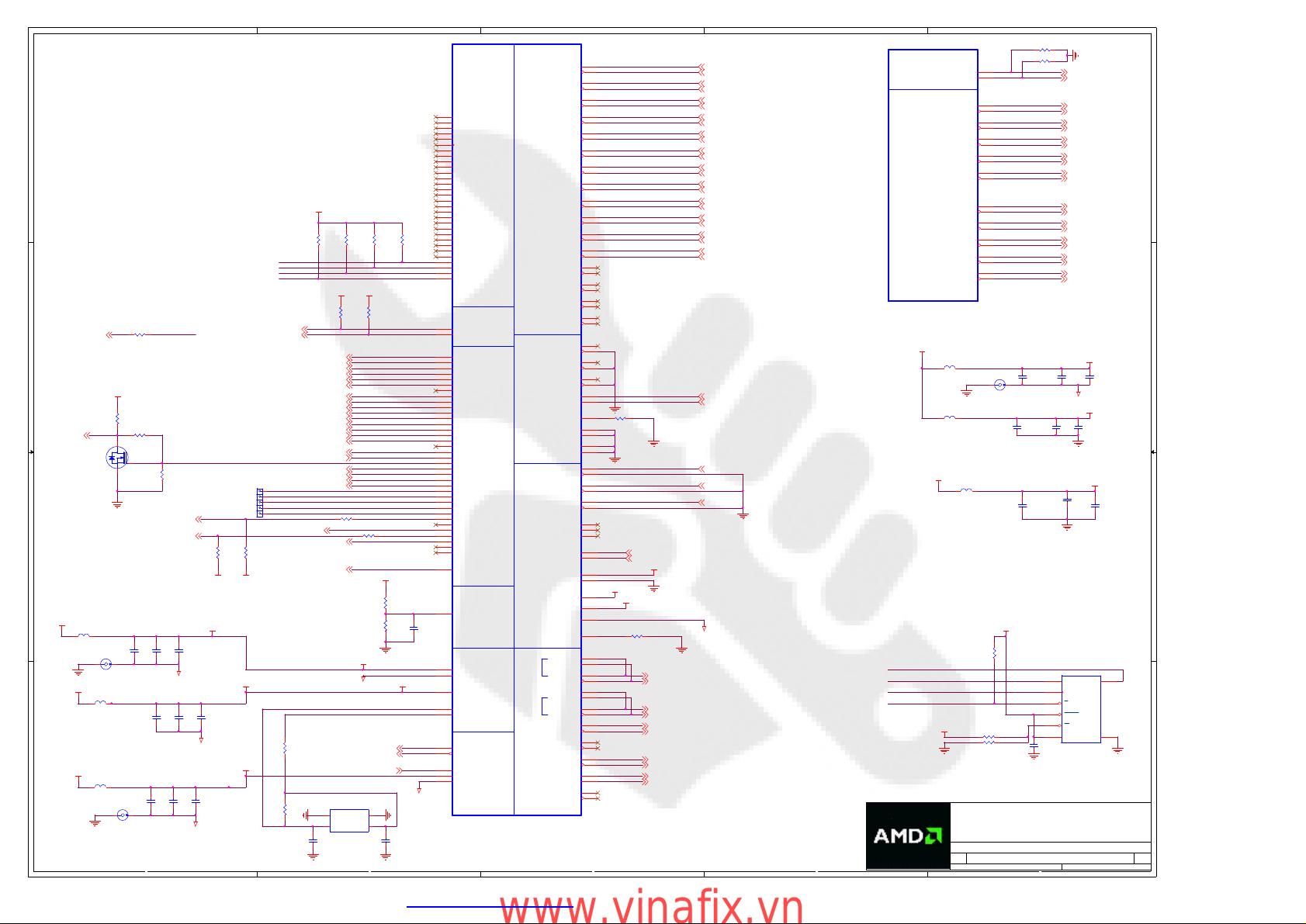

Page 2

5

D D

1.8V_REG

MEM_ID0

MEM_ID1

MEM_ID2

MEM_ID3

TP7 35mil

TP8 35mil

TP9 35mil

TP11 35mil

TSVDD

I2C_CLK9

I2C_DAT9

GENERICC9

4.7K

R544

PLACE VREFG DIVIDER AND CAP

CLOSE TO ASIC

R450

0R

R451

1M

C681

18pF_50V

GPU_SMBDAT8

GPU_SMBCLK8

GPIO7_BLON8

GPIO89

MB_ALERTB8,9

GPIO2010

BB_EN11

GPIO229

CLKREQB8

Q1

1

2N7002_NL

C55

10uF_6.3V

R26

0R

10uF_6.3V

5

R27

10K

HDTV#/TV8

VGA/TV#8

C56

1uF

DPLL_PVSS

C58

10uF_6.3V

C62

GPIO5

C63

1uF

C57

100nF

C59

1uF

TSVSS

DPLL_PVDD

DPLL_PVSS

C64

100nF

JTAG DEBUG PORT

4.7K

R543

VDDR3 VDDR3

C60

100nF

PWR_LEVEL8

C C

CTFb8

B B

1.8V_REG

B6 60R_3A

1.1V_REG

A A

1.8V_REG

R447 0R

VDDR3

R24

10K

32

(1.8V@150mA DPLL_PVDD)

NS3

1 2

NS_VIA

B7 60R_3A

(1.1V@300mA DPLL_VDDC)

(1.8V@15mA TSVDD)

B8

BLM15BD121SN1

NS5

1 2

NS_VIA

R443

10K

VDDR3 VDDR3

GPIO08,9

GPIO18,9

GPIO29

GPIO59

GPIO98,9

GPIO10

GPIO119

GPIO129

GPIO139

HPD28

GPIO1510

HPD38

R448 0R

HPD48

HPD18

Y1

4

GND4

27MHz_16pF

R444

10K

R13

4.7K

R449 0R

DPLL_PVDD

DPLL_PVSSDPLL_VDDC

GPU_DPLUS9

GPU_DMINUS9

GND2

XTAL1XTAL2

4

R445

10K

R14

4.7K

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO_19_CTF

CLKREQB

GPIO24_TRSTB

GPIO25_TDI

GPIO26_TCK

GPIO27_TMS

GPIO28_TDO

GEN_A

1.8V_REG

XTALIN

XTALOUT

TS_FDO8

2

13

4

R446

10K

I2C_CLK

I2C_DAT

R31

499R

R32

249R

DPLL_VDDC

TSVSS

C682

18pF_50V

C54

100nF

U1B

AR8

DVPCNTL_MVP_0

AU8

DVPCNTL_MVP_1

AP8

DVPCNTL_0

AW8

DVPCNTL_1

AR3

DVPCNTL_2

AR1

DVPCLK

AU1

DVPDATA_0

AU3

DVPDATA_1

AW3

DVPDATA_2

AP6

DVPDATA_3

AW5

DVPDATA_4

AU5

DVPDATA_5

AR6

DVPDATA_6

AW6

DVPDATA_7

AU6

DVPDATA_8

AT7

DVPDATA_9

AV7

DVPDATA_10

AN7

DVPDATA_11

AV9

DVPDATA_12

AT9

DVPDATA_13

AR10

DVPDATA_14

AW10

DVPDATA_15

AU10

DVPDATA_16

AP10

DVPDATA_17

AV11

DVPDATA_18

AT11

DVPDATA_19

AR12

DVPDATA_20

AW12

DVPDATA_21

AU12

DVPDATA_22

AP12

DVPDATA_23

AK26

SCL

AJ26

SDA

GENERAL PURPOSE I/O

AH20

GPIO_0

AH18

GPIO_1

AN16

GPIO_2

AH23

GPIO_3_SMBDATA

AJ23

GPIO_4_SMBCLK

AH17

GPIO_5_AC_BATT

AJ17

GPIO_6

AK17

GPIO_7_BLON

AJ13

GPIO_8_ROMSO

AH15

GPIO_9_ROMSI

AJ16

GPIO_10_ROMSCK

AK16

GPIO_11

AL16

GPIO_12

AM16

GPIO_13

AM14

GPIO_14_HPD2

AM13

GPIO_15_PWRCNTL_0

AK14

GPIO_16_SSIN

AG30

GPIO_17_THERMAL_INT

AN14

GPIO_18_HPD3

AM17

GPIO_19_CTF

AL13

GPIO_20_PWRCNTL_1

AJ14

GPIO_21_BB_EN

AK13

GPIO_22_ROMCSB

AN13

GPIO_23_CLKREQB

AM23

JTAG_TRSTB

AN23

JTAG_TDI

AK23

JTAG_TCK

AL24

JTAG_TMS

AM24

JTAG_TDO

AJ19

GENERICA

AK19

GENERICB

AJ20

GENERICC

AK20

GENERICD

AJ24

GENERICE_HPD4

AH26

GENERICF

AH24

GENERICG

AK24

HPD1

AH13

VREFG

AM32

DPLL_PVDD

AN32

DPLL_PVSS

AN31

DPLL_VDDC

AV33

XTALIN

AU34

XTALOUT

AF29

DPLUS

AG29

DMINUS

AK32

TS_FDO

AJ32

TSVDD

AJ33

TSVSS

216-0729012-00

MUTI GFX

I2C

PLL/CLOCK

THERMAL

TXCAP_DPA3P

TXCAM_DPA3N

TX0P_DPA2P

TX0M_DPA2N

DPA

TX1P_DPA1P

TX1M_DPA1N

TX2P_DPA0P

TX2M_DPA0N

TXCBP_DPB3P

TXCBM_DPB3N

TX3P_DPB2P

TX3M_DPB2N

DPB

TX4P_DPB1P

TX4M_DPB1N

TX5P_DPB0P

TX5M_DPB0N

TXCCP_DPC3P

TXCCM_DPC3N

TX0P_DPC2P

TX0M_DPC2N

DPC

TX1P_DPC1P

TX1M_DPC1N

TX2P_DPC0P

TX2M_DPC0N

TXCDP_DPD3P

TXCDM_DPD3N

TX3P_DPD2P

TX3M_DPD2N

DPD

TX4P_DPD1P

TX4M_DPD1N

TX5P_DPD0P

TX5M_DPD0N

DAC1

DAC2

A2VDDQ

A2VSSQ

DDC/AUX

DDC1CLK

DDC1DATA

DDC2CLK

DDC2DATA

DDCCLK_AUX3P

DDCDATA_AUX3N

DDCCLK_AUX4P

DDCDATA_AUX4N

DDCCLK_AUX5P

DDCDATA_AUX5N

DDC6CLK

DDC6DATA

NC_DDCCLK_AUX7P

NC_DDCDATA_AUX7N

HSYNC

VSYNC

RSET

AVDD

AVSSQ

VDD1DI

VSS1DI

COMP

H2SYNC

V2SYNC

VDD2DI

VSS2DI

A2VDD

R2SET

AUX1P

AUX1N

AUX2P

AUX2N

3

AU24

AV23

AT25

AR24

AU26

AV25

AT27

AR26

AR30

AT29

AV31

AU30

AR32

AT31

AT33

AU32

AU14

AV13

AT15

AR14

AU16

AV15

AT17

AR16

AU20

AT19

AT21

AR20

AU22

AV21

AT23

AR22

AD39

R

AD37

RB

AE36

G

AD35

GB

AF37

B

AE38

BB

AC36

AC38

R25

AB34

499R

AD34

AE34

AC33

AC34

AC30

R2

AC31

R2B

AD30

G2

AD31

G2B

AF30

B2

AF31

B2B

AC32

C

AD32

Y

AF32

AD29

AC29

AG31

AG32

AG33

AD33

AF33

AA29

AM26

AN26

AM27

AL27

AM19

AL19

AN20

AM20

AL30

AM30

AL29

AM29

AN21

AM21

AJ30

AJ31

AK30

AK29

3

A2VDD

A2VDDQ

H2SYNC 8,9

V2SYNC8,9

VDD2DI

R33

715R

DPA_AUXP 8

DPA_AUXN 8

DPB_AUXP 8

DPB_AUXN 8

DPC_AUXP 8

DPC_AUXN 8

DPD_AUXP 8

DPD_AUXN 8

DDC6CLK 8

DDC6DATA 8

TXCAP_DPA3P8

TXCAM_DPA3N8

TX0P_DPA2P 8

TX0M_DPA2N8

TX1P_DPA1P 8

TX1M_DPA1N8

TX2P_DPA0P 8

TX2M_DPA0N8

TXCBP_DPB3P8

TXCBM_DPB3N8

TX3P_DPB2P 8

TX3M_DPB2N8

TX4P_DPB1P 8

TX4M_DPB1N8

TX5P_DPB0P 8

TX5M_DPB0N8

TXCCP_DPC3P8

TXCCM_DPC3N8

TX0P_DPC2P 8

TX0M_DPC2N8

TX1P_DPC1P 8

TX1M_DPC1N8

TX2P_DPC0P 8

TX2M_DPC0N8

HSYNC 9

VSYNC 9

VGA_RED 8

VGA_GRN 8

VGA_BLU 8

A2VSSQ

2

U1G

LVDS CONTROL

TXCLK_UP_DPF3P

TXCLK_UN_DPF3N

TXOUT_U0P_DPF2P

TXOUT_U0N_DPF2N

TXOUT_U1P_DPF1P

TXOUT_U1N_DPF1N

TXOUT_U2P_DPF0P

TXOUT_U2N_DPF0N

LVTMDP

TXCLK_LP_DPE3P

TXCLK_LN_DPE3N

TXOUT_L0P_DPE2P

TXOUT_L0N_DPE2N

TXOUT_L1P_DPE1P

TXOUT_L1N_DPE1N

TXOUT_L2P_DPE0P

TXOUT_L2N_DPE0N

216-0729012-00

1.8V_REG

BLM15BD121SN1

BLM15BD121SN1

VDDR3

GPIO8

GPIO9

GPIO10

GPIO22

A 256MB MEMORY APERTURE SIZE

CAN BE DEFINED USING A SEPARATE

ROM OR STRAPPING

A 256MB MEMORY APERTURE SIZE

CAN BE DEFINED USING A SEPARATE

ROM OR STRAPPING

2

AK27

VARY_BL

AJ27

DIGON

AK35

AL36

AJ38

AK37

AH35

AJ36

AG38

AH37

AF35

TXOUT_U3P

AG36

TXOUT_U3N

AP34

AR34

AW37

AU35

AR37

AU39

AP35

AR35

AN36

TXOUT_L3P

AP37

TXOUT_L3N

B1

1 2

NS_VIA

B2

B5

BLM15BD121SN1

R34

10K

VDDR3

R36 0R

R39 0R

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RH M92/M96 M package MXM3.0 DDR3

Size Document Number Rev

C

Date: Sheet of

1

R42510K

R42610K

BLON_PWM 8

FPVCC 8

TXCLK_U+ 8

TXCLK_U- 8

TXOUT_U0+ 8

TXOUT_U0- 8

TXOUT_U1+ 8

TXOUT_U1- 8

TXOUT_U2+ 8

TXOUT_U2- 8

TXOUT_U3+ 8

TXOUT_U3- 8

TXCLK_L+ 8

TXCLK_L- 8

TXOUT_L0+ 8

TXOUT_L0- 8

TXOUT_L1+ 8

TXOUT_L1- 8

TXOUT_L2+ 8

TXOUT_L2- 8

TXOUT_L3+ 8

TXOUT_L3- 8

(1.8V@65mA A2VDD)

C39

NS1

10uF_6.3V

(1.8V@100mA VDD2DI)

C42

10uF_6.3V

(3.3V@?mA A2VDD)

C756

10uF_6.3V

VDDR3

A2VDDQ

C41

C40

100nF

1uF

A2VSSQ

VDD2DI

C44

C43

100nF

1uF

A2VDD

C52

C757

1uFTP10 35mil

100nF

U56

5

Q

D

6

C

1

S

7

HOLD

3

W

8

VCC

M25P05-VMN6T

VSS

C61

100nF

ALTERNATIVE PART :M25P05(512Kbit)

2

4

SERIAL EEPROM 512K/1M

105-B79531-00A

1

2 12Friday, August 29, 2008

0

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

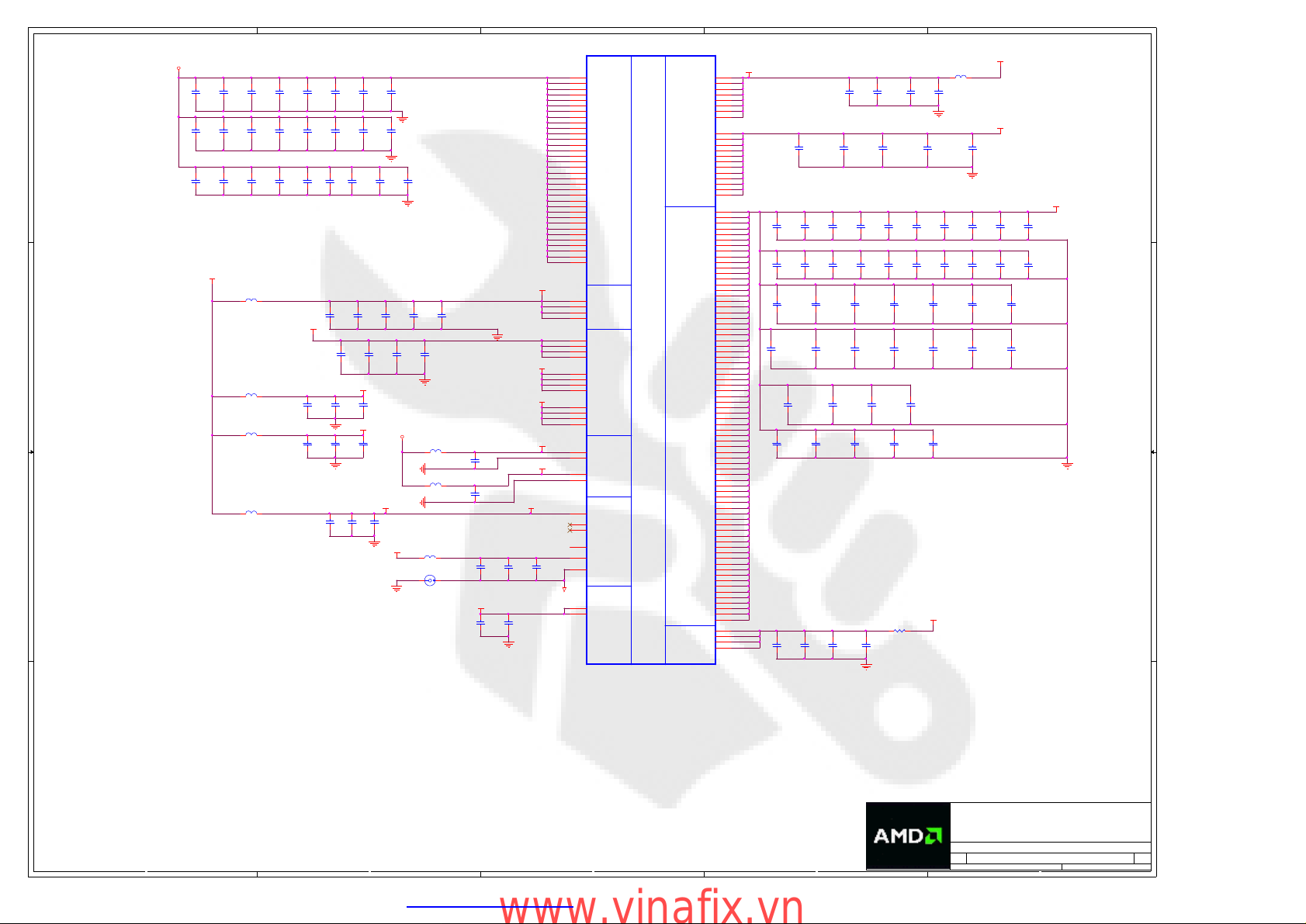

Page 3

5

+1.5V_REG

C89

C88

1uF

C121

1uF

C144

1uF

C74

1uF

C122

1uF

C145

1uF

10uF_6.3V

B12

BLM15BD121SN1

B13

BLM15BD121SN1

B15

BLM15BD121SN1

B19

BLM15BD121SN1

1uF

C123

1uF

C146

C90

1uF

C124

1uF

C147

1uF

(1.8V@110mA VDD_CT)

VDDR3

C199

10uF_6.3V

C213

10uF_6.3V

(1.8V@40mA PCIE_PVDD)

(For M96/M92 SPV10 = VDDC)

C73

1uF

C120

D D

C C

B B

1uF

C143

1uF

1.8V_REG

C91

1uF

C125

1uF

C752

1uF

C168

1uF

10uF_6.3V

C200

1uF

C214

1uF

C226

10uF_6.3V

C185

C753

1uF

VDDR4

VDDR5

C227

1uF

C169

1uF

4

C92

1uF

C126

1uF

C201

1uF

C215

1uF

C186

1uF

C754

1uF

PCIE_PVDD

C228

100nF

C93

1uF

C127

1uF

C755

1uF

C171

C170

1uF

10uF_6.3V

C187

C188

1uF

1uF

+1.5V_REG

B17 BLM15BD121SN1

B18

BLM15BD121SN1

VDDC

NS29

1 2

NS_VIA

C172

1uF

VDDR4 for DVPDATA[12..23]

VDDR5 for DVPDATA[0..11]

C224

1uF

C225

1uF

(0.95V-1.1V@120mA SPV10)

L3

BLM15BD121SN1

C229

10uF_6.3V

+BBP

C232

1uF

C230

1uF

C233

1uF

VDDC_CT

VDDR5

VDDR4

VDDRHA

VDDRHB

PCIE_PVDD

3

U1E

MEM I/O

AC7

VDDR1#1

AD11

VDDR1#2

AF7

VDDR1#3

AG10

VDDR1#4

AJ7

VDDR1#5

AK8

VDDR1#6

AL9

VDDR1#7

G11

VDDR1#8

G14

VDDR1#9

G17

VDDR1#10

G20

VDDR1#11

G23

VDDR1#12

G26

VDDR1#13

G29

VDDR1#14

H10

VDDR1#15

J7

VDDR1#16

J9

VDDR1#17

K11

VDDR1#18

K13

VDDR1#19

K8

VDDR1#20

L12

VDDR1#21

L16

VDDR1#22

L21

VDDR1#23

L23

VDDR1#24

L26

VDDR1#25

L7

VDDR1#26

M11

VDDR1#27

N11

VDDR1#28

P7

VDDR1#29

R11

VDDR1#30

U11

VDDR1#31

U7

VDDR1#32

Y11

VDDR1#33

Y7

VDDR1#34

LEVEL

TRANSLATION

AF26

VDD_CT#1

AF27

VDD_CT#2

AG26

VDD_CT#3

AG27

VDD_CT#4

I/O

AF23

VDDR3#1

AF24

VDDR3#2

AG23

VDDR3#3

AG24

VDDR3#4

AF13

VDDR5#1

AF15

VDDR5#2

AG13

VDDR5#3

AG15

VDDR5#4

AD12

VDDR4#1

AF11

VDDR4#2

AF12

VDDR4#3

AG11

VDDR4#4

MEM CLK

M20

VDDRHA

M21

VSSRHA

V12

VDDRHB

U12

VSSRHB

PLL

AB37

PCIE_PVDD

H7

NC_MPV18#1

H8

NC_MPV18#2

AM10

NC_SPV18

AN9

C231

100nF

SPV10

AN10

SPVSS

SPVSS

BACK BIAS

AA13

BBP#1

Y13 AH27

BBP#2 VDDC#73

216-0729012-00

POWER

PCIE

PCIE_VDDR#1

PCIE_VDDR#2

PCIE_VDDR#3

PCIE_VDDR#4

PCIE_VDDR#5

PCIE_VDDR#6

PCIE_VDDR#7

PCIE_VDDR#8

PCIE_VDDC#1

PCIE_VDDC#2

PCIE_VDDC#3

PCIE_VDDC#4

PCIE_VDDC#5

PCIE_VDDC#6

PCIE_VDDC#7

PCIE_VDDC#8

PCIE_VDDC#9

PCIE_VDDC#10

PCIE_VDDC#11

PCIE_VDDC#12

CORE

ISOLATED

CORE I/O

VDDC#1

VDDC#2

VDDC#3

VDDC#4

VDDC#5

VDDC#6

VDDC#7

VDDC#8

VDDC#9

VDDC#10

VDDC#11

VDDC#12

VDDC#13

VDDC#14

VDDC#15

VDDC#16

VDDC#17

VDDC#18

VDDC#19

VDDC#20

VDDC#21

VDDC#22

VDDC#23

VDDC#24

VDDC#25

VDDC#26

VDDC#27

VDDC#28

VDDC#29

VDDC#30

VDDC#31

VDDC#32

VDDC#33

VDDC#34

VDDC#35

VDDC#36

VDDC#37

VDDC#38

VDDC#39

VDDC#40

VDDC#41

VDDC#42

VDDC#43

VDDC#44

VDDC#45

VDDC#46

VDDC#47

VDDC#48

VDDC#49

VDDC#50

VDDC#51

VDDC#52

VDDC#53

VDDC#54

VDDC#55

VDDC#56

VDDC#57

VDDC#58

VDDC#59

VDDC#60

VDDC#61

VDDC#62

VDDC#63

VDDC#64

VDDC#65

VDDC#66

VDDC#67

VDDC#68

VDDC#69

VDDC#70

VDDC#71

VDDC#72

VDDC#74

VDDCI#1

VDDCI#2

VDDCI#3

VDDCI#4

AA31

AA32

AA33

AA34

V28

W29

W30

Y31

G30

G31

H29

H30

J29

J30

L28

M28

N28

R28

T28

U28

AA15

AA17

AA20

AA22

AA24

AA27

AB13

AB16

AB18

AB21

AB23

AB26

AB28

AC12

AC15

AC17

AC20

AC22

AC24

AC27

AD13

AD16

AD18

AD21

AD23

AD26

AF17

AF20

AF22

AG16

AG18

AG21

AH22

M16

M18

M23

M26

N15

N17

N20

N22

N24

N27

R13

R16

R18

R21

R23

R26

T15

T17

T20

T22

T24

T27

U16

U18

U21

U23

U26

V15

V17

V20

V22

V24

V27

Y16

Y18

Y21

Y23

Y26

Y28

AH28

M15

N13

R12

T12

PCIE_VDDR

2

(1.8V@504mA PCIE_VDDR)

C776

1uF

(1.1V@1920mA PCIE_VDDC)

C111

C112

1uF

1uF

C133

1uF_6.3V

C148

1uF_6.3V

C758

2.2UF_2.5V

C765

2.2UF_2.5V

C217

10uF_6.3V

C772

2.2UF_2.5V

C134

1uF_6.3V

C149

1uF_6.3V

10uF_6.3V

C759

2.2UF_2.5V

C766

2.2UF_2.5V

C218

C135

1uF_6.3V

C150

1uF_6.3V

C773

2.2UF_2.5V

C136

1uF_6.3V

C151

1uF_6.3V

C760

2.2UF_2.5V

C767

2.2UF_2.5V

C219

10uF_6.3V

(For M96/92, 0.95V-1.1V@2A VDDCI)

C235

C234

1uF

C236

1uF

1uF

10uF_6.3V

C774

2.2UF_2.5V

C238

C95

100nF

C113

1uF

C137

1uF_6.3V

C152

1uF_6.3V

10uF_6.3V

C761

2.2UF_2.5V

C768

2.2UF_2.5V

C220

R5570R

C100

1uF

C138

1uF_6.3V

C153

1uF_6.3V

C775

2.2UF_2.5V

VDDC

C101

10uF_6.3V

C114

1uF

C762

2.2UF_2.5V

C769

2.2UF_2.5V

C221

10uF_6.3V

L1 30R_3A

10uF_6.3V

C139

1uF_6.3V

C154

1uF_6.3V

1.8V_REG

1.1V_REG

C117

C140

1uF_6.3V

C155

1uF_6.3V

C763

2.2UF_2.5V

C770

2.2UF_2.5V

C141

1uF_6.3V

C156

1uF_6.3V

C764

2.2UF_2.5V

C771

2.2UF_2.5V

1

For M96/M92 PCIE_VDDC = 1.1V

For M97/RV8xx PCIE_VDDC = 1.0V

VDDC

C142

1uF_6.3V

C157

1uF_6.3V

A A

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RH M92/M96 M package MXM3.0 DDR3

Size Document Number Rev

C

5

4

3

2

Date: Sheet of

105-B79531-00A

1

3 12Thursday, September 11, 2008

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

0

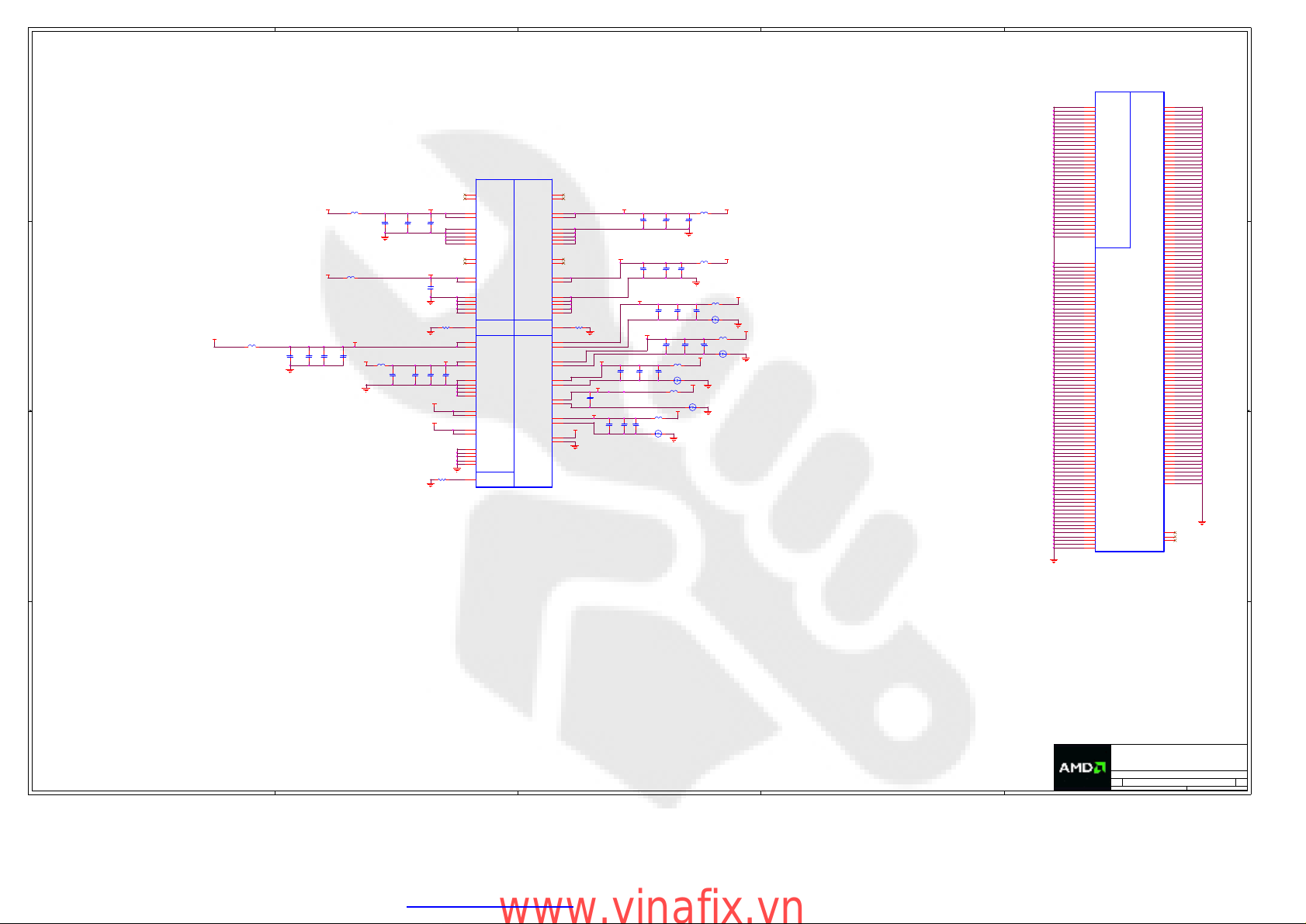

Page 4

5

D D

1.1V_REG

BLM15BD121SN1

1.1V_REG

BLM15BD121SN1

C C

1.8V_REG

BLM15BD121SN1

B B

B31

(1.8V@200mA DPE_VDD18)

C274

C290

10uF_6.3V

1uF

C276

C275

100nF

1uF

(1.1V@200mA DPC_VDD10)

B22

(1.1V@200mA DPD_VDD10)

B27

DPE_VDD18

BLM15BD121SN1

(1.1V@170mA DPE_VDD10)

C254

10uF_6.3V

B33

10uF_6.3V

4

U1H

DP A/B POWERDP C/D POWER

AP20

NC_DPC_VDD18#1

AP21

R59 150R

DPE_VDD101.1V_REG

R63 150R

NC_DPC_VDD18#2

AP13

DPC_VDD10#1

AT13

DPC_VDD10#2

AN17

DPC_VSSR#1

AP16

DPC_VSSR#2

AP17

DPC_VSSR#3

AW14

DPC_VSSR#4

AW16

DPC_VSSR#5

AP22

NC_DPD_VDD18#1

AP23

NC_DPD_VDD18#2

AP14

DPD_VDD10#1

AP15

DPD_VDD10#2

AN19

DPD_VSSR#1

AP18

DPD_VSSR#2

AP19

DPD_VSSR#3

AW20

DPD_VSSR#4

AW22

DPD_VSSR#5

AW18

DPCD_CALR

DP E/F POWER

AH34

DPE_VDD18#1

AJ34

DPE_VDD18#2

AL33

DPE_VDD10#1

AM33

DPE_VDD10#2

C282

AN34

100nF

DPE_VSSR#1

AP39

DPE_VSSR#2

AR39

DPE_VSSR#3

AU37

DPE_VSSR#4

AW35

DPE_VSSR#5

AF34

DPF_VDD18#1

AG34

DPF_VDD18#2

AK33

DPF_VDD10#1

AK34

DPF_VDD10#2

AF39

DPF_VSSR#1

AH39

DPF_VSSR#2

AK39

DPF_VSSR#3

AL34

DPF_VSSR#4

AM34

DPF_VSSR#5

AM39

DPEF_CALR

216-0729012-00

DPC_VDD10

C248

C247

100nF

1uF

DPD_VDD10

C264

100nF

C280

C296

C281

1uF

1uF

DPE_VDD18

DPE_VDD10

NC_DPA_VDD18#1

NC_DPA_VDD18#2

DPA_VDD10#1

DPA_VDD10#2

DPA_VSSR#1

DPA_VSSR#2

DPA_VSSR#3

DPA_VSSR#4

DPA_VSSR#5

NC_DPB_VDD18#1

NC_DPB_VDD18#2

DPB_VDD10#1

DPB_VDD10#2

DPB_VSSR#1

DPB_VSSR#2

DPB_VSSR#3

DPB_VSSR#4

DPB_VSSR#5

DPAB_CALR

DP PLL POWER

DPA_PVDD

DPA_PVSS

DPB_PVDD

DPB_PVSS

DPC_PVDD

DPC_PVSS

DPD_PVDD

DPD_PVSS

DPE_PVDD

DPE_PVSS

NC_DPF_PVDD

NC_DPF_PVSS

AN24

AP24

AP31

AP32

AN27

AP27

AP28

AW24

AW26

AP25

AP26

AN33

AP33

AN29

AP29

AP30

AW30

AW32

R60 150R

AW28

AU28

AV27

AV29

AR28

AU18

AV17

AV19

C286

100nF

AR18

DPE_PVDD

AM37

AN38

DPE_PVDD

AL38

AM35

DPC_PVDD

DPD_PVDD

C292

100nF

100nF

DPA_VDD10

DPB_VDD10

(1.1V@200mA DPB_VDD10)

DPA_PVDD

(1.8V@20mA DPC_PVDD)

C283

C284

1uF

(1.8V@20mA DPD_PVDD)

(1.8V@20mA DPE_PVDD)

C293

1uF

10uF_6.3V

3

(1.1V@200mA DPA_VDD10)

C252

C253

10uF_6.3V

1uF

C257

C256

1uF

10uF_6.3V

(1.8V@20mA DPA_PVDD)

C265

C266

100nF

1uF

DPB_PVDD

(1.8V@20mA DPB_PVDD)

C271

C272

100nF

1uF

BLM15BD121SN1

C285

NS21

10uF_6.3V

BLM15BD121SN1

1.8V_REG

B37

BLM15BD121SN1

C294

NS24

12

NS_VIA

100nF

12

1.8V_REG

B35

BLM15BD121SN1

C249

100nF

BLM15BD121SN1C258

C267

10uF_6.3V

1.8V_REG

B34

NS_VIA

NS22

12

NS_VIA

B23

B25

BLM15BD121SN1

NS15

NS_VIA

C273

BLM15BD121SN1

10uF_6.3V

1.1V_REG

1.1V_REG

12

NS17

NS_VIA

2

1.8V_REG

B28

1.8V_REG

B30

12

AB39

E39

F34

F39

G33

G34

H31

H34

H39

M34

M39

N31

N34

P31

P34

P39

R34

T31

T34

T39

U31

U34

V34

V39

W31

W34

Y34

Y39

F15

F17

F19

F21

F23

F25

F27

F29

F31

F33

J27

K14

L11

L17

L22

L24

M17

M22

M24

N16

N18

N21

N23

N26

R15

R17

R20

R22

R24

R27

T11

T13

T16

T18

T21

T23

T26

U15

U17

U20

U22

U24

U27

V11

V16

V18

V21

V23

V26

Y15

Y17

Y20

Y22

Y24

Y27

U13

V13

J31

J34

K31

K34

K39

L31

L34

F7

F9

G2

G6

H9

J2

J6

J8

K7

L2

L6

N2

N6

R2

R6

U2

U6

W2

W6

U1F

PCIE_VSS#1

PCIE_VSS#2

PCIE_VSS#3

PCIE_VSS#4

PCIE_VSS#5

PCIE_VSS#6

PCIE_VSS#7

PCIE_VSS#8

PCIE_VSS#9

PCIE_VSS#10

PCIE_VSS#11

PCIE_VSS#12

PCIE_VSS#13

PCIE_VSS#14

PCIE_VSS#15

PCIE_VSS#16

PCIE_VSS#17

PCIE_VSS#18

PCIE_VSS#19

PCIE_VSS#20

PCIE_VSS#21

PCIE_VSS#22

PCIE_VSS#23

PCIE_VSS#24

PCIE_VSS#25

PCIE_VSS#26

PCIE_VSS#27

PCIE_VSS#28

PCIE_VSS#29

PCIE_VSS#30

PCIE_VSS#31

PCIE_VSS#32

PCIE_VSS#33

PCIE_VSS#34

PCIE_VSS#35

GND#101

GND#102

GND#103

GND#104

GND#105

GND#106

GND#107

GND#108

GND#109

GND#110

GND#111

GND#112

GND#113

GND#114

GND#115

GND#116

GND#117

GND#118

GND#119

GND#120

GND#121

GND#122

GND#123

GND#124

GND#125

GND#126

GND#127

GND#128

GND#129

GND#130

GND#131

GND#132

GND#133

GND#134

GND#135

GND#136

GND#137

GND#138

GND#139

GND#140

GND#141

GND#142

GND#143

GND#144

GND#145

GND#146

GND#147

GND#148

GND#149

GND#150

GND#151

GND#152

GND#153

GND#154

GND#155

GND#156

GND#157

GND#158

GND#159

GND#160

GND#161

GND#162

GND#163

GND#164

GND#165

GND#166

GND#167

GND#168

GND#169

GND#170

GND#171

GND#172

GND#173

GND#174

GND#175

GND#176

216-0729012-00

1

GND

GND#10

GND#11

GND#12

GND#13

GND#14

GND#15

GND#16

GND#17

GND#18

GND#19

GND#20

GND#21

GND#22

GND#23

GND#24

GND#25

GND#26

GND#27

GND#28

GND#29

GND#30

GND#31

GND#32

GND#33

GND#34

GND#35

GND#36

GND#37

GND#38

GND#39

GND#40

GND#41

GND#42

GND#43

GND#44

GND#45

GND#46

GND#47

GND#48

GND#49

GND#50

GND#51

GND#52

GND#53

GND#54

GND#55

GND#56

GND#57

GND#58

GND#59

GND#60

GND#61

GND#62

GND#63

GND#64

GND#65

GND#66

GND#67

GND#68

GND#69

GND#70

GND#71

GND#72

GND#73

GND#74

GND#75

GND#76

GND#77

GND#78

GND#79

GND#80

GND#81

GND#82

GND#83

GND#84

GND#85

GND#86

GND#87

GND#88

GND#89

GND#90

GND#91

GND#92

GND#93

GND#94

GND#95

GND#96

GND#97

GND#98

GND#99

GND#100

VSS_MECH#1

VSS_MECH#2

VSS_MECH#3

A3

GND#1

A37

GND#2

AA16

GND#3

AA18

GND#4

AA2

GND#5

AA21

GND#6

AA23

GND#7

AA26

GND#8

AA28

GND#9

AA6

AB12

AB15

AB17

AB20

AB22

AB24

AB27

AC11

AC13

AC16

AC18

AC2

AC21

AC23

AC26

AC28

AC6

AD15

AD17

AD20

AD22

AD24

AD27

AD9

AE2

AE6

AF10

AF16

AF18

AF21

AG17

AG2

AG20

AG22

AG6

AG9

AH21

AH29

AJ10

AJ11

AJ2

AJ28

AJ6

AK11

AK31

AK7

AL11

AL14

AL17

AL2

AL20

AL21

AL23

AL26

AL32

AL6

AL8

AM11

AM31

AM9

AN11

AN2

AN30

AN6

AN8

AP11

AP7

AP9

AR5

AW34

B11

B13

B15

B17

B19

B21

B23

B25

B27

B29

B31

B33

B7

B9

C1

C39

E35

E5

F11

F13

A39

AW1

AW39

A A

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RH M92/M96 M package MXM3.0 DDR3

Size Document Number Rev

5

4

3

2

Date: Sheet of

105-B79531-00A

D

1

4 12Friday, August 29, 2008

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

0

Page 5

1

2

3

4

5

6

7

8

AG12

AH12

C37

C35

A35

E34

G32

D33

F32

E32

D31

F30

C30

A30

F28

C28

A28

E28

D27

F26

C26

A26

F24

C24

A24

E24

C22

A22

F22

D21

A20

F20

D19

E18

C18

A18

F18

D17

A16

F16

D15

E14

F14

D13

F12

A12

D11

F10

A10

C10

G13

H13

J13

H11

G10

G8

K9

K10

G9

A8

C8

E8

A6

C6

E6

A5

L18

L20

L27

N12

M12

M27

U1C

DQA_0

DQA_1

DQA_2

DQA_3

DQA_4

DQA_5

DQA_6

DQA_7

DQA_8

DQA_9

DQA_10

DQA_11

DQA_12

DQA_13

DQA_14

DQA_15

DQA_16

DQA_17

DQA_18

DQA_19

DQA_20

DQA_21

DQA_22

DQA_23

DQA_24

DQA_25

DQA_26

DQA_27

DQA_28

DQA_29

DQA_30

DQA_31

DQA_32

DQA_33

DQA_34

DQA_35

DQA_36

DQA_37

DQA_38

DQA_39

DQA_40

DQA_41

DQA_42

DQA_43

DQA_44

DQA_45

DQA_46

DQA_47

DQA_48

DQA_49

DQA_50

DQA_51

DQA_52

DQA_53

DQA_54

DQA_55

DQA_56

DQA_57

DQA_58

DQA_59

DQA_60

DQA_61

DQA_62

DQA_63

MVREFDA

MVREFSA

NC_MEM_CALRN0

NC_MEM_CALRN1

NC_MEM_CALRN2

MEM_CALRP1

NC_MEM_CALRP0

NC_MEM_CALRP2

216-0729012-00

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13/BA2

MAA_14/BA0

MAA_15/BA1

DQMA_0

DQMA_1

DQMA_2

DQMA_3

DQMA_4

DQMA_5

DQMA_6

MEMORY INTERFACE A

DQMA_7

QSA_0/RDQSA_0

QSA_1/RDQSA_1

QSA_2/RDQSA_2

QSA_3/RDQSA_3

QSA_4/RDQSA_4

QSA_5/RDQSA_5

QSA_6/RDQSA_6

QSA_7/RDQSA_7

QSA_0B/WDQSA_0

QSA_1B/WDQSA_1

QSA_2B/WDQSA_2

QSA_3B/WDQSA_3

QSA_4B/WDQSA_4

QSA_5B/WDQSA_5

QSA_6B/WDQSA_6

QSA_7B/WDQSA_7

ODTA0

ODTA1

CLKA0

CLKA0B

CLKA1

CLKA1B

RASA0B

RASA1B

CASA0B

CASA1B

CSA0B_0

CSA0B_1

CSA1B_0

CSA1B_1

CKEA0

CKEA1

WEA0B

WEA1B

RSVD#1

RSVD#2

RSVD#3

RSVD#5

RSVD#6

RSVD#9

RSVD#11

G24

J23

H24

J24

H26

J26

H21

G21

H19

H20

L13

G16

J16

H16

J17

H17

A32

C32

D23

E22

C14

A14

E10

D9

C34

D29

D25

E20

E16

E12

J10

D7

A34

E30

E26

C20

C16

C12

J11

F8

J21

G19

H27

G27

J14

H14

K23

K19

K20

K17

K24

K27

M13

K16

K21

J20

K26

L15

AF28

AG28

AL31

H23

J19

T8

W8

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

A_BA2

A_BA0

A_BA1

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

QSA0

QSA1

QSA2

QSA3

QSA4

QSA5

QSA6

QSA7

QSA#0

QSA#1

QSA#2

QSA#3

QSA#4

QSA#5

QSA#6

QSA#7

ODTA0

ODTA1

CLKA0

CLKA0#

CLKA1

CLKA1#

RASA0#

RASA1#

CASA0#

CASA1#

CSA0#_0

CSA1#_0

CKEA0

CKEA1

WEA0#

WEA1#

CEC_1

ODTA0 6

ODTA1 6

+1.5V_REG

R76

100R

R83

100R

+1.5V_REG

R65

100R

R69

100R

C303

100nF

C299

100nF

R77

5.11K

U1D

MDB0

C5

AA12

AD28

AK10

AL10

C3

E3

E1

F1

F3

F5

G4

H5

H6

J4

K6

K5

L4

M6

M1

M3

M5

N4

P6

P5

R4

T6

T1

U4

V6

V1

V3

Y6

Y1

Y3

Y5

AA4

AB6

AB1

AB3

AD6

AD1

AD3

AD5

AF1

AF3

AF6

AG4

AH5

AH6

AJ4

AK3

AF8

AF9

AG8

AG7

AK9

AL7

AM8

AM7

AK1

AL4

AM6

AM1

AN4

AP3

AP1

AP5

Y12

DQB_0

DQB_1

DQB_2

DQB_3

DQB_4

DQB_5

DQB_6

DQB_7

DQB_8

DQB_9

DQB_10

DQB_11

DQB_12

DQB_13

DQB_14

DQB_15

DQB_16

DQB_17

DQB_18

DQB_19

DQB_20

DQB_21

DQB_22

DQB_23

DQB_24

DQB_25

DQB_26

DQB_27

DQB_28

DQB_29

DQB_30

DQB_31

DQB_32

DQB_33

DQB_34

DQB_35

DQB_36

DQB_37

DQB_38

DQB_39

DQB_40

DQB_41

DQB_42

DQB_43

DQB_44

DQB_45

DQB_46

DQB_47

DQB_48

DQB_49

DQB_50

DQB_51

DQB_52

DQB_53

DQB_54

DQB_55

DQB_56

DQB_57

DQB_58

DQB_59

DQB_60

DQB_61

DQB_62

DQB_63

MVREFDB

MVREFSB

TESTEN

CLKTESTA

CLKTESTB

216-0729012-00

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

TEST_MCLK

TEST_YCLK

R80

R79

22mil

4.7K

4.7K

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_12

MAB_13/BA2

MAB_14/BA0

MAB_15/BA1

DQMB_0

DQMB_1

DQMB_2

DQMB_3

DQMB_4

DQMB_5

DQMB_6

MEMORY INTERFACE B

DQMB_7

QSB_0/RDQSB_0

QSB_1/RDQSB_1

QSB_2/RDQSB_2

QSB_3/RDQSB_3

QSB_4/RDQSB_4

QSB_5/RDQSB_5

QSB_6/RDQSB_6

QSB_7/RDQSB_7

QSB_0B/WDQSB_0

QSB_1B/WDQSB_1

QSB_2B/WDQSB_2

QSB_3B/WDQSB_3

QSB_4B/WDQSB_4

QSB_5B/WDQSB_5

QSB_6B/WDQSB_6

QSB_7B/WDQSB_7

ODTB0

ODTB1

CLKB0

CLKB0B

CLKB1

CLKB1B

RASB0B

RASB1B

CASB0B

CASB1B

CSB0B_0

CSB0B_1

CSB1B_0

CSB1B_1

CKEB0

CKEB1

WEB0B

WEB1B

DRAM_RST

P8

T9

P9

N7

N8

N9

U9

U8

Y9

W9

AC8

AC9

AA7

AA8

Y8

AA9

H3

H1

T3

T5

AE4

AF5

AK6

AK5

F6

K3

P3

V5

AB5

AH1

AJ9

AM5

G7

K1

P1

W4

AC4

AH3

AJ8

AM3

T7

W7

L9

L8

AD8

AD7

T10

Y10

W10

AA10

P10

L10

AD10

AC10

U10

AA11

N10

AB11

AH11

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

B_BA2

B_BA0

B_BA1

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

QSB0

QSB1

QSB2

QSB3

QSB4

QSB5

QSB6

QSB7

QSB#0

QSB#1

QSB#2

QSB#3

QSB#4

QSB#5

QSB#6

QSB#7

ODTB0

ODTB1

CLKB0

CLKB0#

CLKB1

CLKB1#

RASB0#

RASB1#

CASB0#

CASB1#

CSB0#_0

CSB1#_0

CKEB0

CKEB1

WEB0#

WEB1#

C302

10nF

RASB0#7

RASB1#7

CASB0#7

CASB1#7

WEB0#7

WEB1#7

CSB0#_07

CSB1#_07

CKEB07

CKEB17

CLKB0#7

CLKB1#7

QSB#[7..0]7

QSB[7..0]7

DQMB#[7..0]7

MDB[63..0]7

ODTB0 7

ODTB1 7

R81

R82

4.7KC301

4.7KTP12

+1.5V_REG

MAB[12..0]7

B_BA07

B_BA17

B_BA27

DRAM_RST 6,7

RASB0#

RASB1#

CASB0#

CASB1#

WEB0#

WEB1#

CSB0#_0

CSB1#_0

CKEB0

CKEB1

CLKB0

CLKB07

CLKB0#

CLKB1

CLKB17

CLKB1#

QSB#[7..0]

QSB[7..0]

DQMB#[7..0]

MDB[63..0]

MAB[12..0]

B_BA0

B_BA1

B_BA2

A A

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

R67 243R

R70 243R

R68 243R

R71 243R

R73 243R

R75 243R

R72

100R

R78

100R

QSA#[7..0]

QSA[7..0]

DQMA#[7..0]

MDA[63..0]

MAA[12..0]

+1.5V_REG

R64

100R

R66

100R

100nF

RASA0#

RASA1#

CASA0#

CASA1#

WEA0#

WEA1#

CKEA0

CKEA1

CSA0#_0

CSA1#_0

CLKA0

CLKA0#

CLKA1

CLKA1#

A_BA0

A_BA1

A_BA2

C298

100nF

+1.5V_REG

RASA0#6

RASA1#6

CASA0#6

CASA1#6

WEA0#6

WEA1#6

CKEA06

CKEA16

CSA0#_06

CSA1#_06

CLKA06

CLKA0#6

CLKA16

CLKA1#6

QSA#[7..0]6

QSA[7..0]6

B B

C C

DQMA#[7..0]6

MDA[63..0]6

MAA[12..0]6

+1.5V_REG

A_BA06

A_BA16

A_BA26

HDMI_CEC_18

D D

1

HDMI_CEC CEC_1

DNI, For RV8xx Only

R4200R

2

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RH M92/M96 M package MXM3.0 DDR3

Size Document Number Rev

C

3

4

5

6

Date: Sheet of

7

105-B79531-00A

5 12Thursday, August 28, 2008

8

0

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

Page 6

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

DQMA#0

DQMA#1

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

QSA0

QSA1

QSA2

QSA3

QSA4

QSA5

QSA6

QSA7

QSA#0

QSA#1

QSA#2

QSA#3

QSA#4

QSA#5

QSA#6

QSA#7

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

R221

56R

402

R222

56R

402

R223

56R

402

R224

56R

402

5

5

Should be 240

Ohms +-1%

C499

10nF

402

C500

10nF

402

VREFC_U20

VREFD_U20

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

A_BA05

A_BA25

CLKA05

CLKA0#5

CKEA05

ODTA05

CSA0#_05

RASA0#5

CASA0#5

WEA0#5

QSA2

QSA0

DQMA#2

DQMA#0

QSA#2

QSA#0

R217

243R

U20

M8

H1

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

M7

M2

N8

M3

J7

K7

K9

K1

L2

J3

K3

L3

F3

C7

E7

D3

G3

B7

T2

L8

J1

L1

J9

L9

23E22387MNG8

+1.5V_REG

R201

4.99K

R202

4.99K

+1.5V_REG

R209

4.99K

4.99K

VREFCA

VREFDQ

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC

A13

A14

A15

BA0

BA1

BA2

CK

CK

CKE

ODT

CS

RAS

CAS

WE

DQSL

DQSU

DML

DMU

DQSL

DQSU

RESET

ZQ

NC#J1

NC#L1

NC#J9

NC#L9

100-BALL

SDRAM DDR3

VDDQ#A1

VDDQ#A8

VDDQ#C1

VDDQ#C9

VDDQ#D2

VDDQ#E9

VDDQ#F1

VDDQ#H2

VDDQ#H9

VSSQ#G1

VSSQ#G9

VREFC_U20

C413

100nF

VREFD_U20

C486

100nF

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD#B2

VDD#D9

VDD#G7

VDD#K2

VDD#K8

VDD#N1

VDD#N9

VDD#R1

VDD#R9

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#J2

VSS#J8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

VSSQ#E8

VSSQ#F9

+1.5V_REG

+1.5V_REG

MDA[63..0]5

D D

C C

MAA[12..0]5

DQMA#[7..0]5

B B

QSA[7..0]5

QSA#[7..0]5

CLKA05

CLKA0#5

A A

CLKA15

CLKA1#5

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

C406

1uF_6.3V

C490

2.2UF_2.5V

MDA20

MDA17

MDA21

MDA18

MDA23

MDA16

MDA22

MDA19

MDA0

MDA4

MDA1

MDA6

MDA3

MDA7

MDA2

MDA5

C407

1uF_6.3V

4

10uF_6.3V

4

3

CHANNEL A: 256MB/512MB DDR3

VREFC_U21

VREFD_U21

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

+1.5V_REG

+1.5V_REG

C408

1uF_6.3V

C492

Should be 240

Ohms +-1%

C409

1uF_6.3V

C493

10uF_6.3V

C410

1uF_6.3V

402402

C494

10uF_6.3V

A_BA05

A_BA15A_BA15

A_BA25

CLKA05

CLKA0#5

CKEA05

ODTA05

CSA0#_05

RASA0#5

CASA0#5

WEA0#5

QSA3

QSA1

DQMA#3

DQMA#1

QSA#3

QSA#1

R218

243R

+1.5V_REG

C431

1uF_6.3V

U21

M8

VREFCA

H1

VREFDQ

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC

T3

A13

T7

A14

M7

A15

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE

K1

ODT

L2

CS

J3

RAS

K3

CAS

L3

WE

F3

DQSL

C7

DQSU

E7

DML

D3

DMU

G3

DQSL

B7

DQSU

T2

RESET

L8

ZQ

J1

NC#J1

L1

NC#L1

J9

NC#J9

L9

NC#L9

23E22387MNG8

+1.5V_REG

+1.5V_REG

100-BALL

SDRAM DDR3

R203

4.99K

R204

4.99K

R211

4.99K

R212

4.99KR210

C432

1uF_6.3V

VDD#B2

VDD#D9

VDD#G7

VDD#K2

VDD#K8

VDD#N1

VDD#N9

VDD#R1

VDD#R9

VDDQ#A1

VDDQ#A8

VDDQ#C1

VDDQ#C9

VDDQ#D2

VDDQ#E9

VDDQ#F1

VDDQ#H2

VDDQ#H9

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

VSSQ#E8

VSSQ#F9

VSSQ#G1

VSSQ#G9

VREFC_U21

C438

100nF

VREFD_U21

C487

100nF

C433

1uF_6.3V

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VSS#J2

VSS#J8

MDA31

E3

MDA24

F7

MDA29

F2

MDA26

F8

MDA28

H3

MDA27

H8

MDA30

G2

MDA25

H7

MDA15

D7

MDA10

C3

MDA14

C8

MDA11

C2

MDA12

A7

MDA8

A2

MDA13

B8

MDA9

A3

+1.5V_REG +1.5V_REG

B2

D9

G7

K2

K8

N1

N9

R1

R9

+1.5V_REG

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

C435

C434

1uF_6.3V

1uF_6.3V

3

Should be 240

Ohms +-1%

DRAM_RST5,7DRAM_RST5,7DRAM_RST5,7

+1.5V_REG

C495

10uF_6.3V

VREFC_U22

VREFD_U22

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

A_BA05

A_BA15

A_BA25

CLKA15

CLKA1#5

CKEA15

ODTA15

CSA1#_05

RASA1#5

CASA1#5

WEA1#5

QSA4

QSA5

DQMA#4

DQMA#5

QSA#4

QSA#5

R219

243R

+1.5V_REG

C456

1uF_6.3V

10uF_6.3V

C496

+1.5V_REG

R205

4.99K

R206

4.99K

+1.5V_REG

R213

4.99K

R214

4.99K

C457

1uF_6.3V

402 402402402 402402 402402 402402 402 402

10uF_6.3V

U22

M8

H1

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

M7

M2

N8

M3

J7

K7

K9

K1

L2

J3

K3

L3

F3

C7

E7

D3

G3

B7

T2

L8

J1

L1

J9

L9

23E22387MNG8

VREFC_U22

VREFD_U22

C497

VREFCA

VREFDQ

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC

A13

A14

A15

BA0

BA1

BA2

CK

CK

CKE

ODT

CS

RAS

CAS

WE

DQSL

DQSU

DML

DMU

DQSL

DQSU

RESET

ZQ

NC#J1

NC#L1

NC#J9

NC#L9

100-BALL

SDRAM DDR3

C463

100nF

C488

100nF

C458

1uF_6.3V

10uF_6.3V

C498

2

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD#B2

VDD#D9

VDD#G7

VDD#K2

VDD#K8

VDD#N1

VDD#N9

VDD#R1

VDD#R9

VDDQ#A1

VDDQ#A8

VDDQ#C1

VDDQ#C9

VDDQ#D2

VDDQ#E9

VDDQ#F1

VDDQ#H2

VDDQ#H9

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#J2

VSS#J8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

VSSQ#E8

VSSQ#F9

VSSQ#G1

VSSQ#G9

C459

1uF_6.3V

C356

10uF_6.3V

2

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

C460

1uF_6.3V

402

MDA35

MDA36

MDA32

MDA39

MDA34

MDA38

MDA33

MDA37

MDA43

MDA45

MDA40

MDA44

MDA42

MDA47

MDA41

MDA46

+1.5V_REG

+1.5V_REG

Should be 240

Ohms +-1%

1

VREFC_U23

VREFD_U23

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

A_BA05

A_BA15

A_BA25

CLKA15

CLKA1#5

CKEA15

ODTA15

CSA1#_05

RASA1#5

CASA1#5

WEA1#5

DQMA#6

DQMA#7

QSA#6

QSA#7

DRAM_RST5,7

Title

Size Document Number Rev

Date: Sheet of

U23

M8

H1

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

M7

M2

N8

M3

J7

K7

K9

K1

L2

J3

K3

L3

QSA6

F3

QSA7

C7

E7

D3

G3

B7

T2

L8

R220

243R

J1

L1

J9

L9

+1.5V_REG

C481

1uF_6.3V

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

RH M92/M96 M package MXM3.0 GDDR3

C

VREFCA

VREFDQ

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC

A13

A14

A15

BA0

BA1

BA2

CK

CK

CKE

ODT

CS

RAS

CAS

WE

DQSL

DQSU

DML

DMU

DQSL

DQSU

RESET

ZQ

NC#J1

NC#L1

NC#J9

NC#L9

100-BALL

SDRAM DDR3

23E22387MNG8

C482

1uF_6.3V

402 402 402 402402

105-B79531-00A

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD#B2

VDD#D9

VDD#G7

VDD#K2

VDD#K8

VDD#N1

VDD#N9

VDD#R1

VDD#R9

VDDQ#A1

VDDQ#A8

VDDQ#C1

VDDQ#C9

VDDQ#D2

VDDQ#E9

VDDQ#F1

VDDQ#H2

VDDQ#H9

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#J2

VSS#J8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

VSSQ#E8

VSSQ#F9

VSSQ#G1

VSSQ#G9

+1.5V_REG

R207

4.99K

R208

4.99K

+1.5V_REG

R215

4.99K

R216

4.99K

C483

1uF_6.3V

1

VREFC_U23

VREFD_U23

E3

F7

F2

F8

H3

H8

G2

H7

D7

C3

C8

C2

A7

A2

B8

A3

B2

D9

G7

K2

K8

N1

N9

R1

R9

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

C448

100nF

C489

100nF

C484

1uF_6.3V

MDA51

MDA52

MDA49

MDA53

MDA48

MDA54

MDA50

MDA55

MDA63

MDA59

MDA62

MDA56

MDA60

MDA57

MDA61

MDA58

6 12Thursday, August 28, 2008

+1.5V_REG

C485

1uF_6.3V

0

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

Page 7

5

MDB[63..0]5

D D

C C

MAB[12..0]5

DQMB#[7..0]5

B B

QSB[7..0]5

QSB#[7..0]5

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

QSB0

QSB1

QSB2

QSB3

QSB4

QSB5

QSB6

QSB7

QSB#0

QSB#1

QSB#2

QSB#3

QSB#4

QSB#5

QSB#6

QSB#7

R317

243R

U24

M8

H1

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

M7

M2

N8

M3

J7

K7

K9

K1

L2

J3

K3

L3

F3

C7

E7

D3

G3

B7

T2

L8

J1

L1

J9

L9

23E22387MNG8

+1.5V_REG

R301

4.99K

VREFC_U24

R302

4.99K

+1.5V_REG

R309

4.99K

R310

4.99K

VREFCA

VREFDQ

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC

A13

A14

A15

BA0

BA1

BA2

CK

CK

CKE

ODT

CS

RAS

CAS

WE

DQSL

DQSU

DML

DMU

DQSL

DQSU

RESET

ZQ

NC#J1

NC#L1

NC#J9

NC#L9

100-BALL

SDRAM DDR3

VDDQ#A1

VDDQ#A8

VDDQ#C1

VDDQ#C9

VDDQ#D2

VDDQ#E9

VDDQ#F1

VDDQ#H2

VDDQ#H9

VSSQ#G1

VSSQ#G9

C513

100nF

C588

100nF

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD#B2

VDD#D9

VDD#G7

VDD#K2

VDD#K8

VDD#N1

VDD#N9

VDD#R1

VDD#R9

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#J2

VSS#J8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

VSSQ#E8

VSSQ#F9

VREFC_U24

VREFD_U24

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

B_BA05

B_BA15

B_BA25

CLKB05

CLKB0#5

CKEB05

ODTB05

CSB0#_05

RASB0#5

CASB0#5

WEB0#5

QSB3

QSB1

DQMB#3

DQMB#1

QSB#3

QSB#1

DRAM_RST5,6 DRAM_RST5,6

Should be 240

Ohms +-1%

4

3

2

1

CHANNEL B: 256MB/512MB DDR3

R320

243R

U27

M8

H1

N3

P7

P3

N2

P8

P2

R8

R2

T8

R3

L7

R7

N7

T3

T7

M7

M2

N8

M3

J7

K7

K9

K1

L2

J3

K3

L3

F3

C7

E7

D3

G3

B7

T2

L8

J1

L1

J9

L9

23E22387MNG8

R307

4.99K

R308

4.99K

+1.5V_REG

R315

4.99K

R316

4.99K

VREFCA

VREFDQ

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC

A13

A14

A15

BA0

BA1

BA2

CK

CK

CKE

ODT

CS

RAS

CAS

WE

DQSL

DQSU

DML

DMU

DQSL

DQSU

RESET

ZQ

NC#J1

NC#L1

NC#J9

NC#L9

100-BALL

SDRAM DDR3

VREFC_U27

VREFD_U27

VDDQ#A1

VDDQ#A8

VDDQ#C1

VDDQ#C9

VDDQ#D2

VDDQ#E9

VDDQ#F1

VDDQ#H2

VDDQ#H9

VSSQ#G1

VSSQ#G9

C587

100nF

C591

100nF

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD#B2

VDD#D9

VDD#G7

VDD#K2

VDD#K8

VDD#N1

VDD#N9

VDD#R1

VDD#R9

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#J2

VSS#J8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

VSSQ#E8

VSSQ#F9

MDB51

E3

MDB52

F7

MDB49

F2

MDB55

F8

MDB48

H3

MDB54

H8

MDB50

G2

MDB53

H7

MDB63

D7

MDB59

C3

MDB62

C8

MDB56

C2

MDB60

A7

MDB57

A2

MDB61

B8

MDB58

A3

+1.5V_REG

B2

D9

G7

K2

K8

N1

N9

R1

R9

+1.5V_REG

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

U26

M8

VREFCA

H1

VREFDQ

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC

T3

A13

T7

A14

M7

A15

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE

K1

VDDQ#A1

ODT

L2

CS

VDDQ#A8

J3

RAS

VDDQ#C1

K3

CAS

VDDQ#C9

L3

WE

VDDQ#D2

VDDQ#E9

VDDQ#F1

F3

DQSL

VDDQ#H2

C7

DQSU

VDDQ#H9

E7

DML

D3

DMU

G3

DQSL

B7

DQSU

T2

RESET

L8

R319

243R

ZQ

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

J1

NC#J1

VSSQ#E8

L1

NC#L1

VSSQ#F9

J9

NC#J9

VSSQ#G1

L9

VSSQ#G9

NC#L9

100-BALL

SDRAM DDR3

23E22387MNG8

+1.5V_REG +1.5V_REG

R305

4.99K

VREFC_U26

R306

4.99K

+1.5V_REG

R313

4.99K

VREFD_U26

R314

4.99K

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD#B2

VDD#D9

VDD#G7

VDD#K2

VDD#K8

VDD#N1

VDD#N9

VDD#R1

VDD#R9

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#J2

VSS#J8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

C563

100nF

C590

100nF

MDB34

E3

MDB37

F7

MDB32

F2

MDB39

F8

MDB36

H3

MDB38

H8

MDB33

G2

MDB35

H7

MDB43

D7

MDB45

C3

MDB42

C8

MDB44

C2

MDB40

A7

MDB47

A2

MDB41

B8

MDB46

A3

+1.5V_REG

B2

D9

G7

K2

K8

N1

N9

R1

R9

+1.5V_REG

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

Should be 240

Ohms +-1%

VREFC_U27

VREFD_U27

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

B_BA05

B_BA15

B_BA25

CLKB15

CLKB1#5

CKEB15

ODTB15

CSB1#_05

RASB1#5

CASB1#5

WEB1#5

QSB6

QSB7

DQMB#6

DQMB#7

QSB#6

QSB#7

R318

243R

U25

M8

VREFCA

H1

VREFDQ

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC

T3

A13

T7

A14

M7

A15

M2

BA0

N8

BA1

M3

BA2

J7

CK

K7

CK

K9

CKE

K1

ODT

L2

CS

J3

RAS

K3

CAS

L3

WE

F3

DQSL

C7

DQSU

E7

DML

D3

DMU

G3

DQSL

B7

DQSU

T2

RESET

L8

ZQ

J1

NC#J1

L1

NC#L1

J9

NC#J9

L9

NC#L9

23E22387MNG8

100-BALL

SDRAM DDR3

+1.5V_REG

R303

4.99K

R304

4.99K

+1.5V_REG

R311

4.99K

R312

4.99K

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

VDD#B2

VDD#D9

VDD#G7

VDD#K2

VDD#K8

VDD#N1

VDD#N9

VDD#R1

VDD#R9

VDDQ#A1

VDDQ#A8

VDDQ#C1

VDDQ#C9

VDDQ#D2

VDDQ#E9

VDDQ#F1

VDDQ#H2

VDDQ#H9

VSS#A9

VSS#B3

VSS#E1

VSS#G8

VSS#J2

VSS#J8

VSS#M1

VSS#M9

VSS#P1

VSS#P9

VSS#T1

VSS#T9

VSSQ#B1

VSSQ#B9

VSSQ#D1

VSSQ#D8

VSSQ#E2

VSSQ#E8

VSSQ#F9

VSSQ#G1

VSSQ#G9

VREFC_U25

C538

100nF

VREFD_U25VREFD_U24

C589

100nF

MDB20

E3

MDB18

F7

MDB22

F2

MDB16

F8

MDB21

H3

MDB17

H8

MDB23

G2

MDB19

H7

MDB1

D7

MDB7

C3

MDB0

C8

MDB4

C2

MDB3

A7

MDB6

A2

MDB2

B8

MDB5

A3

+1.5V_REG

B2

D9

G7

K2

K8

N1

N9

R1

R9

+1.5V_REG

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

Should be 240

Ohms +-1%

MDB31

E3

MDB24

F7

MDB30

F2

MDB26

F8

MDB28

H3

MDB27

H8

MDB29

G2

MDB25

H7

MDB15

D7

MDB10

C3

MDB14

C8

MDB11

C2

MDB12

A7

MDB8

A2

MDB13

B8

MDB9

A3

+1.5V_REG

B2

D9

G7

K2

K8

N1

N9

R1

R9

+1.5V_REG

A1

A8

C1

C9

D2

E9

F1

H2

H9

A9

B3

E1

G8

J2

J8

M1

M9

P1

P9

T1

T9

B1

B9

D1

D8

E2

E8

F9

G1

G9

Should be 240

Ohms +-1%

VREFC_U25

VREFD_U25

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

B_BA05

B_BA15

B_BA25

CLKB05

CLKB0#5

CKEB05

ODTB05

CSB0#_05

RASB0#5

CASB0#5

WEB0#5

QSB2

QSB0

DQMB#2

DQMB#0

QSB#2

QSB#0

VREFC_U26

VREFD_U26

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

B_BA05

B_BA15

B_BA25

CLKB15

CLKB1#5

CKEB15

ODTB15

CSB1#_05

RASB1#5

CASB1#5

WEB1#5

QSB4

QSB5

DQMB#4

DQMB#5

QSB#4

QSB#5

DRAM_RST5,6 DRAM_RST5,6

CLKB05

A A

CLKB0#5

CLKB15

CLKB1#5

R321

56R

402

R322

56R

402 402

R323

56R

402

R324

56R

402 402

5

C599

10nF

C600

10nF

+1.5V_REG

C506

1uF_6.3V

402

C511

10uF_6.3V

C507

1uF_6.3V

1uF_6.3V

402 402 402

C592

C512

2.2UF_2.5V

10uF_6.3V

C509

1uF_6.3V

C510

1uF_6.3V

4

+1.5V_REG +1.5V_REG

C531

1uF_6.3V

C532

1uF_6.3V

C533

1uF_6.3V

C534

1uF_6.3V

C535

1uF_6.3V

3

+1.5V_REG+1.5V_REG

C595

10uF_6.3V

+1.5V_REG

C556

1uF_6.3V

402 402

C596

10uF_6.3V

C558

C557

1uF_6.3V

1uF_6.3VC508

402402402402402402 402 402402402402

C680

10uF_6.3V

C559

1uF_6.3V

2

C560

1uF_6.3V

C580

1uF_6.3V

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RH M92/M96 M package MXM3.0 GDDR3

Size Document Number Rev

C

Date: Sheet of

C582

C581

1uF_6.3V

1uF_6.3V

105-B79531-00A

1

C583

1uF_6.3V

C584

1uF_6.3V

402

7 12Thursday, August 28, 2008

0

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

Page 8

5

PLACE CAPS ON THIS PAGE AS CLOSE TO CONNECTOR AS POSSIBLE

G_PWR_SRC

VDDR3VDDR3

R547

R545

10K

GPIO02,9

GPIO12,9

D D

GPIO92,9

C C

B B

10K

6

Q80A

Q80B

2

2N7002

2N7002

DNI

DNI

1

Q81

2N7002E

DNI

STRAP OPTIONS FROM MOTEHRBOARD DNI

VGA_RED

VGA_RED2

VGA_GRN

VGA_GRN2

VGA_BLU

VGA_BLU2

PCIE_REFCLKP

PCIE_REFCLKP1

PCIE_REFCLKN

PCIE_REFCLKN1

PCIE_RXP[15..0]

PCIE_RXP[15..0]1

PCIE_RXN[15..0]

PCIE_RXN[15..0]1

PCIE_TXP[15..0]

PCIE_TXP[15..0]1

PCIE_TXN[15..0]

PCIE_TXN[15..0]1

RUNPWROK

RUNPWROK10,11

TXOUT_L0-

TXOUT_L0-2

TXOUT_L0+

TXOUT_L0+2

TXOUT_L1-