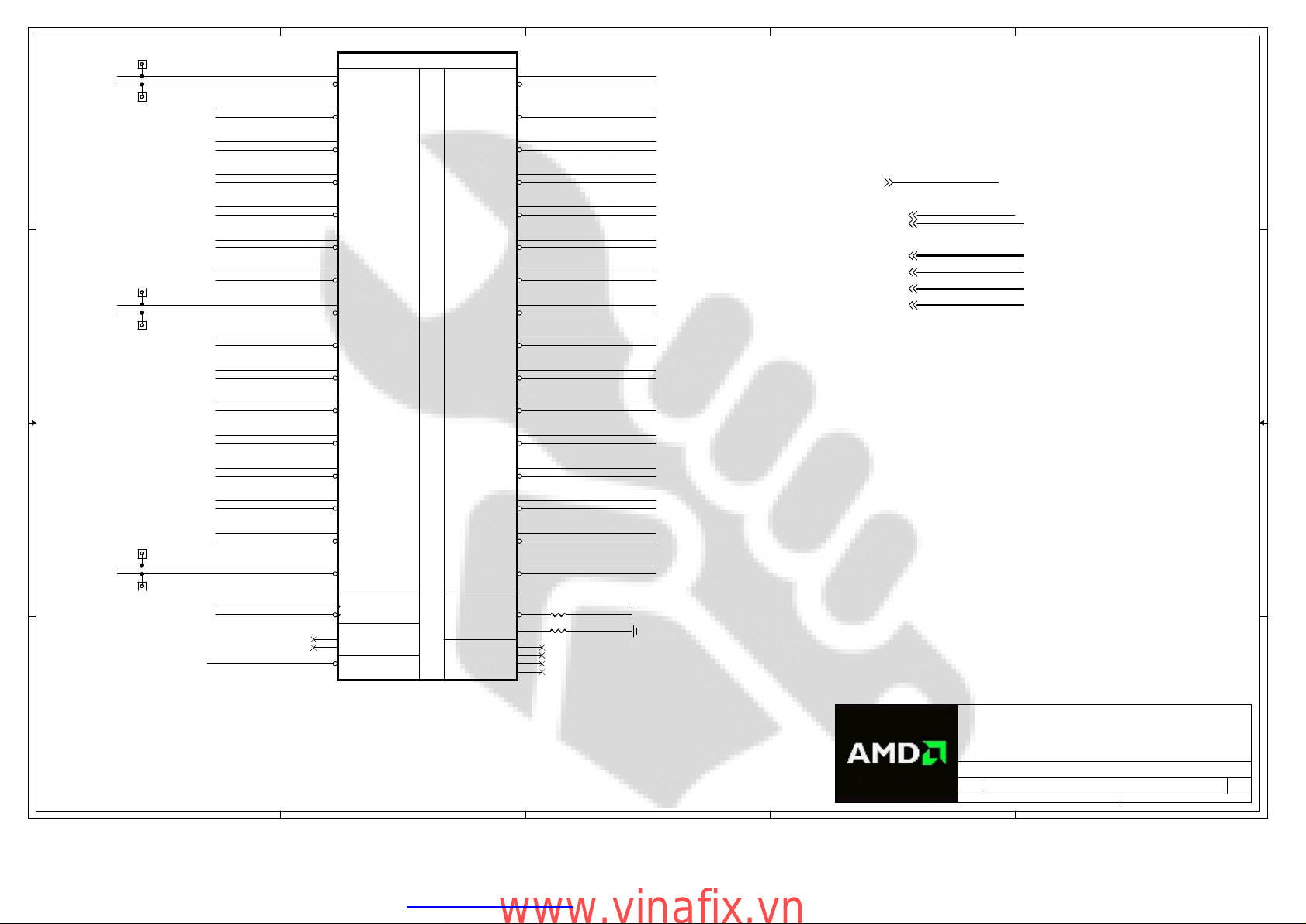

Page 1

5

TP1

TP1

35mil

35mil

PCIE_RXP0

PCIE_RXN0

35mil

35mil

TP2

TP2

D D

TP3

TP3

35mil

35mil

C C

B B

35mil

35mil

TP4

TP4

TP5

TP5

TP_22mil_SM_top

TP_22mil_SM_top

TP_22mil_SM_top

TP_22mil_SM_top

TP6

TP6

PCIE_RXP1

PCIE_RXN1

PCIE_RXP2

PCIE_RXN2

PCIE_RXP3

PCIE_RXN3

PCIE_RXP4

PCIE_RXN4

PCIE_RXP5

PCIE_RXN5

PCIE_RXP6

PCIE_RXN6

PCIE_RXP7

PCIE_RXN7

PCIE_RXP8

PCIE_RXN8

PCIE_RXP9

PCIE_RXN9

PCIE_RXP10

PCIE_RXN10

PCIE_RXP11

PCIE_RXN11

PCIE_RXP12

PCIE_RXN12

PCIE_RXP13

PCIE_RXN13

PCIE_RXP14

PCIE_RXN14

PCIE_RXP15

PCIE_RXN15

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_RST#

AK33

AJ33

AJ35

AJ34

AH35

AH34

AG35

AG34

AF33

AE33

AE35

AE34

AD35

AD34

AC35

AC34

AB33

AA33

AA35

AA34

Y35

Y34

W35

W34

V33

U33

U35

U34

T35

T34

R35

R34

AJ31

AJ30

AK35

AK34

AM32

U1A

U1A

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

PCIE_REFCLKP

PCIE_REFCLKN

NC_SMB_DATA

NC_SMBCLK

PERSTB

M86-M A11

M86-M A11

Clock

Clock

SM Bus

SM Bus

4

PART 1 OF 7

PART 1 OF 7

P

P

C

C

I

I

-

E

E

X

X

P

P

R

R

E

E

S

S

S

S

I

I

N

N

T

T

E

E

R

R

F

F

A

A

C

C

E

E

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Calibration

Calibration

PCIE_CALRN

PCIE_CALRP

NC_DRAM_0

NC_DRAM_1

NC_AC_BATT

NC_FAN_TACH

AG31

AG30

AF31

AF30

AF28

AF27

AD31

AD30

AD28

AD27

AB31

AB30

AB28

AB27

AA31

AA30

AA28

AA27

W31

W30

W28

W27

V31

V30

V28

V27

U31

U30

U28

U27

R31

R30

AG26

AJ27

AF3

AG9

AK29

AK14

PCIE_TXP0

PCIE_TXN0

PCIE_TXP1

PCIE_TXN1

PCIE_TXP2

PCIE_TXN2

PCIE_TXP3

PCIE_TXN3

PCIE_TXP4

PCIE_TXN4

PCIE_TXP5

PCIE_TXN5

PCIE_TXP6

PCIE_TXN6

PCIE_TXP7

PCIE_TXN7

PCIE_TXP8

PCIE_TXN8

PCIE_TXP9

PCIE_TXN9

PCIE_TXP10

PCIE_TXN10

PCIE_TXP11

PCIE_TXN11

PCIE_TXP12

PCIE_TXN12

PCIE_TXP13

PCIE_TXN13

PCIE_TXP14

PCIE_TXN14

PCIE_TXP15

PCIE_TXN15

R1

2.0KR12.0K

R2

1.27KR21.27K

PCIE_VDDC

3

PCIE_RST#7

PCIE_RXP[15..0]7

PCIE_RXN[15..0]7

PCIE_TXP[15..0]7

PCIE_TXN[15..0]7

2

PCIE_RST#

PCIE_REFCLKP7

PCIE_REFCLKN7

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_RXP[15..0]

PCIE_RXN[15..0]

PCIE_TXP[15..0]

PCIE_TXN[15..0]

1

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

A A

5

4

3

2

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

M8X GDDR3

105-B37631-00B

105-B37631-00B

105-B37631-00B

1 11Tuesday, October 16, 2007

1 11Tuesday, October 16, 2007

1 11Tuesday, October 16, 2007

1

0

0

0

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

Page 2

5

4

3

32

Q29

Q29

+5VRUN

1

2N7002_NL

2N7002_NL

R1000

R1000

100K

100K

2

32

Q30

Q30

+5VRUN

1

2N7002_NL

2N7002_NL

R1001

R1001

100K

100K

1

D D

VHAD010

PSYNC10

SCS#10

MEM_ID310

MEM_ID210

THERM_SDAT10

THERM_SCLK10

DVI_HPD27

POW_SW09

R1072 0RR1072 0R

DVI_HPD37

POW_SW19

DVALID10

MEM_ID010

MEM_ID110

GPIO010

GPIO110

GPIO210

GPIO310

GPIO510

SCLK10

GPIO1110

GPIO1210

GPIO1310

OTEMP#10

BB_ENA3

+3VRUN

R5

R6

4.7KR54.7K

4.7KR64.7K

I2C_DAT7

(1.8V @ 400MA LVDDR)

B10 30R_1AB10 30R_1A

1.8V_REG

BLM15BD121SN1

BLM15BD121SN1

L35

1.8V_REG

(1.8V @ 70MA LVDDC)

C C

L35

C393

C393

10uF_6.3V

10uF_6.3V

(1.8V @ 20MA LPVDD)

BLM15BD121SN1

BLM15BD121SN1

1.8V_REG

B B

( .95V-1.1V @ 345MA MPVDD)

VDD_CORE

PCIE_VDDC

(DPLL_VDDC 1.1V @ 100 MA)

A A

CTFb7,10

(1.8V @ 40MA PCIE_PVDD)

L27 30R_1AL27 30R_1A

BLM15BD121SN1

BLM15BD121SN1

NS2

NS2

1 2

NS_VIA

NS_VIA

2N7002_NL

2N7002_NL

1.8V_REG

Q31

Q31

1.8V_REG

L24

L24

LVDDR

C239

C239

C240

C240

10uF_6.3V

10uF_6.3V

1uF_6.3V

1uF_6.3V

C394

C394

C395

C395

100nF

100nF

1uF_6.3V

1uF_6.3V

L11

L11

C254

C254

C255

C255

10uF_6.3V

10uF_6.3V

1uF_6.3V

1uF_6.3V

+3VRUN

R1036

R1036

100K

100K

32

1

(1.8V @ 40MA DPLL_PVDD)

BLM15BD121SN1

BLM15BD121SN1

L16

L16

BLM15BD121SN1

BLM15BD121SN1

DPLL_VDDC

C399

C399

C282

C282

10uF_6.3V

10uF_6.3V

1uF_6.3V

1uF_6.3V

LPVDD

R1037

R1037

100K

100K

1 2

L14

L14

1 2

NS7

NS7

NS_VIA

NS_VIA

NS4

NS4

NS_VIA

NS_VIA

C241

C241

AJ26

100nF

100nF

AH26

AK27

AL27

AM24

AN28

AN21

AN24

AN25

AM22

AP21

AP26

AM27

AR21

AR26

AM26

AJ22

AJ24

AL22

AK22

C256

C256

100nF

100nF

C260

C260

1uF_6.3V

1uF_6.3V

C263

C263

1uF_6.3V

1uF_6.3V

C287

C287

10uF_6.3V

10uF_6.3V

C283

C283

100nF

100nF

I2C_CLK7

U1F

U1F

PART 7 OF 7

PART 7 OF 7

GPIO810

GPIO910

PCIE_PVDD

C288

C288

1uF_6.3V

1uF_6.3V

SOUT10

DPLL_PVDD

C261

C261

10uF_6.3V

10uF_6.3V

C264

C264

10uF_6.3V

10uF_6.3V

MPVDD

SIN10

Control

Control

LVDS ch annel

LVDS ch annel

VARY_BL

DIGON

TXCLK_UP

TXCLK_UN

TXOUT_U0P

TXOUT_U0N

TXOUT_U1P

TXOUT_U1N

TXOUT_U2P

TXOUT_U2N

TXOUT_U3P

TXOUT_U3N

TXCLK_LP

TXCLK_LN

TXOUT_L0P

TXOUT_L0N

TXOUT_L1P

TXOUT_L1N

TXOUT_L2P

TXOUT_L2N

TXOUT_L3P

TXOUT_L3N

C262

C262

100nF

100nF

C265

C265

100nF

100nF

C289

C289

100nF

100nF

LVDDR_1

LVDDR_2

LVDDC_1

LVDDC_2

LVSSR_1

LVSSR_2

LVSSR_3

LVSSR_4

LVSSR_5

LVSSR_6

LVSSR_7

LVSSR_8

LVSSR_9

LVSSR_10

LVSSR_11

LVSSR_12

LVSSR_13

LVSSR_14

LPVDD

LPVSS

M86-M A11

M86-M A11

VREFG VOLTAGE DIVIDER IS

499R/249R

(VREFG = = .6V)

PLACE VREF DIVIDER

AND CAP CLOSE TO ASIC

R4 10KR4 10K

AG7

AJ6

AK24

AL24

AN27

AN26

AP27

AR27

AG24

AH24

AK26

AL26

AR22

AP22

AN23

AN22

AP23

AR23

AP24

AR24

AP25

AR25

R18

R18

499R

499R

R20

R20

249R

249R

OPT_BL_ENA7

1.8V_REG

BLON_PWM 7

FPVCC 7

TXCLK_U+ 7

TXCLK_U- 7

TXOUT_U0+ 7

TXOUT_U0- 7

TXOUT_U1+ 7

TXOUT_U1- 7

TXOUT_U2+ 7

TXOUT_U2- 7

TXOUT_U3+ 7

TXOUT_U3- 7

TXCLK_L+ 7

TXCLK_L- 7

TXOUT_L0+ 7

TXOUT_L0- 7

TXOUT_L1+ 7

TXOUT_L1- 7

TXOUT_L2+ 7

TXOUT_L2- 7

TXOUT_L3+ 7

TXOUT_L3- 7

R10 10KR10 10K

R1065 10KR1065 10K

AC_BAT7

GPIO2210

CLK_REQB*7

C1

100nFC1100nF

U1B

U1B

PART 2 OF 7

VIP_0

VIP_1

VIP_2

VIP / I2C

VIP / I2C

VIP_3

VIP_4

VIP_5

VIP_6

VIP_7

VHAD_0

VHAD_1

VPHCTL

VPCLK0

VIPCLK

PSYNC

DVALID

SDA

SCL

DVPCNTL__MVP_0

DVPCNTL__MVP_1

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPCLK

DVPDATA_0

DVPDATA_1

MULTI_GFX

MULTI_GFX

DVPDATA_2

EXTERNAL

EXTERNAL

DVPDATA_3

TMDS

TMDS

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

GPIO_0

GPIO_1

GENERAL

GENERAL

GPIO_2

PURPOSE

PURPOSE

GPIO_3

I/O

I/O

GPIO_4

GPIO_5

GPIO_6

GPIO_7_BLON

GPIO_8_ROMSO

GPIO_9_ROMSI

GPIO_10_ROMSCK

GPIO_11

GPIO_12

GPIO_13

GPIO_14_HPD2

GPIO_15_PWRCNTL_0

GPIO_16_SSIN

GPIO_17_THERMAL_INT

GPIO_18_HPD3

GPIO_19_CTF

GPIO_20_PWRCNTL_1

GPIO_21_BBEN

GPIO_22_ROMCSB

GPIO_23_CLKREQB

GPIO_24_JMODE

GPIO_25_TDI

GPIO_26_TCK

GPIO_27_TMS

GPIO_28_TDO

GEN_A

GEN_B

GEN_C

GEN_D_HPD4

GEN_E

GEN_F

GEN_G

VREFG

DPLL_PVDD

DPLL_PVSS

PCIE_PVDD

MPVDD

PLL

PLL

MPVSS

CLOCKS

CLOCKS

XTALIN

XTALOUT

DPLL_VDDC

TS_FDO

THERMAL

THERMAL

DMINUS

DPLUS

M86-M A11

M86-M A11

Y1

4

GND4

3

27MHzY127MHz

PART 2 OF 7

INTEGRATED

INTEGRATED

TMDS/DP

TMDS/DP

DAC1

DAC1

DAC2

DAC2

DDC

DDC

DP AUX

DP AUX

DDC3DATA_DP3_AUXN

DDC3CLK_DP3_AUXP

DDC4DATA_DP4_AUXN

DDC4CLK_DP4_AUXP

2

GND2

XTAL11XTAL2

TXCAM_DPA0P

TXCAP_DPA0N

TX0M_DPA1P

TX0P_DPA1N

TX1M_DPA2P

TX1P_DPA2N

TX2M_DPA3P

TX2P_DPA3N

TXCBM_DPB0P

TXCBP_DPB0N

TX3M_DPB1P

TX3P_DPB1N

TX4M_DPB2P

TX4P_DPB2N

TX5M_DPB3P

TX5P_DPB3N

DPB_VDDR_1

DPB_VDDR_2

DPA_VDDR_3

DPA_VDDR_4

DPB_VSSR_1

DPB_VSSR_2

DPB_VSSR_3

DPB_VSSR_4

DPB_VSSR_6

DPA_VSSR_5

DPA_VSSR_7

DPA_VSSR_8

DPA_VSSR_9

DPA_VSSR_10

NC_TPVDDC

NC_TPVSSC

AM12

VID_010

AL12

VID_110

AJ12

VID_210

AH12

VID_310

AM10

VID_410

AL10

VID_510

AJ10

VID_610

AH10

VID_710

AM9

AL9

AJ9

AL7

AK7

AM7

AJ7

AK6

AM6

AN8

AP8

AG1

AH3

AH2

AH1

AJ3

AJ2

AJ1

AK2

AK1

AL3

AL2

AL1

AM3

AM2

AN2

AP3

AR3

AN4

AR4

AP4

AN5

AR5

AP5

AP6

AR6

AN7

AP7

AR7

AG2

AF2

AF1

AE3

AE2

AE1

AD3

AD2

AD1

AD5

AD4

AC3

AC2

AC1

AB3

AB2

AB1

AF5

AF4

AG4

AG3

AD9

AD8

AD7

AB4

AB6

AB7

AB9

AA9

AF8

AF7

AG5

AP9

AR9

AP13

AR13

AD12

AR20

AP20

AM35

A14

B15

AR33

AP33

AG19

AG21

AK4

D-10

AM4

D+10

R9991MR999

1M

C327

C327

18pF_50V

18pF_50V

DPA_PVDD

DPA_PVSS

DPB_PVDD

DPB_PVSS

DP_CALR

HSYNC

VSYNC

AVSSQ

VDD1DI

VSS1DI

COMP

V2SYNC

H2SYNC

A2VDD

A2VDDQ

A2VSSQ

VDD2DI

VSS2DI

R2SET

DDC1DATA

DDC1CLK

DDC2DATA

DDC2CLK

C328

C328

18pF_50V

18pF_50V

DPA0P

DPA0N

DPA1P

DPA1N

DPA2P

DPA2N

DPA3P

DPA3N

DPB0P

DPB0N

DPB1P

DPB1N

DPB2P

DPB2N

DPB3P

DPB3N

DPA_VDDR

R1063150RR1063150R

DVI_DETECT 7

VGA_RED

VGA_GRN

VGA_BLU

HSYNC

VSYNC

R11 499RR11 499R

C292

C292

1uF_6.3V

1uF_6.3V

VDD1DI

TV_CR_PR 7

TV_Y_G 7

TV_COMP_B_PB 7

C397

C397

100nF

100nF

DDC1DATA 7

DDC1CLK 7

DDC2DATA 7

DDC2CLK 7

DDC3DATA 7

DDC3CLK 7

DDC4DATA 7

DDC4CLK 7

C295

C295

1uF_6.3V

1uF_6.3V

100nF

100nF

C272

C272

10uF_6.3V

10uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C291

C291

C298

C298

C398

C398

C610 180nFC610 180nF

C294

C294

10uF_6.3V

10uF_6.3V

10uF_6.3V

10uF_6.3V

C268

C268

100nF

100nF

C273

C273

100nF

100nF

1%

10uF_6.3V

10uF_6.3V

C290

C290

AN9

AN10

AR10

AP10

AR11

AP11

AR12

AP12

AR14

AP14

AR15

AP15

AR16

AP16

AR17

AP17

AM14

AL14

AH17

AG17

AN19

AN20

AP19

AR19

AN18

AP18

AR18

AN16

AN17

AN15

AN11

AN12

AN13

AN14

AG15

AH18

AG18

AG6

HPD1

AR31

R

AP31

RB

AR30

G

AP30

GB

AR29

B

AP29

BB

AN29

AN30

AN31

RSET

AR32

AVDD

AP32

AR28

AP28

AM19

R2

AL19

R2B

AM18

G2

AL18

G2B

AM17

B2

AL17

B2B

AK19

C

AK18

Y

AK17

AL15

AM15

AM21

AL21

AK21

AH22

AG22

AJ21

AM29

AL29

AJ15

AH15

AJ5

AJ4

AH14

AG14

C616 180nFC616 180nF

C611 180nFC611 180nF

C297

C297

C293

C293

100nF

100nF

R21

R21

715R

715R

499R R1002499R R1002

499R R1003499R R1003

C612 180nFC612 180nF

DPA_PVDD

C296

C296

100nF

100nF

L30 120R_450mAL30 120R_450mA

NS14 NS_VIANS14 NS_VIA

AVDD

NS3 NS_VIANS3 NS_VIA

12

*

C396

C396

NS16 NS_VIANS16 NS_VIA

1uF_6.3V

1uF_6.3V

A2VDD

C274

C274

1uF_6.3V

1uF_6.3V

L37

L37

NS5 NS_VIANS5 NS_VIA

*

C266

C266

1uF_6.3V

1uF_6.3V

499R R1004499R R1004

C617 180nFC617 180nF

C618 180nFC618 180nF

NS1 NS_VIANS1 NS_VIA

12

12

BLM15BD121SN1

BLM15BD121SN1

12

499R R1008499R R1008

499R R1006499R R1006

499R R1007499R R1007

499R R1005499R R1005

C619 180nFC619 180nF

C620 180nFC620 180nF

BLM15BD121SN1

BLM15BD121SN1

L32

L32

1.8V_REG

(1.8V @ 20MA DPA_PVDD)

12

PCIE_VDDC

1.1V@ 200 MA

VGA_RED 7

VGA_GRN 7

VGA_BLU 7

HSYNC 7,10

VSYNC 7,10

L28

L28

BLM15BD121SN1

BLM15BD121SN1

L36

L36

BLM15BD121SN1

BLM15BD121SN1

(3.3V @ 135MA A2VDD)

L21

L21

BLM15BD121SN1

BLM15BD121SN1

1.8V_REG

VDD2DI

C635

C635

C267

C267

100nF

100nF

10uF_6.3V

10uF_6.3V

499R R1009499R R1009

DPB_VDDR

1.8V_REG

(1.8V @ 100MA AVDD)

( 1.8V @ 45MA VDD1DI)

1.8V_REG

VDDR3

( 1.8V @ 100MA VDD2DI)

L19

L19

BLM15BD121SN1

BLM15BD121SN1

NS17 NS_VIANS17 NS_VIA

C613 180nFC613 180nF

C627

C627

1uF_6.3V

1uF_6.3V

C629

C629

1uF_6.3V

1uF_6.3V

12

C621 180nFC621 180nF

C614 180nFC614 180nF

C630

C630

10uF_6.3V

10uF_6.3V

1.8V_REG

499R R1010499R R1010

C615

C615

10uF_6.3V

10uF_6.3V

C631

C631

100nF

100nF

499R R1011499R R1011

C622 180nFC622 180nF

C623 180nFC623 180nF

499R R1012499R R1012

C624 180nFC624 180nF

C628

C628

100nF

100nF

NS15 NS_VIANS15 NS_VIA

499R R1014499R R1014

499R R1013499R R1013

C625 180nFC625 180nF

DPB_PVDD

NS13 NS_VIANS13 NS_VIA

L43 120R_450mAL43 120R_450mA

12

499R R1016499R R1016

499R R1017499R R1017

499R R1015499R R1015

C626 180nFC626 180nF

BLM15BD121SN1

BLM15BD121SN1

L42

L42

(1.8V @ 20MA DPB_PVDD)

12

PCIE_VDDC

1.1V@ 200 MA

1.8V_REG

DVI_CLK- 7

DVI_CLK+ 7

DVI_TX0- 7

DVI_TX0+ 7

DVI_TX1- 7

DVI_TX1+ 7

DVI_TX2- 7

DVI_TX2+ 7

DVIB_CLK- 7

DVIB_CLK+ 7

DVIB_TX0- 7

DVIB_TX0+ 7

DVIB_TX1- 7

DVIB_TX1+ 7

DVIB_TX2- 7

DVIB_TX2+ 7

5

4

3

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

M8X GDDR3

M8X GDDR3

M8X GDDR3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

105-B37631-00B

105-B37631-00B

105-B37631-00B

1

0

0

0

2 11Tuesday, October 16, 2007

2 11Tuesday, October 16, 2007

2 11Tuesday, October 16, 2007

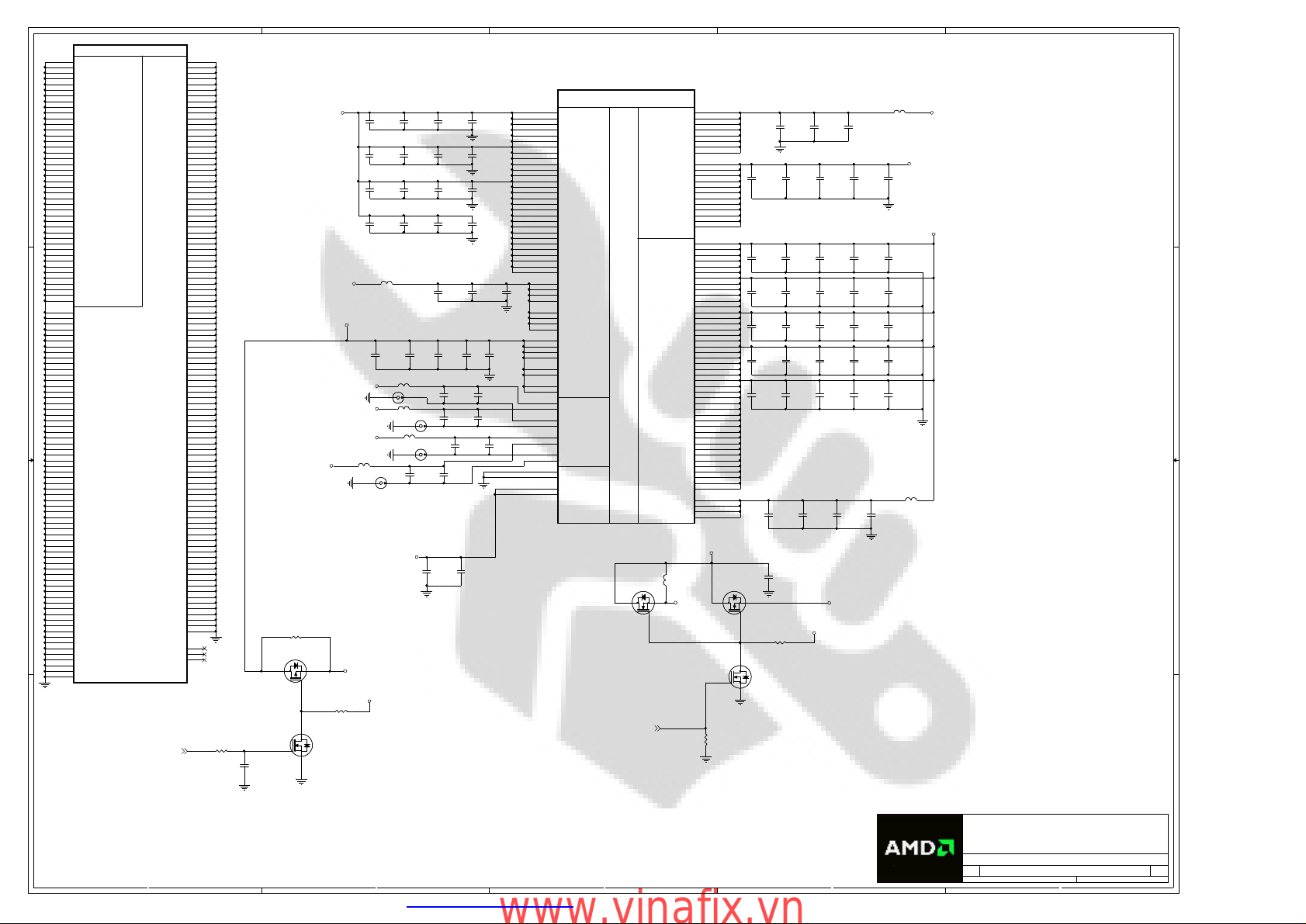

Page 3

Part 6 of 7

Part 6 of 7

CORE GND

CORE GND

5

P6

VSS_66

M9

VSS_67

M26

VSS_68

K28

VSS_69

M32

VSS_70

N14

VSS_71

N17

VSS_72

N19

VSS_73

N22

VSS_74

N33

VSS_75

N3

VSS_76

R5

PCI-Express GND

PCI-Express GND

VSS_77

U8

VSS_78

P13

VSS_79

P15

VSS_80

P18

VSS_81

P21

VSS_82

P23

VSS_83

P26

VSS_84

P29

VSS_85

P30

VSS_86

R1

VSS_87

U5

VSS_88

P9

VSS_89

R10

VSS_90

R14

VSS_91

R17

VSS_92

R19

VSS_93

R22

VSS_94

V3

VSS_95

AK9

VSS_96

U10

VSS_97

U15

VSS_98

U18

VSS_99

U21

VSS_100

U23

VSS_101

V7

VSS_102

W8

VSS_103

V10

VSS_104

V14

VSS_105

V17

VSS_106

V19

VSS_107

V22

VSS_108

V1

VSS_109

AK12

VSS_110

V9

VSS_111

W10

VSS_112

W15

VSS_113

W18

VSS_114

W21

VSS_115

W23

VSS_116

AA6

VSS_117

AA10

VSS_118

AA14

VSS_119

AA17

VSS_120

AA19

VSS_121

AA22

VSS_122

AB8

VSS_123

AB10

VSS_124

AB13

VSS_125

AB15

VSS_126

AB18

VSS_127

AB21

VSS_128

AB23

VSS_129

AC14

VSS_130

AC17

VSS_131

AC19

VSS_132

AC22

VSS_133

AF9

VSS_134

AD6

VSS_135

AB5

VSS_136

AD24

VSS_137

W5

VSS_138

AF6

VSS_139

AF14

VSS_140

AF21

VSS_141

AF22

VSS_142

AK10

VSS_143

AF17

VSS_144

AF18

VSS_145

AF19

VSS_146

AA3

VSS_147

AG12

VSS_148

AJ14

VSS_149

AH21

VSS_150

D4

VSS_151

AF15

VSS_152

AG10

VSS_153

AN6

VSS_154

AK15

VSS_155

AJ17

VSS_156

AJ18

VSS_157

AJ19

VSS_158

AF24

VSS_159

AN32

VSS_160

AK3

VSS_161

AN3

VSS_162

AR8

VSS_163

AM1

VSS_164

AK30

VSS_165

V11

VSS_166

A35

MECH_1

AR1

MECH_2

AR35

MECH_3

1.8V_REG 1.8V_REG

1.8V_REG

1.8V_REG

R654 0RR654 0R

Q1

Si2301BDSQ1Si2301BDS

23

1

32

RUNPWROK7

R26 51KR26 51K

C60

C60

100nF

100nF

Q2

1

2N7002_NLQ22N7002_NL

U1E

U1E

P33

PCIE_VSS_1

P34

PCIE_VSS_2

P35

PCIE_VSS_3

R27

PCIE_VSS_4

R28

PCIE_VSS_5

R29

PCIE_VSS_6

R32

PCIE_VSS_7

R33

PCIE_VSS_8

U29

PCIE_VSS_9

U32

PCIE_VSS_10

V29

PCIE_VSS_11

V32

PCIE_VSS_12

T33

PCIE_VSS_13

V34

PCIE_VSS_14

V35

D D

PCIE_VSS_15

W29

PCIE_VSS_16

W32

PCIE_VSS_17

W33

PCIE_VSS_18

AA29

PCIE_VSS_19

AA32

PCIE_VSS_20

AB29

PCIE_VSS_21

AB32

PCIE_VSS_22

Y33

PCIE_VSS_23

AB34

PCIE_VSS_24

AB35

PCIE_VSS_25

AC33

PCIE_VSS_26

AD29

PCIE_VSS_27

AD32

PCIE_VSS_28

AF29

PCIE_VSS_29

AF32

PCIE_VSS_30

AD33

PCIE_VSS_31

AF34

PCIE_VSS_32

AF35

PCIE_VSS_33

AG27

PCIE_VSS_34

AG29

PCIE_VSS_35

AG32

PCIE_VSS_36

AG33

PCIE_VSS_37

AJ29

PCIE_VSS_38

AJ32

PCIE_VSS_39

AH33

PCIE_VSS_40

AL34

PCIE_VSS_41

AL35

PCIE_VSS_42

AK32

PCIE_VSS_43

A2

VSS_1

A34

VSS_2

C3

VSS_3

C5

VSS_4

A4

VSS_5

C18

VSS_6

A21

VSS_7

C23

VSS_8

C C

C11

VSS_9

C13

VSS_10

C14

VSS_11

A18

VSS_12

A11

VSS_13

C26

VSS_14

C33

VSS_15

F35

VSS_16

R7

VSS_17

G10

VSS_18

F15

VSS_19

H17

VSS_20

G21

VSS_21

D29

VSS_22

A29

VSS_23

G1

VSS_24

F14

VSS_25

J15

VSS_26

E19

VSS_27

E22

VSS_28

E24

VSS_29

D7

VSS_30

G9

VSS_31

F26

VSS_32

G29

VSS_33

D33

VSS_34

M5

VSS_35

G4

VSS_36

E10

VSS_37

E12

VSS_38

F17

VSS_39

G18

VSS_40

G22

VSS_41

F30

VSS_42

J35

VSS_43

J18

VSS_44

H19

VSS_45

J21

B B

VSS_46

F7

VSS_47

J12

VSS_48

J24

VSS_49

J26

VSS_50

K30

VSS_51

J32

VSS_52

F33

VSS_53

K6

VSS_54

K9

VSS_55

K14

VSS_56

K15

VSS_57

K17

VSS_58

K18

VSS_59

K19

VSS_60

K21

VSS_61

K22

VSS_62

M28

VSS_63

K3

VSS_64

L33

VSS_65

M86-M A11

M86-M A11

A A

VDDR3

1.8V_REG

1.8V_REG

1.8V_REG

BLM15BD121SN1

BLM15BD121SN1

+3VRUN

R25 100KR25 100K

4

C2

10uF_6.3VC210uF_6.3V

C6

1uF_6.3VC61uF_6.3V

C10

C10

1uF_6.3V

1uF_6.3V

C14

C14

1uF_6.3V

1uF_6.3V

BLM15BD121SN1

BLM15BD121SN1

C632

C632

10uF_6.3V

10uF_6.3V

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

1 2

+5VRUN

NS9NS_VIA NS9NS_VIA

1 2

BLM15BD121SN1

BLM15BD121SN1

L13

L13

NS12NS_VIA NS12NS_VIA

*

+BBP

C3

10uF_6.3VC310uF_6.3V

C7

1uF_6.3VC71uF_6.3V

C11

C11

1uF_6.3V

1uF_6.3V

C15

C15

1uF_6.3V

1uF_6.3V

L34

L34

C34

C34

1uF_6.3V

1uF_6.3V

*

NS10NS_VIA NS10NS_VIA

1 2

NS11NS_VIA NS11NS_VIA

1 2

VDDRHB2

C258

C258

1uF_6.3V

1uF_6.3V

L6

L6

L9

L9

*

L10

L10

C58

C58

1uF_6.3V

1uF_6.3V

C4

10uF_6.3VC410uF_6.3V

C8

1uF_6.3VC81uF_6.3V

C12

C12

1uF_6.3V

1uF_6.3V

C16

C16

1uF_6.3V

1uF_6.3V

C299

C299

10uF_6.3V

10uF_6.3V

C35

C35

1uF_6.3V

1uF_6.3V

VDDRHA1

C243

C243

1uF_6.3V

1uF_6.3V

VDDRHA2

C249

C249

1uF_6.3V

1uF_6.3V

C259

C259

100nF

100nF

VDDRHB1

C252

C252

1uF_6.3V

1uF_6.3V

C5

10uF_6.3VC510uF_6.3V

C9

1uF_6.3VC91uF_6.3V

C13

C13

1uF_6.3V

1uF_6.3V

C17

C17

1uF_6.3V

1uF_6.3V

C300

C300

1uF_6.3V

1uF_6.3V

( 3.3V @ 50MA VDDR3)

C48

C48

C49

C49

100nF

100nF

1uF_6.3V

1uF_6.3V

C244

C244

100nF

100nF

C250

C250

100nF

100nF

C253

C253

100nF

100nF

C59

C59

1uF_6.3V

1uF_6.3V

100nF

100nF

3

U1D

U1D

D1

VDDR1_1

A8

VDDR1_2

A12

VDDR1_3

A16

VDDR1_4

A20

VDDR1_5

A24

VDDR1_6

A28

VDDR1_7

B1

VDDR1_8

H1

VDDR1_9

H35

VDDR1_10

L18

VDDR1_11

L19

VDDR1_12

L21

VDDR1_13

L22

VDDR1_14

M10

VDDR1_15

M35

VDDR1_16

P10

VDDR1_17

T1

VDDR1_18

Y1

VDDR1_19

B35

VDDR1_20

M1

VDDR1_21

D35

VDDR1_22

K10

VDDR1_23

K12

VDDR1_24

K24

VDDR1_25

K26

VDDR1_26

L14

VDDR1_27

L15

VDDR1_28

L17

VDDR1_29

AA11

AD10

AF10

AB11

AE14

AE15

AF12

AE17

AA13

VDD_CT_1

VDD_CT_2

VDD_CT_3

VDD_CT_4

R11

VDD_CT_5

R25

VDD_CT_6

U11

VDD_CT_7

U25

VDD_CT_8

VDDR3_1

VDDR3_2

VDDR3_3

VDDR3_4

AP2

VDDR4_1

AR2

VDDR4_2

AN1

VDDR5_1

AP1

VDDR5_2

A25

VDDRHA_1

A32

VDDRHA_2

B25

VSSRHA_1

B32

VSSRHA_2

B2

VDDRHB_1

L1

VDDRHB_2

C2

VSSRHB_1

L2

VSSRHB_2

W13

BBN_1

BBN_2

U13

BBP_1

V13

BBP_2

M86-M A11

M86-M A11

C301

C301

PART 5 OF 7

PART 5 OF 7

I/O I nternal

I/O I nternal

Memo ry I/O

Clo ck

Memo ry I/O

Clo ck

Back

Bias

Back

Bias

PCIE_VDDR_1

PCIE_VDDR_2

PCIE_VDDR_3

PCIE_VDDR_4

PCIE_VDDR_5

PCIE_VDDR_6

Memor y I/O

Memor y I/O

PCIE_VDDR_7

PCIE_VDDR_8

PCIE_VDDC_1

PCIE_VDDC_2

PCIE_VDDC_3

PCIE_VDDC_4

PCIE_VDDC_5

PCIE_VDDC_6

PCIE_VDDC_7

PCIE_VDDC_8

PCIE_VDDC_9

PCIE_VDDC_10

PCIE_VDDC_11

PCI- Exp res s

PCI- Exp res s

PCIE_VDDC_12

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

P

P

O

O

W

W

E

E

R

R

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

Core

Core

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

VDDC_24

VDDC_25

VDDC_26

VDDC_27

VDDC_28

VDDC_29

VDDC_30

VDDC_31

VDDC_32

VDDC_33

VDDC_34

VDDC_35

VDDC_36

VDDC_37

VDDC_38

VDDC_39

VDDC_40

VDDC_41

VDDC_42

VDDC_43

VDDC_44

VDDCI_1

VDDCI_2

VDDCI_3

VDDCI_4

(+1.8V 0R VDDC @ 120MA BBP)

L39

L39

Q18

Q18

2N7002E

2N7002E

3 2

**

A

VDD_CORE

BLM15BD121SN1

BLM15BD121SN1

1

BB_ENA2

AR34

AL33

AM33

AN33

AN34

AN35

AP34

AP35

R26

U26

V25

V26

W25

W26

AA25

AD26

AF26

AA26

AB25

AB26

N13

N15

N18

N21

N23

P14

P17

P19

P22

V18

V21

V23

W14

W17

W19

W22

AA15

AA18

AA21

AA23

AB14

AB17

AB19

AB22

AC13

AC15

AC18

AC21

AC23

AE18

AE22

AE19

AE21

R13

R15

R18

R21

R23

U14

U17

U19

U22

V15

W11

M12

M24

P11

P25

+BBP

FET BFET C

FET A

R657

R657

10K

10K

Si2301BDS

Si2301BDS

1

C402

C402

100nF

100nF

C275

C275

1uF_6.3V

1uF_6.3V

C18

C18

10uF_6.3V

10uF_6.3V

C23

C23

10uF_6.3V

10uF_6.3V

C28

C28

10uF_6.3V

10uF_6.3V

C37

C37

10uF_6.3V

10uF_6.3V

C42

C42

10uF_6.3V

10uF_6.3V

C54

C54

10uF_6.3V

10uF_6.3V

C405

C405

Q19

Q19

1uF_6.3V

1uF_6.3V

23

1

R655 100KR655 100K

32

Q20

Q20

2N7002_NL

2N7002_NL

1uF_6.3V

1uF_6.3V

C270

C270

1uF_6.3V

1uF_6.3V

C19

C19

1uF_6.3V

1uF_6.3V

C24

C24

1uF_6.3V

1uF_6.3V

C29

C29

1uF_6.3V

1uF_6.3V

C38

C38

1uF_6.3V

1uF_6.3V

C43

C43

1uF_6.3V

1uF_6.3V

2

L38 30R_1AL38 30R_1A

C401

C55

C55

1uF_6.3V

1uF_6.3V

C271

C271

10uF_6.3V

10uF_6.3V

C20

C20

1uF_6.3V

1uF_6.3V

C25

C25

1uF_6.3V

1uF_6.3V

C30

C30

1uF_6.3V

1uF_6.3V

C39

C39

1uF_6.3V

1uF_6.3V

C44

C44

1uF_6.3V

1uF_6.3V

10uF_6.3V

10uF_6.3V

C56

C56

1uF_6.3V

1uF_6.3V

C401

C276

C276

1uF_6.3V

1uF_6.3V

C21

C21

1uF_6.3V

1uF_6.3V

C26

C26

1uF_6.3V

1uF_6.3V

C31

C31

1uF_6.3V

1uF_6.3V

C40

C40

1uF_6.3V

1uF_6.3V

C45

C45

1uF_6.3V

1uF_6.3V

C57

C57

1uF_6.3V

1uF_6.3V

PCIE_VDDC

C277

C277

1uF_6.3V

1uF_6.3V

C22

C22

1uF_6.3V

1uF_6.3V

C27

C27

1uF_6.3V

1uF_6.3V

C32

C32

1uF_6.3V

1uF_6.3V

C41

C41

1uF_6.3V

1uF_6.3V

C46

C46

1uF_6.3V

1uF_6.3V

L1 120R_2AL1 120R_2A

C400

C400

(1.8V @ 400MA PCIE_VDDR)

(PCIE_VDDC 1.1V @ 1A )

VDD_CORE

1

BB_ENA = 0V FOR BACK BIASING DISABLED

N FET A = OFF, P FET B = OFF, N FET C = ON

+BBP = VDD_CORE

1.8V_REG

BB_ENA = +3.3V FOR BACK BIASING ENABLED

N FET A = ON, P FET B = ON, N FET C = OFF

+5VRUN

+BBP = +1.8V

** FOR NO BACK BIASING

DO NOT INSTALL FETS

AND INSTALL BEAD A

5

4

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

M8X GDDR3

M8X GDDR3

M8X GDDR3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

105-B37631-00B

105-B37631-00B

105-B37631-00B

1

0

0

3 11Tuesday, October 16, 2007

3 11Tuesday, October 16, 2007

3 11Tuesday, October 16, 2007

0

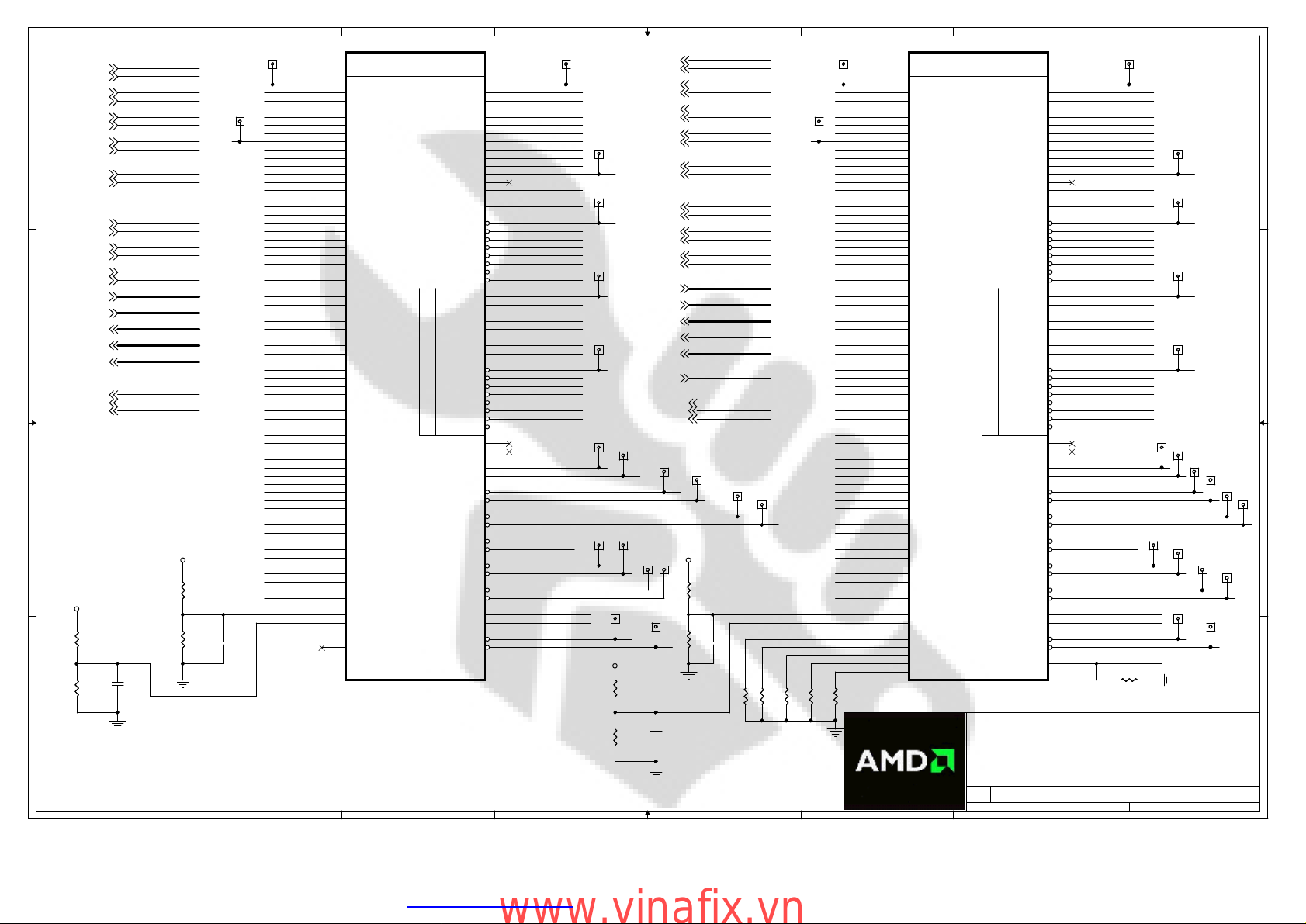

Page 4

1

RASA0#5

RASA1#5

CASA0#5

CASA1#5

WEA0#5

CSA0_0#5

CSA1_0#5

CSA0_1#5

CSA1_1#5

WDQSA[7..0]5

RDQSA[7..0]5

DQMA#[7..0]5

MDA[63..0]5

MAA[11..0]5

1.8V_REG

WEA1#5

CKEA05

CKEA15

CLKA05

CLKA0#5

CLKA15

CLKA1#5

A_BA05

A_BA15

A_BA25

R30

R30

40.2R

40.2R

1%

R33

R33

100R

100R

1%

A A

B B

C C

D D

RASA0#

RASA1#

CASA0#

CASA1#

WEA0#

WEA1#

CSA0_0#

CSA1_0#

CSA0_1#

CSA1_1#

CKEA0

CKEA1

CLKA0

CLKA0#

CLKA1

CLKA1#

WDQSA[7..0]

RDQSA[7..0]

DQMA#[7..0]

MDA[63..0]

MAA[11..0]

A_BA0

A_BA1

A_BA2

1.8V_REG

R27

R27

40.2R

40.2R

1%

R28

R28

100R

100R

1%

C63

C63

100nF

100nF

1

TP15

TP15

35mil

35mil

C61

C61

100nF

100nF

2

U1C

P27

P28

P31

P32

M27

K29

K31

K32

M33

M34

H33

H34

K27

F29

F32

D30

D32

G33

G34

G35

F34

D34

C34

C35

B34

C24

B24

B23

A23

C21

B21

C20

B20

H22

F22

D21

G19

F19

D19

C19

B19

A19

B18

C16

B16

C15

A15

H18

F18

E18

D18

G15

E15

D15

N35

N34

AM34

L34

L35

J33

J34

J29

J30

J31

J22

J19

J17

U1C

DQA_0

DQA_1

DQA_2

DQA_3

DQA_4

DQA_5

DQA_6

DQA_7

DQA_8

DQA_9

DQA_10

DQA_11

DQA_12

DQA_13

DQA_14

DQA_15

DQA_16

DQA_17

DQA_18

DQA_19

DQA_20

DQA_21

DQA_22

DQA_23

DQA_24

DQA_25

DQA_26

DQA_27

DQA_28

DQA_29

DQA_30

DQA_31

DQA_32

DQA_33

DQA_34

DQA_35

DQA_36

DQA_37

DQA_38

DQA_39

DQA_40

DQA_41

DQA_42

DQA_43

DQA_44

DQA_45

DQA_46

DQA_47

DQA_48

DQA_49

DQA_50

DQA_51

DQA_52

DQA_53

DQA_54

DQA_55

DQA_56

DQA_57

DQA_58

DQA_59

DQA_60

DQA_61

DQA_62

DQA_63

MVREFDA

MVREFSA

NC_1

M86-M A11

M86-M A11

TP7

TP7

35mil

35mil

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

PLACE MVREF DIVIDER COMPONENTS

AS CLOSE TO ASIC AS POSSIBLE

2

Part 3 of 7

Part 3 of 7

MEMORY INTERFACE A

MEMORY INTERFACE A

3

C27

MAA_0

B28

MAA_1

B27

MAA_2

G26

MAA_3

F27

MAA_4

E27

MAA_5

D27

MAA_6

J27

MAA_7

E29

MAA_8

C30

MAA_9

E26

MAA_10

A27

MAA_11

G27

MAA_A12

D26

MAA_BA2

C28

MAA_BA0

B29

MAA_BA1

M29

DQMAb_0

K33

DQMAb_1

G30

DQMAb_2

E33

DQMAb_3

C22

DQMAb_4

H21

DQMAb_5

C17

DQMAb_6

G17

DQMAb_7

M30

QSA_0

K34

QSA_1

G31

QSA_2

E34

QSA_3

B22

QSA_4

F21

QSA_5

B17

QSA_6

D17

QSA_7

M31

QSA_0B

K35

QSA_1B

G32

QSA_2B

E35

QSA_3B

A22

QSA_4B

E21

QSA_5B

A17

QSA_6B

E17

QSA_7B

write strobe read strobe

write strobe read strobe

3

ODTA0

ODTA1

CLKA0

CLKA1

CLKA0b

CLKA1b

RASA0b

RASA1b

CASA0b

CASA1b

CSA0b_0

CSA0b_1

CSA1b_0

CSA1b_1

CKEA0

CKEA1

WEA0b

WEA1b

C31

C25

A33

A26

B33

B26

A31

D24

C32

H26

A30

B30

G24

H24

B31

F24

C29

D22

4

TP8

TP8

35mil

35mil

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

A_BA2

A_BA0

A_BA1

DQMA#0 DQMB#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

RDQSA0

RDQSA1

RDQSA2

RDQSA3

RDQSA4

RDQSA5

RDQSA6

RDQSA7

WDQSA0

WDQSA1

WDQSA2

WDQSA3

WDQSA4

WDQSA5

WDQSA6

WDQSA7

CLKA0

CLKA1

CLKA0#

CLKA1#

RASA0#

RASA1#

CASA0#

CASA1#

CSA0_0#

CSA0_1# CSB0_1#

CSA1_0#

CSA1_1#

CKEA0

CKEA1

WEA0#

WEA1#

TP16

TP16

35mil

35mil

TP17

TP17

35mil

35mil

TP18

TP18

35mil

35mil

TP14

TP14

35mil

35mil

TP21

TP21

35mil

35mil

TP33

TP33

35mil

35mil

4

TP22

TP22

35mil

35mil

TP41

TP41

35mil

35mil

TP37

TP37

35mil

35mil

1.8V_REG

R34

R34

40.2R

40.2R

1%

R38

R38

100R

100R

1%

RASB0#6

RASB1#6

CASB0#6

CASB1#6

WEB0#6

WEB1#6

CSB0_0#6

CSB1_0#6

CSB0_1#6

CSB1_1#6

CKEB06

CKEB16

CLKB06

CLKB0#6

CLKB16

CLKB1#6

WDQSB[7..0]6

RDQSB[7..0]6

DQMB#[7..0]6

MDB[63..0]6

MAB[11..0]6

MEM_RST5,6

B_BA06

B_BA16

B_BA26

TP24

TP24

35mil

35mil

TP35

TP35

TP43

TP43

35mil

35mil

35mil

35mil

TP38

TP38

35mil

35mil

C64

C64

100nF

100nF

TP26

TP26

35mil

35mil

1.8V_REG

R29

R29

40.2R

40.2R

R31

R31

100R

100R

1%

5

RASB0#

RASB1#

CASB0#

CASB1#

WEB0#

WEB1#

CSB0_0#

CSB1_0#

CSB0_1#

CSB1_1#

CKEB0

CKEB1

CLKB0

CLKB0#

CLKB1

CLKB1#

WDQSB[7..0]

RDQSB[7..0]

DQMB#[7..0]

MDB[63..0]

MAB[11..0]

MEM_RST

B_BA0

B_BA1

B_BA2

TP28

TP28

35mil

35mil

1%

C62

C62

100nF

100nF

1K

5

6

U1G

TP9

TP9

35mil

35mil

MDB0

MDB1

MDB2

MDB3

TP11

TP11

MDB4

35mil

35mil

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

R1064

R1064

10K

10K

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

TP30

TP30

35mil

35mil

R36

R36

R37

4.7K

4.7K

R37

243R

243R

R35

R35

R321KR32

4.7K

4.7K

U1G

Part 4 of 7

Part 4 of 7

H15

DQB_0

G14

DQB_1

E14

DQB_2

D14

DQB_3

H12

DQB_4

G12

DQB_5

F12

DQB_6

D10

DQB_7

B13

DQB_8

C12

DQB_9

B12

DQB_10

B11

DQB_11

C9

DQB_12

B9

DQB_13

A9

DQB_14

B8

DQB_15

J10

DQB_16

H10

DQB_17

F10

DQB_18

D9

DQB_19

G7

DQB_20

G6

DQB_21

F6

DQB_22

D6

DQB_23

C8

DQB_24

C7

DQB_25

B7

DQB_26

A7

DQB_27

B5

DQB_28

A5

DQB_29

C4

DQB_30

B4

DQB_31

M3

DQB_32

M2

DQB_33

N2

DQB_34

N1

DQB_35

R3

DQB_36

R2

DQB_37

T3

DQB_38

T2

DQB_39

M8

DQB_40

M7

DQB_41

P5

DQB_42

P4

DQB_43

R9

DQB_44

R8

DQB_45

R6

DQB_46

U4

DQB_47

U3

DQB_48

U2

DQB_49

U1

DQB_50

V2

DQB_51

Y3

DQB_52

Y2

DQB_53

AA2

DQB_54

AA1

DQB_55

U9

DQB_56

U7

DQB_57

U6

DQB_58

V4

DQB_59

W9

DQB_60

W7

DQB_61

W6

DQB_62

W4

DQB_63

B14

MVREFDB

A13

MVREFSB

AM30

TESTEN

AA8

TEST_MCLK

AA7

TEST_YCLK

AA5

MEMTEST

AH19

PLLTEST

M86-M A11

M86-M A11

PLACE MVREF DIVIDER COMPONENTS

AS CLOSE TO ASIC AS POSSIBLE

6

MEMORY INTERFACE B

MEMORY INTERFACE B

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

MAB0

H2

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_A12

MAB_BA2

MAB_BA0

MAB_BA1

DQMBb_0

DQMBb_1

DQMBb_2

DQMBb_3

DQMBb_4

DQMBb_5

DQMBb_6

DQMBb_7

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

QSB_0B

QSB_1B

QSB_2B

QSB_3B

QSB_4B

QSB_5B

QSB_6B

QSB_7B

write strobe read strobe

write strobe read strobe

ODTB0

ODTB1

CLKB0

CLKB1

CLKB0b

CLKB1b

RASB0b

RASB1b

CASB0b

CASB1b

CSB0b_0

CSB0b_1

CSB1b_0

CSB1b_1

CKEB0

CKEB1

WEB0b

WEB1b

DRAM_RST

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

H3

J3

J5

J4

J6

G5

J9

F3

F4

J1

J2

J7

F1

G2

G3

D12

C10

E7

C6

P3

R4

W3

V8

J14

B10

F9

B6

P2

P8

W2

V6

H14

A10

E9

A6

P1

P7

W1

V5

D2

K5

A3

K1

B3

K2

D3

K7

C1

K4

E1

E2

L3

M4

E3

K8

F2

M6

AA4

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

B_BA2

B_BA0

B_BA1

RDQSB0

RDQSB1

RDQSB2

RDQSB3

RDQSB4

RDQSB5

RDQSB6

RDQSB7

WDQSB0

WDQSB1

WDQSB2

WDQSB3

WDQSB4

WDQSB5

WDQSB6

WDQSB7

MEM_RST

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

CLKB0

CLKB1

CLKB0#

CLKB1#

RASB0#

RASB1#

CASB0#

CASB1#

CSB0_0#

CSB1_0#

CSB1_1#

CKEB0

CKEB1

WEB0#

WEB1#

M8X GDDR3

105-B37631-00B

105-B37631-00B

105-B37631-00B

7

TP10

TP10

35mil

35mil

R660 4.7KR660 4.7K

TP34

TP34

35mil

35mil

TP23

TP23

35mil

35mil

4 11Tuesday, October 16, 2007

4 11Tuesday, October 16, 2007

4 11Tuesday, October 16, 2007

TP12

TP12

35mil

35mil

TP13

TP13

35mil

35mil

TP19

TP19

35mil

35mil

TP20

TP20

35mil

35mil

TP25

TP25

35mil

35mil

TP42

TP42

35mil

35mil

TP39

TP39

35mil

35mil

8

TP27

TP27

35mil

35milTP29

8

TP36

TP36

35mil

35mil

TP29

35mil

35mil

TP40

TP40

35mil

35mil

TP31

TP31

35mil

35mil

TP44

TP44

35mil

35mil

TP32

TP32

35mil

35mil

0

0

0

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

Page 5

5

U2

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA31

MDA30

MDA18

MDA19

MDA21

VREF = .72*VDDQ

C93

C93

100nF

100nF

1.8V_REG

MDA16

MDA23

MDA20

MDA17

MDA22

MDA4

MDA7

MDA5

MDA6

MDA0

MDA2

MDA3

MDA1

MDA9

MDA11

MDA8

MDA10

MDA15

MDA12

MDA14

MDA13

A_BA2

A_BA1

A_BA0

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

CLKA0#

CLKA0

RDQSA3

RDQSA2

RDQSA0

RDQSA1

WDQSA3

WDQSA2

WDQSA0

WDQSA1

DQMA#3

DQMA#2

DQMA#0

DQMA#1

MEM_RST

R39 243RR39 243R

CSA0_0#

WEA0#

RASA0#

CASA0#

CKEA0

D D

C C

B B

R41

R41

2.37K

2.37K

VREF = .72*VDDQ

R43

R43

5.49K

5.49K

A A

1.8V_REG 1.8V_REG

C70

C70

100nF

100nF

R47

R47

2.37K

2.37K

R49

R49

5.49K

5.49K

U2

T3

DQ31 | DQ23

T2

DQ30 | DQ22

R3

DQ29 | DQ21

R2

DQ28 | DQ20

M3

DQ27 | DQ19

N2

DQ26 | DQ18

L3

DQ25 | DQ17

M2

DQ24 | DQ16

T10

DQ23 | DQ31

T11

DQ22 | DQ30

R10

DQ21 | DQ29

R11

DQ20 | DQ28

M10

DQ19 | DQ27

N11

DQ18 | DQ26

L10

DQ17 | DQ25

M11

DQ16 | DQ24

G10

DQ15 | DQ7

F11

DQ14 | DQ6

F10

DQ13 | DQ5

E11

DQ12 | DQ4

C10

DQ11 | DQ3

C11

DQ10 | DQ2

B10

DQ9 | DQ1

B11

DQ8 | DQ0

G3

DQ7 | DQ15

F2

DQ6 | DQ14

F3

DQ5 | DQ13

E2

DQ4 | DQ12

C3

DQ3 | DQ11

C2

DQ2 | DQ10

B3

DQ1 | DQ9

B2

DQ0 | DQ8

H10

BA2 | RAS

G9

BA1 | BA0

G4

BA0 | BA1

L4

A11 | A7

K2

A10 | A8

M9

A9 | A3

K11

A8/AP | A10

L9

A7 | A11

K10

A6 | A2

H11

A5 | A1

K9

A4 | A0

M4

A3 | A9

K3

A2 | A6

H2

A1 | A5

K4

A0 | A4

F9

CS | CAS

H9

WE | CKE

H3

RAS | BA2

F4

CAS | CS

H4

CKE | WE

J10

CK

J11

CK

P3

RDQS3 | RDQS2

P10

RDQS2 | RDQS3

D10

RDQS1 | RDQS0

D3

RDQS0 | RDQS1

P2

WDQS3 | WDQS2

P11

WDQS2 | WDQS3

D11

WDQS1 | WDQS0

D2

WDQS0 | WDQS1

N3

DM3 | DM2

N10

DM2 | DM3

E10

DM1 | DM0

E3

DM0 | DM1

V9

RESET

A4

ZQ

H1

VREF

H12

VREF#H12

512M

512M

VDDQ#A12

VDDQ#C1

VDDQ#C4

VDDQ#C9

VDDQ#C12

VDDQ#E1

VDDQ#E4

VDDQ#E9

VDDQ#E12

VDDQ#N1

VDDQ#N4

VDDQ#N9

VDDQ#N12

VDDQ#R1

VDDQ#R4

VDDQ#R9

VDDQ#R12

VDDQ#V1

VDDQ#V12

VDD#M12

VSSQ#B12

VSSQ#D1

VSSQ#D4

VSSQ#D9

VSSQ#D12

VSSQ#G2

VSSQ#G11

VSSQ#L11

VSSQ#P12

VSSQ#T12

VDDA#K12

VSSA#J12

PLACE VREF DIVIDER COMPONENTS

AS CLOSE TO MEMORY AS POSSIBLE

VDDQ

VDDQ#J4

VDDQ#J9

VDD

VDD#A11

VDD#F1

VDD#F12

VDD#M1

VDD#V2

VDD#V11

VSSQ

VSSQ#B4

VSSQ#B9

VSSQ#L2

VSSQ#P1

VSSQ#P4

VSSQ#P9

VSSQ#T1

VSSQ#T4

VSSQ#T9

VSS#A10

VSS#G1

VSS#G12

VSS#L1

VSS#L12

VSS#V3

VSS#V10

VDDA

VSSA

RFU2

RFU1

RFU0

GND | VDD

GND | VDD

4

A1

A12

C1

C4

C9

C12

E1

E4

E9

E12

J4

J9

N1

N4

N9

N12

R1

R4

R9

R12

V1

V12

A2

A11

F1

F12

M1

M12

V2

V11

B1

B4

B9

B12

D1

D4

D9

D12

G2

G11

L2

L11

P1

P4

P9

P12

T1

T4

T9

T12

A3

VSS

A10

G1

G12

L1

L12

V3

V10

K1

K12

C66

C66

C67

C67

100nF

100nF

100nF

100nF

J12

J1

CSA0_1# CSA1_1#

J3

J2

V4

A9

MF

1.8V_REG 1.8V_REG

B1

B1

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

B2

B2

1.8V_REG1.8V_REG

R42

R42

2.37K

2.37K

VREF = .72*VDDQ

C71

R50

R50

5.49K

5.49K

C71

100nF

100nF

R44

R44

5.49K

5.49K

R48

R48

2.37K

2.37K

3

MDA37

MDA38

VREF = .72*VDDQ

C94

C94

100nF

100nF

MDA45

MDA40

MDA42

MDA41

MDA46

MDA43

MDA47

MDA44

MDA52

MDA55

MDA50

MDA54

MDA48

MDA53

MDA49

MDA51

MDA60

MDA62

MDA61

MDA63

MDA56

MDA57

MDA58

MDA59

MDA39

MDA32

MDA36

MDA33

MDA35

MDA34

A_BA2

A_BA1

A_BA0

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

CLKA1#

CLKA1

RDQSA5

RDQSA6

RDQSA7

RDQSA4

WDQSA5

WDQSA6

WDQSA7

WDQSA4

DQMA#5

DQMA#6

DQMA#7

DQMA#4

MEM_RST

R40 243RR40 243R

CSA1_0#

WEA1#

RASA1#

CASA1#

CKEA1

U3

U3

T3

DQ31 | DQ23

T2

DQ30 | DQ22

R3

DQ29 | DQ21

R2

DQ28 | DQ20

M3

DQ27 | DQ19

N2

DQ26 | DQ18

L3

DQ25 | DQ17

M2

DQ24 | DQ16

T10

DQ23 | DQ31

T11

DQ22 | DQ30

R10

DQ21 | DQ29

R11

DQ20 | DQ28

M10

DQ19 | DQ27

N11

DQ18 | DQ26

L10

DQ17 | DQ25

M11

DQ16 | DQ24

G10

DQ15 | DQ7

F11

DQ14 | DQ6

F10

DQ13 | DQ5

E11

DQ12 | DQ4

C10

DQ11 | DQ3

C11

DQ10 | DQ2

B10

DQ9 | DQ1

B11

DQ8 | DQ0

G3

DQ7 | DQ15

F2

DQ6 | DQ14

F3

DQ5 | DQ13

E2

DQ4 | DQ12

C3

DQ3 | DQ11

C2

DQ2 | DQ10

B3

DQ1 | DQ9

B2

DQ0 | DQ8

H10

BA2 | RAS

G9

BA1 | BA0

G4

BA0 | BA1

L4

A11 | A7

K2

A10 | A8

M9

A9 | A3

K11

A8/AP | A10

L9

A7 | A11

K10

A6 | A2

H11

A5 | A1

K9

A4 | A0

M4

A3 | A9

K3

A2 | A6

H2

A1 | A5

K4

A0 | A4

F9

CS | CAS

H9

WE | CKE

H3

RAS | BA2

F4

CAS | CS

H4

CKE | WE

J10

CK

J11

CK

P3

RDQS3 | RDQS2

P10

RDQS2 | RDQS3

D10

RDQS1 | RDQS0

D3

RDQS0 | RDQS1

P2

WDQS3 | WDQS2

P11

WDQS2 | WDQS3

D11

WDQS1 | WDQS0

D2

WDQS0 | WDQS1

N3

DM3 | DM2

N10

DM2 | DM3

E10

DM1 | DM0

E3

DM0 | DM1

V9

RESET

A4

ZQ

H1

VREF

H12

VREF#H12

512M

512M

1.8V_REG

VDDQ

VDDQ#A12

VDDQ#C1

VDDQ#C4

VDDQ#C9

VDDQ#C12

VDDQ#E1

VDDQ#E4

VDDQ#E9

VDDQ#E12

VDDQ#J4

VDDQ#J9

VDDQ#N1

VDDQ#N4

VDDQ#N9

VDDQ#N12

VDDQ#R1

VDDQ#R4

VDDQ#R9

VDDQ#R12

VDDQ#V1

VDDQ#V12

VDD

VDD#A11

VDD#F1

VDD#F12

VDD#M1

VDD#M12

VDD#V2

VDD#V11

VSSQ

VSSQ#B4

VSSQ#B9

VSSQ#B12

VSSQ#D1

VSSQ#D4

VSSQ#D9

VSSQ#D12

VSSQ#G2

VSSQ#G11

VSSQ#L2

VSSQ#L11

VSSQ#P1

VSSQ#P4

VSSQ#P9

VSSQ#P12

VSSQ#T1

VSSQ#T4

VSSQ#T9

VSSQ#T12

VSS#A10

VSS#G1

VSS#G12

VSS#L1

VSS#L12

VSS#V3

VSS#V10

VDDA

VDDA#K12

VSSA#J12

VSSA

RFU2

RFU1

RFU0

GND | VDD

GND | VDD

C95

C95

10uF_6.3V

10uF_6.3V

2

A1

A12

C1

C4

C9

C12

E1

E4

E9

E12

J4

J9

N1

N4

N9

N12

R1

R4

R9

R12

V1

V12

A2

A11

F1

F12

M1

M12

V2

V11

B1

B4

B9

B12

D1

D4

D9

D12

G2

G11

L2

L11

P1

P4

P9

P12

T1

T4

T9

T12

A3

VSS

A10

G1

G12

L1

L12

V3

V10

K1

K12

C68

C68

100nF

100nF

J12

J1

J3

J2

V4

A9

MF

C96

C96

10uF_6.3V

10uF_6.3V

C69

C69

100nF

100nF

C105

C105

1uF_6.3V

1uF_6.3V

B3

B3

B4

B4

C97

C97

1uF_6.3V

1uF_6.3V

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

C98

C98

100nF

100nF

RASA0#

RASA0#4

RASA1#

RASA1#4

CASA0#

CASA0#4

CASA1#

CASA1#4

WEA0#

WEA0#4

WEA1#

WEA1#4

CSA0_0#

CSA0_0#4

CSA1_0#

CSA1_0#4

CKEA0

CKEA04

CKEA1

CKEA14

CLKA0

CLKA04

CLKA14

C99

C99

100nF

100nF

C100

100nF

100nF

CLKA0#

CLKA1

CLKA1#

CSA0_1#

CSA1_1#

CLKA0#4

CLKA1#4

CSA0_1#4

CSA1_1#4

MAA[11..0]4

A_BA04

A_BA14

A_BA24

WDQSA[7..0]4

RDQSA[7..0]4

DQMA#[7..0]4

MDA[63..0]4

MEM_RST4,6

R168 121RR168 121R

R169 121RR169 121R

R170 121RR170 121R

R171 121RR171 121R

R172 121RR172 121R

R173 121RR173 121R

R174 121RR174 121R

R175 121RR175 121R

R176 121RR176 121R

R177 121RR177 121R

R702 121RR702 121R

R703 121RR703 121R

C101

C101

100nF

100nF

1

MAA[11..0]

A_BA0

A_BA1

A_BA2

WDQSA[7..0]

RDQSA[7..0]

DQMA#[7..0]

MDA[63..0]

MEM_RST

R178 60.4RR178 60.4R

R179 60.4RR179 60.4R

R180 60.4RR180 60.4R

R181 60.4RR181 60.4R

C107

C107

C106

C106

100nF

100nF

100nF

100nF

C102

C102

10nF

10nF

1.8V_REG

C110

C110C100

10nF

10nF

C73

C73

C72

C72

10uF_6.3V

10uF_6.3V

5

10uF_6.3V

10uF_6.3V

C82

C82

1uF_6.3V

1uF_6.3V

C74

C74

1uF_6.3V

1uF_6.3V

C75

C75

100nF

100nF

4

C76

C76

100nF

100nF

C77

C77

100nF

100nF

C78

C78

100nF

100nF

C83

C83

100nF

100nF

C84

C84

100nF

100nF

C79

C79

10nF

10nF

C87

C87

10nF

10nF

PDF created with pdfFactory Pro trial version www.pdffactory.com

www.vinafix.vn

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

M8X GDDR3

105-B37631-00B

105-B37631-00B

105-B37631-00B

0

0

5 11Tuesday, October 16, 2007

5 11Tuesday, October 16, 2007

5 11Tuesday, October 16, 2007

1

0

Page 6

5

U4

MDB26

MDB27

MDB24

MDB25

MDB31

MDB28

MDB30

MDB29

MDB12

MDB14

MDB15

D D

C C

B B

1.8V_REG

R54

R54

2.37K

2.37K

VREF = .72*VDDQ

R55

R55

5.49K

5.49K

R61

R61

5.49K

5.49K

C117

C117

100nF

100nF

1.8V_REG

R59

R59

2.37K

2.37K

MDB13

MDB11

MDB8

MDB9

MDB10

MDB4

MDB6

MDB5

MDB7

MDB0

MDB2

MDB3

MDB1

MDB20

MDB21

MDB22

MDB23

MDB16

MDB18

MDB19

MDB17

B_BA2

B_BA1

B_BA0

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

CSB0_0#

WEB0#

RASB0#

CASB0#

CKEB0

CLKB0#

CLKB0

RDQSB3

RDQSB1

RDQSB0

RDQSB2

WDQSB3

WDQSB1

WDQSB0

WDQSB2

DQMB#3

DQMB#1

DQMB#0

DQMB#2

MEM_RST

R51 243RR51 243R R52 243RR52 243R

VREF = .72*VDDQ

C116

C116

100nF

100nF 100nF

U4

T3

DQ31 | DQ23

T2

DQ30 | DQ22

R3

DQ29 | DQ21

R2

DQ28 | DQ20

M3

DQ27 | DQ19

N2

DQ26 | DQ18

L3

DQ25 | DQ17

M2

DQ24 | DQ16

T10

DQ23 | DQ31

T11

DQ22 | DQ30

R10

DQ21 | DQ29

R11

DQ20 | DQ28

M10

DQ19 | DQ27

N11

DQ18 | DQ26

L10

DQ17 | DQ25

M11

DQ16 | DQ24

G10

DQ15 | DQ7

F11

DQ14 | DQ6

F10

DQ13 | DQ5

E11

DQ12 | DQ4

C10

DQ11 | DQ3

C11

DQ10 | DQ2

B10

DQ9 | DQ1

B11

DQ8 | DQ0

G3

DQ7 | DQ15

F2

DQ6 | DQ14

F3

DQ5 | DQ13

E2

DQ4 | DQ12

C3

DQ3 | DQ11

C2

DQ2 | DQ10

B3

DQ1 | DQ9

B2

DQ0 | DQ8

H10

BA2 | RAS

G9

BA1 | BA0

G4

BA0 | BA1

L4

A11 | A7

K2

A10 | A8

M9

A9 | A3

K11

A8/AP | A10

L9

A7 | A11

K10

A6 | A2

H11

A5 | A1

K9

A4 | A0

M4

A3 | A9

K3

A2 | A6

H2

A1 | A5

K4

A0 | A4

F9

CS | CAS

H9

WE | CKE

H3

RAS | BA2

F4

CAS | CS

H4

CKE | WE

J10

CK

J11

CK

P3

RDQS3 | RDQS2

P10

RDQS2 | RDQS3

D10

RDQS1 | RDQS0

D3

RDQS0 | RDQS1

P2

WDQS3 | WDQS2

P11

WDQS2 | WDQS3

D11

WDQS1 | WDQS0

D2

WDQS0 | WDQS1

N3

DM3 | DM2

N10

DM2 | DM3

E10

DM1 | DM0

E3

DM0 | DM1

V9

RESET

A4

ZQ

H1

VREF

H12

VREF#H12

512M

512M

VDDQ#A12

VDDQ#C1

VDDQ#C4

VDDQ#C9

VDDQ#C12

VDDQ#E1

VDDQ#E4

VDDQ#E9

VDDQ#E12

VDDQ#N1

VDDQ#N4

VDDQ#N9

VDDQ#N12

VDDQ#R1

VDDQ#R4

VDDQ#R9

VDDQ#R12

VDDQ#V1

VDDQ#V12

VDD#M12

VSSQ#B12

VSSQ#D1

VSSQ#D4

VSSQ#D9

VSSQ#D12

VSSQ#G2

VSSQ#G11

VSSQ#L11

VSSQ#P12

VSSQ#T12

VDDA#K12

VSSA#J12

PLACE VREF DIVIDER COMPONENTS

AS CLOSE TO MEMORY AS POSSIBLE

VDDQ

VDDQ#J4

VDDQ#J9

VDD

VDD#A11

VDD#F1

VDD#F12

VDD#M1

VDD#V2

VDD#V11

VSSQ

VSSQ#B4

VSSQ#B9

VSSQ#L2

VSSQ#P1

VSSQ#P4

VSSQ#P9

VSSQ#T1

VSSQ#T4

VSSQ#T9

VSS

VSS#A10

VSS#G1

VSS#G12

VSS#L1

VSS#L12

VSS#V3

VSS#V10

VDDA

VSSA

RFU2

RFU1

RFU0

GND | VDD

GND | VDD

4

A1

A12

C1

C4

C9

C12

E1

E4

E9

E12

J4

J9

N1

N4

N9

N12

R1

R4

R9

R12

V1

V12

A2

A11

F1

F12

M1

M12

V2

V11

B1

B4

B9

B12

D1

D4

D9

D12

G2

G11

L2

L11

P1

P4

P9

P12

T1

T4

T9

T12

A3

A10

G1

G12

L1

L12

V3

V10

K1

K12

C112

C112

C113

C113

100nF

100nF

100nF

100nF

J12

J1

CSB0_1# CSB1_1#

J3

J2

V4

A9

MF

1.8V_REG 1.8V_REG

B5

B5

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

B6

B6

1.8V_REG

R53

R53

2.37K

2.37K

C139

R62

R62

5.49K

5.49K

C139

100nF

100nF

R56

R56

5.49K

5.49K

VREF = .72*VDDQ

1.8V_REG

R60

R60

2.37K

2.37K

3

MDB35

MDB33

MDB34

MDB32

MDB39

MDB37

MDB38

MDB36

MDB60

MDB62

MDB61

MDB63

MDB56

MDB59

MDB58

MDB57

MDB54

MDB55

MDB52

MDB53

MDB48

MDB51

MDB50

MDB49

MDB41

MDB40

MDB44

MDB42

MDB45

MDB43

MDB47

MDB46

VREF = .72*VDDQ

C140

C140

100nF

100nF

B_BA2

B_BA1

B_BA0

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

CSB1_0#

WEB1#

RASB1#

CASB1#

CKEB1

CLKB1#

CLKB1

RDQSB4

RDQSB7

RDQSB6

RDQSB5

WDQSB4

WDQSB7

WDQSB6

WDQSB5

DQMB#4

DQMB#7

DQMB#6

DQMB#5

MEM_RST

U5

U5

T3

T2

R3

R2

M3

N2

L3

M2

T10

T11

R10

R11

M10

N11

L10

M11

G10

F11

F10

E11

C10

C11

B10

B11

G3

F2

F3

E2

C3

C2

B3

B2

H10

G9

G4

L4

K2

M9

K11

L9

K10

H11

K9

M4

K3

H2

K4

F9

H9

H3

F4

H4

J10

J11

P3

P10

D10

D3

P2

P11

D11

D2

N3

N10

E10

E3

V9

A4

H1

H12

512M

512M

DQ31 | DQ23

DQ30 | DQ22

DQ29 | DQ21

DQ28 | DQ20

DQ27 | DQ19

DQ26 | DQ18

DQ25 | DQ17

DQ24 | DQ16

DQ23 | DQ31

DQ22 | DQ30

DQ21 | DQ29

DQ20 | DQ28

DQ19 | DQ27

DQ18 | DQ26

DQ17 | DQ25

DQ16 | DQ24

DQ15 | DQ7

DQ14 | DQ6

DQ13 | DQ5

DQ12 | DQ4

DQ11 | DQ3

DQ10 | DQ2

DQ9 | DQ1

DQ8 | DQ0

DQ7 | DQ15

DQ6 | DQ14

DQ5 | DQ13

DQ4 | DQ12

DQ3 | DQ11

DQ2 | DQ10

DQ1 | DQ9

DQ0 | DQ8

BA2 | RAS

BA1 | BA0

BA0 | BA1

A11 | A7

A10 | A8

A9 | A3

A8/AP | A10

A7 | A11

A6 | A2

A5 | A1

A4 | A0

A3 | A9

A2 | A6

A1 | A5

A0 | A4

CS | CAS

WE | CKE

RAS | BA2

CAS | CS

CKE | WE

CK

CK

RDQS3 | RDQS2

RDQS2 | RDQS3

RDQS1 | RDQS0

RDQS0 | RDQS1

WDQS3 | WDQS2

WDQS2 | WDQS3

WDQS1 | WDQS0

WDQS0 | WDQS1

DM3 | DM2

DM2 | DM3

DM1 | DM0

DM0 | DM1

RESET

ZQ

VREF

VREF#H12

1.8V_REG

VDDQ#A12

VDDQ#C1

VDDQ#C4

VDDQ#C9

VDDQ#C12

VDDQ#E1

VDDQ#E4

VDDQ#E9

VDDQ#E12

VDDQ#J4

VDDQ#J9

VDDQ#N1

VDDQ#N4

VDDQ#N9

VDDQ#N12

VDDQ#R1

VDDQ#R4

VDDQ#R9

VDDQ#R12

VDDQ#V1

VDDQ#V12

VDD#A11

VDD#F1

VDD#F12

VDD#M1

VDD#M12

VDD#V2

VDD#V11

VSSQ#B4

VSSQ#B9

VSSQ#B12

VSSQ#D1

VSSQ#D4

VSSQ#D9

VSSQ#D12

VSSQ#G2

VSSQ#G11

VSSQ#L2

VSSQ#L11

VSSQ#P1

VSSQ#P4

VSSQ#P9

VSSQ#P12

VSSQ#T1

VSSQ#T4

VSSQ#T9

VSSQ#T12

VSS#A10

VSS#G1

VSS#G12

VSS#L1

VSS#L12

VSS#V3

VSS#V10

VDDA#K12

VSSA#J12

GND | VDD

GND | VDD

C141

C141

10uF_6.3V

10uF_6.3V

VDDQ

VDD

VSSQ

VSS

VDDA

VSSA

RFU2

RFU1

RFU0

MF

2

A1

A12

C1

C4

C9

C12

E1

E4

E9

E12

J4

J9

N1

N4

N9

N12

R1

R4

R9

R12

V1

V12

A2

A11

F1

F12

M1

M12

V2

V11

B1

B4

B9

B12

D1

D4

D9

D12

G2

G11

L2

L11

P1

P4

P9

P12

T1

T4

T9

T12

A3

A10

G1

G12

L1

L12

V3

V10

K1

K12

C114

C114

100nF

100nF

J12

J1

J3

J2

V4

A9

C142

C142

10uF_6.3V

10uF_6.3V

C115

C115

100nF

100nF

C151

C151

1uF_6.3V

1uF_6.3V

B7

B7

B8

B8

C143

C143

1uF_6.3V

1uF_6.3V

RASB0#4

RASB1#4

CASB0#4

CASB1#4

WEB0#4

WEB1#4

CSB0_0#4

CSB1_0#4

CKEB04

CKEB14

CLKB04

CLKB0#4

CLKB14

CLKB1#4

CSB0_1#4

CSB1_1#4

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

BLM15BD121SN1

C144

C144

C145

C145

100nF

100nF

100nF

100nF

C146

C146

100nF

100nF

WDQSB[7..0]4

RDQSB[7..0]4

DQMB#[7..0]4

MDB[63..0]4

MAB[11..0]4

MEM_RST4,5

RASB0#

RASB1#

CASB0#

CASB1#

WEB0#

WEB1#

CSB0_0#

CSB1_0#

CKEB0

CKEB1

CLKB0

CLKB0#

CLKB1

CLKB1#

CSB0_1#

CSB1_1#

C147

C147

100nF

B_BA04

B_BA14

B_BA24

1

WDQSB[7..0]

RDQSB[7..0]

DQMB#[7..0]

MDB[63..0]

MAB[11..0]

B_BA0

B_BA1

B_BA2

MEM_RST

R182 121RR182 121R

R183 121RR183 121R

R184 121RR184 121R

R185 121RR185 121R

R186 121RR186 121R

R187 121RR187 121R

R188 121RR188 121R

R189 121RR189 121R

R190 121RR190 121R

R191 121RR191 121R

R19260.4R R19260.4R

R19360.4R R19360.4R

R19460.4R R19460.4R

R19560.4R R19560.4R

R704 121RR704 121R

R705 121RR705 121R

C152

C152

C153

C153

100nF

100nF

100nF

100nF

C148

C148

10nF

10nF

1.8V_REG

C156

C156

10nF

10nF

A A

5

1.8V_REG

C118

C118

C119

C119

C128

C128

C120

10uF_6.3V

10uF_6.3V

10uF_6.3V

10uF_6.3V 100nF

1uF_6.3V

1uF_6.3V

C120

1uF_6.3V

1uF_6.3V

4

C121

C121

100nF

100nF

C122

C122

100nF

100nF

C123