Page 1

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

ASSEMBLYNVPNVARIANT

B

1

2

SKU

3

4

5

6

12

13

14

7

8

9

10

11

15

P456-A02 DESIGN -- NV43/G73, 128/256 MB DDR3, VGA, DVI-I, SD/HDTV, VIVO

PAGE SUMMARY:

Page 1: TABLE OF CONTENTS & REVISION HISTORY

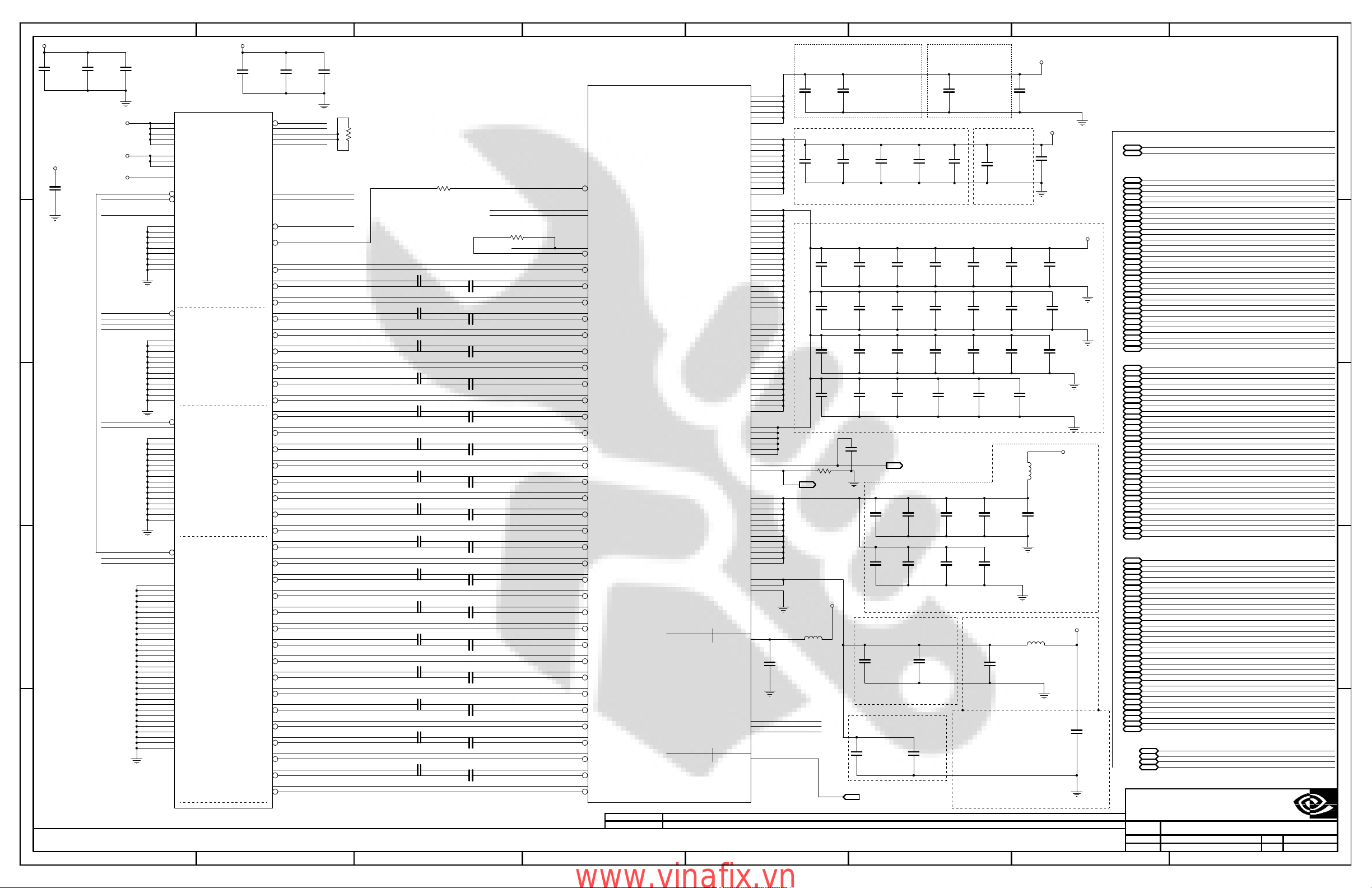

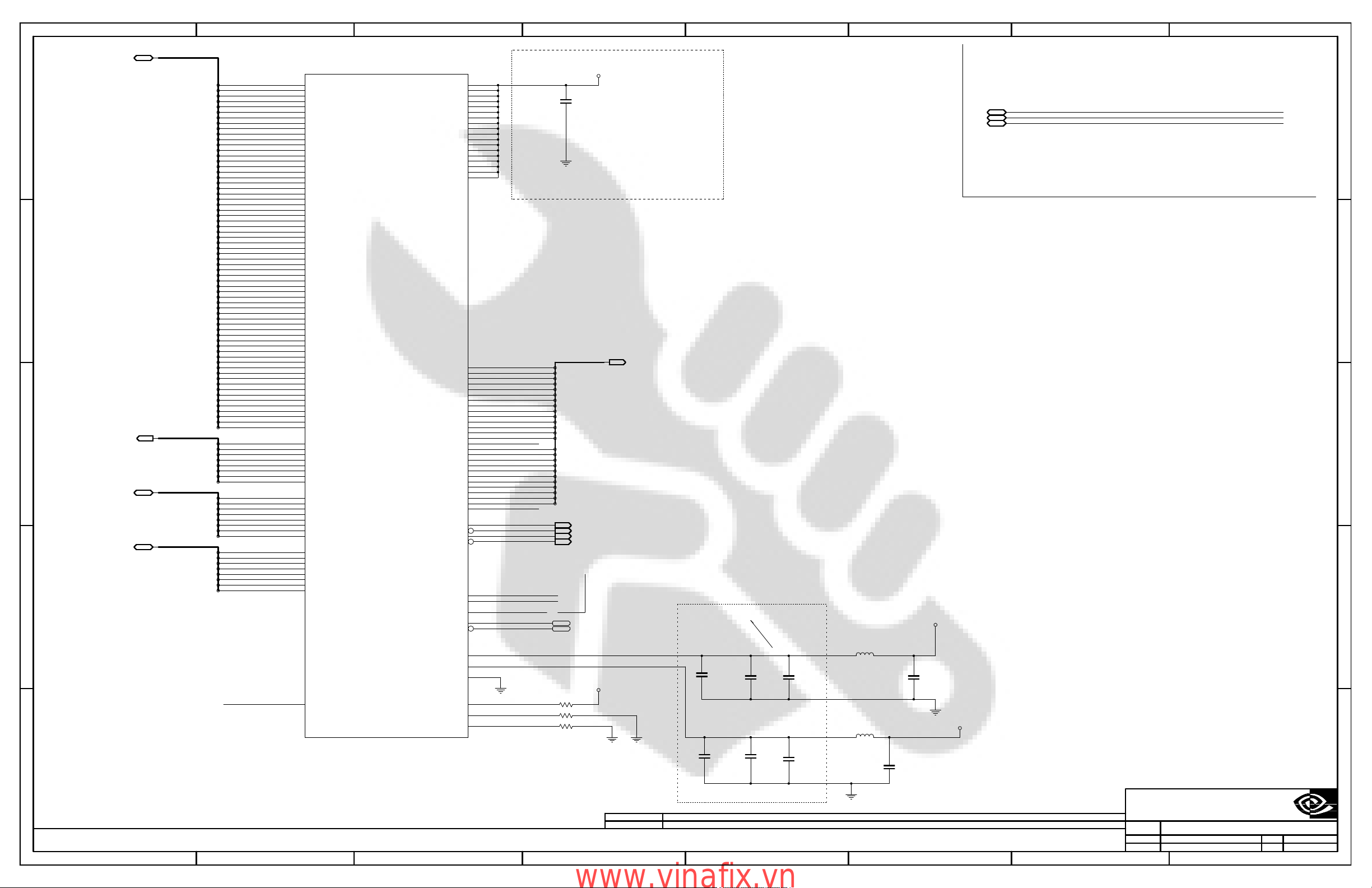

Page 2: PCI EXPRESS 16X, NVVDD DECOUPLING CAPS,PEX_IOVDD/Q DECOUPLING CAPS

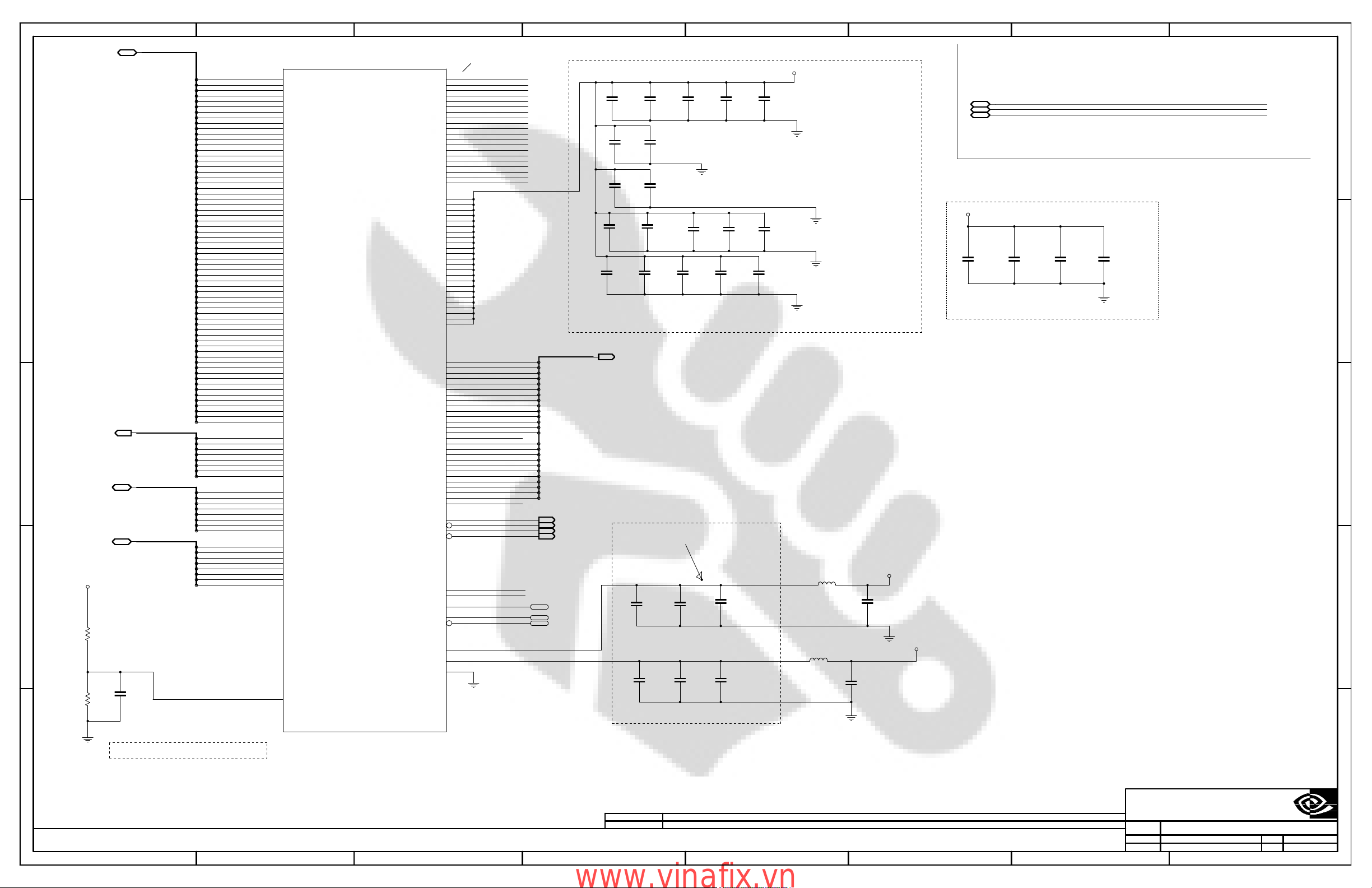

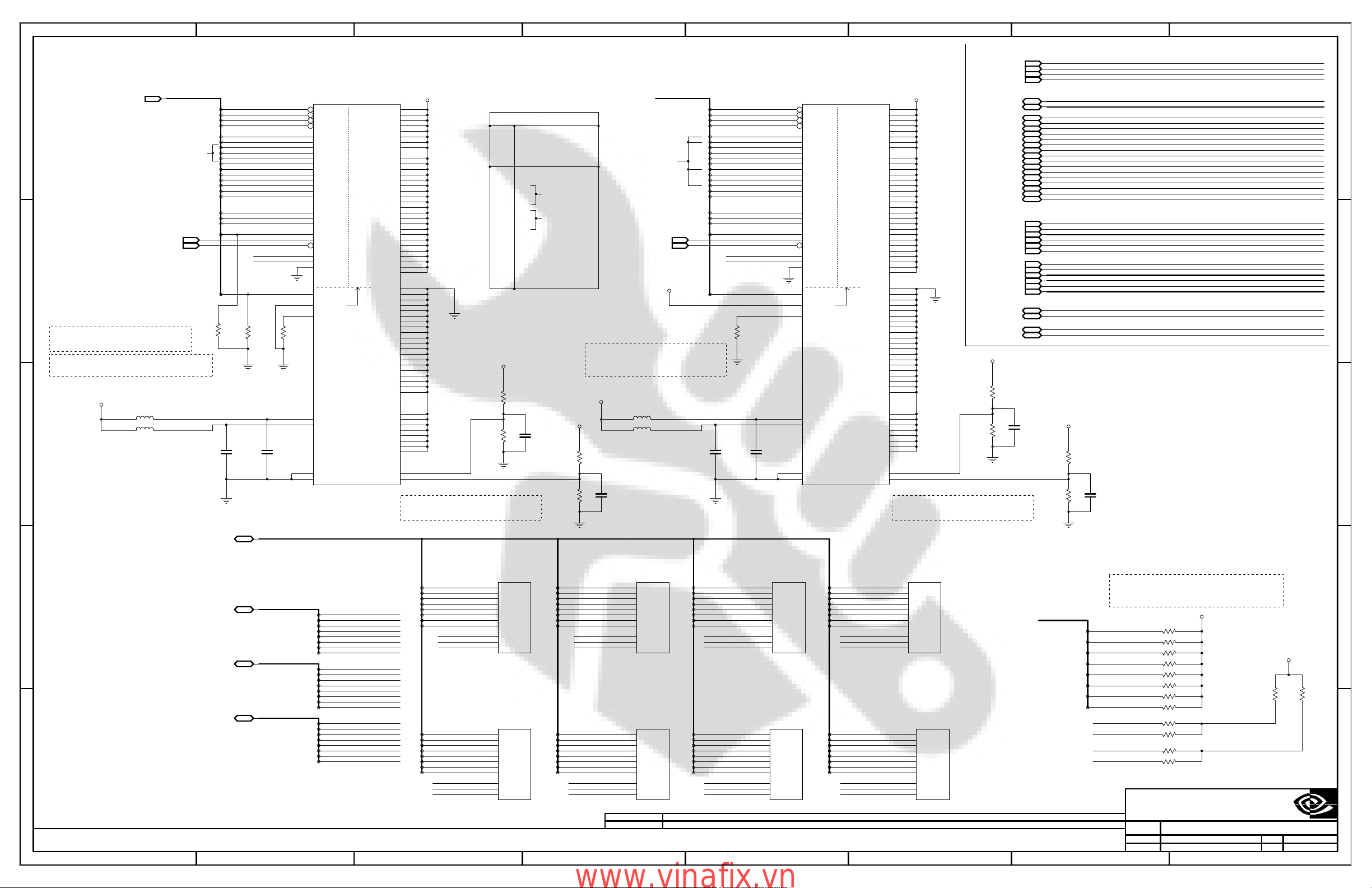

Page 3: FBA MEMORY INTERFACE, GPU FBVDD/Q DECOUPLING CAPS

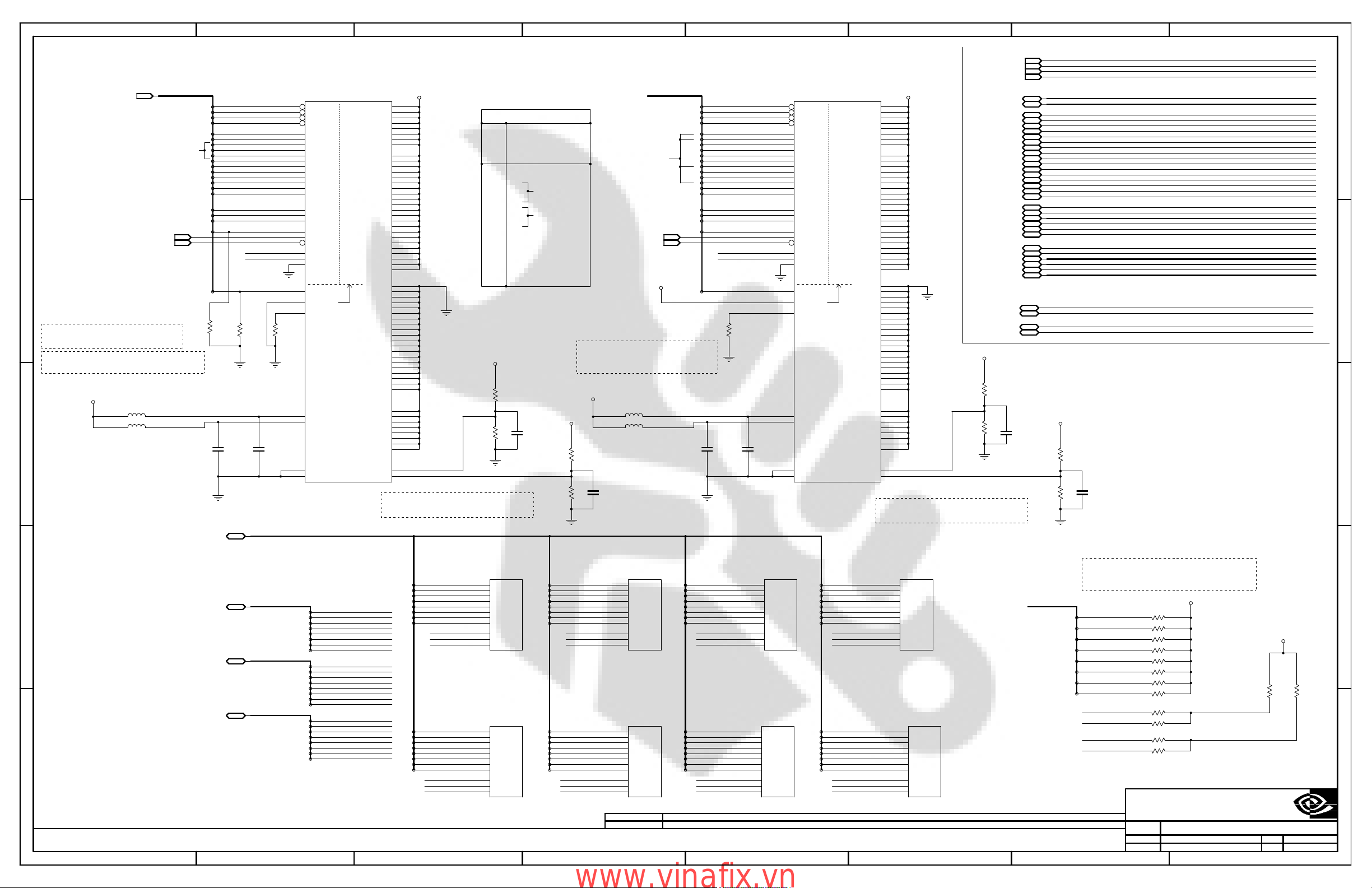

Page 4: FBA 8Mx32 DDR3 MEMORIES, FBA COMMAND BUS PU'S, FBA CLK TERMS

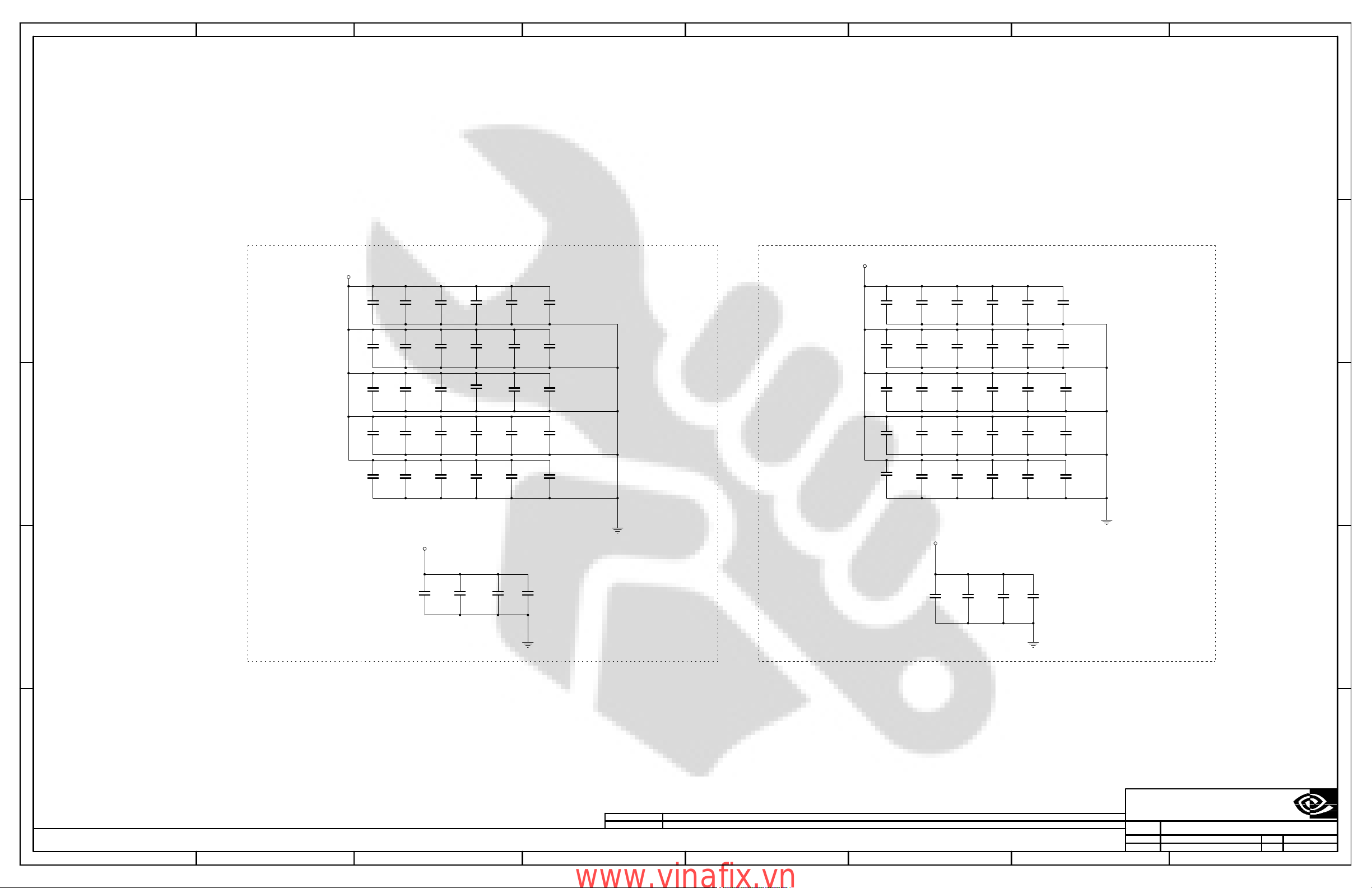

Page 5: FBA MEMORY FBVDD/Q DECOUPLING CAPS

Page 6: FBC MEMORY INTERFACE, GPU FBVTT

Page 7: FBC 8MX32 DDR3 MEMORIES, FBC CMD BUS PU'S, FBC CLK TERMS

Page 8: FBC MEMORY FBVDD/Q DECOUPLING CAPS, GPU GND CONNECTIONS

Page 9: DACA FILTERS, DACA SYNC BUFFERS & DB15 SOUTH

Page 10: DACC FILTERS, DACC SYNC BUFFERS & DB15 MID

Page 11: TMDS LINK A/B & PU's, TMDS IO BACKDRIVE PREVENTION,DVI CONNECTOR SOUTH

Page 12: TMDS LINK C/D & PU's,DVI CONNECTOR MID

Page 13: MIOA & MIOB, SLI CONNECTOR

Page 14: PHILIPS SAA7115 VIDEO DECODER

Page 15: DACB FILTERS, MINIDIN CONNECTOR NORTH, COMPONENT VIDEO OUTPUT CONNECTOR

Page 16: SPDIF-IN HEADER, XTAL

Page 17: JTAG, BIOS ROM, HDCP ROM, 2-PIN/4-PIN FAN CONTROL, GPIO's

Page 18: BIOS STRAPS & MECHANICALS

Page 19: POWER SUPPLY LINEARS: DDC5V, TMDS PLLVDD, DACB VDD, MIOA_VDDQ

Page 20: POWER SUPPLY: 5V, TMDSIOVDD, PEX1V2 AND FBVDDQ SWITCHER

Page 21: POWER SUPPLY: SINGLE PHASE NVVDD, NVVDD SET CONTROL

BASE

DT000

DT001

DT002

WS000

WS0500

WS0501

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

X0

www.vinafix.vn

<UNDEFINED>

<UNDEFINED>

G73 550/600MHZ 256MB DDR3 16MX32 VGA+DVI-I+HDTVOUT

TABLE OF CONTENTS & REVISION HISTORY

600-10456-base-sch

602-10456-0000-200

602-10456-0001-200

602-10456-0002-200

602-50456-0000-200

602-50456-0500-200

602-50456-0501-200

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

G73 550/600MHz 128MB DDR3 8MX32 VGA+DVI-I+HDTVOUT

G73 550/600MHZ 256MB DDR3 16MX32 VGA+DVI-I+HDTVOUT

G73 550/600MHZ 128MB DDR3 8MX32 VGA+DVI-I+HD/VIVO

NV43 WS 350/500 128MB DDR3 8MX32 DVI-I+DVI-I

NV43 WS 360/450 128MB DDR3 8MX32 DVI-I+DVI-I

G73 WS 350/600 128MB DDR3 8MX32 DVI-I+DVI-I_HDTVOUT

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

602-10456-0001-200

p456

rjacoby

1 OF 21

13-JAN-2006

Page 2

NONPHY-X16

BIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIOUT

OUT

IN

OTHER NV43/NV44

OTHER NV43/NV44

1/14 PCI_EXPRESS

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

VDD

VDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD_LP

VDD_LP

VDD_LP

VDD_LP

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

GND_SENSE

VDD_LP

VDD_LP

VDD_SENSE

VDD33

VDD33

PEX_PLLAVDD

PEX_PLLDVDD

PEX_PLLGND

NC

NC

NC

SPDIF NC

NV_PLLAVDD VDD

PEX_RST

RFU

RFU

PEX_TX0

PEX_REFCLK

PEX_REFCLK

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_TX4

PEX_TX4

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX8

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX7

PEX_TX7

PEX_RX7

PEX_RX5

PEX_TX8

PEX_TX5

PEX_RX5

PEX_RX6

PEX_TX7

PEX_RX10

PEX_TX10

PEX_TX9

PEX_RX9

PEX_RX8

PEX_RX8

PEX_TX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX9

PEX_RX9

PEX_RX13

PEX_TX13

PEX_TX15

PEX_RX14

PEX_TX15

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX15

PEX_RX15

END OF X8

END OF X16

END OF X1

END OF X4

TCLK JTAG2

TMS JTAG5

TDO JTAG4

TDI JTAG3

WAKE

SMDAT

SMCLK

PERN0

PERP0

REFCLK

PERST

REFCLK

PETN1

PERP2

PETN0

PERP1

PERN1

PETP0

PETP1

PERN3

PETP3

PETN3

PETP2

PERP3

PETN2

PERN2

PERP4

PERN4

PETN4

PERP5

PETP4

PERN5

PETP5

PETP6

PERN6

PERP6

PETN5

PERP7

PETN6

PERN7

PETN8

PETP8

PERP8

PETN7

PETP7

PERN8

PERN9

PERP9

PERP10

PERN10

PETP10

PETP9

PETN9

PETN10

PETN11

PERP12

PERN12

PERP11

PERN11

PETP11

PETN12

PETP12

PETN13

PERP13

PERN13

PETP13

PERP14

PERN15

PETP15

PETN15

PERN14

PETN14

PETP14

PERP15

TRST* JTAG1+12V

+12V/RSVD

+3V3AUX

+12V

+12V

+12V

+3V3

+3V3

+3V3

PRSNT2

PRSNT1

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

GND

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

PEX12V

NV_SOURCE_POWER_NET

GND

SNN_JTAG_TRST*

JTAG_TDI_TDO

SNN_JTAG_TMS

SNN_PEX_SMCLK

SNN_PEX_SMDAT

SNN_PEX_WAKE*

PEX_PWRGD*

PEX_REFCLK

PEX_REFCLK*

PEX_TXX0

PEX_TXX0*

PEX_RX0*

PEX_TXX1

PEX_TXX1*

PEX_RX1*

PEX_TXX2

PEX_TXX2*

PEX_RX2*

PEX_TXX3

PEX_TXX3*

PEX_RX3*

PEX_TXX4

PEX_TXX4*A36

PEX_RX4*

PEX_TXX5

PEX_TXX5*

PEX_RX5*

PEX_TXX6

PEX_TXX6*

PEX_RX6*

PEX_TXX7

PEX_TXX7*

PEX_RX7*

PEX_TXX8

PEX_TXX8*

PEX_RX8*

PEX_TXX9

PEX_TXX9*

PEX_RX9*

PEX_TXX10

PEX_TXX10*

PEX_RX10

PEX_RX10*

PEX_TXX11

PEX_TXX11*

PEX_RX11

PEX_RX11*

PEX_TXX12

PEX_TXX12*

PEX_RX12

PEX_RX12*

PEX_TXX13

PEX_TXX13*

PEX_RX13

PEX_RX13*

PEX_TXX14

PEX_TXX14*

PEX_RX14

PEX_RX14*

PEX_TXX15

PEX_TXX15*

PEX_RX15

PEX_RX15*

C37

10UF

16V

20%

X5R

1206

COMMON

PEX_RX0

PEX_RX1

PEX_RX2

PEX_RX3

PEX_RX4

PEX_RX5

PEX_RX6

PEX_RX7

PEX_RX8

PEX_RX9

R677

0

5%

0402

NO STUFF

C34

.01UF

10%

X7R

0402

COMMON

C36

.1UF

16V25V

10%

X7R

0603

COMMON

B9

SNN_JTAG_TCLK

A5

A6

A7

A8

this resistor stradles the TDI/TDO pair

B5

B6

B11

A11

A13

A14

A16

A17

B14

B15

A21

A22

B19

B20

A25

A26

B23

B24

A29

A30

B27

B28

A35

B33

B34

A39

A40

B37

B38

A43

A44

B41

B42

A47

A48

B45

B46

A52

A53

B50

B51

A56

A57

B54

B55

A60

A61

B58

B59

A64

A65

B62

B63

A68

A69

B66

B67

A72

A73

B70

B71

A76

A77

B74

B75

A80

A81

B78

B79

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

16X PEX INTERFACE

U5

G73-GT-N-A1

BGA820

CHANGED

PEX_PWRGD_GPU*

0

R14

COMMON

0402

5%

SNN_PEXCAPD_VDDQ

SNN_PEXCALPD_GND

200R51

0402 COMMON

10%

10%

10%

10%

10%

10%

10%

10%

10%

10%

5%

X7R COMMON

X7R

COMMON10%

X7R

COMMON

X7R COMMON

X7R

COMMON10%

X7R

COMMON

X7R COMMON

X7R

COMMON10%

X7R

COMMON

X7R COMMON

X7R

COMMON10%

X7R

COMMON

X7R COMMON

X7R

COMMON10%

X7R COMMON

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

PEX_TEST_PLLCLK_OUT

PEX_TEST_PLLCLK_OUT_N

.1UF

C802

.1UF

C807

16V

040210%

X7RCOMMON

.1UF

C794

16V

040210%

X7R

.1UF

C777

16V

0402

10%

X7R

.1UF

C760

16V

0402

10%

X7RCOMMON

.1UF

C737

16V

0402

10%

X7R

.1UF

C727

16V

0402

10%

X7R

.1UF

C716

16V

040210%

X7RCOMMON

.1UF

C706

16V

0402X7R 10%COMMON

.1UF

C695

16V

040210%

X7R

.1UF

C683

16V

0402

10%

X7R

.1UF

C659

16V

0402

10%

X7RCOMMON

.1UF

C644

16V

0402

10%

X7R

.1UF

C638

16V

0402

10%

X7R

.1UF

C634

16V

040210%

X7RCOMMON

.1UF

C624

16V

0402

10%

X7R

.1UF

C617

16V

0402

10%

X7RCOMMON

16V0402

.1UF

C787

16V

0402

.1UF

C766

16V

0402

.1UF

C746

16V0402

.1UF

C734

16V

0402

.1UF

C719

16V0402

.1UF

C709

16V

0402

.1UF

C701

0402 X7R10%16V COMMON

.1UF

C690

16V0402

.1UF

C673

16V

0402

.1UF

C656

16V0402

.1UF

C641

16V

0402

.1UF

C635

16V0402

.1UF

C632

16V0402

.1UF

C622

16V

0402

.1UF

C613

16V0402

AH15

AG12

AH13

AM12

AM11

AH14

AJ14

AJ15

AK15

AK13

AK14

AH16

AG16

AM14

AM15

AG17

AH17

AL15

AL16

AG18

AH18

AK16

AK17

AK18

AJ18

AL17

AL18

AJ19

AH19

AM18

AM19

AG20

AH20

AK19

AK20

AG21

AH21

AL20

AL21

AK21

AJ21

AM21

AM22

AJ22

AH22

AK22

AK23

AG23

AH23

AL23

AL24

AK24

AJ24

AM24

AM25

AJ25

AH25

AK25

AK26

AH26

AG26

AL26

AL27

AK27

AJ27

AM27

AM28

AJ28

AH27

AL28

AL29

G73 550/600MHZ 256MB DDR3 16MX32 VGA+DVI-I+HDTVOUT

PCI EXPRESS 16X, NVVDD DECOUPLING CAPS,PEX_IOVDD/Q DECOUPLING CAPS

www.vinafix.vn

AD23

AF23

AF24

AF25

AG24

AG25

AC16

AC17

AC21

AC22

AE18

AE21

AE22

AF12

AF18

AF21

AF22

K16

K17

N13

N14

N16

N17

N19

P13

P14

P16

P17

P19

R16

R17

T14

T15

T18

T19

U13

U14

U15

U18

U19

V16

V17

W13

W14

W16

W17

W19

Y13

Y14

Y16

Y17

Y19

Y20

P20

T20

T23

U20

U23

W20

N20

M21

AC11

AC12

AC24

AD24

AE11

AE12

H7

J7

K7

L10

L7

L8

M10

AF15

AE15

AE16

NV_PLLAVDD

T13

GND

AM8

AM9

B32

J6

600mA

NVVDD_SENSE

GND_SENSE

NV43 -- UNSTUFF

F_SPDIFIN

PEX3V3

C889

.01UF

16V

10%

X7R

0402

COMMON

3V3AUX

GND

Place Close to fingers

NV_SOURCE_POWER_NET

C39

.1UF

16V

10%

X5R

0402

COMMON

C887

.1UF

16V

10%

X7R

0402

COMMON

SNN_PE_PRSNT2_A

SNN_PE_RSVD2

SNN_PE_PRSNT2_B

SNN_PE_RSVD3

SNN_PE_RSVD4

SNN_PE_RSVD5

SNN_PE_PRSNT2_C

SNN_PE_RSVD6

SNN_PE_RSVD7

SNN_PE_RSVD8

C876

10UF

16V

20%

X5R

1206

COMMON

GND

PEX12V

PEX3V3

3V3AUX

PRSNT

GND

GND

PRSNT

GND

CN2

CON_X16

CON_PCIEXP_X16_EDGE

NO STUFF

B1

B2

A2

A3

B3

B8

A9

A10

B10

A1

B17

B12

B4

A4

B7

A12

B13

A15

B16

B18

A18

B31

A19

B30

A32

A20

B21

B22

A23

A24

B25

B26

A27

A28

B29

A31

B32

GND

B48

A33

A34

B35

B36

A37

A38

B39

B40

A41

A42

B43

B44

A45

A46

B47

B49

A49

B81

A50

B82

A51

B52

B53

A54

A55

B56

B57

A58

A59

B60

B61

A62

A63

B64

B65

A66

A67

B68

B69

A70

A71

B72

B73

A74

A75

B76

B77

A78

A79

B80

A82

R593

GND

240R@100MHz

LB509

COMMON

C740

.1UF

10%

16V

X7R

0402

COMMON

SNN_GPU_AM10_NC

SNN_GPU_AM8_NC

SNN_GPU_AM9_NC

VALUES TBD

Place near balls

C680

.022UF

16V

10%

X7R

0402

COMMON

2A

C705

.022UF

16V

10%

X7R

0402

COMMON

C703

.47UF

6.3V

10%

X5R

0402

COMMON

C720

.1UF

16V

10%

X7R

COMMON

C721

.47UF

6.3V

10%

X5R

0402

COMMON

C669

.47UF

6.3V

10%

0402

COMMON

Place near balls

VALUES TBD

0

NO STUFF

0402

5%

2<>

VDD33

18MIL

PEX1V2

BEAD_0402

C664

.022UF

16V

10%

X7R

0402

COMMON

VALUES TBD

C731

.022UF

16V

10%

X7R

0402

COMMON

C693

.01UF

16V

10%

X7R

0402

COMMON

Place near balls

C685

.1UF

16V

10%

X7R

0402

COMMON

C717

.1UF

16V

10%

X7R

04020402

COMMON

C702

.1UF

16V

10%

X7R

0402

COMMON

C684

.1UF

16V

10%

X7RX5R

0402

COMMON

C672

1000PF

COMMON

50V

10%

X7R

0402

GND

Place near balls

C743

.1UF

10V

10%

X5R

0402

COMMON

C735

.1UF

10V

10%

0402

COMMON

Place near balls

270mA

PEX_PLL_VDD

C718

.1UF

10%

16V

X7R

0402

COMMON

Place near balls

20mA

C729

4700PF

10%

25V

X7R

0402

COMMON

16>

Place Close to GPU

C625

4.7UF

10%

6.3V

X5R

0603

COMMON

Place Close to GPU

C670

.47UF

6.3V

10%

X5R

0402

COMMON

C666

.47UF

6.3V

10%

X5R

0402

COMMON

C696

.1UF

16V

10%

X7R

0402

COMMON

C689

.1UF

16V

10%

0402

COMMON

2<>

21<

C783

4700PF

25V

10%

X7R

0402

COMMON

C764

4700PF

25V

10%

X7RX5R

0402

COMMON

C697

.01UF

16V

10%

X7R

0402

COMMON

C707

.1UF

16V

10%

X7R

0402

COMMON

C736

.47UF

6.3V

10%

X5R

0402

COMMON

C722

.47UF

6.3V

10%

X5R

0402

COMMON

C738

.47UF

6.3V

10%

X5R X5RX7RX7R

0402

COMMON

C708

.01UF

16V

10%

X7R

0402

COMMON

C658

.022UF

16V

10%

X7R

0402

COMMON

C747

.022UF

16V

10%

X7R

0402

COMMON

C726

.47UF

6.3V

10%

X5R

0402

COMMON

C725

.1UF

16V

10%

X7R

0402

COMMON

C733

.47UF

6.3V

10%

X5R

0402

COMMON

C711

.1UF

16V

10%

0402

COMMON

C688

22UF

6.3V

X5R

0805

COMMON

C795

.022UF

16V

10%

X7R

0402

COMMON

C652

.022UF

16V

10%

X7R

0402

COMMON

Place Near BGA

C728

.01UF

16V

10%

X7R

0402

COMMON

C715

4.7UF

6.3V

X5R

0603

COMMON

Place Near BGA

C730

470PF

16V

10%

X7R

0402

COMMON

C626

4.7UF

6.3V

X5R

0603

COMMON

20%

C724

.1UF

16V

10%

X7R

0402

COMMON

C742

10UF

6.3V

20%

X5R

0805

COMMON

C710

10UF

6.3V

20%

X5R

0805

COMMON

C713

.47UF

6.3V

10%

0402

COMMON

GND

GND

180R@100MHz

LB508

10%

PEX1V2

10%

PEX1V2

C627

22UF

X5R

0805

COMMON

GND

C700

10UF

6.3V

20%

X5R

0805

COMMON

C739

.1UF

16V

10%

X7R

0402

COMMON

C712

.1UF

16V

10%

X7R

0402

COMMON

LB515

180R@100MHz

COMMON

BEAD_0603

C814

1UF

6.3V

10%

X7R

0603

COMMON

COMMONBEAD_0603

GND

20%6.3V

PEX3V3

GND

GND

PEX1V2

GND

GND

NVVDD

GND

GND

C682

4.7UF

10%

6.3V

X5R

0603

COMMON

2>

21<

2>

PEX_REFCLK

PEX_REFCLK*

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

PEX_TXX0

PEX_TXX0*

PEX_TXX1

PEX_TXX1*

PEX_TXX2

PEX_TXX2*

PEX_TXX3

PEX_TXX3*

PEX_TXX4

PEX_TXX4*

PEX_TXX5

PEX_TXX5*

PEX_TXX6

PEX_TXX6*

PEX_TXX7

PEX_TXX7*

PEX_TXX8

PEX_TXX8*

PEX_TXX9

PEX_TXX9*

PEX_TXX10

PEX_TXX10*

PEX_TXX11

PEX_TXX11*

PEX_TXX12

PEX_TXX12*

PEX_TXX13

PEX_TXX13*

PEX_TXX14

PEX_TXX14*

PEX_TXX15

PEX_TXX15*

PEX_RX0

PEX_RX0*

PEX_RX1

PEX_RX1*

PEX_RX2

PEX_RX2*

PEX_RX3

PEX_RX3*

PEX_RX4

PEX_RX4*

PEX_RX5

PEX_RX5*

PEX_RX6

PEX_RX6*

PEX_RX7

PEX_RX7*

PEX_RX8

PEX_RX8*

PEX_RX9

PEX_RX9*

PEX_RX10

PEX_RX10*

PEX_RX11

PEX_RX11*

PEX_RX12

PEX_RX12*

PEX_RX13

PEX_RX13*

PEX_RX14

PEX_RX14*

PEX_RX15

PEX_RX15*

NVVDD_SENSE

GND_SENSE

NV_PLLAVDD

PEX_PLL_VDD

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_TX1

PEX_TX1

PEX_TX2

PEX_TX2

PEX_TX3

PEX_TX3

PEX_TX4

PEX_TX4

PEX_TX5

PEX_TX5

PEX_TX6

PEX_TX6

PEX_TX7

PEX_TX7

PEX_TX8

PEX_TX8

PEX_TX9

PEX_TX9

PEX_TX10

PEX_TX10

PEX_TX11

PEX_TX11

PEX_TX12

PEX_TX12

PEX_TX13

PEX_TX13

PEX_TX14

PEX_TX14

PEX_TX15

PEX_TX15

PEX_TXX0

PEX_TXX0

PEX_TXX1

PEX_TXX1

PEX_TXX2

PEX_TXX2

PEX_TXX3

PEX_TXX3

PEX_TXX4

PEX_TXX4

PEX_TXX5

PEX_TXX5

PEX_TXX6

PEX_TXX6

PEX_TXX7

PEX_TXX7

PEX_TXX8

PEX_TXX8

PEX_TXX9

PEX_TXX9

PEX_TXX10

PEX_TXX10

PEX_TXX11

PEX_TXX11

PEX_TXX12

PEX_TXX12

PEX_TXX13

PEX_TXX13

PEX_TXX14

PEX_TXX14

PEX_TXX15

PEX_TXX15

PEX_RX0

PEX_RX0

PEX_RX1

PEX_RX1

PEX_RX2

PEX_RX2

PEX_RX3

PEX_RX3

PEX_RX4

PEX_RX4

PEX_RX5

PEX_RX5

PEX_RX6

PEX_RX6

PEX_RX7

PEX_RX7

PEX_RX8

PEX_RX8

PEX_RX9

PEX_RX9

PEX_RX10

PEX_RX10

PEX_RX11

PEX_RX11

PEX_RX12

PEX_RX12

PEX_RX13

PEX_RX13

PEX_RX14

PEX_RX14

PEX_RX15

PEX_RX15

602-10456-0001-200

p456

rjacoby

10MIL

10MIL

10MIL

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

VOLTAGEMIN_LINE_WIDTH

1.2

0

1.2

1.2

2 OF 21

13-JAN-2006

NV_CRITICALNV_IMPEDANCEDIFFPAIRNET

1

1100DIFF

1100DIFF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1100DIFF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1100DIFF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Page 3

FBAD<63..0>

BIBIBI

OUT

OUT

OUT

OUT

OUT

BI

2/14 FBA

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD6

FBA_CMD5

FBA_CMD4

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

RFU

RFU

FBA_REFCLK

FBA_DEBUG

FBA_CLK1

FBA_CLK1

FBA_CLK0

FBA_CLK0

FBA_REFCLK

FBA_PLLGND

FBA_PLLAVDD

FBA_PLLVDD

FBAD10

FBAD11

FBAD12

FBAD13

FBAD14

FBAD15

FBAD16

FBAD17

FBAD0

FBAD1

FBAD2

FBAD3

FBAD4

FBAD5

FBAD6

FBAD7

FBAD8

FBAD9

FBAD18

FBAD19

FBAD20

FBAD21

FBAD22

FBAD23

FBAD24

FBAD25

FBAD26

FBAD27

FBAD28

FBAD29

FBAD30

FBAD31

FBAD32

FBAD33

FBAD34

FBAD35

FBAD36

FBAD37

FBAD38

FBAD39

FBAD40

FBAD41

FBAD42

FBAD43

FBAD44

FBAD45

FBAD46

FBAD47

FBAD48

FBAD49

FBAD50

FBAD51

FBAD52

FBAD53

FBAD54

FBAD55

FBAD56

FBAD57

FBAD58

FBAD59

FBAD60

FBAD61

FBAD62

FBAD63

FBADQM0

FBADQM1

FBADQM2

FBADQM3

FBADQM4

FBADQM5

FBADQM6

FBADQM7

FBADQS_WP0

FBADQS_WP1

FBADQS_WP2

FBADQS_WP3

FBADQS_WP4

FBADQS_WP5

FBADQS_WP6

FBADQS_WP7

FBADQS_RN0

FBADQS_RN1

FBADQS_RN2

FBADQS_RN7

FBADQS_RN6

FBADQS_RN5

FBADQS_RN4

FBADQS_RN3

FB_VREF1

OUTBIBI

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

FBADQM<7..0>

FBADQS_WP<7..0>

FBADQS_RN<7..0>

C629

.1UF

16V

10%

X7R

0402

COMMON

VREF = FBVDDQ * Rbot/(Rtop + Rbot)

VREF = 0.70 * FBVDDQ

1.26V = 1.8V * 2.7K/(1.15K + 2.7K)

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBAD<0>

FBAD<1>

FBAD<2>

FBAD<3>

FBAD<4>

FBAD<5>

FBAD<6>

FBAD<7>

FBAD<8>

FBAD<9>

FBAD<10>

FBAD<11>

FBAD<12>

FBAD<13>

FBAD<14>

FBAD<15>

FBAD<16>

FBAD<17>

FBAD<18>

FBAD<19>

FBAD<20>

FBAD<21>

FBAD<22>

FBAD<23>

FBAD<24>

FBAD<25>

FBAD<26>

FBAD<27>

FBAD<28>

FBAD<29>

FBAD<30> E28

FBAD<31>

FBAD<32>

FBAD<33>

FBAD<34>

FBAD<35>

FBAD<36>

FBAD<37>

FBAD<38>

FBAD<39>

FBAD<40> AM30

FBAD<41>

FBAD<42>

FBAD<43>

FBAD<44>

FBAD<45>

FBAD<46>

FBAD<47>

FBAD<48>

FBAD<49>

FBAD<50>

FBAD<51>

FBAD<52>

FBAD<53>

FBAD<54>

FBAD<55>

FBAD<56>

FBAD<57>

FBAD<58>

FBAD<59>

FBAD<60>

FBAD<61>

FBAD<62>

FBAD<63>

FBADQM<0>

FBADQM<1>

FBADQM<2>

FBADQM<3>

FBADQM<4>

FBADQM<5>

FBADQM<6>

FBADQM<7>

FBADQS_WP<0>

FBADQS_WP<1>

FBADQS_WP<2>

FBADQS_WP<3>

FBADQS_WP<4>

FBADQS_WP<5>

FBADQS_WP<6>

FBADQS_WP<7>

FBADQS_RN<0>

FBADQS_RN<1>

FBADQS_RN<2>

FBADQS_RN<3>

FBADQS_RN<4>

FBADQS_RN<5>

FBADQS_RN<6>

FBADQS_RN<7>

FBA_VREF

N27

M27

N28

L29

K27

K28

J29

J28

P30

N31

N30

N32

L31

L30

J30

L32

H30

K30

H31

F30

H32

E31

D30

E30

H28

H29

E29

J27

F27

E27

F28

AD29

AE29

AD28

AC28

AB29

AA30

Y28

AB30

AF30

AJ31

AJ30

AJ32

AK29

AM31

AL30

AE32

AE30

AE31

AD30

AC31

AC32

AB32

AB31

AG27

AF28

AH28

AG28

AG29

AD27

AF27

AE28

M29

M30

G30

F29

AA29

AK30

AC30

AG30

L28

K31

G32

G28

AB28

AL32

AF32

AH30

M28

K32

G31

G27

AA28

AL31

AF31

AH29

U5

G73-GT-N-A1

BGA820

CHANGED

ALL FBVDD PINS ARE NC ON G73 DESKTOP G3 PACKAGE

E32

A12

A15

A18

A21

A24

A27

A3

A30

A6

A9

AA32

AD32

AG32

AK32

C32

F32

J32

M32

R32

V32

AA25

AA26

AB25

AB26

G11

G12

G15

G18

G21

G22

H11

H12

H15

H18

H21

H22

L25

L26

M25

M26

R25

R26

V25

V26

P32

U27

P31

U30

Y31

W32

W31

T32

V27

T28

T31

U32

W29

W30

T27

V28

V30

U31

R27

V29

T30

W28

R29

R30

P29

U28

Y32

R28

Y27

AA27

Y30

AC26

AC27

D32

D31

G25

G24

SNN_GPU_A12

SNN_GPU_A15

SNN_GPU_A18

SNN_GPU_A21

SNN_GPU_A24

SNN_GPU_A27

SNN_GPU_A3

SNN_GPU_A30

SNN_GPU_A6

SNN_GPU_A9

SNN_GPU_AA32

SNN_GPU_AD32

SNN_GPU_AG32

SNN_GPU_AK32

SNN_GPU_C32

SNN_GPU_F32

SNN_GPU_J32

SNN_GPU_M32

SNN_GPU_R32

SNN_GPU_V32

FBA_CMD<0>

FBA_CMD<1>

FBA_CMD<2>

FBA_CMD<3>

FBA_CMD<4>

FBA_CMD<5>

FBA_CMD<6>

FBA_CMD<7>

FBA_CMD<8>

FBA_CMD<9>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<12>

FBA_CMD<13>

SNN_FBA_CMD<14>

FBA_CMD<15>

FBA_CMD<16>

FBA_CMD<17>

FBA_CMD<18>

FBA_CMD<19>

FBA_CMD<20>

FBA_CMD<21>

FBA_CMD<22>

FBA_CMD<23>

FBA_CMD<24>

FBA_CMD<25>

SNN_FBA_CMD<26>

FBA_CLK0P28

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

SNN_FBA_DBI0

SNN_FBA_DBI1

LTP_FBA_DEBUG

LTP_FBA_REFCLK

LTP_FBA_REFCLK*

FBA_PLLAVDD

GND

C647

.47UF

6.3V

10%

X5R

0402

COMMON

C691

.47UF

6.3V

10%

X5R

0402

COMMON

C665

.1UF

16V

10%

X7R

COMMON

C704

.1UF

16V

10%

X7R

0402

COMMON

C694

.1UF

16V

10%

X7R

0402

COMMON

C732

.47UF

6.3V

10%

X5R

0402

COMMON

C757

.1UF

16V

10%

X7R

0402

COMMON

C645

1UF

6.3V

10%

X7R

0603

COMMON

C667

.47UF

6.3V

10%

X5R

0402

COMMON

C681

.1UF

16V

10%

X7R

04020402

COMMON

C660

.1UF

16V

10%

X7R

0402

COMMON

GND

C698

.1UF

16V

10%

X7R

0402

COMMON

C723

.1UF

16V

10%

X7R

0402

COMMON

C768

.1UF

16V

10%

X7R

0402

C699

.47UF

6.3V

10%

X5R

0402

COMMON

C668

.1UF

16V

10%

X7R

0402

COMMON

C686

.1UF

16V

10%

X7R

0402

COMMONCOMMON

C714

1UF

6.3V

10%

X7R

0603

COMMON

C648

.47UF

6.3V

10%

X5R

0402

COMMON

PLACE BELOW GPU

FBA_CMD<26..0>

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

16

17

18

19

20

21

22

23

24

25

4<

4<

4<

4<

TP4

TP7

NO STUFF

TP6

NO STUFF

NO STUFF

FBA_PLLVDDG23

4< 4<>

PLACE close to balls

FBx_PLLVDD NOT REQUIRED FOR G73 -- UNSTUFF

C677

.01UF

16V

10%

X7R

0402

NO STUFF

C651

.01UF

16V

10%

X7R

0402

COMMON

C676

.1UF

16V

10%

X7R

0402

NO STUFF

C650

.1UF

16V

10%

X7R

0402

COMMON

C675

1UF

6.3V

10%

X5R

0402

NO STUFF

C649

1UF

6.3V

10%

X5R

0402

COMMON

Rtop

Rbot

FBVDDQ

1K

R5761K

R577

GND

4<>

4<>

NO STUFF

1%

0402

NO STUFF

1%

0402

4<>

4<>

DDR3:

www.vinafix.vn

G73 550/600MHZ 256MB DDR3 16MX32 VGA+DVI-I+HDTVOUT

FBA MEMORY INTERFACE, GPU FBVDD/Q DECOUPLING CAPS

FBVDDQ

GND

GND

240R@100MHz

LB506

GND

GND

240R@100MHz

LB507

NET

FBA_PLLVDD

FBA_PLLAVDD

FBA_PLLAVDD_R

MIN_LINE_WIDTH

10MIL

10MIL

10MIL

FBVDDQ

GND

C866

10UF

6.3V

20%

X5R

0805

COMMON

C600

10UF

6.3V

20%

X5R

0805

COMMON

C602

10UF

6.3V

20%

X5R

0805

COMMON

C609

10UF

6.3V

20%

X5R

0805

COMMON

PLACE MIDWAY BETWEEN GPU AND MEMORY

PEX3V3

NO STUFFBEAD_0402

COMMONBEAD_0402

C687

4.7UF

6.3V

10%

X5R

0603

NO STUFF

PEX1V2

GND

C637

4.7UF

6.3V

10%

X5R

0603

COMMON

GND

602-10456-0001-200

p456

rjacoby

3 OF 21

13-JAN-2006

Page 4

ININININBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBI

BI

RDQS

WDQS

DQ0

DQ4

DQ3

DQ2

DQ1

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

DQ0

DQ4

DQ3

DQ2

DQ1

DQ5

DQ6

DQ7

DQM

IN

IN

MIRRORNONMIRROR

VDD

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSS

VREF

VREF

VSS

CKE

BA2

CAS

WE

CS

RAS

BA0

BA1

A7

A8/AP

A3

A11

A2

A1

A0

A9

A6

A5

A4

A10

RAS

CAS

A0

CS

WE

A5

A4

A3

A2

A1

A8/AP

A10

A11

BA0

BA1

A7

A6

A9

BA2

CKE

CLK

CLK

NC/RFU

NC/RFU

NC/RFU

MIRROR

RESET

ZQ

VDDA

VDDA

VSSA

VSSA

RDQS

WDQS

DQ0

DQ4

DQ3

DQ2

DQ1

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

DQ0

DQ4

DQ3

DQ2

DQ1

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

DQ0

DQ4

DQ3

DQ2

DQ1

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

DQ0

DQ4

DQ3

DQ2

DQ1

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

DQ0

DQ4

DQ3

DQ2

DQ1

DQ5

DQ6

DQ7

DQM

RDQS

WDQS

DQ0

DQ4

DQ3

DQ2

DQ1

DQ5

DQ6

DQ7

DQM

INININ

MIRRORNONMIRROR

VDD

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSSQ

VSS

VREF

VREF

VSS

CKE

BA2

CAS

WE

CS

RAS

BA0

BA1

A7

A8/AP

A3

A11

A2

A1

A0

A9

A6

A5

A4

A10

RAS

CAS

A0

CS

WE

A5

A4

A3

A2

A1

A8/AP

A10

A11

BA0

BA1

A7

A6

A9

BA2

CKE

CLK

CLK

NC/RFU

NC/RFU

NC/RFU

MIRROR

RESET

ZQ

VDDA

VDDA

VSSA

VSSA

BIBIBI

BI

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

FrameBuffer: Partition A 8Mx32 BGA136 DDR3

DDR3:

DDR3: CKE DETERMINES THE ODT VALUE FOR CMD PINS

ZQ = 6x desired output

Impedence of DQ drivers

Impedence = 240 / 6 = 40 ohm

CKE = 0 --> ODT = ZQ/2

CKE = 1 --> ODT = ZQ

FBVDDQ

LB503

LB502

BEAD_0402

BEAD_0402

3> 4<>

Low Sub-Partition

COMMON

COMMON

FBA_CMD<26..0>

3>

4<

3>

4<

240R@100MHz

240R@100MHz

4<>

4<>

4<>

4<>

1

10

11

8

19

25

22

24

0

2

21

16

23

20

17

9

12

3

7

18

15

R546

10K

5%

0402

COMMON

GND

3<>

3<>

3<>

3>

A-CS0-LOW-32bit

U7

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

CHANGED

FBA_CMD<1>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<8>

CS0

FBA_CMD<19>

FBA_CMD<25>

FBA_CMD<22>

FBA_CMD<24>

FBA_CMD<0>

FBA_CMD<2>

FBA_CMD<21>

FBA_CMD<16>

FBA_CMD<23>

FBA_CMD<20>

FBA_CMD<17>

FBA_CMD<9>

FBA_CMD<12>

FBA_CMD<3>

FBA_CMD<7>

FBA_CMD<18>

FBA_CLK0

FBA_CLK0*

FBA_CMD<15>

SNN_FBA0_NC1

SNN_FBA0_NC2

H3

F4

H9

F9

K4

H2

K3

M4

K9

H11

K10

L9

K11

M9

L4

G4

G9

H10

H4

J11

J10

J2

J3

V4

GND

V9

A9

A4

FBA_ZQ0

R538

10K

5%

0402

COMMON

GND

FBA_VDDA0

FBA_VDDA1

C514

.047UF

16V

10%

X7R

0402 0402

COMMON

R544

243

1%

0402

COMMON

GND

K12

C597

.047UF

16V

10%

X7R

COMMON

J12

FBAD<63..0>

FBADQM<7..0>

FBADQS_RN<7..0>

FBADQS_WP<7..0>

K1

J1

FBADQM<0>

0

FBADQM<1>

1

FBADQM<2>

2

FBADQM<3>

3

FBADQM<4>

4

FBADQM<5>

5

FBADQM<6>

6

FBADQM<7>

7

FBADQS_RN<0>

0

FBADQS_RN<1>

1

FBADQS_RN<2>

2

FBADQS_RN<3>

3

FBADQS_RN<4>

4

FBADQS_RN<5>

5

FBADQS_RN<6>

6

FBADQS_RN<7>

7

FBADQS_WP<0>

0

FBADQS_WP<1>

1

FBADQS_WP<2>

2

FBADQS_WP<3>

3

FBADQS_WP<4>

4

FBADQS_WP<5>

5

FBADQS_WP<6>

6

FBADQS_WP<7>

7

FBVDDQ

F1

M1

A2

V2

A11

V11

F12

M12

A1

C1

E1

N1

R1

V1

C4K2

E4

J4

N4

R4

C9

E9

J9

N9

R9

A12

C12

E12

N12

R12

V12

B1

D1

P1

T1

G2

L2

B4

D4

P4

T4

B9

D9

P9

T9

G11

L11

B12

D12

P12

T12

G1

L1

A3

V3

A10

V10

G12

L12

FBA_VREF0

H1

FBA_VREF1H12

VREF = FBVDDQ * R2/(R1 + R2)

VREF = 0.70 * FBVDDQ

DDR3:

1.26V = 1.8V * 1.3K/(511 + 1.3K)

1.4V = 2.0V * 1.3K/(511 + 1.3K)

FBAD<0>

0

FBAD<1>

1

FBAD<2>

2

FBAD<3>

3

FBAD<4>

4

FBAD<5>

5

FBAD<6>

6

FBAD<7>

7

FBADQM<0>

FBADQS_RN<0>

FBADQS_WP<0>

FBAD<32>

32

FBAD<33>

33

FBAD<34>

34

FBAD<35>

35

FBAD<36>

36

FBAD<37>

37

FBAD<38>

38

FBAD<39>

39

FBADQM<4>

FBADQS_RN<4>

FBADQS_WP<4>

FBA Partition

136BGA CMD Mapping

ADDR

CMD

RAS*

CMD1

CAS*

CMD10

WE*

CMD11

CKE

CMD18

RESET

CMD15

CS0*

CMD8

A<0>

CMD19

A<1>

CMD25

A<2>CMD22

A<3>

CMD24

A<4>

CMD0

A<5>

CMD2

A<2>

CMD4

A<3>

CMD6

A<4>

CMD5

A<5>

CMD13

A<6>

CMD21

A<7>

CMD16

A<8>

CMD23

A<9>

CMD20

A<10

CMD17

A<11>

CMD9

BA0

CMD12

BA1

CMD3

BA2

CMD7

GND

FBVDDQ

R556

511

R1

1%

0402

COMMON

R557

1.3K

COMMON

R11

T11

R10

T10

N11

M11

L10

M10

N10

P10

P11

L3

M2

M3

N2

T3

R2

T2

R3

N3

P3

P2

0402

1%

GND

U7

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

CHANGED

U8

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

CHANGED

C596

.1UF

R2

16V

10%

X7R

0402

COMMON

Low Sub-Partition

Hi Sub-Partition

FBVDDQ

R54

511

1%

0402

COMMON

R55

1.3K

0402

COMMON

GND

8

9

10

11

12

13

14

15

40

41

42

43

44

45

46

47

Hi Sub-Partition

ZQ = 6x desired output

DDR3:

impedence of DQ drivers

Impedence = 240 / 6 = 40 ohm

FBVDDQ

BEAD_0402

LB504

BEAD_0402

R1

C57

.1UF

R2

16V1%

10%

X7R

0402

COMMON

FBAD<8>

FBAD<9>

FBAD<10>

FBAD<11>

FBAD<12>

FBAD<13>

FBAD<14>

FBAD<15>

FBADQS_RN<1>

FBADQS_WP<1>

FBAD<40>

FBAD<41>

FBAD<42> F10

FBAD<43>

FBAD<44>

FBAD<45>

FBAD<46>

FBAD<47>

FBADQM<5>

FBADQS_RN<5>

FBADQS_WP<5>

B10

G10

E11

F11

C10

C11

B11

E10

D10

D11

LB8

T3

R2

R3

T2

M2

N2

L3

M3

N3FBADQM<1>

P3

P2

FBA_CMD<26..0>

4< 3>

4< 3>

FBVDDQ

240R@100MHz

COMMON

240R@100MHz

COMMON

U7

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

CHANGED

U8

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

CHANGED

7

8

18

10

5

13

21

20

19

25

4

9

17

6

23

16

3

12

1

11

15

GND

FBAD<16>

16

FBAD<17>

17

FBAD<18>

18

FBAD<19>

19

FBAD<20>

20

FBAD<21>

21

FBAD<22>

22

FBAD<23>

23

FBADQM<2>

FBADQS_RN<2>

FBADQS_WP<2>

FBAD<48>

48

FBAD<49>

49

FBAD<50> R11

50

FBAD<51>

51

FBAD<52>

52

FBAD<53>

53

FBAD<54>

54

FBAD<55>

55

FBADQM<6>

FBADQS_RN<6>

FBADQS_WP<6>

CS0

FBA_CMD<5>

FBA_CMD<13>

FBA_CMD<4>

FBA_CMD<6>

SNN_FBA1_NC1

SNN_FBA1_NC2

GND

FBA_VDDA2

FBA_VDDA3

C598

.047UF

16V

10%

X7R

0402

COMMON

FBA_CMD<7>

FBA_CMD<8>

FBA_CMD<18>

FBA_CMD<10>

FBA_CMD<21>

FBA_CMD<20>

FBA_CMD<19>

FBA_CMD<25>

FBA_CMD<9>

FBA_CMD<17>

FBA_CMD<23>

FBA_CMD<16>

FBA_CMD<3>

FBA_CMD<12>

FBA_CMD<1>

FBA_CMD<11>

FBA_CLK1

FBA_CLK1*

FBA_CMD<15>

FBA_ZQ1

R529

243

1%

0402

COMMON

B2

E2

C2

B3

C3

F3

G3

F2

E3

D3

D2

R10

M11

T11

N11

T10

M10

L10

N10

P10

P11

H11

K10

K11

H10

J11

J10

GND

K12

C58

.047UF

16V

10%

X7R

0402

COMMON

J12

U7

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

CHANGED

U8

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

CHANGED

A-CS0-HI-32bit

U8

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

CHANGED

H3

F4

H9

F9

K4

H2

K3

M4

K9

L9

M9

K2

L4

G4

G9

H4

J2

J3

V4

V9

A9

A4

K1

J1

24

25

26

27

28

29

30

31

56

57

58

59

60

61

62

63

FBAD<24>

FBAD<25>

FBAD<26>

FBAD<27>

FBAD<28>

FBAD<29>

FBAD<30>

FBAD<31>

FBADQM<3>

FBADQS_RN<3>

FBADQS_WP<3>

FBAD<56>

FBAD<57>

FBAD<58>

FBAD<59>

FBAD<60>

FBAD<61>

FBAD<62>

FBAD<63>

FBADQM<7>

FBADQS_RN<7>

FBADQS_WP<7>

FBVDDQ

F1

M1

A2

V2

A11

V11

F12

M12

A1

C1

E1

N1

R1

V1

C4

E4

J4

N4

R4

C9

E9

J9

N9

R9

A12

C12

E12

N12

R12

V12

B1

D1

P1

T1

G2

L2

B4

D4

P4

T4

B9

D9

P9

T9

G11

L11

B12

D12

P12

T12

G1

L1

A3

V3

A10

V10

G12

L12

H1

H12

VREF = FBVDDQ * R2/(R1 + R2)

F11

F10

B11

B10

C11

E11

G10

C10

E10

D10

D11

GND

FBA_VREF2

FBA_VREF3

VREF = 0.70 * FBVDDQDDR3:

1.26V = 1.8V * 1.3K/(511 + 1.3K)

1.4V = 2.0V * 1.3K/(511 + 1.3K)

U7

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

CHANGED

U8

DDR3BGA136

PACK_TYPE=BGA136

VERSION=BGA136

CHANGED

B3

F3

C2

C3

F2

E2

B2

G3

E3

D3

D2

R57

511

0402

COMMON

R56

1.3K

0402

COMMON

1%

1%

FBVDDQ

GND

R1

R2

4< 3>

4< 3>

4< 3>

4< 3>

3<>

4<>

3>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

3<>

4<>

4<> 3<>

3<>

4<>

3<>

4<>

3>

4<

3>

4<

3>

4<

3>

4<

3>

4<

3>

4<

3>

4<

3>

4<

3>

4<

3>

4<

3>

4<

3>

4<

C59

.1UF

16V

10%

X7R

0402

COMMON

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBAD<63..0>

FBADQM<7..0>

FBADQS_RN<0>

FBADQS_WP<0>

FBADQS_RN<1>

FBADQS_WP<1>

FBADQS_RN<2>

FBADQS_WP<2>

FBADQS_RN<3>

FBADQS_WP<3>

FBADQS_RN<4>

FBADQS_WP<4>

FBADQS_RN<5>

FBADQS_WP<5>

FBADQS_RN<6>

FBADQS_WP<6>

FBADQS_RN<7>

FBADQS_WP<7>

FBA_CMD<0>

FBA_CMD<2>

FBA_CMD<4..6>

FBA_CMD<13>

FBA_CMD<22>

FBA_CMD<24>

FBA_CMD<1>

FBA_CMD<3>

FBA_CMD<7..12>

FBA_CMD<14..21>

FBA_CMD<23>

FBA_CMD<25..26>

FBA_VREF0

FBA_VREF1

FBA_VREF2

FBA_VREF3

FBVDDQ

R562

511

1%

0402

COMMON

R560

1.3K

1%

0402

COMMON

GND

FBA_CMD<26..0>

R1

R2

DIFFPAIRNET

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBADQS_RN0

FBADQS_RN0

FBADQS_RN1

FBADQS_RN1

FBADQS_RN2

FBADQS_RN2

FBADQS_RN3

FBADQS_RN3

FBADQS_RN4

FBADQS_RN4

FBADQS_RN5

FBADQS_RN5

FBADQS_RN6

FBADQS_RN6

FBADQS_RN7

FBADQS_RN7

MIN_LINE_WIDTH

C594

.1UF

16V

10%

X7R

0402

COMMON

Termination for Sub-Partition and CLK

MUST BE PLACED as close as possible to

the BGA memory on the line BEFORE the

MEMORY pin!!

Minimize the stub length!!

FBA_CMD<2>

2

0

24

22

13

4

5

6

FBA_CMD<0>

FBA_CMD<24>

FBA_CMD<22>

FBA_CMD<13>

FBA_CMD<4>

FBA_CMD<5>

FBA_CMD<6>

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

120

COMMON

120

COMMON

120

COMMON

120

COMMON

120

COMMON

120

COMMON

120

COMMON

120

COMMON

240

CHANGED

240

CHANGED

240

CHANGED

240

CHANGED

R525

0402

5%

R536

0402

5%

R545

0402

5%

R537

0402

5%

R528

0402

5%

R539

0402

5%

R531

0402

5%

R542

0402

5%

R526

0402

5%

R527

0402

5%

R551

0402

5%

R549

0402

5%

80DIFF

80DIFF

80DIFF

80DIFF

40OHM

40OHM

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

80DIFF

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

50OHM

12MIL

12MIL

12MIL

12MIL

FBVDDQ

G73 - UNSTUFF 0 OHM PUs, STUFF 0.01uf CAPS

NV43 - UNSTUFF CAPS, STUFF 0 OHM PUs

FBA_CLK0_PU

FBA_CLK1_PU

NV_CRITICAL_NETNV_IMPEDANCE

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

180DIFF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

FBVDDQ

R550

R522

.01UF

.01UF

10%

10%

0402

0402

CHANGED

CHANGED

www.vinafix.vn

G73 550/600MHZ 256MB DDR3 16MX32 VGA+DVI-I+HDTVOUT

FBA 8Mx32 DDR3 MEMORIES, FBA COMMAND BUS PU'S, FBA CLK TERMS

602-10456-0001-200

p456

rjacoby

4 OF 21

13-JAN-2006

Page 5

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

FRAME BUFFER: PARTITION A DECOUPLING

Decoupling for FBA 0..31

PLACE NEAR MEMORY FBVDDQ PINS

Decoupling for FBA 32..63

FBVDDQ

PLACE NEAR MEMORY FBVDD PINS

FBVDDQ

C531C517

.1UF

16V

10%

X7R

0402

COMMON

C572

.1UF

16V

10%

X7R

0402

COMMON

C542

.1UF

16V

10%

X7R

0402

COMMON

C543

.1UF

16V

10%

X7R

0402

COMMON

C563

.01UF

25V

10%

X7R

0402

COMMON

.1UF

16V

10%

X7R

0402

COMMON

C580

.47UF

6.3V

10%

X5R

0402

COMMON

C560

.1UF

16V

10%

X7R

0402

COMMON

C582

.01UF

25V

10%

X7R

0402

COMMON

C553

.01UF

25V

10%

X7R

0402

COMMON

.1UF

16V

10%

X7R

0402

COMMON

C588

.01UF

16V

X7R

0402

COMMON

C584

.01UF

25V

10%

X7R

0402

COMMON

C568

.1UF

16V

10%

X7R

0402

COMMON

C522

.01UF

25V

10%

X7R

0402

COMMON

.1UF

16V

10%

X7R

0402

COMMON

C552

.01UF

25V

10%10%

X7R

0402

COMMON

C583

.01UF

25V

10%

X7R

0402

COMMON

C530

.01UF

25V

10%

X7R

0402

COMMON

C567

.01UF

25V

10%

X7R

0402

COMMON

C585C561 C551

.47UF

6.3V

10%

X5R

0402

COMMON

C555

.01UF

25V

10%

X7R

0402

COMMON

C562

.01UF

25V

10%

X7R

0402

COMMON

C581

.01UF

25V

10%

X7R

0402

COMMON

C518

.01UF

25V

10%

X7R

0402

COMMON

C587

.01UF

25V

10%

X7R

0402

COMMON

C520

.01UF

25V

10%

X7R

0402

COMMON

C521

.01UF

25V

10%

X7R

0402

COMMON

C519

.01UF

25V

10%

X7R

0402

COMMON

C554

.01UF

25V

10%

X7R

0402

COMMON

C566 C547C529

.01UF

25V

10%

X7R

0402

COMMON

C546

.01UF

25V

10% 10%

X7R

0402

COMMON

C569

.1UF

16V

10%

X7R

0402

COMMON

C527

.01UF

25V

10%

X7R

0402

COMMON

C559

.01UF

25V

10%

X7R

0402

COMMON

.01UF

25V

10%

X7R

0402

COMMON

C565

.01UF

25V

X7R

0402

COMMON

C540

.1UF

16V

10%

X7R

0402

COMMON

C538

.1UF

16V

10%

X7R

0402

COMMON

C592

.01UF

25V

10%

X7R

0402

COMMON

.01UF

25V

10%

X7R

0402

COMMON

C591

.01UF

25V

10%

X7R

0402

COMMON

C593

.01UF

25V

10%

X7R

0402

COMMON

C545

.47UF

6.3V

10%

X5R

0402

COMMON

C575

.01UF

25V

10%

X7R

0402

COMMON

C525

.1UF

16V

10%

X7R

0402

COMMON

C573

.1UF

16V

10%

X7R

0402

COMMON

C524

.01UF

25V

10%

X7R

0402

COMMON

C558

.01UF

25V

10%

X7R

0402

COMMON

C557

.01UF

25V

10%

X7R

0402

COMMON

.01UF

16V

10%

X7R

0402

COMMON

C589

.01UF

25V

10%

X7R

0402

COMMON

C556

.01UF

25V

10%

X7R

0402

COMMON

C526

.01UF

25V

10%

X7R

0402

COMMON

C549

.01UF

25V

10%

X7R

0402

COMMON

C590C523

.01UF

25V

10%

X7R

0402

COMMON

C574

.01UF

25V

10%

X7R

0402

COMMON

C550

.01UF

25V

10%

X7R

0402

COMMON

C576

.01UF

25V

10%

X7R

0402

COMMON

C528

.01UF

25V

10%

X7R

0402

COMMON

FBVDDQ

C541

4.7UF

6.3V

10%

X5R

0603

COMMON

C571

4.7UF

6.3V

10%

X5R

0603

COMMON

C544

1UF

6.3V

10%

X7R

0603

COMMON

C595

1UF

6.3V

10%

X7R

0603

COMMON

GND

GND

G73 550/600MHZ 256MB DDR3 16MX32 VGA+DVI-I+HDTVOUT

FBA MEMORY FBVDD/Q DECOUPLING CAPS

www.vinafix.vn

FBVDDQ

C570

4.7UF

6.3V

10%

X5R

0603

COMMON

C539

4.7UF

6.3V

10%

X5R

0603

COMMON

C516

1UF

6.3V

10%

X7R

0603

COMMON

GND

C599

1UF

6.3V

10%

X7R

0603

COMMON

GND

602-10456-0001-200

p456

rjacoby

5 OF 21

13-JAN-2006

Page 6

BIBIBI

OUT

OUT

OUT

OUT

OUT

BI

3/14 FBC

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBC_CMD6

FBC_CMD5

FBC_CMD4

FBC_CMD3

FBC_CMD2

FBC_CMD0

FBC_CMD1

FBC_CMD7

FBC_CMD26

FBC_CMD25

FBC_CMD24

FBC_CMD23

FBC_CMD22

FBC_CMD21

FBC_CMD20

FBC_CMD19

FBC_CMD18

FBC_CMD17

FBC_CMD16

FBC_CMD15

FBC_CMD14

FBC_CMD13

FBC_CMD12

FBC_CMD11

FBC_CMD10

FBC_CMD9

FBC_CMD8

RFU

RFU

FBC_CLK0

FBC_CLK0

FBC_CLK1

FBC_CLK1

FBC_DEBUG

FBC_REFCLK

FBC_REFCLK

FBCAL_TERM_GND

FBC_PLLVDD

FBC_PLLAVDD

FBC_PLLGND

FBCAL_PD_VDDQ

FBCAL_PU_GND

FBCD17

FBCD16

FBCD15

FBCD14

FBCD13

FBCD12

FBCD11

FBCD10

FBCD2

FBCD1

FBCD0

FBCD3

FBCD7

FBCD6

FBCD5

FBCD4

FBCD8

FBCD9

FBCD18

FBCD38

FBCD37

FBCD36

FBCD35

FBCD34

FBCD33

FBCD32

FBCD31

FBCD30

FBCD29

FBCD28

FBCD27

FBCD26

FBCD25

FBCD24

FBCD23

FBCD22

FBCD21

FBCD20

FBCD19

FBCD58

FBCD57

FBCD56

FBCD55

FBCD54

FBCD53

FBCD52

FBCD51

FBCD50

FBCD49

FBCD48

FBCD47

FBCD46

FBCD45

FBCD44

FBCD43

FBCD42

FBCD41

FBCD40

FBCD39

FBCD59

FBCDQS_WP3

FBCDQS_WP2

FBCDQS_WP1

FBCDQS_WP0

FBCDQM7

FBCDQM6

FBCDQM5

FBCDQM4

FBCDQM3

FBCDQM2

FBCDQM1

FBCDQM0

FBCD63

FBCD62

FBCD61

FBCD60

FBCDQS_WP7

FBCDQS_RN7

FBCDQS_RN6

FBCDQS_RN5

FBCDQS_RN4

FBCDQS_RN3

FBCDQS_RN2

FBCDQS_WP4

FBCDQS_WP5

FBCDQS_WP6

FBCDQS_RN0

FBCDQS_RN1

FB_VREF2

OUTBIBI

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

C778

.1UF

16V

10%

X7R

0402

NO STUFF

C749

.1UF

16V

10%

X7R

0402

COMMON

7<>

7<>

7<>

7<>

FBCD<63..0>

FBCDQM<7..0>

FBCDQS_WP<7..0>

FBCDQS_RN<7..0>

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

SNN_FBC_VREF

FBCD<0>

FBCD<1>

FBCD<2>

FBCD<3>

FBCD<4>

FBCD<5>

FBCD<6>

FBCD<7>

FBCD<8>

FBCD<9>

FBCD<10>

FBCD<11>

FBCD<12>

FBCD<13>

FBCD<14>

FBCD<15>

FBCD<16>

FBCD<17>

FBCD<18>

FBCD<19>

FBCD<20>

FBCD<21>

FBCD<22>

FBCD<23>

FBCD<24>

FBCD<25>

FBCD<26>

FBCD<27>

FBCD<28>

FBCD<29>

FBCD<30>

FBCD<31>

FBCD<32>

FBCD<33>

FBCD<34>

FBCD<35>

FBCD<36>

FBCD<37>

FBCD<38>

FBCD<39> A31

FBCD<40>

FBCD<41>

FBCD<42>

FBCD<43>

FBCD<44>

FBCD<45>

FBCD<46>

FBCD<47>

FBCD<48>

FBCD<49>

FBCD<50>

FBCD<51>

FBCD<52>

FBCD<53>

FBCD<54>

FBCD<55>

FBCD<56>

FBCD<57>

FBCD<58>

FBCD<59>

FBCD<60>

FBCD<61>

FBCD<62>

FBCD<63>

FBCDQM<0>

FBCDQM<1>

FBCDQM<2>

FBCDQM<3>

FBCDQM<4>

FBCDQM<5>

FBCDQM<6>

FBCDQM<7>

FBCDQS_WP<0>

FBCDQS_WP<1>

FBCDQS_WP<2>

FBCDQS_WP<3>

FBCDQS_WP<4> A29

FBCDQS_WP<5>

FBCDQS_WP<6>

FBCDQS_WP<7>

FBCDQS_RN<0>

FBCDQS_RN<1>

FBCDQS_RN<2>

FBCDQS_RN<3>

FBCDQS_RN<4>

FBCDQS_RN<5>

FBCDQS_RN<6>

FBCDQS_RN<7>

F10

D12

E12

D11

C10

B10

A10

C11

C12

A11

B11

B28

C27

C26

B26

C30

B31

C29

D28

D27

F26

D24

E23

E26

E24

F23

B23

A23

C25

C23

A22

C22

C21

B22

E22

D22

D21

E21

E18

D19

D18

E19

E11

C28

F24

C24

E20

E10

D25

B25

F20

B29

E25

A25

F21

B7

A7

C7

A2

B2

C4

A5

B5

F9

D9

E8

D8

E7

F7

D6

D5

D3

E4

C3

B4

C8

A4

F5

C9

C5

E5

B8

C6

E9

E6

A8

U5

G73-GT-N-A1

BGA820

CHANGED

A28

AA23

AB23

H16

H17

J10

J23

J24

J9

K11

K12

K21

K22

K24

K9

L23

M23

T25

U25

C13

A16

A13

B17

B20

A19

B19

E16

A14

C15

B16

F17

C19

D15

C17

A17

C16

D14

F16

C14

C18

E14

B13

E15

F15

A20

E13

F13

F18

E17

C20

D1

F12

B1

C1

G8

G10

G9

K26

H26

J26

FBC_CMD<0>

FBC_CMD<1>

FBC_CMD<2>

FBC_CMD<3>

FBC_CMD<4>

FBC_CMD<5>

FBC_CMD<6>

FBC_CMD<7>B14

FBC_CMD<8>

FBC_CMD<9>

FBC_CMD<10>

FBC_CMD<11>

FBC_CMD<12>

FBC_CMD<13>

SNN_FBC_CMD<14>

FBC_CMD<15>

FBC_CMD<16>

FBC_CMD<17>

FBC_CMD<18>

FBC_CMD<19>

FBC_CMD<20>

FBC_CMD<21>

FBC_CMD<22>

FBC_CMD<23>

FBC_CMD<24>

FBC_CMD<25>

SNN_FBC_CMD<26>

FBC_CLK0

FBC_CLK0*

FBC_CLK1

FBC_CLK1*

SNN_FBC_DBI0

SNN_FBC_DBI1

SNN_FBC_DEBUG

LTP_FBC_REFCLK

LTP_FBC_REFCLK*

FBC_PLLVDD

FBC_PLLAVDD

GND

FBCAL_PD

FBCAL_PU

FBCAL_TERM

Place near BGA

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

16

17

18

19

20

21

22

23

24

25

NO STUFF

NO STUFF

FBVDDQ

C653

1UF

6.3V

10%

X7R

0603