Page 1

P489-A02 DESIGN - G73, 128/256/512 MB DDR2

VGA, DVI-I, HDMI, SDTV, HDTV, SCART

1

2

3

PAGE SUMMARY:

Page 1: TABLE OF CONTENTS

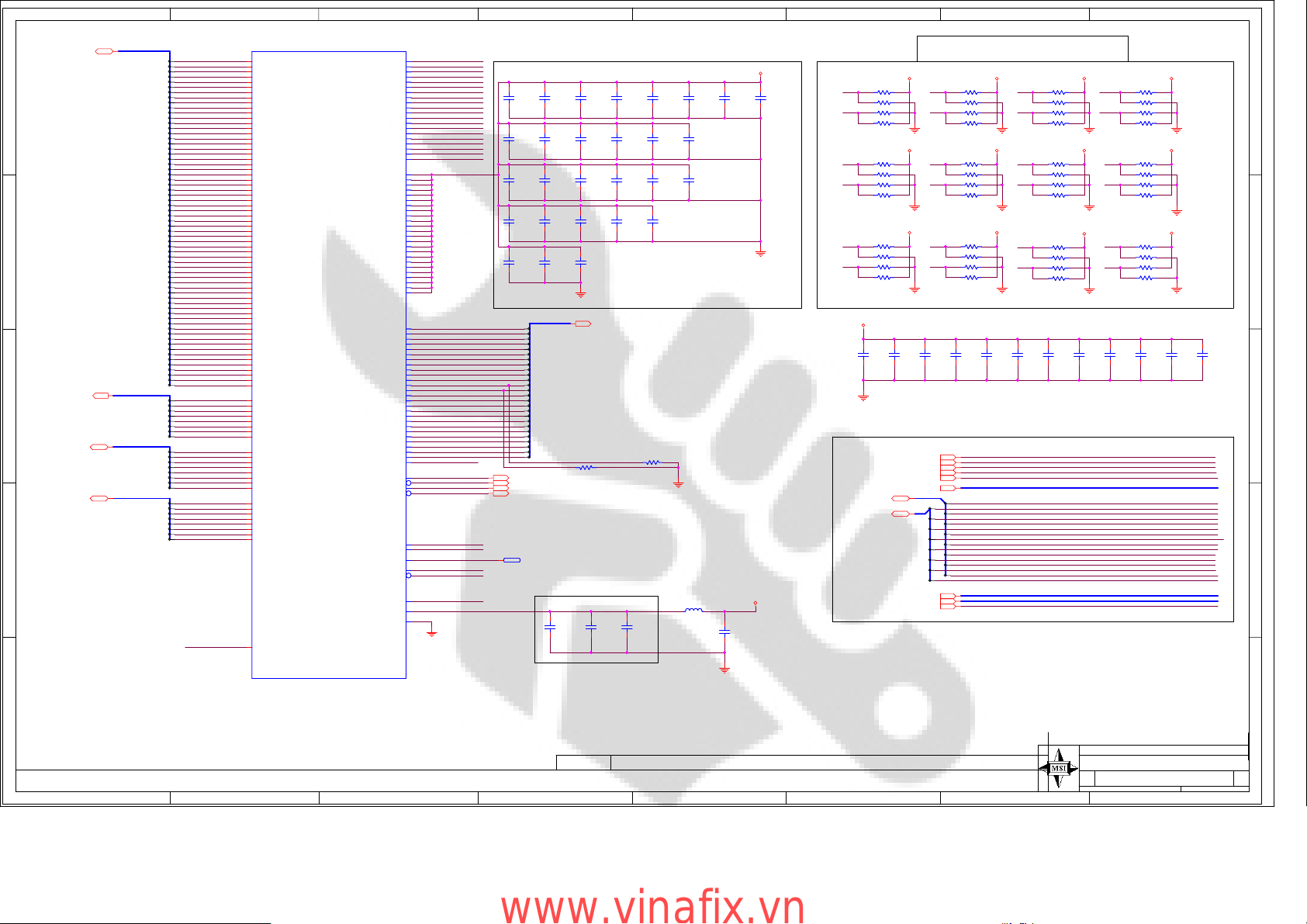

Page 2: PCI EXPRESS 16X, NVVDD DECOUPLING CAPS,PEX_IOVDD/Q DECOUPLING CAPS

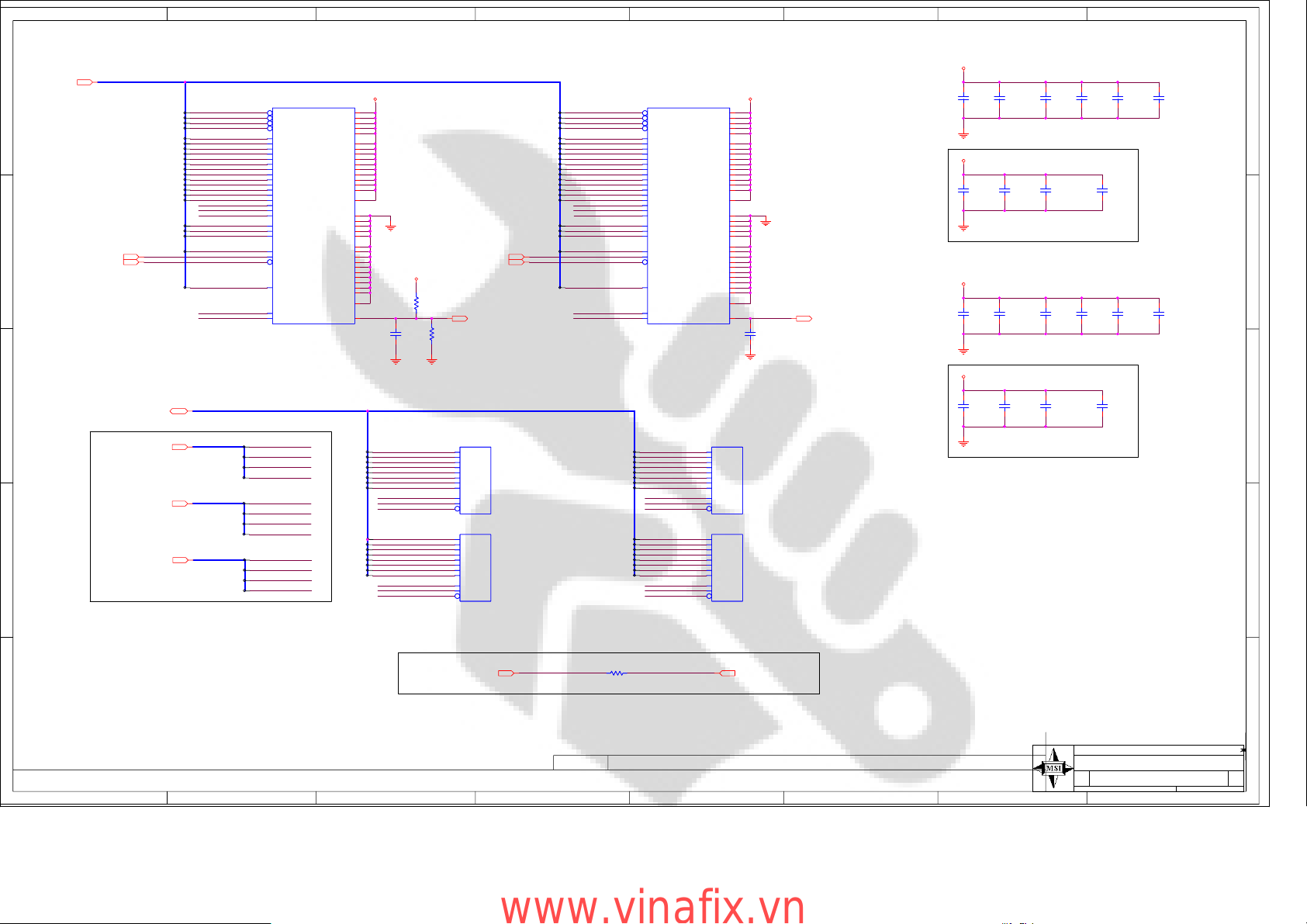

Page 3: FBA MEMORY INTERFACE, GPU FBVDDQ DECOUPLING CAPS

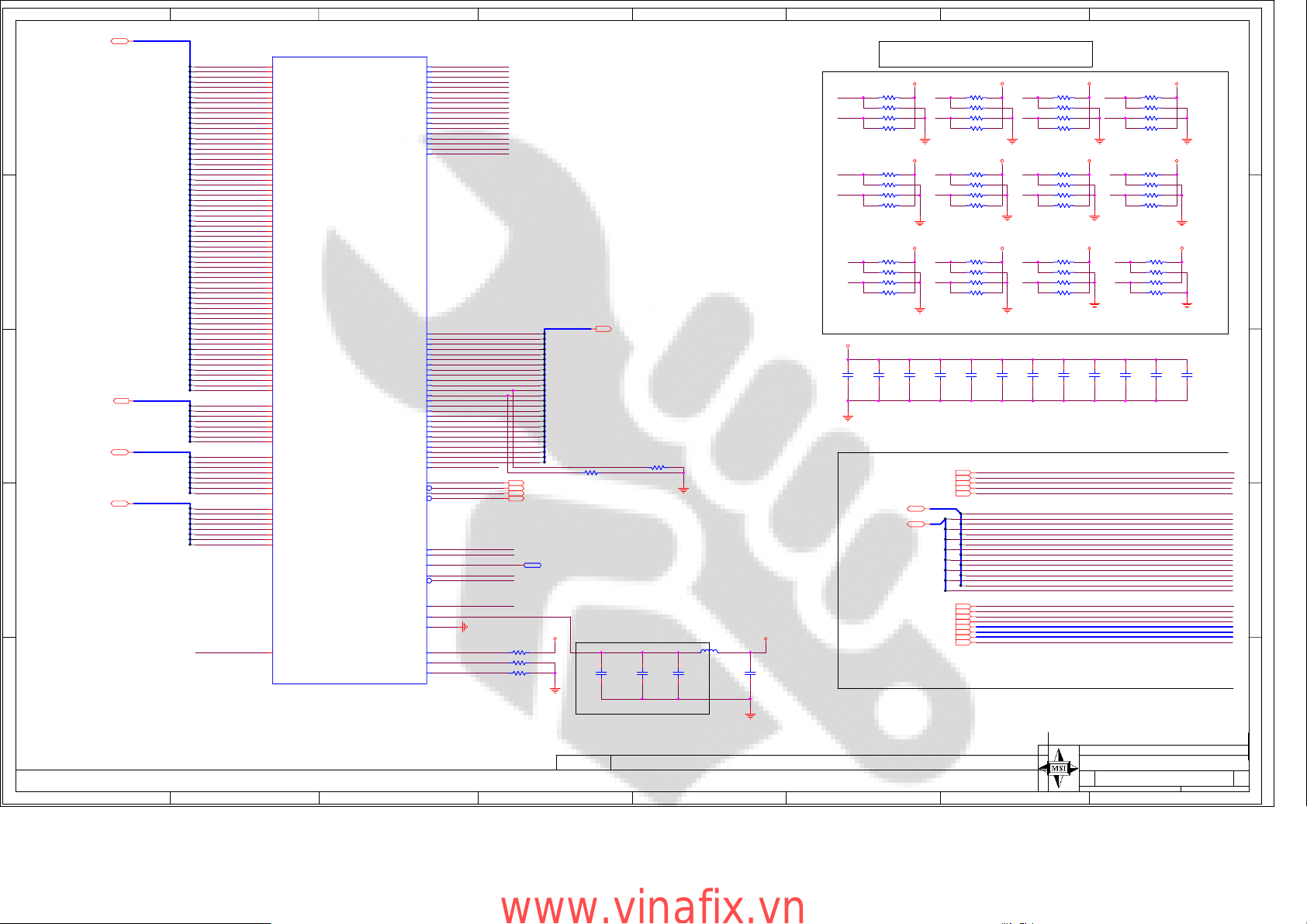

Page 4: FBA 16Mx16 DDR2 MEMORIES, 1ST BANK 0..31

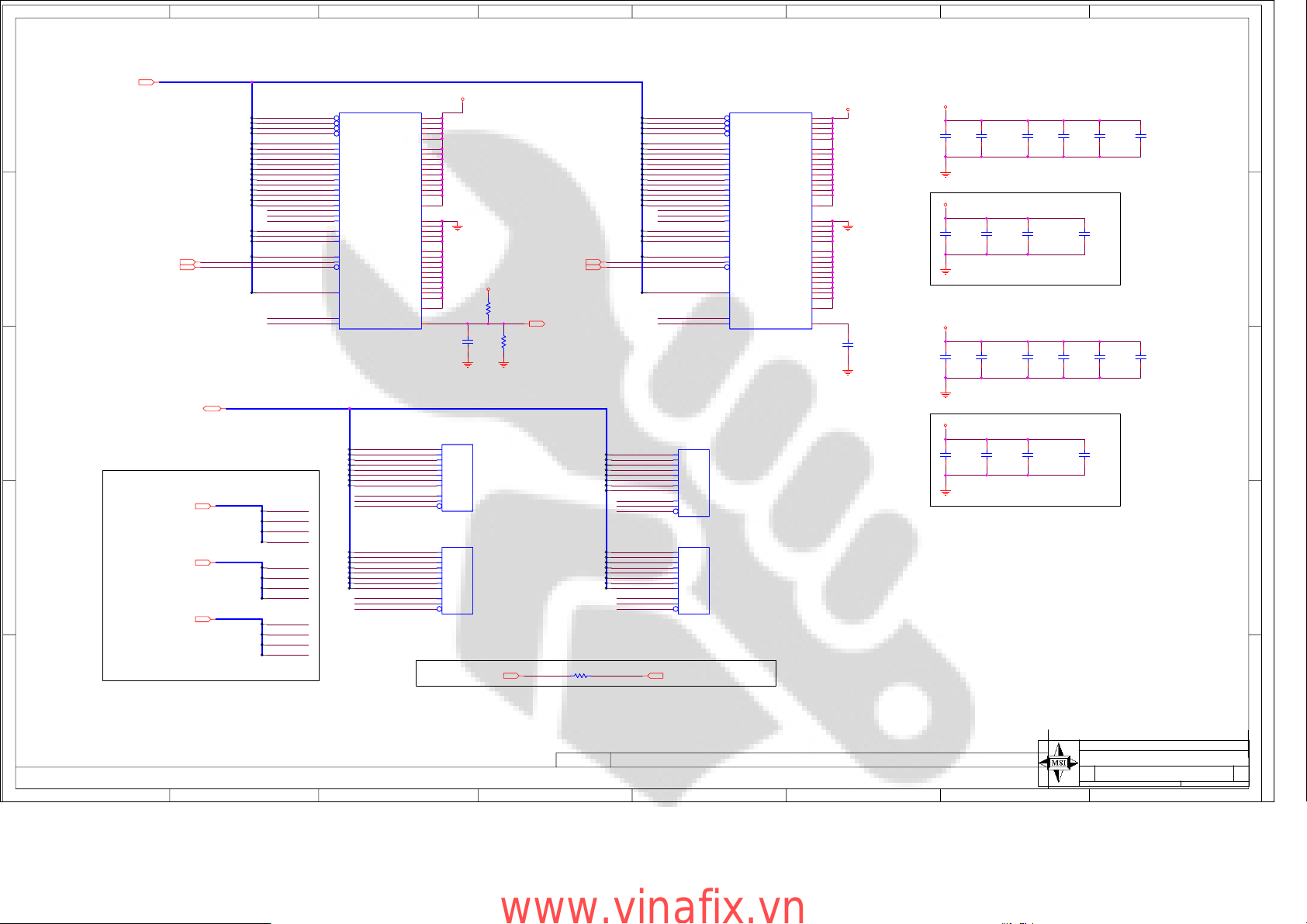

Page 5: FBA 16Mx16 DDR2 MEMORIES, 1ST BANK 32..63

Page 6: FBC MEMORY INTERFACE

Page 7: FBC 16MX16 DDR2 MEMORIES, 2ND BANK 0..31

Page 8: FBC 16Mx16 DDR2 MEMORIES, 2ND BANK 32..63

Page 9: DACA FILTERS, DACA SYNC BUFFERS & DB15 SOUTH

Page 10: DACB, DACC SYNC BUFFER

Page 11: TMDS LINK A & B, DVI CONNECTOR

Page 12: TMDS LINK C, HDMI CONNECTOR MID

Page 13: MIOA & MIOB, SLI CONNECTOR

Page 14: CONEXANT CX25875 VIDEO ENCODER, SCART, COMPONENT CONNECTOR

Page 15: GPU GND CONNECTION, XTAL

Page 16: JTAG, BIOS ROM, HDCP ROM, FAN CONTROL, GPIO's

Page 17: BIOS STRAPS & MECHANICALS

Page 18: POWER SUPPLY I: DDC5V, TMDS_IO_VDD, A2V5, A3V3

Page 19: POWER SUPPLY II: ISL6549 FBVDDQ, PEX1V2

Page 20: POWER SUPPLY III: ISL6549 NVVDD, 5V

V058-0A History

Page 2: reserved PCI-E B12 for M/B SPDIF IN

Page 10: add DACC SYNC BUFFER parts for new slim VGA

Page 14: add SCART J15 for 4073, removed SVIDEO/COMPOSIT connectors.

Page 16: change J6_1 for MSI SPDIF IN housing

Page 19: L10 co-layout L27 dip choke

Page 11: add common mode choke

Page 13: removed CN1 SLI CONNECTOR, change MIOA_IOVDD to 3V3_PEX

Page 17: change MIOAD0/MIOAD2 to 3V3_PEX

Page 12: add HDMI using common mode choke

V058-10 History

Page 14: add SCART Vcc 2.5V.

HGFEDCBA

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

E GC

NVPN

600-10489-9998-200

600-10489-0000-200

600-10489-0001-200

<UNDEFINED>

<UNDEFINED>

<UNDEFINED><UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

VARIANT ASSEMBLY

SKU

B

BASE

1

0000

2

0001

3

<UNDEFINED>

4

<UNDEFINED>

5

6

<UNDEFINED>

7

<UNDEFINED>

8

<UNDEFINED>

9

<UNDEFINED>

10

<UNDEFINED>

11

<UNDEFINED>

12

<UNDEFINED>

13

<UNDEFINED>

14

<UNDEFINED>

15

<UNDEFINED>

G73 ALL COMPONENT BOM

TABLE OF CONTENTS

G73 ALL COMPONENT BOM

G73 400/400Mhz 256Mb 128bit DDR2, DVI-I+HDMI+SDTV+SCART

G73 400/400Mhz 256Mb 126bit DDR2, DVI-I+HDMI+SDTV+YPrPb

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

V058

V058

V058

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date:

Date:

Date:

Tuesday, August 22, 2006

Tuesday, August 22, 2006

Tuesday, August 22, 2006

123

123

123

Sheet of

Sheet of

Sheet of

4

5

10

10

10

Page 2

Place Close to fingers

3V3_PEX

C58

C58

C64

C59

C59

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

1

GND

3V3AUX

C67

C67

.1UF

.1UF

25V

25V

10%

10%

X7R

X7R

0603

0603

COMMON

COMMON

GND

2

3

4

5

SPDIF_IN

reserved MSI M/B use SPDIF IN

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C64

10UF

10UF

.1UF

.1UF

16V

16V

16V

16V

CN2

CN2

NONPHY-X16

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

SNN_PE_PRSNT2_A

SNN_PE_PRSNT2_B

SNN_PE_RSVD3

SNN_PE_RSVD4

SNN_PE_RSVD5

SNN_PE_PRSNT2_C

SNN_PE_RSVD6

SNN_PE_RSVD7

SNN_PE_RSVD8

12V_PEX

3V3_PEX

3V3AUX

PRSNT

20%

20%

X5R

X5R

1206

1206

COMMON

COMMON

GND

OUT

NONPHY-X16

CON_X16

CON_X16

@electro_mechanic.con_pci_express(chips):page2_i510

@electro_mechanic.con_pci_express(chips):page2_i510

COMMON

COMMON

B1

+12V

B2

+12V

A2

+12V

A3

+12V

B3

+12V/RSVD

B8

+3V3

A9

+3V3

A10

+3V3

B10

+3V3AUX

A1

PRSNT1

B17

PRSNT2

B12

RSVD

B4

GND

A4

GND

B7

GND

A12

GND

B13

GND

A15

GND

B16

GND

B18

GND

A18

GND

GND

GND

END OF X1

END OF X1

B31

PRSNT2

A19

RSVD

B30

RSVD

A32

RSVD

A20

GND

B21

GND

B22

GND

A23

GND

A24

GND

B25

GND

B26

GND

A27

GND

A28

GND

B29

GND

A31

GND

B32

GND

END OF X4

END OF X4

GND

B48

PRSNT2

A33

RSVD

A34

GND

B35

GND

B36

GND

A37

GND

A38

GND

B39

GND

B40

GND

A41

GND

A42

GND

B43

GND

B44

GND

A45

GND

A46

GND

B47

GND

B49

GND

A49

GND

END OF X8

END OF X8

B81

PRSNT2

A50

RSVD

B82

RSVD

A51

GND

B52

GND

B53

GND

A54

GND

A55

GND

B56

GND

B57

GND

A58

GND

A59

GND

B60

GND

B61

GND

A62

GND

A63

GND

B64

GND

B65

GND

A66

GND

A67

GND

B68

GND

B69

GND

A70

GND

A71

GND

B72

GND

B73

GND

A74

GND

A75

GND

B76

GND

B77

GND

A78

GND

A79

GND

B80

GND

A82

GND

14,16

END OF X16

END OF X16

TRST* JTAG1

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

SMCLK

SMDAT

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

SNN_JT_TRST*

B9

SNN_JT_TCLK

A5

PEXJT_TDIO

A6

A7

SNN_JT_TMS

A8

this resistor stradles the TDI/TDO pair

SNN_PEX_SMCLK

B5

SNN_PEX_SMDAT

B6

SNN_PEX_WAKE*

B11

WAKE

PEX_RST*

A11

PEX_REFCLK

A13

PEX_REFCLK*

A14

PEX_TXX0 PEX_TXX0

A16

PEX_TXX0* PEX_TXX0*

A17

PEX_RX0

B14

PEX_RX0*

B15

PEX_TXX1

A21

PEX_TXX1*

A22

PEX_RX1

B19

PEX_RX1*

B20

PEX_TXX2

A25

PEX_TXX2*

A26

PEX_RX2

B23

PEX_RX2*

B24

PEX_TXX3

A29

PEX_TXX3*

A30

PEX_RX3

B27

PEX_RX3*

B28

PEX_TXX4

A35

PEX_TXX4*

A36

PEX_RX4

B33

PEX_RX4*

B34

PEX_TXX5

A39

PEX_TXX5*

A40

PEX_RX5

B37

PEX_RX5*

B38

PEX_TXX6

A43

PEX_TXX6*

A44

PEX_RX6

B41

PEX_RX6*

B42

PEX_TXX7

A47

PEX_TXX7*

A48

PEX_RX7

B45

PEX_RX7*

B46

PEX_TXX8

A52

PEX_TXX8*

A53

PEX_RX8 PEX_RX8

B50

PEX_RX8* PEX_RX8*

B51

PEX_TXX9

A56

PEX_TXX9*

A57

PEX_RX9

B54

PEX_RX9*

B55

PEX_TXX10

A60

PEX_TXX10*

A61

PEX_RX10

B58

PEX_RX10*

B59

PEX_TXX11

A64

PEX_TXX11*

A65

PEX_RX11

B62

PEX_RX11*

B63

PEX_TXX12

A68

PEX_TXX12*

A69

PEX_RX12

B66

PEX_RX12*

B67

PEX_TXX13

A72

PEX_TXX13*

A73

PEX_RX13

B70

PEX_RX13*

B71

PEX_TXX14

A76

PEX_TXX14*

A77

PEX_RX14

B74

PEX_RX14*

B75

PEX_TXX15

A80

PEX_TXX15*

A81

PEX_RX15

B78

PEX_RX15*

B79

A B D F H

R566

R566

0

0

5%

5%

0402

0402

COMMON

COMMON

COMMON X7R 16V040210%

COMMON X7R 16V040210%

COMMON 16V040210%X7R

COMMON 16V040210%X7R

12V_PEX

C815

C815

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C798 .1UF

C798 .1UF

C791 .1UF

C791 .1UF

C782 .1UF

C782 .1UF

C770 .1UF

C770 .1UF

10%X7R 16V0402COMMON

10%X7R 16V0402COMMON

C756 .1UF

C756 .1UF

C742

C742

0402

0402

C731

C731

040210%X7RCOMMON

040210%X7RCOMMON

C699 .1UF

C699 .1UF

C676 .1UF

C676 .1UF

C658 .1UF

C658 .1UF

C636 .1UF

C636 .1UF

C611 .1UF

C611 .1UF

C602 .1UF

C602 .1UF

C590 .1UF

C590 .1UF

C583 .1UF

C583 .1UF

C576 .1UF

C576 .1UF

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

.1UF

.1UF

16V10%X7RCOMMON

16V10%X7RCOMMON

.1UF

.1UF

16V

16V

16VCOMMON 0402X7R 10%

16VCOMMON 0402X7R 10%

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

16V040210%X7RCOMMON

C814

C814

.1UF

.1UF

25V

25V

10%

10%

X7R

X7R

0603

0603

COMMON

COMMON

R71 200

R71 200

0402 X7R

0402 X7R

0402 X7R10%

0402 X7R10%

C670 .1UF

C670 .1UF

C628

C628

C589

C589

C580 .1UF

C580 .1UF

C573

C573

16X PCIe Interface

C816

C816

10UF

10UF

16V

16V

20%

20%

X5R

X5R

1206

1206

COMMON

COMMON

GND

SNN_PEXCAL_VDDQ

SNN_PEXCAL_GND

PEX_TEST_PLLCLK_OUT

PEX_TEST_PLLCLK_OUT_N

COMMON0402

COMMON0402

5%

5%

C797

.1UFC797

C789

C789

C780

C780

C768

C768

C754 .1UF

C754 .1UF

C739

C739

C727

C694

C694

C651

C651

C606

C606

C600

C600

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UFC727

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

COMMONX7R0402 16V 10%

COMMONX7R0402 16V 10%

10%0402

COMMON16V X7R

10%0402

COMMON16V X7R

COMMON10%16V

COMMON10%16V

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

COMMONX7R10%16V0402

COMMONX7R10%16V0402

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

X7R COMMON10%16V0402

X7R COMMON10%16V0402

COMMON16V

COMMON16V

COMMONX7R10%16V0402

COMMONX7R10%16V0402

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

COMMONX7R10%

16V0402

COMMONX7R10%16V0402

COMMONX7R10%16V0402

16V COMMON

X7R10%0402

16V COMMON

X7R10%0402

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

AH15

AG12

AH13

AM12

AM11

AH14

AJ14

AJ15

AK15

AK13

AK14

AH16

AG16

AM14

AM15

AG17

AH17

AL15

AL16

AG18

AH18

AK16

AK17

AK18

AJ18

AL17

AL18

AJ19

AH19

AM18

AM19

AG20

AH20

AK19

AK20

AG21

AH21

AL20

AL21

AK21

AJ21

AM21

AM22

AJ22

AH22

AK22

AK23

AG23

AH23

AL23

AL24

AK24

AJ24

AM24

AM25

AJ25

AH25

AK25

AK26

AH26

AG26

AL26

AL27

AK27

AJ27

AM27

AM28

AJ28

AH27

AL28

AL29

G1A

G1A

@digital.u_gpu_g3(chips):page2_i564

@digital.u_gpu_g3(chips):page2_i564

BGA820

BGA820

COMMON

COMMON

1/14 PCI_EXPRESS

1/14 PCI_EXPRESS

PEX_RST

RFU

RFU

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX5

PEX_RX5

PEX_RX5

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX10

PEX_TX10

PEX_RX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX15

PEX_TX15

PEX_RX15

PEX_RX15

ASSEMBLY

PAGE DETAIL

Place near balls

600mA

C637

C637

.022UF

.022UF

16V

NV_PLLAVDD

NVVDD_SENSE

GND_SENSE

GND

240R@100MHz

240R@100MHz

BEAD_0402

BEAD_0402

C679

C679

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

SNN_GPU_AM8_NC

SNN_GPU_AM9_NC

SNN_GPU_B32_NC

SPDIF

VDD33

PEX_PLL_VDD

LB503

LB503

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

COMMON

COMMON

AD23

PEX_IOVDD

AF23

PEX_IOVDD

AF24

PEX_IOVDD

AF25

PEX_IOVDD

AG24

PEX_IOVDD

AG25

PEX_IOVDD

AC16

PEX_IOVDDQ

AC17

PEX_IOVDDQ

AC21

PEX_IOVDDQ

AC22

PEX_IOVDDQ

AE18

PEX_IOVDDQ

AE21

PEX_IOVDDQ

AE22

PEX_IOVDDQ

AF12

PEX_IOVDDQ

AF18

PEX_IOVDDQ

AF21

PEX_IOVDDQ

AF22

PEX_IOVDDQ

K16

VDD

K17

VDD

N13

VDD

N14

VDD

N16

VDD

N17

VDD

N19

VDD

P13

VDD

P14

VDD

P16

VDD

P17

VDD

P19

VDD

R16

VDD

R17

VDD

T14

VDD

T15

VDD

T18

VDD

T19

VDD

U13

VDD

U14

VDD

U15

VDD

U18

VDD

U19

VDD

V16

VDD

V17

VDD

W13

VDD

W14

VDD

W16

VDD

W17

VDD

W19

VDD

Y13

VDD

Y14

VDD

Y16

VDD

Y17

VDD

Y19

VDD

Y20

VDD

P20

VDD_LP

T20

VDD_LP

T23

VDD_LP

U20

VDD_LP

U23

VDD_LP

W20

VDD_LP

N20

VDD_SENSE

M21

GND_SENSE

AC11

VDD33

AC12

VDD33

AC24

VDD33

AD24

VDD33

AE11

VDD33

AE12

VDD33

H7

VDD33

J7

VDD33

K7

VDD33

L10

VDD33

L7

VDD33

L8

VDD33

M10

VDD33

AF15

PEX_PLLAVDD

AE15

PEX_PLLDVDD

AE16

PEX_PLLGND

OTHER NV43/NV44

OTHER NV43/NV44

NV_PLLAVDD VDD

OTHER NV43/NV44

OTHER NV43/NV44

G73 ALL COMPONENT BOM

PCI EXPRESS 16X, NVVDD DECOUPLING CAPS,PEX_IOVDD/Q DECOUPLING CAPS

SPDIF NC

T13

AM8

NC

AM9

NC

B32

NC

J6

E GC

Place near balls

C661

C661

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C656

C656

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C631

C631

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C640

C640

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C634

C634

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

PEX1V2

16,16

IN

C627

C627

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C621

C621

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C690

C690

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C629

C629

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C643

C643

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C673

C673

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C642

C642

1000PF

1000PF

COMMON

COMMON

50V

50V

10%

10%

X7R

X7R

0402

0402

Place near balls

C695

C695

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C709

C709

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

Place near balls

180mA

C681

C681

.1UF

.1UF

16V

16V

X7R

X7R

0402

0402

COMMON

COMMON

C682

C682

4700PF

4700PF

25V 10%

25V 10%

X7R

X7R

0402

0402

COMMON

COMMON

Place near balls

C630

C630

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C691

C691

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C666

C666

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C674

C674

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

OUT

OUT

C707

C707

4700PF

4700PF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C708

C708

4700PF

4700PF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

10%

10%

GND

C591

C591

4.7UF

4.7UF

6.3V

6.3V

X5R

X5R

0603

0603

COMMON

COMMON

C644

C644

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

20,20

20,20

C672

C672

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C683

C683

470PF

470PF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

Place Close to GPU

10%

10%

C689

C689

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C667

C667

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C663

C663

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C669

C669

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C619

C619

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C77

C77

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C592

C592

4.7UF

4.7UF

6.3V

6.3V

X5R

X5R

0603

0603

COMMON

COMMON

C650

C650

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

10%

10%

C687

C687

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C678

C678

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C649

C649

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C654

C654

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

300 mA

C715

C715

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C614

C614

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

Place Near BGA

C665

C665

4.7UF

4.7UF

X5R

X5R

0603

0603

COMMON

COMMON

C638

C638

22UF

22UF

20%

20%

6.3V

6.3V

X5R

X5R

0805

0805

COMMON

COMMON

C664

C664

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

3V3_PEX

GND

GND

180R@100MHz

180R@100MHz

LB502

LB502

BEAD_0603 COMMON

BEAD_0603 COMMON

10%6.3V

10%6.3V

PEX1V2

NVVDD

GND

LB13

LB13

180R@100MHz

180R@100MHz

COMMON

COMMON

BEAD_0603

BEAD_0603

C726

C726

1UF

1UF

16V

16V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

C593

C593

22UF

22UF

6.3V 20%

6.3V 20%

X5R

X5R

0805

0805

COMMON

COMMON

HGFEDCBA

NET NV_CRITICAL NV_IMPEDENCE DIFFPAIR

PEX_REFCLK

BI

PEX_REFCLK*

BI

GPU_PEX_REFCLK

BI

GPU_PEX_REFCLK*

BI

PEX_TX0

BI

PEX_TX0*

BI

PEX_TX1

BI

PEX_TX1*

BI

PEX_TX2

BI

PEX_TX2*

BI

PEX_TX3

BI

PEX_TX3*

BI

PEX_TX4

BI

PEX_TX4*

BI

PEX_TX5

BI

PEX_TX5*

BI

PEX_TX6

BI

PEX_TX6*

BI

PEX_TX7

BI

PEX_TX7*

BI

PEX_TX8

BI

PEX_TX8*

BI

PEX_TX9

BI

PEX_TX9*

BI

GND

PEX1V2

C652

C652

4.7UF

4.7UF

6.3V 10%

6.3V 10%

X5R

X5R

0603

0603

COMMON

COMMON

GND

PEX_TX10

BI

PEX_TX10*

BI

PEX_TX11

BI

PEX_TX11*

BI

PEX_TX12

BI

PEX_TX12*

BI

PEX_TX13

BI

PEX_TX13*

BI

PEX_TX14

BI

PEX_TX14*

BI

PEX_TX15

BI

PEX_TX15*

BI

BI

BI

PEX_TXX1

BI

PEX_TXX1*

BI

PEX_TXX2

BI

PEX_TXX2*

BI

PEX_TXX3

BI

PEX_TXX3*

BI

PEX_TXX4

BI

PEX_TXX4*

BI

PEX_TXX5

BI

PEX_TXX5*

BI

PEX_TXX6

BI

PEX_TXX6*

BI

PEX_TXX7

BI

PEX_TXX7*

BI

PEX_TXX8

BI

PEX_TXX8*

BI

PEX_TXX9

BI

PEX_TXX9*

BI

PEX_TXX10

BI

PEX_TXX10*

BI

PEX_TXX11

BI

PEX_TXX11*

BI

PEX_TXX12

BI

PEX_TXX12*

BI

PEX_TXX13

BI

PEX_TXX13*

BI

PEX_TXX14

BI

PEX_TXX14*

BI

PEX_TXX15

BI

PEX_TXX15*

BI

PEX_RX0

BI

PEX_RX0*

BI

PEX_RX1

BI

PEX_RX1*

BI

PEX_RX2

BI

PEX_RX2*

BI

PEX_RX3

BI

PEX_RX3*

BI

PEX_RX4

BI

PEX_RX4*

BI

PEX_RX5

BI

PEX_RX5*

BI

PEX_RX6

BI

PEX_RX6*

BI

PEX_RX7

BI

PEX_RX7*

BI

BI

BI

PEX_RX9

BI

PEX_RX9*

BI

PEX_RX10

BI

PEX_RX10*

BI

PEX_RX11

BI

PEX_RX11*

BI

PEX_RX12

BI

PEX_RX12*

BI

PEX_RX13

BI

PEX_RX13*

BI

PEX_RX14

BI

PEX_RX14*

BI

PEX_RX15

BI

PEX_RX15*

BI

NET

PEX_PLL_VDD

BI

NV_PLLAVDD

BI

VDD33

BI

SRC_POWER

12V_PEX

12V_PEX

3V3_PEX

3V3_PEX

3V3AUX

3V3AUX

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

V058

V058

V058

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date:

Date:

Date:

100DIFF1 PEX_REFCLK

1 100DIFF PEX_REFCLK

1 100DIFF GPU_PEX_REFCLK

100DIFF1 GPU_PEX_REFCLK

1 PEX_TX1100DIFF

100DIFF1 PEX_TXX0

100DIFF1 PEX_TXX0

1 100DIFF PEX_TXX1

1 100DIFF PEX_TXX2

1 100DIFF PEX_TXX6

1 100DIFF PEX_TXX10

100DIFF1 PEX_TXX11

100DIFF1 PEX_TXX11

1 100DIFF PEX_TXX12

1 100DIFF PEX_TXX12

100DIFF1 PEX_TXX13

1 100DIFF PEX_TXX13

100DIFF1 PEX_TXX14

100DIFF1 PEX_TXX14

1 100DIFF PEX_TXX15

1 100DIFF PEX_TXX15

1 100DIFF PEX_RX0

1 100DIFF PEX_RX0

1 100DIFF PEX_RX1

1 100DIFF PEX_RX1

1 100DIFF PEX_RX2

1 100DIFF PEX_RX2

1 100DIFF PEX_RX3

1 100DIFF PEX_RX3

1 PEX_RX4100DIFF

1 PEX_RX5100DIFF

1 100DIFF PEX_RX5

1 PEX_RX6100DIFF

1 PEX_RX6100DIFF

1 100DIFF PEX_RX7

1 PEX_RX7100DIFF

1 PEX_RX8100DIFF

1 100DIFF PEX_RX8

1 100DIFF PEX_RX9

1 PEX_RX9100DIFF

1 PEX_RX10100DIFF

1 PEX_RX11100DIFF

1 PEX_RX11100DIFF

1 PEX_RX12100DIFF

1 PEX_RX12100DIFF

1 PEX_RX13100DIFF

1 PEX_RX13100DIFF

1 PEX_RX14100DIFF

1 PEX_RX14100DIFF

1 PEX_RX15100DIFF

VOLTAGE

1.2V 10.0

VOLTAGE

Tuesday, August 22, 2006

Tuesday, August 22, 2006

Tuesday, August 22, 2006

PEX_TX01 100DIFF

PEX_TX01 100DIFF

PEX_TX11 100DIFF

PEX_TX21 100DIFF

PEX_TX2100DIFF1

PEX_TX31 100DIFF

PEX_TX3100DIFF1

PEX_TX4100DIFF1

PEX_TX4100DIFF1

PEX_TX5100DIFF1

PEX_TX5100DIFF1

PEX_TX6100DIFF1

PEX_TX6100DIFF1

PEX_TX7100DIFF1

PEX_TX7100DIFF1

PEX_TX8100DIFF1

PEX_TX8100DIFF1

PEX_TX9100DIFF1

PEX_TX9100DIFF1

PEX_TX10100DIFF1

PEX_TX10100DIFF1

PEX_TX11100DIFF1

PEX_TX11100DIFF1

PEX_TX12100DIFF1

PEX_TX12100DIFF1

PEX_TX13100DIFF1

PEX_TX13100DIFF1

PEX_TX14100DIFF1

PEX_TX141 100DIFF

PEX_TX151 100DIFF

PEX_TX151 100DIFF

PEX_TXX11 100DIFF

PEX_TXX2100DIFF1

PEX_TXX3100DIFF1

PEX_TXX3100DIFF1

PEX_TXX4100DIFF1

PEX_TXX4100DIFF1

PEX_TXX5100DIFF1

PEX_TXX5100DIFF1

PEX_TXX61 100DIFF

PEX_TXX7100DIFF1

PEX_TXX7100DIFF1

PEX_TXX8100DIFF1

PEX_TXX8100DIFF1

PEX_TXX9100DIFF1

PEX_TXX9100DIFF1

PEX_TXX10100DIFF1

100DIFF1 PEX_RX4

PEX_RX101 100DIFF

PEX_RX151 100DIFF

MIN_LINE_WIDTH

10.01.2V

10.01.2V

MAX_CURRENTNET

MIN_WIDTH

15 MIL12V 5.5A12V

15 MIL3.3V 3.3V 3.0A

5 MIL3.3V

223

223

223

Sheet of

Sheet of

Sheet of

1

2

3

4

5

10

10

10

www.vinafix.vn

Page 3

HGFEDCBA

G1B

G1B

@digital.u_gpu_g3(chips):page3_i577

@digital.u_gpu_g3(chips):page3_i577

BGA820

BGA820

COMMON

3,4,5

1

2

3

3,4,5

3,4,5

3,4,5

FBAD[63..0]

BI

FBADQM[7..0]

OUT

FBADQS[7..0]

BI

FBADQSN[7..0]

BI

FBAD0

0

FBAD1

1

FBAD2

2

FBAD3

3

FBAD4

4

FBAD5

5

FBAD6

6

FBAD7

7

FBAD8

8

FBAD9

9

FBAD10

10

FBAD11

11

FBAD12

12

FBAD13

13

FBAD14

14

FBAD15

15

FBAD16

16

FBAD17

17

FBAD18

18

FBAD19

19

FBAD20

20

FBAD21

21

FBAD22

22

FBAD23

23

FBAD24

24

FBAD25

25

FBAD26

26

FBAD27

27

FBAD28

28

FBAD29

29

FBAD30

30

FBAD31

31

FBAD32

32

FBAD33

33

FBAD34

34

FBAD35

35

FBAD36

36

FBAD37

37

FBAD38

38

FBAD39

39

FBAD40

40

FBAD41

41

FBAD42

42

FBAD43

43

FBAD44

44

FBAD45

45

FBAD46

46

FBAD47

47

FBAD48

48

FBAD49

49

FBAD50

50

FBAD51

51

FBAD52

52

FBAD53

53

FBAD54

54

FBAD55

55

FBAD56

56

FBAD57

57

FBAD58

58

FBAD59

59

FBAD60

60

FBAD61

61

FBAD62

62

FBAD63

63

FBADQM0

0

FBADQM1

1

FBADQM2

2

FBADQM3

3

FBADQM4

4

FBADQM5

5

FBADQM6

6

FBADQM7

7

FBADQS0

0

FBADQS1

1

FBADQS2

2

FBADQS3

3

FBADQS4

4

FBADQS5

5

FBADQS6

6

FBADQS7

7

FBADQSN0

0

FBADQSN1

1

FBADQSN2

2

FBADQSN3

3

FBADQSN4

4

FBADQSN5

5

FBADQSN6

6

FBADQSN7

7

4

SNN_FBA_VREF

COMMON

2/14 FBA

2/14 FBA

N27

FBAD0

M27

FBAD1

N28

FBAD2

L29

FBAD3

K27

FBAD4

K28

FBAD5

J29

FBAD6

J28

FBAD7

P30

FBAD8

N31

FBAD9

N30

FBAD10

N32

FBAD11

L31

FBAD12

L30

FBAD13

J30

FBAD14

L32

FBAD15

H30

FBAD16

K30

FBAD17

H31

FBAD18

F30

FBAD19

H32

FBAD20

E31

FBAD21

D30

FBAD22

E30

FBAD23

H28

FBAD24

H29

FBAD25

E29

FBAD26

J27

FBAD27

F27

FBAD28

E27

FBAD29

E28

FBAD30

F28

FBAD31

AD29

FBAD32

AE29

FBAD33

AD28

FBAD34

AC28

FBAD35

AB29

FBAD36

AA30

FBAD37

Y28

FBAD38

AB30

FBAD39

AM30

FBAD40

AF30

FBAD41

AJ31

FBAD42

AJ30

FBAD43

AJ32

FBAD44

AK29

FBAD45

AM31

FBAD46

AL30

FBAD47

AE32

FBAD48

AE30

FBAD49

AE31

FBAD50

AD30

FBAD51

AC31

FBAD52

AC32

FBAD53

AB32

FBAD54

AB31

FBAD55

AG27

FBAD56

AF28

FBAD57

AH28

FBAD58

AG28

FBAD59

AG29

FBAD60

AD27

FBAD61

AF27

FBAD62

AE28

FBAD63

M29

FBADQM0

M30

FBADQM1

G30

FBADQM2

F29

FBADQM3

AA29

FBADQM4

AK30

FBADQM5

AC30

FBADQM6

AG30

FBADQM7

L28

FBADQS_WP0

K31

FBADQS_WP1

G32

FBADQS_WP2

G28

FBADQS_WP3

AB28

FBADQS_WP4

AL32

FBADQS_WP5

AF32

FBADQS_WP6

AH30

FBADQS_WP7

M28

FBADQS_RN0

K32

FBADQS_RN1

G31

FBADQS_RN2

G27

FBADQS_RN3

AA28

FBADQS_RN4

AL31

FBADQS_RN5

AF31

FBADQS_RN6

AH29

FBADQS_RN7

E32

FB_VREF1

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_DEBUG

FBA_REFCLK

FBA_REFCLK

FBA_PLLVDD

FBA_PLLAVDD

FBA_PLLGND

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

SNN_GPU_A12

A12

SNN_GPU_A15

A15

SNN_GPU_A18

A18

SNN_GPU_A21

A21

SNN_GPU_A24

A24

SNN_GPU_A27

A27

SNN_GPU_A3

A3

SNN_GPU_A30

A30

SNN_GPU_A6

A6

SNN_GPU_A9

A9

SNN_GPU_AA32

AA32

SNN_GPU_AD32

AD32

SNN_GPU_AG32

AG32

SNN_GPU_AK32

AK32

SNN_GPU_C32

C32

SNN_GPU_F32

F32

SNN_GPU_J32

J32

SNN_GPU_M32

M32

SNN_GPU_R32

R32

SNN_GPU_V32

V32

AA25

AA26

AB25

AB26

G11

G12

G15

G18

G21

G22

H11

H12

H15

H18

H21

H22

L25

L26

M25

M26

R25

R26

V25

V26

FBACMD0

P32

FBACMD1

U27

FBACMD2

P31

FBACMD3

U30

FBACMD4

Y31

FBACMD5

W32

FBACMD6

W31

FBACMD7

T32

FBACMD8

V27

FBACMD9

T28

FBACMD10

T31

FBACMD11

U32

FBACMD12

W29

FBACMD13

W30

FBACMD14

T27

FBACMD15

V28

FBACMD16

V30

FBACMD17

U31

FBACMD18

R27

FBACMD19

V29

FBACMD20

T30

FBACMD21

W28

FBACMD22

R29

FBACMD23

R30

FBACMD24

P29

FBACMD25

U28

SNN_FBA_CMD<26>

Y32

FBACLK0

P28

FBACLK0*

R28

FBACLK1

Y27

FBACLK1*

AA27

SNN_FBA_DBI0

Y30

RFU

RFU

SNN_FBA_DBI1

AC26

TP_FBA_DEBUG

AC27

SNN_FBA_REFCLK

D32

SNN_FBA_REFCLK*

D31

SNN_FBA_PLLVDD

G23

FBA_PLLAVDD

G25

G24

GND

C596

C596

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C601

C601

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C594

C594

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C635

C635

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C585

C585

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

3,4,4,4

OUT

3,4,4,4

OUT

3,5,5,5

OUT

3,5,5,5

OUT

TP503TP503

PLACE BELOW GPU

C595

C595

C616

C616

.1UF

.1UF

.1UF

.1UF

16V

16V

16V

16V

10%

10%

10%

10%

X7R

X7R

X7R

X7R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

C597

C597

C609

C609

.47UF

.47UF

.47UF

.47UF

6.3V

6.3V

6.3V

6.3V

10%

10%

10%

10%

X5R

X5R

X5R

X5R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

C641

C641

C622

C622

.47UF

.47UF

.47UF

.47UF

6.3V

6.3V

6.3V

6.3V

10%

10%

10%

10%

X5R

X5R

X5R

X5R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

C618

C618

C660

C660

1UF

1UF

1UF

1UF

6.3V

6.3V

6.3V

6.3V

10%

10%

10%

10%

X5R

X5R

X5R

X5R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

C607

C607

C582

C582

4.7UF

4.7UF

4.7UF

4.7UF

6.3V

6.3V

6.3V

6.3V

10%

10%

10%

10%

X5R

X5R

X5R

X5R

0603

0603

0603

0603

COMMON

COMMON

COMMON

COMMON

GND

FBACMD[25..0]

OUT

10K

10K

COMMON

COMMON

5%

5%

PLACE close to GPU

C624

C624

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

FBVDDQ

C659

C659

C623

C623

C603

C603

C617

C617

C696

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C680

C680

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C662

C662

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C625

C625

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C598

C598

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C675

C675

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C599

C599

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C612

C612

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C671

C671

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C696

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

3,4,5

R504

10K R504

10K

R505

R505

COMMON

COMMON

0402

0402

0402

0402

5%

5%

CKE PD REQUIRED FOR INITIALIZATION OF DDR2

ODT PD REQUIRED FOR INITIALIZATION OF DDR2

GND

C633

C633

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C632

C632

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

LB501

LB501

BEAD_0603

BEAD_0603

COMMON

COMMON

180R@100MHz

180R@100MHz

C648

C648

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

PEX1V2

FBA CMD/ADDR TERMINATIONS:

FBACMD0

FBACMD17

FBACMD18

FBACMD19

FBACMD25

FBACMD9

FBVDDQ

RP13A 150

RP13A 150

1 8

0402X4

0402X4

RP13B 150

RP13B 150

2 7

0402X4

0402X4

RP19B

RP19B

2 7

0402X4

0402X4

RP19A

RP19A

1 8

0402X4

0402X4

RP16A 150

RP16A 150

1 8

0402X4 COMMON

0402X4 COMMON

RP16B 150

RP16B 150

2 7

0402X4 COMMON

0402X4 COMMON

RP18B 150

RP18B 150

2 7

0402X4

0402X4

RP18A

RP18A

1 8

0402X4

0402X4

RP21D

RP21D

4 5

0402X4

0402X4

RP21C

RP21C

3 6

0402X4

0402X4

RP15C 150

RP15C 150

3 6

RP15D

4 5

0402X4

0402X4

C510

C510

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

DDR2 OPERATION:

1) During initialization CKE and ODT low

2) Runtime .. CKE high and ODT operated by debug state machine

3) No termination rpak for CKE or DEBUG pins

FBVDDQ

FBACMD2

COMMON

COMMON

+/-5%

+/-5%

COMMON

COMMON

+/-5%

+/-5%

FBACMD21

150

150

COMMON

COMMON

+/-5%

+/-5%

150

150

COMMON

COMMON

+/-5%

+/-5%

GND

FBVDDQ

FBACMD13

+/-5%

+/-5%

+/-5%

+/-5%

FBACMD1

COMMON

COMMON

+/-5%

+/-5%

150

150

COMMON

COMMON

+/-5%

+/-5%

GND

FBVDDQ

FBACMD3

150

150

COMMON

COMMON

+/-5%

+/-5%

150

150

COMMON

COMMON

+/-5%

+/-5%

FBACMD22

COMMON0402X4

COMMON0402X4

+/-5%

+/-5%

150RP15D

150

COMMON

COMMON

+/-5%

+/-5%

GND

RP14A

RP14A

1 8

0402X4

0402X4

+/-5%

+/-5%

RP14B

RP14B

2 7

0402X4

0402X4

+/-5%

+/-5%

RP20C 150

RP20C 150

3 6

0402X4

0402X4

+/-5%

+/-5%

RP20D 150

RP20D 150

4 5

0402X4

0402X4

+/-5%

+/-5%

RP23A

RP23A

1 8

0402X4

0402X4

+/-5%

+/-5%

RP23B

RP23B

2 7

0402X4

0402X4

+/-5%

+/-5%

RP17C 150

RP17C 150

3 6

0402X4

0402X4

+/-5%

+/-5%

RP17D

RP17D

4 5

0402X4

0402X4

+/-5%

+/-5%

RP22A

RP22A

1 8

0402X4

0402X4

+/-5%

+/-5%

RP22B 150

RP22B 150

2 7

0402X4

0402X4

+/-5%

+/-5%

RP13C 150

RP13C 150

3 6

0402X4

0402X4

+/-5%

+/-5%

RP13D

4 5

0402X4

0402X4

+/-5%

+/-5%

150

150

COMMON

COMMON

150

150

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

150

150

COMMON

COMMON

150

150

COMMON

COMMON

COMMON

COMMON

150

150

COMMON

COMMON

150

150

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

150RP13D

150

COMMON

COMMON

FBVDDQ

FBVDDQ

FBVDDQ

Place 0.1UF and 4.7UF alternate below the termination R-Paks.

C507

C507

C508

C511

C511

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

FBADQS[7..0]

3,4,5

BI

FBADQSN[7..0]

3,4,5

BI

C508

.1UF

.1UF

.1UF

.1UF

16V

16V

16V

16V

10%

10%

10%

10%

X7R

X7R

X7R

X7R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

FBACLK0

3,4,4,4

IN

FBACLK0*

3,4,4,4

IN

FBACLK1

3,5,5,5

IN

FBACLK1*

3,5,5,5

IN

FBA_PLLAVDD

IN

FBAD[63..0]

3,4,5

IN

FBADQS0

0

FBADQSN0

0

FBADQS1

1

FBADQSN1

1

FBADQS2

2

FBADQSN2

2

FBADQS3

3

FBADQSN3

3

FBADQS4

4

FBADQSN4

4

FBADQS5

5

FBADQSN5

5

FBADQS6

6

FBADQSN6

6

FBADQS7

7

FBADQSN7

7

FBADQM[7..0]

3,4,5

IN

FBACMD[25..0]

3,4,5

IN

FBA_DEBUG_ODT

IN

FBVDDQ

GND

GND

FBACMD16

FBACMD15

FBACMD4

FBACMD5

RP24A

RP24A

1 8

0402X4

0402X4

RP24B

RP24B

2 7

0402X4

0402X4

RP24C

RP24C

3 6

0402X4

0402X4

RP24D

RP24D

4 5

0402X4

0402X4

RP22D

RP22D

4 5

0402X4

0402X4

RP22C

RP22C

3 6

0402X4

0402X4

RP21B

RP21B

2 7

0402X4

0402X4

RP21A 150

RP21A 150

1 8

0402X4

0402X4

FBACMD6

RP23D 150

150

150

COMMON

COMMON

+/-5%

+/-5%

150

150

COMMON

COMMON

+/-5%

+/-5%

150

150

COMMON

COMMON

+/-5%

+/-5%

150

150

COMMON

COMMON

+/-5%

+/-5%

FBVDDQ

150

150

COMMON

COMMON

+/-5%

+/-5%

150

150

COMMON

COMMON

+/-5%

+/-5%

150

150

COMMON

COMMON

+/-5%

+/-5%

COMMON

COMMON

+/-5%

+/-5%

RP23D 150

4 5

0402X4

0402X4

+/-5%

+/-5%

RP23C 150

RP23C 150

3 6

0402X4

0402X4

+/-5%

+/-5%

FBACMD14

RP19C 150

RP19C 150

3 6

0402X4

0402X4

+/-5%

+/-5%

RP19D 150

RP19D 150

4 5

0402X4

0402X4

+/-5%

FBACMD23

FBACMD10

+/-5%

RP18D 150

RP18D 150

4 5

0402X4

0402X4

+/-5%

+/-5%

RP18C 150

RP18C 150

3 6

0402X4

0402X4

+/-5%

+/-5%

RP16C 150

RP16C 150

3 6

0402X4

0402X4

+/-5%

+/-5%

RP16D

RP16D

4 5

0402X4

0402X4

+/-5%

+/-5%

GND

GND

FBVDDQ

FBACMD20

RP15A 150

RP15A 150

FBACMD20

1 8

0402X4

0402X4

RP15B

2 7

0402X4

0402X4

FBACMD24

RP14C 150

RP14C 150

FBACMD24

3 6

0402X4

0402X4

RP14D 150

RP14D 150

4 5

0402X4 COMMON

0402X4 COMMON

GND

C509

C509

C505

C505

.1UF

.1UF

.1UF

.1UF

16V

16V

16V

16V

10%

10%

10%

10%

X7R

X7R

X7R

X7R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

DIFFPAIR

FBACLK0 1100DIFF

FBACLK0 1100DIFF

FBACLK1 1100DIFF

FBACLK1 100DIFF 1

FBADQS0 100DIFF 1

FBADQS0 100DIFF 1

FBADQS1 100DIFF 1

FBADQS1 100DIFF 1

FBADQS2 100DIFF 1

FBADQS2 100DIFF 1

FBADQS3 100DIFF 1

FBADQS3 100DIFF 1

FBADQS4 100DIFF 1

FBADQS4 100DIFF 1

FBADQS5 100DIFF 1

FBADQS5 100DIFF 1

FBADQS6 100DIFF 1

FBADQS6 100DIFF 1

FBACMD8

RP20A 150

RP20A 150

FBACMD8

1 8

0402X4

0402X4

+/-5%

COMMON

COMMON

+/-5%

+/-5%

150RP15B

150

COMMON

COMMON

+/-5%

+/-5%

COMMON

COMMON

+/-5%

+/-5%

+/-5%

+/-5%

GND

C506

C506

C512

C512

.1UF

.1UF

.1UF

.1UF

16V

16V

16V

16V

10%

10%

10%

10%

X7R

X7R

X7R

X7R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

12 MIL

+/-5%

RP20B 150

RP20B 150

2 7

0402X4

0402X4

+/-5%

+/-5%

FBACMD7

RP17A

RP17A

FBACMD7

1 8

0402X4

0402X4

+/-5%

+/-5%

RP17B 150

RP17B 150

2 7

+/-5%

+/-5%

C501

C501

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

60OHM 1

50OHM 1

C502

C502

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

150

150

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

150

150

COMMON

COMMON

COMMON0402X4

COMMON0402X4

FBVDDQ

FBVDDQ

FBVDDQ

1

GND

GND

2

GND

C504

C504

C503

C503

4.7UF

4.7UF

4.7UF

4.7UF

6.3V

6.3V

6.3V

6.3V

10%

10%

10%

10%

X5R

X5R

X5R

X5R

0603

0603

0603

0603

COMMON

COMMON

COMMON

COMMON

3

NV_CRITICAL_NETNV_IMPEDANCEMIN_LINE_WIDTHNET

150OHM

4

1FBADQS7 100DIFF

1FBADQS7 100DIFF

150OHM

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

GND

G73 ALL COMPONENT BOM

FBA MEMORY INTERFACE, GPU FBVDDQ DECOUPLING CAPS

E GC

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

V058

V058

V058

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date:

Date:

Date:

Tuesday, August 22, 2006

Tuesday, August 22, 2006

Tuesday, August 22, 2006

323

323

323

Sheet of

Sheet of

Sheet of

5

10

10

10

Page 4

FBA MEMORY 1st bank 0..31

PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

FBACMD[25..0]

3,3,5

IN

1

2

3

4

USED ONLY FOR 1GB DEVICES ---->

3,3,4,4

IN

3,3,4,4

IN

FBACLK0

FBACLK0* FBACLK0*

3,3,5

3,3,5

3,3,5

3,3,5

FBACMD15 FBACMD15

15

FBACMD25 FBACMD25

25

FBACMD9 FBACMD9

9

FBACMD8 FBACMD8

8

FBACMD1 FBACMD1

1

FBACMD3 FBACMD3

3

FBACMD2 FBACMD2

2

FBACMD0 FBACMD0

0

FBACMD24 FBACMD24

24

FBACMD22 FBACMD22

22

FBACMD21 FBACMD21

21

FBACMD23 FBACMD23

23

FBACMD19 FBACMD19

19

FBACMD20 FBACMD20

20

FBACMD17 FBACMD17

17

FBACMD16 FBACMD16

16

FBACMD14 FBACMD14

14

SNN_U8_FBAA<13>

SNN_U8_FBAA<14>

SNN_U8_FBAA<15>

FBACMD10 FBACMD10

10

FBACMD18 FBACMD18

18

FBACMD7 FBACMD7

7

FBACMD11 FBACMD11

11

FBACMD12 FBACMD12

12

SNN_U8_A2

SNN_U8_E2

FBAD[63..0]

BI

FBADQM[7..0]

IN

FBADQS[7..0]

IN

FBADQSN[7..0]

IN

M6C

M6C

@memory.u_mem_sd_ddr2_x16(chips):page4_i121

@memory.u_mem_sd_ddr2_x16(chips):page4_i121

BGA84

BGA84

COMMON

COMMON

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

FBADQM0

0

FBADQM1

1

FBADQM2

2

FBADQM3

3

FBADQS0 FBADQS0

0

FBADQS1

1

FBADQS2

2

FBADQS3

3

FBADQSN0

0

FBADQSN1

1

FBADQSN2

2

FBADQSN3

3

HGFEDCBA

FBVDDQ

C523

C550

C550

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C528

C528

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C523

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C529

C529

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C556

C556

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C568

C568

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C560

C560

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C545

C545

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

CMD_GTV

CMD_GTV

C514

C514

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C516

C516

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C561

C561

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C547

C547

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C542

C542

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

C541

C541

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

1

2

3

4

M5C

FBVDDQ

1/2

1/2

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

N1

VSS

GND

P9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VSSQ

H2

VSSQ

H8

VSSQ

J7

VSSL

J2

Vref

FBVDDQ

VREF_B VREF_B

C536

C536

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

0

FBAD0

1

FBAD1

2

FBAD2

3

FBAD3

4

FBAD4

5

FBAD5

6

FBAD6

7

FBAD7

FBADQM0

FBADQSN0

8

FBAD8

9

FBAD9

10

FBAD10

11

FBAD11

12

FBAD12

13

FBAD13

14

FBAD14

15

FBAD15

FBADQM1

FBADQS1

FBADQSN1

R509

R509

1K

1K

1%

1%

0402

0402

COMMON

COMMON

R510

R510

1K

1K

1%

1%

0402

0402

COMMON

COMMON

GND

USED ONLY FOR 1GB DEVICES ---->

4,5

OUT

M6B

M6B

@memory.u_mem_sd_ddr2_x16(chips):page4_i147

@memory.u_mem_sd_ddr2_x16(chips):page4_i147

BGA84

BGA84

COMMON

COMMON

2/2

2/2

D1

DQ<0>

C2

DQ<1>

B1

DQ<2>

D3

DQ<3>

C8

DQ<4>

D7

DQ<5>

B9

DQ<6>

D9

DQ<7>

B3

DQM

B7

DQS

A8

DQS

M6A

M6A

@memory.u_mem_sd_ddr2_x16(chips):page4_i164

@memory.u_mem_sd_ddr2_x16(chips):page4_i164

BGA84

BGA84

COMMON

COMMON

2/2

2/2

H1

DQ<0>

F1

DQ<1>

H3

DQ<2>

G2

DQ<3>

H7

DQ<4>

F9

DQ<5>

H9

DQ<6>

G8

DQ<7>

F3

DQM

F7

DQS

E8

DQS

3,3,4,4

IN

3,3,4,4

IN

FBACLK0

15

25

9

8

1

3

2

0

24

22

21

23

19

20

17

16

14

10

18

7

11

12

SNN_U7_FBAA<13>

SNN_U7_FBAA<14>

SNN_U7_FBAA<15>

SNN_U7_A2

SNN_U7_E2

M5C

@memory.u_mem_sd_ddr2_x16(chips):page4_i61

@memory.u_mem_sd_ddr2_x16(chips):page4_i61

BGA84

BGA84

COMMON

COMMON

1/2

1/2

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

16

FBAD16

17

FBAD17

18

FBAD18

19

FBAD19

20

FBAD20

21

FBAD21

22

FBAD22

23

FBAD23

FBADQM2

FBADQS2

FBADQSN2

24

FBAD24

25

FBAD25

26

FBAD26

27

FBAD27

28

FBAD28

29

FBAD29

30

FBAD30

31

FBAD31

FBADQM3

FBADQS3

FBADQSN3

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

N1

VSS

P9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VSSQ

H2

VSSQ

H8

VSSQ

J7

VSSL

J2

Vref

M5B

M5B

@memory.u_mem_sd_ddr2_x16(chips):page4_i99

@memory.u_mem_sd_ddr2_x16(chips):page4_i99

BGA84

BGA84

COMMON

COMMON

2/2

2/2

H3

DQ<0>

H1

DQ<1>

F1

DQ<2>

H7

DQ<3>

G2

DQ<4>

F9

DQ<5>

H9

DQ<6>

G8

DQ<7>

F3

DQM

F7

DQS

E8

DQS

M5A

M5A

@memory.u_mem_sd_ddr2_x16(chips):page4_i108

@memory.u_mem_sd_ddr2_x16(chips):page4_i108

BGA84

BGA84

COMMON

COMMON

2/2

2/2

C2

DQ<0>

D1

DQ<1>

D3

DQ<2>

B1

DQ<3>

C8

DQ<4>

B9

DQ<5>

D9

DQ<6>

D7

DQ<7>

B3

DQM

B7

DQS

A8

DQS

FBVDDQ

GND

4,5

OUT

C533

C533

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

C537

C537

.022UF

.022UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

GND

FBVDDQ

Addtl. Decap initially not stuffed

C548

C548

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

GND

FBVDDQ

C563

C563

.022UF

.022UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

GND

FBVDDQ

Addtl. Decap initially not stuffed

C555

C555

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

GND

C554

C554

.022UF

.022UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C520

C520

.022UF

.022UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

FBACLK0

3,3,4,4

IN

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

121

121

COMMON

COMMON

FBACLK0*

R506

R506

0603

0603

1%

1%

G73 ALL COMPONENT BOM

FBA 16Mx16 DDR2 MEMORIES, 1ST BANK 0..31

3,3,4,4

IN

5

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

V058

V058

V058

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date:

Tuesday, August 22, 2006

Date:

Tuesday, August 22, 2006

Date:

E GC

Tuesday, August 22, 2006

Sheet of

Sheet of

Sheet of

10

10

10

423

423

423

Page 5

FBA MEMORY 1st bank 32..63

PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

FBACMD[25..0]

3,3,4

SUBPARTITION BITS ---->

USED ONLY FOR 1GB DEVICES ---->

IN

FBACMD15 FBACMD15

15

FBACMD25 FBACMD25

25

FBACMD9 FBACMD9

9

FBACMD8 FBACMD8

8

FBACMD1 FBACMD1

1

FBACMD3 FBACMD3

3

FBACMD13 FBACMD13

13

FBACMD4 FBACMD4

4

FBACMD5 FBACMD5

5

FBACMD6 FBACMD6

6

FBACLK1

3,3,5,5

IN

FBACLK1* FBACLK1*

3,3,5,5

IN

FBAD[63..0]

3,3,4

BI

FBADQM[7..0]

3,3,4

IN

FBADQS[7..0]

3,3,4

IN

FBADQSN[7..0]

3,3,4

IN

FBACMD21 FBACMD21

21

FBACMD23 FBACMD23

23

FBACMD19 FBACMD19

19

FBACMD20 FBACMD20

20

FBACMD17 FBACMD17

17

FBACMD16 FBACMD16

16

FBACMD14 FBACMD14

14

SNN_U10_FBAA<13>

SNN_U10_FBAA<14>

SNN_U10_FBAA<15>

FBACMD10 FBACMD10

10

FBACMD18 FBACMD18

18

FBACMD7 FBACMD7

7

FBACMD11 FBACMD11

11

FBACMD12 FBACMD12

12

SNN_U10_A2

SNN_U10_E2

FBADQM4

4

FBADQM5

5

FBADQM6

6

FBADQM7

7

FBADQS4

4

FBADQS5

5

FBADQS6

6

FBADQS7

7

FBADQSN4

4

FBADQSN5

5

FBADQSN6

6

FBADQSN7

7

K7

L7

K3

L8

M8

M3

M7

N2

N8

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

K2

J8

K8

K9

A2

E2

1

2

3

4

M8C

M8C

@memory.u_mem_sd_ddr2_x16(chips):page5_i112

@memory.u_mem_sd_ddr2_x16(chips):page5_i112

BGA84

BGA84

COMMON

COMMON

1/2

1/2

RAS

CAS

WE

CS

A<0>

A<1>

A<2>

A<3>

A<4>

A<5>

A<6>

A<7>

A<8>

A<9>

A<10>

A<11>

A<12>

NC/A<13>

NC/A<14>

NC/A<15>

BA<0>

BA<1>

NC/BA<2>

CKE

CLK

CLK

ODT

NC

NC

FBAD32

32

FBAD33

33

FBAD34

34

FBAD35

35

FBAD36

36

FBAD37

37

FBAD38

38

FBAD39

39

FBADQM4

FBADQS4

FBADQSN4

FBAD40

40

FBAD41

41

FBAD42

42

FBAD43

43

FBAD44

44

FBAD45

45

FBAD46

46

FBAD47

47

FBADQM5

FBADQS5

FBADQSN5

M7B

M7B

@memory.u_mem_sd_ddr2_x16(chips):page5_i1

@memory.u_mem_sd_ddr2_x16(chips):page5_i1

BGA84

FBVDDQ

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

GND

N1

VSS

P9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

VSSQ

VSSQ

VSSQ

VSSL

Vref

FBVDDQ

F8

H2

H8

J7

VREF_A VREF_A

J2

GND

3

3

M7C

M7C

@memory.u_mem_sd_ddr2_x16(chips):page5_i97

@memory.u_mem_sd_ddr2_x16(chips):page5_i97

BGA84

BGA84

COMMON

COMMON

B1

DQ<0>

D1

DQ<1>

C2

DQ<2>

D3

DQ<3>

D7

DQ<4>

B9

DQ<5>

D9

DQ<6>

C8

DQ<7>

B3

DQM

B7

DQS