Page 1

8

7

6

5

4

3

2

1

+12V_BUS

MC1

MC1

C1

470uF

470uF

10UFC110UF

+12V_BUS

+12V_BUS

C3

+3.3V

+3.3V

C2

150nF_16VC2150nF_16V

C4

470uFC4470uF

+3.3V

C5

1uF_6.3VC51uF_6.3V

Place these caps last,

ideally as close to the bus

connector as possible

150nF_16VC3150nF_16V

C6

1uF_6.3VC61uF_6.3V

DNI

R6 0RR6 0R

TESTEN[3]

A_HSYNC_DAC1[3,7,13]

PETp10_GFXRp10[2]

PETn10_GFXRn10[2]

PETp11_GFXRp11[2]

PETn11_GFXRn11[2]

PETp12_GFXRp12[2]

PETn12_GFXRn12[2]

PETp13_GFXRp13[2]

PETn13_GFXRn13[2]

PETp14_GFXRp14[2]

PETn14_GFXRn14[2]

PETp15_GFXRp15[2]

PETn15_GFXRn15[2]

R5 0RR5 0R

R4 0RR4 0R

PETn0_GFXRn0[2]

PETp1_GFXRp1[2]

PETn1_GFXRn1[2]

PETp2_GFXRp2[2]

PETn2_GFXRn2[2]

PETp3_GFXRp3[2]

PETn3_GFXRn3[2]

PETp4_GFXRp4[2]

PETn4_GFXRn4[2]

PETp5_GFXRp5[2]

PETn5_GFXRn5[2]

PETp6_GFXRp6[2]

PETn6_GFXRn6[2]

PETp7_GFXRp7[2]

PETn7_GFXRn7[2]

PETp8_GFXRp8[2]

PETn8_GFXRn8[2]

PETp9_GFXRp9[2]

PETn9_GFXRn9[2]

PRESENCE

D D

C C

B B

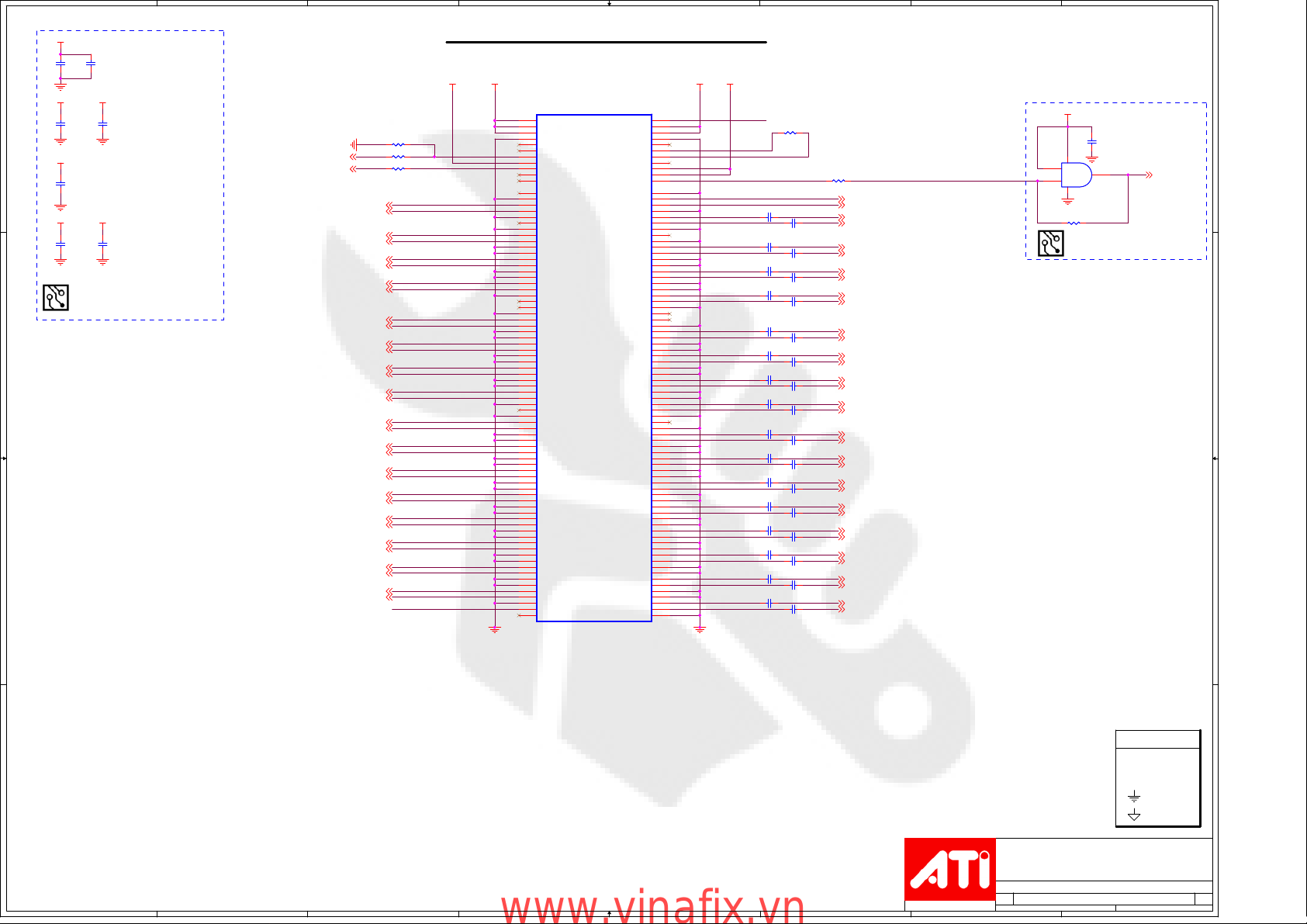

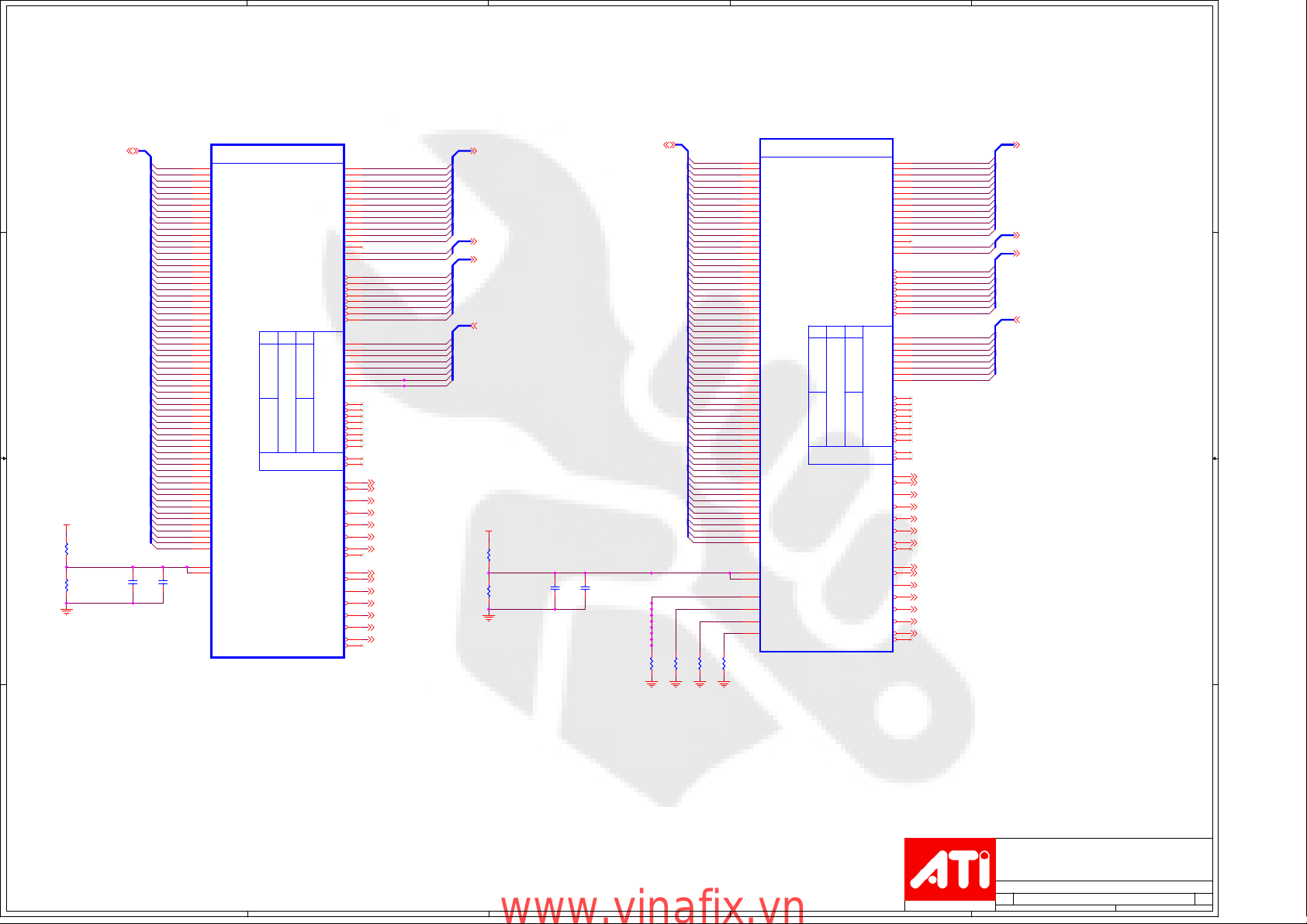

PCI-EXPRESS EDGE CONNECTOR

+12V_BUS+3.3V_BUS +3.3V_BUS+12V_BUS

x16 PCIe

TESTEN_GND

JTAG_TRST#

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+12V#B1

+12V#B2

+12V#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

Mechanical Key

Mechanical Key

x16 PCIe

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

MPCIE1

MPCIE1

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

PRESENCE

JTAG_TDI

JTAG_TDO

R2 0RR2 0R

C7

100nFC7100nF

C9

100nFC9100nF

C11

C11

100nF

100nF

C13

C13

100nF

100nF

C15

C15

100nF

100nF

C17

C17

100nF

100nF

C19

C19

100nF

100nF

C21

C21

100nF

100nF

C23

C23

100nF

100nF

C25

C25

100nF

100nF

C27

C27

100nF

100nF

C29

C29

100nF

100nF

C31

C31

100nF

100nF

C33

C33

100nF

100nF

C35

C35

100nF

100nF

C37

C37

100nF

100nF

DNI

PERST#

C8

100nFC8100nF

C10

C10

100nF

100nF

C12

C12

100nF

100nF

C14

C14

100nF

100nF

C16

C16

100nF

100nF

C18

C18

100nF

100nF

C20

C20

100nF

100nF

C22

C22

100nF

100nF

C24

C24

100nF

100nF

C26

C26

100nF

100nF

C28

C28

100nF

100nF

C30

C30

100nF

100nF

C32

C32

100nF

100nF

C34

C34

100nF

100nF

C36

C36

100nF

100nF

C38

C38

100nF

100nF

R1 0RR1 0R

PCIE_REFCLKP [2]

PCIE_REFCLKN [2]PETp0_GFXRp0[2]

GFXTp0_PERp0 [2]

GFXTn0_PERn0 [2]

GFXTp1_PERp1 [2]

GFXTn1_PERn1 [2]

GFXTp2_PERp2 [2]

GFXTn2_PERn2 [2]

GFXTp3_PERp3 [2]

GFXTn3_PERn3 [2]

GFXTp4_PERp4 [2]

GFXTn4_PERn4 [2]

GFXTp5_PERp5 [2]

GFXTn5_PERn5 [2]

GFXTp6_PERp6 [2]

GFXTn6_PERn6 [2]

GFXTp7_PERp7 [2]

GFXTn7_PERn7 [2]

GFXTp8_PERp8 [2]

GFXTn8_PERn8 [2]

GFXTp9_PERp9 [2]

GFXTn9_PERn9 [2]

GFXTp10_PERp10 [2]

GFXTn10_PERn10 [2]

GFXTp11_PERp11 [2]

GFXTn11_PERn11 [2]

GFXTp12_PERp12 [2]

GFXTn12_PERn12 [2]

GFXTp13_PERp13 [2]

GFXTn13_PERn13 [2]

GFXTp14_PERp14 [2]

GFXTn14_PERn14 [2]

GFXTp15_PERp15 [2]

GFXTn15_PERn15 [2]

+3.3V

CAP, CERAMIC 100NF 10% 10V X5R EIA(0402)

CAP, CERAMIC 100NF 10% 10V X5R EIA(0402)

C39

C39

100nF

100nF

53

1

4

2

U5

U5

NC7SZ08P5X_NL

NC7SZ08P5X_NL

R_RST

R3 0R

R3 0R

DNI

DNI

Place R_RST in U_RST

PERST#_buf [2]

Power Sequence Circuit to ensure SMPS_EN is released after

+12V_BUS and +3.3V_BUS are both in regulation.

Pull-up may or may not be required on SMPS_EN signal depending

on SMPS design.

A A

8

7

6

Node 1 When +12V ramps above min Vbe, SMPS_EN will be helt low

When +3.3V gets close to regulation, one of the two

Node 2

conditions of releasing SMPS_EN is active

Target ~ 900mV when +3.3 at min regulation (worse case)

Typical trigger when +3.3V ramps above 2.2V (650mV)

Node 3 When +12V gets close to regulation, one of the two

conditions of releasing SMPS_EN is active

Target ~ 1.25V when +12 at min regulation (worse case)

Typical trigger when +12V ramps above 10V (1.1V)

5

www.vinafix.vn

4

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

3

Date: Sheet

2

105-A67700-00A

105-A67700-00A

105-A67700-00A

SYMBOL LEGEND

DNI

DO NOT

INSTALL

#

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

119Tuesday, December 20, 2005

119Tuesday, December 20, 2005

119Tuesday, December 20, 2005

1

1

1

1

of

of

of

Page 2

5

D D

4

3

2

1

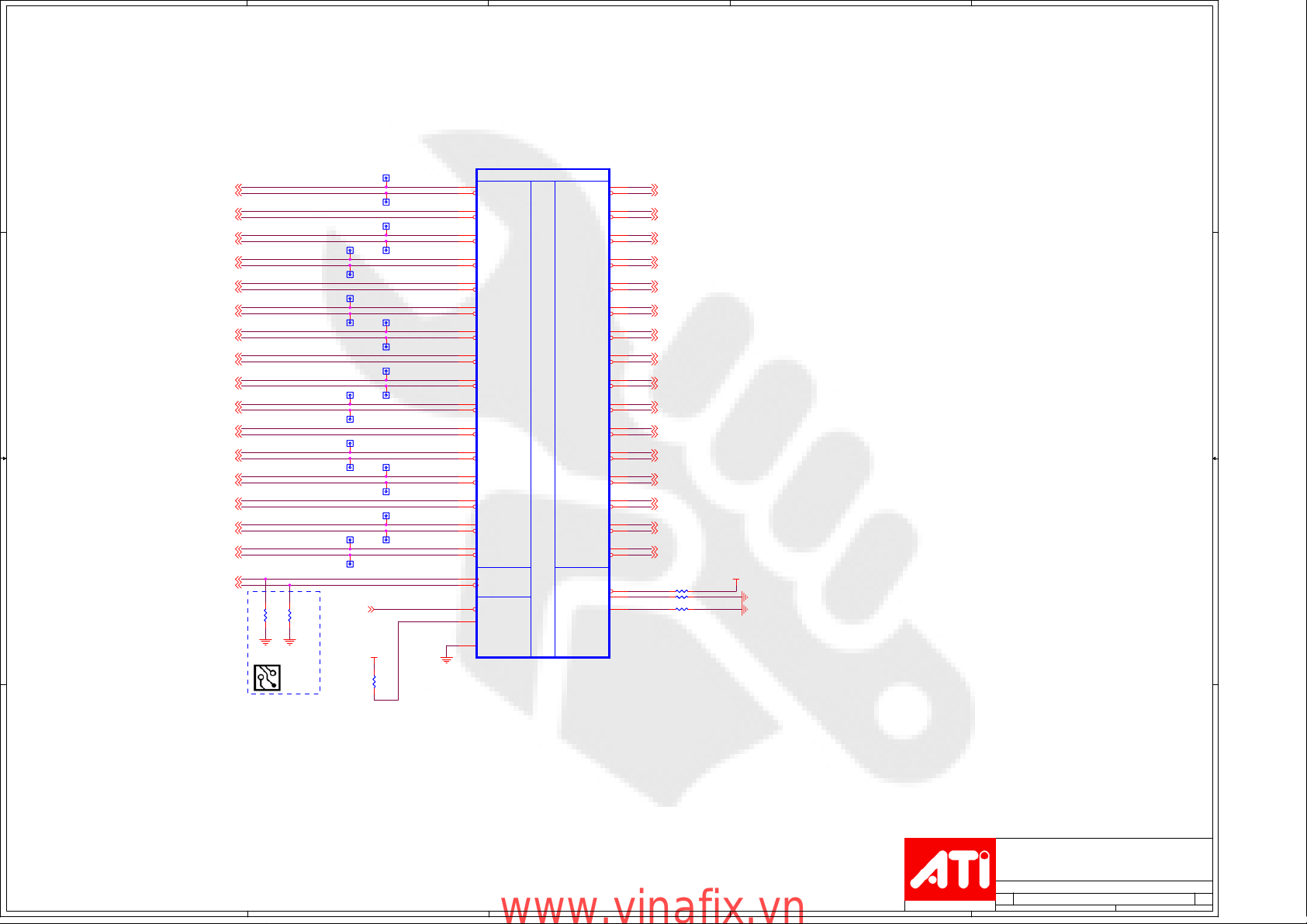

NOTE: some of the PCIE testpoints will

be available trought via on traces.

PETp0_GFXRp0[1]

PETn0_GFXRn0[1]

PETp1_GFXRp1[1]

PETn1_GFXRn1[1]

PETp2_GFXRp2[1]

PETn2_GFXRn2[1]

PETp3_GFXRp3[1]

PETn3_GFXRn3[1]

PETp4_GFXRp4[1]

PETn4_GFXRn4[1]

PETp5_GFXRp5[1]

PETn5_GFXRn5[1]

PETp6_GFXRp6[1]

C C

B B

PETn6_GFXRn6[1]

PETp7_GFXRp7[1]

PETn7_GFXRn7[1]

PETp8_GFXRp8[1]

PETp9_GFXRp9[1]

PETn9_GFXRn9[1]

PETp10_GFXRp10[1]

PETn10_GFXRn10[1]

PETp11_GFXRp11[1]

PETn11_GFXRn11[1]

PETp12_GFXRp12[1]

PETn12_GFXRn12[1]

PETp13_GFXRp13[1]

PETn13_GFXRn13[1]

PETp14_GFXRp14[1]

PETn14_GFXRn14[1]

PETp15_GFXRp15[1]

PETn15_GFXRn15[1]

PCIE_REFCLKP[1]

PCIE_REFCLKN[1]

DNI DNI

R13

R13

51R

51R

402 402

PERST#_buf[1]

R14

R14

51R

51R

For Tektronix LA only

Place close

to ASIC

TP11TP11

TP12TP12

TP13TP13

TP14TP14

TP19TP19

TP20TP20

TP21TP21

TP22TP22

TP27TP27

TP28TP28

R11

R11

4.7K

4.7K

402

TP7TP7

TP8TP8

TP9TP9

TP10TP10

TP15TP15

TP16TP16

TP17TP17

TP18TP18

TP23TP23

TP24TP24

TP25TP25

TP26TP26

+3.3V

DNI

AJ31

AH31

AH30

AG30

AG32

AF32

AF31

AE31

AE30

AD30

AD32

AC32

AC31

AB31

AB30

AA30

AA32

AL28

AK28

AG24

AA24

AF24

Y32

Y31

W31

W30

V30

V32

U32

U31

T31

T30

R30

R32

P32

P31

N31

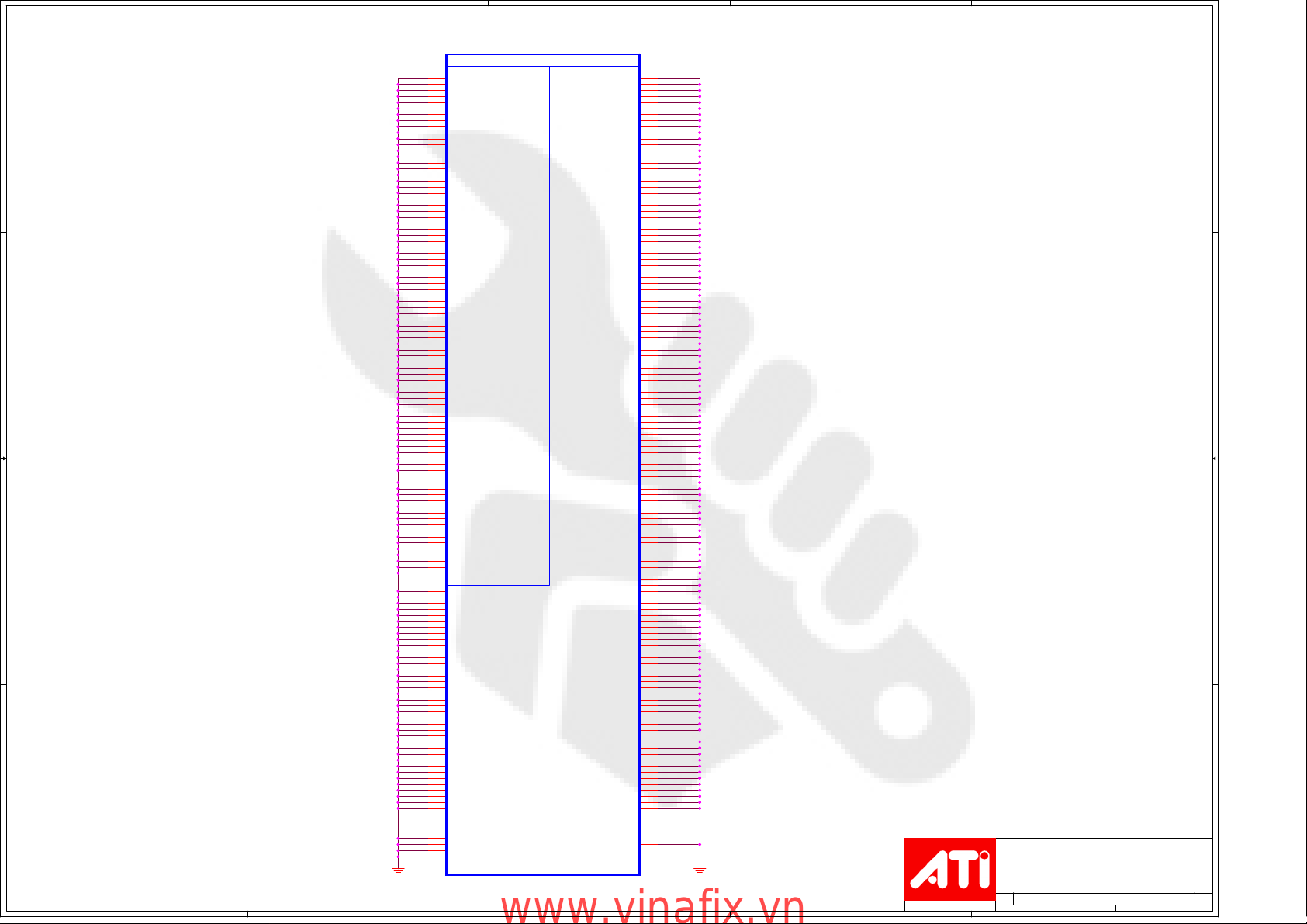

U1A

U1A

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

Clock

Clock

PCIE_REFCLKP

PCIE_REFCLKN

PERSTB

PCIE_TEST

NC

RV530 unfused A11

RV530 unfused A11

PART 1 OF 7

PART 1 OF 7

P

P

C

C

I

I

-

E

E

X

X

P

P

R

R

E

E

S

S

S

S

I

I

N

N

T

T

E

E

R

R

F

F

A

A

C

C

E

E

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Calibration

Calibration

PCIE_CALRN

PCIE_CALRP

PCIE_CALI

AK27

AJ27

AJ25

AH25

AH28

AG28

AG27

AF27

AF25

AE25

AE28

AD28

AD27

AC27

AC25

AB25

AB28

AA28

AA27

Y27

Y25

W25

W28

V28

V27

U27

U25

T25

T28

R28

R27

P27

AE24

AD24

AB24

GFXTp0_PERp0 [1]

GFXTn0_PERn0 [1]

GFXTp1_PERp1 [1]

GFXTn1_PERn1 [1]

GFXTp2_PERp2 [1]

GFXTn2_PERn2 [1]

GFXTp3_PERp3 [1]

GFXTn3_PERn3 [1]

GFXTp4_PERp4 [1]

GFXTn4_PERn4 [1]

GFXTp5_PERp5 [1]

GFXTn5_PERn5 [1]

GFXTp6_PERp6 [1]

GFXTn6_PERn6 [1]

GFXTp7_PERp7 [1]

GFXTn7_PERn7 [1]

GFXTp8_PERp8 [1]

GFXTn8_PERn8 [1]PETn8_GFXRn8[1]

GFXTp9_PERp9 [1]

GFXTn9_PERn9 [1]

GFXTp10_PERp10 [1]

GFXTn10_PERn10 [1]

GFXTp11_PERp11 [1]

GFXTn11_PERn11 [1]

GFXTp12_PERp12 [1]

GFXTn12_PERn12 [1]

GFXTp13_PERp13 [1]

GFXTn13_PERn13 [1]

GFXTp14_PERp14 [1]

GFXTn14_PERn14 [1]

GFXTp15_PERp15 [1]

GFXTn15_PERn15 [1]

402

R82.0K R82.0K

402

R9562R R9562R

R101.47K R101.47K

+PCIE

402

A A

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

www.vinafix.vn

3

2

Date: Sheet

105-A67700-00A

105-A67700-00A

105-A67700-00A

1

1

1

1

of

of

of

219Friday, December 16, 2005

219Friday, December 16, 2005

219Friday, December 16, 2005

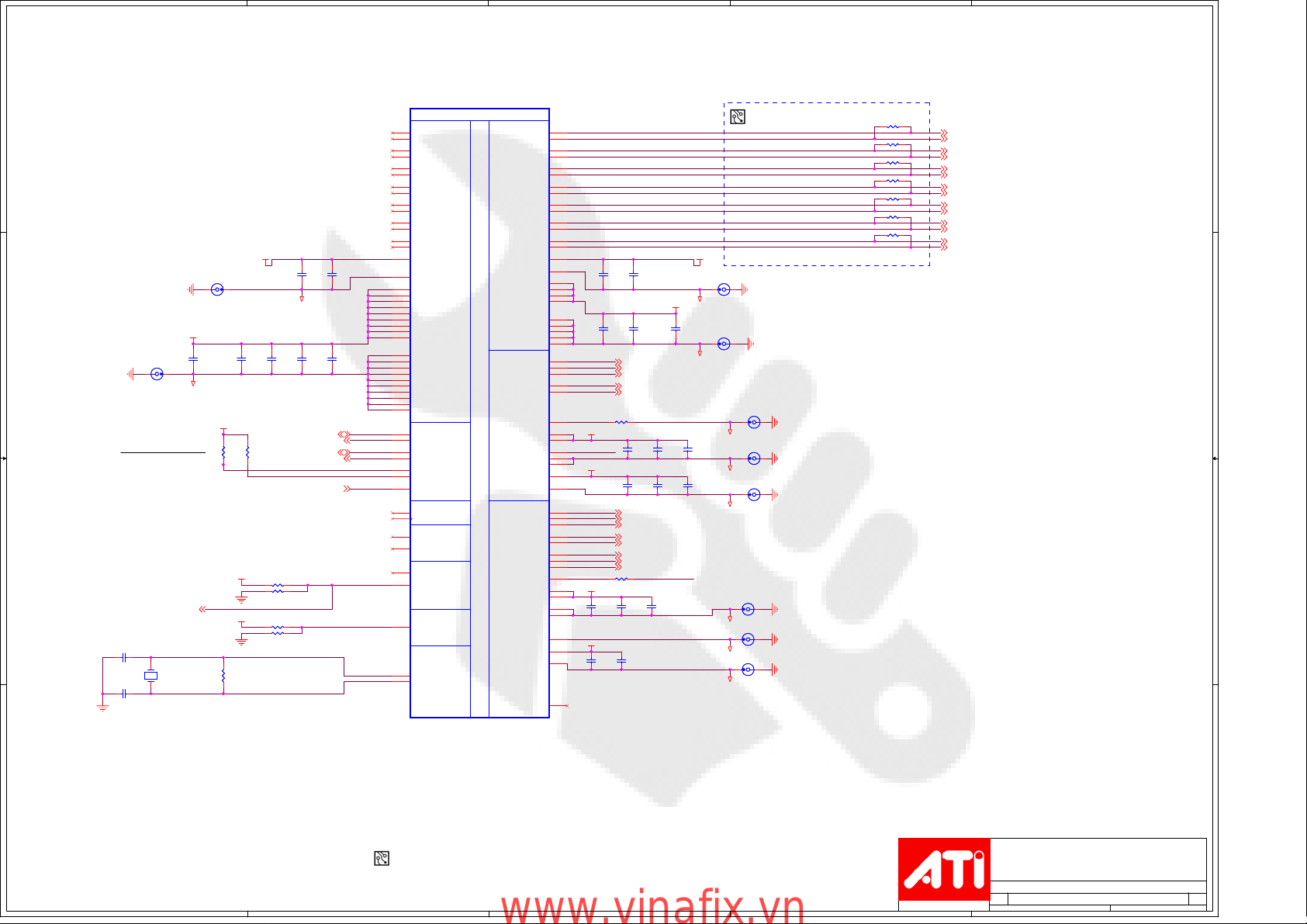

Page 3

5

D D

+T2PVDD

C227

C227

C226

NS15NS_VIA NS15NS_VIA

1 2

C C

I2C DEVICE ADDRESS' ON DDC3

DEVICE

LM63

B B

EC82 15PFEC82 15PF

EC83 15PFEC83 15PF

+T2XVDDR

C225

C225

NS19NS_VIA NS19NS_VIA

10uF

10uF

1uF_6.3V

1 2

GND_T2XVSSR

ADDRESS

x100 1100

EY82

EY82

27_MHZ

27_MHZ

2 1

Change to 10ppm/10ppm p/n 5028270000G

1uF_6.3V

TESTEN[1]

+3.3V

C224

C224

1uF_6.3V

1uF_6.3V

R33

R33

4.7K

4.7K

402 402

+3.3V

+3.3V

R841MR84

1M

GND_T2PVSS

C223

C223

R34

R34

4.7K

4.7K

MR24 10KDNIMR24 10KDNI

R24 10KR24 10K

Overlap Footprints

R25 499RR25 499R

R26 499RR26 499R

XTALIN

XTALOUT

1uF_6.3V

1uF_6.3V

C222

C222

1uF_6.3V

1uF_6.3V

C226

1uF_6.3V

1uF_6.3V

C221

C221

1uF_6.3V

1uF_6.3V

CRT1DDCDATA[13]

CRT1DDCCLK[13]

CRT2DDCDATA[14]

CRT2DDCCLK[14]

4

U1B

U1B

AL18

T2XCM

AM18

T2XCP

AK19

T2X0M

AL19

T2X0P

AL20

T2X1M

AM20

T2X1P

AL21

T2X2M

AM21

T2X2P

AK18

T2X3M

AJ18

T2X3P

AH18

T2X4M

AG18

T2X4P

AJ20

T2X5M

AK20

T2X5P

AE19

T2PVDD

AE18

T2PVSS

AF20

T2XVDDR_1

AE20

T2XVDDR_2

AF19

T2XVDDR_3

AC21

T2XVDDR_4

AC22

T2XVDDR_5

AD22

T2XVDDR_6

AE21

T2XVDDR_7

AD21

T2XVDDR_8

AE22

T2XVDDR_9

AF22

T2XVSSR_1

AF17

T2XVSSR_2

AF21

T2XVSSR_3

AK17

T2XVSSR_4

AJ19

T2XVSSR_5

AF18

T2XVSSR_6

AH17

T2XVSSR_7

AG17

T2XVSSR_8

AG19

T2XVSSR_9

AH19

T2XVSSR_10

AH22

DDC1DATA

AH23

DDC1CLK

AH13

DDC2DATA

AG13

DDC2CLK

AE12

DDC3DATA

AF12

DDC3CLK

TESTEN

VREFG

XTALIN

XTALOUT

AF11

AE13

AF13

AG12

AH12

AG14

AG22

AL26

AM26

AC8

HPD1

SDA

SCL

DPLUS

DMINUS

PLLTEST

TESTEN

VREFG

XTALIN

XTALOUT

RV530 unfused A11

RV530 unfused A11

HPD1[14]

Integrated

Integrated

TMDS2

TMDS2

Monitor

Monitor

Interface

Interface

MMI2C

MMI2C

Thermal

Thermal

Diode

Diode

Test

Test

XTAL

XTAL

PART 2 OF 7

PART 2 OF 7

V

V

I

I

D

D

E

E

O

O

&

&

M

M

U

U

L

L

T

T

I

I

M

M

E

E

D

D

I

I

A

A

Integrated

Integrated

TMDS

TMDS

TXVDDR_1

TXVDDR_2

TXVDDR_3

TXVDDR_4

TXVSSR_1

TXVSSR_2

TXVSSR_3

TXVSSR_4

TXVSSR_5

DAC / CRT

DAC / CRT

DAC2 (TV/CRT2)

DAC2 (TV/CRT2)

A2VSSN_1

A2VSSN_2

NC_A2VDDQ

TXCM

TXCP

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TX3M

TX3P

TX4M

TX4P

TX5M

TX5P

TPVDD

TPVSS

HSYNC

VSYNC

RSET

AVDD_1

AVDD_2

AVSSQ

AVSSN_1

AVSSN_2

VDD1DI

VSS1DI

H2SYNC

V2SYNC

COMP

R2SET

A2VDD_1

A2VDD_2

A2VSSQ

VDD2DI

VSS2DI

AL9

AM9

AK10

AL10

AL11

AM11

AL12

AM12

AK9

AJ9

AK11

AJ11

AK12

AJ12

AM8

AL8

AJ6

AK6

AL6

AM6

AJ7

AK7

AL7

AM7

AK8

AK24

R

AM24

G

AL24

B

AJ23

AJ22

AL22

AL25

AM25

AK23

AK25

AJ24

AM23

AL23

AK15

R2

AM15

G2

AL15

B2

AF15

AG15

AJ15

Y

AJ13

C

AH15

AK14

AM16

AL16

AM17

AL17

AK13

AJ16

AJ17

AL14

3

C246

C246

C247

C247

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

+TXVDDR

C249

C249

C250

C250

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

A_R_DAC1 [13]

A_G_DAC1 [13]

A_B_DAC1 [13]

A_HSYNC_DAC1 [1,7,13]

A_VSYNC_DAC1 [7,13]

RSET

R31 499R

R31 499R

+AVDD

GND_AVSSQ

+VDD1DI

R2SET GND_A2VSSQ

R32 715RR32 715R

+A2VDD

C56

C56

10nF

10nF

+VDD2DI

C59

C59

10nF

10nF

GND_AVSSQ

RESISTOR, 499R 1% 1/16W EIA(0402)

RESISTOR, 499R 1% 1/16W EIA(0402)

C62

C62

C63

C63

100nF

100nF

10nF

10nF

C54

C54

C53

C53

100nF

100nF

10nF

10nF

A_R_DAC2 [14]

A_G_DAC2 [14]

A_B_DAC2 [14]

A_HSYNC_DAC2 [7,14]

A_VSYNC_DAC2 [7,14]

DAC2_Y [15]

DAC2_C [15]

DAC2_COMP [15]

C58

C58

C57

C57

100nF

100nF

1uF_6.3V

1uF_6.3V

C60

C60

1uF_6.3V

1uF_6.3V

C251

C251

10uF

10uF

+TPVDD

C64

C64

1uF_6.3V

1uF_6.3V

C55

C55

1uF_6.3V

1uF_6.3V

NS14 NS_VIANS14 NS_VIA

GND_TPVSS

NS13 NS_VIANS13 NS_VIA

GND_TXVSSR

NS8 NS_VIANS8 NS_VIA

NS9 NS_VIANS9 NS_VIA

NS10 NS_VIANS10 NS_VIA

Place close to ASIC

12

12

NS5 NS_VIANS5 NS_VIA

GND_AVSSQ

NS6 NS_VIANS6 NS_VIA

GND_AVSSN

NS7 NS_VIANS7 NS_VIA

GND_VSS1DI

GND_A2VSSN

GND_A2VSSQ

GND_VSS2DI

2

R136 182RR136 182R

R132 182RR132 182R

R133 182RR133 182R

R134 182RR134 182R

R135 182RR135 182R

R131 182RR131 182R

R130 182R

R130 182R

LF RESISTOR 324R 1% 1/16W EIA(0402)

LF RESISTOR 324R 1% 1/16W EIA(0402)

12

12

12

12

12

12

TjXCM [14]

TjXCP [14]

TjX0M [14]

TjX0P [14]

TjX1M [14]

TjX1P [14]

TjX2M [14]

TjX2P [14]

TjX3M [14]

TjX3P [14]

TjX4M [14]

TjX4P [14]

TjX5M [14]

TjX5P [14]

1

A A

ATI Technologies Inc.

ATI Technologies Inc.

Place R_RTCLK close to XTAL so the

main clock line has shortest stub

5

4

www.vinafix.vn

3

2

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

105-A67700-00A

105-A67700-00A

105-A67700-00A

1

of

of

of

319Monday, December 19, 2005

319Monday, December 19, 2005

319Monday, December 19, 2005

1

1

1

Page 4

5

+MVDDQ

C307

C306

C306

1uF_6.3V

1uF_6.3V

C316

C316

1uF_6.3V

1uF_6.3V

C329

C329

1uF_6.3V

1uF_6.3V

+PVDD

C231

C231

1uF_6.3V

1uF_6.3V

C242

C242

1uF_6.3V

1uF_6.3V

C237

C237

1uF_6.3V

1uF_6.3V

C69

C69

10nF

10nF

C307

1uF_6.3V

1uF_6.3V

C317

C317

1uF_6.3V

1uF_6.3V

C330

C330

1uF_6.3V

1uF_6.3V

C305

C303

C301

C301

1uF_6.3V

1uF_6.3V

C311

C311

1uF_6.3V

D D

C C

B B

1uF_6.3V

C321

C321

1uF_6.3V

1uF_6.3V

C341

C341

10uF

10uF

C303

C302

C302

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C312

C312

C313

C313

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C326

C326

C322

C322

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C343

C343

C342

C342

10uF

10uF

10uF

10uF

+MVDDQ

NS12 NS_VIANS12 NS_VIA

1 2

GND_PVSS +PCIE

C305

C304

C304

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C314

C314

C315

C315

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C328

C328

C327

C327

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C344

C344

C345

C345

10uF

10uF

10uF

10uF

NS16 NS_VIANS16 NS_VIA

12

GND_VSSRH0

+3.3V

+3.3V

B54B54

B55B55

C241

C241

1uF_6.3V

1uF_6.3V

C236

C236

1uF_6.3V

1uF_6.3V

C308

C308

1uF_6.3V

1uF_6.3V

C318

C318

1uF_6.3V

1uF_6.3V

C232

C232

1uF_6.3V

1uF_6.3V

NS17 NS_VIANS17 NS_VIA

12

GND_VSSRH1

C243

C243

1uF_6.3V

1uF_6.3V

C238

C238

1uF_6.3V

1uF_6.3V

C70

C70

100nF

100nF

4

C244

C244

1uF_6.3V

1uF_6.3V

C239

C239

1uF_6.3V

1uF_6.3V

C71

C71

1uF_6.3V

1uF_6.3V

C309

C309

1uF_6.3V

1uF_6.3V

C319

C319

1uF_6.3V

1uF_6.3V

C233

C233

1uF_6.3V

1uF_6.3V

C310

C310

1uF_6.3V

1uF_6.3V

C320

C320

1uF_6.3V

1uF_6.3V

C245

C245

10uF

10uF

C234

C234

1uF_6.3V

1uF_6.3V

+PVDD

GND_PVSS

AB10

AC19

AD18

AC20

AD19

AD20

AH14

C1

J1

M1

R1

V1

AA1

A3

P9

J10

N9

P10

A9

Y10

P8

R9

Y9

J11

A21

M10

N10

Y8

J18

J19

K21

A12

H13

A15

J20

J13

K11

K19

A18

L23

K20

K24

L24

H19

A24

K13

J32

A30

C32

F32

L32

A27

F1

A28

E1

AB9

AA9

AJ5

AM5

AL5

AK5

AE2

AE3

AE4

AE5

AJ14

U1E

U1E

VDDR1_1

VDDR1_2

VDDR1_3

VDDR1_4

VDDR1_5

VDDR1_6

VDDR1_7

VDDR1_8

VDDR1_9

VDDR1_10

VDDR1_11

VDDR1_12

VDDR1_13

VDDR1_14

VDDR1_15

VDDR1_16

VDDR1_17

VDDR1_18

VDDR1_20

VDDR1_21

VDDR1_22

VDDR1_23

VDDR1_24

VDDR1_25

VDDR1_26

VDDR1_27

VDDR1_28

VDDR1_29

VDDR1_30

VDDR1_31

VDDR1_32

VDDR1_33

VDDR1_34

VDDR1_35

VDDR1_36

VDDR1_37

VDDR1_38

VDDR1_39

VDDR1_40

VDDR1_41

VDDR1_42

VDDR1_43

VDDR1_45

VDDR1_46

VDDRH0

VDDRH1

VSSRH0

VSSRH1

VDDR3_1

VDDR3_2

VDDR3_3

VDDR3_4

VDDR3_5

VDDR3_6

VDDR3_7

VDDR3_8

VDDR4_1

VDDR4_2

VDDR4_3

VDDR4_4

VDDR5_1

VDDR5_2

VDDR5_3

VDDR5_4

PVDD

PVSS

RV530 unfused A11

RV530 unfused A11

Memory I/O

Memory I/O

I/O

Clock

I/O

Clock

PART 5 OF 7

PART 5 OF 7

Memory

Memory

Selected PLL's

Selected PLL's

3

PCIE_PVSS

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

BBP_4

BBP_3

BBP_2

BBP_1

VDDCI_1

VDDCI_2

VDDCI_3

VDDCI_4

VDDCI_6

VDDCI_7

VDDCI_8

VDD25_1

VDD25_2

VDD25_3

VDD25_4

VDD25_5

VDD25_6

MPVDD

MPVSS

VDDPLL

V23

N23

P23

U23

W23

N29

N28

N27

N26

N25

AL31

AM31

AM30

AL32

AL30

AM28

AL29

AM29

AM27

AC11

AC12

P14

U15

W14

W15

R17

R15

V15

V16

T16

U16

T17

U17

V14

R18

T18

V18

P18

P19

R19

W19

AD11

AC14

M23

V10

K18

W10

T14

W17

P16

T23

K14

U19

AC13

AC16

AC18

L10

K22

AA10

A6

A5

AC15

+VDDC

+MPVDD

GND_MPVSS

+VDDPLL

C214

C214

1uF_6.3V

1uF_6.3V

C201

C201

1uF_6.3V

1uF_6.3V

C191

C191

1uF_6.3V

1uF_6.3V

C161

C161

1uF_6.3V

1uF_6.3V

C171

C171

1uF_6.3V

1uF_6.3V

C215

C215

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C202

C202

1uF_6.3V

1uF_6.3V

C192

C192

1uF_6.3V

1uF_6.3V

C162

C162

1uF_6.3V

1uF_6.3V

C172

C172

1uF_6.3V

1uF_6.3V

C67

C67

C211

C211

1uF_6.3V

1uF_6.3V

C206

C206

1uF_6.3V

1uF_6.3V

B56B56

PCIE_PVDD_12_1

PCIE_PVDD_12_2

PCIE_PVDD_12_3

PCIE_PVDD_12_4

PCIE_VDDR_12_1

PCIE_VDDR_12_2

PCIE_VDDR_12_3

PCIE_VDDR_12_4

PCIE_VDDR_12_5

PCIE_VDDR_12_6

PCIE_VDDR_12_7

PCIE_VDDR_12_8

PCIE_VDDR_12_9

PCIE_VDDR_12_10

PCIE_VDDR_12_11

PCIE_VDDR_12_12

PCIE_VDDR_12_13

PCI-Express

PCI-Express

PCIE_VDDR_12_14

P

P

O

O

Core

Core

W

W

E

E

R

R

I/0

I/0

I/O Internal

I/O Internal

100nF

100nF

C203

C203

1uF_6.3V

1uF_6.3V

C193

C193

1uF_6.3V

1uF_6.3V

C163

C163

1uF_6.3V

1uF_6.3V

C173

C173

1uF_6.3V

1uF_6.3V

C66

C66

C212

C212

1uF_6.3V

1uF_6.3V

C207

C207

1uF_6.3V

1uF_6.3V

2

+PCIE

C204

C204

1uF_6.3V

1uF_6.3V

GND_PCIE_PVSS

C194

C194

1uF_6.3V

1uF_6.3V

C164

C164

1uF_6.3V

1uF_6.3V

C174

C174

1uF_6.3V

1uF_6.3V

+VDDC

C208

C208

1uF_6.3V

1uF_6.3V

C65

C65

10nF

10nF

C213

C213

10uF

10uF

22uF_16V

22uF_16V

NS18 NS_VIANS18 NS_VIA

C195

C195

1uF_6.3V

1uF_6.3V

C165

C165

1uF_6.3V

1uF_6.3V

C175

C175

1uF_6.3V

1uF_6.3V

C209

C209

1uF_6.3V

1uF_6.3V

+MPVDD

C68

C68

12

C196

C196

1uF_6.3V

1uF_6.3V

C166

C166

1uF_6.3V

1uF_6.3V

C177

C177

1uF_6.3V

1uF_6.3V

C197

C197

1uF_6.3V

1uF_6.3V

C167

C167

1uF_6.3V

1uF_6.3V

C178

C178

1uF_6.3V

1uF_6.3V

+VDDC_CT

C210

C210

10uF

10uF

NS11NS_VIA NS11NS_VIA

GND_MPVSS

1

+PCIE

C198

C198

1uF_6.3V

1uF_6.3V

C168

C168

1uF_6.3V

1uF_6.3V

C179

C179

1uF_6.3V

1uF_6.3V

12

C169

C169

1uF_6.3V

1uF_6.3V

C180

C180

1uF_6.3V

1uF_6.3V

C199

C199

10uF

10uF

C170

C170

1uF_6.3V

1uF_6.3V

C200

C200

10uF

10uF

C181

C181

10uF

10uF

C182

C182

10uF

10uF

C183

C183

10uF

10uF

C184

C184

10uF

10uF

+VDDC

C185

C185

10uF

10uF

A A

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

www.vinafix.vn

3

2

Date: Sheet

105-A67700-00A

105-A67700-00A

105-A67700-00A

1

1

1

1

of

of

of

419Thursday, October 13, 2005

419Thursday, October 13, 2005

419Thursday, October 13, 2005

Page 5

5

4

3

2

1

RV530 MEMORY CHANNELS A and B

D D

U1C

C352

C352

10nF

10nF

U1C

M31

DQA_0

M30

DQA_1

L31

DQA_2

L30

DQA_3

H30

DQA_4

G31

DQA_5

G30

DQA_6

F31

DQA_7

M27

DQA_8

M29

DQA_9

L28

DQA_10

L27

DQA_11

J27

DQA_12

H29

DQA_13

G29

DQA_14

G27

DQA_15

M26

DQA_16

L26

DQA_17

M25

DQA_18

L25

DQA_19

J25

DQA_20

G28

DQA_21

H27

DQA_22

H26

DQA_23

F26

DQA_24

G26

DQA_25

H25

DQA_26

H24

DQA_27

H23

DQA_28

H22

DQA_29

J23

DQA_30

J22

DQA_31

E23

DQA_32

D22

DQA_33

D23

DQA_34

E22

DQA_35

E20

DQA_36

F20

DQA_37

D19

DQA_38

D18

DQA_39

B19

DQA_40

B18

DQA_41

C17

DQA_42

B17

DQA_43

C14

DQA_44

B14

DQA_45

C13

DQA_46

B13

DQA_47

D17

DQA_48

E18

DQA_49

E17

DQA_50

F17

DQA_51

E15

DQA_52

E14

DQA_53

F14

DQA_54

D13

DQA_55

H18

DQA_56

H17

DQA_57

G18

DQA_58

G17

DQA_59

G15

DQA_60

G14

DQA_61

H14

DQA_62

J14

DQA_63

C31

MVREFD_0

C30

MVREFS_0

RV530 unfused A11

RV530 unfused A11

M_MDA[63..0][11]

M_MDA0

M_MDA1

M_MDA2

M_MDA3

M_MDA4

M_MDA5

M_MDA6

M_MDA7

M_MDA8

M_MDA9

M_MDA10

M_MDA11

M_MDA12

M_MDA13

M_MDA14

M_MDA15

M_MDA16

M_MDA17

M_MDA18

M_MDA19

M_MDA20

M_MDA21

M_MDA22

M_MDA23

M_MDA24

M_MDA25

M_MDA26

M_MDA27

M_MDA28

M_MDA29

MVREF_0

C351

C351

100nF

100nF

M_MDA30

M_MDA31

M_MDA32

M_MDA33

M_MDA34

M_MDA35

M_MDA36

M_MDA37

M_MDA38

M_MDA39

M_MDA40

M_MDA41

M_MDA42

M_MDA43

M_MDA44

M_MDA45

M_MDA46

M_MDA47

M_MDA48

M_MDA49

M_MDA50

M_MDA51

M_MDA52

M_MDA53

M_MDA54

M_MDA55

M_MDA56

M_MDA57

M_MDA58

M_MDA59

M_MDA60

M_MDA61

M_MDA62

M_MDA63

C C

+MVDDQ

R161

R161

100R

100R

1%

B B

R162

R162

100R

100R

1%

Channel A

Part 3 of 7

Part 3 of 7

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13

MAA_14

MAA_15

DQMAb_0

DQMAb_1

DQMAb_2

DQMAb_3

DQMAb_4

DQMAb_5

DQMAb_6

DQMAb_7

MEMORY INTERFACE A

MEMORY INTERFACE A

DDR1 DDR2 DDR3

DDR1 DDR2 DDR3

Not usedbidir. strobe

Not usedbidir. strobe

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

QSA_0B

QSA_1B

QSA_2B

QSA_3B

QSA_4B

QSA_5B

QSA_6B

bidir. differential strobe

bidir. differential strobe

QSA_7B

write stroberead strobe

write stroberead strobe

ODTA0

For DDR2

For DDR2

ODTA1

CLKA0

CLKA0b

CKEA0

RASA0b

CASA0b

WEA0b

CSA0b_0

CSA0b_1

CLKA1

CLKA1b

CKEA1

RASA1b

CASA1b

WEA1b

CSA1b_0

CSA1b_1

D26

F28

D28

D25

E24

E26

D27

F25

C26

B26

D29

B27

E27

E29

B25

C25

H31

J29

J26

G23

E21

B15

D14

J17

J31

K29

K25

F23

D20

B16

D16

H15

K31

K28

K26

G24

D21

C16

D15

J15

F29

D24

D31

E31

B30

B28

C29

B31

B29

C28

B20

C19

C22

B24

B22

B21

B23

C23

M_MAA0

M_MAA1

M_MAA2

M_MAA3

M_MAA4

M_MAA5

M_MAA6

M_MAA7

M_MAA8

M_MAA9

M_MAA10

M_MAA11

M_MAA12

M_MAA14

M_MAA15

M_DQMA#0

M_DQMA#1

M_DQMA#2

M_DQMA#3

M_DQMA#4

M_DQMA#5

M_DQMA#6

M_DQMA#7

M_QSA0

M_QSA1

M_QSA2

M_QSA3

M_QSA4

M_QSA5

M_QSA6

M_QSA7

CLKA0 [11]

CLKA#0 [11]

CKEA0 [11]

RASA#0 [11]

CASA#0 [11]

WEA#0 [11]

CSA#0_0 [11]

CLKA1 [11]

CLKA#1 [11]

CKEA1 [11]

RASA#1 [11]

CASA#1 [11]

WEA#1 [11]

CSA#1_0 [11]

M_MAA[12..0] [11]

M_MAA[15..14] [11]

M_DQMA#[7..0] [11]

M_QSA[7..0] [11]

+MVDDQ

R165

R165

100R

100R

1%

R166

R166

100R

100R

1%

MVREF_1

C355

C355

100nF

100nF

C356

C356

10nF

10nF

M_MDB[63..0][12]

R172

R172

R171

R171

4.7K

4.7K

4.7K

4.7K

RESISTOR, 4.7K 5% 1/16W EIA(0402)

RESISTOR, 4.7K 5% 1/16W EIA(0402)

M_MDB0

M_MDB1

M_MDB2

M_MDB3

M_MDB4

M_MDB5

M_MDB6

M_MDB7

M_MDB8

M_MDB9

M_MDB10

M_MDB11

M_MDB12

M_MDB13

M_MDB14

M_MDB15

M_MDB16

M_MDB17

M_MDB18

M_MDB19

M_MDB20

M_MDB21

M_MDB22

M_MDB23

M_MDB24

M_MDB25

M_MDB26

M_MDB27

M_MDB28

M_MDB29

M_MDB30

M_MDB31

M_MDB32

M_MDB33

M_MDB34

M_MDB35

M_MDB36

M_MDB37

M_MDB38

M_MDB39

M_MDB40

M_MDB41

M_MDB42

M_MDB43

M_MDB44

M_MDB45

M_MDB46

M_MDB47

M_MDB48

M_MDB49

M_MDB50

M_MDB51

M_MDB52

M_MDB53

M_MDB54

M_MDB55

M_MDB56

M_MDB57

M_MDB58

M_MDB59

M_MDB60

M_MDB61

M_MDB62

M_MDB63

R170

R170

R169

R169

4.7K

4.7K

243R

243R

LF RES EIA(0402) 243R 1% 1/16W

LF RES EIA(0402) 243R 1% 1/16W

U1D

U1D

B12

DQB_0

C12

DQB_1

B11

DQB_2

C11

DQB_3

C8

DQB_4

B7

DQB_5

C7

DQB_6

B6

DQB_7

F12

DQB_8

D12

DQB_9

E11

DQB_10

F11

DQB_11

F9

DQB_12

D8

DQB_13

D7

DQB_14

F7

DQB_15

G12

DQB_16

G11

DQB_17

H12

DQB_18

H11

DQB_19

H9

DQB_20

E7

DQB_21

F8

DQB_22

G8

DQB_23

G6

DQB_24

G7

DQB_25

H8

DQB_26

J8

DQB_27

K8

DQB_28

L8

DQB_29

K9

DQB_30

L9

DQB_31

K5

DQB_32

L4

DQB_33

K4

DQB_34

L5

DQB_35

N5

DQB_36

N6

DQB_37

P4

DQB_38

R4

DQB_39

P2

DQB_40

R2

DQB_41

T3

DQB_42

T2

DQB_43

W3

DQB_44

W2

DQB_45

Y3

DQB_46

Y2

DQB_47

T4

DQB_48

R5

DQB_49

T5

DQB_50

T6

DQB_51

V5

DQB_52

W5

DQB_53

W6

DQB_54

Y4

DQB_55

R8

DQB_56

T8

DQB_57

R7

DQB_58

T7

DQB_59

V7

DQB_60

W7

DQB_61

W8

DQB_62

W9

DQB_63

B3

MVREFD_1

C3

MVREFS_1

AA3

DRAM_RST

AA5

TEST_MCLK

AA2

TEST_YCLK

AA7

MEMTEST

RV530 unfused A11

RV530 unfused A11

Channel B

Part 4 of 7

Part 4 of 7

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_12

MAB_13

MAB_14

MAB_15

DQMBb_0

DQMBb_1

DQMBb_2

DQMBb_3

DQMBb_4

DQMBb_5

DQMBb_6

DQMBb_7

MEMORY INTERFACE B

MEMORY INTERFACE B

DDR1 DDR2 DDR3

DDR1 DDR2 DDR3

Not used bidir. strobe

Not used bidir. strobe

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

QSB_0B

QSB_1B

QSB_2B

read strobe

read strobe

QSB_3B

QSB_4B

QSB_5B

QSB_6B

QSB_7B

bidir. differential strobe

bidir. differential strobe

write strobe

write strobe

ODTB0

For DDR2

For DDR2

ODTB1

CLKB0

CLKB0b

CKEB0

RASB0b

CASB0b

WEB0b

CSB0b_0

CSB0b_1

CLKB1

CLKB1b

CKEB1

RASB1b

CASB1b

WEB1b

CSB1b_0

CSB1b_1

G4

E6

E4

H4

J5

G5

F4

H6

G3

G2

D4

F2

F5

D5

H2

H3

B8

D9

G9

K7

M5

V2

W4

T9

B9

D10

H10

K6

N4

U2

U4

V8

B10

E10

G10

J7

M4

U3

V4

V9

D6

J4

B4

B5

C2

E2

D3

B2

D2

E3

N2

P3

L3

J2

L2

M2

K2

K3

M_MAB0

M_MAB1

M_MAB2

M_MAB3

M_MAB4

M_MAB5

M_MAB6

M_MAB7

M_MAB8

M_MAB9

M_MAB10

M_MAB11

M_MAB12

M_MAB14

M_MAB15

M_DQMB#0

M_DQMB#1

M_DQMB#2

M_DQMB#3

M_DQMB#4

M_DQMB#5

M_DQMB#6

M_DQMB#7

M_QSB0

M_QSB1

M_QSB2

M_QSB3

M_QSB4

M_QSB5

M_QSB6

M_QSB7

CLKB0 [12]

CLKB#0 [12]

CKEB0 [12]

RASB#0 [12]

CASB#0 [12]

WEB#0 [12]

CSB#0_0 [12]

CLKB1 [12]

CLKB#1 [12]

CKEB1 [12]

RASB#1 [12]

CASB#1 [12]

WEB#1 [12]

CSB#1_0 [12]

M_MAB[12..0] [12]

M_MAB[15..14] [12]

M_DQMB#[7..0] [12]

M_QSB[7..0] [12]

A A

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

www.vinafix.vn

3

2

Date: Sheet

105-A67700-00A

105-A67700-00A

105-A67700-00A

1

1

1

1

of

of

of

519Friday, December 16, 2005

519Friday, December 16, 2005

519Friday, December 16, 2005

Page 6

5

D D

C C

B B

A A

4

U1F

AH27

AC23

AL27

AB26

AC26

AD25

AE26

AF26

AD26

AG25

AH26

AC28

AH29

AF28

AC29

AB27

AJ26

AJ32

AK29

AA29

AB29

AD29

AE29

AF29

AG29

AJ29

AK26

AK30

AG26

AF30

AC30

AA31

AD31

AK32

AJ28

AJ30

AK31

AA23

AG31

AB23

AC24

AH24

AA25

AA26

AE27

AD10

AF14

AG11

AG16

R23

P25

R25

T26

U26

W26

Y26

Y28

U28

P28

V29

W27

V26

P26

P29

R29

T29

U29

W29

Y29

N30

R31

V31

P30

U30

Y30

N24

P24

R24

T24

U24

V24

W24

Y24

V25

R26

T27

AD7

AE8

AL1

AM2

K10

T10

E12

AC9

AD8

F10

AA4

B1

H1

L1

P1

U1

Y1

A2

E8

H5

M8

C5

J3

L6

M6

P6

V3

R3

C6

C9

F6

H7

J6

U1F

PCIE_VSS_1

PCIE_VSS_2

PCIE_VSS_3

PCIE_VSS_4

PCIE_VSS_5

PCIE_VSS_6

PCIE_VSS_7

PCIE_VSS_8

PCIE_VSS_9

PCIE_VSS_10

PCIE_VSS_11

PCIE_VSS_12

PCIE_VSS_13

PCIE_VSS_14

PCIE_VSS_15

PCIE_VSS_16

PCIE_VSS_17

PCIE_VSS_18

PCIE_VSS_19

PCIE_VSS_20

PCIE_VSS_21

PCIE_VSS_22

PCIE_VSS_23

PCIE_VSS_24

PCIE_VSS_25

PCIE_VSS_26

PCIE_VSS_27

PCIE_VSS_28

PCIE_VSS_29

PCIE_VSS_30

PCIE_VSS_31

PCIE_VSS_32

PCIE_VSS_33

PCIE_VSS_34

PCIE_VSS_35

PCIE_VSS_36

PCIE_VSS_37

PCIE_VSS_38

PCIE_VSS_39

PCIE_VSS_40

PCIE_VSS_41

PCIE_VSS_42

PCIE_VSS_43

PCIE_VSS_44

PCIE_VSS_45

PCIE_VSS_46

PCIE_VSS_47

PCIE_VSS_48

PCIE_VSS_49

PCIE_VSS_50

PCIE_VSS_51

PCIE_VSS_52

PCIE_VSS_53

PCIE_VSS_54

PCIE_VSS_55

PCIE_VSS_56

PCIE_VSS_57

PCIE_VSS_58

PCIE_VSS_59

PCIE_VSS_60

PCIE_VSS_61

PCIE_VSS_62

PCIE_VSS_63

PCIE_VSS_64

PCIE_VSS_65

PCIE_VSS_66

PCIE_VSS_69

PCIE_VSS_70

PCIE_VSS_71

PCIE_VSS_72

PCIE_VSS_73

PCIE_VSS_74

PCIE_VSS_75

PCIE_VSS_76

PCIE_VSS_77

PCIE_VSS_78

PCIE_VSS_79

PCIE_VSS_80

PCIE_VSS_81

PCIE_VSS_82

PCIE_VSS_83

PCIE_VSS_84

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

Part 6 of 7

Part 6 of 7

CORE GND

CORE GND

3

VSS_45

VSS_44

VSS_43

VSS_42

VSS_41

VSS_40

VSS_39

VSS_38

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

PCI-Express GND

PCI-Express GND

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_163

VSS_164

VSS_165

AD16

AA6

P7

P5

M3

M9

L7

M7

AD17

AH11

A8

U7

C10

E9

F3

J9

N7

N3

Y5

AM13

AC10

Y6

U6

E5

AL13

A11

U8

U9

U10

R6

AD6

V6

AD14

AD13

D11

J12

K12

A13

F13

E13

F15

K16

J21

H16

T15

V17

C15

C4

U14

P15

A16

E16

G13

G16

P17

R16

R14

W16

C18

F16

W18

U18

AE16

AE17

A19

H32

F19

G19

N8

Y7

T19

V19

G21

C21

F21

AE14

AK16

U5

F22

F18

K30

C24

F24

M24

A25

D30

E25

G25

G20

G22

F27

E28

H21

C27

E32

H28

J30

K17

K27

M32

A22

C20

E19

H20

J24

M28

J28

J16

F30

L29

A31

B32

E30

AE15

AG23

AD9

AF16

AH10

AJ10

AD15

AH16

2

1

Y23

BBN_4

K15

BBN_3

R10

BBN_2

AC17

BBN_1

RV530 unfused A11

RV530 unfused A11

5

4

www.vinafix.vn

3

VEFUSE

K23

2

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

105-A67700-00A

105-A67700-00A

105-A67700-00A

1

of

of

of

619Thursday, October 13, 2005

619Thursday, October 13, 2005

619Thursday, October 13, 2005

1

1

1

Page 7

5

D D

STV/HDTV#_OUT_DET[15]

C C

4

U1G

DVPDATA_14

AF10

AG10

AE10

AH9

AJ8

AH8

AG9

AH7

AG8

AF7

AE9

AG7

AF9

AG1

AF2

AF1

AF3

AG2

AG3

AH2

AH3

AJ2

AJ1

AK2

AK1

AK3

AL2

AL3

AM3

AE6

AF4

AF5

AG4

AJ3

AH4

AJ4

AG5

AH5

AF6

AE7

AG6

U1G

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

VID_7

VPCLK0

VHAD_0

VHAD_1

VPHCTL

VIPCLK

DVPCLK

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

RV530 unfused A11

RV530 unfused A11

VIP

VIP

Capture

Capture

VIP

VIP

Host

Host

PART 7 OF 7

PART 7 OF 7

Zoom Video Port

Zoom Video Port

General

General

Purpose

Purpose

I/O

I/O

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GENERICA

GENERICB

GENERICC

GENERICD

ROMCSb

VARY_BL

No Connect

No Connect

NC_DVOVMODE_0

NC_DVOVMODE_1

3

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

DVALID

PSYNC

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_22

AD4

AD2

AD1

AD3

AC1

AC2

AC3

AB2

AC6

AC5

AC4

AB3

AB4

AB5

AD5

AB8

AA8

AB7

AK22

AF23

AE23

AD23

AH6

AF8

AC7

AD12

AE11

AJ21

AK21

AH21

AG21

AG20

AH20

AB6

AK4

AL4

GENERICC

DVALID

PSYNC

ROMCSb

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_9

DEBUG BUS

No testpoint means the net

can be accessed from a pad

somewhere else

GPIO_10

GPIO_11

GPIO_12

GPIO_13

2

GPIO PIN STRAP ALTERNATE USE

GPIO_0 YES VIDB_0 (OUTPUT)

GPIO_1 YES VIDB_1 (OUTPUT)

GPIO_2 YES VIDB_2 (OUTPUT)

GPIO_3 YES VIDB_3 (OUTPUT)

GPIO_4 YES VIDB_4 (OUTPUT)

GPIO_5 YES VIDB_5 (OUTPUT)

GPIO_6 YES LDAC (OUTPUT)

GPIO_7 NO PAL/NTSC TV (INPUT)

GPIO_8 YES GPIO_9 YES FLOW_CNTL_EN (OUTPUT)

GPIO_10 NO TESTOUT(8) (OUTPUT)

GPIO_11 YES TESTOUT(9) (OUTPUT)

GPIO_12 YES TESTOUT(10) (OUTPUT)

GPIO_13 YES TESTOUT(11 (OUTPUT))

GPIO_14 NO HPD_DVI1 (HPD2) (INPUT)

GPIO_15 NO VIDA#/B (OUTPUT)

GPIO_16 NO 12VEXT_DETECT (INPUT)

GPIO_17 NO T_INT#(INPUT) & 12VEXT_DETECT# (INPUT)

1

PIN BASED STRAPS

+3.3V

GPIO_0

GPIO_1

GPIO_3

B B

A_VSYNC_DAC1[3,13]

A_HSYNC_DAC1[1,3,13]

A_VSYNC_DAC2[3,14]

A A

5

A_HSYNC_DAC2[3,14]

GPIO_2

GPIO_4

GPIO_6

GPIO_5

GPIO_8

GPIO_9

GPIO_13

GPIO_12

GPIO_11

A_VSYNC_DAC1

A_HSYNC_DAC1

A_VSYNC_DAC2

A_HSYNC_DAC2

GENERICC

DVALID

PSYNC

GPIO_7

4

R51 10KR51 10K

R52 10KR52 10K

R53 10KDNIR53 10KDNI

R54 10KDNIR54 10KDNI

R55 10KDNIR55 10KDNI

R56 10KDNIR56 10KDNI

R57 10KR57 10K

R58 10KDNIR58 10KDNI

R59 10KR59 10K

R60 10KR60 10K

R61 10KDNIR61 10KDNI

R62 10KDNIR62 10KDNI

R63 10KDNIR63 10KDNI MR63 10KMR63 10K

R64 10KR64 10K

R65 10KDNIR65 10KDNI

R66 10KDNIR66 10KDNI

R67 10KDNIR67 10KDNI

R68 10KDNIR68 10KDNI

R69 10K DNIR69 10K DNI

R70 10KR70 10K

MR51 10KDNIMR51 10KDNI

MR52 10KDNIMR52 10KDNI

MR53 10KMR53 10K

MR54 10KMR54 10K

MR55 10KMR55 10K

MR56 10KMR56 10K

MR57 10KDNIMR57 10KDNI

MR58 10KMR58 10K

MR59 10KDNIMR59 10KDNI

MR60 10KDNIMR60 10KDNI

MR61 10KMR61 10K

MR62 10KMR62 10K

MR64 10KDNIMR64 10KDNI

MR65 10KMR65 10K

MR66 10KMR66 10K

MR67 10KMR67 10K

MR68 10KMR68 10K

MR69 10KMR69 10K

MR70 10KDNIMR70 10KDNI

www.vinafix.vn

GPIO(0) - TX_PWRS_ENB (Transmitter Power Savings Enable)

0: 50% Tx output swing for mobile mode

1: full Tx output swing (Default setting for Desktop)

GPIO(1) - TX_DEEMPH_EN (Transmitter De-emphasis Enable)

0: Tx de-emphasis disabled for mobile mode

1: Tx de-emphasis enabled (Default setting for Desktop)

GPIO(3:2) - Miscellaneous PCI-Express Modes

00: Halt impedance calibration before transmitter is enabled and enable receiver detection (Default

setting for Desktop)

01: Allow impedance calibration to continue on in the background AFTER transmitter has

been enabled and enable receive detection.

10: Bypass common-mode detection & receiver detection and halt impedance calibration before TX_EN.

11: Short-circuit internal loopback and halt impedance calibration before TX_EN and enable

receiver detection.

GPIO(4) - DEBUG_ACCESS: 0 for normal operation, 1 for debug mode

GPIO(6:5) - PLL_IBIAS_RD (Reduced mirror bias setting for PHY PLL)

Provide 4 different IBIAS settings - Set to 00 for R520

GPIO(8) - FORCE_COMPLIANCE: 0 for Normal operation, 1 for Force into Compliance Mode

GPIO(9,13:11) - ROMIDCFG[3..0]

1001 - 1M AT25F1024 ROM (Atmel)

1010 - 1M AT45DB011 ROM (Atmel)

1011 - 1M M25P10 ROM (ST)

1100 - 512K M25P05 ROM (ST) (ATI default)

1101 - 1M SST45LF010 ROM (SST), 1M W45B512 ROM (WinBond), 512K W45B012 ROM (WinBond)

1110 - 1M SST25VF010 ROM (SST), 512K SST25VF512 ROM (SST)

1111 - 1M NX25F011B ROM (NexFlash)

VSYNC - VIP_DEVICE

0: Slave VIP host port devices present (use if Theater is populated)

1: No slave VIP host port devices reporting presence during reset (use for configurations without video-in)

HSYNC - DWNGRD

This straps allow a Workstation bonded part to be downgraded to a normal part on a board. This

allow inventory management to better balance demand.

0 - Device remain a Workstation grade part

1 - Part is downgraded to a Normal part

H2SYNC, V2SYNC, GENERICC - Star Memory System repair mode

000 - Default

00 : RESERVED

01 : SAMSUNG

TV OUT STANDARD (Jumper position overwrite resistor settings)

0 - PAL TVO (Jumper position 2-3)

1 - NTSC TVO (Jumper position 1-2)

3

ATI Feature I

FOR TSOP ONLYMEMORY CONFIG

10: INFINEON

11: HYNIX

DEFAULT

ATI PCIE FEATURE I

ATI PCIE FEATURE II

ATI PCIE FEATURE III

ATI Feature II

ATI Board Feature II

+3.3V

R35

R35

10K

10K

GPIO_8

GPIO_9

GPIO_10

ROMCSb

R36 10KR36 10K

+3.3V

2

+3.3V

MR36

MR36

10K

10K

DNI

DNI

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

U2

U2

5

D

6

C

1

S

7

HOLD

3

W

8

VCC

VSS

M25P05-AVNM6P

M25P05-AVNM6P

C51

C51

100nF

100nF

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

105-A67700-00A

105-A67700-00A

105-A67700-00A

2

Q

BIOS1

BIOS1

BIOS

BIOS

4

113-XXXXXX-XXX

113-XXXXXX-XXX

VIDEO BIOS

FIRMWARE

1

1

1

of

of

of

719Friday, December 16, 2005

719Friday, December 16, 2005

1

719Friday, December 16, 2005

Page 8

8

7

6

5

4

3

2

1

CORE REGULATOR +VDDC

+12V_BUS

ER1593

ER1593

2R2

D D

C C

2R2

ED28

ED28

BAT54SLT1

BAT54SLT1

EC3

EC3

0.1uF

0.1uF

ER15920RER1592

EMU31

EMU31

1

BOOT

2

UGATE

3

GND

LGATE4VCC

APW7120

APW7120

ER16180RER1618

PHASE

0R

+12V_BUS

VDDC=1.22V

EC116

EC116

10uF

EL21

EL21

Dip 1.6uH

Dip 1.6uH

10uF

EC1532

EC1532

1.0uF

1.0uF

ER15940RER1594

0R

0R

8

7

OPS

6

FB

5

SS_VDDC3

EC143

EC143

0.1uF

0.1uF

APM2512 TO-252

APM2512 TO-252

ER6

ER6

19K

19K

ER5

ER5

383ohm

383ohm

EC1688

EC1688

100nF

100nF

G

G

DS

EQ28

EQ28

(TO-252)

DS

EQ31

EQ31

(TO-252)

APM2512 TO-252

APM2512 TO-252

ER1686

ER1686

205ohm

205ohm

ER7

ER7

200RF

200RF

VDDC=0.8 * [ 1 + ( ER1686 / ER5 )]

EC1149

EC1149

10uF

10uF

EC117

EC117

10uF

10uF

EC1146

EC1146

10uF

10uF

+12V_BUS

820uF_6.3V

820uF_6.3V

EB1

EB1

Chock 1.2u

Chock 1.2u

EC301

EC301

470UF

470UF

EC323

EC323

+VDDC

EC321

EC321

820uF_6.3V

820uF_6.3V

+MPVDD

EB61

EB61

60R

60R

EB60

EB60

60R

60R

+PCIE

B B

A A

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

105-A67700-00A

105-A67700-00A

105-A67700-00A

1

1

1

of

of

of

819Tuesday, December 20, 2005

819Tuesday, December 20, 2005

819Tuesday, December 20, 2005

1

www.vinafix.vn

Page 9

8

+12V_BUS

ER1595

D D

C C

ER1595

2R2

2R2

ED2

ED2

BAT54SLT1

BAT54SLT1

EC124

EC124

0.1uF

0.1uF

EMU42

EMU42

1

BOOT

2

UGATE

3

GND

LGATE4VCC

APW7120

APW7120

+12V_BUS

ER3070RER307

PHASE

0R

ER3080RER308

0R

ER15960RER1596

0R

8

7

OPS

6

FB

5

EC168

EC168

0.1uF

0.1uF

7

DS

EQ36

EQ36

G

APM3023NUC-TRL,TO252

APM3023NUC-TRL,TO252

ER10

ER10

19K

19K

DS

EQ37

EQ37

G

APM3023NUC-TRL,TO252

APM3023NUC-TRL,TO252

ER12

ER12

2.26K

2.26K

ER131KER13

1K

EC7

EC7

0.1uF

0.1uF

ER11

ER11

200RF

200RF

EL64

EL64

Dip 1.6uH

Dip 1.6uH

EC108

EC108

470uF_10V

470uF_10V

6

+12V_BUS

EB16

EB16

Chock 1.2u

Chock 1.2u

EC182

EC182

EC181

EC181

10uF

10uF

10uF

10uF

DNI DNI

EC164

EC164

10uF

10uF

Cout1

EC159

EC159

10uF

10uF

DNI

5

EC169

EC169

10uF

10uF

+MVDDC=2.6V

***

EC184

EC184

470uF_10V

470uF_10V

***

+MVDDC

4

+MVDDQ +MVDDC

EC346

EC346

EC347

EC347

10uf

10uf

10uf

10uf

3

2

1

MVDDC=0.8 * [ 1 + ( ER12 / ER13 )]

Q995

Q995

+3.3V_BUS

1234

R985

R985

100K

100K

APM2054NVC

APM2054NVC

6.3V

1206

C994

C994

0.1uf

0.1uf

C992

C992

10uf

10uf

Y5V

C993

C993

10uf

10uf

+3.3V

ER12 ER13

2.6V

B B

R11-0102T23-R01 R11-2261T13-W08

+VDDC

R9811KR981

1K

402

1%

R9822KR982

2K

402

1%

1

+12V_BUS

2 3

R983

R983

5.1K

5.1K

402

5%

Q991

Q991

MMBT3904

MMBT3904

R988 5.1KR988 5.1K

+12V_BUS

R984

R984

10K

10K

Q994

Q994

1

MMBT3904

MMBT3904

2 3

402

Power Sequencing

A A

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

105-A67700-00A

105-A67700-00A

105-A67700-00A

1

1

1

of

of

of

919Tuesday, December 27, 2005

919Tuesday, December 27, 2005

919Tuesday, December 27, 2005

1

www.vinafix.vn

Page 10

8

+3.3V

ER124

ER124

15R

15R

D D

APL431BAC_SOT23

APL431BAC_SOT23

2

3 1

EREG9

EREG9

EC109

EC109

10uF_6.3V

10uF_6.3V

DNI

DNI

ER125

ER125

250R

250R

1%

ER126

ER126

1.00K

1.00K

1%

2.5V_REF1

R1

2.0V_REF1

R2

7

6

2.5V_REF1

2.5V_REF1

ER105 1.00KER105 1.00K

ER201 1.00KER201 1.00K

+12V_BUS

3

2

ER107

ER107

100R

100R

ER207

ER207

3.32K

3.32K

5

+12V_BUS

EC110

EC110

1.0uF

1.0uF

411

U101A

U101A

+

+

ER127 0RER127 0R

1

-

-

LM324M

LM324M

ER106

ER106

100R

100R

U101B

U101B

5

+

+

ER227 0RER227 0R

7

6

-

-

LM324M

LM324M

ER2060RER206

0R

1

ER108

ER108

40.2R

40.2R

EQ105

EQ105

PMBT2222A

PMBT2222A

2 3

+3.3V

Q1

Q1

1234

N-APM2054N_SOT89

N-APM2054N_SOT89

EC126

EC126

100nF

100nF

EC123

EC123

DIP_470uF

DIP_470uF

+5V

4

EC183

EC183

DIP_470uF

DIP_470uF

+2.5V

EC125

EC125

100nF

100nF

3

C40

C40

C41

C41

C42

10uF

10uF

C42

10uF

10uF

10uF

10uF

2

1

C C

U101C

ER3001KER300

10

ER115

ER115

10K

10K

9

1K

402

U101C

+

+

8

-

-

LM324M

LM324M

R106 0RR106 0R

U101D

U101D

12

+

+

13

-

-

ER302 0RER302 0R

ER303

ER303

10K

10K

B922B922

ER128 0RER128 0R

APM3055LUC-TR

APM3055LUC-TR

ER301 0RER301 0R

14

LM324M

LM324M

+VDD1DI +VDD2DI +PVDD +TPVDD +TXVDDR +T2PVDD +T2XVDDR

B923B923

B925B925

B924B924

2.0V_REF1

ER113 1KER113 1K

402

2.0V_REF1

B B

ER298

ER298

665R

665R

1%

ER299

ER299

1.00K

1.00K

1%

R1

1.2V_REF1

R2

+2.5V +AVDD +A2VDD

+3.3V

***

EC306

EC306

470uF_10V

470uF_10V

***

DS

EQ34

EQ34

G

DS

EQ35

EQ35

G

B926B926

+MVDDQ

EC315

EC315

10u_10V

10u_10V

+3.3V

D703

D703

DIODE_SMC

DIODE_SMC

EC339

EC339

10uf

10uf

APM3023NUC-TRL,TO252

APM3023NUC-TRL,TO252

B928B928B927B927

EC305

EC305

470uF_10V

470uF_10V

+PCIE

B929B929

EC805

EC805

DIP_820uF

DIP_820uF

B930B930

C339

C339

10uf

10uf

C340

C340

10uf

10uf

+VDDC_CT

U84B

U84B

5

+

+12V_BUS

EC100

EC100

100nF

100nF

U84A

2.5V_REF1

ER102 1.00KER102 1.00K

ER1041KER104

1K

B931B931

3

2

+

+

-

-

4 8

U84A

ER100 120RER100 120R

1

LM358MX_SOIC8

LM358MX_SOIC8

ER103 100RER103 100R

+3.3V

ER101

ER101

0 R

0 R

EQ104

EQ104

1

PMBT2222A

PMBT2222A

2 3

+

6

-

-

4 8

EC102

EC102

DIP_470uF

DIP_470uF

7

LM358MX_SOIC8

LM358MX_SOIC8

+VDDC_CT

EC103

EC103

100nF

100nF

A A

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

MS-V050 RV515 TSOP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

105-A67700-00A

105-A67700-00A

105-A67700-00A

1

1

1

of

of

of

10 19Tuesday, December 27, 2005

10 19Tuesday, December 27, 2005

10 19Tuesday, December 27, 2005

1

www.vinafix.vn

Page 11

8

7

6

5

4

3

2

1

CHANNEL A: RANK 0 128/256MB DDR1

M_DQMA#[7..0][5]

D D

M_MDA[63..0][5]

M_MAA[12..0][5]

C C

M_MAA[15..14][5]

B B

M_DQMA#0

M_DQMA#1

M_DQMA#2

M_DQMA#3

M_DQMA#4

M_DQMA#5

M_DQMA#6

M_DQMA#7

VREF_U201 VREF_U202 VREF_U203 VREF_U204

49

M_MAA0

29

M_MAA1

30

M_MAA2

31

M_MAA3

32

M_MAA4

35

M_MAA5

36

M_MAA6

37

M_MAA7

38

M_MAA8

39

M_MAA9

40

M_MAA10

28

M_MAA11

41

M_QSA2

M_QSA3

M_DQMA#2

M_DQMA#3

M_MAA14

M_MAA15

45

46

44

24

23

22

21

16

51

20

47

26

27

+MVDDQ

CLKA0[5]

CLKA#0[5]

CKEA0[5]

CSA#0_0[5]

RASA#0[5]

CASA#0[5]

WEA#0[5]

U201

U201

VREF

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

CK

CK

CKE

CS

RAS

CAS

WE

LDQS

UDQS

LDM

UDM

BA0

BA1

1MX16X4

1MX16X4

R201

R201

4.99K

4.99K

R202

R202

4.99K

4.99K

M_QSA[7..0][5]

NC#17

NC#19

NC#25

NC#42

NC#43

NC#50

NC#53

VDD#18

VDD#33

VDDQ#9

VDDQ#15

VDDQ#55

VDDQ#61

VSS#48

VSS#66

VSSQ#6

VSSQ#12

VSSQ#58

VSSQ#64

VREF_U201

C413

C413

100nF

100nF

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

VDDQ

VSSQ

M_QSA0

M_QSA1

M_QSA2

M_QSA3

M_QSA4

M_QSA5

M_QSA6

M_QSA7

U204

U203

U202

M_MAA0

M_MAA1

M_MAA2

M_MAA3

M_MAA4

M_MAA5

M_MAA6

M_MAA7

M_MAA8

M_MAA9

M_MAA10

M_MAA11

+MVDDQ

49

29

30

31

32

35

36

37

38

39

40

28

41

45

46

44

24

23

22

21

16

51

20

47

26

27

R203

R203

4.99K

4.99K

R204

R204

4.99K

4.99K

U202