Page 1

8

7

6

5

4

3

2

1

+12V_BUS

C1

CAP CER 10UF 20% 16V X5R

10UFC110UF

(1206)1.8MM H MAX

+12V_BUS

+12V_BUS

C3

C3

D D

C C

B B

C2

150nF_16VC2150nF_16V

+3.3V_BUS

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

C4

10uFC410uF

+3.3V_BUS

+3.3V_BUS

C5

1uF_6.3VC51uF_6.3V

Place these caps last,

ideally as close to the bus

connector as possible

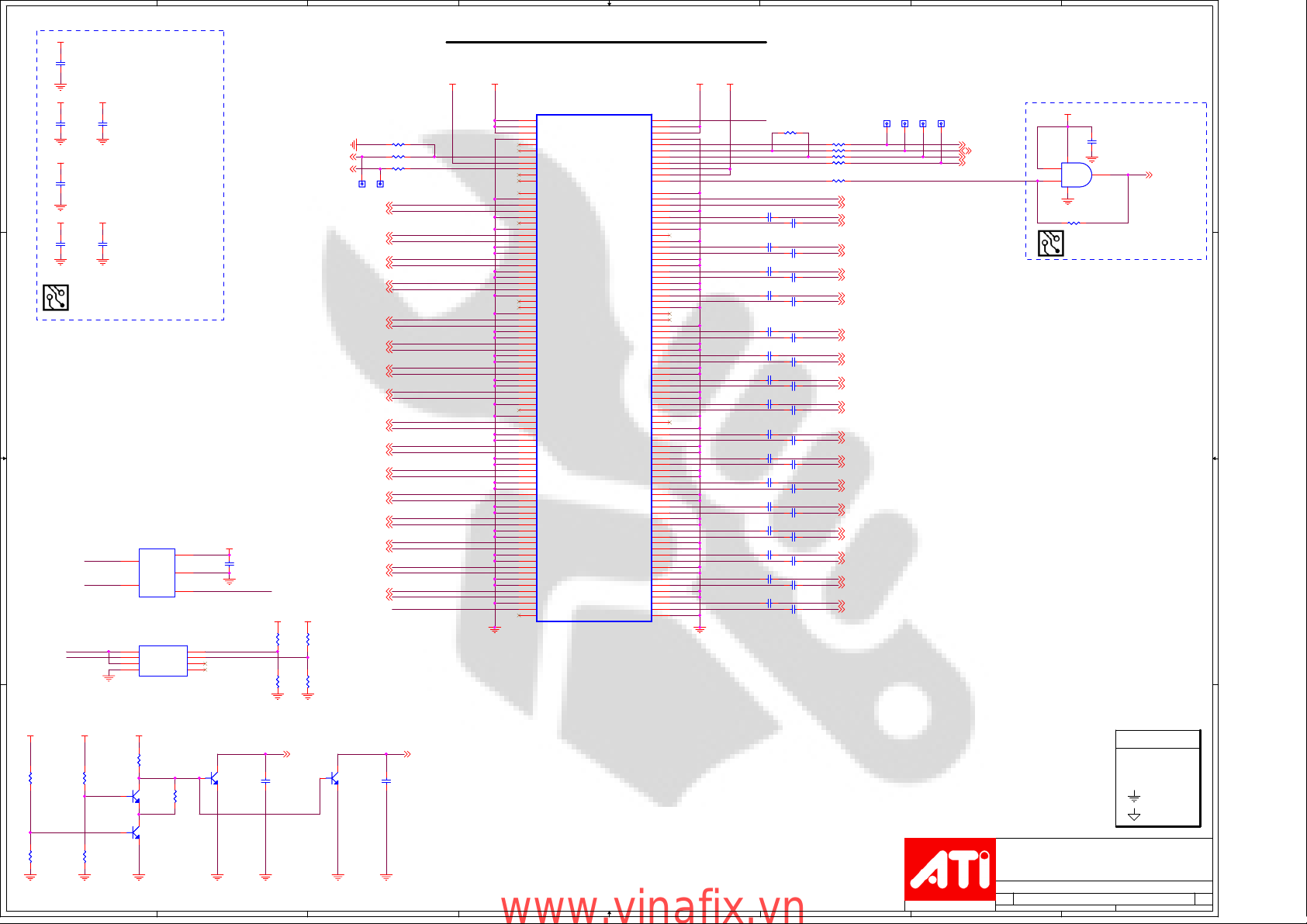

POWER SEQUENCING

VMON1

VMON2

U41_VCC

U41_PGOOD

150nF_16V

150nF_16V

LF CAP CER 150NF 10% 16V X7R (0603)

LF CAP CER 150NF 10% 16V X7R (0603)

C6

C6

1uF_6.3V

1uF_6.3V

LF CAP CER 1UF 10% 6.3V X5R (0402)

LF CAP CER 1UF 10% 6.3V X5R (0402)

U41

U41

5

VMON1

4

VMON2

APL6535

APL6535

APL6535

APL6536

APL6536

1

VCC

2

PGOOD

3

ENABLE

GND4VMON4

MU41

MU41

APL6536

ISL6536

PGOOD

VCC

GND

VMON1

VMON2

VMON3

U41_VCC

1

2

U41_PGOODU41_PGOOD SMPS_EN1

3

8

7

6

5

+3.3V_BUS

VMON1

VMON2

C42

C42

1uF_6.3V

1uF_6.3V

MR41

MR41

15K

15K

402

1%

MR42

MR42

4.64K

4.64K

402

1%

DNI

R6 0RR6 0R

R5 0RR5 0R

A_HSYNC_DAC1(3,7,14)

PETp10_GFXRp10(2)

PETn10_GFXRn10(2)

PETp11_GFXRp11(2)

PETn11_GFXRn11(2)

PETp12_GFXRp12(2)

PETn12_GFXRn12(2)

PETp13_GFXRp13(2)

PETn13_GFXRn13(2)

PETp14_GFXRp14(2)

PETn14_GFXRn14(2)

PETp15_GFXRp15(2)

PETn15_GFXRn15(2)

+12V_BUS+3.3V_BUS

MR43

MR43

22.1K

22.1K

402

1%

MR44

MR44

1.5K

1.5K

402

1%

R4 0RR4 0R

TP5TP5

TP6TP6

PETn0_GFXRn0(2)

PETp1_GFXRp1(2)

PETn1_GFXRn1(2)

PETp2_GFXRp2(2)

PETn2_GFXRn2(2)

PETp3_GFXRp3(2)

PETn3_GFXRn3(2)

PETp4_GFXRp4(2)

PETn4_GFXRn4(2)

PETp5_GFXRp5(2)

PETn5_GFXRn5(2)

PETp6_GFXRp6(2)

PETn6_GFXRn6(2)

PETp7_GFXRp7(2)

PETn7_GFXRn7(2)

PETp8_GFXRp8(2)

PETn8_GFXRn8(2)

PETp9_GFXRp9(2)

PETn9_GFXRn9(2)

PRESENCE

PCI-EXPRESS EDGE CONNECTOR

+12V_BUS+3.3V_BUS +3.3V_BUS+12V_BUS

x16 PCIe

TESTEN_GND

JTAG_TRST#

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+12V#B1

+12V#B2

+12V#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

Mechanical Key

Mechanical Key

x16 PCIe

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

MPCIE1

MPCIE1

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

PRESENCE

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

DNI

R2 0RR2 0R

C7

100nFC7100nF

C9

100nFC9100nF

C11

C11

100nF

100nF

C13

C13

100nF

100nF

C15

C15

100nF

100nF

C17

C17

100nF

100nF

C19

C19

100nF

100nF

C21

C21

100nF

100nF

C23

C23

100nF

100nF

C25

C25

100nF

100nF

C27

C27

100nF

100nF

C29

C29

100nF

100nF

C31

C31

100nF

100nF

C33

C33

100nF

100nF

C35

C35

100nF

100nF

C37

C37

100nF

100nF

8 1

7 2

6 3

5 4

PERST#

R1 0RR1 0R

C8

C8

100nF

100nF

CAP, CER 100NF 10% 10V X5R EIA(0402)

CAP, CER 100NF 10% 10V X5R EIA(0402)

C10

C10

100nF

100nF

C12

C12

100nF

100nF

C14

C14

100nF

100nF

C16

C16

100nF

100nF

C18

C18

100nF

100nF

C20

C20

100nF

100nF

C22

C22

100nF

100nF

C24

C24

100nF

100nF

C26

C26

100nF

100nF

C28

C28

100nF

100nF

C30

C30

100nF

100nF

C32

C32

100nF

100nF

C34

C34

100nF

100nF

C36

C36

100nF

100nF

C38

C38

100nF

100nF

TP1TP1

RP1A0R RP1A0R

RP1B0R RP1B0R

RP1C0R RP1C0R

RP1D0R RP1D0R

PCIE_REFCLKP (2)

PCIE_REFCLKN (2)PETp0_GFXRp0(2)

GFXTp0_PERp0 (2)

GFXTn0_PERn0 (2)

GFXTp1_PERp1 (2)

GFXTn1_PERn1 (2)

GFXTp2_PERp2 (2)

GFXTn2_PERn2 (2)

GFXTp3_PERp3 (2)

GFXTn3_PERn3 (2)

GFXTp4_PERp4 (2)

GFXTn4_PERn4 (2)

GFXTp5_PERp5 (2)

GFXTn5_PERn5 (2)

GFXTp6_PERp6 (2)

GFXTn6_PERn6 (2)

GFXTp7_PERp7 (2)

GFXTn7_PERn7 (2)

GFXTp8_PERp8 (2)

GFXTn8_PERn8 (2)

GFXTp9_PERp9 (2)

GFXTn9_PERn9 (2)

GFXTp10_PERp10 (2)

GFXTn10_PERn10 (2)

GFXTp11_PERp11 (2)

GFXTn11_PERn11 (2)

GFXTp12_PERp12 (2)

GFXTn12_PERn12 (2)

GFXTp13_PERp13 (2)

GFXTn13_PERn13 (2)

GFXTp14_PERp14 (2)

GFXTn14_PERn14 (2)

GFXTp15_PERp15 (2)

GFXTn15_PERn15 (2)

TP3TP3

TP2TP2

TP4TP4

A_VSYNC_DAC1 (3,7,14)

CRT1DDCDATA (3,14)

CRT3DDCCLK (3,17)TESTEN(3)

CRT1DDCCLK (3,14)

+3.3V

CAP, CERAMIC 100NF 10% 10V X5R EIA(0402)

CAP, CERAMIC 100NF 10% 10V X5R EIA(0402)

C39

C39

100nF

100nF

53

1

4

2

U5

TC7SZ08FUU5TC7SZ08FU

R_RST

R3 0RR3 0R

Place R_RST in U_RST

PERST#_buf (2,16)

+12V_BUS+3.3V_BUS +12V_BUS

SMPS_EN1 SMPS_EN2

R45

R45

4.7K

4.7K

402

Node 1

R41

R41

475R

475R

402

1%

A A

R42

R42

200R

200R

402

1%

R43

R43

1.62K

1.62K

402

1%

VMON2

Node 3

VMON1

Node 2

R44

R44

200R

200R

402

1%

8

5%

Q41

Q41

1

MMBT3904

MMBT3904

2 3

Q42

Q42

1

MMBT3904

MMBT3904

2 3

R460RR46

0R

402

DNI

Q43

Q43

1

MMBT3904

MMBT3904

2 3

5mA

7

SMPS_EN1 (8) SMPS_EN2 (9)

Q44

Q44

1

MMBT3904

C43

C43

100nF

100nF

MMBT3904

2 3

C44

C44

100nF

100nF

6

Power Sequence Circuit to ensure SMPS_EN is released after

+12V_BUS and +3.3V_BUS are both in regulation.

Pull-up may or may not be required on SMPS_EN signal depending

on SMPS design.

Node 1 When +12V ramps above min Vbe, SMPS_EN will be helt low

When +3.3V gets close to regulation, one of the two

Node 2

conditions of releasing SMPS_EN is active

Target ~ 900mV when +3.3 at min regulation (worse case)

Typical trigger when +3.3V ramps above 2.2V (650mV)

Node 3 When +12V gets close to regulation, one of the two

conditions of releasing SMPS_EN is active

Target ~ 1.25V when +12 at min regulation (worse case)

Typical trigger when +12V ramps above 10V (1.1V)

5

www.vinafix.vn

4

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

RV530/RV515 512MB DDR2 VGA 2xDVI VIVO FH

RV530/RV515 512MB DDR2 VGA 2xDVI VIVO FH

RV530/RV515 512MB DDR2 VGA 2xDVI VIVO FH

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

3

Date: Sheet

2

105-A676xx-00C

105-A676xx-00C

105-A676xx-00C

SYMBOL LEGEND

DNI

DO NOT

INSTALL

#

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

120Saturday, August 06, 2005

120Saturday, August 06, 2005

120Saturday, August 06, 2005

1

2

2

2

of

of

of

Loading...

Loading...