Page 1

8

7

6

5

4

3

2

1

+12V_BUS

C1

CAP CER 10UF 20% 16V X5R

10UF

(1206)1.8MM H MAX

+12V_BUS

+12V_BUS

C2

D D

+3.3V_BUS

+3.3V_BUS

C C

B B

C3

150nF_16V

150nF_16V

LF CAP CER 150NF 10% 16V X7R (0603)

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

C4

10uF

+3.3V_BUS

C6

C5

1uF_6.3V

1uF_6.3V

LF CAP CER 1U F 10% 6.3V X5R (0402)

Place these caps last,

ideally as close to the bu s

connector as possibl e

DNI

R6 0R

R5 0R

A_HSYNC_DAC1(3,7,14)

PETp10_GFXRp10(2)

PETn10_GFXRn10(2)

PETp11_GFXRp11(2)

PETn11_GFXRn11(2)

PETp12_GFXRp12(2)

PETn12_GFXRn12(2)

PETp13_GFXRp13(2)

PETn13_GFXRn13(2)

PETp14_GFXRp14(2)

PETn14_GFXRn14(2)

PETp15_GFXRp15(2)

PETn15_GFXRn15(2)

R4 0R

TP6

TP5

PETn0_GFXRn0(2)

PETp1_GFXRp1(2)

PETn1_GFXRn1(2)

PETp2_GFXRp2(2)

PETn2_GFXRn2(2)

PETp3_GFXRp3(2)

PETn3_GFXRn3(2)

PETp4_GFXRp4(2)

PETn4_GFXRn4(2)

PETp5_GFXRp5(2)

PETn5_GFXRn5(2)

PETp6_GFXRp6(2)

PETn6_GFXRn6(2)

PETp7_GFXRp7(2)

PETn7_GFXRn7(2)

PETp8_GFXRp8(2)

PETn8_GFXRn8(2)

PETp9_GFXRp9(2)

PETn9_GFXRn9(2)

PRESENCE

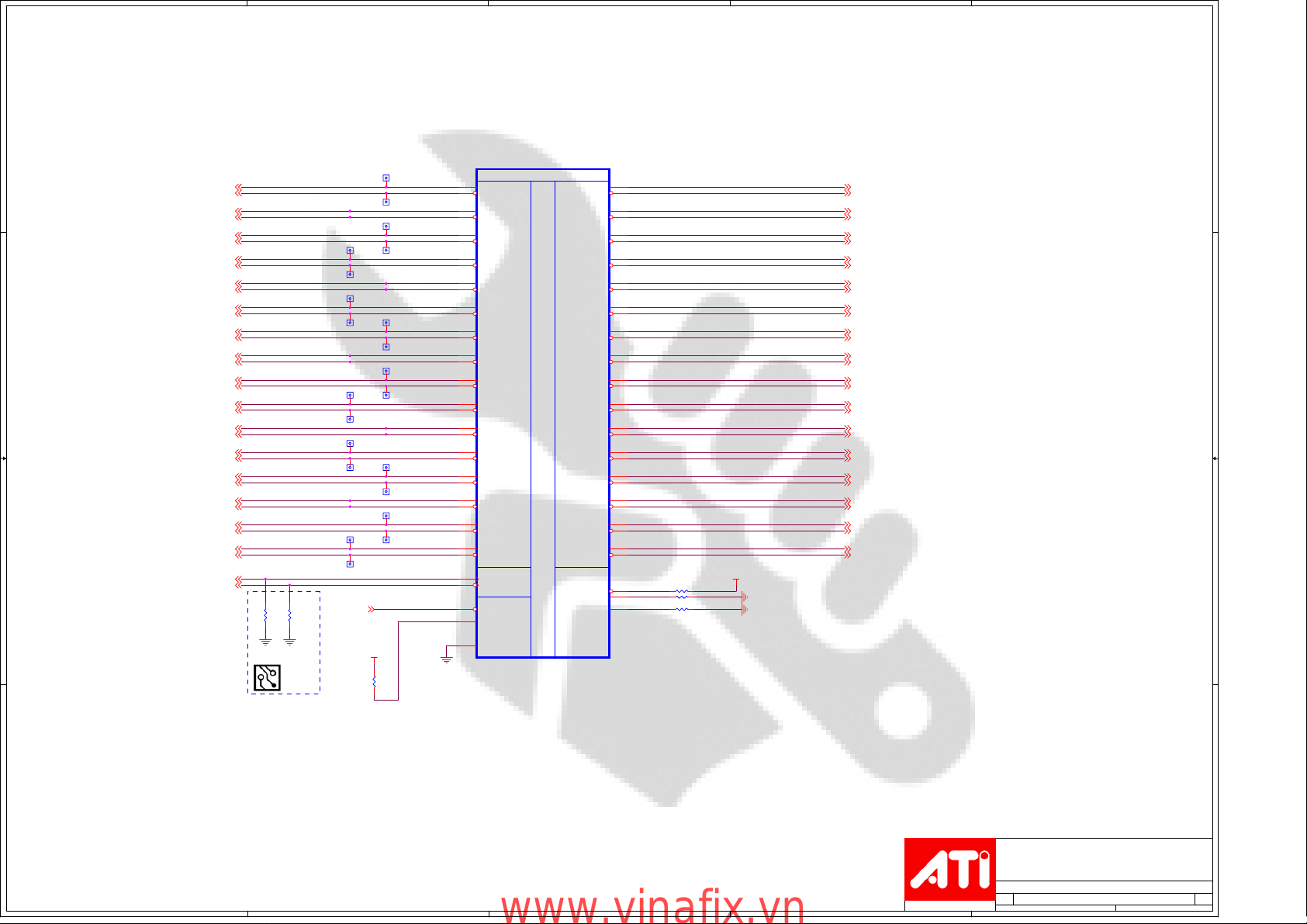

PCI-EXPRESS EDGE CONNECTOR

+12V_BUS+3.3V_BUS +3.3V_BUS+12V_BUS

TESTEN_GND

JTAG_TRST#

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+12V#B1

+12V#B2

+12V#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

Mechanical Key

x16 PCIe

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

MPCIE1

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

PRESENCE

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

R2 0R

C7

100nF

C9

100nF

C11

100nF

C13

100nF

C15

100nF

C17

100nF

C19

100nF

C21

100nF

C23

100nF

C25

100nF

C27

100nF

C29

100nF

C31

100nF

C33

100nF

C35

100nF

C37

100nF

DNI

PERST#

C8

100nF

C10

100nF

C12

100nF

C14

100nF

C16

100nF

C18

100nF

C20

100nF

C22

100nF

C24

100nF

C26

100nF

C28

100nF

C30

100nF

C32

100nF

C34

100nF

C36

100nF

C38

100nF

8 1

7 2

6 3

5 4

R1 0R

TP1

RP1AEXB28VR000X

RP1BEXB28VR000X

RP1CEXB28VR000X

RP1DEXB28VR000X

PCIE_REFCLKP (2)

PCIE_REFCLKN (2)PETp0_GFXRp0(2)

GFXTp0_PERp0 (2)

GFXTn0_PERn0 (2)

GFXTp1_PERp1 (2)

GFXTn1_PERn1 (2)

GFXTp2_PERp2 (2)

GFXTn2_PERn2 (2)

GFXTp3_PERp3 (2)

GFXTn3_PERn3 (2)

GFXTp4_PERp4 (2)

GFXTn4_PERn4 (2)

GFXTp5_PERp5 (2)

GFXTn5_PERn5 (2)

GFXTp6_PERp6 (2)

GFXTn6_PERn6 (2)

GFXTp7_PERp7 (2)

GFXTn7_PERn7 (2)

GFXTp8_PERp8 (2)

GFXTn8_PERn8 (2)

GFXTp9_PERp9 (2)

GFXTn9_PERn9 (2)

GFXTp10_PERp10 (2)

GFXTn10_PERn10 (2)

GFXTp11_PERp11 (2)

GFXTn11_PERn11 (2)

GFXTp12_PERp12 (2)

GFXTn12_PERn12 (2)

GFXTp13_PERp13 (2)

GFXTn13_PERn13 (2)

GFXTp14_PERp14 (2)

GFXTn14_PERn14 (2)

GFXTp15_PERp15 (2)

GFXTn15_PERn15 (2)

TP4

TP3

TP2

A_VSYNC_DAC1 (3,7,14)

CRT1DDCDATA (3,14)

CRT3DDCCLK (3,13,17)TESTEN(3)

CRT1DDCCLK (3,14)

+3.3V

CAP, CERAMIC 100NF 10% 10V X5R EIA (0402)

C39

100nF

53

1

4

2

U5

NC7SZ08P5X_NL

R_RST

R3 0R

Place R_RST in U_RST

PERST#_buf (2, 13,16)

POWER SEQ UENCING

+12V_BUS+3.3V_BUS +12V_BUS

SMPS_EN1 SMPS_EN2

R45

4.7K

402

Node 1

R41

475R

402

1%

A A

R42

200R

402

1%

R43

1.62K

402

1%

VMON2

Node 3

VMON1

Node 2

R44

200R

402

1%

8

5%

Q41

1

MMBT3904

2 3

Q42

1

MMBT3904

2 3

Q43

1

MMBT3904

2 3

R46

0R

402

DNI

5mA

7

SMPS_EN1 (8) SMPS_EN2 (9)

Q44

1

C43

100nF

MMBT3904

2 3

C44

100nF

6

Power Sequence Circuit to ensure SMPS_EN is released after

+12V_BUS and +3.3V_BUS are both in regulation.

Pull-up may or may not be required on SMPS_EN signal depending

on SMPS design.

Node 1 When +12V ramps above min Vbe, SMPS_EN will be helt low

When +3.3V gets close to regulation, one of the two

Node 2

conditions of releasing SMPS_EN is active

Target ~ 900mV when +3.3 at min regulation (worse case)

Typical trigger when +3.3V ramps above 2.2V (650mV)

Node 3 When +12V gets close to regulation, one of the two

conditions of releasing SMPS_EN is active

Target ~ 1.25V when +12 at min regulation (worse case)

Typical trigger when +12V ramps above 10V (1.1V)

5

www.vinafix.vn

4

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RV530/RV515 256MB DDR3-136 Dual 2xDVI VIVO FH

Size Docum e n t N u mb er Re v

C

3

Date: Sheet

2

105-A671xx-00

SYMBOL LEGEND

DNI

DO NOT

INSTALL

#

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

120Saturday, O ctober 08, 2005

1

2

of

Page 2

5

D D

4

3

2

1

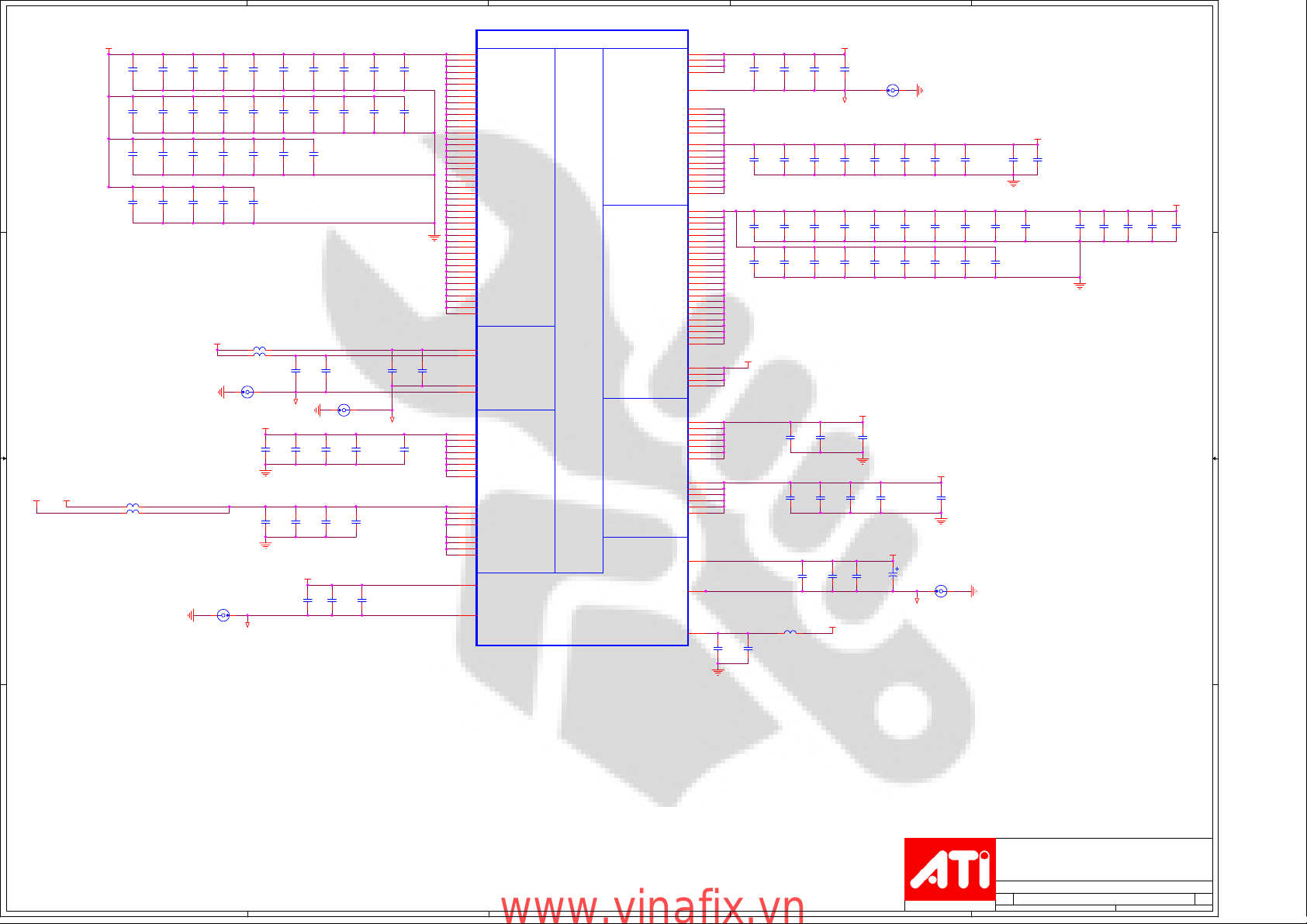

NOTE: some of the PCIE testpoints will

be available trought via on traces.

PETp0_GFXRp0(1)

PETn0_GFXRn0(1)

PETp1_GFXRp1(1)

PETn1_GFXRn1(1)

PETp2_GFXRp2(1)

PETn2_GFXRn2(1)

PETp3_GFXRp3(1)

PETn3_GFXRn3(1)

PETp4_GFXRp4(1)

PETn4_GFXRn4(1)

PETp5_GFXRp5(1)

PETn5_GFXRn5(1)

PETp6_GFXRp6(1)

C C

B B

PETn6_GFXRn6(1)

PETp7_GFXRp7(1)

PETn7_GFXRn7(1)

PETp8_GFXRp8(1)

PETp9_GFXRp9(1)

PETn9_GFXRn9(1)

PETp10_GFXRp10(1)

PETn10_GFXRn10(1)

PETp11_GFXRp11(1)

PETn11_GFXRn11(1)

PETp12_GFXRp12(1)

PETn12_GFXRn12(1)

PETp13_GFXRp13(1)

PETn13_GFXRn13(1)

PETp14_GFXRp14(1)

PETn14_GFXRn14(1)

PETp15_GFXRp15(1)

PETn15_GFXRn15(1)

PCIE_REFCLKP(1)

PCIE_REFCLKN(1)

DNI DNI

R13

51R

402 402

PERST#_buf(1,13,16)

R14

51R

For Tektronix LA only

Place close

to ASIC

TP11

TP12

TP13

TP14

TP19

TP20

TP21

TP27

TP28

R11

4.7K

402

TP7

TP8

TP9

TP10

TP15

TP16

TP17

TP18

TP23TP22

TP24

TP25

TP26

+3.3V

DNI

U1A

AJ31

PCIE_RX0P

AH31

PCIE_RX0N

AH30

PCIE_RX1P

AG30

PCIE_RX1N

AG32

PCIE_RX2P

AF32

PCIE_RX2N

AF31

PCIE_RX3P

AE31

PCIE_RX3N

AE30

PCIE_RX4P

AD30

PCIE_RX4N

AD32

PCIE_RX5P

AC32

PCIE_RX5N

AC31

PCIE_RX6P

AB31

PCIE_RX6N

AB30

PCIE_RX7P

AA30

PCIE_RX7N

AA32

PCIE_RX8P

Y32

PCIE_RX8N

Y31

PCIE_RX9P

W31

PCIE_RX9N

W30

PCIE_RX10P

V30

PCIE_RX10N

V32

PCIE_RX11P

U32

PCIE_RX11N

U31

PCIE_RX12P

T31

PCIE_RX12N

T30

PCIE_RX13P

R30

PCIE_RX13N

R32

PCIE_RX14P

P32

PCIE_RX14N

P31

PCIE_RX15P

N31

PCIE_RX15N

AL28

PCIE_REFCLKP

AK28

PCIE_REFCLKN

AG24

PERSTB

AA24

PCIE_TEST

AF24

NC

RV530 Unfused LF A11

Clock

PART 1 OF 7

P

C

I

E

X

P

R

E

S

S

I

N

T

E

R

F

A

C

E

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Calibration

PCIE_CALRN

PCIE_CALRP

PCIE_CALI

AK27

AJ27

AJ25

AH25

AH28

AG28

AG27

AF27

AF25

AE25

AE28

AD28

AD27

AC27

AC25

AB25

AB28

AA28

AA27

Y27

Y25

W25

W28

V28

V27

U27

U25

T25

T28

R28

R27

P27

AE24

AD24

AB24

GFXTp0_PERp0 (1)

GFXTn0_PERn0 (1)

GFXTp1_PERp1 (1)

GFXTn1_PERn1 (1)

GFXTp2_PERp2 (1)

GFXTn2_PERn2 (1)

GFXTp3_PERp3 (1)

GFXTn3_PERn3 (1)

GFXTp4_PERp4 (1)

GFXTn4_PERn4 (1)

GFXTp5_PERp5 (1)

GFXTn5_PERn5 (1)

GFXTp6_PERp6 (1)

GFXTn6_PERn6 (1)

GFXTp7_PERp7 (1)

GFXTn7_PERn7 (1)

GFXTp8_PERp8 (1)

GFXTn8_PERn8 (1)PETn8_GFXRn8(1)

GFXTp9_PERp9 (1)

GFXTn9_PERn9 (1)

GFXTp10_PERp10 (1)

GFXTn10_PERn10 (1)

GFXTp11_PERp11 (1)

GFXTn11_PERn11 (1)

GFXTp12_PERp12 (1)

GFXTn12_PERn12 (1)

GFXTp13_PERp13 (1)

GFXTn13_PERn13 (1)

GFXTp14_PERp14 (1)

GFXTn14_PERn14 (1)

GFXTp15_PERp15 (1)

GFXTn15_PERn15 (1)

+PCIE

402

R82.0K

402

R9562R

402

R101.47K

A A

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RV530/RV515 256MB DDR3-136 Dual 2xDVI VIVO FH

Size Docum e n t N u mb er Re v

C

5

4

www.vinafix.vn

3

2

Date: Sheet

105-A671xx-00

1

2

of

220Saturday, O ctober 08, 2005

Page 3

5

4

3

2

1

D D

C C

I2C DEVICE ADDRESS' ON DDC3

DEVICE

LM63

B B

Place close to ASIC

T2XCM(13)

T2XCP(13)

T2X0M(13)

T2X0P(13)

T2X1M(13)

T2X1P(13)

T2X2M(13)

T2X2P(13)

T2X3M(15)

T2X3P(15)

T2X4M(15)

T2X4P(15)

T2X5M(15)

T2X5P(15)

LF RESIST OR 324R 1% 1/ 16W EIA (0402)

+T2XVDDR

C225

NS19NS_VIA

10uF

1 2

GND_T2XVSSR

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

ADDRESS

x100 1100

CRT3DDCDATA(13,17)

CRT3DDCCLK(1,13,17)

TESTEN(1)

402

R101 324R

R102 324R

R103 324R

R104 324R

R105 324R

R106 324R

R107 324R

NS15NS_VIA

1 2

C224

1uF_6.3V

+3.3V

+T2PVDD

1uF_6.3V

R33

4.7K

402 402

+3.3V

+3.3V

C227

1uF_6.3V

GND_T2PVSS

C223

C222

1uF_6.3V

CRT1DDCDATA(1,14)

R34

CRT2DDCDATA(15)

4.7K

MR24 10K

R24 10K

Overlap Footprints

R25 499R

R26 499R

CRT1DDCCLK(1,14)

CRT2DDCCLK(15)

C226

1uF_6.3V

C221

1uF_6.3V

GPU_DPLUS(17)

GPU_DMINUS(17)

HPD1(14)

T2XCM

T2XCP

T2X0M

T2X0P

T2X1M

T2X1P

T2X2M

T2X2P

T2X3M

T2X3P

T2X4M

T2X4P

T2X5M

T2X5P

TP30

TESTEN

VREFG

XTALIN

XTALOUT

U1B

AL18

T2XCM

AM18

T2XCP

AK19

T2X0M

AL19

T2X0P

AL20

T2X1M

AM20

T2X1P

AL21

T2X2M

AM21

T2X2P

AK18

T2X3M

AJ18

T2X3P

AH18

T2X4M

AG18

T2X4P

AJ20

T2X5M

AK20

T2X5P

AE19

T2PVDD

AE18

T2PVSS

AF20

T2XVDDR_1

AE20

T2XVDDR_2

AF19

T2XVDDR_3

AC21

T2XVDDR_4

AC22

T2XVDDR_5

AD22

T2XVDDR_6

AE21

T2XVDDR_7

AD21

T2XVDDR_8

AE22

T2XVDDR_9

AF22

T2XVSSR_1

AF17

T2XVSSR_2

AF21

T2XVSSR_3

AK17

T2XVSSR_4

AJ19

T2XVSSR_5

AF18

T2XVSSR_6

AH17

T2XVSSR_7

AG17

T2XVSSR_8

AG19

T2XVSSR_9

AH19

T2XVSSR_10

AH22

DDC1DATA

AH23

DDC1CLK

AH13

DDC2DATA

AG13

DDC2CLK

AE12

DDC3DATA

AF12

DDC3CLK

AF11

HPD1

AE13

SDA

AF13

SCL

AG12

DPLUS

AH12

DMINUS

AG14

PLLTEST

AG22

TESTEN

AC8

VREFG

AL26

XTALIN

AM26

XTALOUT

RV530 Unfused LF A11

Integrated

TMDS2

Monitor

Interfa ce

MMI2C

Thermal

Diode

Test

XTAL

PART 2 OF 7

V

I

D

E

O

&

M

U

L

T

I

M

E

D

I

A

Integrated

TMDS

TXVDDR_1

TXVDDR_2

TXVDDR_3

TXVDDR_4

TXVSSR_1

TXVSSR_2

TXVSSR_3

TXVSSR_4

TXVSSR_5

DAC / CRT

DAC2 (TV/CRT2)

A2VSSN_1

A2VSSN_2

NC_A2VDDQ

TXCM

TXCP

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TX3M

TX3P

TX4M

TX4P

TX5M

TX5P

TPVDD

TPVSS

HSYNC

VSYNC

RSET

AVDD_1

AVDD_2

AVSSQ

AVSSN_1

AVSSN_2

VDD1DI

VSS1DI

H2SYNC

V2SYNC

COMP

R2SET

A2VDD_1

A2VDD_2

A2VSSQ

VDD2DI

VSS2DI

AL9

AM9

AK10

AL10

AL11

AM11

AL12

AM12

AK9

AJ9

AK11

AJ11

AK12

AJ12

AM8

AL8

AJ6

AK6

AL6

AM6

AJ7

AK7

AL7

AM7

AK8

AK24

R

AM24

G

AL24

B

AJ23

AJ22

RSET

AL22

+AVDD

AL25

AM25

GND_AVSSQ

AK23

AK25

AJ24

+VDD1DI

AM23

AL23

AK15

R2

AM15

G2

AL15

B2

AF15

AG15

AJ15

Y

AJ13

C

AH15

R2SET GND_A2VSSQ

AK14

+A2VDD

AM16

AL16

C56

AM17

10nF

AL17

AK13

+VDD2DI

AJ16

C59

AJ17

10nF

AL14

C246

C247

1uF_6.3V

1uF_6.3V

+TXVDDR

C250

C249

1uF_6.3V

1uF_6.3V

A_R_DAC1 (14)

A_G_DAC1 (14)

A_B_DAC1 (14)

A_HSYNC_DAC1 (1,7,14)

A_VSYNC_DAC1 (1,7,14)

R31 499R

R32 715R

GND_AVSSQ

RESISTOR, 499R 1% 1/16W E IA(0402)

C62

C63

100nF

10nF

10V X5R

10V X7R

402 10%

402 10%

C54

C53

100nF

10nF

A_R_DAC2 (15)

A_G_DAC2 (15)

A_B_DAC2 (15)

A_HSYNC_DAC2 (7,15)

A_VSYNC_DAC2 (7,15)

DAC2_Y (16)

DAC2_C (16)

DAC2_COMP (16)

C57

C58

100nF

1uF_6.3V

C60

1uF_6.3V

+TPVDD

NS14 NS_VIA

12

GND_TPVSS

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

C251

NS13 NS_VIA

10uF

GND_TXVSSR

C64

1uF_6.3V

6.3V X5R

402 10%

C55

1uF_6.3V

12

NS5 NS_VIA

GND_AVSSQ

NS6 NS_VIA

GND_AVSSN

NS7 NS_VIA

GND_VSS1DI

NS8 NS_VIA

GND_A2VSSN

NS9 NS_VIA

GND_A2VSSQ

NS10 NS_VIA

GND_VSS2DI

Place close to ASIC

TjXCM

TjXCP

TjX0M

TjX0P

TjX1M

TjX1P

TjX2M

TjX2P

TjX3M

TjX3P

TjX4M

TjX4P

TjX5M

TjX5P

12

12

12

12

12

12

R136 324R

R132 324R

R133 324R

R134 324R

R135 324R

R131 324R

R130 324R

LF RESIST OR 324R 1% 1/ 16W EIA (0402)

TjXCM ( 14)

TjXCP (14)

TjX0M (14)

TjX0P (14)

TjX1M (14)

TjX1P (14)

TjX2M (14)

TjX2P (14)

TjX3M (14)

TjX3P (14)

TjX4M (14)

TjX4P (14)

TjX5M (14)

TjX5P (14)

XTALIN_S

MR81 82R

R81 82R

R82

51.1R

R83 0R

MR83 0R

XTALIN

C82

Y82

22pF

27_MHZ

XTALOUT

4

www.vinafix.vn

CRYSTA L 27MHZ 30P PM F UND H C49SMT

2 1

Change to 10ppm/10ppm p/n 5028270000G

C83

22pF

XTALIN_S

XTALOUT_S

3

R_RTCLK

R85 0R

MR85 0R

R84

1M

MR86 0R

R86 330R

Place R_RTCLK close to XTAL so the

main clock line has shortest stub

XTALIN

XTALOUT

RTXTALIN (16)

RTXTALOUT (16)

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RV530/RV515 256MB DDR3-136 Dual 2xDVI VIVO FH

Size Docu m en t N u m be r Re v

Custom

2

Date: Sheet

105-A671xx-00

1

2

of

320Saturday , O ctober 08, 2005

RTCLK(16)

+3.3V

A A

C81

1uF_6.3V

4

2

XTAL

Y81

VCC

GND

27.000MHz

5

OUT

E/D

XTAL_EN

3

1

Page 4

5

+MVDD

C306

1uF_6.3V

C316

1uF_6.3V

C329

1uF_6.3V

C231

1uF_6.3V

C242

1uF_6.3V

C237

1uF_6.3V

+PVDD

C69

10nF

C307

1uF_6.3V

C317

1uF_6.3V

C330

1uF_6.3V

C301

1uF_6.3V

C311

D D

C C

+1.8V +3.3V

1uF_6.3V

C321

1uF_6.3V

C341

10uF

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

B57 1 2 0R_300m A

MB57 1 20R_300mA

1uF_6.3V

C312

1uF_6.3V

C322

1uF_6.3V

C342

10uF

1uF_6.3V

C313

1uF_6.3V

C326

1uF_6.3V

C343

10uF

+MVDD

C303

C302

Possible alt ernate 5150005600G

B B

NS12 NS_VIA

1 2

GND_PVSS +PCIE

C305

C304

1uF_6.3V

1uF_6.3V

C314

C315

1uF_6.3V

1uF_6.3V

C327

C328

1uF_6.3V

1uF_6.3V

C344

C345

10uF

10uF

Possible alt ernate 5150005600G

B54 120R_300mA

B55 120R_300mA

NS16 NS_VIA

12

GND_VSSRH0

+3.3V

C241

1uF_6.3V

C236

1uF_6.3V

C308

1uF_6.3V

C318

1uF_6.3V

C232

1uF_6.3V

NS17 N S_VIA

12

GND_VSSRH1

C243

1uF_6.3V

C238

1uF_6.3V

C70

100nF

4

C309

1uF_6.3V

C319

1uF_6.3V

C233

1uF_6.3V

C244

1uF_6.3V

CAP CER 10UF 10%

6.3V X5R (0805)1.4MM

MAX THICK

C239

1uF_6.3V

C71

1uF_6.3V

C310

1uF_6.3V

C320

1uF_6.3V

C245

10uF

C234

1uF_6.3V

+PVDD

GND_PVSS

U1E

C1

VDDR1_1

J1

VDDR1_2

M1

VDDR1_3

R1

VDDR1_4

V1

VDDR1_5

AA1

VDDR1_6

A3

VDDR1_7

P9

VDDR1_8

J10

VDDR1_9

N9

VDDR1_10

P10

VDDR1_11

A9

VDDR1_12

Y10

VDDR1_13

P8

VDDR1_14

R9

VDDR1_15

Y9

VDDR1_16

J11

VDDR1_17

A21

VDDR1_18

M10

VDDR1_20

N10

VDDR1_21

Y8

VDDR1_22

J18

VDDR1_23

J19

VDDR1_24

K21

VDDR1_25

A12

VDDR1_26

H13

VDDR1_27

A15

VDDR1_28

J20

VDDR1_29

J13

VDDR1_30

K11

VDDR1_31

K19

VDDR1_32

A18

VDDR1_33

L23

VDDR1_34

K20

VDDR1_35

K24

VDDR1_36

L24

VDDR1_37

H19

VDDR1_38

A24

VDDR1_39

K13

VDDR1_40

J32

VDDR1_41

A30

VDDR1_42

C32

VDDR1_43

F32

VDDR1_45

L32

VDDR1_46

A27

VDDRH0

F1

VDDRH1

A28

VSSRH0

E1

VSSRH1

AB9

VDDR3_1

AB10

VDDR3_2

AA9

VDDR3_3

AC19

VDDR3_4

AD18

VDDR3_5

AC20

VDDR3_6

AD19

VDDR3_7

AD20

VDDR3_8

AJ5

VDDR4_1

AM5

VDDR4_2

AL5

VDDR4_3

AK5

VDDR4_4

AE2

VDDR5_1

AE3

VDDR5_2

AE4

VDDR5_3

AE5

VDDR5_4

AJ14

PVDD

AH14

PVSS

RV530 Unfused LF A11

Clock

Memory I/O

I/O

PART 5 OF 7

P

O

W

E

R

Memory

Selected PLL's

3

PCIE_PVSS

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

BBP_4

BBP_3

BBP_2

BBP_1

VDDCI_1

VDDCI_2

VDDCI_3

VDDCI_4

VDDCI_6

VDDCI_7

VDDCI_8

VDD25_1

VDD25_2

VDD25_3

VDD25_4

VDD25_5

VDD25_6

MPVDD

MPVSS

VDDPLL

V23

N23

P23

U23

W23

N29

N28

N27

N26

N25

AL31

AM31

AM30

AL32

AL30

AM28

AL29

AM29

AM27

AC11

AC12

P14

U15

W14

W15

R17

R15

V15

V16

T16

U16

T17

U17

V14

R18

T18

V18

P18

P19

R19

W19

AD11

AC14

M23

V10

K18

W10

T14

W17

P16

T23

K14

U19

AC13

AC16

AC18

L10

K22

AA10

A6

A5

AC15

+VDDC

+MPVDD

GND_MPVSS

+VDDPLL

C214

1uF_6.3V

C202

C201

1uF_6.3V

1uF_6.3V

C191

C192

1uF_6.3V

1uF_6.3V

C162

C161

1uF_6.3V

1uF_6.3V

C172

C171

1uF_6.3V

1uF_6.3V

C211

1uF_6.3V

C206

1uF_6.3V

C67

1uF_6.3V

B56

C215

1uF_6.3V

120R_300mA

Possible alt ernate 5150005600G

PCIE_PVDD_12_1

PCIE_PVDD_12_2

PCIE_PVDD_12_3

PCIE_PVDD_12_4

PCIE_VDDR_12_1

PCIE_VDDR_12_2

PCIE_VDDR_12_3

PCIE_VDDR_12_4

PCIE_VDDR_12_5

PCIE_VDDR_12_6

PCIE_VDDR_12_7

PCIE_VDDR_12_8

PCIE_VDDR_12_9

PCIE_VDDR_12_10

PCIE_VDDR_12_11

PCIE_VDDR_12_12

PCIE_VDDR_12_13

PCI-Express

PCIE_VDDR_12_14

Core

I/0

I/O Internal

100nF

C203

1uF_6.3V

C193

1uF_6.3V

C163

1uF_6.3V

C173

1uF_6.3V

C66

+PCIE

C212

1uF_6.3V

C207

1uF_6.3V

10nF

2

C204

1uF_6.3V

GND_PCIE_PVSS

C194

1uF_6.3V

C164

1uF_6.3V

C174

1uF_6.3V

+VDDC

C208

1uF_6.3V

C65

22uF_16V

NS18 NS_VIA

C195

1uF_6.3V

C165

1uF_6.3V

C175

1uF_6.3V

C213

10uF

C209

1uF_6.3V

+MPVDD

C68

12

C196

1uF_6.3V

C166

1uF_6.3V

C177

1uF_6.3V

C197

1uF_6.3V

C167

1uF_6.3V

C178

1uF_6.3V

+VDDC_CT

C210

10uF

NS11NS_VIA

GND_MPVSS

1

+PCIE

C198

1uF_6.3V

C168

1uF_6.3V

C179

1uF_6.3V

12

C200

C199

10uF

10uF

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

C169

C170

1uF_6.3V

1uF_6.3V

C180

1uF_6.3V

C181

10uF

C183

C182

10uF

10uF

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

C184

10uF

+VDDC

C185

10uF

A A

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RV530/RV515 256MB DDR3-136 Dual 2xDVI VIVO FH

Size Docum e n t N u mb er Re v

C

5

4

www.vinafix.vn

3

2

Date: Sheet

105-A671xx-00

1

2

of

420Saturday, O ctober 08, 2005

Page 5

5

4

3

2

1

+MVDD

+MVDD

R161

100R

R162

100R

R163

100R

R164

100R

M_MDA[63..0](12)

MVREFD_0

C351

100nF

MVREFS_0

C353

100nF

M_MDA0

M_MDA1

M_MDA2

M_MDA3

M_MDA4

M_MDA5

M_MDA6

M_MDA7

M_MDA8

M_MDA9

M_MDA10

M_MDA11

M_MDA12

M_MDA13

M_MDA14

M_MDA15

M_MDA16

M_MDA17

M_MDA18

M_MDA19

M_MDA20

M_MDA21

M_MDA22

M_MDA23

M_MDA24

M_MDA25

M_MDA26

M_MDA27

M_MDA28

M_MDA29

M_MDA30

M_MDA31

M_MDA32

M_MDA33

M_MDA34

M_MDA35

M_MDA36

M_MDA37

M_MDA38

M_MDA39

M_MDA40

M_MDA41

M_MDA42

M_MDA43

M_MDA44

M_MDA45

M_MDA46

M_MDA47

M_MDA48

M_MDA49

M_MDA50

M_MDA51

M_MDA52

M_MDA53

M_MDA54

M_MDA55

M_MDA56

M_MDA57

M_MDA58

M_MDA59

M_MDA60

M_MDA61

M_MDA62

M_MDA63

C352

10nF

C354

10nF

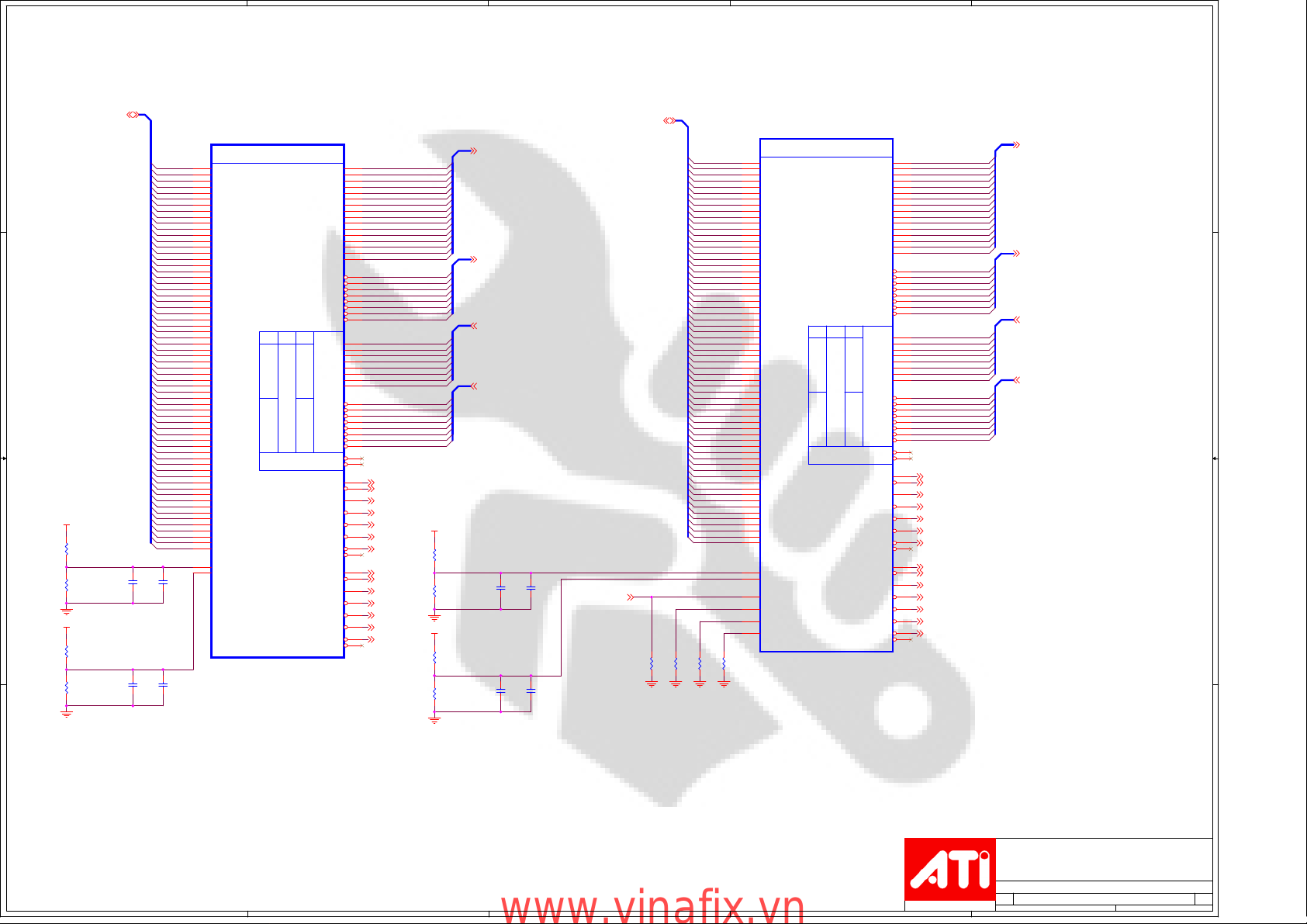

U1C

M31

DQA_0

M30

DQA_1

L31

DQA_2

L30

DQA_3

H30

DQA_4

G31

DQA_5

G30

DQA_6

F31

DQA_7

M27

DQA_8

M29

DQA_9

L28

DQA_10

L27

DQA_11

J27

DQA_12

H29

DQA_13

G29

DQA_14

G27

DQA_15

M26

DQA_16

L26

DQA_17

M25

DQA_18

L25

DQA_19

J25

DQA_20

G28

DQA_21

H27

DQA_22

H26

DQA_23

F26

DQA_24

G26

DQA_25

H25

DQA_26

H24

DQA_27

H23

DQA_28

H22

DQA_29

J23

DQA_30

J22

DQA_31

E23

DQA_32

D22

DQA_33

D23

DQA_34

E22

DQA_35

E20

DQA_36

F20

DQA_37

D19

DQA_38

D18

DQA_39

B19

DQA_40

B18

DQA_41

C17

DQA_42

B17

DQA_43

C14

DQA_44

B14

DQA_45

C13

DQA_46

B13

DQA_47

D17

DQA_48

E18

DQA_49

E17

DQA_50

F17

DQA_51

E15

DQA_52

E14

DQA_53

F14

DQA_54

D13

DQA_55

H18

DQA_56

H17

DQA_57

G18

DQA_58

G17

DQA_59

G15

DQA_60

G14

DQA_61

H14

DQA_62

J14

DQA_63

C31

MVREFD_0

C30

MVREFS_0

RV530 Unfused LF A11

Part 3 of 7

MEMORY INTERFACE A

DDR1 DDR2 DDR3

bidir. differential strobe

Not usedbidir. strobe

For DDR2

write stroberead strobe

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13

MAA_14

MAA_15

DQMAb_0

DQMAb_1

DQMAb_2

DQMAb_3

DQMAb_4

DQMAb_5

DQMAb_6

DQMAb_7

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

QSA_0B

QSA_1B

QSA_2B

QSA_3B

QSA_4B

QSA_5B

QSA_6B

QSA_7B

ODTA0

ODTA1

CLKA0

CLKA0b

CKEA0

RASA0b

CASA0b

WEA0b

CSA0b_0

CSA0b_1

CLKA1

CLKA1b

CKEA1

RASA1b

CASA1b

WEA1b

CSA1b_0

CSA1b_1

M_MAA0

D26

M_MAA1

F28

M_MAA2

D28

M_MAA3

D25

M_MAA4

E24

M_MAA5

E26

M_MAA6

D27

M_MAA7

F25

M_MAA8

C26

M_MAA9

B26

M_MAA10

D29

M_MAA11

B27

M_MAA12

E27

M_MAA13

E29

M_MAA14

B25

M_MAA15

C25

M_DQMA#0

H31

M_DQMA#1

J29

M_DQMA#2

J26

M_DQMA#3

G23

M_DQMA#4

E21

M_DQMA#5

B15

M_DQMA#6

D14

M_DQMA#7

J17

M_QSA0

J31

M_QSA1

K29

M_QSA2

K25

M_QSA3

F23

M_QSA4

D20

M_QSA5

B16

M_QSA6

D16

M_QSA7

H15

M_QSA#0

K31

M_QSA#1

K28

M_QSA#2

K26

M_QSA#3

G24

M_QSA#4

D21

M_QSA#5

C16

M_QSA#6

D15

M_QSA#7

J15

F29

D24

D31

CLKA0 (12)

E31

CLKA#0 (12)

B30

CKEA0 (12)

B28

RASA#0 (12)

C29

CASA#0 (12)

B31

WEA#0 (12)

B29

CSA#0_0 (12)

C28

B20

CLKA1 (12)

C19

CLKA#1 (12)

C22

CKEA1 (12)

B24

RASA#1 (12)

B22

CASA#1 (12)

B21

WEA#1 (12)

B23

CSA#1_0 (12)

C23

+MVDD

+MVDD

R165

100R

R166

100R

R167

100R

R168

100R

M_MAA[15..0] (12)

M_DQMA#[7..0] (12)

M_QSA[7..0] (12)

M_QSA#[7..0] (12)

MVREFD_1

C355

100nF

MVREFS_1

C357

100nF

C356

10nF

C358

10nF

D D

C C

B B

M_MDB[63..0](12)

U1D

M_MDB0

B12

M_MDB1

M_MDB2

M_MDB3

M_MDB4

M_MDB5

M_MDB6

M_MDB7

M_MDB8

M_MDB9

M_MDB10

M_MDB11

M_MDB12

M_MDB13

M_MDB14

M_MDB15

M_MDB16

M_MDB17

M_MDB18

M_MDB19

M_MDB20

M_MDB21

M_MDB22

M_MDB23

M_MDB24

M_MDB25

M_MDB26

M_MDB27

M_MDB28

M_MDB29

M_MDB30

M_MDB31

M_MDB32

M_MDB33

M_MDB34

M_MDB35

M_MDB36

M_MDB37

M_MDB38

M_MDB39

M_MDB40

M_MDB41

M_MDB42

M_MDB43

M_MDB44

M_MDB45

M_MDB46

M_MDB47

M_MDB48

M_MDB49

M_MDB50

M_MDB51

M_MDB52

M_MDB53

M_MDB54

M_MDB55

M_MDB56

M_MDB57

M_MDB58

M_MDB59

M_MDB60

M_MDB61

M_MDB62

M_MDB63

DRAM_RST(12)

R171

4.7K

R170

4.7K

R172

4.7K

RESISTOR, 4.7K 5% 1/16W E IA( 0402)

DQB_0

C12

DQB_1

B11

DQB_2

C11

DQB_3

C8

DQB_4

B7

DQB_5

C7

DQB_6

B6

DQB_7

F12

DQB_8

D12

DQB_9

E11

DQB_10

F11

DQB_11

F9

DQB_12

D8

DQB_13

D7

DQB_14

F7

DQB_15

G12

DQB_16

G11

DQB_17

H12

DQB_18

H11

DQB_19

H9

DQB_20

E7

DQB_21

F8

DQB_22

G8

DQB_23

G6

DQB_24

G7

DQB_25

H8

DQB_26

J8

DQB_27

K8

DQB_28

L8

DQB_29

K9

DQB_30

L9

DQB_31

K5

DQB_32

L4

DQB_33

K4

DQB_34

L5

DQB_35

N5

DQB_36

N6

DQB_37

P4

DQB_38

R4

DQB_39

P2

DQB_40

R2

DQB_41

T3

DQB_42

T2

DQB_43

W3

DQB_44

W2

DQB_45

Y3

DQB_46

Y2

DQB_47

T4

DQB_48

R5

DQB_49

T5

DQB_50

T6

DQB_51

V5

DQB_52

W5

DQB_53

W6

DQB_54

Y4

DQB_55

R8

DQB_56

T8

DQB_57

R7

DQB_58

T7

DQB_59

V7

DQB_60

W7

DQB_61

W8

DQB_62

W9

DQB_63

B3

MVREFD_1

C3

MVREFS_1

AA3

DRAM_RST

AA5

TEST_MCLK

AA2

TEST_YCLK

AA7

MEMTEST

RV530 Unfused LF A11

R169

243R

LF RES EIA( 0402) 243R 1% 1/ 16W

Part 4 of 7

MEMORY INTERFACE B

DDR1 DDR2 DDR3

read strobe

Not used bidir. strobe

bidir. differential strobe

write strobe

For DDR2

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_12

MAB_13

MAB_14

MAB_15

DQMBb_0

DQMBb_1

DQMBb_2

DQMBb_3

DQMBb_4

DQMBb_5

DQMBb_6

DQMBb_7

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

QSB_0B

QSB_1B

QSB_2B

QSB_3B

QSB_4B

QSB_5B

QSB_6B

QSB_7B

ODTB0

ODTB1

CLKB0

CLKB0b

CKEB0

RASB0b

CASB0b

WEB0b

CSB0b_0

CSB0b_1

CLKB1

CLKB1b

CKEB1

RASB1b

CASB1b

WEB1b

CSB1b_0

CSB1b_1

M_MAB0

G4

M_MAB1

E6

M_MAB2

E4

M_MAB3

H4

M_MAB4

J5

M_MAB5

G5

M_MAB6

F4

M_MAB7

H6

M_MAB8

G3

M_MAB9

G2

M_MAB10

D4

M_MAB11

F2

M_MAB12

F5

M_MAB13

D5

M_MAB14

H2

M_MAB15

H3

M_DQMB#0

B8

M_DQMB#1

D9

M_DQMB#2

G9

M_DQMB#3

K7

M_DQMB#4

M5

M_DQMB#5

V2

M_DQMB#6

W4

M_DQMB#7

T9

M_QSB0

B9

M_QSB1

D10

M_QSB2

H10

M_QSB3

K6

M_QSB4

N4

M_QSB5

U2

M_QSB6

U4

M_QSB7

V8

M_QSB#0

B10

M_QSB#1

E10

M_QSB#2

G10

M_QSB#3

J7

M_QSB#4

M4

M_QSB#5

U3

M_QSB#6

V4

M_QSB#7

V9

D6

J4

B4

CLKB0 (12)

B5

CLKB#0 (12)

C2

CKEB0 (12)

E2

RASB#0 (12)

D3

CASB#0 (12)

B2

WEB#0 (12)

D2

CSB#0_0 (12)

E3

N2

CLKB1 (12)

P3

CLKB#1 (12)

L3

CKEB1 (12)

J2

RASB#1 (12)

L2

CASB#1 (12)

M2

WEB#1 (12)

K2

CSB#1_0 (12)

K3

M_MAB[15..0] (12)

M_DQMB#[7..0] (12)

M_QSB[7..0] (12)

M_QSB#[7..0] (12)

A A

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RV530/RV515 256MB DDR3-136 Dual 2xDVI VIVO FH

Size Docum e n t N u mb er Re v

C

5

4

www.vinafix.vn

3

2

Date: Sheet

105-A671xx-00

1

2

of

520Saturday, O ctober 08, 2005

Page 6

5

4

3

2

1

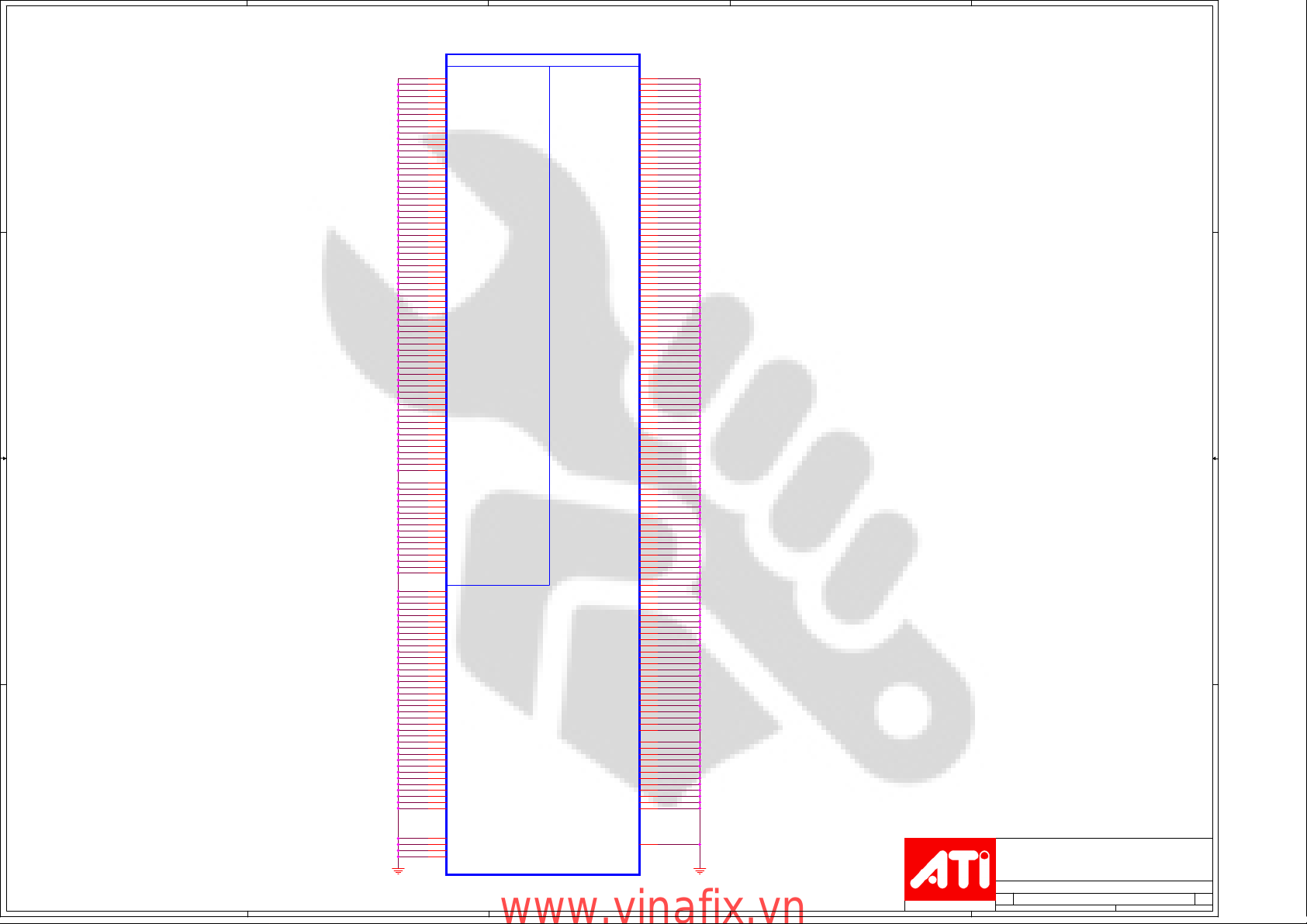

U1F

AH27

PCIE_VSS_1

AC23

PCIE_VSS_2

AL27

PCIE_VSS_3

R23

PCIE_VSS_4

P25

PCIE_VSS_5

R25

PCIE_VSS_6

T26

PCIE_VSS_7

AB26

AC26

AD25

AE26

AF26

AD26

AG25

AH26

AC28

AH29

AF28

AC29

AB27

AJ26

AJ32

AK29

AA29

AB29

AD29

AE29

AF29

AG29

AJ29

AK26

AK30

AG26

AF30

AC30

AA31

AD31

AK32

AJ28

AJ30

AK31

AA23

AG31

AB23

AC24

AH24

AA25

AA26

AE27

AD10

AF14

AG11

AG16

U26

W26

Y26

Y28

U28

P28

V29

W27

V26

P26

P29

R29

T29

U29

W29

Y29

N30

R31

V31

P30

U30

Y30

N24

P24

R24

T24

U24

V24

W24

Y24

V25

R26

T27

AD7

AE8

AL1

AM2

K10

T10

E12

AC9

AD8

F10

AA4

B1

H1

L1

P1

U1

Y1

A2

E8

H5

M8

C5

J3

L6

M6

P6

V3

R3

C6

C9

F6

H7

J6

PCIE_VSS_8

PCIE_VSS_9

PCIE_VSS_10

PCIE_VSS_11

PCIE_VSS_12

PCIE_VSS_13

PCIE_VSS_14

PCIE_VSS_15

PCIE_VSS_16

PCIE_VSS_17

PCIE_VSS_18

PCIE_VSS_19

PCIE_VSS_20

PCIE_VSS_21

PCIE_VSS_22

PCIE_VSS_23

PCIE_VSS_24

PCIE_VSS_25

PCIE_VSS_26

PCIE_VSS_27

PCIE_VSS_28

PCIE_VSS_29

PCIE_VSS_30

PCIE_VSS_31

PCIE_VSS_32

PCIE_VSS_33

PCIE_VSS_34

PCIE_VSS_35

PCIE_VSS_36

PCIE_VSS_37

PCIE_VSS_38

PCIE_VSS_39

PCIE_VSS_40

PCIE_VSS_41

PCIE_VSS_42

PCIE_VSS_43

PCIE_VSS_44

PCIE_VSS_45

PCIE_VSS_46

PCIE_VSS_47

PCIE_VSS_48

PCIE_VSS_49

PCIE_VSS_50

PCIE_VSS_51

PCIE_VSS_52

PCIE_VSS_53

PCIE_VSS_54

PCIE_VSS_55

PCIE_VSS_56

PCIE_VSS_57

PCIE_VSS_58

PCIE_VSS_59

PCIE_VSS_60

PCIE_VSS_61

PCIE_VSS_62

PCIE_VSS_63

PCIE_VSS_64

PCIE_VSS_65

PCIE_VSS_66

PCIE_VSS_69

PCIE_VSS_70

PCIE_VSS_71

PCIE_VSS_72

PCIE_VSS_73

PCIE_VSS_74

PCIE_VSS_75

PCIE_VSS_76

PCIE_VSS_77

PCIE_VSS_78

PCIE_VSS_79

PCIE_VSS_80

PCIE_VSS_81

PCIE_VSS_82

PCIE_VSS_83

PCIE_VSS_84

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

D D

C C

B B

A A

Part 6 of 7

CORE GND

AD16

VSS_45

AA6

VSS_44

P7

VSS_43

P5

VSS_42

M3

VSS_41

M9

VSS_40

L7

VSS_39

M7

VSS_38

AD17

VSS_47

AH11

VSS_48

A8

VSS_49

U7

VSS_50

C10

VSS_51

E9

VSS_52

F3

VSS_53

J9

VSS_54

N7

VSS_55

N3

VSS_56

Y5

VSS_57

AM13

VSS_58

AC10

VSS_59

Y6

VSS_60

U6

VSS_61

E5

VSS_62

AL13

VSS_63

A11

VSS_64

U8

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_163

VSS_164

VSS_165

U9

U10

R6

AD6

V6

AD14

AD13

D11

J12

K12

A13

F13

E13

F15

K16

J21

H16

T15

V17

C15

C4

U14

P15

A16

E16

G13

G16

P17

R16

R14

W16

C18

F16

W18

U18

AE16

AE17

A19

H32

F19

G19

N8

Y7

T19

V19

G21

C21

F21

AE14

AK16

U5

F22

F18

K30

C24

F24

M24

A25

D30

E25

G25

G20

G22

F27

E28

H21

C27

E32

H28

J30

K17

K27

M32

A22

C20

E19

H20

J24

M28

J28

J16

F30

L29

A31

B32

E30

AE15

AG23

AD9

AF16

AH10

AJ10

AD15

AH16

PCI-Express GND

Y23

BBN_4

K15

BBN_3

R10

BBN_2

AC17

BBN_1

RV530 Unfused LF A11

5

4

www.vinafix.vn

3

VEFUSE

K23

2

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

Title

RV530/RV515 256MB DDR3-136 Dual 2xDVI VIVO FH

Size Docum e n t N u mb er Re v

C

Date: Sheet

105-A671xx-00

1

of

620Saturday, O ctober 08, 2005

2

Page 7

5

4

3

2

1

U1G

PART 7 OF 7

VID_[7..0](16)

D D

DVPCLK_R(13)

DVP_CNT L_R_[ 2.. 0](13)

DVPDATA_R_[11..0](13)

DVPDATA

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

C C

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

ALTERNATE USE

-

-

-

-

-

-

-

-

-

-

-

-

-

STV/HDTV#_O UT_DET (INPUT)

TESTOUT(0) (OUTPUT)

TESTOUT(1) (OUTPUT)

TESTOUT(2) (OUTPUT)

TESTOUT(3) (OUTPUT)

TESTOUT(4) (OUTPUT)

TESTOUT(5) (OUTPUT)

TESTOUT(6) (OUTPUT)

TESTOUT(7) (OUTPUT)

DEBUG BUS

No testpoint means the net

can be accessed from a pad

somewhere else

DVPDATA_16

TP31

DVPDATA_17

TP32 35mil

DVPDATA_18

TP33

DVPDATA_19

TP34 35mil

DVPDATA_20

TP35

DVPDATA_21

TP36

DVPDATA_22

TP37

DVPDATA_23

TP38 35mil

DVP_CNT L_R_[2..0]

DVPDATA_R_[11..0]

STV/HDTV#_OUT_DET(16)

DVPCLK_R

DVP_CNTL_R_0

DVP_CNTL_R_1

DVP_CNTL_R_2

DVPDATA_R_0

DVPDATA_R_1

DVPDATA_R_2

DVPDATA_R_3

DVPDATA_R_4

DVPDATA_R_5

DVPDATA_R_6

DVPDATA_R_7

DVPDATA_R_8

DVPDATA_R_9

DVPDATA_R_10

DVPDATA_R_11

DVPDATA_14

RP5004A 22R

RP5004B 22R

RP5004C 22R

RP5004D 22R

RP5001A 22R

RP5001B 22R

RP5001C 22R

RP5001D 22R

RP5002B 22R

RP5002A 22R

RP5002D 22R

RP5002C 22R

RP5003B 22R

RP5003A 22R

RP5003C 22R

RP5003D 22R

VID_0

AF10

AG10

AE10

AH9

AJ8

AH8

AG9

AH7

AG8

AF7

AE9

AG7

AF9

AG1

AF2

AF1

AF3

AG2

AG3

AH2

AH3

AJ2

AJ1

AK2

AK1

AK3

AL2

AL3

AM3

AE6

AF4

AF5

AG4

AJ3

AH4

AJ4

AG5

AH5

AF6

AE7

AG6

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

VID_7

VPCLK0

VHAD_0

VHAD_1

VPHCTL

VIPCLK

DVPCLK

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

VIP

Capture

VIP

Host

Zoom Video Port

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

VID_7

VPCLK0(16)

VHAD_0(16)

VHAD_1(16)

VPHCTL(16)

VIPCLK(16)

DVPCLK

18

DVP_CNTL_0

27

DVP_CNTL_1

36

DVP_CNTL_2

45

DVPDATA_0

81

DVPDATA_1

72

DVPDATA_2

63

DVPDATA_3

54

DVPDATA_4

72

DVPDATA_5

81

DVPDATA_6

54

DVPDATA_7

63

DVPDATA_8

72

DVPDATA_9

81

DVPDATA_10

63

DVPDATA_11

54

GPIO_0

GPIO_1

General

GPIO_2

Purpose

GPIO_3

I/O

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GENERICA

GENERICB

GENERICC

GENERICD

DVALID

PSYNC

ROMCSb

VARY_BL

No Connect

NC_DVOVMODE_0

NC_DVOVMODE_1

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_22

AD4

AD2

AD1

AD3

AC1

AC2

AC3

AB2

AC6

AC5

AC4

AB3

AB4

AB5

AD5

AB8

AA8

AB7

AK22

AF23

AE23

AD23

AH6

AF8

AC7

AD12

AE11

AJ21

AK21

AH21

AG21

AG20

AH20

AB6

AK4

AL4

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GENERICA

GENERICB

GENERICC

DVALID

PSYNC

ROMCSb

RST#_Ext-TMDS (13)

GPIO_8 (15)

GPIO_9 (14)

DEBUG BUS

No testpoint means the net

can be accessed from a pad

somewhere else

GPIO_10

GPIO_11

GPIO_12

GPIO_13

HPD2 ( 13,15)

GPIO_15 (10)

ThermINT (17)

GENERICA (14)

GENERICB (14)

GENERICC (15)

GPIO PIN STRAP ALTERNATE USE

GPIO_0 YES V I DB_0 (OUTPUT)

GPIO_1 YES V I DB_1 (OUTPUT)

GPIO_2 YES V I DB_2 (OUTPUT)

GPIO_3 YES V I DB_3 (OUTPUT)

GPIO_4 YES V I DB_4 (OUTPUT)

GPIO_5 YES V I DB_5 (OUTPUT)

GPIO_6 YES LDAC (OUTPUT)

GPIO_7 NO PAL/NTSC TV (INPUT)/Ext-TMDS Reset# (OUTPUT)

GPIO_8 YES GPIO_9 YES F L OW_CNTL_EN (OUTPUT)

GPIO_10 NO TESTOUT(8) (OUTPUT)

GPIO_11 YES TESTOUT(9) (OUTPUT)

GPIO_12 YES TESTOUT(10) (OUTPUT)

GPIO_13 YES TESTOUT(11 (OUTPUT))

GPIO_14 NO HPD_DVI1 (HPD2) (INPUT)

GPIO_15 NO VIDA#/B (OUTPUT)

GPIO_16 NO 12VEXT_DETECT (INPUT)

GPIO_17 NO T_INT#(INPUT) & 12VEXT_DETECT# (INPUT)

RV530 Unfused LF A11

PIN BASED STRAPS

+3.3V

GPIO_0

GPIO_1

GPIO_3

B B

GPIO_2

GPIO_4

GPIO_6

GPIO_5

GPIO_8

GPIO_9

GPIO_13

GPIO_12

GPIO_11

A_VSYNC_DAC1(1,3,14)

A_HSYNC_DAC1(1,3,14)

A_VSYNC_DAC2(3,15)

A A

A_HSYNC_DAC2(3,15)

DVALID(15)

A_VSYNC_DAC1

A_HSYNC_DAC1

A_VSYNC_DAC2

A_HSYNC_DAC2

GENERICC

DVALID

PSYNC

GPIO_7

5

4

R51 10K

R52 10K

DNI

R53 10K

DNI

R54 10K

DNI

R55 10K

DNI

R56 10K

R57 10K

DNI

R58 10K

R59 10K

R60 10K

DNI

R61 10K

DNI

R62 10K

DNI

R63 10K MR63 10K

R64 10K

DNI

R65 10K

DNI

R66 10K

DNI

R67 10K

DNI

R68 10K

DNI

R69 10K

R70 10K

P2

PLUG

MR51 10K

MR52 10K

MR53 10K

MR54 10K

MR55 10K

MR56 10K

MR57 10K

MR58 10K

MR59 10K

MR60 10K

MR61 10K

MR62 10K

MR64 10K

MR65 10K

MR66 10K

MR67 10K

MR68 10K

MR69 10K

MR70 10K

NR70 1K

123

www.vinafix.vn

JU2

Header_3_Pin_1X3

DNI

GPIO(0) - TX _ P WRS _ E N B ( T ransmitter Po w er Savings Enable)

0: 50% Tx output swing for mobile mode

1: full Tx ou t put swing (De f a ult setting for Desktop)

GPIO(1) - TX_DEEMPH_EN (Transmitter De-emphasis Enable)

DNI

0: Tx de-emphasis disabled for mobile mode

1: Tx de-emphasis enabled (Default setting for Desktop)

GPIO(3:2) - Mi s ce l laneous PCI-Express Modes

00: Halt impedance calibration before transmitter is enabled and enable receiver detection (Default

setting for Desktop)

01: Allow impedance calibration to continue on in the background AFTER transmitter ha s

been enabled an d en able receive detection.

10: Bypass common - mo de detection & receiver detection and halt impedance calibration before TX_EN.

11: Short-circuit internal loopback and halt impedance calibration before TX_EN and enable

receiver detection.

GPIO(4) - DEBUG_ACCESS: 0 for normal operation, 1 for debug mode

GPIO(6:5) - PLL_IBIAS_RD (Reduced mirror bias setting for PHY PLL)

DNI

Provide 4 dif f erent IBI AS s e t t i n g s - S e t t o 0 0 f o r R520

GPIO(8) - FORCE_COMPLIANCE: 0 for Normal operation, 1 for Force into Compliance Mode

DNI

GPIO(9,13:11) - ROMIDCFG[3..0]

1001 - 1M AT25F1024 ROM (Atmel)

1010 - 1M AT45DB011 ROM (Atmel)

DNI

1011 - 1M M25P10 ROM (ST)

1100 - 512K M25P05 ROM (ST) (ATI default)

1101 - 1M SST45LF010 ROM (SST), 1M W45B512 ROM ( WinBond), 512K W45B012 ROM (WinBond)

1110 - 1M SST25VF010 ROM (SST), 512K SST25VF512 ROM (SST)

1111 - 1M NX25F011B ROM (NexFlash)

VSYNC - VIP_DEVICE

0: Slave VIP host port devices present (use if Theater is populated)

1: No slave VIP host port devices reporting presence during res et (use for configurations without video-in)

HSYNC - DWNGRD

DNI

This straps allow a Workstation bonded part to be downgraded to a normal part on a board. This

allow inventory mana ge men t t o better balance demand.

0 - Device remain a Workstation grade part

1 - Part is downgraded to a Normal part

H2SYNC, V2S YNC, GENERIC C - S t a r Memory System repair mode

000 - Default

MEMORY CONFIG

DVALID: 0 = 4 bank memo ry , 1 = 8 bank memory

PSYNC: 0 = 1 ra n k o f memory, 1 = 2 ranks of memory

TV OUT STANDARD (Jumper position overwrite resistor settings)

0 - PAL TVO (Ju mp er position 2-3)

1 - NTSC TVO (Jumper position 1-2)

3

ATI Feature I

ATI Board Feature I

ATI PCIE FEATURE I

ATI PCIE FEATURE II

ATI Feature II

ATI Board Feature II

ATI PCIE FEATURE III

+3.3V

R35

10K

GPIO_8

GPIO_9

GPIO_10

ROMCSb

2

+3.3V

R36

10K

MR36

10K

+3.3V

Title

Size Docum e n t N u mb er Re v

C

Date: Sheet

U2

D

C

S

HOLD

W

VCC

VSS

M25P05-AVNM6P

105-A671xx-00

2

Q

BIOS1

BIOS

4

113-XXXXXX-XXX

VIDEO BIOS

FIRMWARE

of

1

720Saturday, O ctober 08, 2005

5

6

1

7

3

8

C51

100nF

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham, Ontario

Canada, L3T 7X6

(905) 882-2600

RV530/RV515 256MB DDR3-136 Dual 2xDVI VIVO FH

2

Page 8

8

7

6

5

4

3

2

1

VDDC-PWM1

BST

GH

GND

GL

Vcc

VCC

PVCC

LGATE

PGND

BOOT

UGATE

PHASE

+PW_VDDC_M

VDDC_EN

VDDC_FB

+VDDC_B

R609 1K

+VDDC_B

10

9

3

2

+VDDC_VCC

1

14

13

12

11

10

9

8

R608 20K

+12V_BUS_F1

402

+PW_VDDC_LGD

+PW_VDDC_HGD

+12V_BUS_F1

+VDDC_B

C603

0.22uF

+PW_VDDC_LGD

+PW_VDDC_HGD

C604

0.22uF

402

+PW_VDDC_M

+PW_VDDC_LGD

+PW_VDDC_HGD

+PW_VDDC_M

+PW_VDDC_HGD

SMPS_EN1 (1)

+PW_VDDC_M

+PW_VDDC_LGD

+PW_VDDC_HGDR +PW_VDDC_LGDR

MQ601

+VDDC_S +VDDC_S

Thermal

Pad

9

4 5

3

6

2

7

1

8

FDS7096N3

+PW_VDDC_M

R621 0R

R622 0R

+PW_VDDC_HGDR

402

+PW_VDDC_LGDR

402

MQ603

Thermal

Pad

4 5

3

2

1

FDS7096N3

9

6

7

8

VDDC_SS

VDDC_FB

+VDDC_S

R624

221K

VDDC_COMP

VDDC_FB

1% 1%

R602 30.1K

C602 1nF

R603 2.37K

R604 0R

R623 0R

D D

+VDDC_S

C601

22nF

603

C C

VDDC_FB

VDDC_COMP

+12V_BUS_F1

VDDC_UVIN

R625

100K

402402

+3.3V_BUS

402

VDDC_RT

402

VDDC_OCS

X7R 10V

402

VDDC_SS

VDDC_COMP_U601

+PW_VDDC_HGD

+VDDC_B

+PW_VDDC_LGD

VDDC_COMP_U104

VDDC_COMP_U601

+PW_VDDC_M

R601 10K

2

3

1

2

3

1

U602

7

SS

4

Vfb

5

COMP

6

UVIN

8

SWN

SP6132CU

SIPEX SP6132A p/n 2480054700G

402

VDDC_EN

VDDC-PWM2

U601

1

RT

2

OCSET

3

SS

4

COMP

5

FB

6

EN

7

GND

ISL6522CB

INTERSIL ISL6522/ISL6535

RICHTEK RT9232/RT9232A

ANPEC APW7062A

ANPEC APW7062B

VDDC-PWM3

U603

8

UGATE

PS

7

OPS

GND

6

BOOT

FB

5

LGATE4VCC

RT9214CS

RICHTEK RT9214

INTERSIL ISL6545

VDDC-PWM4

U604

8

UGATE

PS

7

OPS

GND

6

BOOT

FB

5

LGATE4VCC

RT9214CS

Q601

QH

4 5

3

2

1

BSC119N03SG

Q603

4 5

3

2

1

BSC119N03SG

Q602

QL

4 5

3

2

1

BSC119N03SG

Q604

4 5

3

2

1

BSC119N03SG

MQ602

4 5

3

2

1

FDS7096N3

Thermal

Pad

Thermal

Pad

Thermal

Pad

Thermal

Pad

Thermal

Pad

+VDDC_S

9

6

7

8

9

6

7

8

9

6

7

8

9

6

Place Rs and Cs across QL

7

8

RC snubber values shown

are for reference only,

tuning is required

9

6

7

8

CAP CER 10UF 20% 16V X5R

(1206)1.8MM H MAX

C616

C615

10UF

10UF

L601

R68UH

ML601

1.71uH_14A

1 2

NL601 2.2uH_13A

1 2

R619

R620

33MOHM

33MOHM

Rs

1210

1210

1%

1%

C608

10nF_25V

Cs

402

X7R

25V

MULTI FOOTPRINT

MQ604

Thermal

Pad

FDS7096N3

9

6

7

8

4 5

3

2

1

C617

10UF

1206

MULTI FOOTPRINT

VDDC_FB(10)

C619

10UF

VDDC_FB

C620

10UF

1206 1206120612061206

C621

10UF

1206

R1

R611

1K

402

1%

R4

R610

2.0K

402

1%

C622

10UF

C613

2.2nF_50V

R613

49.9R

Place R1 and

R4 close to

PWM and

routed with

separate

20mil trace to

the ASIC

***

***

***

C618

150nF_16V

603

**

MC623

22uF_16V

**

ALT ALT

0.8V Ref

R4 = (R1 x 0.8V) / (Vout1 - 0.8V)

***

C625

470uF_10V

***

TH TH

CAP AE 470UF 20% 10V 10x12 .5MM LOW ESR

+12V_BUS

B601

60R

***

+VDDC

**

MC624

C623

10uF

DUAL FOOTPRINT DUAL FOOTPRINT

***

MC625

470uF

***

ALT

POLY

DUAL FOOTPRINT

LF CAP, AL/POLY, 470UF 6.3V, LOW ESR, 8MM DIA, SMT

22uF_16V

**

***

C626

470uF_10V

***

DUAL FOOTPRINT

C624

10uF

CAP CER 10UF 10%

6.3V X5R (0805)1.4MM

MAX THICK

+VDDC

***

MC626

470uF

***

ALT

POLY

ANPEC APW7061A

B B

This symbol is used for 103 SMPS p/n.

VDDC1

402

VDDC_EN

R614 0R

VDDC_COMP

RV410SOCKET

Regulator for VDDC (ASIC Core)

Vout = 1V ~ 1.3V

COMPENSAT IO N CIRCUIT FILTERED +12V_BUS BOOT CI RCUIT

MR606

0R

402 402

21

D601

SD103AWS

R605

0R

16V

+5V+12V_BUS

402

R606

0R

C606

150nF_16V

+PW_VDDC_M

+VDDC_VCC

+VDDC_B

Part

Vout

0.8V Ref 1.2V

1.25V

1.00K 1%

1.00K 1% 1.78K 1%

R2R1

2.00K 1%

1.3V 1.00K 1% 1.6K 1%

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham , O ntario

Canada, L3T 7X6

(905) 882-2600

Title

RV530/RV515 256MB DDR3-136 Dual 2xDVI VIVO FH

Size Document Number Rev

Custom

5

4

3

Date: Sheet

2

105-A671xx-00

2

of

820Saturday, October 08, 2005

1

+12V_BUS

R615

0R

402

VDDC_COMP

C612

C611

33pF

10nF

10V

603

A A

402

R612

8.06K

402

1%

50V

10%

NPOX7R

10%

402

VDDC_FB

7

R616 0R

R617

0R

402

8

+12V_BUS_F1

+12V_BUS

R607

2.2R

C607

100nF

MD601

BAT54S

603

X7R

5%

C605

100nF

603

X7R

5%

6

www.vinafix.vn

Page 9

8

7

6

5

4

3

2

1

Thermal

Pad

9

6

7

8

Thermal

Pad

9

6

7

8

MQ702

Thermal

Pad

4 5

3

2

1

FDS7096N3

+MVDDC_S

CAP CER 10UF 20% 16V X5R

(1206)1.8MM H MAX

Rs

R719

33MOHM

1210

1%

C708

10nF_25V

402

X7R

25V

Place Rs and Cs across QL

MVDDC_FB

9

6

7

8

*** ***

C715

C716

10UF

10UF

*** ***

L701 2.2uH_13A

1 2

Cs

MULTI FOOTPRINT

C718

C717

150nF_16V

10UF

1206

603

C713

2.2nF_50V

R713

49.9R

R1

R711

1.78K

402

1%

Place R1 and

R4

R4 close to

PWM and

R710

routed with

1.3K

separate

402

20mil trace to

1%

the ASIC

RC snubber values shown

are for reference only,

tuning is required

+12V_BUS

B701

60R

***

+MVDD

***

C725

470uF_10V

***

DUAL FOOTPRINT

0.8V Ref

R4 = (R1 x 0.8V) / (Vout1 - 0.8V)

***

MC725

470uF_6.3V

***

ALT

POLY

*** ***

C723

100uF_6.3V

1210 1210

*** ***

C724

100uF_6.3V

Q701

QH

MVDDC-PWM1

U702

MVDDC_EN

MVDDC_FB

+PW_MVDDC_M

R701 10K

1

HSD

ILIM

DH

2

COMP

DL

3

FB

GND

9

LX

10

BST

PGND

MAX1954EUB

MAXIM MAX1954

MAXIM MAX1954A

MVDDC_EN

402

MVDDC-PWM2

U701

1

RT

2

OCSET

3

SS

4

COMP

5

FB

6

EN

7

GND

ISL6522CB

INTERSIL ISL6522

RICHTEK RT9232A

ANPEC APW7062A

ANPEC APW7062B

+MVDDC_S

603

R718

1%

301K

C709

D D

C C

C710

470pF_50V

402

X7R

+MVDDC_S

MVDDC_COMP

C701

22nF

603

47pF_50V

402

NPO

5%

R702 30.1K

402

C702 1nF

R703 2.37K

402

R704 0R

402

+MVDDC_B

+3.3V_BUS

MVDDC_RT

402

X7R10V

MVDDC_OCS

MVDDC_SS

MVDDC_COMP_U1049

MVDDC_FB

+PW_MVDDC_HGD

8

+PW_MVDDC_LGD

6

5

+MVDDC_VCC

IN

4

7

SMPS_EN2 (1)

PVCC

LGATE

PGND

BOOT

UGATE

PHASE

+12V_BUS_F2

C704

+MVDDC_B

0.22uF

+PW_MVDDC_LGD

+PW_MVDDC_HGD

+PW_MVDDC_M

14

VCC

13

12

11

10

9

8

MVDDC-PWM3

+PW_MVDDC_HGD

+MVDDC_B

+PW_MVDDC_LGD

U703

2

3

1

8

UGATE

PS

7

OPS

GND

6

BOOT

FB

5

LGATE4VCC

RT9214CS

RICHTEK RT9214

INTERSIL ISL6545

+PW_MVDDC_M

MVDDC_EN

MVDDC_FB

R708 20K

+12V_BUS_F2

C703

0.22uF

402

+PW_MVDDC_HGD

+PW_MVDDC_M

+PW_MVDDC_LGD

+PW_MVDDC_HGDR

MQ701

Thermal

Pad

4 5

3

2

1

FDS7096N3

+PW_MVDDC_M

+MVDDC_S

9

6

7

8

R721 0R

R722 0R

+PW_MVDDC_HGDR

402

+PW_MVDDC_LGDR

402

4 5

3

2

1

BSC119N03SG

Q702

QL

4 5

3

2

1

BSC119N03SG

+PW_MVDDC_LGDR

MVDDC-PWM4

B B

MVDDC_FB

MVDDC_COMP

+12V_BUS_F2

R723 0R

MVDDC_COMP_U204

402

2

3

1

U704

RT9214CS

UGATE

GND

BOOT

LGATE4VCC

8

PS

7

OPS

+MVDDC_B

6

FB

R709 1K

5

+PW_MVDDC_LGD

+PW_MVDDC_HGD

+PW_MVDDC_M

402

ANPEC APW7061A

R714 0R

402

MVDDC_EN MVDDC_ COMP

This symbol is used for 103 SMPS p/n.

MVDD1

RV410SOCKET

Regulator for MVDD

Vout = 1.8V ~ 2.85V

COMPENSAT IO N CIRCUIT FILTERED +12V_BUS BOOT C I RCUIT

MR706

0R

402 402

21

D701

SD103AWS

R705

0R

16V

+5V+12V_BUS

R706

0R

C706

150nF_16V

402

+MVDDC_VCC

+MVDDC_B

+PW_MVDDC_M

5

4

3

+12V_BUS

R715

0R

402402

A A

C711

10nF

402

10V

10%

R712

4.99K

402

1%

C712

33pF

603

50V

NPOX7R

10%

R716 0R

R717

0R

402

8

MVDDC_COMP

MVDDC_FB

402

+12V_BUS_F2

7

+12V_BUS

R707

2.2R

C707

100nF

MD701

BAT54S

603

X7R

5%

C705

100nF

603

X7R

5%

6

Part R2R1

0.8V Ref

Vout

1.9V

2.0V 1.69K 1.1K

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham , O ntario

Canada, L3T 7X6

(905) 882-2600

Title

RV530/RV515 256MB DDR3-136 Dual 2xDVI VIVO FH

Size Document Number Rev

Custom

Date: Sheet

2

1.78K 1.3K

1.78K 1.21K

105-A671xx-00

2

of

920Saturday, October 08, 2005

1

www.vinafix.vn

Page 10

8

7

6

5

4

3

2

1

Option for Dynamic VDDC

+5V

D D

GPIO15 LO = LED "OFF" AND 1 .2V VDDC

GPIO15 HI = LED "ON" AND 1.0V VDDC

GPIO_15(7)

R696 1K

R695

R694

10K

10K

402

402

DNI

+3.3V

C C

402

Regulator for +MVDDQ

Vout = 1.85V ~ 2.65V

Iout = 1.7A MAX

P_QMVDD = 2.5W MAX

2 1

D699

LED

**

MC981

22uF_16V

**

ALT

C699

100nF

2 4

3 5

C981

10uF

VDDC_FB(8)

Install a 0 Ohm resistor for

Rx for regular operation

R697 0R

DNI

U699

NC7SZ04M5

C983

1uF_6.3V

LF CAP CER 1UF 10% 6.3V X5R (0402)

+MVDD

4

Rm1

**

C982

MC982

22uF_16V

**

ALT

Rm2

10uF

R699

301R

402

VCORE_PLAY

R698

75R

Rx

402

+3.3V

MVDD_EN(11)

Q951

FQD20N06TM

12A 60V

Rds(on) = 0.15R MAX

QMVDD

1

3 2

C985

10uF

R954

CAP, TANTALUM 10UF 20% 6.3V A CASE

562R

402

1%

R6 = (R5 x Vr e f) / (Vout - Vref)

R955

1K

603

1%

32

MVDD_G

MVDD_FB

2N7002E

Q699

1

C986

100nF

Place Big Copper Area Under QMVDD

pin 2 and 4 for Heat Dissipation.

+12V_BUS

R956

470R

1/4W

1206

5%

3 2

C984

150nF_16V

LF CAP CER 150NF 10% 16V X7R (0603)

REG951

AS432S

4

1

NC

1

NC

2

5 3

MREG951

SC431LC5SK-1

Voltage Req.

2.85V

2.55V 316022R100G22.1R

2.5V

Rm1 Rm2

0R 3150000000 DNI

681R 3160681000G 953R 3240953000

562R1.9V min, 1. 94V nom. 1K

1.1K

3240110100G

3160681000G681R2.0V min

1.1K 3240110100G

2.5V Ref.

2.5V Ref.

1.24V Ref.2.1V min

1.24V Ref.

1.24V Ref.3160562000G 3160100100G

DUAL FOOTPRINT

CAP CER 10UF 10% 6.3V X5R

B B

A A

8

7

(0805)1.4MM MAX THICK

+2.5V +2.5V

R908

0R

402

1%

Q905

1

MMBT3904

2 3

R909

249R

402

1%

3 2

REG905

AS432S

1

DUAL FOOTPRINT

R906

604R

1%

R907

1.37K

1%

6

R905

10R

805, 1/10W

Rt1

402

4

NC

1

NC

2

MREG905

Rt2

5 3

402

SC431LC5SK-1

D905

1.8V

2 1

+1.8V

C906

C905

100nF

10uF

ATI Technologies Inc.

1 Commerce Valley Drive East

Markham , O ntario

Canada, L3T 7X6

(905) 882-2600

Title

RV530/RV515 256MB DDR3-136 Dual 2xDVI VIVO FH

Size Document Number Rev

Custom

5

4

3

Date: Sheet

2

105-A671xx-00

2

of

10 20Saturday, October 08, 2005

1

www.vinafix.vn

Page 11

8

+3.3V_BUS

+2.5V_REF

4

1

2

5V_EN

8

C901

10uF

+2.5V

+12V_BUS

3

2

R913

1K

1%

DNI

5

6

R923

1K

1%

10

9

R933

1K

1%

12

13

R943

1K

1%

+

-

+

-

R922 1K

+

-

R932 1K

+

-

R942 1K

B901

120R_300mA

ALT

Possible alternate

5150005600G

Place caps very

close to power pin

C903

C902

100nF

100nF

603

603

X7R

X7R

411

R910 0R

1

U901A

LM324M

C917

10nF

R912 0R

R920 0R

7

C929

U901B

10nF

LM324M

1%

Req = 120.7R

Use 845R, 1206, 1/4W

8

C939

U901C

10nF

LM324M

1%

Req = 120.7R

Use 845R, 1206, 1/4W

14

C949

U901D

10nF

LM324M

1%

R901

33R

402

REG901

TL431C

D D

+2.5V_REF

+VDDC

C C

B B

A A

+2.5V_REF

+2.5V_REF

+2.5V_REF

NC

NC

5 3

MR911 1K

R911 1K

R918 1K

R921 1K

R931 1K

R941 1K

7

Alt regulator for +MPVDD

Vout = 1.2V (not tracking to VDDC)

Iout = 10mA MAX

+3.3V

3 2

R915

75R

REG911

AS432S

+MPVDD

R916

681R

1%

1

R917

1.5K

1%

+VDDC

B911

120R_300mA

ALT

Possible al te r na t e 5150005600G

Rt1

402

Rt2

402

4

NC

1

NC

2

5 3

MREG911

SC431LC5SK-1

GND_MPVSS

1.61V 432R

1.69V

1.718V

1.75V

+3.3V

C916

+MPVDD

1/4 W

10uF

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

C911

10uF

Q911

1

MMBT3904

200mA, SOT-23

2 3

CMPT3904: 40V 200mA

R914

4.99R

~ 2.5V Drop MAX

200mW MAX

R924 40.2R

270mW MAX for 60mA

Q921

1

R930 0R

R925 0R

1

1

2 3

7

MMBT3904

200mA, SOT-23

2 3

CMPT3904: 40V 200mA

R934

845R

Q931

MMBT3904