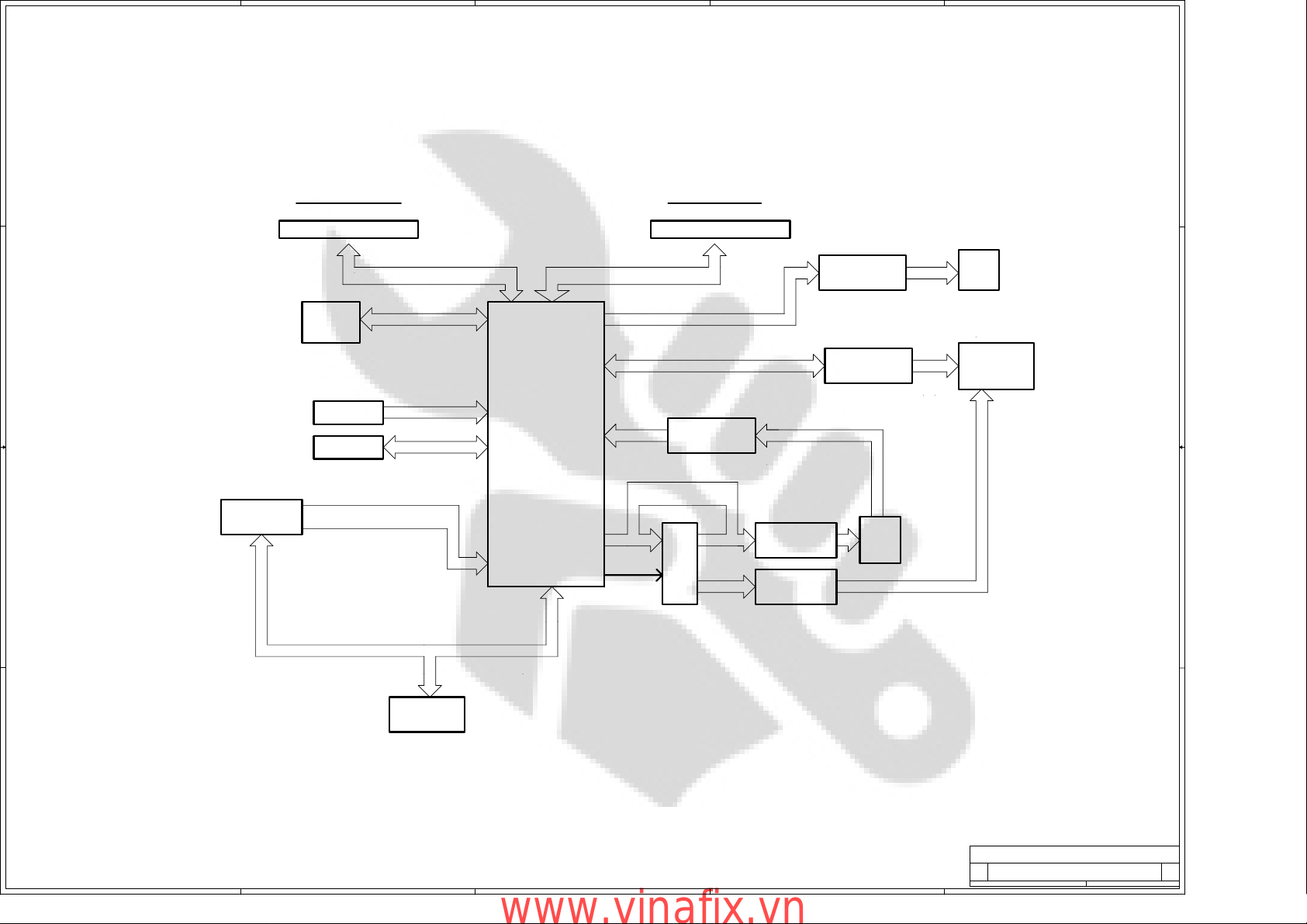

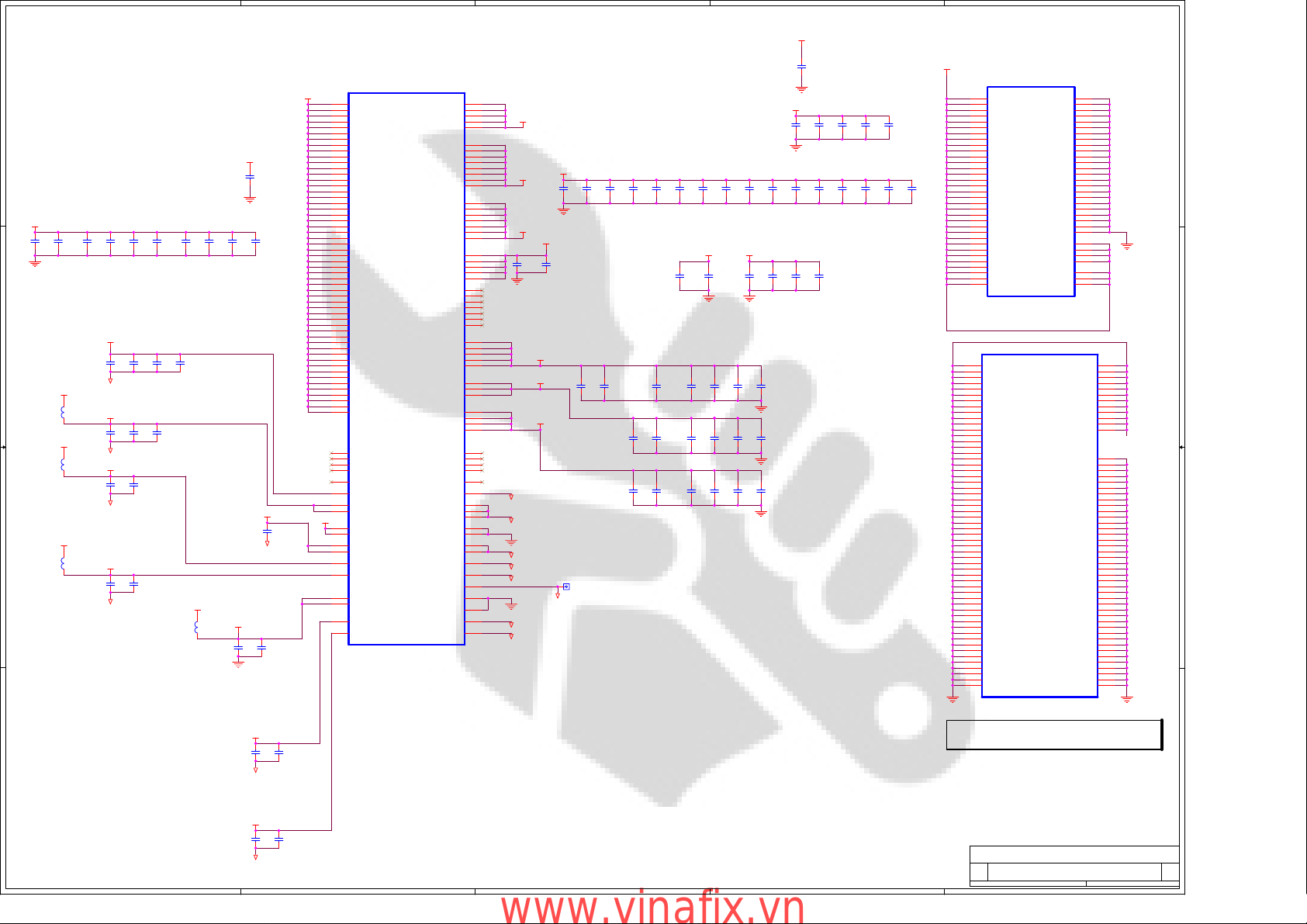

Page 1

5

D D

4

3

2

1

MEMORY CHANNEL A

MEMORY CHANNEL B

DDR2 16X16M MEMORYDDR2 16X16M MEMORY

PRIMARY CRT

LOGIC

MEM B

CLOCK

C C

STRAPS

BIOS

POWER

REGULATION

B B

MEM A

ROM

RV380PRO/XT

PCI-E

DAC1

Int. TMDS

VID

VIP

DAC2

LCDDATA19

RageTheater 1

D

E

M

U

SEL

X

TVOUT Filters

Secondary

CRT LOGIC

INTEGRATED TMDS

LOGIC

VO or

VIVO

CONN

VGA

DB15

CONN

DVI-I CONN

and/or VGA Slim

DB15 CONN

PCI-Express

A A

MS-V031 / ATI X550 / DDRII

Size Document Number Rev

C

Monday, June 27, 2005

5

4

3

2

Date: Sheet

1

117

0A

of

www.vinafix.vn

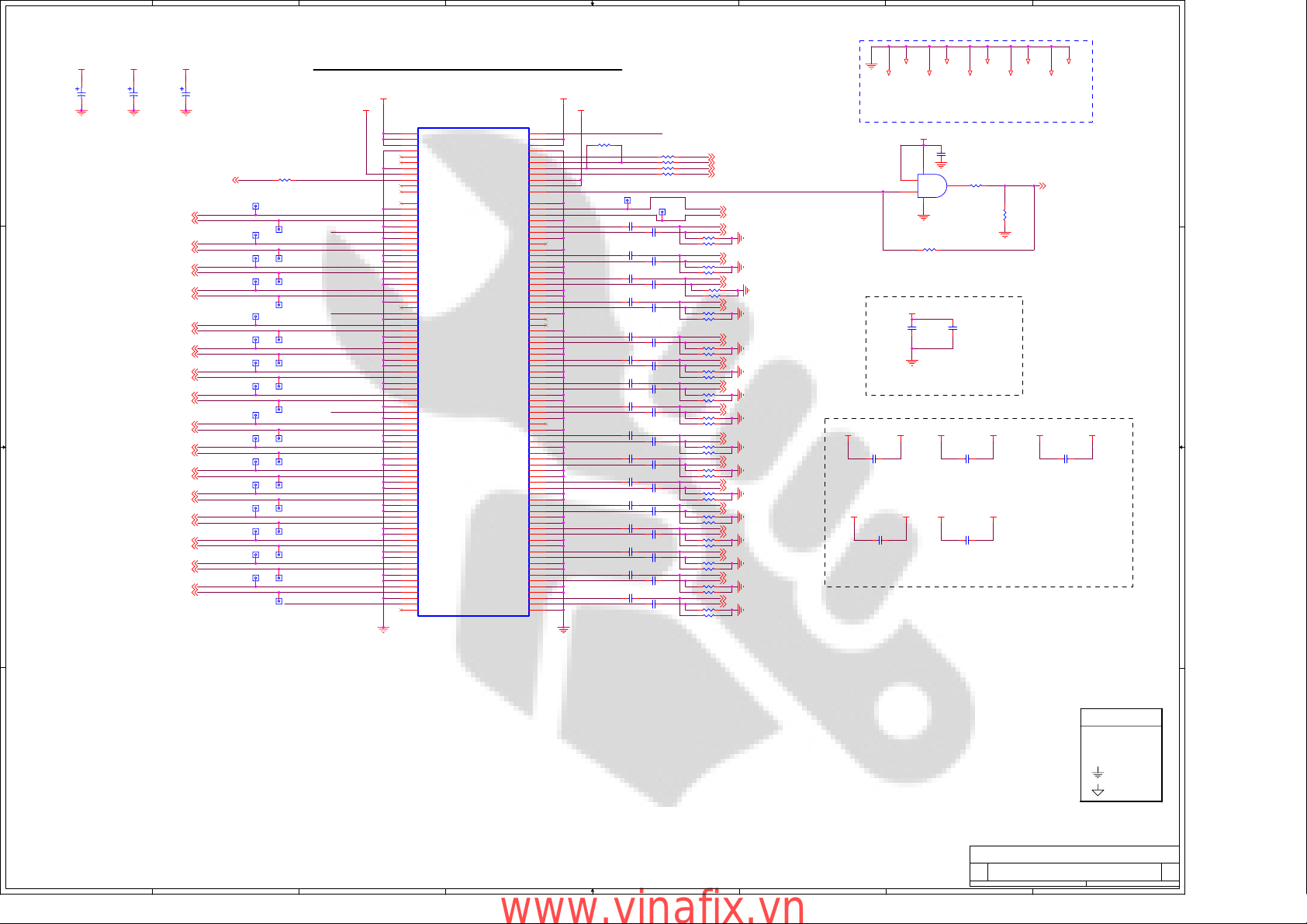

Page 2

8

7

6

5

4

3

2

1

PCI-EXPRESS EDGE CONNECTOR

+12V_BUS

+3.3V_BUS

MPCIE1

B1

402

PRESENCE

JTAG_TRST#

PRESENT_NULL

PRESENT_NULL

PRESENT_NULL

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+12V#B1

+12V#B2

RSVD#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

x16 PCIe

Mechanical Key

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

+12V_BUS

+3.3V_BUS

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

PRESENCE

R12440R

RP194A 0R DNI

8 1

RP194B 0R DNI

7 2

RP194C 0R DNI

6 3

RP194D 0R DNI

5 4

TP26

TP27

C607

100nF

C608

100nF

C617

100nF

C618

100nF

C626

C627

100nF

100nF

C631

100nF

C632

100nF

C611

100nF

C612

100nF

C622

100nF

C623

100nF

C621

100nF

C630

100nF

C605

C606

100nF

100nF

C615

100nF

C616

100nF

C624

100nF

C625

100nF

C633

100nF

C634

100nF

C609

100nF

C610

100nF

C619

100nF

C620

100nF

C628

C629

100nF

100nF

C603

100nF

C604

100nF

C613

100nF

C614

100nF

R701 1.0K

R702 1.0K

R703 1.0K

R704 1.0K

R705 1.0K

R706 1.0K

R707 1.0K

R708 1.0K

R709 1.0K

R710 1.0K

R711 1.0K

R712 1.0K

R713 1.0K

R714 1.0K

R715 1.0K

R716 1.0K

R717 1.0K

R718 1.0K

R719 1.0K

R720 1.0K

R721 1.0K

R722 1.0K

R723 1.0K

R724 1.0K

R725 1.0K

R726 1.0K

R727 1.0K

R728 1.0K

R729 1.0K

R730 1.0K

R731 1.0K

R732 1.0K

A_VSYNC_DAC1 (3,12)

CRT1DDCDATA (3,12)

SCL (3)

CRT1DDCCLK (3,12)

PCIE_REFCLKP (3)

PCIE_REFCLKN (3)

GFXTp0_PERp0 (3)

GFXTn0_PERn0 (3)

GFXTp1_PERp1 (3)

GFXTn1_PERn1 (3)

GFXTp2_PERp2 (3)

GFXTn2_PERn2 (3)

GFXTp3_PERp3 (3)

GFXTn3_PERn3 (3)

GFXTp4_PERp4 (3)

GFXTn4_PERn4 (3)

GFXTp5_PERp5 (3)

GFXTn5_PERn5 (3)

GFXTp6_PERp6 (3)

GFXTn6_PERn6 (3)

GFXTp7_PERp7 (3)

GFXTn7_PERn7 (3)

GFXTp8_PERp8 (3)

GFXTn8_PERn8 (3)

GFXTp9_PERp9 (3)

GFXTn9_PERn9 (3)

GFXTp10_PERp10 (3)

GFXTn10_PERn10 (3)

GFXTp11_PERp11 (3)

GFXTn11_PERn11 (3)

GFXTp12_PERp12 (3)

GFXTn12_PERn12 (3)

GFXTp13_PERp13 (3)

GFXTn13_PERn13 (3)

GFXTp14_PERp14 (3)

GFXTn14_PERn14 (3)

GFXTp15_PERp15 (3)

GFXTn15_PERn15 (3)

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

NOTE: THIS IS A DRAWING. THESE

GROUNDS MUST BE MANUALLY

CONNECTED TO THE GROUND PLANE

PERST#

EC222

100nF

EC225

100nF

C5

100uF_16V

+3.3V_BUS

C8

100uF_16V

>=6.3V

PETp0_GFXRp0(3)

PETn0_GFXRn0(3)

PETp1_GFXRp1(3)

PETn1_GFXRn1(3)

PETp2_GFXRp2(3)

PETn2_GFXRn2(3)

PETp3_GFXRp3(3)

PETn3_GFXRn3(3)

PETp4_GFXRp4(3)

PETn4_GFXRn4(3)

PETp5_GFXRp5(3)

PETn5_GFXRn5(3)

PETp6_GFXRp6(3)

PETn6_GFXRn6(3)

PETp7_GFXRp7(3)

PETn7_GFXRn7(3)

PETp8_GFXRp8(3)

PETn8_GFXRn8(3)

PETp9_GFXRp9(3)

PETn9_GFXRn9(3)

PETp10_GFXRp10(3)

PETn10_GFXRn10(3)

PETp11_GFXRp11(3)

PETn11_GFXRn11(3)

PETp12_GFXRp12(3)

PETn12_GFXRn12(3)

PETp13_GFXRp13(3)

PETn13_GFXRn13(3)

PETp14_GFXRp14(3)

PETn14_GFXRn14(3)

PETp15_GFXRp15(3)

PETn15_GFXRn15(3)

A_HSYNC_DAC1(3,12)

C2

47uF_6.3V

>=6.3V

R1008 0RDNI

TP28

TP30

TP32

TP34

TP36

TP38

TP40

TP42

TP44

TP46

TP48

TP50

TP52

TP54

TP56

TP58

TP29

TP31

TP33

TP35

TP37

TP39

TP41

TP43

TP45

TP47

TP49

TP51

TP53

TP55

TP57

TP59

+12V_BUS +3.3V_BUS

D D

C C

B B

GND_TPVSSGND_MPVSS

GND_A2VSSN

GND_PVSS GND_TXVSSR

+5V

C972

100nF

402

53

+

1

4

2

-U2TC7SZ08FU

R64 0RDNI

402

+5V

EC218

100nF

R3 100R

EC219

100nF

GND_AVSSQ GND_RSET

GND_A2VSSQ

R4

180R

402

GND_R2SETGND_AVSSN

For EMI

+3.3V_BUS+12V_BUS +3.3V_BUS+12V_BUS +3.3V_BUS+12V_BUS

EC223

100nF

+3.3V_BUS+12V_BUS +3.3V_BUS+12V_BUS

EC226

100nF

PERST#_buf (3,15)

EC224

100nF

For EMI

SYMBOL LEGEND

DO NOT

DNI

INSTALL

ACTIVE

#

LOW

DIGITAL

A A

MS-V031 / ATI X550 / DDRII

Size Document Number Rev

C

Tuesday, June 28, 2005

8

7

6

5

4

3

Date: Sheet

2

GROUND

ANALOG

GROUND

of

217

1

0A

www.vinafix.vn

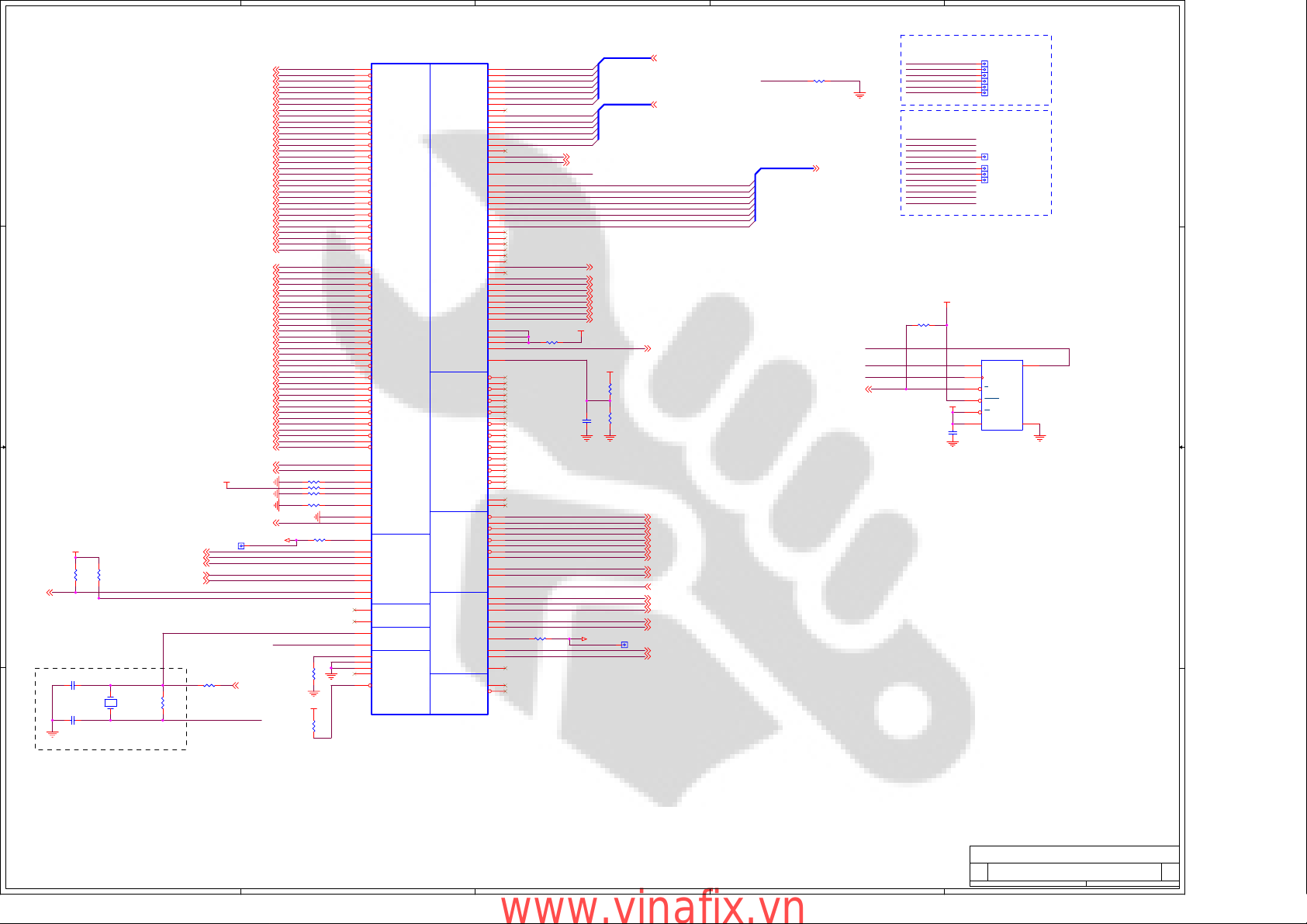

Page 3

5

4

3

2

1

BOUNDARY SCAN TEST ACCESS

A_HSYNC_DAC1

SCL

CRT1DDCDATA

CRT1DDCCLK

A_VSYNC_DAC1

TESTEN

DEBUG BUS ACCESS

VID/DVO16

VID/DVO17

VID/DVO18

VID/DVO19

VID/DVO20

VID/DVO21

VID/DVO22

VID/DVO23

GPIO10

GPIO11

GPIO12

GPIO13

R91

GPIO8

GPIO9

GPIO10

10K

TRST/

TP1

TDO

TP2

TDI

TP3

TMS

TP4

TCK

TP5

TP8

TESTOUT(0)

TESTOUT(1)

TESTOUT(2)

TESTOUT(3)

TP17

TESTOUT(4)

TESTOUT(5)

TP19

TESTOUT(6)

TP20

TESTOUT(7)

TP21

TESTOUT(8)

TESTOUT(9)

TESTOUT(10)

TESTOUT(11)

+3.3V_BUS

U11

D

C

S

HOLD

W

VCC

VSS

M25P05-AVMN6T

2

Q

4

+3.3V_BUS

C80

100nF

5

6

1

7

3

8

SERIAL EEPROM 512K

Mem_Strap1 (11)

Mem_Strap0 (11)

SVHS/YPrPbb (13)

LCDDATA16 (11)

LCDDATA17 (11)

PAL/NTSC (11)

DEMUX_SEL (13)

VHAD0 (11,15)

VHAD1 (15)

VPHCTL (15)

CLK_VIPCLK (15)

+3.3V_BUS

+3.3V_BUS

C16

100nF

402

A_HSYNC_DAC1

GND_RSET

GPIO[6..0]

GPIO[13..8]

U1A

AH30

402

TESTEN

PCIE_RX0P

AG30

PCIE_RX0N

AG29

PCIE_RX1P

AF29

PCIE_RX1N

AE29

PCIE_RX2P

AE30

PCIE_RX2N

AD30

PCIE_RX3P

AD29

PCIE_RX3N

AC29

PCIE_RX4P

AB29

PCIE_RX4N

AB30

PCIE_RX5P

AA30

PCIE_RX5N

AA29

PCIE_RX6P

Y29

PCIE_RX6N

W29

PCIE_RX7P

W30

PCIE_RX7N

V30

PCIE_RX8P

V29

PCIE_RX8N

U29

PCIE_RX9P

T29

PCIE_RX9N

T30

PCIE_RX10P

R30

PCIE_RX10N

R29

PCIE_RX11P

P29

PCIE_RX11N

N29

PCIE_RX12P

N30

PCIE_RX12N

M30

PCIE_RX13P

M29

PCIE_RX13N

L29

PCIE_RX14P

K29

PCIE_RX14N

K30

PCIE_RX15P

J30

PCIE_RX15N

AF26

PCIE_TX0P

AE26

PCIE_TX0N

AC25

PCIE_TX1P

AB25

PCIE_TX1N

AC27

PCIE_TX2P

AB27

PCIE_TX2N

AC26

PCIE_TX3P

AB26

PCIE_TX3N

Y25

PCIE_TX4P

W25

PCIE_TX4N

Y27

PCIE_TX5P

W27

PCIE_TX5N

Y26

PCIE_TX6P

W26

PCIE_TX6N

U25

PCIE_TX7P

T25

PCIE_TX7N

U27

PCIE_TX8P

T27

PCIE_TX8N

U26

PCIE_TX9P

T26

PCIE_TX9N

P25

PCIE_TX10P

N25

PCIE_TX10N

P27

PCIE_TX11P

N27

PCIE_TX11N

P26

PCIE_TX12P

N26

PCIE_TX12N

L25

PCIE_TX13P

K25

PCIE_TX13N

L27

PCIE_TX14P

K27

PCIE_TX14N

L26

PCIE_TX15P

K26

PCIE_TX15N

AF27

PCIE_REFCLKP

AE27

PCIE_REFCLKN

402

AC23

PCIE_CALRP

402

AB24

PCIE_CALRN

402

AB23

PCIE_CALI

402

AE25

PCIE_TEST

AD24

PWRGD_MASK

AD25

PWRGD

AH21

R2SET

AJ22

C_R_PR

AK21

Y_G

AK22

COMP_B_PB

AJ24

H2SYNC

AK24

V2SYNC

AG22

DDC3CLK

AG23

DDC3DATA

AJ23

NC#AJ23

AH24

NC#AH24

AH28

XTALIN

AJ29

XTALOUT

AH27

TESTEN

E8

TEST_YCLK

B6

TEST_MCLK

AF25

PLLTEST

AH25

STEREOSYNC

RV370GL

PETp0_GFXRp0(2)

PETn0_GFXRn0(2)

PETp1_GFXRp1(2)

PETn1_GFXRn1(2)

PETp2_GFXRp2(2)

PETn2_GFXRn2(2)

PETp3_GFXRp3(2)

PETn3_GFXRn3(2)

R47 0RRT

PETp4_GFXRp4(2)

PETn4_GFXRn4(2)

PETp5_GFXRp5(2)

PETn5_GFXRn5(2)

PETp6_GFXRp6(2)

PETn6_GFXRn6(2)

PETp7_GFXRp7(2)

PETn7_GFXRn7(2)

PETp8_GFXRp8(2)

PETn8_GFXRn8(2)

PETp9_GFXRp9(2)

PETn9_GFXRn9(2)

PETp10_GFXRp10(2)

PETn10_GFXRn10(2)

PETp11_GFXRp11(2)

PETn11_GFXRn11(2)

PETp12_GFXRp12(2)

PETn12_GFXRn12(2)

PETp13_GFXRp13(2)

PETn13_GFXRn13(2)

PETp14_GFXRp14(2)

PETn14_GFXRn14(2)

PETp15_GFXRp15(2)

PETn15_GFXRn15(2)

GFXTp0_PERp0(2)

GFXTn0_PERn0(2)

GFXTp1_PERp1(2)

GFXTn1_PERn1(2)

GFXTp2_PERp2(2)

GFXTn2_PERn2(2)

GFXTp3_PERp3(2)

GFXTn3_PERn3(2)

GFXTp4_PERp4(2)

GFXTn4_PERn4(2)

GFXTp5_PERp5(2)

GFXTn5_PERn5(2)

GFXTp6_PERp6(2)

GFXTn6_PERn6(2)

GFXTp7_PERp7(2)

GFXTn7_PERn7(2)

GFXTp8_PERp8(2)

GFXTn8_PERn8(2)

GFXTp9_PERp9(2)

GFXTn9_PERn9(2)

GFXTp10_PERp10(2)

GFXTn10_PERn10(2)

GFXTp11_PERp11(2)

GFXTn11_PERn11(2)

GFXTp12_PERp12(2)

GFXTn12_PERn12(2)

GFXTp13_PERp13(2)

GFXTn13_PERn13(2)

GFXTp14_PERp14(2)

GFXTn14_PERn14(2)

GFXTp15_PERp15(2)

GFXTn15_PERn15(2)

PCIE_REFCLKP(2)

PCIE_REFCLKN(2)

+PCIE_VDDR

TP6

RV380_CLKOUT

PERST#_buf(2,15)

GND_R2SET

RV380_CLKIN (15)

R1009 150R

R1010 100R

R1011 10K

R1089 10K

R40 715R

RV380_CLKIN_R1

RV380_CLKOUT

R33

1.0K

402

+3.3V_BUS

R44

10K

402

D D

C C

B B

+3.3V_BUS

R45

R46

4.7K

4.7K

SCL(2)

402 402

C71 15PF

402

C72 15PF

402

2 1

Y1

27_MHZ

A_R/C_DAC2(13)

A_G/Y_DAC2(13)

A_B/COMP_DAC2(13)

A_HSYNC_DAC2(12)

A_VSYNC_DAC2(12)

R32

1.0M

PCI Express

DAC2CLK

Part 1 of 6

GPIO_PWRCNTL

GPIO_MEMSSIN

DVOVMODE

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVO / EXT TMDS / GPIOTMDSDAC1

DVPDATA_22

DVPDATA_23

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPCNTL_3

DDC2DATA

DDC1DATA

GPIO__AUXWIN

THERM

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

VREFG

NC#AH15

NC#AH16

NC#AJ16

NC#AJ17

NC#AJ18

NC#AK18

NC#AJ20

NC#AJ21

NC#AK19

NC#AJ19

NC#AG16

NC#AG17

NC#AF16

NC#AF17

NC#AE18

NC#AE19

NC#AF19

NC#AF20

NC#AG19

NC#AG20

NC#AE12

NC#AG12

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TXCM

TXCP

DDC2CLK

HPD1

HSYNC

VSYNC

RSET

DDC1CLK

DPLUS

DMINUS

R

G

B

AJ5

AH5

AJ4

AK4

AH4

AF4

AJ3

AK3

AH3

AJ2

AH2

AH1

AG3

AG1

AG2

AF3

AF2

AE10

AH6

AJ6

AK6

AH7

AK7

AJ7

AH8

AJ8

AH9

AJ9

AK9

AH10

AE6

AG6

AF6

AE7

AF7

AE8

AG8

AF8

AE9

AF9

AG10

AF10

AJ10

AK10

AJ11

AH11

AG4

AH15

AH16

AJ16

AJ17

AJ18

AK18

AJ20

AJ21

AK19

AJ19

AG16

AG17

AF16

AF17

AE18

AE19

AF19

AF20

AG19

AG20

AE12

AG12

AK13

AJ13

AJ14

AJ15

AK15

AK16

AJ12

AK12

AE13

AE14

AF12

AK27

AJ27

AJ26

AJ25

AK25

AH26

AG25

AF24

AG24

AF11

AE11

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

DVOMODE

VID/DVO0

VID/DVO1

VID/DVO2

VID/DVO3

VID/DVO4

VID/DVO5

VID/DVO6

VID/DVO7

VID/DVO14

VID/DVO16

VID/DVO17

VID/DVO18

VID/DVO19

VID/DVO20

VID/DVO21

VID/DVO22

VID/DVO23

R43 10K

R39 499R

402

402

GPIO[6..0] (11)

GPIO[13..8] (11)

CLK_VID/DVO (15)

R35

1.0K

402

Both resistors and

capacitor close to ASIC

R34

1.0K

402

TMDS_TX0N (14)

TMDS_TX0P (14)

TMDS_TX1N (14)

TMDS_TX1P (14)

TMDS_TX2N (14)

TMDS_TX2P (14)

TMDS_TXCN (14)

TMDS_TXCP (14)

DVIDDCCLK (12)

DVIDDCDATA (12)

HPD (14)

A_R_DAC1 (12)

A_G_DAC1 (12)

A_B_DAC1 (12)

A_HSYNC_DAC1 (2,12)

A_VSYNC_DAC1 (2,12)

TP7

CRT1DDCDATA (2,12)

CRT1DDCCLK (2,12)

DVOMODE

R23 10K

402

PULL DOWN TO GND

+3.3V RAGE THEATRE INTERFACE

VID/DVO[7..0]

VID/DVO[7..0] (15)

ROMCS#(4)

A A

MS-V031 / ATI X550 / DDRII

Size Document Number Rev

C

Tuesday, June 28, 2005

5

4

3

2

Date: Sheet

1

317

0A

of

www.vinafix.vn

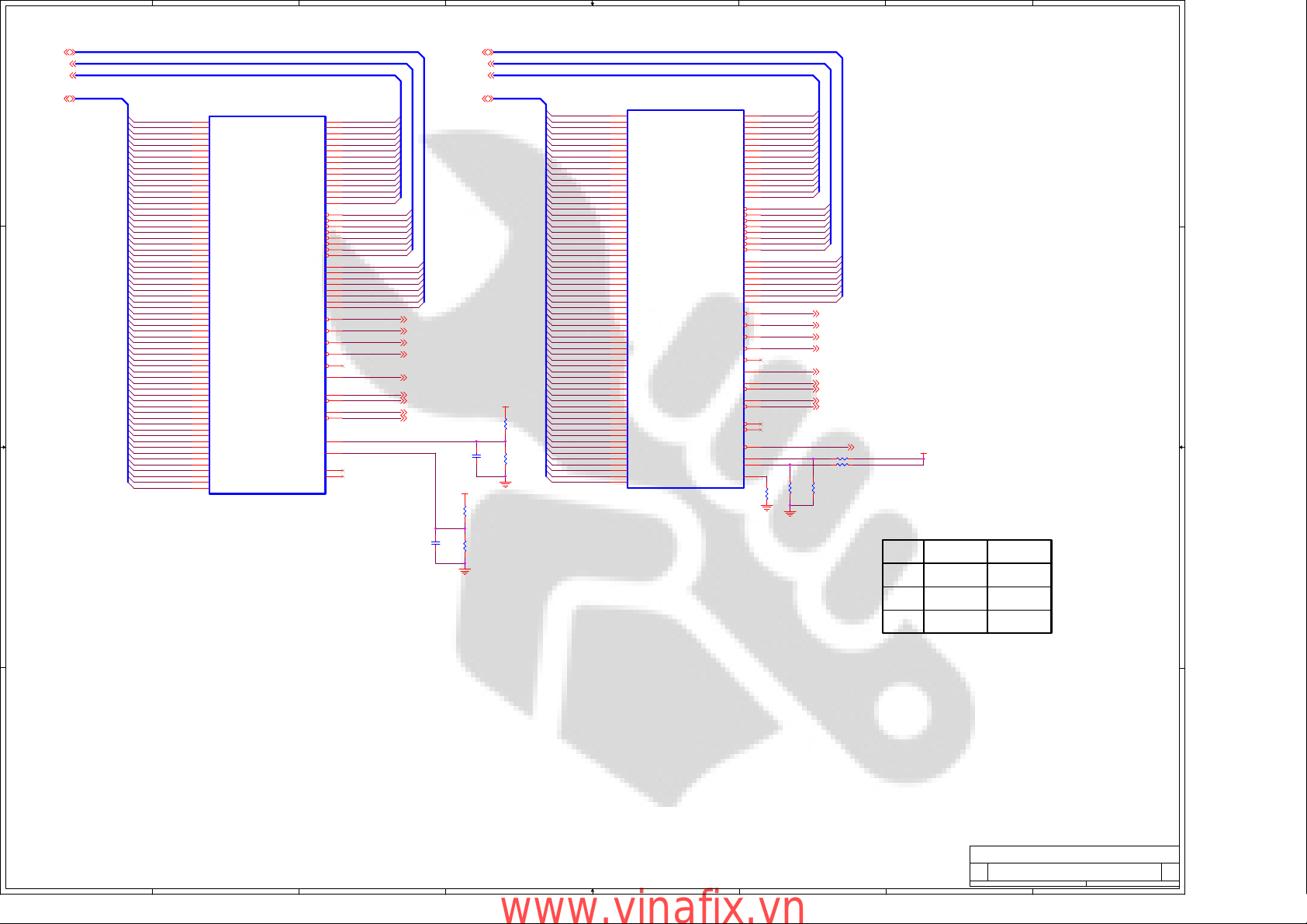

Page 4

1

2

3

4

5

6

7

8

QSA[7..0]

QSA[7..0](9) QSB[7..0](10)

DQMA#[7..0](9)

MAA[14..0](9)

MDA[63..0](9) MDB[63..0](10)

A A

B B

C C

DQMA#[7..0]

MAA[14..0]

MDA[63..0]

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

U1B

H28

DQA_0

DQA_1

DQA_2

DQA_3

DQA_4

DQA_5

DQA_6

DQA_7

DQA_8

DQA_9

DQA_10

DQA_11

DQA_12

DQA_13

DQA_14

DQA_15

DQA_16

DQA_17

DQA_18

DQA_19

DQA_20

DQA_21

DQA_22

DQA_23

DQA_24

DQA_25

DQA_26

DQA_27

DQA_28

DQA_29

DQA_30

DQA_31

DQA_32

DQA_33

DQA_34

DQA_35

DQA_36

DQA_37

DQA_38

DQA_39

DQA_40

DQA_41

DQA_42

DQA_43

DQA_44

DQA_45

DQA_46

DQA_47

DQA_48

DQA_49

DQA_50

DQA_51

DQA_52

DQA_53

DQA_54

DQA_55

DQA_56

DQA_57

DQA_58

DQA_59

DQA_60

DQA_61

DQA_62

DQA_63

RV370GL

Part 2 of 6

MEMORY

INTERFACE A

H29

J28

J29

J26

H25

H26

G26

G30

D29

D28

E28

E29

G29

G28

F28

G25

F26

E26

F25

E24

F23

E23

D22

B29

C29

C25

C27

B28

B25

C26

B26

F17

E17

D16

F16

E15

F14

E14

F13

C17

B18

B17

B15

C13

B14

C14

C16

A13

A12

C12

B12

C10

C9

B9

B10

E13

E12

E10

F12

F11

E9

F9

F8

MEMORY CHANNEL A

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13

MAA_14

DQMAb_0

DQMAb_1

DQMAb_2

DQMAb_3

DQMAb_4

DQMAb_5

DQMAb_6

DQMAb_7

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

RASAb

CASAb

WEAb

CSAb_0

CSAb_1

CKEA

CLKA0

CLKA0b

CLKA1

CLKA1b

MVREFD

MVREFS

DIMA_0

DIMA_1

DQMB#[7..0](10)

MAA0

E22

MAA1

B22

MAA2

B23

MAA3

B24

MAA4

C23

MAA5

C22

MAA6

F22

MAA7

F21

MAA8

C21

MAA9

A24

MAA10

C24

MAA11

A25

MAA12

E21

MAA13

B20

MAA14

C19

DQMA#0

J25

DQMA#1

F29

DQMA#2

E25

DQMA#3

A27

DQMA#4

F15

DQMA#5

C15

DQMA#6

C11

DQMA#7

E11

QSA0

J27

QSA1

F30

QSA2

F24

QSA3

B27

QSA4

E16

QSA5

B16

QSA6

B11

QSA7

F10

RASA#

A19

CASA#

E18

WEA#

E19

CSA#0

E20

F20

CKEA

B19

CLKA0

B21

CLKA#0

C20

CLKA1

C18

CLKA#1

A18

B7

B8

D30

B13

RASA# (9)

CASA# (9)

WEA# (9)

CSA#0 (9)

CKEA (8,9)

CLKA0 (8,9)

CLKA#0 (8,9)

CLKA1 (8,9)

CLKA#1 (8,9)

C154

100nF

402

PLACE C351/152 VERY CLOSE TO ASIC

R56/57/58/59 CLOSE TO ASIC AS WELL

MAB[14..0](10)

+MVDDQ

R58

100R

402

R59

100R

402

C153

100nF

402

QSB[7..0]

DQMB#[7..0]

MAB[14..0]

MDB[63..0]

+MVDDQ

R56

100R

402

R57

100R

402

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB57

MDB56

MDB59

MDB58

MDB60

MDB61

MDB62

MDB63

U1C

D7

DQB_0

DQB_1

DQB_2

DQB_3

DQB_4

DQB_5

DQB_6

DQB_7

DQB_8

DQB_9

DQB_10

DQB_11

DQB_12

DQB_13

DQB_14

DQB_15

DQB_16

DQB_17

DQB_18

DQB_19

DQB_20

DQB_21

DQB_22

DQB_23

DQB_24

DQB_25

DQB_26

DQB_27

DQB_28

DQB_29

DQB_30

DQB_31

DQB_32

DQB_33

DQB_34

DQB_35

DQB_36

DQB_37

DQB_38

DQB_39

DQB_40

DQB_41

DQB_42

DQB_43

DQB_44

DQB_45

DQB_46

DQB_47

DQB_48

DQB_49

DQB_50

DQB_51

DQB_52

DQB_53

DQB_54

DQB_55

DQB_56

DQB_57

DQB_58

DQB_59

DQB_60

DQB_61

DQB_62

DQB_63

RV370GL

Part 3 of 6

MEMORY

MEMVMODE_0

MEMVMODE_1

INTERFACE B

F7

E7

G6

G5

F5

E5

C4

B5

C5

A4

B4

C2

D3

D1

D2

G4

H6

H5

J6

K5

K4

L6

L5

G2

F3

H2

E2

F2

J3

F1

H3

U6

U5

U3

V6

W5

W4

Y6

Y5

U2

V2

V1

V3

W3

Y2

Y3

AA2

AA6

AA5

AB6

AB5

AD6

AD5

AE5

AE4

AB2

AB3

AC2

AC3

AD3

AE1

AE2

AE3

MEMORY CHANNEL B

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_12

MAB_13

MAB_14

DQMBb_0

DQMBb_1

DQMBb_2

DQMBb_3

DQMBb_4

DQMBb_5

DQMBb_6

DQMBb_7

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

RASBb

CASBb

WEBb

CSBb_0

CSBb_1

CKEB

CLKB0

CLKB0b

CLKB1

CLKB1b

DIMB_0

DIMB_1

ROMCSb

MEMTEST

MAB0

N5

MAB1

M1

MAB2

M3

MAB3

L3

MAB4

L2

MAB5

M2

MAB6

M5

MAB7

P6

MAB8

N3

MAB9

K2

MAB10

K3

MAB11

J2

MAB12

P5

MAB13

P3

MAB14

P2

DQMB#0

E6

DQMB#1

B2

DQMB#2

J5

DQMB#3

G3

DQMB#4

W6

DQMB#5

W2

DQMB#6

AC6

DQMB#7

AD2

QSB0

F6

QSB1

B3

QSB2

K6

QSB3

G1

QSB4

V5

QSB5

W1

QSB6

AC5

QSB7

AD1

RASB#

R2

CASB#

T5

WEB#

T6

CSB#0

R5

R6

CKEB

R3

CLKB0

N1

CLKB#0

N2

CLKB1

T2

CLKB#1

T3

E3

AA3

AF5

C6

C7

C8

R55

47R

402

RASB# (10)

CASB# (10)

WEB# (10)

CSB#0 (10)

CKEB (8,10)

CLKB0 (8,10)

CLKB#0 (8,10)

CLKB1 (8,10)

CLKB#1 (8,10)

ROMCS# (3)

R51 4.7KDNI

R52 4.7K

R53

4.7K

R54

DNI

4.7K

402 402

LAYOUT NOTE: SOME OF THE RESISTORS R51-54 MAY BE

REMOVED IF SPACE IS AN ISSUE, ASK BEFORE REMOVING

+VDDC_CT

402

402

VDDR1 MEMVMODE_0 MEMVMODE_1

1.8V

2.5V

2.8V

+VDDC_CT GND

+VDDC_CT +VDDC_CT

+VDDC_CTGND

DEFAULT

D D

MS-V031 / ATI X550 / DDRII

Size Document Number Rev

C

Tuesday, June 28, 2005

1

2

3

4

5

6

Date: Sheet

7

417

8

0A

of

www.vinafix.vn

Page 5

5

+MVDDQ

D D

+MVDDQ

C38

10uf

+MVDDQ

C32

100nF

402 402 402

C C

B B

A A

100nF

100nF

+TPVDD

GND_TPVSS

+1.8V

B11

200R

+TXVDDR_PINS

ALT: 0R

+1.8V

GND_TXVSSR

B14

+A2VDDQ

200R

ALT: 0R

GND_A2VSSQ

AVDD/A2VDDQ (1st & 2nd

DAC Band Gap) - 200mA

+1.8V

B13

200R

+AVDD

ALT: 0R

GND_AVSSN

C35

C33

C31

100nF

402 402402

C50

10uf

OPT

C59

4.7uF

C63

4.7uF

C67

4.7uF

C74

100nF

C43

2.2uF

C60

100nF

C64

100nF

402

C68

100nF

402

C75

100nF

C58

2.2uF

C81

100nF

402402

C73

100nF

402

+1.8V

C94

100nF

B12

200R

ALT: 0R

C95

100nF

402402 402402

+VDDOI_PINS

C96

100nF

C66

4.7uF

+PVDD

GND_PVSS

C97

100nF

+A2VDD

GND_A2VSSN

C65

100nF

402

C54

4.7uF

C62

100nF

402

C53

100nF

402

4

U1D

T7

R4

R1

N8

N7

M4

L8

K23

K24

L23

J8

J7

J4

J1

H10

H13

H15

H17

T8

V4

V7

V8

AA1

AA4

AA7

AA8

A3

A9

A15

A21

A28

B1

B30

D26

D23

D20

D17

D14

D11

D8

D5

E27

F4

G7

G10

G13

G15

G19

G22

G27

H22

H19

AD4

N4

AE15

AE16

AE17

AF15

AH19

AH13 AH12

AF13

AF14

+MVDDQ

F18

N6

AE20

AF21

AF23

AH23

AE23

AE22

AK28 AJ28

A7 A6

Part 4 of 6

VDDR1#T7

VDDR1#R4

VDDR1#R1

VDDR1#N8

VDDR1#N7

VDDR1#M4

VDDR1#L8

VDDR1#K23

VDDR1#K24

VDDR1#L23

VDDR1#J8

VDDR1#J7

VDDR1#J4

VDDR1#J1

VDDR1#H10

VDDR1#H13

VDDR1#H15

VDDR1#H17

VDDR1#T8

VDDR1#V4

VDDR1#V7

VDDR1#V8

VDDR1#AA1

VDDR1#AA4

VDDR1#AA7

VDDR1#AA8

VDDR1#A3

VDDR1#A9

VDDR1#A15

VDDR1#A21

VDDR1#A28

VDDR1#B1

VDDR1#B30

VDDR1#D26

VDDR1#D23

VDDR1#D20

VDDR1#D17

VDDR1#D14

VDDR1#D11

VDDR1#D8

VDDR1#D5

VDDR1#E27

VDDR1#F4

VDDR1#G7

VDDR1#G10

VDDR1#G13

VDDR1#G15

VDDR1#G19

VDDR1#G22

VDDR1#G27

VDDR1#H22

VDDR1#H19

VDDR1#AD4

VDDR1#N4

NC#AE15

NC#AE16

NC#AE17

NC#AF15

NC#AH19

TPVDD TPVSS

TXVDDR#AF13

TXVDDR#AF14

VDDRH0

VDDRH1

A2VDD#AE20

A2VDD#AF21

A2VDDQ

AVDD

VDD1DI

I/O POWER

VDD2DI

PVDD PVSS

MPVDD MPVSS

RV370GL

VDDC#AC13

VDDC#AC15

VDDC#AC17

VDDC#AD13

VDDC#AD15

VDD15#H11

VDD15#H20

VDD15#M23

VDD15#Y23

VDD15#AC11

VDD15#AC20

VDDR3#AC8

VDDR3#AC19

VDDR3#AC21

VDDR3#AC22

VDDR3#AD7

VDDR3#AD19

VDDR3#AD21

VDDR4#AC9

VDDR4#AC10

VDDR4#AD9

VDDR4#AD10

VDDR4#AG7

PCIE_VDDR_12#AG26

PCIE_VDDR_12#AG27

PCIE_VDDR_12#AG28

PCIE_VDDR_12#AJ30

PCIE_VDDR_12#AK29

PCIE_PVDD_12#N23

PCIE_PVDD_12#N24

PCIE_PVDD_12#P23

PCIE_PVDD_18#T23

PCIE_PVDD_18#U23

PCIE_PVDD_18#V23

PCIE_PVDD_18#W23

TXVSSR#AH14

TXVSSR#AG13

TXVSSR#AG14

A2VSSN#AH20

A2VSSN#AG21

VDD15#P8

VDD15#Y8

NC#D9

NC#D13

NC#D19

NC#D25

NC#E4

NC#T4

NC#AB4

NC#AF18

NC#AG15

NC#AG18

NC#AH17

NC#AH18

VSSRH0

VSSRH1

A2VSSQ

AVSSN

AVSSQ

VSS1DI

VSS2DI

AC13

AC15

AC17

AD13

AD15

H11

H20

M23

P8

Y23

Y8

AC11

AC20

AC8

AC19

AC21

AC22

AD7

AD19

AD21

AC9

AC10

AD9

AD10

AG7

D9

D13

D19

D25

E4

T4

AB4

AG26

AG27

AG28

AJ30

AK29

N23

N24

P23

T23

U23

V23

W23

AF18

AG15

AG18

AH17

AH18

AH14

AG13

AG14

F19

M6

AH20

AG21

AF22

AH22

AD22

AE24

AE21

+VDDC

+VDDC_CT

+3.3V_BUS

GND_TPVSS

GND_TXVSSR

GND_A2VSSN

GND_A2VSSQ

GND_AVSSN

GND_PVSS

GND_MPVSS

+3.3V_BUS

C70

4.7uF

+PCIE_VDDR

+PCIE_PVDD_12

+PCIE_PVDD_18

GND_AVSSQ

+VDDC

C69

100nF

402

C20

100nF

3

C21

C22

C23

100nF

100nF

100nF

402 402402

C99

C98

1.0uF

1.0uF

C968

2.2uF

C970

1.0uF

TP9

C84

C82

C83

100nF

100nF

402 402 402 402 402 402 402 402402 402 402 402 402

+3.3V_BUS

C44

100nF

C37

C39

1.0uF

100nF

402 402

C41

C969

100nF

2.2uF

402 402

C971

C55

1.0uF

100nF

402 402

100nF

C46

100nF

C40

100nF

C42

100nF

C56

100nF

C85

100nF

C86

100nF

+VDDC_CT

C45

100nF

402 402 402 402402 402

C76

100nF

402 402

C78

100nF

402 402

C57

100nF

402 402

C77

100nF

C79

100nF

C61

100nF

C87

100nF

C47

100nF

+VDDC

+VDDC

C26

100nF

C88

100nF

C48

100nF

2

C24

10uf

C28

C29

C27

100nF

100nF

100nF

402 402 402 402402

C91

C89

C90

100nF

100nF

100nF

C49

100nF

C30

100nF

C92

100nF

+VDDC

U1F

P17

VDDC#P17

P18

VDDC#P18

P19

VDDC#P19

U12

VDDC#U12

U13

VDDC#U13

U14

VDDC#U14

U17

VDDC#U17

U18

VDDC#U18

U19

VDDC#U19

V19

VDDC#V19

V18

VDDC#V18

V17

VDDC#V17

V14

VDDC#V14

V13

VDDC#V13

V12

VDDC#V12

N18

C93

100nF

VDDC#N18

N17

VDDC#N17

N14

VDDC#N14

W17

VDDC#W17

W18

VDDC#W18

W12

VDDC#W12

W13

VDDC#W13

W14

VDDC#W14

N13

VDDC#N13

N19

VDDC#N19

M19

VDDC#M19

M18

VDDC#M18

M12

VDDC#M12

N12

VDDC#N12

M13

VDDC#M13

M14

VDDC#M14

P12

VDDC#P12

P13 P14

VDDC#P13 VDDC#P14

RV370GL

U1E

A2

VSS#A2

A10

VSS#A10

A16

VSS#A16

A22

VSS#A22

A29

VSS#A29

C1

VSS#C1

C3

VSS#C3

C28

VSS#C28

C30

VSS#C30

D27

VSS#D27

D24

VSS#D24

D21

VSS#D21

D18

VSS#D18

D15

VSS#D15

D12

VSS#D12

D6

VSS#D6

D4

VSS#D4

D10

VSS#D10

F27

VSS#F27

G9

VSS#G9

G12

VSS#G12

G16

VSS#G16

G18

VSS#G18

G21

VSS#G21

G24

VSS#G24

H27

VSS#H27

H23

VSS#H23

H21

VSS#H21

H18

VSS#H18

H16

VSS#H16

H14

VSS#H14

H12

VSS#H12

H9

VSS#H9

H8

VSS#H8

H4

VSS#H4

J23

VSS#J23

J24

VSS#J24

AD12

VSS#AD12

AG5

VSS#AG5

AG9

VSS#AG9

AG11

VSS#AG11

R7

VSS#R7

P4

VSS#P4

M7

VSS#M7

M8

VSS#M8

L4

VSS#L4

K1

VSS#K1

K7

VSS#K7

K8

VSS#K8

R8

VSS#R8

T1

VSS#T1

W8

VSS#W8

W7

VSS#W7

U8

VSS#U8

U4

VSS#U4

Y4

VSS#Y4

RV370GL

ADD ASIC DECOUPLING FOR ALL POWER AS REQUIRED

PLACED CLOSE TO THE POWER/GND PINS

WITH AS MANY AS POSSIBLE PLACED UNDER THE ASIC

Part 6 of 6

VSS#M16

VSS#N16

VSS#N15

VSS#P15

VSS#P16

VSS#R18

VSS#R17

VSS#R16

VSS#R15

VSS#R14

VSS#R13

VSS#R12

VSS#T13

VSS#T14

VSS#T15

VSS#W15

VSS#V16

VSS#V15

VSS#U15

VSS#U16

VSS#T19

VSS#T18

VSS#T17

VSS#T16

CENTER ARRAY

VDDCI#W16

VDDCI#M15

VDDCI#R19

VDDCI#T12

VDDC#W19

VDDC#M17

Part 5 of 6

CORE GND

PCIE_VSS#AA23

PCIE_VSS#AA24

PCIE_VSS#AA25

PCIE_VSS#AA26

PCIE_VSS#AA27

PCIE_VSS#AA28

PCIE_VSS#AB28

PCIE_VSS#AC28

PCIE_VSS#AD26

PCIE_VSS#AD27

PCIE_VSS#AD28

PCIE_VSS#AE28

PCIE_VSS#AF28

PCIE_VSS#AH29

1

M16

N16

N15

P15

P16

R18

R17

R16

R15

R14

R13

R12

T13

T14

T15

W15

V16

V15

U15

U16

T19

T18

T17

T16

W16

M15

R19

T12

W19

M17

VSS#AB8

VSS#AB7

VSS#AB1

VSS#AC4

VSS#AC12

VSS#AC14

VSS#AD16

VSS#AC16

VSS#AC18

VSS#AD18

VSS#AK2

VSS#AJ1

PCIE_VSS#K28

PCIE_VSS#L28

PCIE_VSS#M24

PCIE_VSS#M25

PCIE_VSS#M26

PCIE_VSS#M27

PCIE_VSS#M28

PCIE_VSS#N28

PCIE_VSS#P28

PCIE_VSS#R23

PCIE_VSS#R24

PCIE_VSS#R25

PCIE_VSS#R26

PCIE_VSS#R27

PCIE_VSS#R28

PCIE_VSS#T24

PCIE_VSS#T28

PCIE_VSS#U28

PCIE_VSS#V24

PCIE_VSS#V25

PCIE_VSS#V26

PCIE_VSS#V27

PCIE_VSS#V28

PCIE_VSS#W24

PCIE_VSS#W28

PCIE_VSS#Y28

AB8

AB7

AB1

AC4

AC12

AC14

AD16

AC16

AC18

AD18

AK2

AJ1

K28

L28

M24

M25

M26

M27

M28

N28

P28

R23

R24

R25

R26

R27

R28

T24

T28

U28

V24

V25

V26

V27

V28

W24

W28

Y28

AA23

AA24

AA25

AA26

AA27

AA28

AB28

AC28

AD26

AD27

AD28

AE28

AF28

AH29

+MPVDD

C52

C51

4.7uF

100nF

GND_MPVSS

5

402

4

3

2

MS-V031 / ATI X550 / DDRII

Size Document Number Rev

C

Tuesday, June 28, 2005

Date: Sheet

1

of

517

0A

www.vinafix.vn

Page 6

5

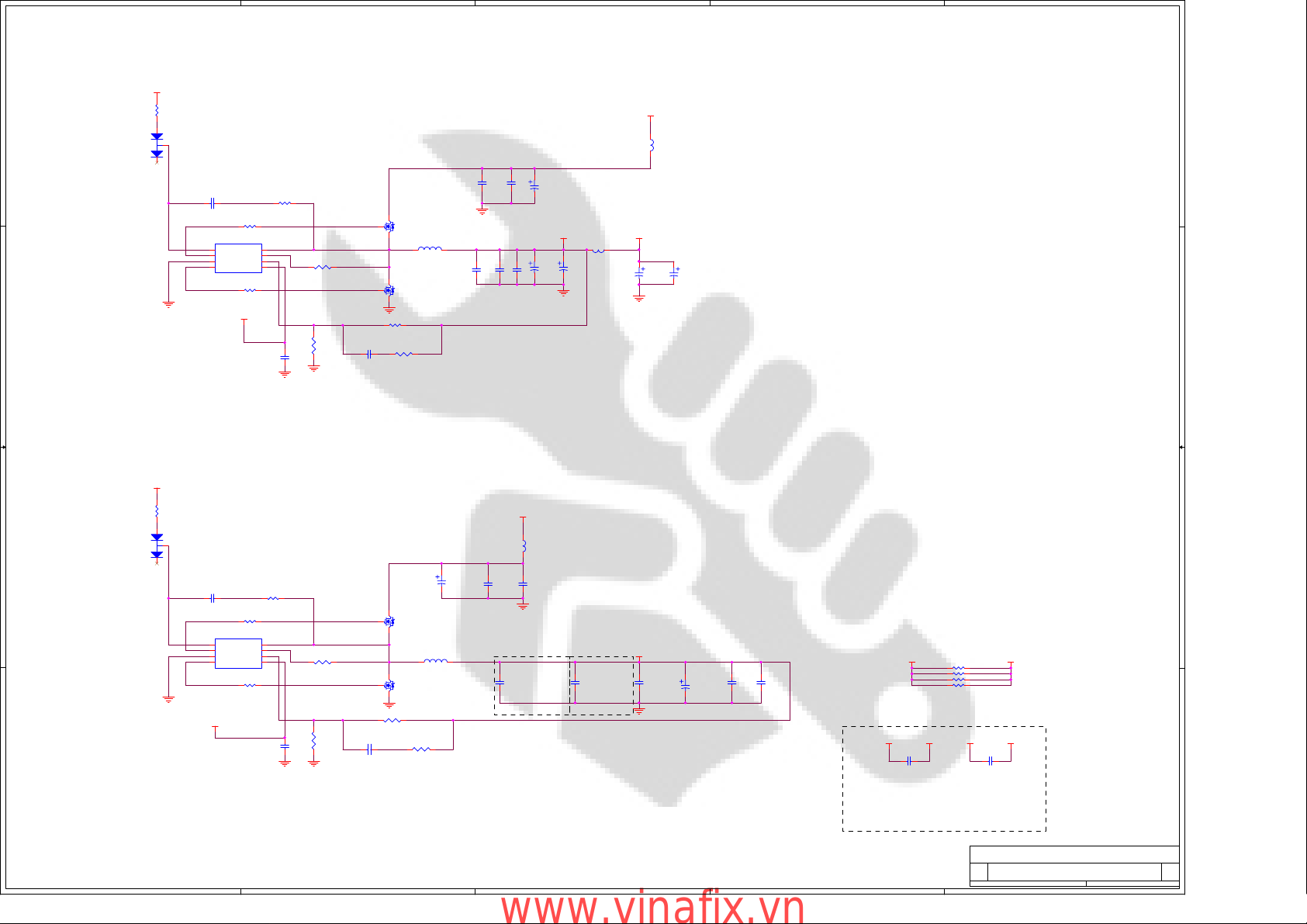

+12V_BUS

ER1593

D D

C C

1

2

2R2

ED1

BAT54SLT1

3

CORE REGULATOR VDDC

ER1592

2R2

PHASE

ER1618

2R2

+12V_BUS

ER1594

0R

8

7

OPS

6

FB

EC143

0.1uF

EC3

0.1uF

EMU31

1

BOOT

2

UGATE

3

GND

4 5

LGATE VCC

APW7120

N-APM3023N TO-252

ER6

19K

ER5

1.2KRF

4

EC1688

100nF

DS

G

DS

G

ER1686

698R

EQ23

(TO-252)

EL21

Dip 1.6uH

EQ21

(TO-252)

N-APM3023N TO-252

ER7

200RF

10uF

EC1532

1.0uF

EC116

EC1149

3

+12V_BUS

EB17

Chock 1.2u

EC117

10uF

EC301

470UF

+VDDC

EC323

820uF_6.3V

EC321

820uF_6.3V

EC1146

10uF

10uF

EB60

+PCIE_VDDR

60R

EC805

EC806

10u_10V

10u_10V

2

1

+VDDC=1.26V

APW7120 Application Circuit

+12V_BUS

ER1595

2R2

1

ED2

BAT54SLT1

B B

A A

3

2

EC124

0.1uF

1

2

3

4 5

+12V_BUS

ER307

EMU42

BOOT

UGATE

GND

LGATE VCC

APW7120

2R2

PHASE

ER308

2R2

ER1596

0R

8

7

OPS

6

FB

EC168

0.1uF

ER10

19K

ER13

1.2K

G

G

EC7

0.1uF

DS

EQ36

N-APM3023N TO-252

DS

EQ37

N-APM3023N TO-252

ER12

1.87K

(TO-252)

(TO-252)

ER11

200RF

EL64

Dip 1.6uH

EC108

470uF_10V

EC182

10uF

+12V_BUS

DNI

EC164

10uF

Cout1

EB16

Chock 1.2u

EC181

10uF

+MVDDC=2.0V

Dual footprint

EC159

10uF

DNI

+MVDDC

DNI

EC169

10uF

Dual footprint Dual footprintDual footprint

***

EC184

470uF_10V

***

C346

10uf

C347

10uf

ER104 0R

ER105 0R

ER106 0R

ER107 0R

+MVDDQ +MVDDC +MVDDQ +MVDDC

EC220

100nF

+MVDDC+MVDDQ

EC221

100nF

For EMI

APW7120 Application Circuit

MS-V031 / ATI X550 / DDRII

Size Document Number Rev

C

Tuesday, June 28, 2005

5

4

3

2

Date: Sheet

1

617

0A

of

www.vinafix.vn

Page 7

8

7

6

5

4

3

2

1

U101A

LM324M

1%

Rc1

U101B

1

LM324M

C110

1.0uF

7

Place caps very

close to power

pin

C120

100nF

R129 120R

R127 120R

R106 0R

1

+3.3V_BUS

1

Q102

MMBT2222ALT1

2 3

+3.3V_BUS

Q103

MMBT2222ALT1

2 3

C112

10uf

C123

10uf

+VDDC_CT

+A2VDD

C113

100nF

C124

100nF

+VDDC_CT = 1.55V

Iout = 70mA MAX

+A2VDD = 2.5V

Iout = 120mA MAX

+12V_BUS

EC1590

1.0uF

EC1663

10uF

+PCIE_VDDR

+5V

3 2

EREG29

LT1117CST

3 2

IN OUT

ADJ

1

ER1041

3.01K

1%

+5V regulator

L106 1.8uH

EREG8

3.3V

IN OUT

CASE

GND

1

4

CASE

Vin = 12v

Vout = 5V

+PCIE_PVDD_12

4

10u_10V

C108

2.2uF

EC1589

+5V

+RTAVDD

GND_RTGND_RTGND_RT GND_RT

ER1040

1.00K

1%

EC1591

1.0uF

EC183

DIP_220uF_10V

+PCIE_VDDR = 1.2V

Iout = 1200mA MAX

+12V_BUS

D D

R101 1.00K

1.0V_REF1

+3.3V_BUS

R124

APL431BAC_SOT23

15R

C109

EREG9

2

10uF_6.3V

DNI

3 1

R125

1.50K

1%

R126

1.00K

1%

2.5V_REF1

R1

1.0V_REF1

R2

Rc2

411

3

+

2

-

R102 825R

R103

1.50K

1%

Change to SOT-23

C C

2.5V_REF1

R105 1.00K

R107

3.32K

5

+

6

-

+3.3V_BUS

1.0V_REF1

R109 1.00K

B B

Rc2

12

ER113 1K

1.0V_REF1

A A

8

7

402

13

ER115

10K

402

Ry2

10

+

9

-

R111

1.50K

U101D

+

-

LM324M

ER114 301R

6

U101C

8

LM324M

R110 1.21K

Rc1

ER128 0R

14

402

Ry1

R128 120R

1%

1

DS

G

4

Q104

3 2

BCP68

EQ34

N-APM3023N TO-252

5

+PCIE_PVDD_18

C125

C126

10uf

100nF

+3.3V_BUS

ER1560REMR156

ER157

0R

805

***

EC306

470uF_10V

***

DUAL FOOTPRINT

5.8A continuous @ 70'C

58A pulse drain current @ 25'C

RDS(on) MA X = 50mR@Vgs=4.5V,Id=3.7A

550mW MAX

+PCIE_PVDD = 1.8V

Iout = 500mA MAX

+MVDDC

0R

0R

805

805

10u_10V

4

EMR157

EC315

+MVDDQ

***

EC305

470uF_10V

***

DUAL FOOTPRINT

C339

10uf

C340

10uf

3

+1.8V

+PCIE_PVDD_18

Rails derived from +1.8V

+PVDD

L103

L101

1.8uH

1.8uH

+AVDD: 10mA MAX

+A2VDDQ: 20mA MAX

+VDDOI_PINS: 20mA MAX

+TXVDDR_PINS: 20mA MAX

MS-V031 / ATI X550 / DDRII

Size Document Number Rev

C

Tuesday, June 28, 2005

Date: Sheet

2

+TPVDD

L102

1.8uH

+MPVDD

EL12

1.8uH

of

717

1

0A

www.vinafix.vn

Page 8

5

D D

4

3

2

1

TAKE OUT THE PARALLEL TERMINATION ON ADDRESS AND CONTROL

C C

CKEA(4,9)

CLKA#0(4,9)

B B

A A

5

CLKA0(4,9)

CLKA#1(4,9)

CLKA1(4,9)

R243

10K

R250 56R

C300

R251 56R R255 56R

R252 56R

R253 56R

10nF

C301

10nF R257 56R

4

3

CKEB(4,10)

R254 56R

CLKB#0(4,10)

CLKB0(4,10)

R256 56R

CLKB#1(4,10)

CLKB1(4,10)

R244

10K

C302

10nF

C303

10nF

MS-V031 / ATI X550 / DDRII

Size Document Number Rev

C

Tuesday, June 28, 2005

2

Date: Sheet

1

817

0A

of

www.vinafix.vn

Page 9

8

7

6

5

4

3

2

1

DQMA#[7..0]

DQMA#[7..0](4)

D D

MDA[63..0](4)

MAA[14..0](4)

C C

B B

DQMA#0

DQMA#1

DQMA#2

DQMA#3 QSA2

DQMA#4

DQMA#5

DQMA#6

MDA[63..0]

MAA[14..0]

CLKA#0(4,8)

CLKA0(4,8)

CKEA(4,8)

CSA#0(4)

WEA#(4)

RASA#(4)

CASA#(4)

VREF_A0 VREF_A0 VREF_A1

+MVDDQ +MVDDQ +MVDDQ

R300

4.99K

R301

4.99K

QSA[7..0](4)

MAA12

MAA13

MAA14

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1 MAA1

MAA0

DQMA#1

DQMA#0

ODTA0 ODTA0

QSA1

R320 10R

QSA0

R321 10R

VREF_U20 VREF_U21 VREF_U22 VREF_U23

C281

100nF

QSA[7..0]

U20

L2

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

CK

CKE

CS

WE VDDQ10

RAS

CAS

LDM

UDM

ODT

LDQS

LDQS

UDQS

UDQS

VREF

VSSQ10

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

HY5PS561621F-25

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSS1

VSS2

VSS3

VSS4

VSS5

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3 G9

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

R3

R7

R8

QSA0

QSA1

QSA3

QSA4

QSA5

QSA6DQMA#7

QSA7

U22

L2

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

VDDQ1

CK

VDDQ2

VDDQ3

VDDQ4

CKE

VDDQ5

VDDQ6

VDDQ7

CS

VDDQ8

VDDQ9

WE VDDQ10

RAS

CAS

LDM

UDM

VSSDL

ODT

LDQS

VSSQ1

LDQS

VSSQ2

VSSQ3

VSSQ4

VSSQ5

UDQS

UDQS

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VREF

VSSQ10

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

HY5PS561621F-25

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSS1

VSS2

VSS3

VSS4

VSS5

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3 G9

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

R3

R7

R8

L2

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3 G9

K7

L7

F3

B3

K9

QSA6

F7

E8

QSA7

B7

A8

J2

A2

E2

L1

R3

R7

R8

U23

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

CK

CKE

CS

WE VDDQ10

RAS

CAS

LDM

UDM

ODT

LDQS

LDQS

UDQS

UDQS

VREF

VSSQ10

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

HY5PS561621F-25

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSS1

VSS2

VSS3

VSS4

VSS5

R326 10R

R327 10R

R306

4.99K

R307

4.99K

C284

100nF

MAA12

MAA13

MAA14

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

CLKA#1

CLKA1

CKEA

CSA#0

WEA#

RASA#

CASA#

DQMA#6

DQMA#7

ODTA1

MDA34

B9

MDA36

B1

MDA33 MDA63

D9

MDA39

D1

MDA38

D3

MDA32

D7

MDA37

C2

MDA35

C8

MDA47

F9

MDA43

F1

MDA41

H9

MDA44

H1

MDA45

H3

MDA40

H7

MDA46

G2

MDA42

G8

A9

C1

C3

C7

C9

E9

G1

G3

G7

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

B302

220R

C226

100nF

+MVDDQ

B310

220R

DNI

C236

1uF

+MVDDC

VREF_A1

+MVDDQ

MDA58

B9

MDA60

B1

D9

MDA56

D1

MDA59

D3

MDA61

D7

MDA57

C2

DQ9

MDA62

C8

DQ8

MDA52

F9

DQ7

MDA51

F1

DQ6

MDA54

H9

DQ5

MDA48

H1

DQ4

MDA50

H3

DQ3

MDA53

H7

DQ2

MDA49

G2

DQ1

MDA55

G8

DQ0

A9

C1

C3

C7

C9

E9

G1

G3

G7

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

B303

220R

C246

100nF

+MVDDQ

B311

220R

DNI

C256

1uF

+MVDDC

QSA2

R2

M2

N7

N3

N8

N2

M7

M3

M8

R3

R7

R8

U21

L2

BA0

L3

P7

P3

P8

P2

K8

J8

K2

L8

K3 G9

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

HY5PS561621F-25

DQ15

BA1

DQ14

DQ13

A12

DQ12

A11

DQ11

A10/AP

DQ10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

VDDQ1

CK

VDDQ2

VDDQ3

VDDQ4

CKE

VDDQ5

VDDQ6

VDDQ7

CS

VDDQ8

VDDQ9

WE VDDQ10

RAS

VDD1

VDD2

VDD3

CAS

VDD4

VDD5

LDM

UDM

VDDL

VSSDL

ODT

LDQS

VSSQ1

LDQS

VSSQ2

VSSQ3

VSSQ4

VSSQ5

UDQS

UDQS

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VREF

VSSQ10

NC#A2

VSS1

NC#E2

VSS2

NC#L1

VSS3

NC#R3

VSS4

NC#R7

VSS5

NC#R8

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

CLKA#1(4,8)

CLKA1(4,8)

R324 10R

R325 10R

R304

4.99K

R305

4.99K

C283

100nF

MAA12

MAA13

MAA14

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA0

CKEA

CSA#0

WEA#

RASA#

CASA#

DQMA#5

DQMA#4

ODTA1

QSA5

QSA4

MDA20

B9

MDA19

B1

MDA23

D9

MDA16

D1

MDA17

D3

MDA22

D7

MDA18MDA5

C2

MDA21

C8

MDA30

F9

MDA27

F1

MDA29

H9

MDA25

H1

MDA24

H3

MDA26

H7

MDA28

G2

MDA31

G8

A9

C1

C3

C7

C9

E9

G1

G3

G7

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

B301

220R

C210

100nF

+MVDDQ

B309

220R

DNI

C216

1uF

+MVDDC

MDA3

B9

MDA4

B1

MDA0

D9

MDA7

D1

MDA6

D3

MDA1

D7

C2

MDA2

C8

MDA15

F9

MDA11

F1

MDA14

H9

MDA9

H1

MDA10

H3

MDA13

H7

MDA12

G2

MDA8

G8

A9

C1

C3

C7

C9

E9

G1

G3

G7

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

B300

220R

C200

100nF

+MVDDQ

B308

220R

DNI

C206

1uF

+MVDDC

R322 10R

R323 10R

R302

4.99K

R303

4.99K

C282

100nF

MAA12

MAA13

MAA14

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

CLKA#0

CLKA0

CKEA

CSA#0

WEA#

RASA#

CASA#

DQMA#3

DQMA#2

QSA3

+MVDDC

C208

100nF

C223

100nF

C228

100nF

C209

100nF

402402402

C224

100nF

C229

100nF

C225

100nF

C207

100nF

+MVDDQ

A A

C221

C222

100nF

100nF

402 402 402 402

402 402 402 402 402

+MVDDC +MVDDC

C227

100nF

402 402402

8

+MVDDQ

C231

100nF

402

+MVDDC

C217

100nF

402 402402

C232

100nF

C237

100nF

402 402402

7

C218

100nF

C233

100nF

C238

100nF

C219

100nF

C234

100nF

C239

100nF

C235

100nF

Put 1 1uF cap per power pin of m em o r y

+MVDDQ+MVDDQ

C205

C201

C202

100nF

100nF

402 402 402 402

402

6

C203

100nF

C204

100nF

100nF

C211

100nF

402

C213

C212

100nF

100nF

402 402 402 402

5

C214

100nF

C215

100nF

4

+MVDDQ +MVDDQ +MVDDQ +MVDDQ

R308

4.99K

ODTA0 VREF_A0 VREF_A1

3

ODTA1

R310

4.99K

2

R312

4.99K

R313

4.99K

MS-V031 / ATI X550 / DDRII

Size Document Number Rev

C

Tuesday, June 28, 2005

Date: Sheet

R314

4.99K

R315

4.99K

917

1

0A

of

www.vinafix.vn

Page 10

8

DQMB#[7..0]

DQMB#[7..0]

D D

MDB[63..0]

MAB[14..0]

C C

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

MDB[63..0]

MAB[14..0]

MAB12

MAB13

MAB14

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

CLKB#0

CLKB0

CKEB

CSB#0

WEB#

RASB#

CASB#

DQMB#1

DQMB#0

ODTB0

QSB1

R350 10R

VREF_B0

+MVDDQ

QSB0

R351 10R

R328

4.99K

VREF_U24 VREF_U25 VREF_U26 VREF_U27

R329

C285

4.99K

100nF

7

QSB[7..0]

QSB[7..0]

U24

L2

BA0

L3

BA1

R2

A12

P7

A11

M2

A10/AP

P3

A9

P8

A8

P2

A7

N7

A6

N3

A5

N8

A4

N2

A3

M7

A2

M3

A1

M8

A0

K8

CK

J8

CK

K2

CKE

L8

CS

K3 G9

WE VDDQ10

K7

RAS

L7

CAS

F3

LDM

B3

UDM

K9

ODT

F7

LDQS

E8

LDQS

B7

UDQS

A8

UDQS

J2

VREF

A2

NC#A2

E2

NC#E2

L1

NC#L1

R3

NC#R3

R7

NC#R7

R8

NC#R8

HY5PS561621F-25

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSS1

VSS2

VSS3

VSS4

VSS5

6

QSB0

QSB1

QSB2

QSB3

QSB4

QSB5

QSB6

QSB7

MDB3

B9

MDB7

B1

MDB0

D9

MDB4

D1

MDB5

D3

MDB1

D7

MDB6

C2

DQ9

MDB2

C8

DQ8

MDB11

F9

DQ7

MDB12

F1

DQ6

H9

DQ5

MDB15

H1

DQ4

MDB14

H3

DQ3

MDB9

H7

DQ2

MDB13

G2

DQ1

MDB10

G8

DQ0

A9

C1

C3

C7

C9

E9

G1

G3

G7

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

B304

220R

C260

100nF

+MVDDQ

B312

220R

DNI

C287

1uF

+MVDDC

VREF_B0

+MVDDQ

R352 10R

R353 10R

R330

4.99K

R331

4.99K

C286

100nF

MAB12

MAB13

MAB14

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

CLKB#0

CLKB0

CKEB

CSB#0

WEB#

RASB#

CASB#

DQMB#3

DQMB#2

ODTB0

QSB3

QSB2

L2

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3 G9

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

R3

R7

R8

U25

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

CK

CKE

CS

WE VDDQ10

RAS

CAS

LDM

UDM

ODT

LDQS

LDQS

UDQS

UDQS

VREF

VSSQ10

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

HY5PS561621F-25

5

MDB20

B9

DQ15

MDB19

B1

DQ14

MDB23

D9

DQ13

MDB16

D1

DQ12

MDB17

D3

DQ11

MDB21

D7

DQ10

MDB18

C2

DQ9

MDB22 MDB34

C8

DQ8

MDB24

F9

DQ7

MDB30

F1

DQ6

MDB29

H9

DQ5

MDB27

H1

DQ4

MDB25

H3

DQ3

MDB26

H7

DQ2

MDB28

G2

DQ1

MDB31

G8

DQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSS1

VSS2

VSS3

VSS4

VSS5

A9

C1

C3

C7

C9

E9

G1

G3

G7

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

B305

220R

C288

100nF

+MVDDQ

B313

220R

DNI

C289

1uF

+MVDDC

VREF_B1

+MVDDQ

4

MAB12

MAB13

MAB14

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

CLKB#1

CLKB1

CKEB

CSB#0

WEB#

RASB#

CASB#

DQMB#5 DQMB#7

DQMB#4

ODTB1

R354 10R

R355 10R

R332

4.99K

R333

C295

4.99K

100nF

U26

L2

BA0

L3

BA1

R2

A12

P7

A11

M2

A10/AP

P3

A9

P8

A8

P2

A7

N7

A6

N3

A5

N8

A4

N2

A3

M7

A2

M3

A1

M8

A0

K8

CK

J8

CK

K2

CKE

L8

CS

K3 G9

WE VDDQ10

K7

RAS

L7

CAS

F3

LDM

B3

UDM

K9

QSB5

QSB4 QSB6

ODT

F7

LDQS

E8

LDQS

B7

UDQS

A8

UDQS

J2

VREF

A2

NC#A2

E2

NC#E2

L1

NC#L1

R3

NC#R3

R7

NC#R7

R8

NC#R8

HY5PS561621F-25

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSS1

VSS2

VSS3

VSS4

VSS5

3

MDB35

B9

MDB36

B1

MDB32

D9

MDB39

D1

MDB38

D3

MDB33

D7

C2

DQ9

C8

DQ8

MDB43

F9

DQ7

MDB44

F1

DQ6

MDB40MDB8

H9

DQ5

MDB47

H1

DQ4

H3

DQ3

MDB41

H7

DQ2

MDB45

G2

DQ1

MDB42

G8

DQ0

A9

C1

C3

C7

C9

E9

G1

G3

G7

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

B306

220R

C266

100nF

+MVDDQ

B314

220R

DNI

C270

1uF

+MVDDC

VREF_B1

+MVDDQ

R356 10R

R357 10R

R334

4.99K

R335

4.99K

C296

100nF

2

MAB12

MAB13

MAB14

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

CLKB#1

CLKB1

CKEB

CSB#0

WEB#

RASB#

CASB#

DQMB#6

ODTB1

QSB7

U27

L2

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

CK

CKE

CS

WE VDDQ10

RAS

CAS

LDM

UDM

ODT

LDQS

LDQS

UDQS

UDQS

VREF

VSSQ10

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

HY5PS561621F-25

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSS1

VSS2

VSS3

VSS4

VSS5

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3 G9

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

R3

R7

R8

1

MDB52

B9

MDB50

B1

MDB55

D9

MDB48

D1

MDB49

D3

MDB54

D7

MDB51MDB37

C2

MDB53

C8

MDB60

F9

MDB59

F1

MDB63

H9

MDB56

H1

MDB57MDB46

H3

MDB62

H7

MDB58

G2

MDB61

G8

A9

C1

C3

C7

C9

E9

G1

G3

G7

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

B307

220R

C276

100nF

+MVDDQ

B315

220R

DNI

C280

1uF

+MVDDC

B B

+MVDDQ

R336

4.99K

ODTB0

+MVDDQ

A A

8

C242

C241

100nF

100nF

402 402 402 402

402

+MVDDC

C247

100nF

402 402402

C243

100nF

C248

100nF

C244

100nF

C249

100nF

C245

100nF

7

+MVDDQ

C251

100nF

402

+MVDDC

C252

100nF

C257

100nF

C253

100nF

C258

100nF

C254

C255

100nF

100nF

402402402402

C259

100nF

402 402402

6

+MVDDQ

C261

100nF

402 402

+MVDDC

C262

100nF

402

C267

100nF

402

C263

100nF

C268

100nF

5

C264

100nF

402

C269

100nF

+MVDDQ

C272

C271

C265

100nF

100nF

402 402402402

402

402402

C273

100nF

100nF

+MVDDC

C278

C277

100nF

100nF

402

402 402

4

C274

100nF

C279

100nF

C275

100nF

402

3

ODTB1

+MVDDQ

R337

4.99K

Size Document Number Rev

Date: Sheet

2

+MVDDQ +MVDDQ

R338

4.99K

VREF_B0 VREF_B1

R339

4.99K

MS-V031 / ATI X550 / DDRII

C

Tuesday, June 28, 2005

R340

4.99K

R341

4.99K

10 17

1

0A

of

www.vinafix.vn

Page 11

8

7

6

5

4

3

2

1

GPIO0

OPTION STRAPS

+3.3V_BUS

D D

C C

Mem_Strap0(3)

Mem_Strap1(3)

LCDDATA16(3)

B B

LCDDATA17(3)

VHAD0(3,15)

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO11

GPIO12

GPIO13

GPIO9

GPIO8

R201 10K DESKTOP

R202 10K MOBO

R203 10K DESKTOP

R204 10K MOBO

R205 10K DNI

R206 10K

R207 10K DNI

Tumwater

R208 10K COMMON

Grantsdale

R219 10K

R220 10K DNI

R221 10K DNI

R222 10K

R223 10K DNI

R224 10K

R209 10K DNI

R210 10K

R211 10K DNI

R212 10K

R213 10K

R214 10K DNI

R215 10K

R216 10K DNI

R217 10K DNI

R218 10K

R235 10K DNI

R236 10K

R237 10K DNI

R238 10K

R227 10K DNI

R228 10K

R229 10K DNI

R230 10K

R231 10K DNI

R232 10K

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

STRAPS

STRAP_B_PTX_PWRS_ENB

STRAP_B_PTX_DEEMPH_EN

PCIE_MODE(1:0)

STRAP_FORCE_COMPLIANCE

STRAP_B_PPLL_BW GPIO6

STRAP_DEBUG_ACCESS Strap to set the debug muxes to bring out DEBUG signals

ROMIDCFG(3:0)

STRAP P INTERRUPT

ENABLED (DEFAULT)

LOW

DISABLED

HIGH

GPIO[6..0]

GPIO[13..8]

GPIO[6..0] (3)

GPIO[13..8] (3)

DESCRIPTIONPIN

GPIO0

GPIO1

GPIO(3:2)

GPIO4

GPIO5

GPIO8

GPIO(9,13:11)

DVPDATA_20VIP_DEVICE Indicates if any slave VIP host devices drove this in low during reset.

(VHAD0 net)

Transmitter Power Savings Enable

0: 50% Tx output swing for mobile mode

1: full Tx output swing

Transmitter De-emphasis Enable

0: Tx de-emphasis disabled for mobile mode

1: Tx de-emphasis enabled

00: PCI Express 1.0A mode (Grantsdale)

01: Kyrene-compatible mode

10: PCI Express 1.0 mode (Tumwater)

11: PCI Express 1.0A mode and short-circuit internal loopback mode

(Rx connected directly to Tx of PHY)

Transmitter Extra Current

0: normal mode

1: extra current in Tx output stage - potential power savings for mobile mode

Force chip to go to Compliance state quickly for Tester purposes

0: normal operational mode

1: compliance mode

PLL Bandwidth

0: full PLL Bandwidth

1: reduced PLL bandwidth

even if registers are inaccessible.

If no ROM attached, comtrols chip IDis. If rom attached identifies ROM type

0000 - No ROM, CHG_ID=0

0001 - No ROM, CHG_ID=1

0100 - reserved

0110 - reserved

1000 - Parallel ROM, chip IDis from ROM

1001 - Serial AT25F1024 ROM (Atmel), chip IDis from ROM

1010 - Serial AT45DB011 ROM (Atmel), chip IDis from ROM

1011 - Serial M25P10 ROM (ST), chip IDis from ROM

1100 - Serial M25P05 ROM (ST), chip IDis from ROM

1100 - Serial NX25F011B ROM (ISSI), chip IDis from ROM

0 - Slave VIP host port devices present

1 - No slave VIP host port devices reporting presence during reset

ASIC DEFAULT

0

0

00

0STRAP_B_PTX_IEXT

0

0

0

MEMORY TYPE STRAPS

Mem_Strap0 Mem_Strap1

SAM

00

INF

HYN

ELPIDA

A A

8

7

6

5

0

1

0

1

11

STRAPS

4

PIN

3

+3.3V_BUS

R584

10K

402

PAL/NTSC (3)

R585

10K

402

DESCRIPTION

TVO Standard Default (Resistor pull-up and switch short to GND)LCDDATA18NTSC/PAL

0 - PAL (on board resistor pull-down and switch closed)

1 -NTSC (on board resistor pull-up)

MS-V031 / ATI X550 / DDRII

Size Document Number Rev

C

Tuesday, June 28, 2005

Date: Sheet

2

11 17

1

0A

of