Page 1

A B C

D

REVISIONS

1

SCHEMATIC TABLE OF CONTENTS

SHEET DESCRIPTION

1

2

TITLE PAGE

BLOCK DIAGRAM

REV

X00

X01

X02

X03

DESCRIPTIONECO DATE

Initial Prototype Release

Assembly drawing change only

pinout changes

adding buzzer

APPROVED

03/02/2005

04/26/2005

08/10/2005

10/10/2005

1

2

3

4

5

6

7

8

STACKUP

CD CONNECTOR

X16 PLANAR GOLDFINGER CONNECTOR

X8 PCIE CONNECTOR FOR INTERNAL SAS

CONTROL PANEL CONNECTOR, INTRUSION SWITCH

ROUTING RULES

IMPEDANCE COUPONS AND MOUNTING HOLES9

DB400 CLOCK BUFFER10

2

3

Berlin Sideplane

3

4

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY

OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN

WHOLE OR IN PART AND MUST BE RETURNED TO DELL INC.

UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE

OF THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED

FOR SUCH USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE

LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

JIM DUPUY

JIM DUPUY

ROBERT TUNG

PWA = N7190

PWB = N7186

ASSY = N7187

SCHEM = N7188

BUILD 0 = PRODUCTION

BUILD 1 = PROTOTYPE

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

TITLE

SCHEM,RSR,PE1950,SV,DELL

DWG NO.

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

INC.

ROUND ROCK,TEXAS

N7188

DATE

7/14/2005

SHEET

4

REV.

X02

1 OF 10

DCBA

Page 2

A B C

D

1

CD CONNECTOR

BLOCK DIAGRAM

1

PCI EXPRESS X16 GOLDFINGER

CONTROL PANEL CONNECTOR

PERC5 CONNECTOR

2

VIDEO

USB

2

PCI-EXP, I2C

OTHER CONTROL SIGNALS

IDE

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,RSR,PE1950,SV,DELL

N7188

SHEET

7/14/2005

DCBA

4

REV.

X02

2 OF 10

Page 3

A B C

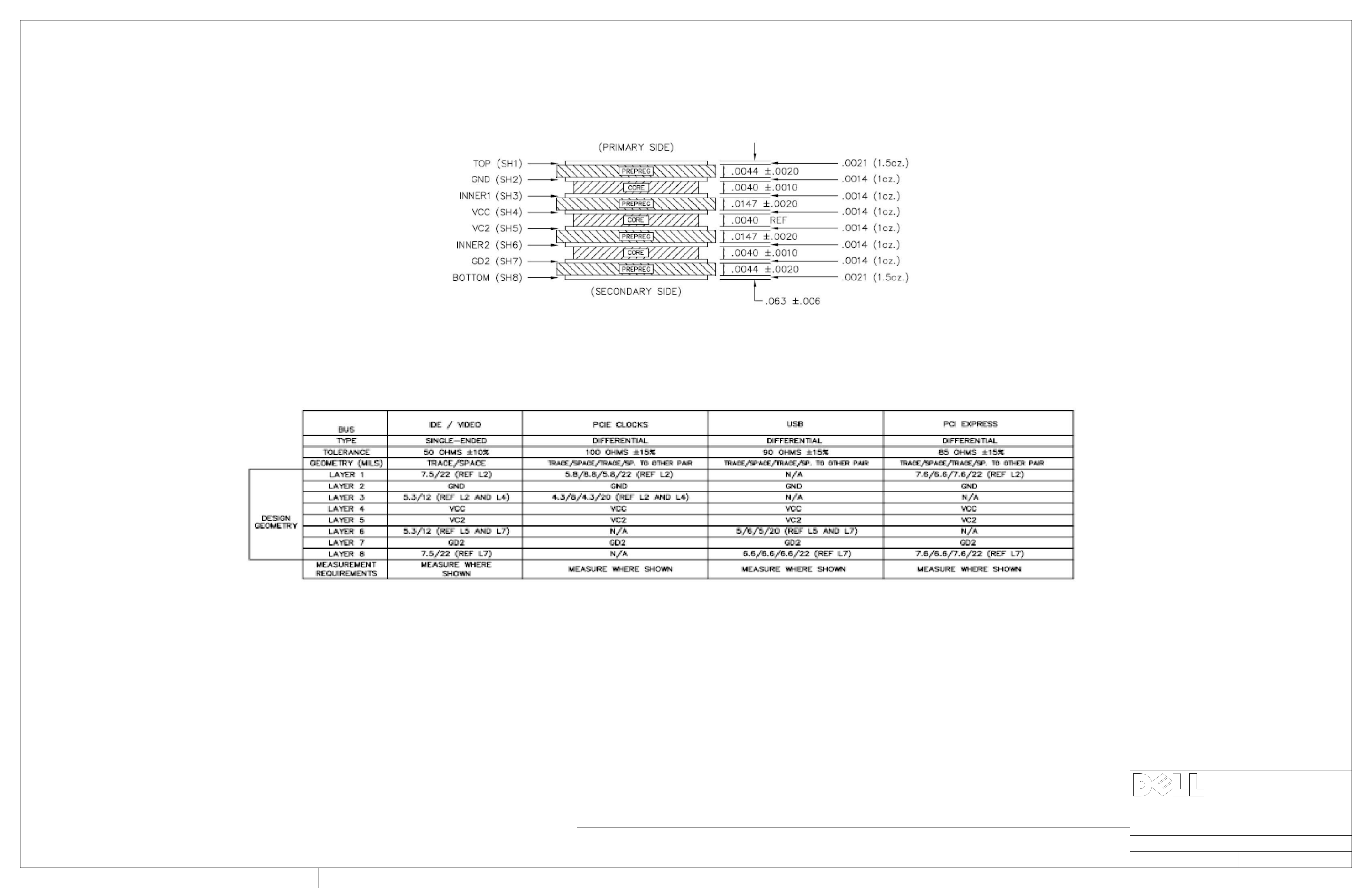

STACKUP

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,RSR,PE1950,SV,DELL

N7188

SHEET

7/14/2005

DCBA

4

REV.

X02

3 OF 10

Page 4

A B C

D

1

2

5-3/B

5-3/B

5-4/B

5-4/B

NP

X

C507

1

CD Connector

+5V+5V

J_IDE

5-3/B

5-3/B

5-3/B

5-3/B

5-3/B

5-3/B

5-3/B

5-3/B

5-3/B

5-3/B

IORDY pullup on IDE page

IRQ pullup on ESB page

NP

21

68pF

1 2

50V-5%

X

C505

68pF

NP

X

C506

50V-5%

68pF

1 2

50V-5%

5-4/B

5-4/B

5-4/D

5-4/D

CD_RST_N

IDE_PDD7

IDE_PDD6

IDE_PDD5

IDE_PDD4

IDE_PDD3

IDE_PDD2

IDE_PDD1

IDE_PDD0

IDE_PDDREQ

IDE_PDIOW_N

IDE_PDIOR_N

IDE_PDIORDY

IDE_PDDACK_N

IDE_IRQ14_N

IDE_PDA1

IDE_PDA0

IDE_PDCS1_N

NC_J_IDE_HDLED_N

1

3

5 6

7 8

9

11 12

13 14

15 16

17 18

19

21 22

23 24

25 26

27 28

29

31 32

33 34

35 36

37 38

39

41 42

43 44

2

4

10

20

30

40

IDE_PDD8

IDE_PDD9

IDE_PDD10

IDE_PDD11

IDE_PDD12

IDE_PDD13

IDE_PDD14

IDE_PDD15

NC_J_IDE_20

CDROM_PRES_N

NC_PIO16S_N

NC_IDE_P66_DET_N

IDE_PDA2

IDE_PDCS3_N

NC_J_IDE_44

5-3/D

5-3/D

5-3/D

5-3/D

5-3/D

5-3/D

5-3/D

5-3/D

5-2/D

5-4/D

5-4/D

pin 20 is not pulled like on standard connector

2

3

2x22 2MM VERT

SHR LATCH SLOT

ROOM = CD_CONN

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,RSR,PE1950,SV,DELL

REV.

N7188

SHEET

7/14/2005 4 OF 10

DCBA

4

X02

Page 5

A B C

SIDEPLANE_PRES_N

D

21

1

2

+12V

1 2

C3191

.1uF

16V-10%

21

C3187

.1uF

16V-10%

1 2

C3188

.1uF

16V-10%

21

C3189

.1uF

16V-10%

1 2

C3190

.1uF

16V-10%

6-3/B

6-3/B

7-3/D

7-3/C

7-3/C

7-3/C

6-3/B

6-3/B

7-2/B

6-3/B

6-3/B

6-4/B

6-4/B

6-4/B

6-4/B

4-2/B

4-3/B

I2C_BMC_PERC_VAUX_SCL

I2C_BMC_PERC_VAUX_SDA

USB_FRONT_N

USB_FRONT_P

NC_STORAGE_PWRGOOD

NC_B09

NC_B10

BTN_NMI_N

PS_ENABLE_CPLD_N

EXP_SB_0_P

EXP_SB_0_N

INTRUSION_COVER_N

EXP_SB_1_P

EXP_SB_1_N

EXP_SB_2_P

EXP_SB_2_N

EXP_SB_3_P

EXP_SB_3_N

CD_RST_N

IDE_PDDREQ

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

GND_B13

PETP0

PETN0

GND_B16

B17

GND_B18

PETP1

PETN1

GND_B21

GND_B22

PETP2

PETN2

GND_B25

GND_B26

PETP3

PETN3

GND_B29

B30

B31

GND_B32

P_EDGE

PRSNT1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

GND_A15

PERP0

PERN0

GND_A18

A19

GND_A20

PERP1

PERN1

GND_A23

GND_A24

PERP2

PERN2

GND_A27

GND_A28

PERP3

PERN3

GND_A31

A32

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

C3192

.1uF

16V-10%

NC_A02

CDROM_PRES_N

NC_ESB_USB_P6_N

NC_ESB_USB_P6_P

CTRLPNL_MUX_S0

CTRLPNL_MUX_S1

BTN_PWR_ON_N

BTN_ID_RAW_N

CK_100M_SRC_P

CK_100M_SRC_N

EXP_NB_0_P

EXP_NB_0_N

SAS_PERST_N

EXP_NB_1_P

EXP_NB_1_N

EXP_NB_2_P

EXP_NB_2_N

EXP_NB_3_P

EXP_NB_3_N

STORAGE_ADAPTER_PRES_N

4-3/C

7-4/C

7-4/D

7-3/C

7-3/D

10-4/B

10-4/B

6-3/C

6-3/C

6-3/C

6-4/C

6-4/C

6-4/C

6-4/C

6-4/C

6-4/C

6-5/B

1

For IDE contingency

was CK_100M_ROMB_P/N

2

3

4

+3.3V

21

C990

+3.3V_AUX

21

C3185

.1uF

16V-10%

.1uF

16V-10%

21

C349

21

C3186

.1uF

16V-10%

.1uF

16V-10%

21

C350

.1uF

16V-10%

21

C642

.1uF

16V-10%

1 2

C3193

.1uF

16V-10%

+5V_AUX

+5V

+3.3V_AUX

4-2/B

4-3/B

4-3/B

4-3/B

4-3/B

4-3/B

4-3/B

4-3/B

4-3/B

4-3/B

4-3/B

4-3/B

4-3/B

4-3/B

7-3/C

7-3/C

7-3/C

7-4/C

7-4/D

IDE_PDD7

IDE_PDD6

IDE_PDD5

IDE_PDD4

IDE_PDD3

IDE_PDD2

IDE_PDD1

IDE_PDD0

IDE_PDIOW_N

IDE_PDIOR_N

IDE_PDIORDY

IDE_PDDACK_N

IDE_IRQ14_N

IDE_PDA1

VIDFRONT_VS_OUT

VIDFRONT_RED

VIDFRONT_BLUE

CTRLPNL_CLK

CTRLPNL_DATA

+3.3V

B33

PETP4

B34

PETN4

B35

GND_B35

B36

GND_B36

B37

PETP5

B38

PETN5

B39

GND_B39

B40

GND_B40

B41

PETP6

B42

PETN6

B43

GND_B43

B44

GND_B44

B45

PETP7

B46

PETN7

B47

GND_B47

B48

B48

B49

GND_B49

B50

PETP8

B51

PETN8

B52

GND_B52

B53

GND_B53

B54

PETP9

B55

PETN9

B56

GND_B56

B57

GND_B57

B58

PETP10

B59

PETN10

B60

GND_B60

B61

GND_B61

B62

PETP11

B63

PETN11

B64

GND_B64

B65

GND_B65

B66

PETP12

B67

PETN12

B68

GND_B68

B69

GND_B69

B70

PETP13

B71

PETN13

B72

GND_B72

B73

GND_B73

B74

PETP14

B75

PETN14

B76

GND_B76

B77

GND_B77

B78

PETP15

B79

PETN15

B80

GND_B80

B81

PRSNT2_X16

B82

B82

GND_A34

GND_A37

GND_A38

GND_A41

GND_A42

GND_A45

GND_A46

GND_A49

GND_A51

GND_A54

GND_A55

GND_A58

GND_A59

GND_A62

GND_A63

NOT STANDARD PCI EXPRESS PINOUT (TRIATHLON SPECIFIC)

GND_A66

GND_A67

GND_A70

GND_A71

GND_A74

GND_A75

GND_A78

GND_A79

GND_A82

16X CARD EDGE CONNECTOR

SUB=NO_PKG

A33

PERP4

PERN4

PERP5

PERN5

PERP6

PERN6

PERP7

PERN7

A50

PERP8

PERN8

PERP9

PERN9

PERP10

PERN10

PERP11

PERN11

PERP12

PERN12

PERP13

PERN13

PERP14

PERN14

PERP15

PERN15

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

IDE_PDD8

IDE_PDD9

IDE_PDD10

IDE_PDD11

IDE_PDD12

IDE_PDD13

IDE_PDD14

IDE_PDD15

CK_PWRDN_N

IDE_PDA2

IDE_PDCS3_N

IDE_PDA0

IDE_PDCS1_N

CTRLPNL_PRES_N

FRONT_MONITOR_PRES_N

I2C_VIDFRONT_5V_SCL

I2C_VIDFRONT_5V_SDA

VIDFRONT_HS_OUT

VIDFRONT_GREEN

I2C_BMC_SEG3_VAUX_SCL

I2C_BMC_SEG3_VAUX_SDA

+5V

+12V

4-2/C

4-3/C

4-3/C

4-3/C

4-3/C

4-3/C

4-3/C

4-3/C

10-3/B

4-3/C

4-3/C

4-3/B

4-3/B

7-4/C

7-3/E

7-3/C

7-3/D

7-3/C

7-3/C

7-3/C

7-3/D

+3.3V

+5V

21

C3181

+5V_AUX

21

C3184

.1uF

16V-10%

.1uF

16V-10%

TITLE

21

C3182

.1uF

16V-10%

21

C3183

.1uF

16V-10%

INC.

21

C3180

.1uF

16V-10%

1 2

C3195

ROUND ROCK,TEXAS

.1uF

16V-10%

1 2

C3194

.1uF

16V-10%

3

4

ROOM=PCIE_ROMB

PCI EXPRESS GOLDFINGER CONNECTOR

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

SCHEM,RSR,PE1950,SV,DELL

DWG NO.

N7188

DATE

7/14/2005

DCBA

REV.

X02

SHEET

5 OF 10

Page 6

1

A B C

PCI EXPRESS CONNECTOR

FOR INTERNAL SAS

(PERC5/I OR SAS HBA/emb)

6-3/C

6-3/C

6-3/C

6-3/B

STORAGE_JTAG_TMS

STORAGE_JTAG_TDI

STORAGE_JTAG_TCK

STORAGE_JTAG_TRST_N

D

R39

4.7K-5%

R38

1 2

4.7K-5%

R37

4.7K-5%

R36

1 2

+3.3V

21

1

21

2

5-2/B

5-2/B

6-2/D

+3.3V_AUX

I2C_BMC_PERC_VAUX_SCL

I2C_BMC_PERC_VAUX_SDA

STORAGE_JTAG_TRST_N

NC_ROMB_WAKE_N

B1

+12V_1

B2

+12V_2

B3

+12V_5

B4

GND_B4

B5

SMCLK

B6

SMDATA

B7

GND_B7

B8

+3.3V_1

B9

JTAG_TRST

B10

+3.3V_AUX

B11

WAKE

J_PCIE_STORAGE

PRSNT1

+12V_3

+12V_4

GND_A4

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

+3.3V_2

+3.3V_3

PERST

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

+12V

+3.3V

STORAGE_JTAG_TCK

STORAGE_JTAG_TDI

NC_STORAGE_JTAG_TDO

STORAGE_JTAG_TMS

SAS_PERST_N

6-2/D

6-2/D

6-2/D

5-2/D

4.7K-5%

2

+12V

3

5-2/B

5-2/B

5-2/B

5-2/B

5-3/B

5-3/B

5-3/B

5-3/B

NC_RSVD_B12

EXP_SB_0_P

EXP_SB_0_N

NC_PRSNT2_N_X1

EXP_SB_1_P

EXP_SB_1_N

EXP_SB_2_P

EXP_SB_2_N

EXP_SB_3_P

EXP_SB_3_N

NC_ROMB_RSVD_B30

NC_EXP_ROMB_PRSNT2_N_X4

B12

RSVD_B12

B13

GND_B13

B14

PETP0

B15

PETN0

B16

GND_B16

B17

PRSNT2_X1

B18

GND_B18

B19

PETP1

B20

PETN1

B21

GND_B21

B22

GND_B22

B23

PETP2

B24

PETN2

B25

GND_B25

B26

GND_B26

B27

PETP3

B28

PETN3

B29

GND_B29

B30

RSVD_B30

B31

PRSNT2_X4

B32

GND_B32

GND_A12

REFCLK+

REFCLKGND_A15

PERP0

PERN0

GND_A18

RSVD_A19

GND_A20

PERP1

PERN1

GND_A23

GND_A24

PERP2

PERN2

GND_A27

GND_A28

PERP3

PERN3

GND_A31

RSVD_A32

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

CK_100M_ROMB_P

CK_100M_ROMB_N

EXP_NB_0_P

EXP_NB_0_N

NC_RSVD_A19

EXP_NB_1_P

EXP_NB_1_N

EXP_NB_2_P

EXP_NB_2_N

EXP_NB_3_P

EXP_NB_3_N

NC_RSVD_A32

10-4/C

10-4/C

5-2/D

5-2/D

5-2/D

5-2/D

5-3/D

5-3/D

5-3/D

5-3/D

1 2

C3175

.1uF

16V-10%

21

C3176

.1uF

16V-10%

+3.3V

21

C3179

1 2

C3177

.1uF

16V-10%

.1uF

16V-10%

21

C3168

21

C3178

.1uF

16V-10%

.1uF

16V-10%

1 2

C3196

1 2

C3136

.1uF

16V-10%

.1uF

16V-10%

3

5-3/D

NC_B33

NC_B34

NC_B37

NC_B38

NC_B41

NC_B42

NC_B45

NC_B46

STORAGE_ADAPTER_PRES_N

Pulled up on planar

B33

PETP4

B34

PETN4

B35

GND_B35

B36

GND_B36

B37

PETP5

B38

PETN5

B39

GND_B39

B40

GND_B40

B41

PETP6

B42

PETN6

B43

GND_B43

B44

GND_B44

B45

PETP7

B46

PETN7

B47

GND_B47

B48

PRSNT2_X8

B49

GND_B49

RSVD_A33

GND_A34

PERP4

PERN4

GND_A37

GND_A38

PERP5

PERN5

GND_A41

GND_A42

PERP6

PERN6

GND_A45

GND_A46

PERP7

PERN7

GND_A49

PCI-E X8 CONNECTOR

PCI-E SPECIFICATION 1.1

SILKSCREEN=INT_STORAGE

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

NC_RSVD_A33

NC_A35

NC_A36

NC_A39

NC_A40

NC_A43

NC_A44

NC_A47

NC_A48

+3.3V_AUX

21

C820

.1uF

16V-10%

4

ROOM=PCIE_ROMB

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,RSR,PE1950,SV,DELL

N7188

SHEET

DCBA

4

REV.

X02

6 OF 107/14/2005

Page 7

A B C

INTRUSION SWITCH

D

1

INTRUSION

2

4 3

SWITCH

SPST PUSH BUTTON

1

INTRUSION_COVER_N

When lid is closed, switch is open

Shorted (0) = Intruded

Open (1) = Not Intruded

1

5-2/B

2

5-4/D

5-4/D

5-2/B

5-4/D

5-4/B

5-4/B

5-4/D

5-4/B

5-2/D

5-2/B

5-2/B

5-4/B

5-2/D

5-4/D

I2C_BMC_SEG3_VAUX_SCL

I2C_VIDFRONT_5V_SCL

PS_ENABLE_CPLD_N

VIDFRONT_HS_OUT

VIDFRONT_VS_OUT

VIDFRONT_RED

VIDFRONT_GREEN

VIDFRONT_BLUE

BTN_PWR_ON_N

BTN_NMI_N

USB_FRONT_P

CTRLPNL_CLK

CTRLPNL_MUX_S0

CTRLPNL_PRES_N

+3.3V_AUX

+3.3V

CONTROL PANEL CONNECTOR

+5V_AUX

+5V

+5V

+3.3V

J_CTRL

1

3

5 6

7 8

9

11 12

13 14

15 16

17 18

19

21 22

23 24

25 26

27 28

29

31 32

33 34

35 36

37 38

39

2

4

10

20

30

40

I2C_BMC_SEG3_VAUX_SDA

I2C_VIDFRONT_5V_SDA

NC_J_CTRL_10

FRONT_MONITOR_PRES_N

BTN_ID_RAW_N

USB_FRONT_N

NC_J_CTRL_30

CTRLPNL_DATA

CTRLPNL_MUX_S1

5-4/D

5-4/D

5-2/D

5-2/B

5-4/B

5-2/D

NP

C3170

X

2

5-4/D

.1uF

1 2

16V-10%

3

2x20 2MM VERT

SHR LATCH SLOT

3

NEW 40 PIN CONNECTOR PINOUT

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

INC.

TITLE

SCHEM,RSR,PE1950,SV,DELL

DWG NO.

N7188

DATE

7/14/2005

DCBA

4

ROUND ROCK,TEXAS

REV.

X02

SHEET

7 OF 10

Page 8

A B C

D

1

1

BERLIN SIDEPLANE

GENERAL ROUTING RULES & PLACEMENT:

--> ANY NON-PCI-E AND NON-USB SIGNAL NOT MENTIONED BELOW CAN BE ROUTED WITH A 5 MIL TRACE WIDTH (OUTER LAYERS)

AND A 5 MIL SPACING TO THE NEXT SIGNAL

--> PLEASE PLACE ALL TOTEM POLE RESISTORS ON TOP OF ONE ANOTHER

--> THE FOLLOWING NETS SHOULD HAVE A TRACE WIDTH OF AT LEAST 50 MILS:

5V, 12V, 3.3V

2

--> PLEASE PLACE 470PF CAPS (C57-C60) DIRECTLY OFF OF MUX POWER PINS.

--> PLEASE PLACE 1UF and 10UF CAPS (C43,C56) AS CLOSE AS POSSIBLE TO REGULATOR (U2).

2

PCI-E AND USB CHANNEL SIGNALS' ROUTING RULES:

3

--> THERE ARE 8 TOTAL PCI-E CHANNEL SIGNALS, A PAIR (+ AND -) FOR EACH OF THE FOLLOWING NET NAMES

SB AND NB

--> PCI-E, CLOCKS AND USB DIFF PAIRS SHOULD BE ROUTED ONLY ON TOP AND BOTTOM LAYERS REFERENCING GND PLANE.

--> AVOID VIAS. ANY VIAS ON THESE SIGNALS MUST BE APPROVED BY THE BOARD DESIGNER

--> THE + AND - SIGNAL OF A DIFFERENTIAL PAIR MUST BE ROUTED PARALLEL TO ONE ANOTHER THROUGHOUT THE SIGNAL.

--> THE LENGTHS OF THE + AND - SIGNAL WITHIN A DIFFERNTIAL PAIR SHOULD NOT DIFFER BY MORE THAN 5 MIL FROM SOURCE TO DESTINATION

--> PAIR TO PAIR SPACING SHOULD BE A MINIMUM OF 30 MILS (OUTER LAYERS).

--> SEE ADDITIONAL NOTES IN ECAD ROUTING GUIDELINES DOCUMENT.

3

--> AVOID ROUTING OVER SPLITS, SLOTS OR VIA CLEARANCES.

--> KEEP ONE GROUND/RETURN PATH VIA TO LESS THAN 50 MIL (OR AS PHYSICALLY CLOSE AS POSSIBLE) TO ONE SIGNAL VIA.

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

N7188

7/14/2005

DCBA

4

INC.

ROUND ROCK,TEXAS

SCHEM,RSR,PE1950,SV,DELL

REV.

X02

SHEET

8 OF 10

Page 9

A B C

IMPEDANCE COUPONS AND MOUNTING HOLES

D

VOLTAGE PROPERTY ALLOCATION

1

IMPEDANCE COUPONS

CLOCK

PROPAGATION_DELAY=L:S:5995:6005

PROPAGATION_DELAY=L:S:5995:6005

Z_TOP_D100

2

+

41

-

PROPAGATION_DELAY=L:S:5995:6005

NP*

RX

RY

3

ZDI4PINS2R

COUPON TEST

IMP_Z100D_TOP_P

IMP_Z100D_TOP_N

1

1

Z_TOP_D100_END

2

2

3

3

4

NP*

IMPEDENCE DIFFERENTIAL

4

TEST POINT

1

3

NP*

1

3

NP*

PROPAGATION_DELAY=L:S:5995:6005

Z_IN2_D90

RX

RY

ZDI4PINS2R

COUPON TEST

PROPAGATION_DELAY=L:S:5995:6005

PROPAGATION_DELAY=L:S:5995:6005

Z_BOT_D90

RX

RY

ZDI4PINS2R

COUPON TEST

USB

+3.3V

RATSNEST_SCHEDULE=MIN_TREE

VOLTAGE=3.3

MH4

1

+5V

RATSNEST_SCHEDULE=MIN_TREE

VOLTAGE=5

1

1

2

+

4

-

2

+

4

-

IMP_Z90D_IN2_P

IMP_Z90D_IN2_N

IMP_Z90D_BOT_P

IMP_Z90D_BOT_N

Z_IN2_D90_END

2

2

3

3

4

NP*

IMPEDENCE DIFFERENTIAL

NP*

IMPEDENCE DIFFERENTIAL

4

TEST POINT

1

1

Z_BOT_D90_END

2

2

3

3

4

4

TEST POINT

+12V

RATSNEST_SCHEDULE=MIN_TREE

VOLTAGE=12

+5V_AUX

RATSNEST_SCHEDULE=MIN_TREE

VOLTAGE=5

+3.3V_AUX

RATSNEST_SCHEDULE=MIN_TREE

VOLTAGE=3.3

RATSNEST_SCHEDULE=MIN_TREE

VOLTAGE=0

2

3

4

5

6

7

8

9

.140 DRILL

.310 PAD

8 GND VIAS

SUB=NO_PKG

MH5

2

3

4

5

6

7

8

9

.140 DRILL

.310 PAD

8 GND VIAS

SUB=NO_PKG

ADD*_FG703_LATCH

ADD*_HF606_PLSCRW1

ADD*_HF606_PLSCRW2

ADD*_94682_M3SCRW1

ADD*_94682_M3SCRW2

ADD*_RC649_FORMEX1

ADD*_TC345_FORMEX2

ADD*_PC909_BRKTASSY

ADD*_CC462_GDEBLK

ADD*_T6977_GDBLKSCR

ADD*_KC408_CD_CBL

ADD*_NC071_CP_CBL

ADD*_N7186_PWB

ADD*_N7187_ASSY_DWG

ADD*_N7188_SCHEM

ADD*_42610_PPID

ADD*_42753_REV

2

PROPAGATION_DELAY=L:S:5995:6005

Z_IN1_D100

IMP_Z100D_IN1_P2

IMP_Z100D_IN1_N

NP*

RX

RY

3

ZDI4PINS2R

COUPON TEST

+

41

-

50 OHM TRACES (PCI, IDE, MISC)

PROPAGATION_DELAY=L:S:5995:6005

Z_TOP_50

NP*

3

RY

ZSE3PINS2R

COUPON TEST

21

+RX

IMP_TOP_50

1

1

Z_IN1_D100_END

2

2

3

3

4

NP*

IMPEDENCE DIFFERENTIAL

4

TEST POINT

Z_TOP_50_END

1

1

2

2

3

3

IMPEDENCE SINGLE END

TEST POINT

NP*

NP*

PROPAGATION_DELAY=L:S:5995:6005

PROPAGATION_DELAY=L:S:5995:6005

Z_TOP_D85

RX

RY

3

ZDI4PINS2R

COUPON TEST

2

PCIE

1

1

Z_TOP_D85_END

2

+

41

-

IMP_Z85D_TOP_P

IMP_Z85D_TOP_N

NP*

IMPEDENCE DIFFERENTIAL

2

2

3

3

4

4

TEST POINT

3

PROPAGATION_DELAY=L:S:5995:6005

NP*

PROPAGATION_DELAY=L:S:5995:6005

NP*

Z_IN1_50

1 2

3

RY

ZSE3PINS2R

COUPON TEST

Z_IN2_50

1 2

3

RY

ZSE3PINS2R

COUPON TEST

+RX

+RX

IMP_IN1_50

IMP_IN2_50

Z_IN1_50_END

1

1

2

2

3

3

IMPEDENCE SINGLE END

TEST POINT

Z_IN2_50_END

1

1

2

2

3

3

IMPEDENCE SINGLE END

TEST POINT

NP*

NP*

NP*

PROPAGATION_DELAY=L:S:5995:6005

PROPAGATION_DELAY=L:S:5995:6005

Z_BOT_D85

RX

RY

3

ZDI4PINS2R

COUPON TEST

3

1

1

Z_BOT_D85_END

2

+

41

-

IMP_Z85D_IN1_P

IMP_Z85D_IN1_N

NP*

IMPEDENCE DIFFERENTIAL

2

2

3

3

4

4

TEST POINT

4

PROPAGATION_DELAY=L:S:5995:6005

NP*

Z_BOT_50

3

RY

ZSE3PINS2R

COUPON TEST

21

+RX

IMP_BOT_50

Z_BOT_50_END

1

1

2

2

3

3

IMPEDENCE SINGLE END

TEST POINT

NP*

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

SCHEM,RSR,PE1950,SV,DELL

N7188

7/14/2005

DCBA

4

INC.

ROUND ROCK,TEXAS

REV.

X02

SHEET

9 OF 10

Page 10

A B C

D

8-2-2005_8:37

1

+3.3V

NP

C3201

X

10-1/B,10-3/B

NP

BLM18BD601SN1_PB

NP

BLM18BD601SN1_PB

21

.1uF

16V-10%

V_3P3_SRC

L2

L1

21

X

21

X

NP

C3200

X

V_3P3_SRC

NP

21

.1uF

1 2

16V-10%

X

C3209

NP

21

C3206

X

10uF 6.3V

.1uF

16V-10%

NP

C3205

X

NP

21

.1uF

1 2

C3204

X

16V-10%

NP

.1uF

16V-10%

1 2

C3202

X

NP

.1uF

C3203

X

16V-10%

21

.1uF

16V-10%

10-2/A,10-3/B

R11

NP

1 2

0-5%

R12

NP

0-5%

X

21

X

1

CK_100M_DIF2_P

CK_100M_DIF2_N

2

NP

R8

X

0 = Disable output 1/6

1 = Enable Output 1/6

21

NP

21

R7

X

8.2K-5%

NP

R3

X

8.2K-5%

NP

R18

X

NP

21

1 2

0 = High BW

1 = Low BW

21

R5

X

8.2K-5%

NP

21

R10

X

8.2K-5%

NP

21

R6

X

8.2K-5%

NP

21

R9

X

8.2K-5%

NP

21

R4

X

8.2K-5%

0 = Bypass (fan-out)

1 = PLL (Zero Delay Buffer)

8.2K-5%

8.2K-5%

+3.3V

NP

21

C3208

X

10-1/B,10-2/A

NP

BLM18BD601SN1_PB

.1uF

16V-10%

L3

5-3/D

21

X

NP

DB400_SRC_BYPASS_PLL

DB400_HIGH_BW_N

DB400_CK_OE

CK_100M_SRC_IN_P

CK_100M_SRC_IN_N

DB400_SRC_STOP_N

DB400_SCLK NC_CK_100M_DIF6_N

DB400_SDA

CK_PWRDN_N

V_3P3_SRC

V_3P3_VDDA_SRC

NP

C3207

X

1 2

.1uF

16V-10%

NP

C3199

X

1 2

4.7uF

6.3V-10%

12 6

BYPASS/PLL DIF_1

17

HIGH_BW

8

OE_1

21

OE_6

2

SRC_IN

3

SRC_IN

16

SRC_STOP

13

SCLK

14

SDATA

15

PD

1

VDD_1

5

VDD_5

11

VDD_11

18

X

VDD_18

24

VDD_24

28

VDDA_28

U_DB400

GNDA_27

ICS9DB104 FOUR

OUTPUT BUFFER

DB400 Buffer

DIF_1

DIF_2

DIF_2

DIF_5

DIF_5

DIF_6

DIF_6

IREF

GND_4

GND_25

7

9

10

20

19

23

22

26

4

25

27

NC_CK_100M_DIF1_P

NC_CK_100M_DIF1_N

CK_100M_DIF2_P_R

CK_100M_DIF2_N_R

CK_100M_DIF5_P_R

CK_100M_DIF5_N_R

NC_CK_100M_DIF6_P

DB400_IREF

NP

R33

475-1%

21

X

NP

NP

R27

33-5%

R26

33-5%

21

X

NP

21

X

NP

R31

33-5%

R30

33-5%

21

X

21

X

CK_100M_DIF2_P

CK_100M_DIF2_N

CK_100M_DIF5_P

CK_100M_DIF5_N

NP

R24

X

1 2

NP

R23

X

49.9-1%

21

49.9-1%

NP

R20

X

1 2

NP

R21

X

49.9-1%

2

21

49.9-1%

3

50 ohm

If clock buffer is used, we want 0 1 1

DB400

INOUT

33 ohm

5-2/D

5-2/D

CK_100M_SRC_P

CK_100M_SRC_N

R14

0-5%

3

21

R13

1 2

0-5%

CK_100M_ROMB_P

CK_100M_ROMB_N

6-3/D

6-3/D

4

To PERC

R11/R12

2 1

R13/R14

12

SRC

If using DB400:

Connect R14.1 to R11.1 with 0 ohm

Connect R13.1 to R12.1 with 0 ohm

Connect R14.2 to R11.2 with 0 ohm

Connect R13.2 to R12.2 with 0 ohm

If bypassing DB400:

Populate R13 and R14 with 0 ohm

Gold finger

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DB400 100MHZ CLOCK REPEATER

INC.

TITLE

SCHEM,RSR,PE1950,SV,DELL

DWG NO.

N7188

DATE

ROUND ROCK,TEXAS

REV.

X02

SHEET

10 OF 107/14/2005

4

DCBA

Loading...

Loading...