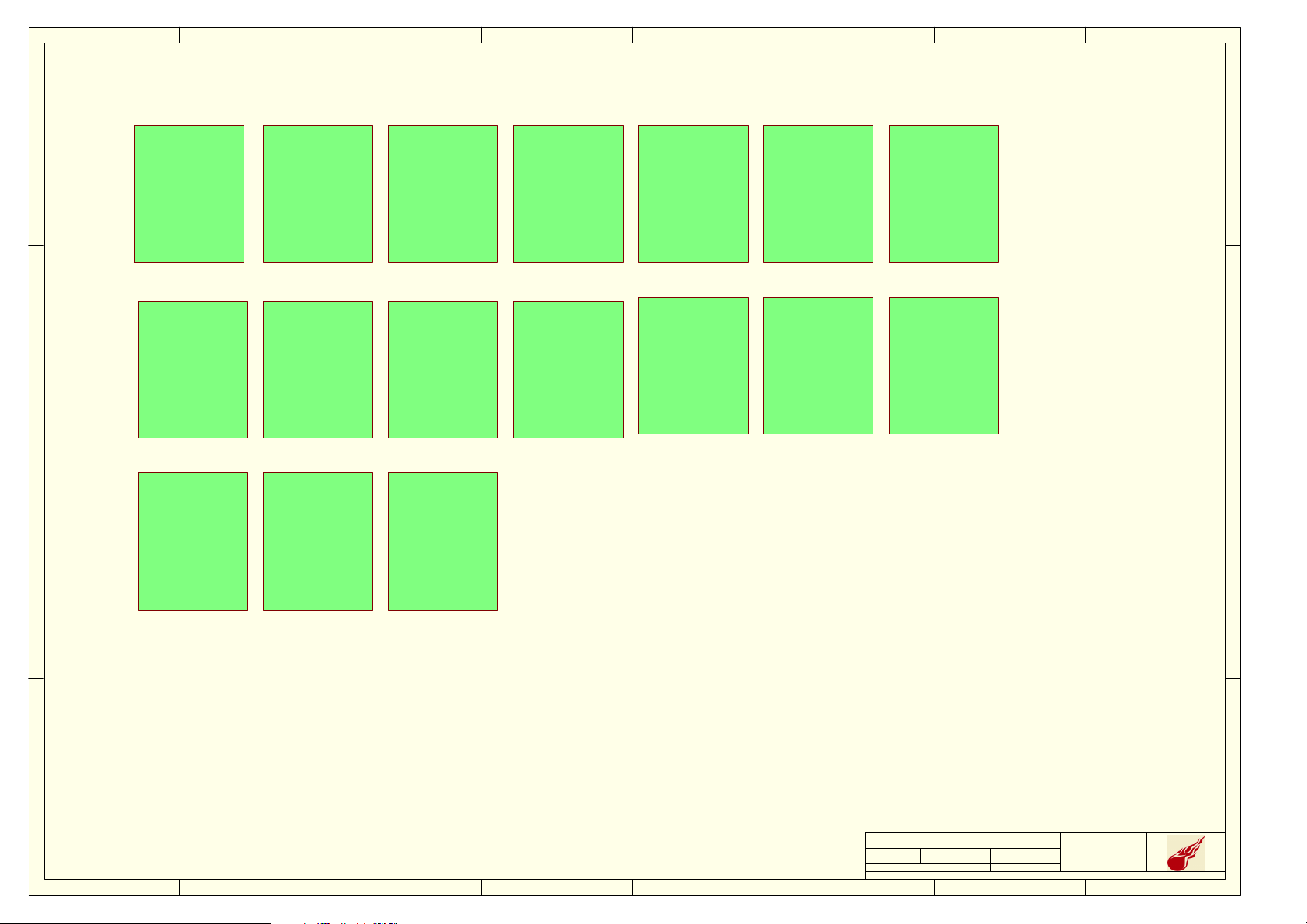

Page 1

87654321

D

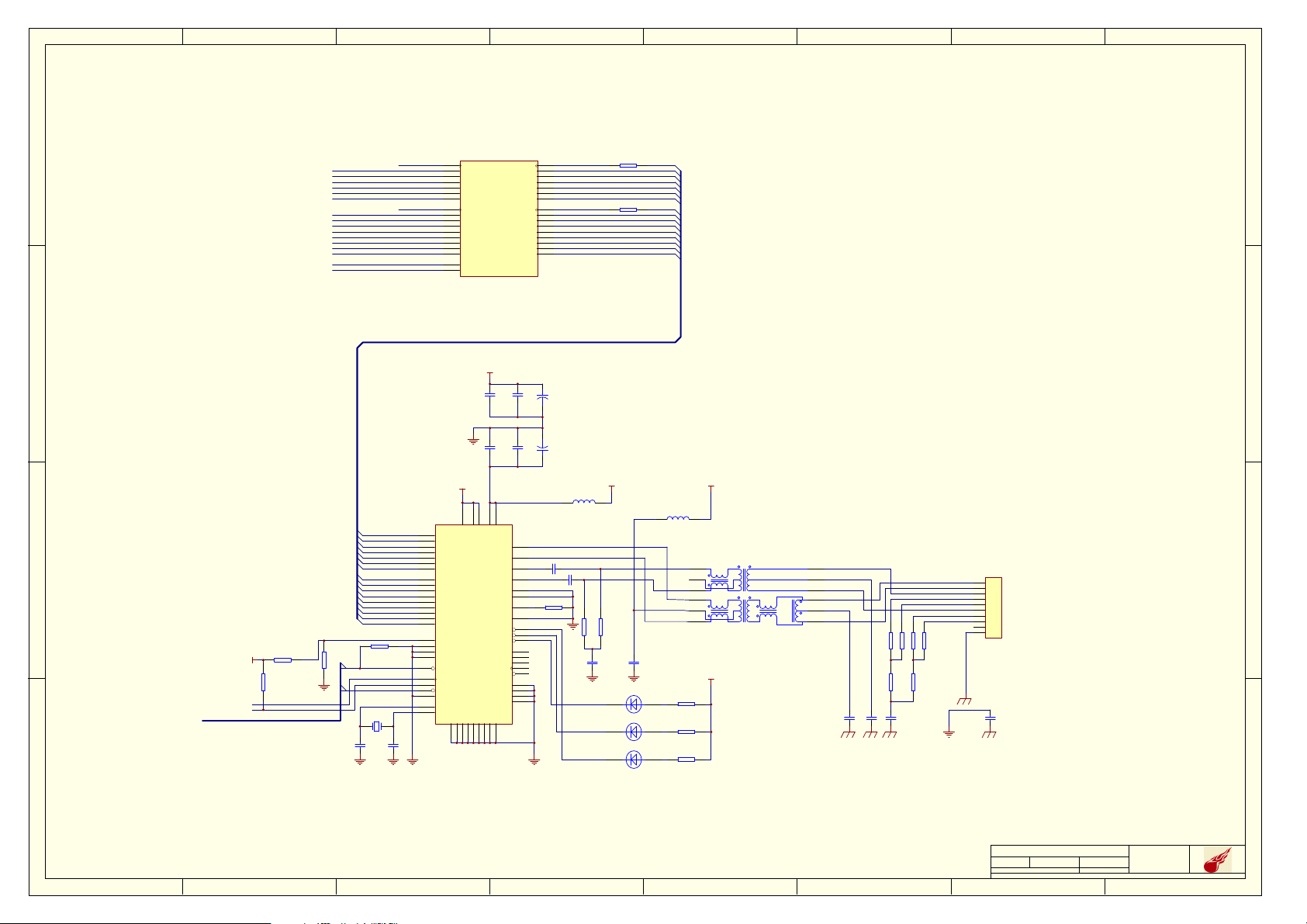

KIM_MSI-01-DIMMCON.Sch

DIMMCON

File Name

C

Name

KIM_MSI-15-VSC_SDRAM.Sch

VSC_SDRAM

B

KIM_MSI-02-PPCPower.Sch

KIM_MSI-03-FLASH.Sch

PPCPower

KIM_MSI-09-ETH.Sch File Name

ETH

KIM_MSI-16-USB.Sch

KIM_MSI-17-DVI.Sch

USB 2.0

FLASH

DVI

KIM_MSI-04-SDRAM.Sch

SDRAM

KIM_MSI-11-VSC.Sch

VSC

File Name

KIM_MSI-06-IO.Sch

KIM_MSI-07-PCI.Sch

IO

KIM_MSI-13-VSCPwr.Sch File Name

VSCPwr

D

PCI

C

B

A

Title

KIM MSI

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI.Sch

Revision:

Sheet of

0 0Date: 29-Jun-2005

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

A

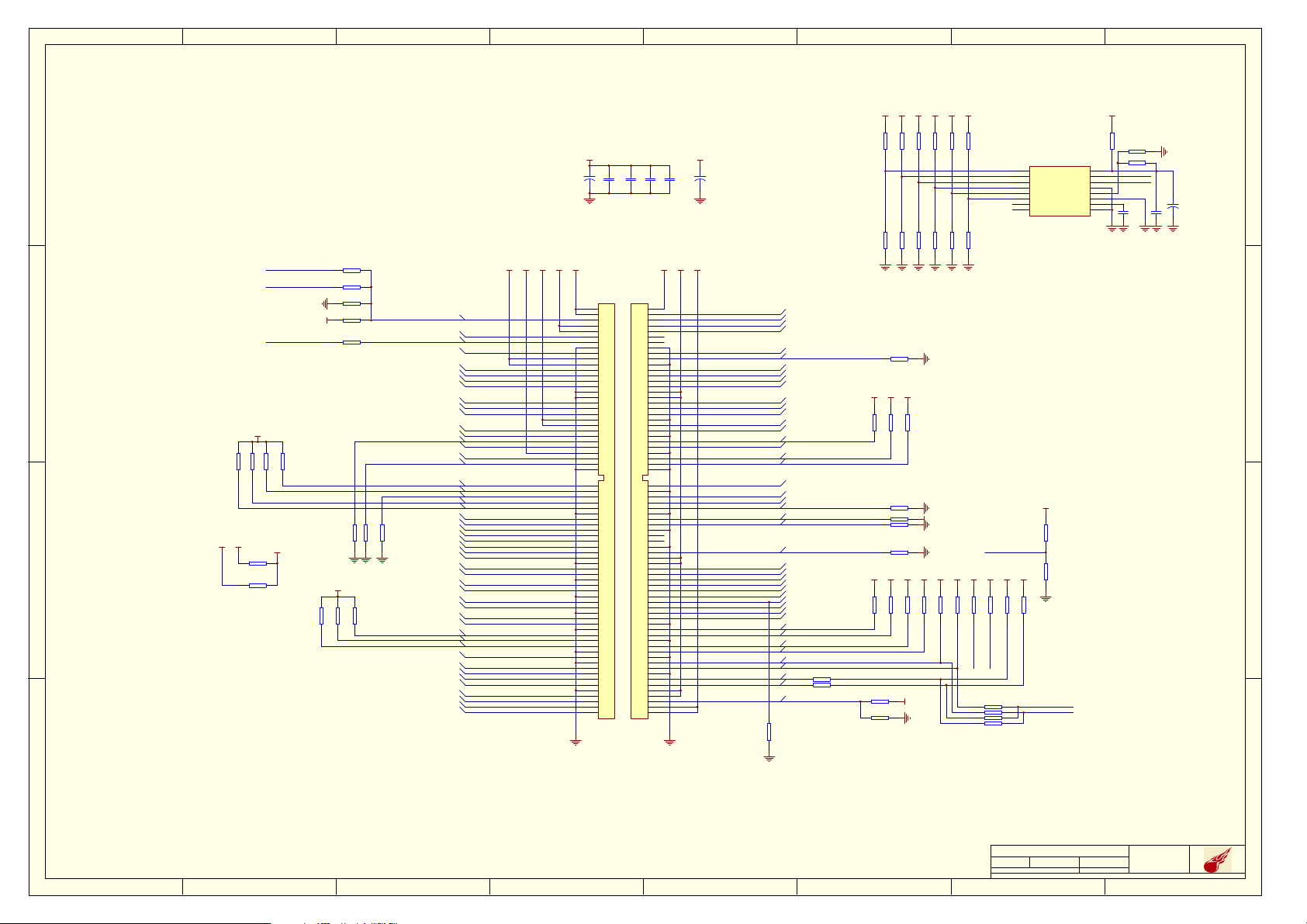

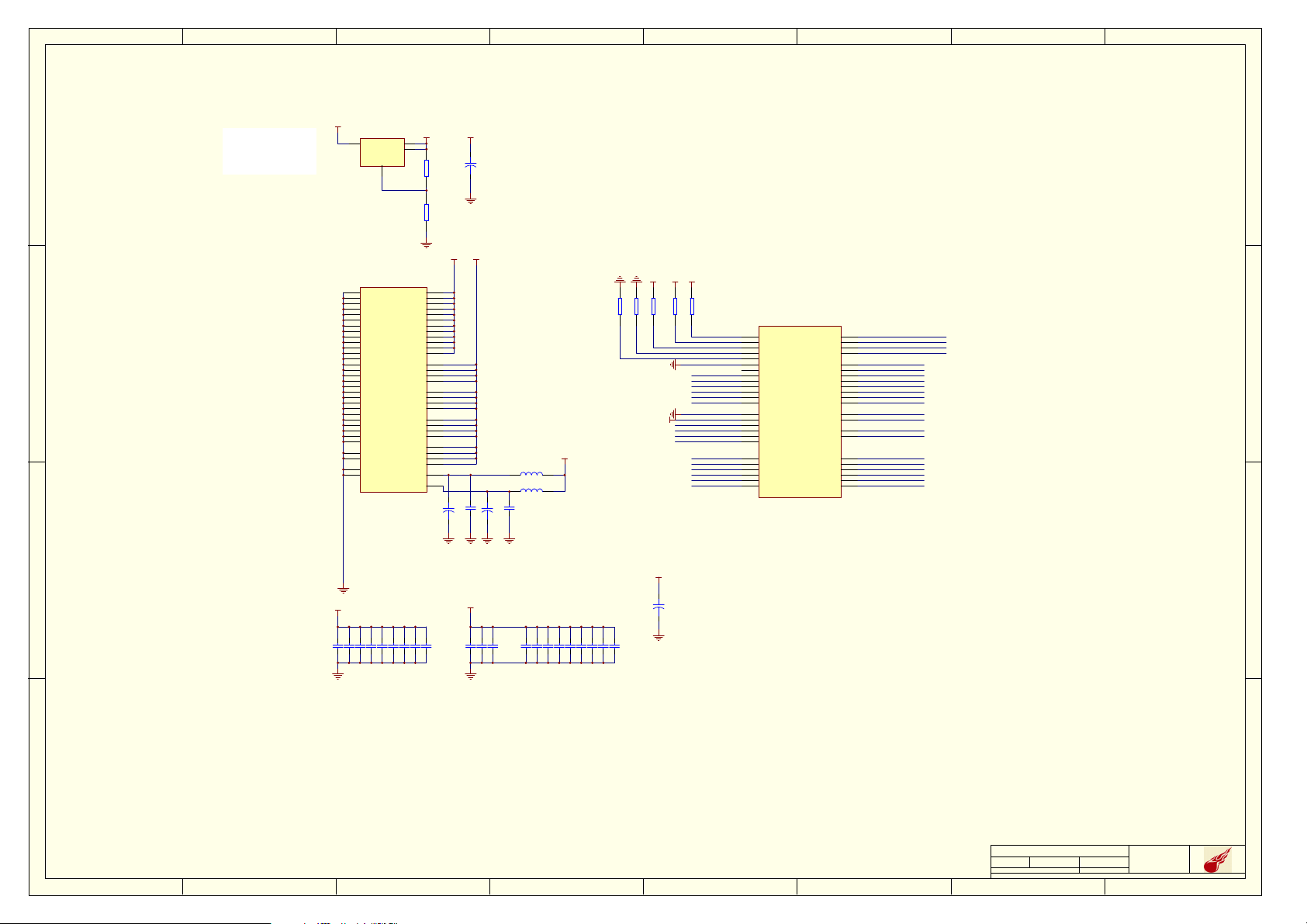

Page 2

87654321

1/10

1/10

1/10

1/2

1/2

R149

1.8k(1%)

R148

200(1%)

+3.3V

1/2

+3.3V

VBAT

+3.3VM

R150

R151

R157

1k8k(1%)

180k(1%)

1k8k(1%)

R145

R152

R158

1k8(1%)

180k(1%)

1k8(1%)

+PS2

+3.3V

+3.3V

+3.3V

R117

R118

R119

open

R129

open

open

open

I2C4_DATA

R143

R144

R141

R142

+3.3V

R130

open

I2C4_CLOCK

ADC0

ADC1

ADC2

ADC3

ADC4

ADC5

EXT_GPIO3

+3.3V

0

0

open

open

R139

open

U100

1

CH0

2

CH1

3

CH2

4

CH3

5

CH4

6

CH5

7

CH6

8

CH7

ADS7830IPWT

+3.3V

R140

open

I2C0_CLOCK_PPC

I2C0_DATA_PPC

+3.3V

R156

open

R159

3k3

+12V

+5VS

+5V

R134

R124

+3.3V

R132

R108

R128

R133

+3.3V

I2C0_DATA

I2C0_CLOCK

R120

open

R112

open

R135

1k8(1%)

1k8(1%)

R146

R147

200(1%)

200(1%)

10k

+3.3V

+3.3V

R104

R110

R111

10k

open

open

4k7

open

open

4k7

+3.3V

+3.3V

R114

R115

R116

open

open

open

+3.3V

D

+3.3V +3.3V

10u/10V

C803

+

C805

C807

100n

100n

+3.3V

R160

0

R136

open

R109

open

R113

open

R121

open

R126

R125

10k

10k

+PS2

R107

R106

R105

open

open

open

BMC_RST_BTN#

BMC_RST#

BMC_PWR_BTN#

BMC_SECURE_MODE_KB#

BMC_SPKR#

BMC_ID_BTN#

FD_WRITE_PROTECT#

BIOS_SELECT

BMC_NMI_BTN#

VIDEO_BLANK

SIO_KB_CLK

SIO_KB_DATA

KM_INHB

SIO_MS_CLK

SIO_MS_DATA

R127

10k

PS2_KB_DATA

PS2_MS_CLK

PS2_MS_DATA

nc

CARD_PRESNT_R

BMC_CARD_PRESENCE2

/MASTER_RESET

C

+PS2

R103

R102

R101

R100

open

open

open

open

+3.3V+5VS

+PS2

R122

B

open

R123

0

+3.3VM

BMC_CARD_PRESENCE1

EXT_GPIO28

EXT_GPIO29

EXT_GPIO31

TACHO_IN4

TACHO_IN5

TACHO_IN6

TACHO_IN7

EXT_GPIO26

EXT_GPIO12

EXT_GPIO32

EXT_GPIO10

EXT_GPIO18

EXT_GPIO21

EXT_GPIO6

FML_SINTEX

EXT_GPIO19

PWM_OUT1

PWM_OUT2

EXT_GPIO5

PWM_OUT3

PWM_OUT6

/U0_DCD

U0_RX_MSI

/U0_RTS

/U0_DSR

U0_TX_MSI

/U0_CTS

/U0_DTR

/U0_RI

Rx2+

Rx2-

Rx1+

Rx1-

Rx0+

Rx0-

RxC+

RxC-

PWM_OUT7

PWM_OUT4

PWM_OUT5

LPC_CLK

LAD0

LAD1

LAD2

LAD3

LFRAME#

LPCPD#

LDRQ#

LRESET#

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

J100A

SO-DIMM-144_PINS

SO-DIMM-144_PINS

J100B

C812

C811

100n

100n

+12V+3.3V +3.3V +5VS +5V +3.3V +5VS

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

10u/10V

+

C804

EXT_GPIO27

EXT_GPIO25

EXT_GPIO13

EXT_GPIO24

PWM_OUT0BMC_SLP_BTN#

EXT_GPIO30

TACHO_IN0

TACHO_IN1

TACHO_IN2

TACHO_IN3

EXT_GPIO9

EXT_GPIO8

VBAT

I2C4_DATA

I2C4_CLOCK

EXT_GPIO34

FML_SD

FML_MD

FML_CLK

CLK32K_RTC

EXT_GPIO1

EXT_GPIO20

EXT_GPIO16

EXT_GPIO14

EXT_GPIO0

EXT_GPIO2

EXT_GPIO33

EXT_GPIO3

EXT_GPIO4

EXT_GPIO17

EXT_GPIO22

EXT_GPIO23

GPIO9

EXT_GPIO15

EXT_GPIO7

EXT_GPIO11

I2C3_DATA

I2C3_CLOCK

I2C2_DATA

I2C2_CLOCK

I2C1_DATA

I2C1_CLOCK

I2C0_DATAR

I2C0_CLOCKR

BMC_CARD_PRESENCE2

PCI_I2C

PCI_I2C

LAN_I2C

LAN_I2C

I2C3

I2C3

I2C2

I2C2

I2C1

I2C1

IPMB

IPMB

R131

open

BMC_SYSRDY_LED

FP_COOL_FLT_LED

FP_SYSFLT_LED

BMC_ID_LED

BMC_FAN_CTL

CHIPSET_PWRGD

MEM_ERR_ALERT#

RST_PWRGD_PS

nc

LAN1_SMBALT#

nc

CHIPSET_SLP_S5#

CHIPSET_PWR_BTN#

BNC_NMI

PS2_KB_CLK

SIO_COM_ISOLATE

BMC_SYSIRQ

BMC_SMI#

RST_PWRON_PS#

SMI_INPUT#

BMC_CLR_CMOS#

RST_REQ#

LAN_ALTRST#

RS232 DRV_EN

BMC_SCI#

BMC_SWI#

FRB3_TIMER_HALT#

R137

R138

nc

PPC GPIO !!

100

100

REF_in/out

+3.3V

R153

4R7

R154

0

open

R155

16

Vdd

15

I2C0_DATA_PPC

SDA

14

I2C0_CLOCK_PPC

SCL

13

A1

12

A0

11

COM

10

9

GND

C100

100n

C102

+

10u/6V3

C101

100n

D

C

B

A

Title

KIM-DIMMCON

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI-01-DIMMCON.Sch

Revision:

1 1

Sheet of

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

1 0Date: 29-Jun-2005

A

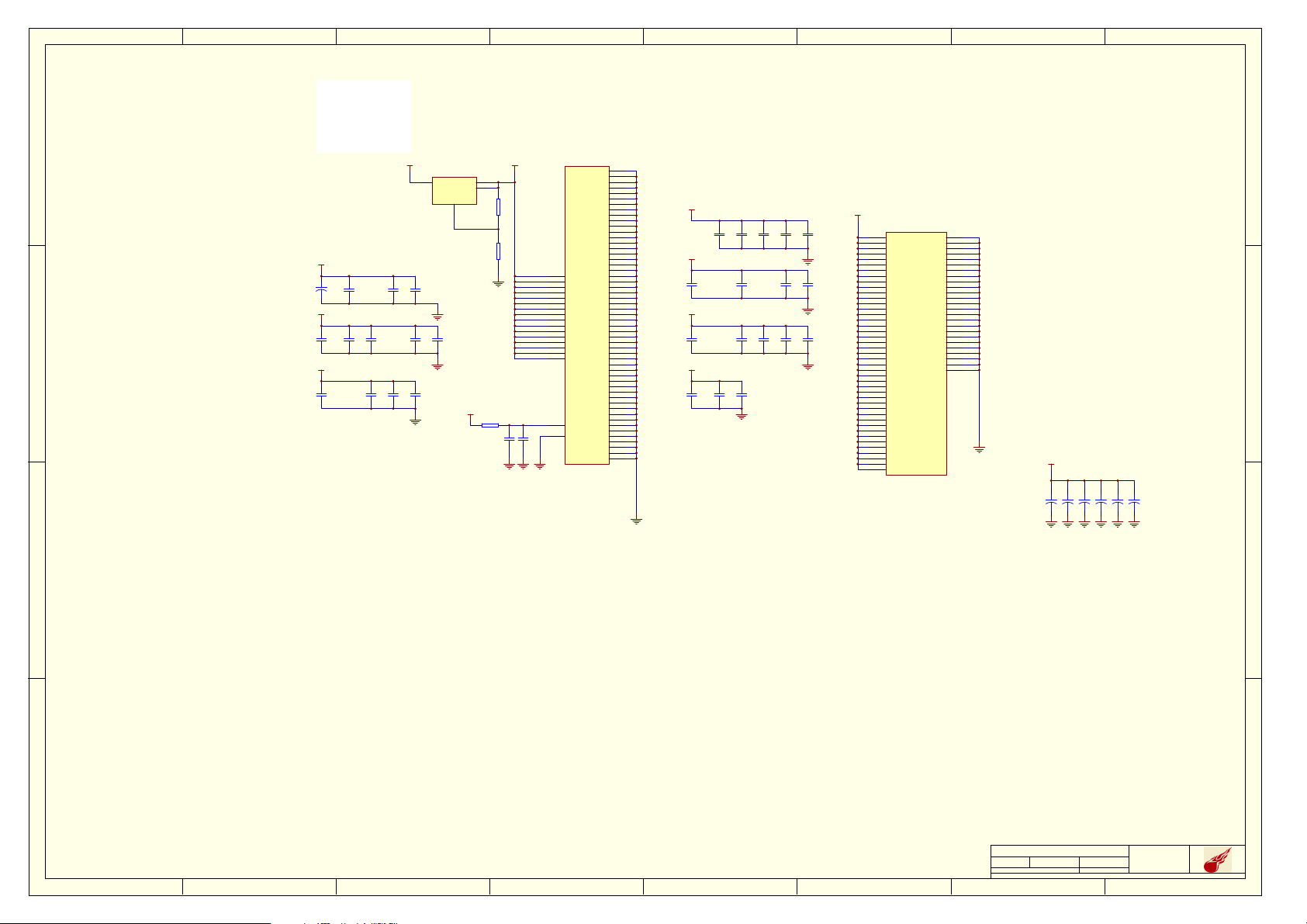

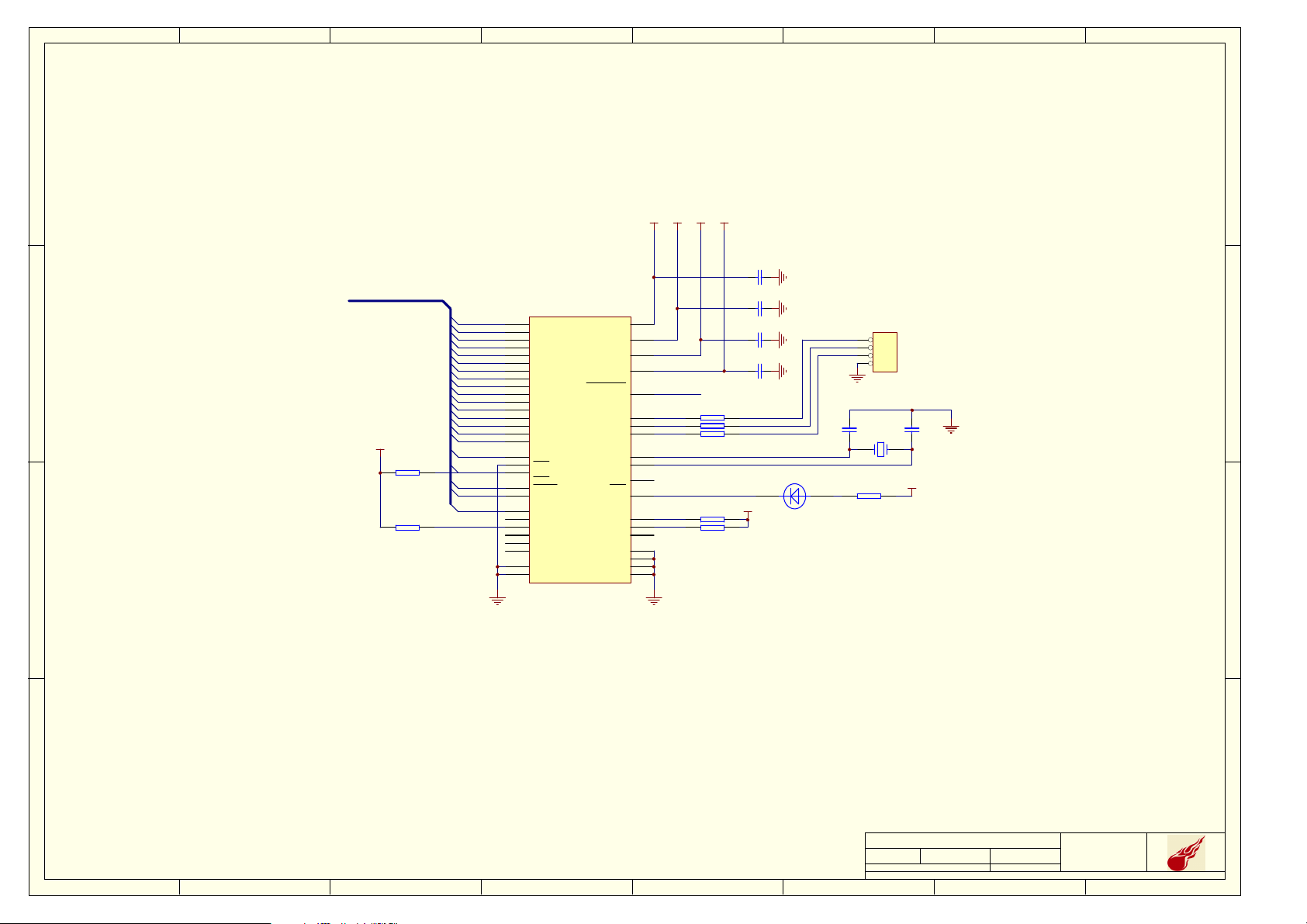

Page 3

87654321

VREF = 1.25

Iadj = 35uA

Vout - 1.25

R2 = ----------------- (1.25 / R1 + Iadj)

für 1.8V

R2/ R1 = 0.44

D

für 1.5V

R2/ R1 = 0.2

+1.8V

C242

+

C201

10u/10V

100n

+1.8V

C200

C202

100n

C

+1.8V

100n

C228

100n

V OUT = V REF (1+R202/R201) + I ADJ * R202

+3.3V +1.8V

U200

FAN1117ASX

3

Vin

1

C205

C207

100n

100n

C204

C208

100n

C230

100n

C210

100n

100n

C231

C232

100n

100n

ADJ/GND

U200_ADJ

D

U201A

2

Vout

4

Vout

R201

270

R202

120

E10

VDD

E11

VDD

E13

VDD

E14

VDD

K5

VDD

K19

VDD

L5

VDD

L19

VDD

N5

VDD

N19

VDD

P5

VDD

P19

VDD

W10

VDD

W11

VDD

W13

VDD

W14

VDD

+1.8V

R200

0

C247

10n

AC20

AVDD

AVDD

AB21

AGND

C234

100n

PPC405EP

A1

GND

A2

GND

A7

GND

A12

GND

A17

GND

A22

GND

A23

GND

B1

GND

B2

GND

B22

GND

B23

GND

C3

GND

C21

GND

D4

GND

D20

GND

E5

GND

E9

GND

E12

GND

E15

GND

E19

GND

G1

GND

G23

GND

J5

GND

J19

GND

M1

GND

M5

GND

M19

GND

M20

GND

M23

GND

R5

GND

R19

GND

U1

GND

U23

GND

W5

GND

W9

GND

W12

GND

W15

GND

W19

GND

Y4

GND

Y20

GND

AA3

GND

AA21

GND

AB1

GND

AB2

GND

AB22

GND

AB23

GND

AC1

GND

AC2

GND

AC7

GND

AC12

GND

AC17

GND

AC22

GND

AC23

GND

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

C213

C216

C219

C222

100n

100n

C217

100n

C212

100n

C235

100n

C220

100n

C218

100n

C237

C238

100n

100n

C225

100n

100n

100n

C221

C224

100n

100n

C239

C240

C241

100n

100n

100n

B11

B9

B19

C17

D13

E6

E7

E8

E16

E17

E18

E21

F5

F19

F23

G5

G19

H5

H19

H22

K4

K20

K23

M22

N1

P20

P23

T5

T19

T20

U5

U19

V1

V5

V19

W6

W7

W8

W16

W17

W18

Y12

AC6

U201B PPC405EP

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

VDD_IO

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

TH_GND

K10

K11

K12

K13

K14

L10

L11

L12

L13

L14

M10

M11

M12

M13

M14

N10

N11

N12

N13

N14

P10

P11

P12

P13

P14

+3.3V

Board Power Supply

C249 10u/10V+C250 10u/10V+C251 10u/10V+C252 10u/10V+C253 10u/10V+C255 10u/10V

C

+

B

A

Title

KIM-PPCPower

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI-02-PPCPower.Sch

Revision:

1 2

Sheet of

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

2 13Date: 29-Jun-2005

B

A

Page 4

87654321

D

PER_DATA

PER_CTRL

PER_ADDR

PD00

PD01

PD02

PD03

PD04

PD05

PD06

PD07

C

B

A

PD08

PD09

PD10

PD11

PD12

PD13

PD14

PD15

U201F

P2

PerData0

N4

PerData1

P1

PerData2

M2

PerData3

PerData4

PerData5

PerData6

PerData7

PerData8

PerData9

PerData10

PerData11

PerData12

PerData13

PerData14

PerData15

PPC405EP

PerAddr3(GPIO14)

PerAddr4(GPIO15)

PerAddr5(GPIO16)

PerAddr6

PerAddr7

PerAddr8

PerAddr9

PerAddr10

PerAddr11

PerAddr12

PerAddr13

PerAddr14

PerAddr15

PerAddr16

PerAddr17

PerAddr18

PerAddr19

PerAddr20

PerAddr21

PerAddr22

PerAddr23

PerAddr24

PerAddr25

PerAddr26

PerAddr27

PerAddr28

PerAddr29

PerAddr30

PerAddr31

/PerWBE0

/PerWBE1

/PerCS0

/PerCS1(GPIO10)

/PerCS2(GPIO11)

/PerCS3(GPIO12)

/PerCS4(GPIO13)

/PerOE

PerR/W

/PerBLast(GPIO0)

PerReady

PerClk

/ExtReset

M3

L2

L3

K2

K3

H1

J4

G2

G4

H4

F1

D1

B4

A4

A5

D7

B6

A6

D8

C7

B7

C8

B8

D9

A8

C9

D10

C10

B10

D11

A10

C11

A11

D12

B12

C12

A13

B13

C13

A14

B14

F3

E1

E4

C2

E3

D3

D5

F4

D2

A9

B3

C4

A3

PA03

PA04

PA05

PA06

PA07

PA08

PA09

PA10

PA11

PA12

PA13

PA14

PA15

PA16

PA17

PA18

PA19

PA20

PA21

PA22

PA23

PA24

PA25

PA26

PA27

PA28

PA29

PA30

PA31

/PER_WBE0

/PER_WBE1

/CS_FLASH0

/CS1

/CS2

/PHY_RESET_R

/CS4

/PER_OE

/PER_WE

/PERBLAST

PER_RDY

PER_CLK

/EXT_RESET

+3.3V

+3.3V

R1102

R304

3k3

3k3

/CS4

Flash

USB

Version

R302

open

Pull PerReady down for FPGA

R308

3.3k

Load 28F128J3A (16MB), 28F640J2A (8MB) or 28F320J3A

(4MB) alternatively

+3.3V

A6

PA31

G2

A0

A1

A1

B1

A2

C1

A3

D1

A4

D2

A5

A2

A6

C2

A7

A3

A8

B3

A9

C3

A10

D3

A11

C4

A12

A5

A13

B5

A14

C5

A15

D7

A16

D8

A17

A7

A18

B7

A19

C7

A20

C8

A21

A8

A22

G1

A23

H8

A24

B2

+3.3V

C300

100n

R303

0

PA30

PA29

PA28

PA27

PA26

PA25

PA24

PA23

PA22

PA21

PA20

PA19

PA18

PA17

PA16

PA15

PA14

PA13

PA12

PA11

PA10

PA09

PA08

PA07

/PHY_RESET

/SYSRESET

A4

H3

G4

U300

PD15

F2

DQ0

DQ1

VCC

VCC

VPEN

VCCQ

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

CE0

CE1

CE2

WE#

OE#

RP#

STS

BYTE#

GND

GND

GND

H4

H6

C301

100n

E2

G3

E4

E5

G5

G6

H7

E1

E3

F3

F4

F5

H5

G7

E7

B4

B8

H1

G8

F8

D4

E8

F1

28F128J3_BGA

C302

100n

PD14

PD13

PD12

PD11

PD10

PD09

PD08

PD07

PD06

PD05

PD04

PD03

PD02

PD01

PD00

/CS_FLASH0

/PER_WE

/PER_OE

/EXT_RESET

/FLASH_IRQ

/BYTE

/BYTE

/FLASH_IRQ

R326 open

R327 open

R33510k

R33610k

+3.3V

R300

3.3k

R301

3.3k

+3.3V

R328 open

R329 open

R330 10k

R334 10k

R331 10k

R332 open

"Hardware Version"

00001110

PD07_B

PD06_B

PD05_B

PD04_B

PD03_B

PD02_B

PD01_B

PD00_B

R34110k

R340open

R333open

R339open

R33810k

R33710k

U301

18

B1

17

B2

16

B3

15

B4

14

B5

13

B6

12

B7

11

B8

19

OE

SN74LVC245APWR

/CS2

/PER_OE

L

L

H

2

PD07

A1

3

PD06

A2

4

PD05

A3

5

PD04

A4

6

PD03

A5

7

PD02

A6

8

PD01

A7

9

PD00

A8

1

BUS

B -> A

A -> B

/PER_OE

/CS2

Z

DIR

L

H

X

PER_BUS

D

C

B

A

Title

KIM-FLASH

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI-03-FLASH.Sch

Revision:

1 2

Sheet of

3 13Date: 29-Jun-2005

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

Page 5

87654321

ASSUME STRIPLINE FR-4 H OVER H 75 OHMS

PPC405GP HAS DRIVER RESISTANCE OF 35 OHMS

D

AB12

AA12

AC11

AA11

AA10

Y11

AC9

AB9

AC8

AA8

AB7

AB6

AA6

AC5

AB5

AC4

AA4

AB3

U201E

MemData0

MemAddr0

MemData1

MemAddr1

MemData2

MemAddr2

MemData3

MemAddr3

MemData4

MemAddr4

MemData5

MemAddr5

MemData6

MemAddr6

MemData7

MemAddr7

MemData8

MemData9

MemData10

MemData11

MemData12

MemData13

MemData14

MemData15

MemData16

MemData17

MemData18

MemData19

MemData20

MemData21

MemData22

MemData23

MemData24

MemData25

MemData26

MemData27

MemData28

MemData29

MemData30

MemData31

MemAddr8

MemAddr9

MemAddr10

MemAddr11

MemAddr12

BA0

BA1

/RAS

/CAS

DQM0

DQM1

DQM2

DQM3

/BankSel0

/BankSel1

/WE

ClkEn0

ClkEn1

MemClkOut0

MemClkOut1

Y9

Y7

Y5

Y3

W3

V4

W2

U4

V2

T4

T2

R4

R3

R2

PPC405EP

MD00

MD01

MD02

MD03

MD04

MD05

MD06

MD07

C

B

MD08

MD09

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

AB15

AB16

AB17

AA17

AC18

AA18

AC19

AB19

Y18

AA19

Y19

AA20

AC21

Y15

AC16

AA15

Y14

AC10

AA7

W4

U2

AB13

AC13

AC15

AB14

AC14

AA14

Y13

MA00

MA01

MA02

MA03

MA04

MA05

MA06

MA07

MA08

MA09

MA10

MA11

MA12

MBS0

MBS1

/RAS

/CAS

/BS0

/WE

CKEN0

MCK0

SDRAM DATA

SDRAM ADDRESS

DQM0

DQM1

DQM2

DQM3

SDRAM CONTROL

MA00

MA01

MA02

MA03

MA04

MA05

MA06

MA07

MA08

MA09

MA10

MA11

MBS0

MBS1

/BS0

/RAS

/CAS

/WE

CKEN0

MCK0

DQM0

DQM1

DQM2

DQM3

D

+3.3V+3.3V

A7

R7

B7

D9

B2

C9

VDDF9VDDL7VDD

VDD

VDDQ

VDDQ

VDDQ

G8

A0

G9

A1

F7

A2

F3

A3

G1

A4

G2

A5

G3

A6

H1

A7

H2

A8

J3

A9

G7

A10

H9

A11

J7

BS0

H8

BS1

J8

/CS

J9

/RAS

K7

/CAS

K8

/WE

J2

CKE

J1

CLK

K9

DQM0

K1

DQM1

F8

DQM2

F2

DQM3

VSS

VSS

VSSQ

VSS

A3

VSSQ

VSSQC1VSSQ

VSS

F1

L3

B3

B8

R3

VDDQ

VDDQE1VDDQL1VDDQM9VDDQN9VDDQP2VDDQ

VSSQE9VSSQL9VSSQM1VSSQN1VSSQP3VSSQ

D1

P7

U400

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

MT48LC8M32B2B5-7

P8

MD00

R8

MD01

N7

MD02

R9

MD03

N8

MD04

P9

MD05

M8

MD06

M7

MD07

L8

MD08

L2

MD09

M3

MD10

M2

MD11

P1

MD12

N2

MD13

R1

MD14

N3

MD15

R2

MD16

E8

MD17

D7

MD18

D8

MD19

B9

MD20

C8

MD21

A9

MD22

C7

MD23

A8

MD24

A2

MD25

C3

MD26

A1

MD27

C2

MD28

B1

MD29

D2

MD30

D3

MD31

E2

+3.3V

C400

100n

One C for each of the Corners

C402

100n

C405

100n

C406

100n

C407

100n

C

B

A

Title

KIM-SDRAM

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI-04-SDRAM.Sch

Revision:

1 2

Sheet of

4 13Date: 29-Jun-2005

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

A

Page 6

87654321

+3.3V

+3.3V

R621

3.3k

D

R611

CPU_TCK

0

R614

Open

CPU_TCK_I

CPU_TDO

/CPU_HALT

CPU_TDI

/CPU_TRST

CPU_TMS

+3.3V

J601

open

1

2

3

4

5

6

7

8

C

J611

1

CPU_TDO

2

3

CPU_TDI

4

/CPU_TRST

+3.3V

5

6

7

CPU_TCK_I

8

9

CPU_TMS

10

11

/CPU_HALT

12

13

Key

14

15

16

Q601

Open(BC850C)

/CPU_HALT

/CPU_TRST

CPU_TDI

CPU_TMS

R600

R615

R620

R622

RISC WATCH

+3.3V

3.3k

1k

3.3k

3.3k

U0_RX

/U0_DCD

/U0_DSR

/U0_CTS

/U0_RI

CPU_TDI

CPU_TMS

CPU_TDO

CPU_TCK

/CPU_TRST

/CPU_HALT

CPU_33MHz

AB18

AB20

AA1

AC3

AA2

C22

Y17

T1

M4

K1

T3

L4

Y2

H2

U201G PPC405EP

UART0_Rx

/UART0_DTR(GPIO27)

/UART0_DCD(GPIO24)

/UART0_DSR(GPIO25)

/UART0_CTS

/UART0_RI(GPIO26)

UART1_Tx(GPIO29)

UART1_Rx(GPIO28)

TDI

TMS

TDO

TCK

/TRST

/Halt

SysClk

/SysReset

SysErr

GPIO30(RejectPkt0)

GPIO31(RejectPkt0)

BERG16

B

SYS_ERR

/SYSRESET

100n

100n

MAX_C1+

C600

C601

MAX_C1-

MAX_C2+

MAX_C2-

U1_TX

U1_RX RS232_2_RX

A

RS485_#RE

RS485_DE

GPIO6

GPIO7

UART1

U600

2

C1+

4

C1-

5

C2+

6

C2-

11

T1IN

9

R1OUT

1

/EN

12

FORCEON

14

GND

MAX3221

T1OUT

R1IN

/INVALID

/FORCEOFF

VCC

V+

V-

U602

1

R

2

3

4

Vcc

B

A

D

GND

C602

3

MAX_V+

7

MAX_V-

13

8

10

16

15

8

7

C603

RS232_2_TX

+3.3V

C604

100n

100n

100n

RS485_A

RS485_B

RS232_2_RX

RS232_2_TX

RS485_Y

RS485_Z

6

+3.3V

4

3

1

J604

1

6

2

7

3

8

4

9

5

PIN HEADER 2,54mm, 2x5

U603

/RESET

VCC

/MR

GND

MAX811SEUS

MAX811, AD811 oder MIC811

2

U1_RX

3

U1_TX

4

5

open (MAX3485CSA)

1 2 3 4 5 6 7 8

+3.3V

+3.3V

R601

R602

UART0_Tx

/UART0_RTS

IICSCL

IICSDA

IRQ0(GPIO17)

IRQ1(GPIO18)

IRQ2(GPIO19)

IRQ3(GPIO20)

IRQ4(GPIO21)

IRQ5(GPIO22)

IRQ6(GPIO23)

GPIO1(TS1E)

GPIO2(TS2E)

GPIO3(TS1O)

GPIO4(TS2O)

GPIO5(TS3)

GPIO6(TS4)

GPIO7(TS5)

GPIO8(TS6)

GPIO9(TrcClk)

D600

2

3

ADM6315_2

BAR43

U604

R

D

GND

open (MAX3490CSA)

C6081nC607

3.3k

3.3k

P4

J1

N2

AB4

Y1

J3

J2

GPIO30

W20

GPIO31

Y21

USB_INT

W22

/PHY_IRQ

W23

INTA#

V21

GPIO20

V22

IRQ4

T22

GPIO22

R20

INTC#

T23

GPIO1

AA23

GPIO2

Y22

GPIO3

Y23

GPIO4

W21

GPIO5

U20

GPIO6

V23

GPIO7

U21

GPIO8

U22

GPIO9

T21

2

1

8

A

7

B

5

Y

6

Z

1

Vcc

C609

+

10u/10V

100n

U0_TX

/U0_DTR

/U0_RTS

I2C0_CLOCK_PPC

I2C0_DATA_PPC

U1_TX

U1_RX

USB_IRQ

/PHY_IRQ

PCI_INT

FPGA_TDO

/VSC_IRQ

RS232X

DEFAULT_JUMPER

RS485_#RE

RS485_DE

FPGA_TMS

DRV_EN

R610

3.3k

/MASTER_RESET

RS485_A

RS485_B

RS485_Y

RS485_Z

+3.3V

C605

100n

+3.3V

U601

4

VCC

NC1GND

SG8002JC 33MHz

GPIO30

GPIO31

SYS_ERR

3

OUT

2

UART1

IIC_BUS

UART0

IIC EEPROM OFF

U0_TX

R603

R604

Boot ROM Size = 16Bit

/U0_RTS

R606

R612

AC2

SYS_ERR

R613

R607

16 BIT ROM

R617

R624

R625

R618

GPIO2

GPIO5

GPIO8

D601

LED_RED

R623

R605

R608

OSC_33MHz

open

1k

open

1k

3.3k

open

12

+3.3V

Idea: Overwrite it on Mainboard

to enable EEPROM config

+3.3V

open

3.3k

3.3k

open

3.3k

3.3k

3.3k

R619

330

D602_ANODE1

Title

KIM-IO

Size: Number:

A3

File:

KIM_MSI-06-IO.Sch

14

U605A

2

112

+3.3V

GND

74LVX14MTC

7

+3.3V

R628

3k3

GPIO5

/MASTER_RESET

+3.3V

U0_TX

GPIO1

R631

3k3

U0_RX

Revision:

1 2

Sheet of

3 4

OSC_CLK_N

5 6

9 8

11 10

13 12

1

7

14

SN74LVC125APWR

10

SN74LVC125APWR

6

SN74LVC125APWR

11

SN74LVC125APWR

5 13Date: 29-Jun-2005

U605B

74LVX14MTC

U605C

74LVX14MTC

U605D

74LVX14MTC

U605E

74LVX14MTC

U605F

7414

S600

J600

open

Master Reset

U606A

A2Y

OE

GND

VCC

U606C

A9Y

OE

U606B

A5Y

OE

U606D

A12Y

OE

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

PCI_CLK

R627

R616

R626

R609

33

33

33

33

VSC_33MHz

VSC_PCI_CLK

CPU_33MHz

D

C

+3.3V

Default jumper

3

PIN HEADER 2,54mm, 1x2

U0_TX_MSI

U0_RX_MSI

B

1

2

+3.3V

8

4

R630

3k3

R629

10k

Q602

BC850C

13

/GPIO1

A

Page 7

87654321

D

A18

D19

L20

N20

J21

F22

H20

G21

G22

H21

A21

J20

H23

B21

E20

F20

E22

U201C PPC405EP

PCIC0(/BE0)

PCIC1(/BE1)

PCIC2(/BE2)

PCIC3(/BE3)

PCIParity

/PCIFRAME

/PCIIRDY

/PCITRDY

/PCIStop

/PCIDevSel

PCIIDSel

/PCISErr

/PCIPErr

PCIClk

/PCIReq0(/Gnt)

/PCIReq1

/PCIReq2

PCIAD10

PCIAD11

PCIAD12

PCIAD13

PCIAD14

PCIAD15

PCIAD16

PCIAD17

PCIAD18

PCIAD19

PCIAD20

PCIAD21

PCIAD22

PCIAD23

PCIAD24

PCIAD25

PCIAD26

PCIAD27

PCIAD28

PCIAD29

PCIAD30

PCIAD31

/PCIReset

/PCIint(PerWE)

/PCIGnt0(/Req)

C/BE[0]#

C/BE[1]#

C/BE[2]#

C/BE[3]#

REQ1#

REQ0#

REQ2#

PAR

FRAME#

IRDY#

TRDY#

STOP#

DEVSEL#

PPC_IDSEL

SERR#

PERR#

PCI_CLK

REQ0#

REQ1#

REQ2#

C

generated on Mainboard

+3.3V

10k

R700

10k

R701

10k

B

R702

PCIAD0

PCIAD1

PCIAD2

PCIAD3

PCIAD4

PCIAD5

PCIAD6

PCIAD7

PCIAD8

PCIAD9

/PCIGnt1

/PCIGnt2

AD[00]

B16

AD[01]

C16

AD[02]

B17

AD[03]

D16

AD[04]

B18

AD[05]

D17

AD[06]

C18

AD[07]

A19

AD[08]

D18

AD[09]

C19

AD[10]

A20

AD[11]

B20

AD[12]

C20

AD[13]

C23

AD[14]

D21

AD[15]

D22

J22

J23

K21

K22

L21

L22

L23

M21

N23

N22

N21

P22

P21

R23

R22

R21

G20

D15

D23

E23

F21

AD[16]

AD[17]

AD[18]

AD[19]

AD[20]

AD[21]

AD[22]

AD[23]

AD[24]

AD[25]

AD[26]

AD[27]

AD[28]

AD[29]

AD[30]

AD[31]

PCI_RST#

PCI_INT#

GNT0#

GNT1#

GNT2#

+3.3V

AD[18]

AD[17]

33

R705

open

R703

PPC_IDSEL

R718

3.3k

PERR#

SERR#

STOP#

DEVSEL#

IRDY#

TRDY#

FRAME#

+3.3V

10k

R710

10k

R711

10k

R712

10k

R713

10k

R714

10k

R715

10k

R716

D

C

B

A

Title

KIM-PCI

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI-07-PCI.Sch

Revision:

1 2

Sheet of

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

7 13Date: 29-Jun-2005

A

Page 8

87654321

D

ET1_TXCLK_R

ET1_TXD0

ET1_TXD1

ET1_TXD2

ET1_TXD3

ET1_TXERR

ET1_TXEN

ET1_RXCLK_R

ET1_RXD0

ET1_RXD1

ET1_RXD2

ET1_RXD3

ET1_RXERR

ET1_RXDV

ET1_COL

ET1_CRS

MD_CLK

MDIO

U201D PPC405EP

C6

PHY0Tx1Clk

B15

EMC0Tx1D0

C14

EMC0Tx1D1

A15

EMC0Tx1D2

D14

EMC0Tx1D3

C15

EMC0Tx1Err

A16

EMC0Tx1En

E2

PHY0Rx1Clk

R1

PHY0Rx1D0

H3

PHY0Rx1D1

G3

PHY0Rx1D2

F2

PHY0Rx1D3

C1

PHY0Rx1Err

D6

PHY0Rx1DV

C5

PHY0Col1

B5

PHY0CrS1

Y6

EMCMDClk

AA5

EMCMDIO(PHYMDIO)

PHY0Tx0Clk

EMC0Tx0D0

EMC0Tx0D1

EMC0Tx0D2

EMC0Tx0D3

EMC0Tx0Err

EMC0Tx0En

PHY0Rx0Clk

PHY0Rx0D0

PHY0Rx0D1

PHY0Rx0D2

PHY0Rx0D3

PHY0Rx0Err

PHY0Rx0DV

PHY0Col0

PHY0CrS0

Y8

U3

N3

L1

P3

V3

W1

AB10

Y16

AA22

AA16

AA13

AB11

Y10

AB8

AA9

ET0_TXCLK_R

ET0_TXD0

ET0_TXD1

ET0_TXD2

ET0_TXD3

ET0_TXERR

ET0_TXEN

ET0_RXCLK_R

ET0_RXD0

ET0_RXD1

ET0_RXD2

ET0_RXD3

ET0_RXERR

ET0_RXDV

ET0_COL

ET0_CRS

49R9(1%)

R916

ET0_TXCLK

49R9(1%)

R917

ET0_RXCLK

C

D

C

+3.3V

C908

C900

100n

C901

100n

+3.3V

22

51

8

40

LXTXI

LXTXO

55

TX_CLK

57

TXD0

58

TXD1

59

TXD2

60

TXD3

54

TX_ER

56

TX_EN

52

RX_CLK

48

RXD0

47

RXD1

46

RXD2

45

RXD3

53

RX_ER

49

RX_DV

62

COL

63

CRS

12

ADDR0

33

PAUSE

34

TEST0

35

TEST1

4

/RESET

43

MDC

42

MDIO

64

/MDINT

3

MDDIS

1

XI(CLKIN)

2

XO

C911

22p

VCCA21VCCA

VCCD

VCCIO

VCCIO

TPO+

TPO-

TXSLEW0

TXSLEW1

RBIAS

PWRDWN

LED1(CFG1)

LED2(CFG2)

LED3(CFG3)

/TRST

GND

GND

GND13GND14GND15GND

GND

GND25GND

7

11

16

18

26

ET0_TXCLK

ET0_TXD0

ET0_TXD1

ET0_TXD2

ET0_TXD3

ET0_TXERR

R915

open

MD_ADDR0

ET0_TXEN

ET0_RXCLK

ET0_RXD0

ET0_RXD1

ET0_RXD2

ET0_RXD3

ET0_RXERR

ET0_RXDV

ET0_COL

ET0_CRS

R908

open

/PHY_RESET

MD_CLK

MDIO

/PHY_IRQ

X900

25MHz

C910

22p

B

R907

+3.3V

3k3

R906

3k3

PER_CTRL

A

+

C904

10u/10V

10n

C909

C905

10u/10V

+

10n

+3.3V

ETH_TX+

ETH_TX-

ETH_RX+

ETH_RX-

ETH_RBIAS

ETH_LED1

ETH_LED2

ETH_LED3

R926

22k1(1%)

C912 270p

C913 270p

L900

1000Ohm,0.2A

ETH_RX+C

ETH_RX-C

R918 49R9(1%)

ACTIVITY

FULL

100

R919 49R9(1%)

ETH_RX_TERM

C906

10n

CHIP LED 0805, GREEN

CHIP LED 0805, GREEN

VCCA_CENTER

D901

D902

D903

C907

10n

12

12

12

VCCA

U900

19

20

23

TP+

24

TP-

5

6

17

39

38

37

36

27

TDI

28

TDO

29

TMS

30

TCK

31

32

GND

41

GND

50

GND

61

GND

LXT972

CHIP LED 0805, GREEN

+3.3V

L902

1000Ohm,0.2A

T901

6

7

8 9

1

2

3

ETH_H1102

+3.3V

D901_A

R929

D902_A

R928

D903_A

R927

To LED on Chassis Front Panel via Cable ETH_RJ45_TERM_GND

330

To RJ45 J901 LED1

330

To RJ45 J901 LED2

330

11

10

16

15

14

LINE_RX_MID

LINE_TX_MID

ETH_RJ45_TX+

ETH_RJ45_TXETH_RJ45_RX+

ETH_RJ45_4_TERM

ETH_RJ45_5_TERM

ETH_RJ45_RXETH_RJ45_7_TERM

ETH_RJ45_8_TERM

R922

R923

R924

R925

49R9(1%)

49R9(1%)

49R9(1%)

49R9(1%)

ETH_RJ45_PAIR78ETH_RJ45_PAIR45

R930 49R9(1%)

R931 49R9(1%)

C902 1n(2kV)

C903 1n(2kV)

C914 1n(2kV)

J901

CON10

1

2

3

4

5

6

7

8

9

10

C916

100n

B

A

Title

KIM-ETH

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI-09-ETH.Sch

Revision:

1 2

Sheet of

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

8 13Date: 29-Jun-2005

Page 9

87654321

D

U1101C

ALTERA_EP1C4

AD[19]

AD[22]

AD[21]

SERR#

AD[23]

AD[16]

STOP#

AD[24]

AD[26]

C/BE[3]#

PAR

AD[27]

AD[29]

AD[15]

VSC_MD01

AD[31]

IRDY#

C/BE[2]#

AD[20]

REQ0#

AD[30]

TRDY#

DEVSEL#

AD[18]

EXT_GPIO9

EXT_GPIO10

REQ1#

DIV

DIV

DIV

DIV

GNT2#

PCI_RST#

ADC_A_R5

ADC_A_R2

EXT_GPIO34

ADC_A_R3

ADC_HSYNC

ADC_A_G6

CARD_PRESNT_R

ADC_A_G3

ADC_A_G4

LAD0

LAD1

ADC_A_R6

ADC_DE

ADC_A_G1

ADC_A_B7

ADC_A_R4

LAD2

ADC_A_B5

ADC_A_B4

VGA_HSYNC

LAD3

ADC_A_B2

ADC_B_R7

ADC_A_G7

ADC_A_G5

GND_C20_8

+1.5V_C20_8

ADC_B_R5

ADC_B_R4

ADC_B_R6

ADC_A_B3

ADC_A_B6

EXT_GPIO11

ADC_B_R3

ADC_B_R2

ADC_B_G7

ADC_B_G4

ADC_B_G5

C

B

IO Block 1

C2

I/O

D2

I/O

D1

I/O

E3

I/O DQ0L0

E2

I/O DQ0L1

E4

I/O DQ0L2

E5

I/O DQ0L3

F2

I/O

F3

I/O

F4

I/O

F5

I/O

G2

I/O

G1

I/O

F6

I/O

F7

I/O

G4

I/O DQ0L4

G3

I/O

G5

I/O DQ0L5

G6

I/O DQ0L6

H1

I/O DQ0L7

H2

I/O

H3

I/O

H4

I/O

H5

I/O DM0L

L6

I/O

L7

I/O DM1L

L2

I/O

L3

I/O

L5

I/O

L4

I/O

U1101F

IO Block 4

U3

I/O

V4

I/O

T4

I/O

U4

I/O

T5

I/O DQ1B7

U5

I/O DQ1B6

M8

I/O

N8

I/O

V6

I/O

U6

I/O DQ1B5

P6

I/O DQ1B4

P7

I/O

T6

I/O

R6

I/O

U7

I/O DQ1B3

V7

I/O DQ1B2

T7

I/O DQ1B1

R7

I/O DQ1B0

U8

I/O

V8

I/O

T8

I/O

R8

I/O

U9

I/O

V9

I/O

R9

I/O DM1B

T9

I/O

M9

I/O

N9

I/O

U10

I/O

V10

I/O

T10

I/O

R10

I/O

P10

I/O

R11

I/O

T11

I/O

U11

I/O DM0B

V11

I/O

V12

I/O

U12

I/O

ALTERA_EP1C4

I/O DQ1L0

I/O DQ1L1

I/O DQ1L2

I/O DQ1L3

I/O DQ1L4

I/O DQ1L5

I/O DQ1L6

I/O DQ1L7

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O DQ0B7

I/O DQ0B6

I/O DQ0B5

I/O DQ0B4

I/O DQ0B3

I/O DQ0B2

I/O DQ0B1

I/O DQ0B0

EXT_GPIO8

M1

C/BE[1]#

M3

LDRQ#

M2

LFRAME#

M5

SERIRQ

M4

LRESET#

N1

CLKRUN#

N2

LPCPD#

M6

LSMI#

N7

LPME#

N5

I2C1_DATA

N6

I2C1_CLOCK

N3

I2C0_CLOCK

N4

I2C0_DATA

P2

I2C4_DATA

P3

I2C4_CLOCK

P4

I2C3_DATA

R2

I2C3_CLOCK

R3

ADC_A_R7

T2

VGA_VSYNC

T3

ADC_B_G6

T12

I2C2_DATA

R12

ADC_B_G1

V13

ADC_B_G2

U13

ADC_B_G3

T13

I/O

I2C2_CLOCK

R13

I/O

N10

I/O

M10

I/O

P12

I/O

N11

I/O

M11

I/O

T14

R14

V15

U15

U16

I/O

T15

I/O

GND_C20_6+1.5V_C20_7

+1.5V_C20_6

EXT_GPIO7

+1.5V_C20_5

GND_C20_5

ADC_B_B6

ADC_B_B7

ADC_B_B3

ADC_B_B4

ADC_B_B2

ADC_B_B5

DIV

DIV

DIV

DIV

PWM_OUT0

PWM_OUT1

PWM_OUT2

PWM_OUT3

PWM_OUT4

PWM_OUT5

PWM_OUT6

PWM_OUT7

TACHO_IN0

TACHO_IN1

TACHO_IN2

TACHO_IN3

TACHO_IN4

TACHO_IN5

TACHO_IN6

TACHO_IN7

EXT_GPIO33

EXT_GPIO0

EXT_GPIO1

EXT_GPIO2

EXT_GPIO3

EXT_GPIO4

EXT_GPIO5

EXT_GPIO6

FML_SINTEXEXT_GPIO12

FML_SD

FML_MD

AD[01]

AD[00]

AD[08]

AD[03]

PCI_INT#

/SYSRESET

VSC_MD21

VSC_MD20

VSC_MD18

VSC_MD19

VSC_MD30

VSC_MD31

DIV

+1.5V_C20_2

DIV

GND_C20_2

VSC_MDQM1

DIV

GND_C20_3

DIV

+1.5V_C20_3

VSC_MDQM2

VSC_MD16

VSC_MCKE

VSC_MA09

VSC_MA07

VSC_MA06

VSC_MA01

VSC_MA02

VSC_MDQM3

VSC_MA04

VSC_MA10

VSC_MA00

VSC_MA03

VSC_MD10

VSC_MD09

VSC_MBS0

VSC_MBS1

DIV

+1.5V_C20_4

DIV

GND_C20_4

VSC_MD11

VSC_MD12

VSC_/MCS

VSC_/MRAS

VSC_MD15

VSC_MD00

VSC_/MCAS

VSC_/MWE

U1101D

IO Block 3

T16

I/O

T17

I/O

R17

I/O

R18

I/O

R15

I/O DQ1R7

R16

I/O

P17

I/O DQ1R6

P14

I/O DQ1R5

N14

I/O DQ1R4

N18

I/O

N17

I/O

N13

I/O

N12

I/O

N16

I/O

N15

I/O

M18

I/O

M17

I/O DQ1R3

M15

I/O DQ1R1

M14

I/O DQ1R2

M16

I/O DQ1R0

L18

I/O

L17

I/O

M13

I/O

L13

I/O

L15

I/O

L16

I/O DM1R

L14

I/O

J13

I/O

H13

I/O DM0R

H14

I/O

H15

I/O

H16

I/O

H17

I/O

ALTERA_EP1C4

U1101E

ALTERA_EP1C4

IO Block 2

C16

I/O

B16

I/O

B15

I/O DQ0T0

A15

I/O DQ0T1

C15

I/O DQ0T2

D14

I/O DQ0T3

G11

I/O

F11

I/O

E13

I/O

G10

I/O

F10

I/O

B13

I/O

A13

I/O

D13

I/O DQ0T4

C13

I/O DQ0T5

D12

I/O DQ0T6

C12

I/O DQ0T7

B12

I/O

A12

I/O

C11

I/O

D11

I/O

B11

I/O

A11

I/O DM0T

E11

I/O

C10

I/O

D10

I/O

B10

I/O

A10

I/O

G9

I/O

F9

I/O

D9

I/O DM1T

C9

I/O

A9

I/O

B9

I/O

D8

I/O

C8

I/O

A8

I/O

B8

I/O

I/O DQ0R7

I/O DQ0R6

I/O DQ0R5

I/O DQ0R4

I/O DQ0R3

I/O DQ0R2

I/O DQ0R1

I/O DQ0R0

I/O DQ1T0

I/O DQ1T1

I/O DQ1T2

I/O DQ1T3

I/O DQ1T4

I/O DQ1T5

I/O DQ1T6

I/O DQ1T7

H18

INTA#

PCI_INT

AD[11]

G18

AD[10]

G17

AD[02]

G13

AD[06]

G14

I/O

AD[04]

G15

I/O

AD[09]

G16

I/O

AD[05]

G12

I/O

VSC_MA05

F12

I/O

AD[12]

F17

I/O

AD[14]

F18

I/O

VSC_MD08

F14

I/O

VSC_MA08

F13

I/O

AD[07]

F16

I/O

C/BE[0]#

F15

VSC_MD26

E16

VSC_MD28

E15

VSC_MD24

D18

VSC_MD27

D16

I/O

VSC_MD29

D15

I/O

VSC_MD22

C17

I/O

VSC_MD23

D17

I/O

VSC_MD14

E8

VSC_MD02

E7

VSC_MDQM0

A7

VSC_MD07

B7

AD[13]

D7

I/O

GNT0#

C7

I/O

GNT1#

E6

I/O

REQ2#

D6

I/O

VSC_MD06

B6

I/O

FRAME#

C6

I/O

F8

I/O

G8

I/O

C5

D5

A4

B4

GND_C20_1

AD[17]

PERR#

VSC_MD04

VSC_MD03

DIV+1.5V_C20_1

DIV

D

C

B

A

Title

KIM-VSC

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI-11-VSC.Sch

Revision:

1 2

Sheet of

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

11 13Date: 29-Jun-2005

A

Page 10

87654321

+3.3V

VREF = 1.25

D

Iadj = 35uA

Vout - 1.25

R2 = ----------------- (1.25 / R1 + Iadj)

3

U1300

FAN1117ASX

Vin

+1.5V

R1306

330

+1.5V

C1300

+

10u/10V

2

Vout

4

Vout

ADJ/GND

1

D

U1300_ADJ

R1307

68

+1.5V

+3.3V

+3.3V +3.3V

R1302

10K

R1303

10K

+3.3V

R1304

10K

+3.3V

R1300

R1301

10K

10K

VSC_CONF_DONE

VSC_nSTATUS

VSC_nCONFIG

VSC_DCLK

VSC_DATA0

EXT_GPIO26

EXT_GPIO27

EXT_GPIO29

EXT_GPIO30

EXT_GPIO31

EXT_GPIO28

Passive Slave Mode

EXT_GPIO25

AD[28]

EXT_GPIO32

EXT_GPIO24

EXT_GPIO16

EXT_GPIO13

U1101B

ALTERA_EP1C4

Config, Clock

K17

CONF_DONE

L12

nSTATUS

J2

nCONFIG

L1

DCLK

H7

DATA0

J7

nCE

K2

nCEO

K6

ASDO_I/O

J1

nCSO_I/O

C3

INIT_DONE_I/O

D3

CLKUSR_I/O

C4

DEV_CLRn_I/O

B3

DEV_OE_I/O

K7

MSEL1

K3

MSEL0

K14

GPIO8

TMS

J17

GPIO2

TDI

K18

GPIO4

TCK

K13

GPIO20

TDO

D4

VREF0B1

H6

VREF1B1

R1

VREF2B1

C14

VREF0B2

E10

VREF1B2

A6

VREF2B2

DPCLK7_I/O DQS1B

DPCLK6_I/O DQS0B

DPCLK5_I/O DQS1R

DPCLK4_I/O DQS0R

DPCLK3_I/O DQS0T

DPCLK2_I/O DQS1T

DPCLK1_I/O DQS0L

DPCLK0_I/O DQS1L

PLL1_OUTp_I/O

PLL1_OUTn_I/O

PLL2_OUTp_I/O

PLL2_OUTn_I/O

VREF0B3

VREF1B3

VREF2B3

VREF0B4

VREF1B4

VREF2B4

CLK0

CLK1

CLK2

CLK3

ADC_CLK

J3

LPC_CLK

J4

VSC_33MHz

J15

VSC_PCI_CLK

J16

EXT_GPIO18

R4

EXT_GPIO19

U14

EXT_GPIO20

P15

E17

VSC_MD25

B14

VSC_MD17

B5

VSC_MD05

F1

AD[25]

EXT_GPIO21

P5

FML_CLK

K4

K5

VSC_MD13

VSC_MCLK

K15

EXT_GPIO22

K16

E14

EXT_GPIO23

J14

EXT_GPIO17

P16

EXT_GPIO14

P13

EXT_GPIO15

P9

ADC_A_G2

R5

ADC_VSYNC

C

U1101A

A1

GND

A16

GND

A18

GND

A3

GND

B17

GND

B2

GND

C1

GND

C18

GND

H11

GND

H8

GND

H9

GND

J10

C

GND

J11

GND

J8

GND

K11

GND

K8

GND

K9

GND

L10

GND

L11

GND

L8

GND

T1

GND

T18

GND

U17

GND

U2

GND

V1

GND

V16

GND

V18

GND

V3

GND

K1

GNDA_PLL1

J6

GNDG_PLL1

J18

GNDG_PLL2

K12

GNDA_PLL2

ALTERA_EP1C4

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCIO1

VCCIO1

VCCIO1

VCCIO1

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO3

VCCIO3

VCCIO3

VCCIO3

VCCIO2

VCCIO2

VCCIO2

VCCIO2

VCCA_PLL1

VCCA_PLL2

A17

A2

B1

B18

H10

J9

K10

L9

U1

U18

V17

V2

E1

G7

M7

P1

P11

P8

V14

V5

E18

H12

M12

P18

A14

A5

E12

E9

VCCA_PLL1

J5

J12

VCCA_PLL2

C1312 100n

C1329

+

10u/10V

C1316 100n

C1328

+

10u/10V

+1.5V

L1300 10nH

L1301 10nH

B

+1.5V

C1302 100n

C1303 100n

C1304 100n

C1305 100n

C1306 100n

C1308 100n

C1309 100n

C1310 100n

+3.3V

C1311 100n

C1313 100n

C1314 100n

C1315 100n

C1319 100n

C1320 100n

C1321 100n

C1322 100n

C1323 100n

C1324 100n

C1325 100n

C1326 100n

+3.3V

C1301

+

10u/10V

C1327 100n

A

Title

KIM-VSCPwr

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI-13-VSCPwr.Sch

Revision:

1 2

Sheet of

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

10 13Date: 29-Jun-2005

B

A

Page 11

87654321

D

ASSUME STRIPLINE FR-4 H OVER H 75 OHMS

SDRAM DATA

SDRAM ADDRESS

R1500

R1501

R1502

R1503

R1504

R1505

R1506

33

33

33

33

33

33

33

VSC_MA00_R

VSC_MA01_R

VSC_MA02_R

VSC_MA03_R

VSC_MA08_R

VSC_MA09_R

VSC_MA10_R

VSC_MA00

VSC_MA01

VSC_MA02

VSC_MA03

VSC_MA08

VSC_MA09

VSC_MA10

C

B

VSC_MA04

VSC_MA05

VSC_MA06

VSC_MA07

VSC_/MCS

VSC_/MRAS

VSC_/MCAS

VSC_/MWE

VSC_MDQM0

VSC_MDQM1

VSC_MDQM2

VSC_MDQM3

VSC_MBS0

VSC_MBS1 VSC_MBS1_R

VSC_MCKE

VSC_MCLK

R1507

R1508

R1509

R1510

R1511

R1512

R1513

R1514

R1515

R1516

R1517

R1518

R1519

R1520

R1521

R1522

33

VSC_MA04_R

33

VSC_MA05_R

33

VSC_MA06_R

33

VSC_MA07_R

33

/VSC_MCS_R

33

/VSC_MRAS_R

33

/VSC_MCAS_R

33

/VSC_MWE_R

33

VSC_MDQM0_R

33

VSC_MDQM1_R

33

VSC_MDQM2_R

33

VSC_MDQM3_R

33

VSC_MBS0_R

33

33

VSC_MCKE_R

33

VSC_MCLK_R

SDRAM CONTROL

+3.3V

VSC_MA00_R

VSC_MA01_R

VSC_MA02_R

VSC_MA03_R

VSC_MA04_R

VSC_MA05_R

VSC_MA06_R

VSC_MA07_R

VSC_MA08_R

VSC_MA09_R

VSC_MA10_R

VSC_MBS0_R

VSC_MBS1_R

/VSC_MCS_R

/VSC_MRAS_R

/VSC_MCAS_R

/VSC_MWE_R

VSC_MCKE_R

VSC_MCLK_R

VSC_MDQM0_R

VSC_MDQM1_R

VSC_MDQM2_R

VSC_MDQM3_R

25

26

27

60

61

62

63

64

65

66

24

22

23

20

19

18

17

67

68

16

71

28

59

1

15

29

43

+3.3V

3

9

A0

A1

VDDQ

A2

A3

A4

A5

A6

A7

A8

A9

A10[AP]

BA0

BA1

/CS

/RAS

/CAS

/WE

CKE

CLK

DQM0

DQM1

DQM2

DQM3

VDD

VDD

VDD

VDD

VSSQ6VSSQ12VSSQ32VSSQ38VSS44VSSQ46VSSQ52VSS58VSS72VSSQ78VSSQ84VSS

41

VDDQ

VDDQ35VDDQ

KM432S2030C

VDDQ49VDDQ55VDDQ75VDDQ

81

U1500

2

VSC_MD00

DQ0

4

VSC_MD01

DQ1

5

VSC_MD02

DQ2

7

VSC_MD03

DQ3

8

VSC_MD04

DQ4

10

VSC_MD05

DQ5

11

VSC_MD06

DQ6

13

VSC_MD07

DQ7

74

VSC_MD08

DQ8

76

VSC_MD09

DQ9

77

VSC_MD10

DQ10

79

VSC_MD11

DQ11

80

VSC_MD12

DQ12

82

VSC_MD13

DQ13

83

VSC_MD14

DQ14

85

VSC_MD15

DQ15

31

VSC_MD16

DQ16

33

VSC_MD17

DQ17

34

VSC_MD18

DQ18

36

VSC_MD19

DQ19

37

VSC_MD20

DQ20

39

VSC_MD21

DQ21

40

VSC_MD22

DQ22

42

VSC_MD23

DQ23

45

VSC_MD24

DQ24

47

VSC_MD25

DQ25

48

VSC_MD26

DQ26

50

VSC_MD27

DQ27

51

VSC_MD28

DQ28

53

VSC_MD29

DQ29

54

VSC_MD30

DQ30

56

VSC_MD31

DQ31

86

D

C

B

+3.3V

C1500

C1502

C1504

100n

100n

One C for each of the Corners

C1501

C1503

100n

100n

A

1 2 3 4 5 6 7 8

100n

C1505

100n

C1506

100n

C1507

100n

Title

KIM-VSC_SDRAM

Size: Number:

A3

File:

KIM_MSI-15-VSC_SDRAM.Sch

Revision:

1 2

Sheet of

A

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

12 13Date: 29-Jun-2005

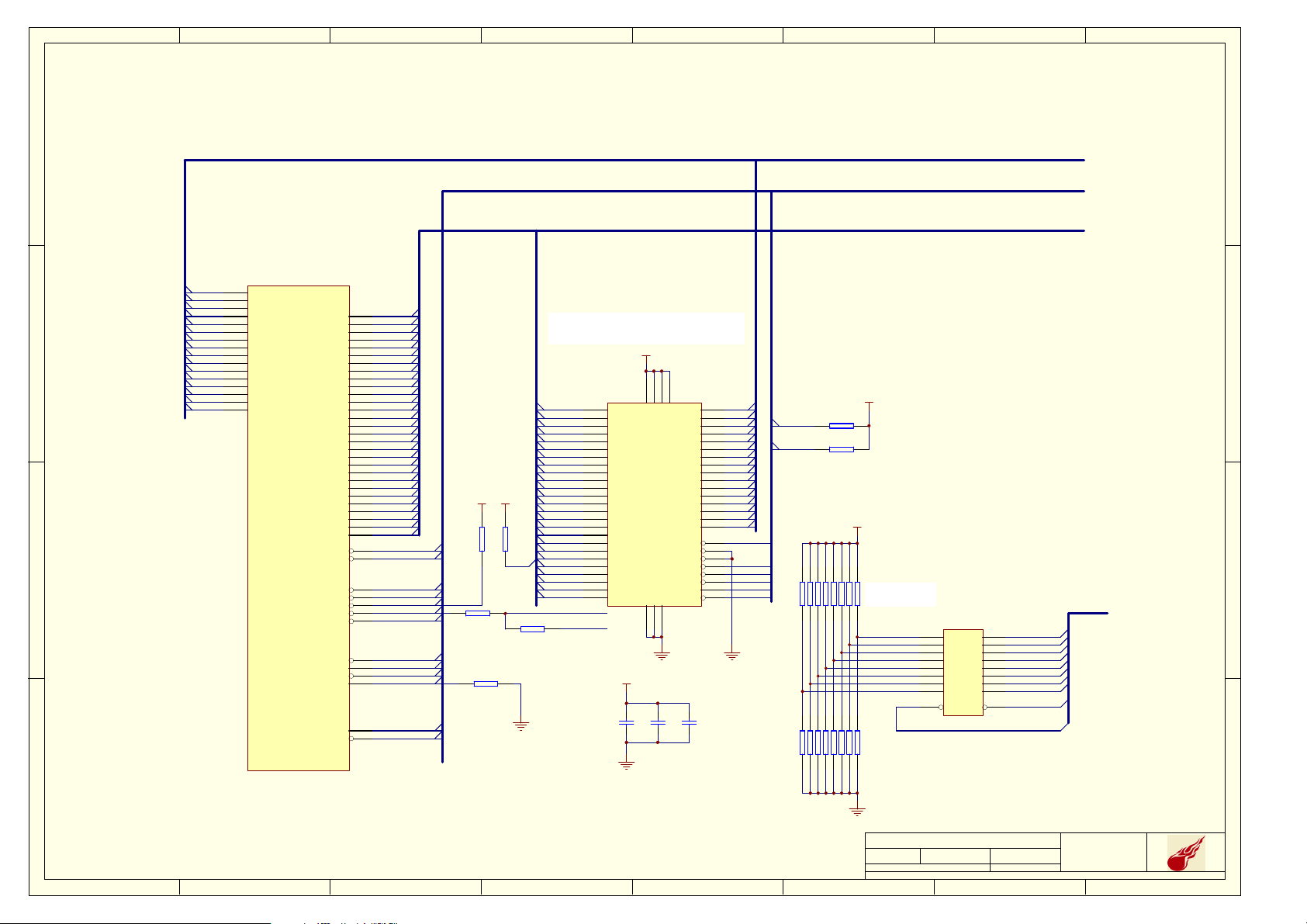

Page 12

87654321

D

+3.3V

+3.3V

+3.3V

+3.3V

C1601

100n

PER BUS

33

30

29

28

27

26

25

24

23

22

19

18

17

16

15

14

34

37

38

35

36

10

4

3

6

7

5

12

13

U1601

AD0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

A0

ALE

CS

RD

WR

INT

SUSPEND

WAKEUP

DREQ

DACK

EOT

BUS_CONF0

BUS_CONF1

ISP1181BBS

Vreg(3.3)

Vcc(3.3)

Vref

RESET

Vbus

XTAL1

XTAL2

CLKOUT

TEST1

TEST2

TEST3

REGGND

GND

GND

GND

46

32

44

Vcc

21

/EXT_RESET

39

USB_VBUS

1

R1610

D-

47

48

43

42

40

2

8

9

11

45

41

31

20

R1608

D+

R1609

USB_XTAL1

USB_XTAL2

USB_LED

USB_TEST1

USB_TEST2

R1603

R1602

10k

10k

D-

D+

GL

PD15

PD14

PD13

PD12

C

+3.3V

R1604

3k3

R1601

10k

B

PD11

PD10

PD09

PD08

PD07

PD06

PD05

PD04

PD03

PD02

PD01

PD00

PA30

/CS1

/PER_OE

/PER_WE

USB_INT

USB_WAKEUP

C1604

100n

C1603

100n

C1602

100n

4k7

+5V_USB_HOST

22

USB_D-

22

USB_D+

+3.3V

D1601

12

CHIP LED 0805, GREEN

J1602

1

2

3

4

PIN HEADER 2,54mm, 1x4

C1605

18p

X1601

6MHz

R1611

330

+3.3V

C1606

18p

D

C

B

A

Title

KIM-USB

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI-16-USB.Sch

Revision:

1 2

Sheet of

13 13Date: 29-Jun-2005

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

A

Page 13

87654321

D

DVI Input

Rx2+

Rx2Rx1+

Rx1Rx0+

Rx0RxC+

RxC-

+3.3V

L1700

Ferrite Bead 200Ohm@100MHz 74279263

C

+

+3.3V

L1701

Ferrite Bead 200Ohm@100MHz 74279263

C1700

+

+3.3V

L1702

Ferrite Bead 200Ohm@100MHz 74279263

+3.3V

L1703

Ferrite Bead 200Ohm@100MHz 74279263

B

C1702

+

10u/6.3V

C1704

+

AVDD_DVI

+3.3V

+3.3V

+3.3V

+3.3V

I2C0_DATA_PPC

R1720

I2C0_CLOCK_PPC

R1721

C1701

10u/6.3V

10u/6.3V

10u/6.3V

R1711

R1712

R1700

R1701

R1707

R1702

open

open

C1705100n

OVDD

C1706100n

C1708100n

AVDD_DVI

C1707100n

C1709100n

DVDD

PVCC

C17191nC1717

C1710100n

C1711100n

C1714100n

open (390)

open

10k

10k

10k

10k

Mode

/PD

/PDO

ST

100n

U1700

80

Rx2+

81

Rx2-

85

Rx1+

86

Rx1-

90

Rx0+

91

Rx0-

93

RxC+

94

RxC-

18

OVDD

29

OVDD

43

OVDD

C1712100n

57

OVDD

78

OVDD

19

OGND

28

OGND

45

OGND

58

OGND

76

OGND

82

AVDD

84

AVDD

88

AVDD

95

C1713100n

AVDD

79

AGND

83

AGND

87

AGND

92

AGND

6

DVDD

38

DVDD

67

DVDD

C1716100n

5

DGND

39

DGND

68

DGND

97

PVCC1

98

PGND

96

EXT_RES

99

RSVD

2

/PD

9

/PDO

3

ST

TFP401

QO23

QO22

QO21

QO20

QO19

QO18

QO17

QO16

QO15

QO14

QO13

QO12

QO11

QO10

QO9

QO8

QO7

QO6

QO5

QO4

QO3

QO2

QO1

QO0

QE23

QE22

QE21

QE20

QE19

QE18

QE17

QE16

QE15

QE14

QE13

QE12

QE11

QE10

QE9

QE8

QE7

QE6

QE5

QE4

QE3

QE2

QE1

QE0

ODCK

VSYNC

HSYNC

CTL1

CTL2

CTL3

OCKINV

DFO

PIXS

SCDT

/STAG

DE

ADC_A_R7

77

ADC_A_R6

75

ADC_A_R5

74

ADC_A_R4

73

ADC_A_R3

72

ADC_A_R2

71

ADC_A_R1

70

69

ADC_A_R0

66

ADC_A_G7

65

ADC_A_G6

64

ADC_A_G5

63

ADC_A_G4

62

ADC_A_G3

61

ADC_A_G2

60

ADC_A_G1

59

ADC_A_G0

56

ADC_A_B7

55

ADC_A_B6

ADC_A_B5

54

ADC_A_B4

53

ADC_A_B3

52

ADC_A_B2

51

ADC_A_B1

50

ADC_A_B0

49

ADC_B_R7

37

ADC_B_R6

36

ADC_B_R5

35

ADC_B_R4

34

ADC_B_R3

33

ADC_B_R2

32

ADC_B_R1

31

ADC_B_R0

30

ADC_B_G7

27

ADC_B_G6

26

ADC_B_G5

25

ADC_B_G4

24

ADC_B_G3

23

ADC_B_G2

22

ADC_B_G1

21

ADC_B_G0

20

ADC_B_B7

17

ADC_B_B6

16

ADC_B_B5

15

ADC_B_B4

14

ADC_B_B3

13

ADC_B_B2

12

ADC_B_B1

11

ADC_B_B0

10

ADC_CLK

44

ADC_DE

46

ADC_VSYNC

47

ADC_HSYNC

48

40

41

42

100

1

4

8

7

OCKINV

DFO

PIXS

/STAG

open

open

3k3

10k

R1703

R1704

R1713

+3.3V

+3.3V

1 pixel/clock

2 pixel/clock

R1715

R1710

open

3k3

open

open

3k3

RGB & control

R1705

R1708

R1706

R1709

ODCK polarity:

+3.3V

Latches output data on rising ODCK edge

Latches output data on falling ODCK edge

Output clock data format:

+3.3V

DSTN support/ODCK held low when DE = low

TFT support/ODCK runs continuously

D

C

B

no Link => Power down Mode of Receiver

A

Title

KIM-17-DVI

Size: Number:

A3

File:

1 2 3 4 5 6 7 8

KIM_MSI-17-DVI.Sch

Revision:

1 1

Sheet of

17 17Date: 29-Jun-2005

Peppercon AG

Scheringerstrasse 1

Zwickau

D-08056

Germany

A

Loading...

Loading...