Page 1

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

DEVELOPMENT NO. Q/M

A

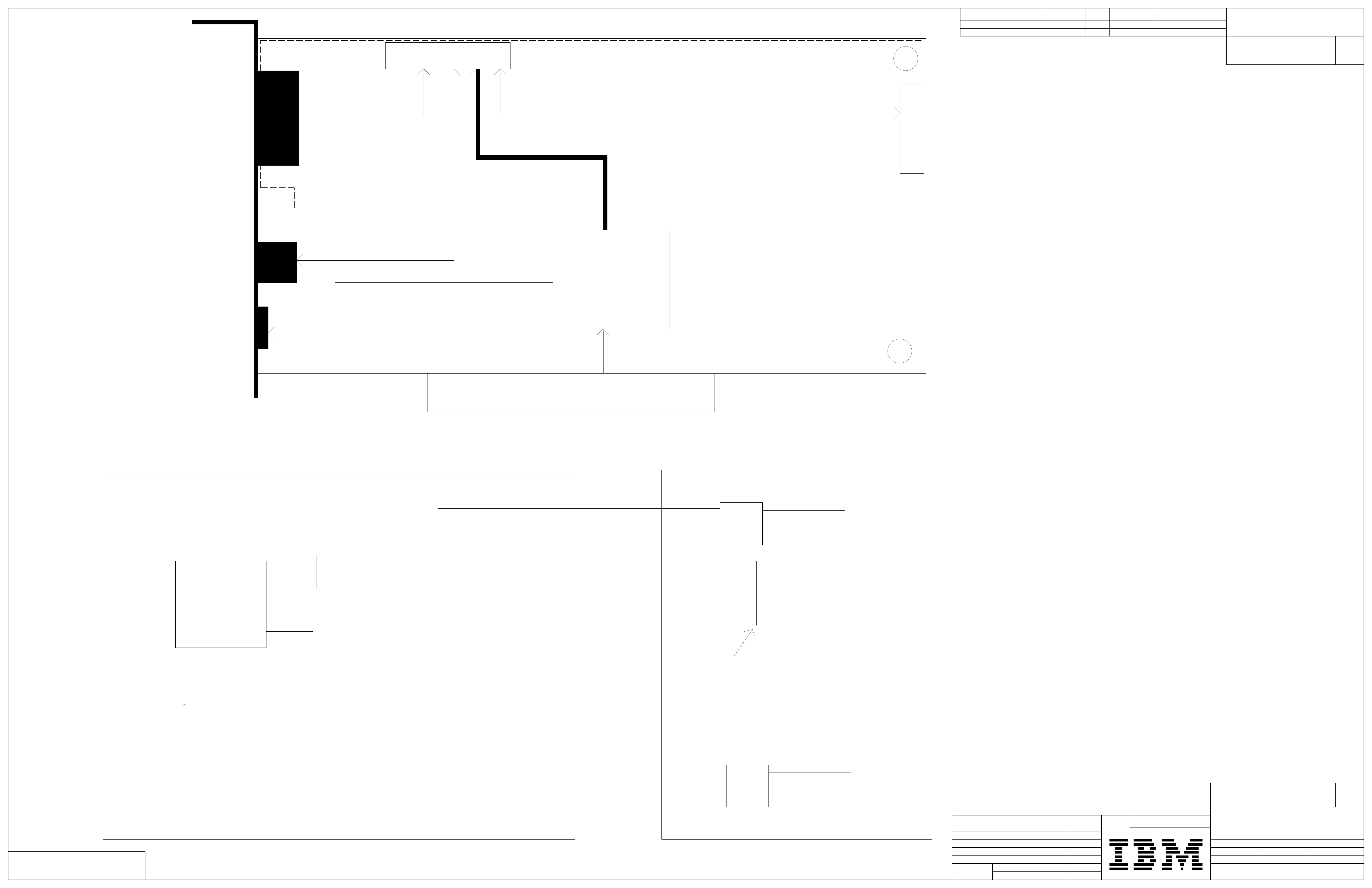

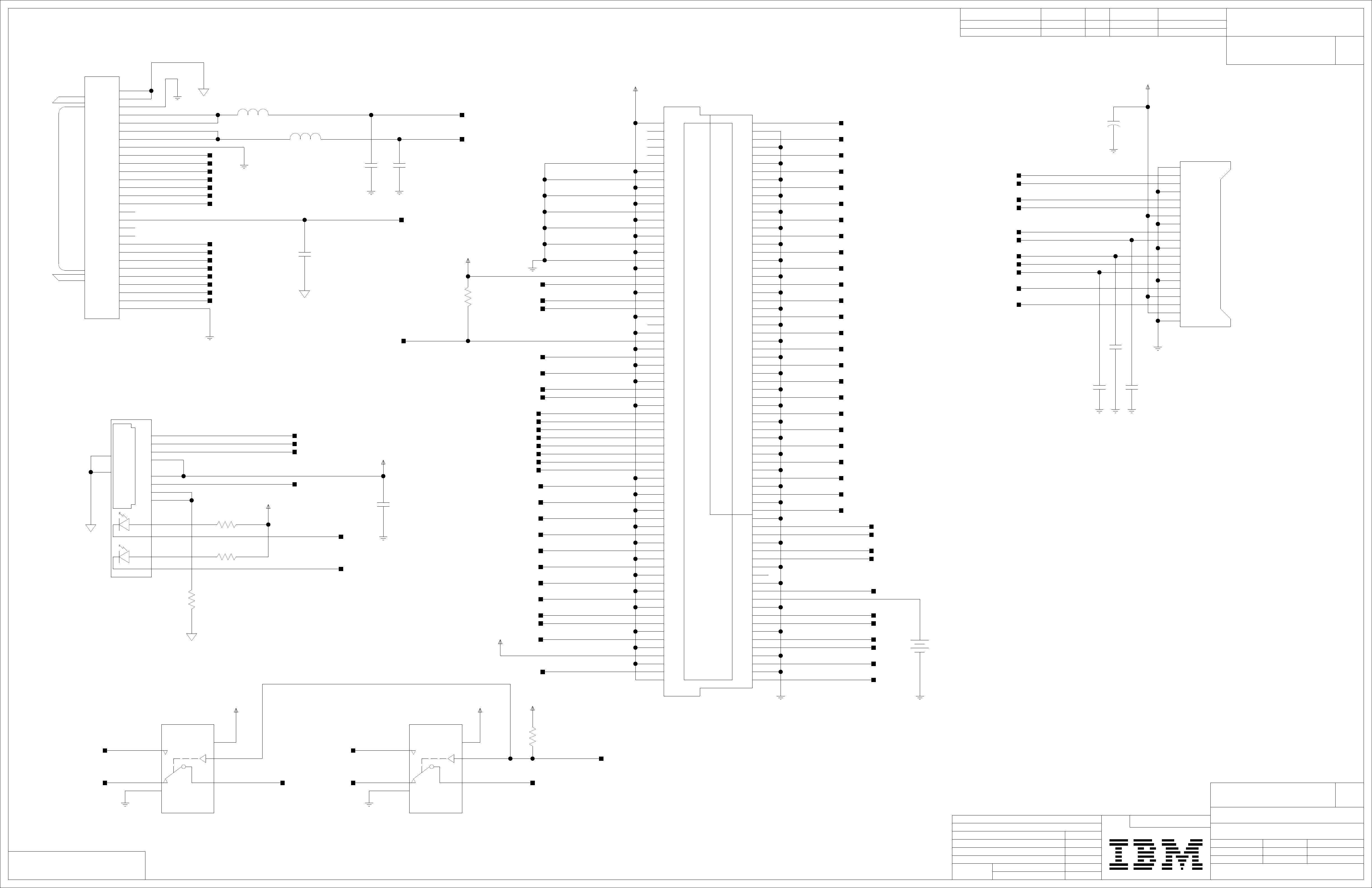

CROW-R SCHEMATICS

B

CONTENTS

Pass2

1. TABLE OF CONTENTS - (MJS)

B

2. CHANGE LOG

C

C

3. CROW BLOCK DIAGRAM

4. PCI EDGE CONNECTOR

5. VIDEO PCI INTERFACE AND DVO

6. VIDEO PWR AND GND

D

7.

VIDEO MEMORY

D

8. ANALOG VIDEO CONNECTOR

9.

10.

CONNECTORS

RS232 DRIVER

11.

E

12.

13.

14.

MECHANICAL PARTS

E

3.3V CONT POWER

1.2V, 1.8V, POWER

SPARE PARTS

15. COMPONENT LIST: A-Y

F

F

G

H

G

H

I

TOC Generated 28 Jan 2005

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

I

PART NO.

39M4939

TITLE

1/1SCALE:

TABLE OF CONTENTS

DESIGNER

CHECKED

APPROVED

6-27-2005_9:24

MJS

SHEET OF

1

108754321

Physical DesignRobert Piper

Les Garrett

15

JJ

Page 2

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

DEVELOPMENT NO. Q/M

A

Change Log:

PASS 1

CHANGED VIDEO TO RN50 - 1/28/05 - RMP

B

CHANGED TO DDR2 MEMORY - 1/28/05 - RMP

Removed COM3 Debug header - 1/28/05 - RMP

PASS 2

Header Code J1MHA Assembly P/N: 39M4941

B

CHANGED TO DDR1 MEMORY - 5/28/05 - RMP

C

Fixed Memory address wiring - 5/28/05 - RMP

C

Added Regulator for DDR1 memory - 5/28/05 - RMP

D

D

E

F

E

F

G

H

G

H

I

PART NO.

I

39M4939

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

CHANGE LOG

6-27-2005_9:24

SHEET OF

2

108754321

Physical DesignRobert Piper

Les Garrett

15

JJ

Page 3

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

DEVELOPMENT NO. Q/M

A

SMP

CONDOR

RS232

B

I2C/USB/misc

Digital Video

B

C

C

Ethernet

Analog Video

D

Video

D

Video

E

Harrier

F

MUX

Com Port Block Diagram

PCI

Crow

E

F

RS232 Driver

External

Debug Header

Bus A

External

G

G

Com1

405GP

Com2

Internal

Bus B

H

H

RS232 Driver

I

RS232 Driver

I

External

PART NO.

39M4939

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

CROW BLOCK DIAGRAM

6-27-2005_9:24

Les Garrett

SHEET OF

3

108754321

Physical DesignRobert Piper

JJ

15

Page 4

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

4/7/02 JWD- Added PRSNT, PME test point, Changed M66EN pull-down to 0-Ohm

DEVELOPMENT NO. Q/M

A

PRIMARY PCI

J31

B

5

5

5

5

5

5

5

5

5

5

5

5

C

5

5

5

5

5

Maximum PCI Power

Aux3 ±5% 375mA max. =1.237 W

3.3 V ±0.3 V 7.6 A max.

5 V ±5% 5 A max.

D

12 V ±5% 500 mA

-12 V ±10% 100 mA

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

E

PCI_3.3V

5

5

5

PPCI_AD0

PPCI_AD1

PPCI_AD2

PPCI_AD3

PPCI_AD4

PPCI_AD5

PPCI_AD6

PPCI_AD7

PPCI_AD8

PPCI_AD9

PPCI_AD10

PPCI_AD11

PPCI_AD12

PPCI_AD13

PPCI_AD14

PPCI_AD15

PPCI_AD16

PPCI_AD17

PPCI_AD18

PPCI_AD19

PPCI_AD20

PPCI_AD21

PPCI_AD22

PPCI_AD23

PPCI_AD24

PPCI_AD25

PPCI_AD26

PPCI_AD27

PPCI_AD28

PPCI_AD29

PPCI_AD30

PPCI_AD31

PPCI_C/BE0_N

PPCI_C/BE1_N

PPCI_C/BE2_N

PPCI_C/BE3_N

A58

B58

A57

B56

A55

B55

A54

B53

B52

A49

B48

A47

B47

A46

B45

A44

A32

B32

A31

B30

A29

B29

A28

B27

A25

B24

A23

B23

A22

B21

A20

B20

A52

B44

B33

B26

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE0#

C/BE1#

C/BE2#

C/BE3#

RSV1

RSV2

RSV3

RSV4

3.3Vaux

PME#

PRSNT1#

PRSNT2#

LOCK#

PERR#

SERR#

REQ64#

ACK64#

SBO#

SDONE

TRST#

TCK

TMS

TDO

TDI

A9

B10

A11

B14

A14

A19

B9

B11

B39

B40

B42

A60

B60

A41

A40

A1

B2

A3

B4

A4

PRSNT1# PRSNT2# Expansion Configuration

Open Open No expansion board present

Ground Open Expansion board present, 25 W maximum

Open Ground Expansion board present, 15 W maximum

Ground Ground Expansion board present, 7.5 W maximum

5

0

R527

0

0

R73

PPCI_SERR#

R72

NOPOP

NOPOP

5/23/02 JWD - Added 0 OHM NOPOP per ATI request

B

C

D

E

CLK

-12V

A6

B7

A7

B8

B16

A15

B49

B1

A2

B3

B15

B17

A18

B22

A24

B28

A30

B34

A35

A37

B38

A42

B46

A48

A56

B57

PPCI_INTA#

PPCI_CLK

PPCI_RST_N

M66EN

5

5

5

11

F

G

H

I

5

C188

C184

C180 C179

C178 C177

C185

C194

C174 C173

C169

C183

5

5

100N

100N 100N

100N 100N

100N

100N

100N 100N

100N 100N

100N

5

5

F

5

5

5

5

G

H

I

PCI_5V

C650 C526

100N

PCI_5V

C172

C525 C524

100N 100N

C171C170

100N100N

C195

100N

C196

100N

C191

100N

C523

100N

C192 C189

100N

C522

100N

C190

100N

100N

100N

C649

PCI_3.3V

100N

100N

PPCI_PAR

PPCI_FRAME_N

PPCI_TRDY_N

PPCI_IRDY_N

PPCI_STOP_N

PPCI_DEVSEL_N

PPCI_IDSEL

PPCI_REQ0_N

PPCI_GNT0_N

PCI_3.3V

PCI_5V

A43

A34

A36

B35

A38

B37

A26

B18

A17

A21

B25

A27

B31

A33

B36

A39

B41

B43

A45

A53

B54

A10

A16

B19

A59

B59

A5

B5

B6

A8

A61

B61

A62

B62

PAR

FRAME#

TRDY#

IRDY#

STOP#

DEVSEL#

IDSEL

REQ#

GNT#

3.3V0

3.3V1

3.3V2

3.3V3

3.3V4

3.3V5

3.3V6

3.3V7

3.3V8

3.3V9

3.3V10

3.3V11

VIO_0

VIO_1

VIO_2

VIO_3

VIO_4

5V0

5V1

5V2

5V3

5V4

5V5

5V6

5V7

INTA#

INTB#

INTC#

INTD#

RESET#

M66EN

+12V

GND0

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

CONN2x60

PCI UNIVERSAL

SILKSCREEN:

ADD SILKSCREEN PIN NUMBER EVERY

5 PINS ON BOTH "A" AND "B" SIDES.

6 9

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

0.13

2.0

PART NO.

39M4939

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

PCI EDGE CONNECTOR

6-27-2005_9:24

Physical DesignRobert Piper

Les Garrett

SHEET OF

4

108754321

15

JJ

Page 5

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

PCI Buffers

U76

P/D_NUM=77P3820

PPCI_AD9

4

4

4

B

4

4

4

4

4

4

C

4

4

4

4

4

4

4

4

D

4

4

4

E

4

4

4

4

4

4

4

4

4

F

4

4

4

4

4

G

4

4

4

4

4

H

4

4

4

4

4

4

4

4

I

4

PPCI_AD7

PPCI_AD6

PPCI_AD2

PPCI_AD1

PPCI_AD0

PPCI_AD3

PPCI_AD4

PPCI_AD5

PPCI_C/BE0_N

R522

PPCI_AD14

PPCI_PAR

PPCI_AD15

PPCI_AD12

PPCI_AD10

PPCI_AD8

PPCI_AD11

PPCI_AD13

PPCI_C/BE1_N

PPCI_SERR#

R521

P/D_NUM=77P3820

PPCI_AD18

PPCI_C/BE2_N

PPCI_IRDY_N

PPCI_DEVSEL_N

PPCI_CLK

PPCI_INTA#

PPCI_STOP_N

PPCI_TRDY_N

PPCI_FRAME_N

PPCI_AD16

R520

R661

PPCI_AD25

PPCI_C/BE3_N

PPCI_AD23

PPCI_AD22

PPCI_AD17

PPCI_AD19

PPCI_AD20

PPCI_AD21

PPCI_IDSEL

PPCI_AD24

R519

R660

P/D_NUM=77P3820

PPCI_RST_N

PPCI_GNT0_N

PPCI_AD31

PPCI_AD29

PPCI_AD28

PPCI_AD26

PPCI_AD27

PPCI_AD30

PPCI_REQ0_N

R81

R518

R659

-The Clock (PCI_CLK) has been buffered.

1K

1K

1K

1K

1K

1K

100

1K

1K

3

1A1

4

1A2

7

1A3

8

1A4

11

1A5

14

2A1

17

2A2

18

2A3

21

2A4

22

2A5

1

1OE#

13 12

2OE# GND

3384

PI3C3384QEX

U72

3

1A1

4

1A2

7

1A3

8

1A4

11

1A5

14

2A1

17

2A2

18

2A3

21

2A4

22

2A5

1

1OE#

13 12

2OE# GND

3384

PI3C3384QEX

U73

3

1A1

4

1A2

7

1A3

8

1A4

11

1A5

14

2A1

17

2A2

18

2A3

21

2A4

22

2A5

1

1OE#

13 12

2OE# GND

3384

PI3C3384QEX

U74

3

1A1

4

1A2

7

1A3

8

1A4

11

1A5

14

2A1

17

2A2

18

2A3

21

2A4

22

2A5

1

1OE#

13 12

2OE# GND

3384

PI3C3384QEX

U75

3

1A1

4

1A2

7

1A3

8

1A4

11

1A5

14

2A1

17

2A2

18

2A3

21

2A4

22

2A5

1

1OE#

13 12

2OE# GND

3384

PI3C3384QEX

VCC

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

VCC

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

VCC

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

VCC

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

VCC

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

24

2

5

6

9

10

15

16

19

20

23

24P/D_NUM=77P3820

2

5

6

9

10

15

16

19

20

23

24

2

5

6

9

10

15

16

19

20

23

24P/D_NUM=77P3820

2

5

6

9

10

15

16

19

20

23

24

2

5

6

9

10

15

16

19

20

23

PCI_3.3V

3V_PPCI_AD9

3V_PPCI_AD7

3V_PPCI_AD6

3V_PPCI_AD2

3V_PPCI_AD1

3V_PPCI_AD0

3V_PPCI_AD3

3V_PPCI_AD4

3V_PPCI_AD5

3V_PPCI_C/BE0_N

PCI_3.3V

3V_PPCI_AD14

3V_PPCI_PAR

3V_PPCI_AD15

3V_PPCI_AD12

3V_PPCI_AD10

3V_PPCI_AD8

3V_PPCI_AD11

3V_PPCI_AD13

3V_PPCI_C/BE1_N

3V_PPCI_SERR#

PCI_3.3V

3V_PPCI_AD18

3V_PPCI_C/BE2_N

3V_PPCI_IRDY_N

3V_PPCI_DEVSEL_N

3V_PPCI_CLK

3V_PPCI_INTA#

3V_PPCI_STOP_N

3V_PPCI_TRDY_N

3V_PPCI_FRAME_N

3V_PPCI_AD16

PCI_3.3V

3V_PPCI_AD25

3V_PPCI_C/BE3_N

3V_PPCI_AD23

3V_PPCI_AD22

3V_PPCI_AD17

3V_PPCI_AD19

3V_PPCI_AD20

3V_PPCI_AD21

3V_PPCI_IDSEL

3V_PPCI_AD24

PCI_3.3V

3V_PPCI_RST_N

3V_PPCI_GNT0_N

3V_PPCI_AD31

3V_PPCI_AD29

3V_PPCI_AD28

3V_PPCI_AD26

3V_PPCI_AD27

3V_PPCI_AD30

3V_PPCI_REQ0_N

R80

100

54

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5,9

5

5

5

5

5

5

5

5

R24

R25

0 0

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5,9

5

5

5

5

5

5

5

5

5

5

SR4

3V_PPCI_AD0

3V_PPCI_AD1

3V_PPCI_AD2

3V_PPCI_AD3

3V_PPCI_AD4

3V_PPCI_AD5

3V_PPCI_AD6

3V_PPCI_AD7

3V_PPCI_AD8

3V_PPCI_AD9

3V_PPCI_AD10

3V_PPCI_AD11

3V_PPCI_AD12

3V_PPCI_AD13

3V_PPCI_AD14

3V_PPCI_AD15

3V_PPCI_AD16

3V_PPCI_AD17

3V_PPCI_AD18

3V_PPCI_AD19

3V_PPCI_AD20

3V_PPCI_AD21

3V_PPCI_AD22

3V_PPCI_AD23

3V_PPCI_AD24

3V_PPCI_AD25

3V_PPCI_AD26

3V_PPCI_AD27

3V_PPCI_AD28

3V_PPCI_AD29

3V_PPCI_AD30

3V_PPCI_AD31

3V_PPCI_IDSEL

3V_PPCI_C/BE0_N

3V_PPCI_C/BE1_N

3V_PPCI_C/BE2_N

3V_PPCI_C/BE3_N

3V_PPCI_CLK

3V_PPCI_RST_N

3V_PPCI_DEVSEL_N

3V_PPCI_FRAME_N

3V_PPCI_INTA#

3V_PPCI_IRDY_N

3V_PPCI_PAR

3V_PPCI_SERR#

3V_PPCI_STOP_N

3V_PPCI_TRDY_N

3V_PPCI_REQ0_N

3V_PPCI_GNT0_N

TP_PPCI_VREF

TP_TESTEN

1K

RN50_XTALIN

5

RN50_XTALOUT

5

0

R22

R23

0

AB21

AA21

Y21

AB20

AA20

Y20

AB19

Y19

AB18

AA18

Y18

AB17

AA17

Y17

AB16

AA16

Y13

AA12

Y12

AB11

AA11

Y11

AB10

AA10

Y9

AB8

AA8

Y8

AB7

AA7

Y7

AA6

Y10

AA19

AB15

AA13

AA9

Y16

AB5

Y15

Y14

W18

AB13

AA15

Y6

AA5

AA14

AB14

Y5

W5

Y3

AA3

V22

U21

V21

Place all components close to BGA

C657

RN50_XTALIN

5

Y1

27

MHz

5 RN50_XTALOUT

423

1MEG

1

R64

10P

C656

10P

UPDATE P/N

AD_0

AD_1

AD_2

AD_3

AD_4

AD_5

AD_6

AD_7

AD_8

AD_9

AD_10

AD_11

AD_12

AD_13

AD_14

AD_15

AD_16

AD_17

AD_18

AD_19

AD_20

AD_21

AD_22

AD_23

AD_24

AD_25

AD_26

AD_27

AD_28

AD_29

AD_30

AD_31

IDSEL

CBE0_N

CBE1_N

CBE2_N

CBE3_N

PCICLK

RESET_N

DEVSEL_N

FRAME_N

INTROUT_N

IRDY_N

PAR

SERR_N

STOP_N

TRDY_N

REQ_N

GNT_N

NC_W5

TEST_MCLK

TEST_YCLK

TESTEN

XTALIN

XTALOUT

U1

ATI_RN50

SIGNAL

1 of 4

V

3.3

DVO INTERFACE

PCI INTERFACE

INTERFACE

TEST

XTAL

DAC2 INTERFACE DAC INTERFACE GPIO INTERFACE

LCDCNTL_0

LCDCNTL_1

LCDCNTL_2

LCDCNTL_3

LCDDATA_0

LCDDATA_1

LCDDATA_2

LCDDATA_3

LCDDATA_4

LCDDATA_5

LCDDATA_6

LCDDATA_7

LCDDATA_8

LCDDATA_9

LCDDATA_10

LCDDATA_11

LCDDATA_12

LCDDATA_13

LCDDATA_14

LCDDATA_15

LCDDATA_16

LCDDATA_17

LCDDATA_18

LCDDATA_19

LCDDATA_20

LCDDATA_21

LCDDATA_22

LCDDATA_23

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

HSYNC

VSYNC

VGADDCCLK

VGADDCDAT

RSET

R2

G2

B2

H2SYNC

V2SYNC

CRT2DDCCLK

CRT2DDCDAT

R2SET

B21

C21

A20

B20

C20

A19

B19

C19

A18

B18

C18

A17

B17

C17

A16

B16

C16

A15

B15

C15

A14

B14

C14

A13

B13

C13

B12

C12

A12

C11

B11

A11

C10

B10

A10

C9

B9

A9

C8

B8

A8

C7

B7

F22

R

G21

G

G22

B

T22

U22

T20

T21

F21

K21

L22

L21

P21

P20

R20

R21

K22

EXT_TMDS_VSYNC

EXT_TMDS_HSYNC

EXT_TMDS_DE

EXT_TMDS_CLK

TP_EXT_TMDS_BLU0

EXT_TMDS_BLU1

EXT_TMDS_BLU2

EXT_TMDS_BLU3

EXT_TMDS_BLU4

EXT_TMDS_BLU5

EXT_TMDS_BLU6

EXT_TMDS_BLU7

TP_EXT_TMDS_GRN0

EXT_TMDS_GRN1

EXT_TMDS_GRN2

EXT_TMDS_GRN3

EXT_TMDS_GRN4

EXT_TMDS_GRN5

EXT_TMDS_GRN6

EXT_TMDS_GRN7

TP_EXT_TMDS_RED0

EXT_TMDS_RED1

EXT_TMDS_RED2

EXT_TMDS_RED3

EXT_TMDS_RED4

EXT_TMDS_RED5

EXT_TMDS_RED6

EXT_TMDS_RED7

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

VEEPROM_DAT

VEEPROM_CLK

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

VIDEO_RED

VIDEO_GREEN

VIDEO_BLUE

VIDEO_HSYNC

VIDEO_VSYNC

ATI_DDCCLK

ATI_DDCDAT

SR2

+1%/-1%

TP_RED2

TP_GREEN2

TP_BLUE2

TP_H2SYNC

TP_V2SYNC

TP_DDC_CLK

TP_DDC_DAT

R2SET

6 9

5

5

5

5

5,11

5

5

5

5

5

5

5

5

499

5,8

5,8

5,8

8

8

8

8

5

5

5

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

9

5

5

5

5

VID_R_ROM_CS

7

GPIO_8

5

VEEPROM_CLK

VEEPROM_DAT

STRAPS

PCIFBSKEW(1:0)

X1CLK_SKEW(1:0)

ROMIDCFG(2:0)

BUSCFG GPIO(4)

VGA_DISABLE

The default values outlines in the table above are with respect to these logics-not the video chip.

PCI_3.3V

R626

10K

VEN_P/D_NUM=M25P10-AVMN6P

PCI_3.3V

EEPROM_AT24C01A-10SU-1_8

PIN DESCRIPTION

GPIO(1:0)

GPIO(3:2) CLOCK PHASE ADJUSTMENT BETWEEN X1 CLK AND X2 CLK

GPIO(13:11)

GPIO(8)ID_DISABLE

PCI CLOCK FEEDBACK PHASE ADJUSTMENT FOR PCI66

00 = 0 tap delay from default

01 = -1 tap delay from default

10 = +1 taps delay from default

11 = -2 taps delay from default

00- 0 TAP DELAY

01-1 TAP DELAY

10-2 TAP DELAY

11-3 TAP DELAY

IF NO ROM ATTACHED, CONTROLS CHIP IDS.

IF ROM ATTACHED IDENTIFIES ROM TYPE

000-NO ROM (VIDEO BIOS INTEGRATED INTO SYSTEM BIOS)

001-RESERVED

010-RESERVED

011-RESERVED

100-RESERVED

101-SERIAL AT25F1024ROM (ATMEL), CHIP ID IS FROM ROM

110-SERIAL ST MICRO M25P10/M25P05 ROM (ST), CHIP ID FROM ROM

111-SERIAL NEXFLASH NX25F011B/NX25F015B ROM (ISSI)

CHIP ID IS FROM ROM

0-NORMAL OPERATION

1-SHUTS THE CHIP DOWN BY NOT RESPONDING TO ANY CONFIG

CYCLES. IN A SYSTEM WITH TWO GRAPHICS CHIPS, ONE ON THE

MOTHERBOARD, THE OTHER ON AN ADD-IN CARD, THE STRAP CAN BE

USED TO DISABLE ONE OF THE TWO THROUGH A JUMER

BUS_CFG

0 = PCI 66MHz (default)

1 = PCI 33MHz(PLL bypass)

0-VGA CONTROLLER CAPABILITY ENABLINGGPIO(7)

1-THE DEVICE WILL NOT BE RECOGNIZED AS THE SYSTEM VGA COTROLLER

PCI_3.3V

Change Part

U90

EEPROM_SERIAL_SPI

1 8

S_N VCC

2

Q

3

W_N

4

GND

P/D_NUM=77P4341

U89

EEPROM

8 1

7

5

A0_NC

VCC

WP_NC

A2_NC

SCL

SDA

SERIAL-I2C

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

A1

GND

2

36

4

OUTSIDE MAX

INSIDE MAX

HOLD_N

7

6

C

5

D

C661

NOPOP

R530

R529

R5372KR5382KR539

GPIO_10

GPIO_9

100N

PCI_3.3V

NOPOP

R531

4.7K

0.13

2.0

NOPOP

4.7K

4.7K

2K

DEFAULT

INTERNAL

PULL-DWN

INTERNAL

PULL-DWN

000

INTERNAL

PULL-DWN

1

INTERNAL

PULL-DWN

5

5

Check POP/ NOPOP

5

5

5

5

5,11

5

5

5

5

5

5

5

5

5

5

5,8

5,8

5,8

5

1/1SCALE:

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_8

VIDEO_RED

VIDEO_GREEN

VIDEO_BLUE

R2SET

DEVELOPMENT NO. Q/M

PCI_3.3V

R627

NOPOP

4.7K

R628

POP

4.7K

R629

NOPOP

NOPOP

R632

4.7K

POP

NOPOP

R638

4.7K

NOPOP

POP

R643

4.7K

NOPOP

R646

4.7K

POP

POP

R652

4.7K

NOPOP

R655

4.7K

4.7K

POP

R635

4.7K

NOPOP

NOPOP

NOPOP

R649

4.7K

NOPOP

NOPOP

PART NO.

R573

R574

R575

R557

R630

4.7K

R636

4.7K

R639

4.7K

R641

4.7K

R644

4.7K

R650

4.7K

R653

4.7K

R656

4.7K

+1%/-1%

+1%/-1%

+1%/-1%

+1%/-1%

R633

4.7K

NOPOP

NOPOP

R645

4.7K

R647

4.7K

POP

POP

R631

4.7K

NOPOP

R634

4.7K

NOPOP

R637

4.7K

R640

4.7K

NOPOP

R642

4.7K

NOPOP

R648

4.7K

NOPOP

R651

4.7K

NOPOP

R654

4.7K

75

75

75

499

39M4939

TITLE

VIDEO PCI INTERFACE AND DVO

6-27-2005_9:24

DESIGNER

CHECKED

APPROVED

SHEET OF

5

108754321

Physical DesignRobert Piper

Les Garrett

15

A

B

C

D

E

F

G

H

I

JJ

Page 6

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

1_2V

Place caps close to VDDC balls

B

ATI_RN50

A21

VSS_A21

B2 L12

VSS_B2 VSS_L12

B22

VSS_B22

2_5V

1_2V

U1

B3

C

D

PCI_3.3V

E

1_8V

DAC_1.8

F

G

6

DAC2_1.8

6

AVDDI_1.8

6

PCI_3.3V

VDDR1_B3

B5

VDDR1_B5

B6

VDDR1_B6

E2

VDDR1_E2

E4

VDDR1_E4

F4

VDDR1_F4

G4

VDDR1_G4

H4

VDDR1_H4

J2

VDDR1_J2

J4

VDDR1_J4

N2

VDDR1_N2

P4

VDDR1_P4

R4

VDDR1_R4

T4

VDDR1_T4

U2

VDDR1_U2

U4

VDDR1_U4

W3

VDDR1_W3

D7

VDDR3_D7

D8

VDDR3_D8

D9

VDDR3_D9

T19

VDDR3_T19

U19

VDDR3_U19

V19

VDDR3_V19

W19

VDDR3_W19

D12

VDDR4_D12

D13

VDDR4_D13

D14

VDDR4_D14

D18

VDDR4_D18

D19

VDDR4_D19

D20

VDDR4_D20

F19

AVDD_F19

F20

AVDD_F20

J20

A2VDD_J20

J21

A2VDD_J21

H20

AVDDDI_H20

M20

A2VDDDI_M20

E5

PESD_E5

J5

PESD_J5

N5

PESD_N5

ATI_RN50

POWER

3 of 4

V

3.3

VDDC_D22

VDDC_E19

VDDC_E20

VDDC_E21

VDDC_G7

VDDC_G8

VDDC_G9

VDDC_G15

VDDC_G16

VDDC_H7

VDDC_H16

VDDC_J16

VDDC_J19

VDDC_K19

VDDC_M22

VDDC_N19

VDDC_N20

VDDC_N21

VDDC_N22

VDDC_P7

VDDC_R7

VDDC_R16

VDDC_T7

VDDC_T8

VDDC_T14

VDDC_T15

VDDC_T16

VDDC18_F6

VDDC18_F17

VDDC18_U6

VDDC18_U17

VDDP_W6

VDDP_W7

VDDP_W8

VDDP_W9

VDDP_W14

VDDP_W15

VDDP_W16

VDDP_W17

MPVDD_Y1

PVDD_V20

D22

E19

E20

E21

G7

G8

G9

G15

G16

H7

H16

J16

J19

K19

M22

N19

N20

N21

N22

P7

R7

R16

T7

T8

T14

T15

T16

F6

F17

U6

U17

W6

W7

W8

W9

W14

W15

W16

W17

Y1

V20

MEMPLL1.8

PLL1.8

1_8V

PCI_3.3V

6

6

C2

VSS_C2

C6

VSS_C6

C22

VSS_C22

D4

VSS_D4

D5

VSS_D5

D6

VSS_D6

D10

VSS_D10

D11

VSS_D11

D15

VSS_D15

D16

VSS_D16

D17

VSS_D17

D21

VSS_D21

G2

VSS_G2

H9

VSS_H9

H10

VSS_H10

H11

VSS_H11

H12

VSS_H12

H13

VSS_H13

H14

VSS_H14

H22

VSS_H22

J8

VSS_J8

J9

VSS_J9

J10

VSS_J10

J11

VSS_J11

J12

VSS_J12

J13

VSS_J13

J14

VSS_J14

J15

VSS_J15

J22

VSS_J22

K4

VSS_K4

K8

VSS_K8

K9

VSS_K9

K10

VSS_K10

K11

VSS_K11

K12

VSS_K12

K13

VSS_K13

K14

VSS_K14

K15

VSS_K15

L2

VSS_L2

L4

VSS_L4

L8

VSS_L8

L9

VSS_L9

L10

VSS_L10

G19

AVSSN_G19

H19

AVSSN_H19

K20

A2VSSN_K20

L20

A2VSSN_L20

G20

AVSSQ_G20

M21

A2VSSQ_M21

H21

AVSSDI_H21

L19

A2VSSDI_L19

W1

MPVSS_W1

U20

PVSS_U20

U1

GROUND

4 of 4

V

3.3

VSS_L11

VSS_L13

VSS_L14

VSS_L15

VSS_M4

VSS_M8

VSS_M9

VSS_M10

VSS_M11

VSS_M12

VSS_M13

VSS_M14

VSS_M15

VSS_M19

VSS_N4

VSS_N8

VSS_N9

VSS_N10

VSS_N11

VSS_N12

VSS_N13

VSS_N14

VSS_N15

VSS_P8

VSS_P9

VSS_P10

VSS_P11

VSS_P12

VSS_P13

VSS_P14

VSS_P15

VSS_P19

VSS_P22

VSS_R2

VSS_R9

VSS_R10

VSS_R11

VSS_R12

VSS_R13

VSS_R14

VSS_R19

VSS_V1

VSS_V4

VSS_W2

VSS_W4

VSS_W10

VSS_W11

VSS_W12

VSS_W13

VSS_W20

VSS_W21

VSS_W22

VSS_Y4

VSS_Y22

VSS_AA4

VSS_AA22

VSS_AB2

VSS_AB3

L11

L13

L14

L15

M4

M8

M9

M10

M11

M12

M13

M14

M15

M19

N4

N8

N9

N10

N11

N12

N13

N14

N15

P8

P9

P10

P11

P12

P13

P14

P15

P19

P22

R2

R9

R10

R11

R12

R13

R14

R19

V1

V4

W2

W4

W10

W11

W12

W13

W20

W21

W22

Y4

Y22

AA4

AA22

AB2

AB3

1_8V

L63

IND2P_FE_BLM21BB201SN1L

IND2P_FE_BLM21BB201SN1L

IND2P_FE_BLM21BB201SN1L

IND2P_FE_BLM21BB201SN1L

IND2P_FE_BLM21BB201SN1L

200

L62

200

L64

200

L65

200

L66

200

C679 C678

100N

Place caps close to AVDD balls

ohms

Place caps close to AVDD2 balls

ohms

Place caps close to VDDI balls

ohms

100N

Place caps close to MPVDD balls

ohms

C718

Place caps close to PVDD balls

ohms

C717

C658

10U

C659

10U

C666 C695

100N

C715

C720

10U

C670

4.7U

4.7U

100N

C684

C683

4.7U

C668

C669

C712

10N

2.2U10U

2.2U

AVDDI_1.8

C660

MEMPLL1.8

100N

PLL1.8

100N

10N

DAC2_1.8

DAC_1.8

C690C689

6

6

6

6

6

C692C691

10N10N

C694C693

10N10N

C716 C674

C685

10N10N

Place caps close to VDDR4 balls

C719

10U

Place caps close to VDDC balls

C677

10U 100N

C706

10U

10N

C675

100N 10N

C680

C667 C703

100N

C673 C672

100N 100N

C676

100N 10N

C710

100N

C665 C688

100N

C711

10N

C702 C701

10N 10N

1_8V

C671

100N 100N

C708C709

10N10N

PCI_3.3V

C713

10N

Place caps evenly around VDDP, PESD, and VDDR3 balls

C687

DEVELOPMENT NO. Q/M

1_2V

C700 C699

10N 10N

C681

C707

C686 C7141UC682

10N 10N

C664

100N

10N10N

C698 C697

10N 10N

1_8V

C663 C662

100N 100N

2_5V

C704C705

10N

C696

10N 10N

100N

22U

A

B

C

D

E

F

G

H

A

I

R658

0

A

PART NO.

H

I

39M4939

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

6-27-2005_9:24

DESIGNER

CHECKED

APPROVED

VIDEO PWR AND GND

Physical DesignRobert Piper

Les Garrett

SHEET OF

6

108754321

15

JJ

Page 7

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

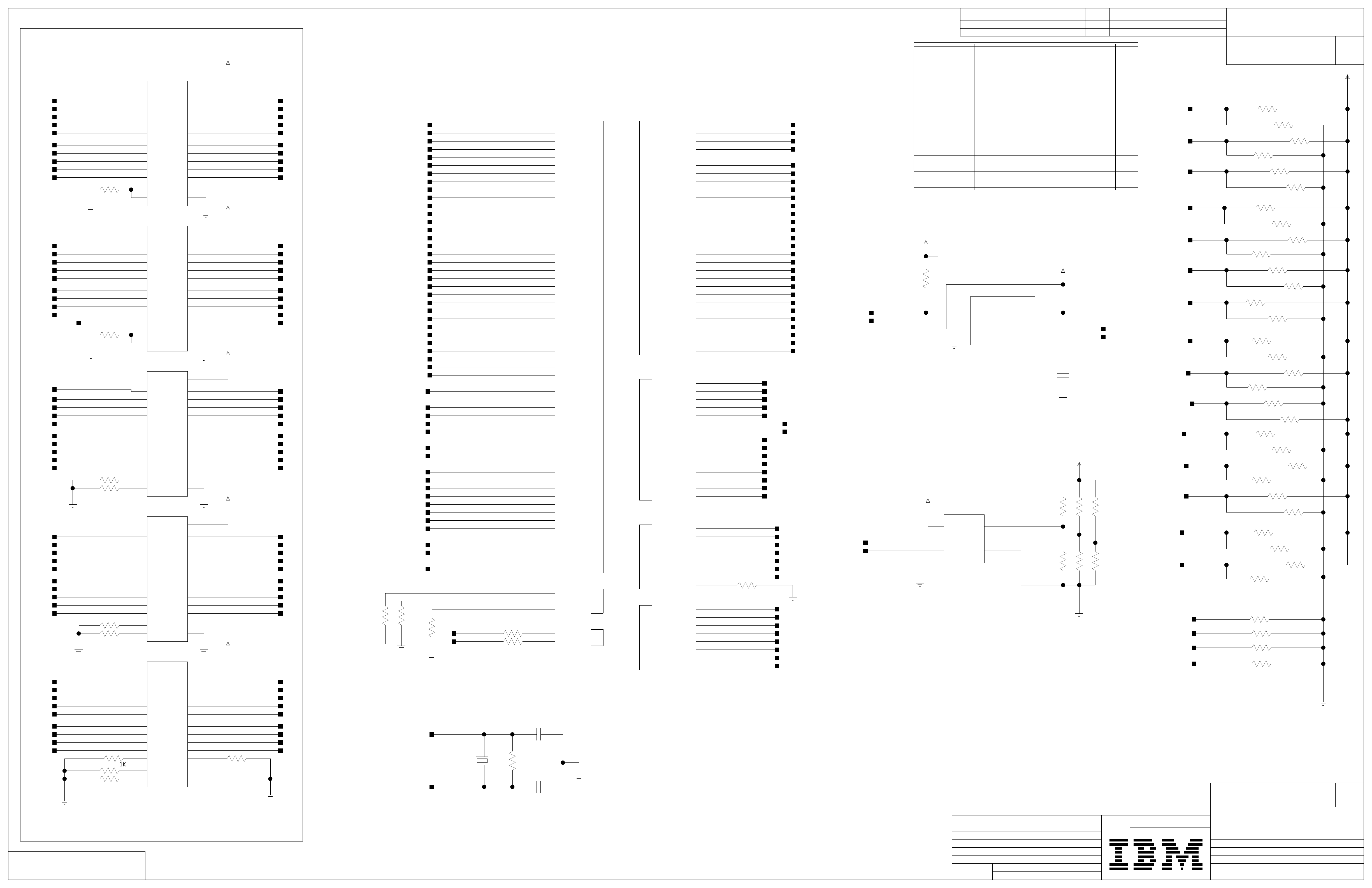

VIDEO MEMORY INTERFACE

DEVELOPMENT NO. Q/M

A

2_5V

VIDEO_MEM_A[0:15]

7

VIDEO_MEM_A0

VIDEO_MEM_A1

VIDEO_MEM_A2

VIDEO_MEM_A3

B

VIDEO_MEM_A4

VIDEO_MEM_A5

VIDEO_MEM_A6

VIDEO_MEM_A7

VIDEO_MEM_A8

VIDEO_MEM_A9

VIDEO_MEM_A10

VIDEO_MEM_A11

VIDEO_MEM_A12

VIDEO_MEM_A13

VIDEO_MEM_A14

C

VID_R_ROM_CS

5

VIDEO_MEM_A15

VIDEO_MEM_CLK_P

7

VIDEO_MEM_CLK_N

7

VIDEO_MEM_CKE

7

7

7

MEMMODE_0

MEMMODE_1

R657 22

0402

VID_ROMCS_N

D

7

MEM_VREF

P1

MEM_A0

N1

MEM_A1

P2

MEM_A2

T3

MEM_A3

R1

MEM_A4

R3

MEM_A5

P3

MEM_A6

M1

MEM_A7

M3

MEM_A8

U3

MEM_A9

T1

MEM_A10

T2

MEM_A11

M2

MEM_A12

L3

MEM_A13

L1

MEM_A14

N3

MEM_A15

H2

MEM_CLK_P

H3

MEM_CLK_N

K1

MEM_CKE

V3

MEMVMODE_0

V2

MEMVMODE_1

A7

ROMCS_N

AA2

MEM_VREFD

Y2

MEM_VREFS

AA1

MEMTEST

MEMORY INTERFACE

R29

44.2

+1%/-1%

This pin is used to control the variable

drive capability of the memory section

I/Os. It is connected to memory VSS

through a 45ohm +/-1% resistor.

E

1_8V

MEMMODE_0

7

F

MEMMODE_1

7

R33

R34

4.7K

R31

R32

NOPOP

4.7K

NOPOP

4.7K

4.7K

Determine voltage value for S(D/G)RAM chips

MEMVMODE_1 MEMVMODE_0 I/O Voltage

1.8V

0V

0V

U1

ATI_RN50

2 of 4

V

3.3

1.8V

2.5V1.8V

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQM0

MEM_DQM1

MEM_CS_N

MEM_ODT

MEM_QS0

MEM_QS1

MEM_RAS_N

MEM_CAS_N

MEM_WE_N

A5

A6

C5

A4

C4

A2

A3

D3

E1

F2

G3

F3

E3

D2

C1

B1

C3

G1

K2

H1

B4

D1

K3

J3

J1

VIDEO_MEM_CLK_P

7

VIDEO_MEM_DQ0

VIDEO_MEM_DQ1

VIDEO_MEM_DQ2

VIDEO_MEM_DQ3

VIDEO_MEM_DQ4

VIDEO_MEM_DQ5

VIDEO_MEM_DQ6

VIDEO_MEM_DQ7

VIDEO_MEM_DQ8

VIDEO_MEM_DQ9

VIDEO_MEM_DQ10

VIDEO_MEM_DQ11

VIDEO_MEM_DQ12

VIDEO_MEM_DQ13

VIDEO_MEM_DQ14

VIDEO_MEM_DQ15

VIDEO_MEM_DQM0

VIDEO_MEM_DQM1

VIDEO_MEM_CS_N

VIDEO_MEM_ODT

VIDEO_MEM_QS0

VIDEO_MEM_QS1

VIDEO_MEM_RAS_N

VIDEO_MEM_CAS_N

VIDEO_MEM_WE_N

VIDEO_MEM_DQ[0:15]

7

7

7

7

7

7

7

7

R601 22

0402

7

R622

56

0402

MEM_CLK_R_DIV

R621

56

C653

10N

MEM_CLK_P

0402

U92

1

VDD_1

18

VDD_18

33

VDD_33

3

VDDQ_3

9

VDDQ_9

15

VDDQ_15

55

VDDQ_55

61

VDDQ_61

VIDEO_MEM_A[0:15]

7

VIDEO_MEM_A0

1 8

VIDEO_MEM_A1

VIDEO_MEM_A2

4 5

VIDEO_MEM_A3

VIDEO_MEM_A4

3 6

VIDEO_MEM_A5

VIDEO_MEM_A6

1 8

VIDEO_MEM_A7

VIDEO_MEM_A8

3 6

VIDEO_MEM_A9

VIDEO_MEM_A10

2 7

VIDEO_MEM_A11

VIDEO_MEM_A12

2 7

VIDEO_MEM_A13

VIDEO_MEM_A14

1 8

VIDEO_MEM_A15

VIDEO_MEM_CS_N

7

VIDEO_MEM_RAS_N

7

VIDEO_MEM_CAS_N

7

VIDEO_MEM_WE_N

7

VIDEO_MEM_DQM0

7

VIDEO_MEM_DQM1

7

VIDEO_MEM_CKE

7

7

MEM_CLK_P

7

MEM_CLK_N

7

R595 22

R597 22

R591 22

R599 22

7

RN2

RN1

RN1

RN4

RN3

RN1

RN3

RN3

0402

0402

0402

0402

DDR1_VREF

22

22

22

22

22

22

22

22

RN2

2 7

RN4

3 6

RN4

2 7

RN2

3 6

RN4

4 5

RN1

1 8

RN3

4 5

RN2

4 5

R598 22

0402

R596 22

0402

R592 22

MEM_A0

MEM_A1

22

MEM_A2

MEM_A3

22

MEM_A4

MEM_A5

22

MEM_A6

MEM_A7

22

MEM_A8

MEM_A9

22

MEM_A10

MEM_A11

22

MEM_A12

MEM_A13

22

MEM_A14

22

MEM_A15

MEM_CS_N

MEM_RAS_N

MEM_WE_N

MEM_LDM

MEM_UDM

0402

49

29

30

31

32

35

36

37

38

39

40

28

41

42

17

26

27

24

23

22

21

20

47

44

45

46

VREF

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10_AP

A11

A12

A13_NC

BA0

BA1

CS_N

RAS_N

CAS_N

WE_N

LDQM

UDQM

CKE

CK

CK_N

DRAM16MX16

LDQS

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

UDQS

NC_14

NC_DNU_19

NC_25

NC_43

NC_DNU_50

NC_53

GND_34

GND_48

GND_66

GNDQ_6

GNDQ_12

GNDQ_52

GNDQ_58

GNDQ_64

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

2

4

5

7

8

10

11

13

16

54

56

MEM_DQ9

57

59

60

62

63

65

51

14

19

25

43

50

53

34

48

66

6

12

52

58

64

TP_VIDEOMEM_NC_14

TP_VIDEOMEM_NC_19

TP_VIDEOMEM_NC_25

TP_VIDEOMEM_NC_43

TP_VIDEOMEM_NC_50

TP_VIDEOMEM_NC_53

TSOP66

DRAM_MT46V16M16TG-75Z

P/D_NUM=77P3910

Place resistors close to

DDR1 SDRAM memory module.

RN8

2 7

RN8

4 5

RN5

1 8

RN5

3 6

R593 22

0402

RN7

3 6

RN7

2 7

RN6

1 8

RN6

4 5

R594 22

0402

33

33

33

33

33

33

33

33

VIDEO_MEM_QS1

2 7

4 5

3 6

1 8

VIDEO_MEM_QS0

3 6

2 7

4 5

1 8

RN5

RN5

RN8

RN8

RN6

RN6

RN7

RN7

33

VIDEO_MEM_DQ0

VIDEO_MEM_DQ1

33

VIDEO_MEM_DQ2

VIDEO_MEM_DQ3

33

VIDEO_MEM_DQ4

VIDEO_MEM_DQ5

33

VIDEO_MEM_DQ6

VIDEO_MEM_DQ7

33

VIDEO_MEM_DQ8

VIDEO_MEM_DQ9

33

VIDEO_MEM_DQ10

VIDEO_MEM_DQ11

33

VIDEO_MEM_DQ12

VIDEO_MEM_DQ13

33

VIDEO_MEM_DQ14

VIDEO_MEM_DQ15

VIDEO_MEM_DQ[0:15]

7

B

7

C

7

D

E

F

0402

VIDEO_MEM_CLK_N

7

R602 22

0402

MEM_CLK_N

7

G

G

2_5V

Place caps close to VDD balls

2_5V

C729

C728 C727

10N

10N

C726 C725

10N 10N

C724

10N 10N

R565

1_8V

R559

C723

C722

10U 100N

C721 C731

100N

C730

10N 10N

H

H

100

+1%/-1%

MEM_VREF

+1%/-1%

7

4.99K

0402

DDR1_VREF

7

R566

100

+1%/-1%

C641

0402

100N

R558

+1%/-1%

4.99K

0402

C638

0402

100N

I

I

PART NO.

39M4939

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

0.13

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

2.0

6 9

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

VIDEO MEMORY

6-27-2005_9:24

SHEET OF

7

108754321

Physical DesignRobert Piper

Les Garrett

15

JJ

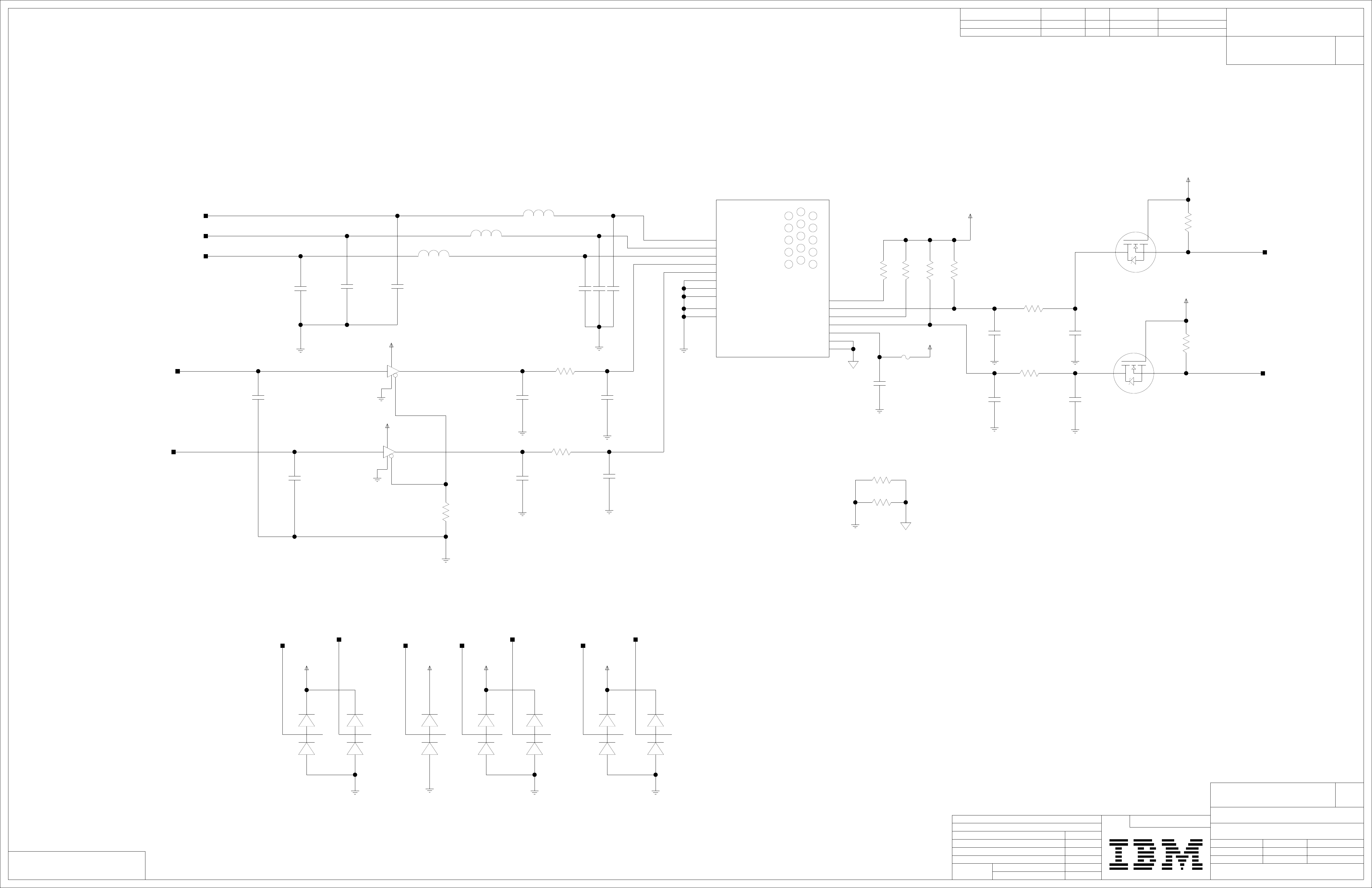

Page 8

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

DEVELOPMENT NO. Q/M

4/7/02 JWD Changed 5V symbol, Changed ESD back to 5V

01/15/03 JWD Placed two 0 ohm resistors between chassis ground and signal ground to fix EMC problem.

B

PCI_3.3V

A

B

PLEASE REFER TO UPDATED IN DXDATABOOK

J5

L4

5,8

C

5,8

5,8

D

VIDEO_HSYNC5

E

VIDEO_RED

VIDEO_GREEN

VIDEO_BLUE

C59

10P

NOPOP

15P

C636

15P

C634

AHCT125_SO14N

15P

PCI_5V

U7

14

5

7

L2

IND2P_FE_HF30ACB-321611-T

C635

6

4

19

L3

IND2P_FE_HF30ACB-321611-T

ohms

HSYNC_BUF

19

IND2P_FE_HF30ACB-321611-T

ohms

C60

19

100P

NOPOP

ohms

R49

10

10P

C642

10P

C56 C644

10P

C643

82P

RED_L

GREEN_L

BLUE_L

HSYNC_R

VSYNC_R

1

RED

2

GREEN

3

BLUE

13

HSYNC

14

VSYNC/DDC_CLK

6

REDRTN/CGND1

7

GRNRTN/CGND2

8

BLUERTN/CGND3

5

GND1

10

GND2

15 PIN DSHELL NC

VIDEO CONN

"VIDEO"

6

111

MID0

SDA/MID1

MID2

SCL/MID3

SHELL2

SHELL1

11

12

4

15

9

MH1

MH2

VIDEO_P11A

DDCDAT_N_R

VIDEO_P4A

DDCCLK_N_R

VIDEO_VCC_TH

c

R54

TH1

1K

PCI_5V

R59

1K

R53

VENDOR=RAYCHEM

VEN_P/D_NUM=SMD100-2

C55

100N

2.2K

R60

PCI_5V

2.2K

C651

C652

100P

100P

R65

33

R52

33

FET_2N7002_NL

DDCDAT_N_R_R

C646

DDCCLK_N_R_R

C645

10P

FET_2N7002_NL

10P

R66

1

G

2

S

2

S

R67

PCI_3.3V

3

D

Q3

1

G

3

D

Q4

6.8K

6.8K

ATI_DDCDAT

ATI_DDCCLK

5,8

5,8

C

D

E

PCI_5V

U7

VIDEO_VSYNC5

AHCT125_SO14N

C58

F

G

10P

NOPOP

14

2

3

1

7

R58

VSYNC_BUF

1K

C61

100P

NOPOP

R50

10

C57

82P

VENDOR=TYCO

0

0

R556

R540

CYA for EMC

F

c

G

5,8

5,8

H

VIDEO_RED

2

CR1

3

V V V V V V V

I

80

1

VIDEO_GREEN

2

CR2

3

80

1

5,8

VIDEO_BLUE

2

CR3

3

80

1

PCI_5VPCI_5VPCI_5V

HSYNC_BUF

2

CR4

3

80

1

VSYNC_BUF

2

CR5

3

80

1

5,8

PCI_3.3V

ATI_DDCDAT

2

CR10

3

80

1

5,8

ATI_DDCCLK

2

CR11

3

80

1

H

I

PART NO.

DIO_BAV99-F-T116

DIO_BAV99-F-T116

DIO_BAV99-F-T116

DIO_BAV99-F-T116

DIO_BAV99-F-T116

ESD Protection

DIO_BAV99-F-T116

DIO_BAV99-F-T116

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

39M4939

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

ANALOG VIDEO CONNECTOR

6-27-2005_9:24

Physical DesignRobert Piper

Les Garrett

SHEET OF

8

108754321

15

JJ

Page 9

961 2 3 4 5 7 8 10

4/7/02 JWD-NOPOP all USB power components.

4/7/02 JWD-Added PCI_3.3V to SMP connector, Will be used to determine if server is on

4/10/02 JWD-Added FAULT_LED signal to SMP

A

VENDOR=MOLEX

Ext I/O Connector

01/15/03 JWD-populated R563 and R564 to fix EMC problems.

06/16/03 RMK-Changed J35 to molex part number 500596-1409 from 52760-1409 for gold plated pins

07/16/03 JAD - Changed J35 to IBM P/N 23K8777 from 89G3896 to match the correct Molex P/N (500596-1409) in our database

09/03/03 JAD - Changed J36 to IBM P/N 23K8863 from 61P6425

REL

EC NO.DATEQTYREL FOR ASM

PART NO.

DEVELOPMENT NO. Q/M

A

22U

NOPOP

C529

100N

CONT_PWR

NOPOP

J36

20

C20

19

C19

18

C18

17

C17

16

C16

15

C15

14

C14

13

C13

12

C12

11

C11

10

C10

9

C9

8

C8

7

C7

6

C6

5

C5

4

C4

3

C3

2

C2

1

C1

Crow 2002

VENDOR=MOLEX

VEN_P/D_NUM=55176-2061

P/D_NUM=41C4934

B

C

D

E

F

G

H

3.3VC

c

c

R619

0

L52

BLM21P300S

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

ENET_PHY_TX

ENET_PHY_TX_N

ENET_PHY_RX

ENET_PHY_RX_N

R9

470

R10

470

Keep inductor/capacitor filter near connector

485_EXT_P

L53

485_EXT_N

BLM21P300S

C564

220P

9

4.7K

Can be used by host in Harrier only implementations.

405_BIST_N9

C654

10N

C633

100N

c

9

9

9

9

3.3VC

ENET_PHY_LNK_LED_N

ENET_PHY_ACT_LED_N

C563

220P

405_BIST_N

3.3VC

9

9

9

9

Crow-R ID = 10000000'b

3.3VC

R543

used for manufacturing test

PCI_3.3V

10

10

10

10

10

10

10

10

10

10

10

10

10

5

10

9

10

9

9

9

9

9

9

9

9

9

HOST_ID0

HOST_ID1

HOST_ID2

HOST_ID3

HOST_ID4

HOST_ID5

HOST_ID6

HOST_ID7

COM4_RTS#

USB_INT_P

USB_INT_N

3V_PPCI_RST_N

RS232_DETECT

485_SWITCH

SMBUS_BUSY_N

COM5_DTR#

COM5_DSR#

COM5_TX

COM5_CTS#

COM5_232RX

COM5_RI#

COM5_DCD#

COM5_RTS#

COM4_TX

COM4_RX

HOST_I2C_SDA

HOST_I2C_SCL

HOST_PWRGD/RST#

HOST_PWR_REQ#

HOST_I2C_INT#

SMBUS_REQ#

COM4_CTS#

COM4_DTR#

HOST_SMI#

COM4_DSR#

RS232_ENABLE

P_EXT_ACK#

IRQ4

IRQ1

GPIO1

GPIO16

J35

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

KEY

C71

C72

C73

C74

C75

C76

C77

C78

C79

C80

C81

C82

C83

C84

C85

C86

C87

C88

C89

C90

C91

C92

C93

C94

C95

C96

C97

C98

C99

C100

C101

C102

C103

C104

C105

C106

C107

C108

C109

C110

C111

C112

C113

C114

C115

C116

C117

C118

C119

C120

C121

C122

C123

C124

C125

C126

C127

C128

C129

C130

C131

C132

C133

C134

C135

C136

C137

C138

C139

C140

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C20

C21

C22

C23

C24

C25

C26

C27

C28

C29

C30

C31

C32

C33

C34

C35

LCD Port (Raw Digital Video)

C36

C37

C38

C39

C40

C41

C42

C43

C44

C45

C46

C47

C48

C49

C50

C51

C52

C53

C54

C55

C56

C57

C58

C59

C60

C61

C62

C63

C64

C65

C66

C67

C68

C69

C70

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

EXT_TMDS_RED6

EXT_TMDS_RED7 5

EXT_TMDS_RED2

EXT_TMDS_RED3

EXT_TMDS_RED4

EXT_TMDS_RED5

EXT_TMDS_GRN6

EXT_TMDS_GRN7

EXT_TMDS_BLU7

EXT_TMDS_HSYNC

EXT_TMDS_VSYNC

EXT_TMDS_DE

EXT_TMDS_CLK

EXT_TMDS_RED1

EXT_TMDS_GRN3

EXT_TMDS_GRN4

EXT_TMDS_GRN5

EXT_TMDS_BLU1

EXT_TMDS_BLU4

EXT_TMDS_GRN1

EXT_TMDS_GRN2

EXT_TMDS_BLU3 5

EXT_TMDS_BLU6 5

EXT_TMDS_BLU2 5

EXT_TMDS_BLU5 5

485_N_BUS_B

485_P_BUS_B

485_EXT_N

485_EXT_P

405GP_INSANE_N

COM4_CD#

ENET_PHY_RX_N

ENET_PHY_RX

ENET_PHY_TX_N

ENET_PHY_TX

ENET_PHY_LNK_LED_N

ENET_PHY_ACT_LED_N

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

10

9

9

9

9

9

9

+

C521

NOPOP

9

9

USB_INT_N

USB_INT_P

485_INT_P

485_INT_N

HOST_SMI#

HOST_I2C_INT#

HOST_PWR_REQ#

SMBUS_REQ#

HOST_PWRGD/RST#

HOST_I2C_SCL

HOST_I2C_SDA

C528

100N

C527

100N

NOPOP

9

9

9

9

9

9

9

9

9

Raptor Umbilical Connector

Cable must swap pins 16 and 17 to connect to Condor 2000 Header

Cable must swap pins 10 and 18 to connect to Condor 2000 Header

9

9

9

9

1

+

PANASONIC

3v

BH1

BR1225-1HC

2

SH2

SH2

SH1

SH1

C1

1

C2

2

C3

3

B

C

D

J37

VEN_P/D_NUM=52629-2670

E

P/D_NUM=41C4935

F

c

G

ENET_GND is a seperate ground plane under connector

that is isolated from GND, but connected to the chassis ground.

H

C4

4

C5

5

C6

6

C7

7

C8

8

C9

9

C10

10

C11

11

C12

12

C13

13

C14

14

C15

15

C16

16

C17

17

C18

18

C19

19

C20

20

C21

21

C22

22

Molex 52629-2651

C23

23

C24

24

C25

25

C26

26

PULSE J0011D21E

MH3

MH3

MH4

MH4

GL_AN

GL_CA

GRN

GR_AN

GR_CA

GRN

COM4_RTS1#

COM4_DTR1#

COM4_TX1

COM4_CD1#

COM4_CTS1#

COM4_DSR1#

COM4_RX1

COM5_RI1#

COM5_232RX1

COM5_DSR1#

COM5_CTS1#

COM5_DCD1#

COM5_TX1

COM5_DTR1#

COM5_RTS1#

RS232_GND

J1

MATCHING LENGTHS, SAME LAYER FOR PAIRS (50 Ohm SE, 100 Ohm Diff)

1

A

2

B

3

C

4

D

5

E

6

F

G

7

8

H

9

10

12

11

Ethernet Connector

KEY

R545

3.3VC

4.7K

9

485_SWITCH

9

3.3VC

U86

VCC

5

I

9

9

485_INT_P

485_EXT_P

S1ININ = 1

1

S2

3

2

IN = 0

GND

6

D

4

485_P_BUS_B

9

9

9

485_INT_N

485_EXT_N

U87

S1ININ = 1

1

S2

3

2

IN = 0

GND

VCC

5

6

4

3.3VC

D

485_N_BUS_B

VENDOR=MOLEX

VEN_P/D_NUM=500596-1479

SMP Connector

P/D_NUM=41C4937

I

PART NO.

39M4939

CONNECTORS

6-27-2005_9:24

SHEET OF

9

108754321

Physical DesignRobert Piper

Les Garrett

15

JJ

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR/LF

P/D_NUM=77P1926

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR/LF

P/D_NUM=77P1926

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

Page 10

01/15/03 JWD- NOPOPed U85,CR132,CR142,CR152,J38

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

DEVELOPMENT NO. Q/M

A

A

C553

C552

100N

U83

100N

28

C1

24

C1_N

1

C2

B

9

9

9

9

9

9

C

9

9

COM5_TX

COM5_DTR#

COM5_RTS#

COM5_RI#

COM5_232RX

COM5_DSR#

COM5_CTS#

COM5_DCD#

2

C2_N

14 9

T1IN T1OUT

13 10

T2IN T2OUT

12 11

T3IN T3OUT

20

R2OUTB

ST3243ECTR

V_N

R1INR1OUT

R2INR2OUT

R3INR3OUT

R4INR4OUT

R5INR5OUT

27

V

3

C550

C551

100N

100N

B

COM5_TX1_L

COM5_DTR1#_L

COM5_RTS1#_L

419

518

COM5_232RX1_L

617

716

815

COM5_DSR1#_L

COM5_CTS1#_L

COM5_DCD1#_L

COM5_RI1#_L

3 6

2 7

1 8

4 5

3 6

2 7

1 8

4 5

120

120

120

120

120

120

120

120

ohms

ohms

ohms

ohms

ohms

ohms

ohms

ohms

L56

L56

L56

L57

L57

L57

L57

L56

COM5_TX1

COM5_DTR1#

COM5_RTS1#

COM5_RI1#

COM5_232RX1

COM5_DSR1#

COM5_CTS1#

COM5_DCD1#

9

9

9

9

9

9

9

C

9

3.3VC

22

FORCEOFF_N

23

FORCEON

INVALID_N

21

3.3VC

CN4

3 6

470P

470P

CN4

CN3

470P

4 5

470P

CN4

CN4

2 7

1 8

470P

1 8

CN3

470P

CN3

CN3

3 6

2 7

4 5

470P

470P

25

GND

VCC

26

D

D

R550

NOPOP

VENDOR=ST_MICRO

0

VEN_P/D_NUM=ST3243ECTR-E

C581

C549

10N

9

RS232_DETECT

R551

0

100N

C588

C589

28

24

U88

1

2

C1

C1_N

C2

C2_N

ST3243ECTR

V_N

E

27

V

3

C591

C590

100N

100N

Place caps and inductors close to 26 pin connector

E

2CR13

For Debug (NOPOP for production)

100N

100N

LED2P_TLMG-3100_GRN

mA

10

PLACE=NOPOP

1

Place on Back

R533

330

9

9

F

9

9

9

9

9

COM4_TX

COM4_DTR#

COM4_RTS#

COM4_RX

COM4_DSR#

COM4_CTS#

COM4_CD#

3.3VC

G

14 9

T1IN T1OUT

13 10

T2IN T2OUT

12 11

T3IN T3OUT

419

R1INR1OUT

518

R2INR2OUT

617

R3INR3OUT

716

R4INR4OUT

815

R5INR5OUT

20

R2OUTB

22

FORCEOFF_N

23

FORCEON

25

GND

INVALID_N

VCC

21

26

COM4_TX1_L

COM4_DTR1#_L

COM4_RTS1#_L

COM4_RX1_L

COM4_DSR1#_L

COM4_CTS1#_L

COM4_CD1#_L

3.3VC

CN2

470P

CN2

CN2

2 7

1 8

3 6

470P

470P

CN2

CN1

4 5

2 7

470P

470P

CN1

CN1

3 6

3 6

2 7

1 8

3 6

2 7

1 8

4 5

470P

4 5

470P

120

120

120

120

120

120

120

ohms

ohms

ohms

ohms

ohms

ohms

ohms

L54

L54

L54

L55

L55

L55

L54

COM4_TX1

COM4_DTR1#

COM4_RTS1#

COM4_RX1

COM4_DSR1#

COM4_CTS1#

COM4_CD1#

9

9

9

F

9

9

9

9

G

VENDOR=ST_MICRO

C593

C592

VEN_P/D_NUM=ST3243ECTR-E

10N

100N

H

H

2CR14

LED2P_TLMG-3100_GRN

10

PLACE=NOPOP

mA

1

For Debug (NOPOP for production)

R549

I

330

I

PART NO.

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

0.13

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

2.0

6 9

39M4939

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

RS232 DRIVER

6-27-2005_9:24

SHEET OF

10

108754321

Physical DesignRobert Piper

Les Garrett

15

JJ

Page 11

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

B

PCI_3.3V

U91

5

4

C

M66EN

LVC1G14_SC70_5

PWR

GND

42

3

R515

2/10/05 - RMP - Changed to single gate package

10K

GPIO_4

5

DEVELOPMENT NO. Q/M

A

B

C

C547

10N

D

D

E

F

MH1

E

F

Stand-Offs

MH1

TOP

c

Dummy part place holder for bom

MECH3

MECH_PART

STAND-OFFS

Dummy part place holder for bom

MECH8

MECH_PART

STAND-OFFS

Dummy part place holder for bom

G

MECH2

MECH_PART

BRACKET_SCREW

BRACKET

H

Video Connector Screws

Dummy part place holder for bom

MECH11

MECH_PART

JACKSCREW

Dummy part place holder for bom

MECH9

MECH_PART

STAND-OFFS

Dummy part place holder for bom

Dummy part place holder for bom

MECH10

MECH_PART

STAND-OFFS

Connector Screws

Dummy part place holder for bom

MECH4

MECH_PART

CONNECTOR_SCREW

CONNECTOR_SCREW

MECH5

MECH_PART

G

H

EMC Foam

Dummy part place holder for bom

MECH13

MECH_PART

EMC_FOAM

I

Dummy part place holder for bom

MECH12

Dummy part place holder for bom

MECH6

MECH_PART

MECH_PART

JACKSCREW

CONNECTOR_SCREW

Dummy part place holder for bom

MECH7

MECH_PART

CONNECTOR_SCREW

I

PART NO.

39M4939

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

MECHANICAL PARTS

6-27-2005_9:24

SHEET OF

11

108754321

Physical DesignRobert Piper

Les Garrett

15

JJ

Page 12

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

DEVELOPMENT NO. Q/M

B

A

B

C

C

Vout

3.3VC

CONT_PWR

D

PCI_5V

5V Cont

CONT_PWR

PCI_5V

DIO2P_MBRS340T3G

40

V

2

DIO2P_MBRS340T3G

2

D1

1

3.3VC

40

V

D5

D

1

Create 3.3VC Power Island under SMP

0

R623

0

PKG_TYPE=1206

R624

PKG_TYPE=1206

Vin for

EXT16V CONN (regulated)

3.3VC

E

J34

3

RAPC712

40

1

2

NET_VOLTAGE=16

C647

C648

EXT16V

V

2

DIO2P_MBRS340T3G

D4

1

EXT_CONT+INT_CONT+INT_NON_CONT

4 AMP

F1

C576

10U

C574

100N

L5973_IN

7

6

VCC

VREF

U78

L5973D

OUT

SYNCGND

INH

L49

uH

18

2

3

IND2P_DS3316P-333

33

+

C575

150U

R541

C554

100N

L5973_OUT_LL5973_OUT

E

10U

F

G

10U

5

FB

COMP

C573

4

U78_COMP

V = 50V

220P

C548

R532

22N

4.7K

V = 50V

CR12

30

2

DIO_CMS06_TE12L-Q

V

1

R534

16.9K

F

10K

G

H

I

PART NO.

H

I

39M4939

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

3.3V CONT POWER

6-27-2005_9:24

Doug Evans

Doug Evans Doug Evans

SHEET OF

12

108754321

Physical DesignRobert Piper

Les Garrett

15

JJ

Page 13

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

DEVELOPMENT NO. Q/M

A

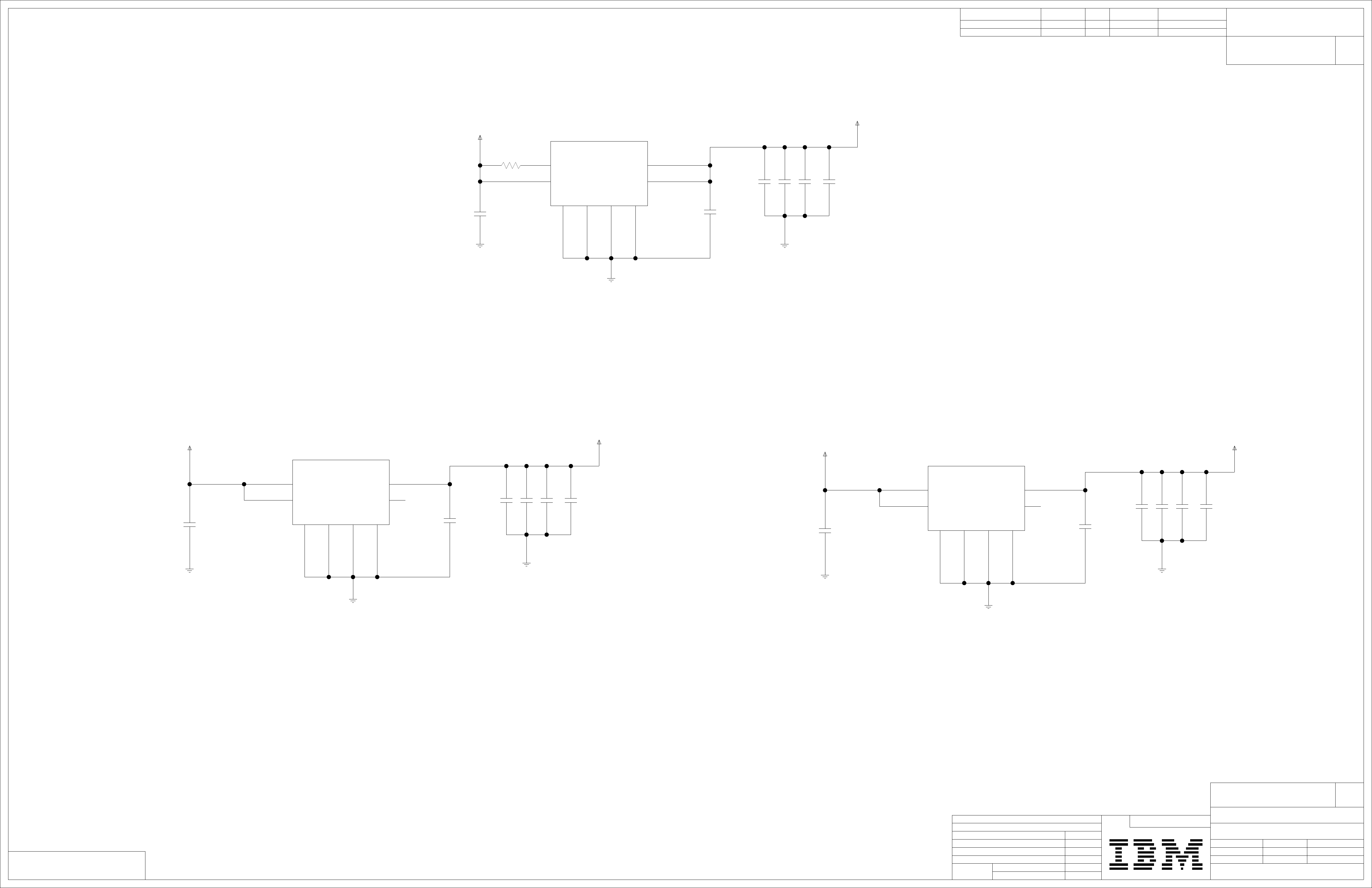

Check 2.5 V current requirements for RN50

1.2V Regulator @ 1.5 amp max (non-cont)

1_2V

B

P/D_NUM=26P1421

C

PCI_3.3V

C577

10U

R625

10K

U79

VREG8P_E-L6932D1_2TR

5

V

1

EN

2

IN

GND7

GND8GND6GND5

7

ADJ

OUT

865

3

100N

4

C578

P/D_NUM=26P1421

10U

C558

100N

C555

100N

C556

100N

P/D_NUM=40H8328

C557

B

C

D

E

D

E

1.8V Regulator @ 1.5 amp (non-cont)

1_8V

PCI_3.3V 2_5V

PCI_3.3V

U84

VREG8P_E-L6932D1_8TR

5

V

1

F

C579

P/D_NUM=26P1421

10U

EN

2

IN

PGOOD_FLG

GND7

GND8GND6GND5

7

OUT

865

3

100N

4

C580

P/D_NUM=26P1421

10U

C561

100N

C559

100N

C560

100N

P/D_NUM=40H8328

C562

C736

P/D_NUM=26P1421

10U

2.5V Regulator @ 1.5 amp (non-cont)

U93

VREG8P_E-L6932D2_5TR

5

V

1

EN

2

IN

PGOOD_FLG

GND7

GND8GND6GND5

7

OUT

865

3

100N

4

C737

P/D_NUM=26P1421

10U

C734

100N

C732

100N

C733

F

100N

C735

G

H

G

H

I

PART NO.

I

39M4939

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

2.5V, 1.8V, POWER

6-27-2005_9:24

Doug Evans

Doug Evans

SHEET OF

13

108754321

Physical DesignRobert Piper

Les Garrett

15

JJ

Page 14

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

CONT_PWR

A

1.8

DAC2_1.8

B

MEMPLL1.8

DAC_1.8

AVDDI_1.8

PLL1.8

MEM_CLK_R_DIV

MEM_VREF

DDR2_VREF

VIDEO_MEM_L/UDQS_N

2_5V1_8V

1.8

1.8

1.8

1.8

PCI_3.3V

2.5

1.8

1.8

1.8

1.8

3.3

3.3VC

3.3

1.8

PCI_5V

5

1_2V

5

1.2

PCI_3.3V

100N

100N

100N

100N

100N

100N

100N

100N

100N

DEVELOPMENT NO. Q/M

100N

A

B

C

D

E

VIDEO_RED

VIDEO_GREEN

VIDEO_BLUE

RED_L

VSYNC_R

VIDEO_HSYNC

VIDEO_VSYNC

GREEN_L

HSYNC_R

HSYNC_BUF

VSYNC_BUF

COM5_DTR1#_L

COM5_RTS1#_L

COM5_RI1#_L

COM5_232RX1_L

COM5_DSR1#_L

COM5_CTS1#_L

COM5_DCD1#_L

COM4_TX1_L

COM4_DTR1#_L

COM4_RTS1#_L

BLUE_L

COM5_TX1_L

C594

100N

C604

100N

C614

C595

100N

C613

100N

C623

C596

100N

C605

100N

C615

C597

100N

C606

100N

C616

C598

100N

C607

100N

C617

C599

100N

C608

100N

C618

C600

100N

C609

100N

C619

C601

100N

C610

100N

C620

C602

100N

C611

100N

C621

C603

100N

C612

100N

C622

C

D

E

COM4_RX1_L

COM4_DSR1#_L

COM4_CTS1#_L

COM4_CD1#_L

12

PCI_5VPCI_5V

U7

14

11

13

7

VID_VDDL_C

DDCDAT_N_R

DDCCLK_N_R

VIDEO_VCC_TH

DDCCLK_N_R_R 5

F

G

DDCDAT_N_R_R 5

L5973_OUT_L

U78_COMP

L5973_IN

5

16

1.8

16

5

5

AHCT125_SO14N

3.3

U7

9

14

8

10

7

AHCT125_SO14N

PCI_3.3V

100N

100N

100N

3.3VC

C624

C625

C626

PCI_3.3V

1_2V

C629

100N

C628

100N

C627

100N

PCI_3.3V

1_8V

C632

100N

F

C631

100N

C630

100N

G

H

I

PART NO.

H

I

39M4939

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

SPARE PARTS

6-27-2005_9:24

SHEET OF

14

108754321

Physical DesignRobert Piper

Les Garrett

15

JJ

Page 15

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

REL

PART NO.

Q

A

B

C

D

E

F

G

H

I

10 Feb 2005

07:35:36

CROW

BH

BH1_____ 9

C

C169____ 4

C170____ 4

C171____ 4

C172____ 4

C173____ 4

C174____ 4

C177____ 4

C178____ 4

C179____ 4

C180____ 4

C183____ 4

C184____ 4

C185____ 4

C188____ 4

C189____ 4

C190____ 4

C191____ 4

C192____ 4

C194____ 4

C195____ 4

C196____ 4

C521____ 9

C522____ 4

C523____ 4

C524____ 4

C525____ 4

C526____ 4

C527____ 9

C528____ 9

C529____ 9

C547____ 11

C548____ 12

C549____ 10

C55_____ 8

C550____ 10

C551____ 10

C552____ 10

C553____ 10

C554____ 12

C555____ 13

C556____ 13

C557____ 13

C558____ 13

C559____ 13

C56_____ 8

C560____ 13

C561____ 13

C562____ 13

C563____ 9

C564____ 9

C57_____ 8

C573____ 12

C574____ 12

C575____ 12

C576____ 12

C577____ 13

C578____ 13

C579____ 13

C58_____ 8

C580____ 13

C581____ 10

C588____ 10

C589____ 10

C59_____ 8

C590____ 10

C591____ 10

C592____ 10

C593____ 10

C594____ 14

C595____ 14

C596____ 14

C597____ 14

C598____ 14

C599____ 14

C60_____ 8

C600____ 14

C601____ 14

C602____ 14

C603____ 14

C604____ 14

C605____ 14

C606____ 14

C607____ 14

C608____ 14

C609____ 14

C61_____ 8

C610____ 14

C611____ 14

C612____ 14

C613____ 14

C614____ 14

C615____ 14

C616____ 14

C617____ 14

C618____ 14

C619____ 14

C620____ 14

C621____ 14

C622____ 14

C623____ 14

C624____ 14

C625____ 14

C626____ 14

C627____ 14

C628____ 14

C629____ 14

C630____ 14

C631____ 14

C632____ 14

C633____ 9

C634____ 8

C635____ 8

C636____ 8

C637____ 7

C638____ 7

C639____ 7

C641____ 7

C642____ 8

C643____ 8

C644____ 8

C645____ 8

C646____ 8

C647____ 12

C648____ 12

C649____ 4

C650____ 4

C651____ 8

C652____ 8

C653____ 7

C654____ 9

C655____ 7

C656____ 5

C657____ 5

C658____ 6

C659____ 6

C660____ 6

C661____ 5

C662____ 6

C663____ 6

C664____ 6

C665____ 6

C666____ 6

C667____ 6

C668____ 6

C669____ 6

C670____ 6

C671____ 6

C672____ 6

C673____ 6

C674____ 6

C675____ 6

C676____ 6

C677____ 6

C678____ 6

C679____ 6

C680____ 6

C681____ 6

C682____ 6

C683____ 6

C684____ 6

C685____ 6

C686____ 6

C687____ 6

C688____ 6

C689____ 6

C690____ 6

C691____ 6

C692____ 6

C693____ 6

C694____ 6

C695____ 6

C696____ 6

C697____ 6

C698____ 6

C699____ 6

C700____ 6

C701____ 6

C702____ 6

C703____ 6

C704____ 6

C705____ 6

C706____ 6

C707____ 6

C708____ 6

C709____ 6

C710____ 6

C711____ 6

C712____ 6

C713____ 6

C714____ 6

C715____ 6

C716____ 6

C717____ 6

C718____ 6

C719____ 6

C720____ 6

CN

CN1_____ 10

CN2_____ 10

CN3_____ 10

CN4_____ 10

CR

CR1_____ 8

CR10____ 8

CR11____ 8

CR12____ 12

CR13____ 10

CR14____ 10

CR2_____ 8

CR3_____ 8

CR4_____ 8

CR5_____ 8

D

D1______ 12

D4______ 12

D5______ 12

F

F1______ 12

J

J1______ 9

J31_____ 4

J34_____ 12

J35_____ 9

J36_____ 9

J37_____ 9

J5______ 8

L

L2______ 8

L3______ 8

L4______ 8

L49_____ 12

L52_____ 9

L53_____ 9

L54_____ 10

L55_____ 10

L56_____ 10

L57_____ 10

L61_____ 7

L62_____ 6

L63_____ 6

L64_____ 6

L65_____ 6

L66_____ 6

ME

MECH10__11

MECH11__11

MECH12__11

MECH13__11

MECH2___11

MECH3___11

MECH4___11

MECH5___11

MECH6___11

MECH7___11

MECH8___11

MECH9___11

MH

MH1_____ 11

Q3______ 8

Q4______ 8

R

R10_____ 9

R22_____ 5

R23_____ 5

R24_____ 5

R25_____ 5

R29_____ 7

R31_____ 7

R32_____ 7

R33_____ 7

R34_____ 7

R49_____ 8

R50_____ 8

R515____ 11

R518____ 5

R519____ 5

R52_____ 8

R520____ 5

R521____ 5

R522____ 5

R527____ 4

R529____ 5

R53_____ 8

R530____ 5

R531____ 5

R532____ 12

R533____ 10

R534____ 12

R537____ 5

R538____ 5

R539____ 5

R54_____ 8

R540____ 8

R541____ 12

R543____ 9

R545____ 9

R549____ 10

R550____ 10

R551____ 10

R556____ 8

R557____ 5

R558____ 7

R559____ 7

R560____ 7

R561____ 7

R562____ 7

R565____ 7

R566____ 7

R571____ 7

R572____ 7

R573____ 5