MSI MS-95B6 95b6_8Y810_A02

ABC

Dell Controlled Print

REV

40 DATA LINES

REMC DP0

225 PBGA

1

REMC DP1

225 PBGA

10 STROBES

32 DATA LINES

8 STROBES

32 DATA LINES

8 STROBES

40 DATA LINES

10 STROBES

A_SD/DQS[8,3,0,1,2]_[0:7]

B_SD/DQS[3,2,0,1]_[0:7]

A_SD/DQS[6,7,5,4]_[0:7]

B_SD/DQS[8,6,7,5,4]_[0:7]

CARD A

TABLE OF CONTENTS

A01

A02

137924

162394

164090

RELEASE TO A-REV FROM X02A00

Update PWA ref. for MSI Transition

Removed Intersil as vendor for U30, 3F153 -->009TG

Removed U95, R622, R624, R619, R620, R625,

R621 & R626 for cost saving purposes

DESCRIPTIONECO DATE

REVISIONS

D

6-16-2004_18:08

4/15/03

5/21/04

6/15/04

CLAY PHENNICIE

APPROVED

1

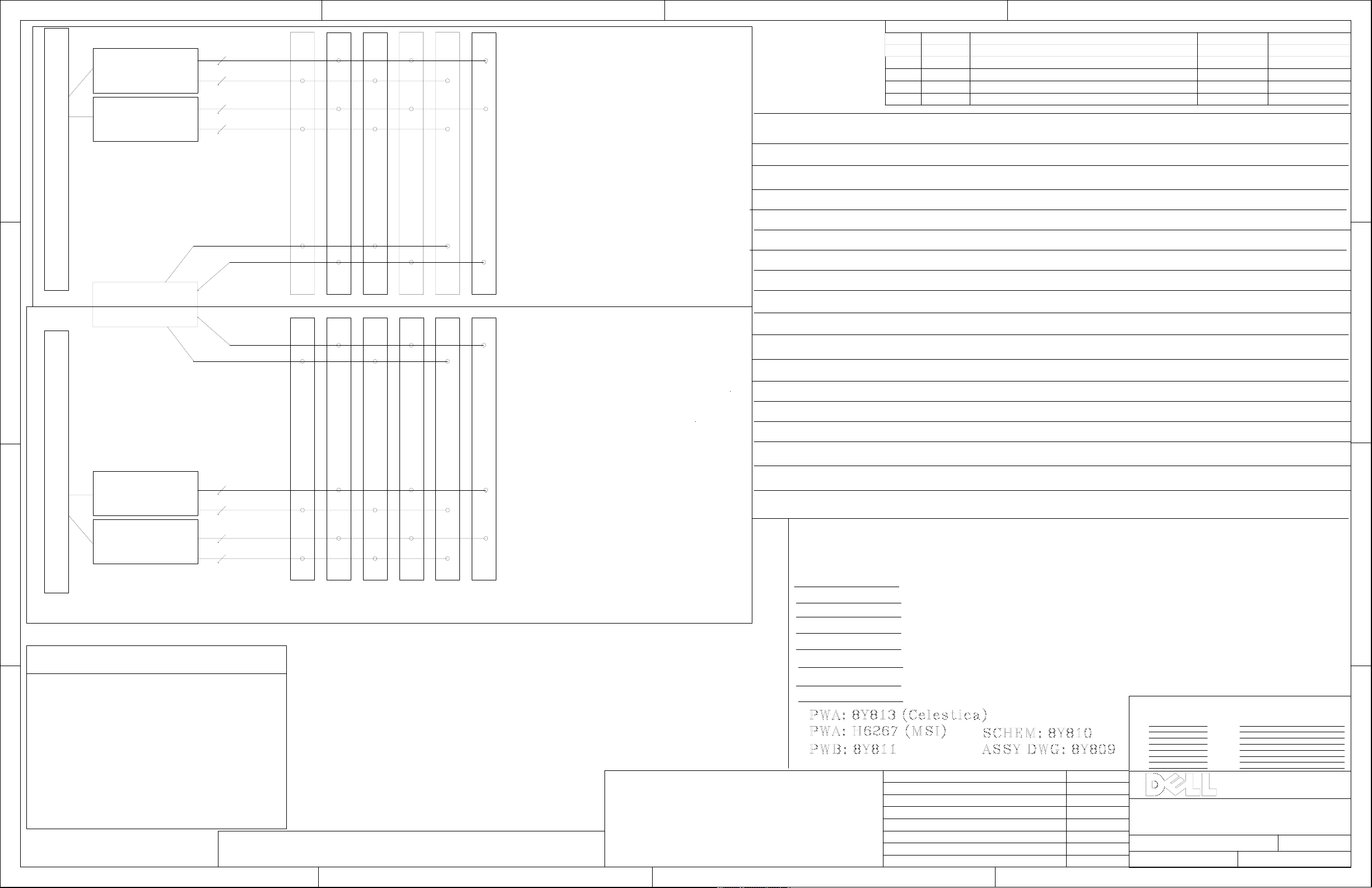

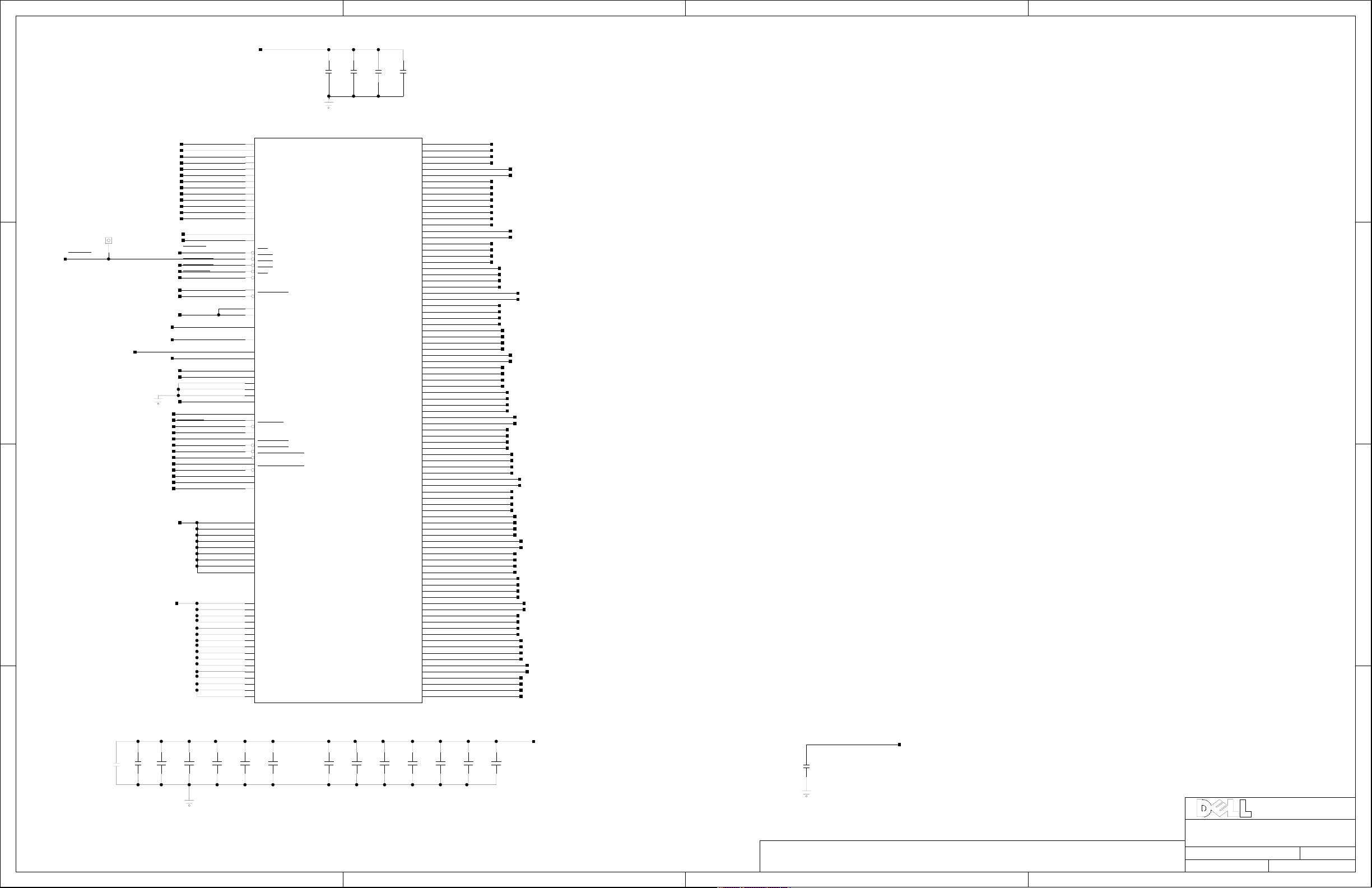

PAGE 1: BLOCK DIAGRAM

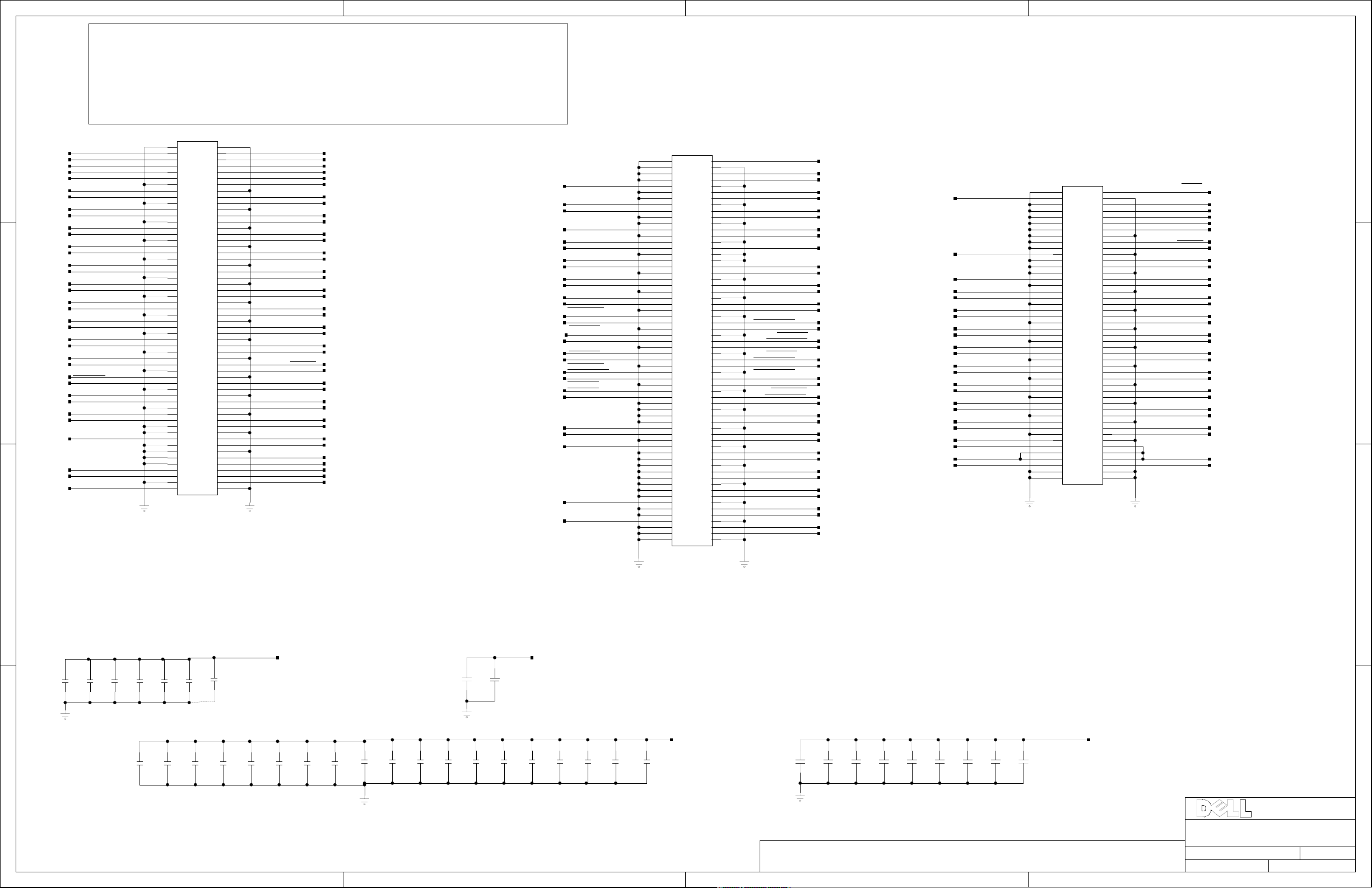

PAGE 2: PLANAR CONNECTOR

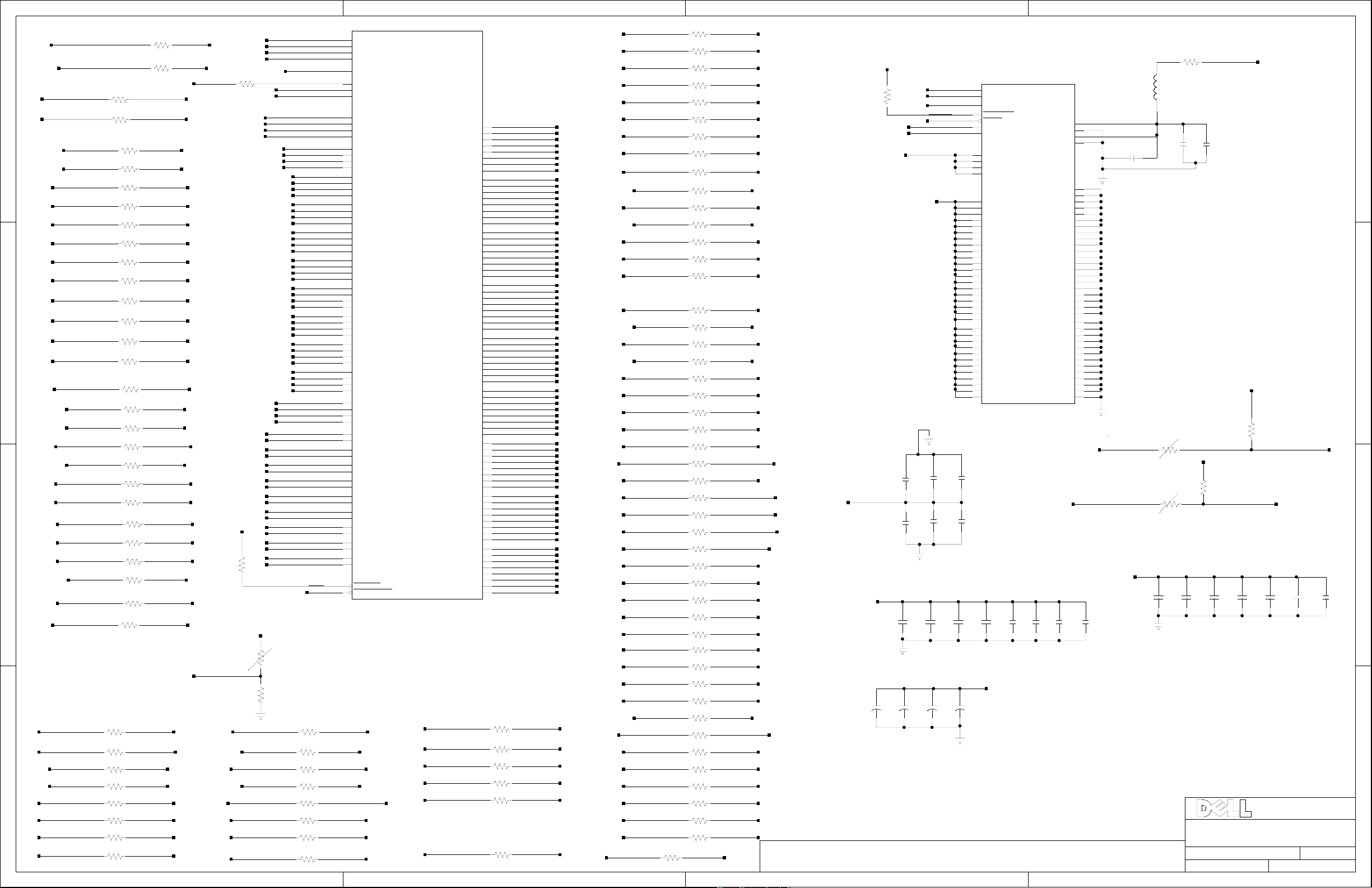

PAGE 3: REMC DP0

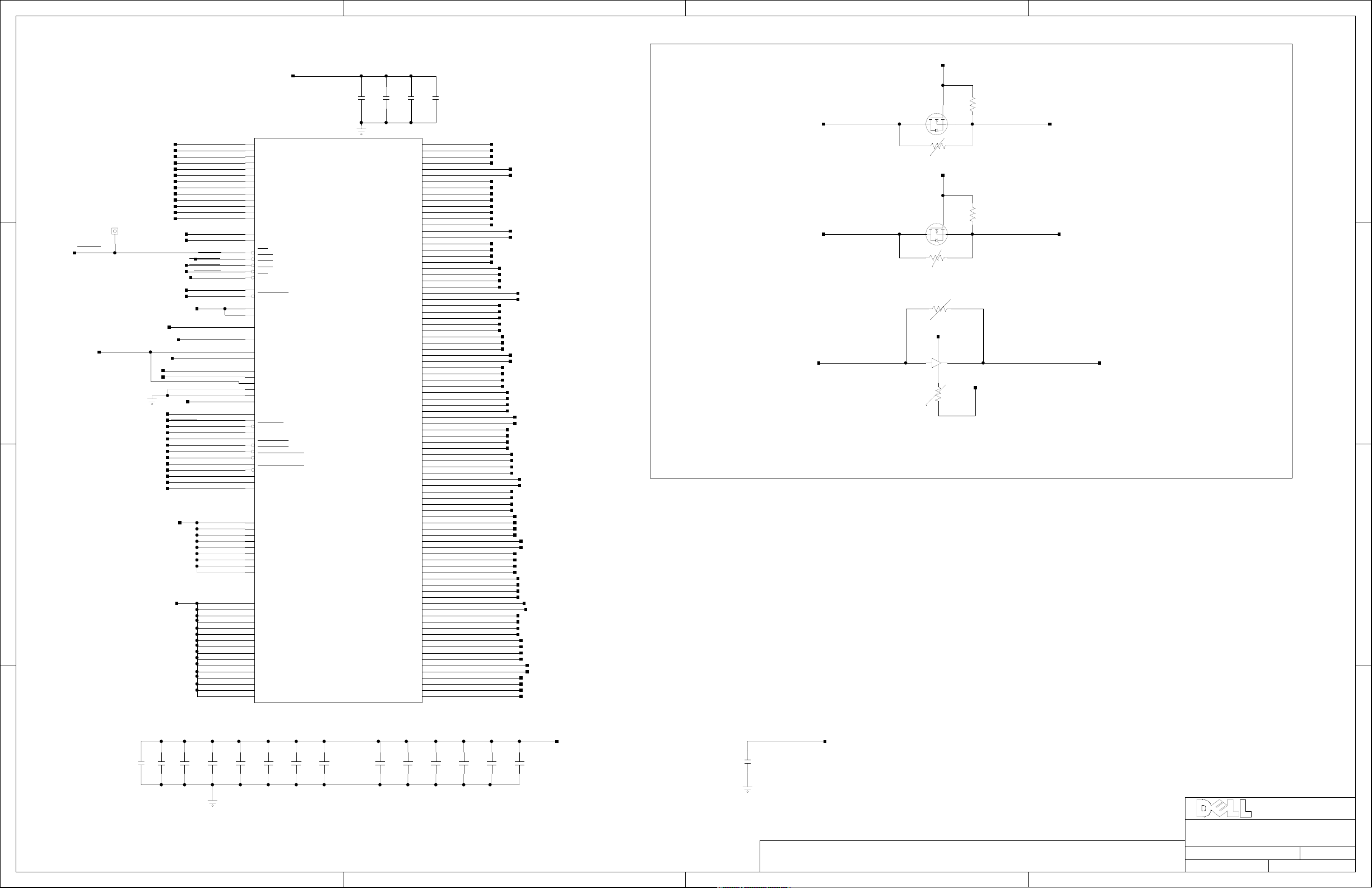

PAGE 4: REMC DP1

A_MA[0:9,11:12], Rx_MA10, Rx_RASN, Rx_CASN, Rx_WEN, A_CSx, Rx_BAx_x, A_CKE

DIMM_J6

DIMM_J5

DIMM_J4

DIMM_J3

DIMM_J2

DIMM_J1

PAGE 5: DIMM J2 (A R0)

B_MA[0:9,11:12, Rx_MA10, Rx_RASN, Rx_CASN, Rx_WEN, A_CSx, Rx_BAx_x, B_CKE

MEM CARD CONNS

REMC AP

on planar

2

REMC DP2

225 PBGA

REMC DP3

3

C_MA[0:9,11:12], Rx_MA10, Rx_RASN, Rx_CASN, Rx_WEN, B_CSx, Rx_BAx_x, C_CKE

D_MA[0:9,11:12], Rx_MA10, Rx_RASN, Rx_CASN, Rx_WEN, B_CSx, Rx_BAx_x, D_CKE

40 DATA LINES

10 STROBES

32 DATA LINES

8 STROBES

32 DATA LINES

8 STROBES

225 PBGA

40 DATA LINES

10 STROBES

MEM CARD CONNS

R: \ Schematic_Projects \ PowerEdge \ Jaguar \ memory _card \ 6_dimm_8Y810 \ A02

I2C ADDRESSES

JAGUAR DDR 6

ASCLK/ASDATA

J1 1010 000xb

J2 1010 001xb

J3 1010 010xb

J4 1010 011xb

J5 1010 100xb

J6 1010 101xb

REMC DP0 1110 1Y0xb

REMC DP1 1110 1Y1xb

CLKBUF0 1101001xb

4

Y = 0 FOR MEM CARD A

Y = 1 FOR MEM CARD B

EACH MEM CARD ON SEPARATE I2C BUS

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

DIMM MEMORY CARD

CARD B

DIMM_J12

C_SD/DQS[8,3,0,1,2]_[0:7]

D_SD/DQS[3,2,0,1]_[0:7]

C_SD/DQS[6,7,5,4]_[0:7]

D_SD/DQS[8,6,7,5,4]_[0:7]

DIMM_J11

PRODUCTION BUILD = BUILD 1

PROTOTYPE BUILD = BUILD 0

DIMM_J10

DIMM_J9

DIMM_J8

DIMM_J7

CIRCUITRY WILL

BE SAME AS CARD

A BUT C/D BUSSES

CALLED OUT FOR

SIMULATION

THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER

CORP., EXCEPT AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN

ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE

REPRODUCED IN WHOLE OR IN PART AND MUST BE RETURNED TO DELL

COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION

OF THE PURPOSE OF THE LOAN. NEITHER THIS ITEM NOR THE

INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS

NOT HAVING A NEED FOR SUCH USE OR DISCLOSURE CONSISTENT WITH

THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF

DELL COMPUTER CORPORATION.

PAGE 6: DIMM J1 (B R0)

PAGE 7: DIMMS J4 & J6 (A R1 &R2)

PAGE 8: A DATA END TERM RES

PAGE 9: DIMMS J3 & J5 (B R1 & R2)

PAGE 10: B DATA END TERM RES

PAGE 11: CLOCK BUFFER

PAGE 12: ADDR & MISC END TERM RES

PAGE 13: ESM3 & RESET & SPARES & WHs

PAGE 14: VREF, VTT REGULATION

PAGE 15: CMD SERIES TERM RES

PAGE 16: 2.5V REGULATION

PAGE 17: CLOCK ROUTING DIAGRAM

Outer layers are 1.5 oz Cu

Inner layers are 1.0 oz Cu

PROPRIETARY NOTE

4 mils

4 mils

15 mils

4 mils

15 mils

4 mils

4 mils

STACKUP INFO

TOP - 2.1 mils

GROUND1 - 1.4mils

INNER 1 - 1.4 mils

GROUND2 - 1.4 mils

VCC (2.5V) - 1.4 mils

INNER 2 - 1.4 mils

GROUND3 - 1.4 mils

BOTTOM - 2.1 mils

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

HASEEB BHUTTA 6/15/04

L MCTEER/ S DUBE/B KRUEGER

Danny King

50 ohm traces are 6.5 mil outer

and 4.5 mil inner w/ 2W min spacing

100 ohm diff clks are 5.5 mil w/

9.5 mils separation outer and

4.5 mils w/ 20.5 mil separation

inner

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

12/17/01

6/16/04

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

TITLE

SCHEM,MEM-CRD,6DIMM,PE4600

DWG NO.

DATE

8Y810

6/15/2004 1 OF 18

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

COMPUTER

CORPORATION

AUSTIN,TEXAS

SHEET

REV.

DCBA

2

3

4

A02

1

2,16

2,16

2,16

2

6,9,12

6,9,12

6,9,12

6,9,12

5,7,12

,3,5,6,8,10,12-14

3

ADD*_1E891_BRKT,LF,MEC,PE4600

ADD*_6G099_BRKT, PLSTC, LF, MEC, REAR, PE4600

ADD*_7G436_ASSY, BRKT, MTG, RT, BK, MEC, PE4600

ADD*_9G342_ASSY, BRKT, MTG, RT, MEC, PE4600

ADD*_9G991_BRKT SCREW

ADD*_9G991_BRKT SCREW

Bracket and screw part numbers

P1

NC_A2

VCC12_VCC25

VCC12_VCC25

VCC12_VCC25

NC_A6

CSTRB1

3

CSTRB0

3

CMD18

15

CMD21

15

CMD23

15

CMD19

15

CMD1

15

CMD7

15

CMD5

15

CMD4

15

CMD8

15

CMD9

15

CMD12

15

CMD10

15

CMD25

15

CMD31

15

CMD29

15

CMD30

15

MECC3

15

MECC1

15

16

VCC25_START

16

B_MA12

UNIQUE_ID

3,4

B_MA11

B_MA9

B_MA7

A_MA5

ENV_SDA

13

VTT_SSTL

VCC25_PWRGD

1

A1

2

A2

3

A3

4

A4

5

A5

6

A6

7

A7

8

A8

9

A9

10

A10

11

A11

12

A12

13

A13

14

A14

15

A15

16

A16

17

A17

18

A18

19

A19

20

A20

21

A21

22

A22

23

A23

24

A24

25

A25

26

A26

27

A27

28

A28

29

A29

30

A30

31

A31

32

A32

33

A33

34

A34

35

A35

36

A36

37

A37

38

A38

39

A39

40

A40

41

A41

42

A42

43

A43

44

A44

45

A45

46

A46

47

A47

48

A48

49

A49

50

A50

51

A51

52

A52

53

A53

54

A54

55

A55

56

A56

2X165 EDGE

HETERO 1 OF 3

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

166

B1

167

B2

168

B3

169

B4

170

B5

171

B6

172

B7

173

B8

174

B9

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

MEM_PRES0 GROUNDED ON PLANAR

VCC12_VCC25

VCC12_VCC25

VCC12_VCC25

NC_B2

CMD17

CMD20

CMD16

CMD22

CMD3

CMD6

CMD2

CMD0

CMD15

CMD13

CMD14

CMD11

CMD24

CMD28

CMD26

CMD27

NC_B30

MECC2

MSTRB0

MECC0

NC_18

RESET

A_MA12

NC_50

NC_33

A_MA11

NC_31

A_MA9

NC_29

A_MA7

A_MA8

NC_27

MEM_PRES0

NC_15

ENV_SCL

2,16

2,16

2,16

15

15

15

15

15

15

15

15

15

15

15

15

15

15

15

15

15

15

15

13

5,7,12

5,7,12

5,7,12

5,7,12

5,7,12

13

13

6,9,12

5,7,12

6,9,12

5,7,12

6,9,12

5,7,12

5,7,12

5,7,12

5,7,12

5,6

7,9

5,6

7,9

7,9

7,9

5,6

5,6

5,6

7,9

7,9

7,9

15

15

15

3,4,12

3,4,12

3,4,12

3,4,12

CA

P1

119

NC_13

PLLRST

3,4

CSTRB2

4

CSTRB3

4

CMD38

15

CMD39

15

CMD32

15

CMD36

15

CMD33

15

CMD37

15

CMD46

15

CMD43

15

CMD48

15

CMD51

15

CMD55

15

CMD52

15

CMD63

15

CMD61

15

CMD62

15

CMD60

15

NC_A160

VCC12_VTT

2,14

NC_A163 NC_B163

A119

120

A120

121

A121

122

A122

123

A123

124

A124

125

A125

126

A126

127

A127

128

A128

129

A129

130

A130

131

A131

132

A132

133

A133

134

A134

135

A135

136

A136

137

A137

138

A138

139

A139

140

A140

141

A141

142

A142

143

A143

144

A144

145

A145

146

A146

147

A147

148

A148

149

A149

150

A150

151

A151

152

A152

153

A153

154

A154

155

A155

156

A156

157

A157

158

A158

159

A159

160

A160

161

A161

162

A162

163

A163

164

A164

165

A165

2X165 EDGE

HETERO 3 OF 3

B119

B120

B121

B122

B123

B124

B125

B126

B127

B128

B129

B130

B131

B132

B133

B134

B135

B136

B137

B138

B139

B140

B141

B142

B143

B144

B145

B146

B147

B148

B149

B150

B151

B152

B153

B154

B155

B156

B157

B158

B159

B160

B161

B162

B163

B164

B165

284

285

286

287

288

289

290

291

292

293

294

295

296

297

298

299

300

301

302

303

304

305

306

307

308

309

310

311

312

313

314

315

316

317

318

319

320

321

322

323

324

325

326

327

328

329

330

MEM_PRES1

NC_ISOLATE

CLKIN0_N

CLKIN0_P

NC_B133

VTT_PWRGD

VCC12_VTT

MEM_PRES1 PULLED UP ON PLANAR

B D

6,9,12

5,11

5,11

6,9,12

6,9,12

11,13,14,16

6,9,12

6,9,12

6,9,12

5,7,12

2-7,9,11,13,14,16

B_MA5

ASCLK_3P3V

ASDATA_3P3V

R1_MA10

7,9

B_MA3

B_MA2

VCC33

B_MA1

B_MA0

B_CKE

A_CKE

R2_MA10

7,9

R1_WE_0

7,9

R2_BA1_0

7,9

A_CS_3

7,9

R1_BA0_0

7,9

R0_BA0_0

5,6

A_CS_0

5,6

R0_WE_0

5,6

R2_RAS_0

7,9

A_CS_4

7,9

A_CS_5

7,9

NC_200

MECC7

15

MECC6

15

NC_25

VCC25

P1

57

A57

58

A58

59

A59

60

A60

61

A61

62

A62

63

A63

64

A64

65

A65

66

A66

67

A67

68

A68

69

A69

70

A70

71

A71

72

A72

73

A73

74

A74

75

A75

76

A76

77

A77

78

A78

79

A79

80

A80

81

A81

82

A82

83

A83

84

A84

85

A85

86

A86

87

A87

88

A88

89

A89

90

A90

91

A91

92

A92

93

A93

94

A94

95

A95

96

A96

97

A97

98

A98

99

A99

100

A100

101

A101

102

A102

103

A103

104

A104

105

A105

106

A106

107

A107

108

A108

109

A109

110

A110

111

A111

112

A112

113

A113

114

A114

115

A115

116

A116

117

A117

118

A118

2X165 EDGE

HETERO 2 OF 3

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

B83

B84

B85

B86

B87

B88

B89

B90

B91

B92

B93

B94

B95

B96

B97

B98

B99

B100

B101

B102

B103

B104

B105

B106

B107

B108

B109

B110

B111

B112

B113

B114

B115

B116

B117

B118

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

275

276

277

278

279

280

281

282

283

B_MA8

A_MA6

NC_22

NC_19

B_MA6

A_MA4

B_MA4

A_MA3

A_MA2

NC_P1_236

A_MA1

NC_24

NC_21

A_MA0

R0_MA10

R1_BA1_0

R0_BA1_0

R1_CAS_0

A_CS_2

R1_RAS_0

A_CS_1

R0_RAS_0

R0_CAS_0

R2_BA0_0

R2_WE_0

R2_CAS_0

NC_20

NC_357

MSTRB1

MECC4

MECC5

RCMD1

RCMD2

RCMD3

RCMD0

NC_3001

NC_28

NC_800

NC_17

NC_37

SDOE

NC_12

NC_11

NC_10

NC_14

VTT_START

CMD45

CMD34

CMD44

CMD35

CMD47

CMD42

CMD41

CMD40

CMD49

CMD50

CMD54

CMD53

CMD56

CMD57

CMD59

CMD58

3,4,12

13

14

11

11

14

15

15

15

15

15

15

15

15

15

15

15

15

15

15

15

15

2,14

6-15-2004_13:22

1

2

3

NC PINS CONNECTED TO VIAS (conn pin #):

100, 112, 120, 263, 278, 281, 282, 289, 290, 293

VCC25

C711

12

C710

C709

C708

C707

C706

C705

12

12

0.1uF 16V

0.1uF 16V

4 4

12

0.1uF 16V

12

2

1

C633

0.1uF 16V

+80%-20%

.22uF 16V

12

0.1uF 16V

2

1

C634

.22uF 16V

12

0.1uF 16V

2

1

C635

+80%-20%

0.1uF 16V

2

1

C636

+80%-20%

.22uF 16V

C637

+80%-20%

.22uF 16V

2

1

.22uF 16V

+80%-20%

2-7,9,11,13,14,16

2

2

1

1

C639

C638

+80%-20%

.22uF 16V

.22uF 16V

2

1

C640

+80%-20%

2

1

C623

+80%-20%

.22uF 16V

2

1

C624

+80%-20%

.22uF 16V

2

1

C625

+80%-20%

.22uF 16V

SUB*_78020

2

1

C626

+80%-20%

.22uF 16V

C641

12

+80%-20%

.22uF 16V

CAPS ARE FOR DECOUPLING/BYPASS THROUGHOUT BRD

A B

VCC25

C642

.01UF

12

50V-20%

SUB*_78020

Substitution for part number consolidation

2

1

1

C628

C627

+80%-20%

.22uF 16V

.01UF

50V-20%

2

+80%-20%

.22uF 16V

2-7,9,11,13,14,16

2

2

1

1

C630

C629

+80%-20%

.22uF 16V

.22uF 16V

2

1

C631

+80%-20%

.22uF 16V

VTT_SSTL

2

1

C632

+80%-20%

2

1

C652

+80%-20%

.22uF 16V

2,3,5,6,8,10,12-14

+80%-20%

.22uF 16V

Substitution for part number consolidation

C649

.01UF

12

SUB*_78020

SUB*_78020

C650

12

50V-20%

C651

.01UF

50V-20%

12

SUB*_78020

C648

.01UF

12

50V-20%

SUB*_78020

SUB*_78020

.01UF

12

50V-20%

SUB*_78020

C647

C646

C645

C644

C643

.01UF

.01UF

.01UF

.01UF

12

12

12

12

50V-20%

50V-20%

50V-20%

SUB*_78020

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

SUB*_78020

SUB*_78020

50V-20%

.01UF

50V-20%

VCC25

2-7,9,11,13,14,16

PLANAR CONNECTOR

COMPUTER

CORPORATION

TITLE

AUSTIN,TEXAS

SCHEM,MEM-CRD,6DIMM,PE4600

DWG NO.

DATE

8Y810

6/15/2004

SHEET

DC

REV.

A02

2 OF 18

B D

R431

R_CSTRB1

3

R_CSTRB0

3

1

R242

12 OHM 5%

R247

12 OHM 5%

RN406

18

12 OHM-5%

RN406

27

12 OHM-5%

RN406

36

12 OHM-5%

RN406

45

12 OHM-5%

RN338

18

12 OHM-5%

RN338

45

12 OHM-5%

RN338

36

12 OHM-5%

RN338

27

12 OHM-5%

RN408

45

12 OHM-5%

RN408

36

12 OHM-5%

RN408

27

12 OHM-5%

RN408

18

12 OHM-5%

RN409

45

12 OHM-5%

RN409

36

12 OHM-5%

RN409

27

12 OHM-5%

RN409

18

12 OHM-5%

R226

12

150-5%

R227

12

150-5%

21

21

2

3

R_A_SD0_7

3

R_A_SD0_3

3

NC_RN_1

R_B_SD0_4

3

R_B_SD0_0

3

R_B_SD0_5

3

NC_RN338_1

R_B_SD1_4

3

R_B_SD1_1

3

R_B_SD1_0

3

R_A_SD8_2

3

R_A_SD8_6

3

R_A_SD8_3

3

R_A_SD8_7

3

R_A_SD8_0

3

R_A_SD8_1

3

R_A_DQS8_0

3

R_A_DQS8_1

3

REMC0_ID0

3

REMC0_ID1

3

Strapping option:

~SDOE=0 (DP Mode)

R_A_SD1_1

3

R_A_DQS1_0

3

R_A_SD1_4

3

R_A_SD1_0

3

R_A_SD1_7

3

R_A_SD1_6

3

4 4

R_A_DQS1_1

3

R_A_SD1_5

3

RN180

27

12 OHM-5%

RN180

18

12 OHM-5%

RN180

36

12 OHM-5%

RN180

45

12 OHM-5%

RN181

18

12 OHM-5%

RN181

27

12 OHM-5%

RN181

36

12 OHM-5%

RN181

45

12 OHM-5%

A_SD1_1

A_DQS1_0

A_SD1_4

A_SD1_0

A_SD1_7

A_SD1_6

A_DQS1_1

A_SD1_5

21

15

R433

21

15

2-7,9,11,13,14,16

A_SD0_7

A_SD0_3

NC_RN_8

B_SD0_4

B_SD0_0

B_SD0_5

NC_RN338_8

B_SD1_4

B_SD1_1

B_SD1_0

A_SD8_2

A_SD8_6

A_SD8_3

A_SD8_7

A_SD8_0

A_SD8_1

A_DQS8_0

A_DQS8_1

UNIQUE_ID

SDOE

2-4,12

5,7,8

5,7,8

CSTRB1

2

CSTRB0

2

5,7,8

5,7,8

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

VCC25

2-7,9,11,13,14,16

2,4

NP*

R453

1K-5%

12

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

VCC25

R617

R451

1K-5%

12

R_B_SD1_5

3

R_B_DQS1_0

3

R_B_DQS1_1

3

R_B_SD1_6

3

R_B_SD1_7

3

R_B_SD1_2

3

R_B_SD1_3

3

R_B_SD2_4

3

R_CSTRB0

3

R_CSTRB0

3

R_CSTRB1

3

R_CSTRB1

3

15

R221

12

249 Ohm-1%

2,4,12

2,4,12

2,4,12

2,4,12

R_A_DQS3_1

3

R_A_DQS3_0

3

R_B_DQS2_1

3

R_B_DQS2_0

3

R_A_DQS8_1

3

R_A_DQS8_0

3

R_B_DQS3_1

3

R_B_DQS3_0

3

R_A_DQS0_1

3

R_A_DQS0_0

3

R_B_DQS0_1

3

R_B_DQS0_0

3

R_A_DQS1_1

3

R_A_DQS1_0

3

R_B_DQS1_1

3

R_B_DQS1_0

3

R_A_DQS2_1

3

R_A_DQS2_0

3

1K-5%

12

PU_ISOLATE_DP0

R_MSTRB0

COMP0_DP0

REMC0_ID1

3

REMC0_ID0

3

NC_DP0_B14

NC_DP0_C13

NC_DP0_B15

NC_DP0_C14

R_MECC3

15

R_MECC2

15

R_MECC1

15

R_MECC0

15

R_CMD15

15

R_CMD14

15

R_CMD13

15

R_CMD12

15

R_CMD11

15

R_CMD10

15

R_CMD9

15

R_CMD8

15

R_CMD7

15

R_CMD6

15

R_CMD5

15

R_CMD4

15

R_CMD3

15

R_CMD2

15

R_CMD1

15

R_CMD0

15

R_CMD23

15

R_CMD22

15

R_CMD21

15

R_CMD20

15

R_CMD19

15

R_CMD18

15

R_CMD17

15

R_CMD16

15

R_CMD31

15

R_CMD30

15

R_CMD29

15

R_CMD28

15

R_CMD27

15

R_CMD26

15

R_CMD25

15

R_CMD24

15

RCMD3

RCMD2

RCMD1

RCMD0

2-4,12

RN182

27

12 OHM-5%

RN182

18

12 OHM-5%

RN182

36

12 OHM-5%

RN182

45

12 OHM-5%

RN183

18

12 OHM-5%

RN183

27

12 OHM-5%

RN183

36

12 OHM-5%

RN183

45

12 OHM-5%

L12

D13

N15

SDOE

B_SD1_5

B_DQS1_0

B_DQS1_1

B_SD1_6

B_SD1_7

B_SD1_2

B_SD1_3

B_SD2_4

U24

CSTRB1_1/MA16

R6

CSTRB1_0/NC

G3

CSTRB0_1/MA15

D9

CSTRB0_0/CKE

MSTRB/MEMPAR

C3

COMP0

A2

RSVD2/ECS1_2

B3

RSVD1/ECS1_1

B14

CMD9_3/D_WE1

C13

CMD9_2/C_WE1

B15

CMD9_1/B_WE1

C14

CMD9_0/A_WE1

E12

CMD8_3/D_RAS1

D14

CMD8_2/C_RAS1

F11

CMD8_1/B_RAS1

D15

CMD8_0/A_RAS1

K11

CMD7_3/D_CAS1

L14

CMD7_2/C_CAS1

L13

CMD7_1/B_CAS1

M15

CMD7_0/A_CAS1

M14

CMD6_3/D_BA1_0

CMD6_2/C_BA1_0

M13

CMD6_1/B_BA1_0

L11

CMD6_0/A_BA1_0

R7

CMD5_3/B_CS7

P7

CMD5_2/A_CS7

N7

CMD5_1/B_CS6

M7

CMD5_0/A_CS6

N6

CMD4_3/B_CS5

M6

CMD4_2/A_CS5

R5

CMD4_1/B_CS4

L6

CMD4_0/A_CS4

H2

CMD3_3/B_CS3

H3

CMD3_2/A_CS3

G1

CMD3_1/B_CS2

G2

CMD3_0/A_CS2

G4

CMD2_3/B_CS1

F1

CMD2_2/A_CS1

F2

CMD2_1/B_CS0

F3

CMD2_0/A_CS0

C8

CMD1_3/D_BA0_0

A9

CMD1_2/C_BA0_0

B9

CMD1_1/B_BA0_0

C9

CMD1_0/A_BA0_0

A10

CMD0_3/D_CKE0

B10

CMD0_2/C_CKE0

C10

CMD0_1/B_CKE0

D10

CMD0_0/A_CKE0

C4

RCMD3/ECS1_0

B4

RCMD2/ECS0_2

D5

RCMD1/ECS0_1

A3

RCMD0/ECS0_0

F15

DQS8_1/WE

G11

DQS8_0/RAS

J14

DQS7_1/CAS

J13

DQS7_0/MA14

R13

DQS6_1/MA13

M11

DQS6_0/MA2

N9

DQS5_1/MA11

R9

DQS5_0/MA10

M3

DQS4_1/MA9

N1

DQS4_0/MA8

K1

DQS3_1/MA7

J4

DQS3_0/MA6

E4

DQS2_1/MA5

D2

DQS2_0/MA4

A6

DQS1_1/MA3

D7

DQS1_0/MA12

A13

DQS0_1/MA1

C12

DQS0_0/MA0

B2

ISOLATE

A4

SDOE/ALERT

Jaguar 2.0 Change: Changed REMC fom rev 2.0 to 3.0 (with deglitching circuit)

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

REMC Version 1.0

HETERO 1 OF 2

SUB*_8Y113

This is REMC version 3.0

SD8_7/D_WE

SD8_6/C_WE

SD8_5/B_WE

SD8_4/A_WE

SD8_3/D_RAS

SD8_2/C_RAS

SD8_1/B_RAS

SD8_0/A_RAS

SD7_7/D_CAS

SD7_6/C_CAS

SD7_5/B_CAS

SD7_4/A_CAS

SD7_3/D_MA12

SD7_2/C_MA12

SD7_1/B_MA12

SD7_0/A_MA12

SD6_7/D_BA1_1

SD6_6/C_BA1_1

SD6_5/B_BA1_1

SD6_4/A_BA1_1

SD6_3/D_MA2

SD6_2/C_MA2

SD6_1/B_MA2

SD6_0/A_MA2

SD5_7/D_MA11

SD5_6/C_MA11

SD5_5/B_MA11

SD5_4/A_MA11

SD5_3/D_MA10

SD5_2/C_MA10

SD5_1/B_MA10

SD5_0/A_MA10

SD4_7/D_MA9

SD4_6/C_MA9

SD4_5/B_MA9

SD4_4/A_MA9

SD4_3/D_MA8

SD4_2/C_MA8

SD4_1/B_MA8

SD4_0/A_MA8

SD3_7/D_MA7

SD3_6/C_MA7

SD3_5/B_MA7

SD3_4/A_MA7

SD3_3/D_MA6

SD3_2/C_MA6

SD3_1/B_MA6

SD3_0/A_MA6

SD2_7/D_MA5

SD2_6/C_MA5

SD2_5/B_MA5

SD2_4/A_MA5

SD2_3/D_MA4

SD2_2/C_MA4

SD2_1/B_MA4

SD2_0/A_MA4

SD1_7/D_MA3

SD1_6/C_MA3

SD1_5/B_MA3

SD1_4/A_MA3

SD1_3/D_BA0_1

SD1_2/C_BA0_1

SD1_1/B_BA0_1

SD1_0/A_BA0_1

SD0_7/D_MA1

SD0_6/C_MA1

SD0_5/B_MA1

SD0_4/A_MA1

SD0_3/D_MA0

SD0_2/C_MA0

SD0_1/B_MA0

SD0_0/A_MA0

R_A_SD2_4

3

R_A_SD2_0

3

R_A_SD1_3

3

R_A_SD1_2

3

R_A_DQS2_1

3

R_A_DQS2_0

3

R_A_SD2_5

3

R_A_SD2_1

3

R_A_SD3_6

E14

R_A_SD3_7

E15

R_A_SD3_5

F13

R_A_SD3_4

F14

R_A_SD3_3

G12

R_A_SD3_2

G13

R_A_SD3_0

G15

R_A_SD3_1

H11

R_B_SD2_7

H15

R_B_SD2_5

H14

R_B_SD2_4

H13

R_B_SD2_6

J15

R_B_SD2_0

J12

R_B_SD2_2

K15

R_B_SD2_3

K14

R_B_SD2_1

K13

R_A_SD8_5

N13

R_A_SD8_6

R14

R_A_SD8_7

P13

R_A_SD8_4

N12

R_A_SD8_2

P12

R_A_SD8_3

R12

R_A_SD8_1

N11

R_A_SD8_0

M10

R_B_SD3_5

N10

R_B_SD3_6

P10

R_B_SD3_7

R10

R_B_SD3_4

M9

R_B_SD3_2

P9

R_B_SD3_1

M8

R_B_SD3_3

R8

R_B_SD3_0

P8

R_A_SD0_7

P2

R_A_SD0_6

N3

R_A_SD0_5

P1

R_A_SD0_4

N2

R_A_SD0_3

L4

R_A_SD0_2

M2

R_A_SD0_1

K5

R_A_SD0_0

M1

R_B_SD0_7

L2

R_B_SD0_6

L1

R_B_SD0_5

K3

R_B_SD0_4

K2

R_B_SD0_3

J3

R_B_SD0_2

J1

R_B_SD0_1

J2

R_B_SD0_0

H5

R_A_SD1_7

F5

R_A_SD1_6

E2

R_A_SD1_5

E3

R_A_SD1_4

D1

R_A_SD1_3

C1

R_A_SD1_2

D3

R_A_SD1_1

C2

R_A_SD1_0

B1

R_B_SD1_7

B5

R_B_SD1_6

A5

R_B_SD1_5

C6

R_B_SD1_4

B6

R_B_SD1_3

C7

R_B_SD1_2

A7

R_B_SD1_1

B7

R_B_SD1_0

D8

R_A_SD2_7

C11

R_A_SD2_5

A12

R_A_SD2_6

D11

R_A_SD2_4

B12

R_A_SD2_3

E11

R_A_SD2_2

A14

R_A_SD2_1

B13

R_A_SD2_0

D12

RN184

27

12 OHM-5%

RN184

18

12 OHM-5%

RN184

36

12 OHM-5%

RN184

45

12 OHM-5%

RN185

18

12 OHM-5%

RN185

27

12 OHM-5%

RN185

36

12 OHM-5%

RN185

45

12 OHM-5%

A_SD2_4

A_SD2_0

A_SD1_3

A_SD1_2

A_DQS2_1

A_DQS2_0

A_SD2_5

A_SD2_1

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

4

4

3

4

3

4

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

R_A_SD3_2

3

R_A_SD3_6

3

R_A_DQS3_1

3

R_A_DQS3_0

3

R_A_SD8_5

3

R_A_SD8_4

3

R_A_SD3_7

3

R_A_SD3_3

3

R_B_SD3_5

3

R_B_SD3_1

3

R_B_DQS3_0

3

R_B_DQS3_1

3

R_B_SD2_3

3

NC_RN171_2

R_B_SD3_0

3

R_B_SD3_4

3

R_A_SD3_5

3

R_A_SD3_1

3

R_A_SD3_4

3

R_A_SD3_0

3

R_A_SD2_3

3

R_A_SD2_7

3

R_A_SD2_6

3

R_A_SD2_2

3

R_B_SD2_2

3

R_B_DQS2_1

3

R_B_SD2_6

3

R_B_SD2_7

3

R_B_SD2_0

3

R_B_SD2_1

3

R_B_SD2_5

3

R_B_DQS2_0

3

R_A_SD0_2

3

R_A_SD0_6

3

R_A_DQS0_0

3

R_A_DQS0_1

3

R_A_SD0_1

3

R_A_SD0_5

3

R_A_SD0_0

3

R_A_SD0_4

3

R_B_SD0_1

3

NC_RN178_1 NC_RN178_8

R_B_DQS0_0

3

R_B_DQS0_1

3

R_B_SD0_2

3

R_B_SD0_6

3

R_B_SD0_3

3

R_B_SD0_7

3

RN168

18

12 OHM-5%

RN168

27

12 OHM-5%

RN168

36

12 OHM-5%

RN168

45

12 OHM-5%

RN169

18

12 OHM-5%

RN169

27

12 OHM-5%

RN169

36

12 OHM-5%

RN169

45

12 OHM-5%

RN170

27

12 OHM-5%

RN170

18

12 OHM-5%

RN170

36

12 OHM-5%

RN170

45

12 OHM-5%

RN171

18

12 OHM-5%

RN171

27

12 OHM-5%

RN171

36

12 OHM-5%

RN171

45

12 OHM-5%

RN172

27

12 OHM-5%

RN172

18

12 OHM-5%

RN172

36

12 OHM-5%

RN172

45

12 OHM-5%

RN173

18

12 OHM-5%

RN173

27

12 OHM-5%

RN173

36

12 OHM-5%

RN173

45

12 OHM-5%

RN174

27

12 OHM-5%

RN174

18

12 OHM-5%

RN174

36

12 OHM-5%

RN174

45

12 OHM-5%

RN175

18

12 OHM-5%

RN175

27

12 OHM-5%

RN175

36

12 OHM-5%

RN175

45

12 OHM-5%

RN176

27

12 OHM-5%

RN176

18

12 OHM-5%

RN176

36

12 OHM-5%

RN176

45

12 OHM-5%

RN177

18

12 OHM-5%

RN177

27

12 OHM-5%

RN177

36

12 OHM-5%

RN177

45

12 OHM-5%

RN178

27

12 OHM-5%

RN178

18

12 OHM-5%

RN178

36

12 OHM-5%

RN178

45

12 OHM-5%

RN179

18

12 OHM-5%

RN179

27

12 OHM-5%

RN179

36

12 OHM-5%

RN179

45

12 OHM-5%

A_SD3_2

A_SD3_6

A_DQS3_1

A_DQS3_0

A_SD8_5

A_SD8_4

A_SD3_7

A_SD3_3

B_SD3_5

B_SD3_1

B_DQS3_0

B_DQS3_1

B_SD2_3

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

NC_RN171_7

B_SD3_0

B_SD3_4

A_SD3_5

A_SD3_1

A_SD3_4

A_SD3_0

A_SD2_3

A_SD2_7

A_SD2_6

A_SD2_2

B_SD2_2

B_DQS2_1

B_SD2_6

B_SD2_7

B_SD2_0

B_SD2_1

B_SD2_5

B_DQS2_0

A_SD0_2

A_SD0_6

A_DQS0_0

A_DQS0_1

A_SD0_1

A_SD0_5

A_SD0_0

A_SD0_4

B_SD0_1

B_DQS0_0

B_DQS0_1

B_SD0_2

B_SD0_6

B_SD0_3

B_SD0_7

6,9,10

6,9,10

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

A B

CA

VCC25

3,14

2-7,9,11,13,14,16

2-7,9,11,13,14,16

1uF

12

C619

10V-10%

1uF

12

C620

10V-10%

SUB*_78020

C81

.01UF

12

50V-20%

10V-20%

100uF

C582

2

R2

P3

N5

M12

A1

L5

N4

R15

P15

D4

C5

P14

P11

P6

M4

L15

L9

L7

K10

K9

K7

K6

K4

J11

J10

J6

H12

H4

H1

G10

G6

F10

F9

F7

F6

F4

E13

E9

E7

D6

B8

A15

A11

C732

+80%-20%

.22uF 16V

C731

+80%-20%

.22uF 16V

C82

.01UF

50V-20%

SUB*_78020

+

C579

1

2

CLKN

CLKP

PLLRST

TESTMODE

RESET

SDA

SCK

VREF_R15

VREF_P15

VREF_D4

VREF_C5

VDD_P14

VDD_P11

VDD_P6

VDD_M4

VDD_L15

VDD_L9

VDD_L7

VDD_K10

VDD_K9

VDD_K7

VDD_K6

VDD_K4

VDD_J11

VDD_J10

VDD_J6

VDD_H12

VDD_H4

VDD_H1

VDD_G10

VDD_G6

VDD_F10

VDD_F9

VDD_F7

VDD_F6

VDD_F4

VDD_E13

VDD_E9

VDD_E7

VDD_D6

VDD_B8

VDD_A15

VDD_A11

10V-20%

CLKDP0_N

11

CLKDP0_P

1K-5%

3,14

VCC25

11

2,4

TESTMODE_DP0

4,13

R_ASDATA_DP0

3

R_ASCLK_DP0

3

SSTLREF_R1

C79

.01UF

12

50V-20%

SUB*_78020

10V-20%

+

33uF

C583

1

2

PLLRST

SRESET

VCC25

21

C600

21

C603

C80

12

10V-20%

+

33uF

1

R447

12

2-7,9,11,13,14,16

SSTLREF_R1

Substitution for p/n consolidation

SUB*_78020

U24

DVDD

DGND

AVDD

AGND

GND_R11

GND_R1

GND_P5

GND_N14

GND_N8

GND_L10

GND_L8

GND_L3

GND_K12

GND_K8

GND_J9

GND_J8

GND_J7

GND_J5

GND_H10

GND_H9

GND_H8

GND_H7

GND_H6

GND_G14

GND_G9

GND_G8

GND_G7

GND_G5

GND_F12

GND_F8

GND_E10

GND_E8

GND_E6

GND_E5

GND_E1

GND_C15

GND_B11

REMC Version 1.0

HETERO 2 OF 2

SUB*_8Y113

This is REMC version 3.0

12

+80%-20%

.22uF 16V

12

+80%-20%

.22uF 16V

C1

12

.01UF

12

50V-20%

VCC25

+

33uF

C581

1

2

GND_A8

C4

C2

12

12

0.1uF 16V

0.1uF 16V

2-7,9,11,13,14,16

12

C590

.22uF 16V

R3

P4

M5

R4

22uF 10V

12

BE USED ON NEW DESIGNS.

THIS PART IS NOT TO

R11

R1

P5

N14

N8

L10

L8

L3

K12

K8

J9

J8

J7

J5

H10

H9

H8

H7

H6

G14

G9

G8

G7

G5

F12

F8

E10

E8

E6

E5

E1

C15

B11

A8

4-7,9,13

FSTEDG_ASCLK_2P5V

4,5

C474

DPLL TEST MODE:

TESTMODE = 0 AND

RCMD1 = 1

INPUTS IN DPLL TESTMODE:

R_CMD[32:53]

OUTPUTS IN DPLL AND XOR

TESTMODE

SDA, SCK, ~SDOE/~ALERT

XOR TREE MODE:

TESTMODE = 0, RCMD1 = 0,

AND ECS1[2:1] = 2'b00

MDLL TEST MODE:

TESTMODE = 0, RCMD1 = 0,

AND ECS1[2:1] = 2'b01

SDLL TREE MODE:

TESTMODE = 0, RCMD1 = 0,

AND ECS1[2:1] = 2'b10

ASDATA_2P5V

21

L14

47uH 135MA

NP*

NP*

R441

12

2-1%

C712

12

0.1uF 16V

R488

12

0-5%

R489

12

0-5%

VCC25

C713

12

0.1uF 16V

VCC25

2-7,9,11,13,14,16

R484

12

8.2K-5%

VCC25

2-7,9,11,13,14,16

R485

12

8.2K-5%

DISCONNECT REMC I2C BUS

DUE TO NO POST PROBLEM

Substitution for p/n consolidation

2-7,9,11,13,14,16

0.1uF 16V

12

C589

+80%-20%

+80%-20%

.22uF 16V

VCC25

SUB*_79015

VTT_SSTL

SUB*_79015

21

C38

C37

.001UF

50V-20%

2,5,6,8,10,12-14

21

.001UF

50V-20%

SUB*_79015

21

C39

REMC DATA PATH 0

TITLE

SCHEM,MEM-CRD,6DIMM,PE4600

DWG NO.

8Y810

DATE

6/15/2004

DC

6-15-2004_13:22

2-7,9,11,13,14,16

R_ASDATA_DP0

R_ASCLK_DP0

SUB*_79015

21

21

C41

C40

.001UF

.001UF

50V-20%

50V-20%

SUB*_79015

COMPUTER

CORPORATION

AUSTIN,TEXAS

SHEET

3

3

SUB*_79015

21

C42

.001UF

50V-20%

REV.

3 OF 18

.001UF

50V-20%

A02

1

2

3

4,14

CA

VCC25

R448

12

2-7,9,11,13,14,16

SSTLREF_R2

VCC25

SUB*_78020

10V-20%

+

33uF

C585

1

2

2-7,9,11,13,14,16

12

C733

+80%-20%

.22uF 16V

12

C734

+80%-20%

.22uF 16V

C547

12

50V-20%

SUB*_78020

VCC25

10V-20%

+

33uF

1

2

R2

P3

N5

M12

A1

L5

N4

R15

P15

D4

C5

P14

P11

P6

M4

L15

L9

L7

K10

K9

K7

K6

K4

J11

J10

J6

H12

H4

H1

G10

G6

F10

F9

F7

F6

F4

E13

E9

E7

D6

B8

A15

A11

+80%-20%

.22uF 16V

+80%-20%

.22uF 16V

SUB*_78020

C548

.01UF

50V-20%

C584

CLKDP1_N

11

CLKDP1_P

11

1K-5%

4,14

C545

10V-20%

PLLRST

2,3

TESTMODE_DP1

SRESET

3,13

R_ASDATA_DP1

4

R_ASCLK_DP1

4

SSTLREF_R2

VCC25

21

1uF

12

C621

C604

10V-10%

21

1uF

12

C622

C607

10V-10%

Substitution for p/n consolidation

SUB*_78020

C546

.01UF

.01UF

12

12

50V-20%

10V-20%

100uF

+

+

33uF

1

2

C586

C580

1

2

CLKN

CLKP

PLLRST

TESTMODE

RESET

SDA

SCK

VREF_R15

VREF_P15

VREF_D4

VREF_C5

VDD_P14

VDD_P11

VDD_P6

VDD_M4

VDD_L15

VDD_L9

VDD_L7

VDD_K10

VDD_K9

VDD_K7

VDD_K6

VDD_K4

VDD_J11

VDD_J10

VDD_J6

VDD_H12

VDD_H4

VDD_H1

VDD_G10

VDD_G6

VDD_F10

VDD_F9

VDD_F7

VDD_F6

VDD_F4

VDD_E13

VDD_E9

VDD_E7

VDD_D6

VDD_B8

VDD_A15

VDD_A11

12

U25

DVDD

DGND

AVDD

AGND

GND_R11

GND_R1

GND_P5

GND_N14

GND_N8

GND_L10

GND_L8

GND_L3

GND_K12

GND_K8

GND_J9

GND_J8

GND_J7

GND_J5

GND_H10

GND_H9

GND_H8

GND_H7

GND_H6

GND_G14

GND_G9

GND_G8

GND_G7

GND_G5

GND_F12

GND_F8

GND_E10

GND_E8

GND_E6

GND_E5

GND_E1

GND_C15

GND_B11

C518

12

0.1uF 16V

0.1uF 16V

GND_A8

3,5-7,9,13

C520

12

REMC Version 1.0

HETERO 2 OF 2

SUB*_8Y113

This is REMC version 3.0

C519

12

.01UF

50V-20%

2-7,9,11,13,14,16

R442

12

2-1%

21

L15

47uH 135MA

R3

P4

M5

R4

BE USED ON NEW DESIGNS.

THIS PART IS NOT TO

R11

R1

P5

N14

N8

L10

L8

L3

K12

K8

J9

J8

J7

J5

H10

H9

H8

H7

H6

G14

G9

G8

G7

G5

F12

F8

E10

E8

E6

E5

E1

C15

B11

A8

ASDATA_2P5V

FSTEDG_ASCLK_2P5V

3,5

22uF 10V

12

C475

R490

12

NP*

0-5%

R491

12

NP*

0-5%

C715

C714

12

0.1uF 16V

VCC25

2-7,9,11,13,14,16

R487

12

12

0.1uF 16V

8.2K-5%

DISCONNECT REMC I2C BUS

DUE TO NO POST PROBLEM

Substitution for p/n consolidation

2-7,9,11,13,14,16

21

1uF

C592

10V-10%

0.1uF 16V

VCC25

SUB*_79015

21

C527

SUB*_79015

C528

.001UF

50V-20%

SUB*_79015

21

.001UF

21

C529

50V-20%

REMC DATA PATH 1

TITLE

SCHEM,MEM-CRD,6DIMM,PE4600

DWG NO.

DATE

DC

6-15-2004_13:22

VCC25

VCC25

R486

12

R_ASCLK_DP1

21

C530

.001UF

50V-20%

SUB*_79015

8Y810

6/15/2004

2-7,9,11,13,14,16

2-7,9,11,13,14,16

8.2K-5%

R_ASDATA_DP1

4

SUB*_79015

C531

.001UF

50V-20%

21

21

C532

.001UF

50V-20%

SUB*_79015

COMPUTER

CORPORATION

AUSTIN,TEXAS

REV.

SHEET

4 OF 18

C591

.001UF

50V-20%

A02

21

4

1uF

10V-10%

B D

U25

SD8_7/D_WE

SD8_6/C_WE

SD8_5/B_WE

SD8_4/A_WE

SD8_3/D_RAS

SD8_2/C_RAS

SD8_1/B_RAS

SD8_0/A_RAS

SD7_7/D_CAS

SD7_6/C_CAS

SD7_5/B_CAS

SD7_4/A_CAS

SD7_3/D_MA12

SD7_2/C_MA12

SD7_1/B_MA12

SD7_0/A_MA12

SD6_7/D_BA1_1

SD6_6/C_BA1_1

SD6_5/B_BA1_1

SD6_4/A_BA1_1

SD6_3/D_MA2

SD6_2/C_MA2

SD6_1/B_MA2

SD6_0/A_MA2

SD5_7/D_MA11

SD5_6/C_MA11

SD5_5/B_MA11

SD5_4/A_MA11

SD5_3/D_MA10

SD5_2/C_MA10

SD5_1/B_MA10

SD5_0/A_MA10

SD4_7/D_MA9

SD4_6/C_MA9

SD4_5/B_MA9

SD4_4/A_MA9

SD4_3/D_MA8

SD4_2/C_MA8

SD4_1/B_MA8

SD4_0/A_MA8

SD3_7/D_MA7

SD3_6/C_MA7

SD3_5/B_MA7

SD3_4/A_MA7

SD3_3/D_MA6

SD3_2/C_MA6

SD3_1/B_MA6

SD3_0/A_MA6

SD2_7/D_MA5

SD2_6/C_MA5

SD2_5/B_MA5

SD2_4/A_MA5

SD2_3/D_MA4

SD2_2/C_MA4

SD2_1/B_MA4

SD2_0/A_MA4

SD1_7/D_MA3

SD1_6/C_MA3

SD1_5/B_MA3

SD1_4/A_MA3

SD1_3/D_BA0_1

SD1_2/C_BA0_1

SD1_1/B_BA0_1

SD1_0/A_BA0_1

SD0_7/D_MA1

SD0_6/C_MA1

SD0_5/B_MA1

SD0_4/A_MA1

SD0_3/D_MA0

SD0_2/C_MA0

SD0_1/B_MA0

REMC Version 1.0

HETERO 1 OF 2

SD0_0/A_MA0

SUB*_8Y113

This is REMC version 3.0

R_A_SD4_1

4

R_A_SD4_5

4

R_A_SD4_4

4

R_A_SD4_0

4

R_B_SD4_1

4

R_B_SD8_3

4

R_B_SD4_6

E14

R_B_SD4_7

E15

R_B_SD4_5

F13

R_B_SD4_4

F14

R_B_SD4_1

G12

R_B_SD4_2

G13

R_B_SD4_3

G15

R_B_SD4_0

H11

R_B_SD5_4

H15

R_B_SD5_6

H14

R_B_SD5_7

H13

R_B_SD5_5

J15

R_B_SD5_3

J12

R_B_SD5_2

K15

R_B_SD5_1

K14

R_B_SD5_0

K13

R_A_SD6_5

N13

R_A_SD6_7

R14

R_A_SD6_6

P13

R_A_SD6_4

N12

R_A_SD6_3

P12

R_A_SD6_2

R12

R_A_SD6_1

N11

R_A_SD6_0

M10

R_B_SD6_5

N10

R_B_SD6_6

P10

R_B_SD6_7

R10

R_B_SD6_4

M9

R_B_SD6_1

P9

R_B_SD6_0

M8

R_B_SD6_2

R8

R_B_SD6_3

P8

R_A_SD7_6

P2

R_A_SD7_4

N3

R_A_SD7_7

P1

R_A_SD7_5

N2

R_A_SD7_0

L4

R_A_SD7_2

M2

R_A_SD7_1

K5

R_A_SD7_3

M1

R_B_SD7_6

L2

R_B_SD7_7

L1

R_B_SD7_4

K3

R_B_SD7_5

K2

R_B_SD7_3

J3

R_B_SD7_2

J1

R_B_SD7_1

J2

R_B_SD7_0

H5

R_A_SD4_7

F5

R_A_SD4_5

E2

R_A_SD4_6

E3

R_A_SD4_4

D1

R_A_SD4_3

C1

R_A_SD4_2

D3

R_A_SD4_1

C2

R_A_SD4_0

B1

R_B_SD8_5

B5

R_B_SD8_4

A5

R_B_SD8_7

C6

R_B_SD8_6

B6

R_B_SD8_2

C7

R_B_SD8_0

A7

R_B_SD8_1

B7

R_B_SD8_3

D8

R_A_SD5_7

C11

R_A_SD5_5

A12

R_A_SD5_6

D11

R_A_SD5_4

B12

R_A_SD5_3

E11

R_A_SD5_0

A14

R_A_SD5_1

B13

R_A_SD5_2

D12

RN351

18

12 OHM-5%

RN351

27

12 OHM-5%

RN351

36

12 OHM-5%

RN351

45

12 OHM-5%

RN370

45

12 OHM-5%

R445

12 OHM 5%

A_SD4_1

A_SD4_5

A_SD4_4

A_SD4_0

B_SD4_1

B_SD8_3

21

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

5,7,8

5,7,8

5,7,8

5,7,8

6,9,10

6,9,10

SDOE

RN369

B_SD4_5

18

RN369

27

B_DQS4_0

RN369

B_SD4_2

36

RN369

45

B_DQS4_1

RN370

NC_RN370_8NC_RN370_1

18

RN370

B_SD4_0

27

RN370

B_SD4_4

36

R446

B_SD7_3

21

L12

CSTRB1_1/MA16

R6

CSTRB1_0/NC

G3

CSTRB0_1/MA15

D9

CSTRB0_0/CKE

D13

MSTRB/MEMPAR

C3

COMP0

A2

RSVD2/ECS1_2

B3

RSVD1/ECS1_1

B14

CMD9_3/D_WE1

C13

CMD9_2/C_WE1

B15

CMD9_1/B_WE1

C14

CMD9_0/A_WE1

E12

CMD8_3/D_RAS1

D14

CMD8_2/C_RAS1

F11

CMD8_1/B_RAS1

D15

CMD8_0/A_RAS1

K11

CMD7_3/D_CAS1

L14

CMD7_2/C_CAS1

L13

CMD7_1/B_CAS1

M15

CMD7_0/A_CAS1

M14

CMD6_3/D_BA1_0

N15

CMD6_2/C_BA1_0

M13

CMD6_1/B_BA1_0

L11

CMD6_0/A_BA1_0

R7

CMD5_3/B_CS7

P7

CMD5_2/A_CS7

N7

CMD5_1/B_CS6

M7

CMD5_0/A_CS6

N6

CMD4_3/B_CS5

M6

CMD4_2/A_CS5

R5

CMD4_1/B_CS4

L6

CMD4_0/A_CS4

H2

CMD3_3/B_CS3

H3

CMD3_2/A_CS3

G1

CMD3_1/B_CS2

G2

CMD3_0/A_CS2

G4

CMD2_3/B_CS1

F1

CMD2_2/A_CS1

F2

CMD2_1/B_CS0

F3

CMD2_0/A_CS0

C8

CMD1_3/D_BA0_0

A9

CMD1_2/C_BA0_0

B9

CMD1_1/B_BA0_0

C9

CMD1_0/A_BA0_0

A10

CMD0_3/D_CKE0

B10

CMD0_2/C_CKE0

C10

CMD0_1/B_CKE0

D10

CMD0_0/A_CKE0

C4

RCMD3/ECS1_0

B4

RCMD2/ECS0_2

D5

RCMD1/ECS0_1

A3

RCMD0/ECS0_0

F15

DQS8_1/WE

G11

DQS8_0/RAS

J14

DQS7_1/CAS

J13

DQS7_0/MA14

R13

DQS6_1/MA13

M11

DQS6_0/MA2

N9

DQS5_1/MA11

R9

DQS5_0/MA10

M3

DQS4_1/MA9

N1

DQS4_0/MA8

K1

DQS3_1/MA7

J4

DQS3_0/MA6

E4

DQS2_1/MA5

D2

DQS2_0/MA4

A6

DQS1_1/MA3

D7

DQS1_0/MA12

A13

DQS0_1/MA1

C12

DQS0_0/MA0

B2

ISOLATE

A4

SDOE/ALERT

Jaguar 2.0 Change: Changed REMC fom rev 2.0 to 3.0 (with deglitching circuit)

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

R435

21

R_CSTRB3

4

R_CSTRB2

4

2-7,9,11,13,14,16

R228

R229

RN359

18

12 OHM-5%

RN359

27

12 OHM-5%

RN359

36

12 OHM-5%

RN359

45

12 OHM-5%

RN360

18

12 OHM-5%

RN360

27

12 OHM-5%

RN360

36

12 OHM-5%

RN360

45

12 OHM-5%

RN361

18

12 OHM-5%

RN361

27

12 OHM-5%

RN361

36

12 OHM-5%

RN361

45

12 OHM-5%

RN344

45

12 OHM-5%

RN344

18

12 OHM-5%

RN344

27

12 OHM-5%

RN362

18

12 OHM-5%

RN362

27

12 OHM-5%

RN344

36

12 OHM-5%

RN362

36

12 OHM-5%

RN407

18

12 OHM-5%

RN407

27

12 OHM-5%

RN407

36

12 OHM-5%

RN407

45

12 OHM-5%

R483

12 OHM 5%

RN362

45

12 OHM-5%

UNIQUE_ID

B_DQS8_0

B_DQS8_1

B_SD8_2

B_SD8_6

B_SD5_7

B_SD6_0

B_SD6_1

B_SD6_4

B_SD4_6

B_SD4_7

B_SD4_3

B_SD5_4

A_SD5_5

A_DQS5_0

A_DQS5_1

A_SD7_6

A_DQS7_1

A_SD5_1

A_SD7_1

21

A_SD7_0

REMC1_ID1

4

1

2

3

REMC1_ID0

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

R_B_DQS8_0

4

R_B_DQS8_1

4

R_B_SD8_2

R_B_SD8_6

R_B_SD5_7

R_B_SD6_0

R_B_SD6_1

R_B_SD6_4

R_B_SD4_6

R_B_SD4_7

R_B_SD4_3

R_B_SD5_4

R_A_SD5_5

R_A_DQS5_0

4

R_A_DQS5_1

4

R_A_SD7_6

R_A_DQS7_1

4

R_A_SD5_1

R_A_SD7_1

R_A_SD7_3

R_A_SD7_7

R_A_SD7_2

R_A_DQS7_0

4

R_B_SD8_7

R_A_SD7_0

12

150-5%

12

150-5%

15

R437

21

15

VCC25

A_SD7_3

A_SD7_7

A_SD7_2

A_DQS7_0

B_SD8_7

CSTRB3

2

CSTRB2

2

VCC25

2,3

2-7,9,11,13,14,16

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

5,7,12

5,7,12

5,7,12

5,7,8

5,7,8

5,7,12

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

6,9,10

5,7,8

249 Ohm-1%

R_CSTRB3

4

R_CSTRB3

4

R_CSTRB2

4

R_CSTRB2

4

R222

VCC25

R618

12

15

COMP0_DP112

REMC1_ID1

4

REMC1_ID0

4

NC_CMD9_3_DP1

NC_CMD9_2_DP1

NC_CMD9_1_DP1

NC_CMD9_0_DP1

15

15

15

15

RCMD3

2,3,12

RCMD2

2,3,12

RCMD1

2,3,12

RCMD0

2-4,12

R_B_DQS4_1

4

R_B_DQS4_0

4

R_B_DQS5_1

4

R_B_DQS5_0

4

R_A_DQS6_1

4

R_A_DQS6_0

4

R_B_DQS6_1

4

R_B_DQS6_0

4

R_A_DQS7_1

4

R_A_DQS7_0

4

R_B_DQS7_1

4

R_B_DQS7_0

4

R_A_DQS4_1

2-7,9,11,13,14,16

4

R_A_DQS4_0

4

R_B_DQS8_1

4

R_B_DQS8_0

4

R_A_DQS5_1

4

R_A_DQS5_0

4

1K-5%

PU_ISOLATE_DP1

VCC25

2-7,9,11,13,14,16

R_MSTRB1

R_MECC7

R_MECC6

R_MECC5

R_MECC4

R_CMD63

15

R_CMD62

15

R_CMD61

15

R_CMD60

15

R_CMD59

15

R_CMD58

15

R_CMD57

15

R_CMD56

15

R_CMD55

15

R_CMD54

15

R_CMD53

15

R_CMD52

15

R_CMD51

15

R_CMD50

15

R_CMD49

15

R_CMD48

15

R_CMD47

15

R_CMD46

15

R_CMD45

15

R_CMD44

15

R_CMD43

15

R_CMD42

15

R_CMD41

15

R_CMD40

15

R_CMD39

15

R_CMD38

15

R_CMD37

15

R_CMD36

15

R_CMD35

15

R_CMD34

15

R_CMD33

15

R_CMD32

15

2,3,12

Strapping option:

RCMD0 = 0 (PLL enabled)

RCMD0

2-4,12

R_A_SD4_6

4

R_A_SD4_2

4

R_A_DQS4_1

4 4

4

R_A_DQS4_0

4

R_A_SD5_4

4

R_A_SD5_0

4

R_A_SD4_3

4

R_A_SD4_7

4

RN349

18

12 OHM-5%

RN349

27

12 OHM-5%

RN349

36

12 OHM-5%

RN349

45

12 OHM-5%

RN350

18

12 OHM-5%

RN350

27

12 OHM-5%

RN350

36

12 OHM-5%

RN350

45

12 OHM-5%

A_SD4_6

A_SD4_2

A_DQS4_1

A_DQS4_0

A_SD5_4

A_SD5_0

A_SD4_3

A_SD4_7

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

R_B_SD4_5

4

R_B_DQS4_0

4

R_B_SD4_2

4

R_B_DQS4_1

4

R_B_SD4_0

4

R_B_SD4_4

4

R_B_SD7_3

4

R454

1K-5%1K-5%

NP*

12

R452

12

12 OHM-5%

12 OHM-5%

12 OHM-5%

12 OHM-5%

12 OHM-5%

12 OHM-5%

12 OHM-5%

12 OHM 5%

3

3

3

3

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

R_B_DQS5_1

4

R_B_SD3_2

R_B_SD3_6

R_B_SD3_3

R_B_SD3_7

R_B_SD8_4

R_B_SD8_5

R_B_SD8_0

R_B_SD8_1

R_B_SD6_5

R_B_DQS6_1

4

R_B_SD6_6

R_B_DQS6_0

4

R_B_SD6_2

R_B_SD6_7

R_B_SD6_3

R_A_SD6_7

R_A_DQS6_0

4

R_A_SD6_6

R_A_DQS6_1

4

R_A_SD7_5

R_A_SD7_4

R_A_SD6_3

R_B_SD7_6

R_B_SD7_4

R_B_DQS7_0

R_B_SD7_2

R_B_SD7_7

R_B_SD7_5

R_B_SD7_0

R_B_SD7_1

R_A_SD5_7

R_A_SD6_2

R_A_SD5_6

R_A_SD5_3

R_A_SD5_2

R_A_SD6_0

R_A_SD6_5

R_A_SD6_4

R_A_SD6_1

R_B_DQS5_0

4

R_B_DQS7_1

R_B_SD5_2

R_B_SD5_6

R_B_SD5_3

R_B_SD5_0

R_B_SD5_5

R_B_SD5_1

12 OHM-5%

18

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

45

12 OHM-5%

18

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

45

12 OHM-5%

18

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

45

12 OHM-5%

18

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

18

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

45

12 OHM-5%

18

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

18

12 OHM-5%

45

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

45

12 OHM-5%

18

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

18

12 OHM-5%

45

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

45

12 OHM-5%

45

12 OHM-5%

18

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

18

12 OHM-5%

45

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

45

12 OHM-5%

18

12 OHM-5%

27

12 OHM-5%

36

12 OHM-5%

RN368

45

B_DQS5_1

RN186

RN186

RN186

RN186

RN187

RN187

RN187

RN187

RN363

RN363

RN363

RN363

RN364

RN364

RN364

RN345

RN345

RN345

RN345

RN346

RN346

RN346

RN365

RN364

RN365

RN365

RN365

RN366

RN366

RN366

RN347

RN346

RN347

RN347

RN347

RN348

RN348

RN348

RN348

RN367

RN366

RN367

RN367

RN367

RN368

RN368

RN368

B_SD3_2

B_SD3_6

B_SD3_3

B_SD3_7

B_SD8_4

B_SD8_5

B_SD8_0

B_SD8_1

B_SD6_5

B_DQS6_1

B_SD6_6

B_DQS6_0

B_SD6_2

B_SD6_7

B_SD6_3

A_SD6_7

A_DQS6_0

A_SD6_6

A_DQS6_1

A_SD7_5

A_SD7_4

A_SD6_3

B_SD7_6

B_SD7_4

B_DQS7_0

B_SD7_2

B_SD7_7

B_SD7_5

B_SD7_0

B_SD7_1

A_SD5_7

A_SD6_2

A_SD5_6

A_SD5_3

A_SD5_2

A_SD6_0

A_SD6_5

A_SD6_4

A_SD6_1

B_DQS5_0

B_DQS7_1

B_SD5_2

B_SD5_6

B_SD5_3

B_SD5_0

B_SD5_5

B_SD5_1

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

5,7,8

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

6,9,10

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

2-7,9,11,13,14,16

A B

1

2

3

B D

.01UF

12

50V-20%

SSTLREF_D1

DDR SDRAM DIMM

SUB*_726NT

SUB*_78020

C320

.01UF

12

50V-20%

J2

C321

.01UF

12

SUB*_78020

SUB*_78020

50V-20%

2

1

C329

+80%-20%

.22uF 16V

DM1_DQS10

DM2_DQS11

DM3_DQS12

DM4_DQS13

DM5_DQS14

DM6_DQS15

DM7_DQS16

DM8_DQS17

C323

1

C735

C330

2

+80%-20%

.22uF 16V

DQS0

DM0_DQS9

D10

D11

DQS1

D12

D13

D14

D15

D16

D17

D18

D19

DQS2

D20

D21

D22

D23

D24

D25

D26

D27

DQS3

D28

D29

D30

D31

D32

D33

D34

D35

DQS4

D36

D37

D38

D39

D40

D41

D42

D43

DQS5

D44

D45

D46

D47

D48

D49

D50

D51

DQS6

D52

D53

D54

D55

D56

D57

D58

D59

DQS7

D60

D61

D62

D63

ECC0

ECC1

ECC2

ECC3

DQS8

ECC4

ECC5

ECC6

ECC7

C324

.01UF

12

12

50V-20%

SUB*_78020

2

1

C736

+80%-20%

.22uF 16V

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

SUB*_78020

C325

.01UF

50V-20%

1

2

+80%-20%

.22uF 16V

2

4

6

8

5

97

94

95

98

99

12

13

19

20

14

107

105

106

109

110

23

24

28

31

25

119

114

117

121

123

33

35

39

40

36

129

126

127

131

133

53

55

57

60

56

149

146

147

150

151

61

64

68

69

67

159

153

155

161

162

72

73

79

80

78

169

165

166

170

171

83

84

87

88

86

177

174

175

178

179

44

45

49

51

47

140

134

135

142

144

.01UF

12

A_SD0_0

A_SD0_1

A_SD0_2

A_SD0_3

A_DQS0_0

A_DQS0_1

A_SD0_4

A_SD0_5

A_SD0_6

A_SD0_7

A_SD1_0

A_SD1_1

A_SD1_2

A_SD1_3

A_DQS1_0

A_DQS1_1

A_SD1_4

A_SD1_5

A_SD1_6

A_SD1_7

A_SD2_0

A_SD2_1

A_SD2_2

A_SD2_3

A_DQS2_0

A_DQS2_1

A_SD2_4

A_SD2_5

A_SD2_6

A_SD2_7

A_SD3_0

A_SD3_1

A_SD3_2

A_SD3_3

A_DQS3_0

A_DQS3_1

A_SD3_4

A_SD3_5

A_SD3_6

A_SD3_7

A_SD4_0

A_SD4_1

A_SD4_2

A_SD4_3

A_DQS4_0

A_DQS4_1

A_SD4_4

A_SD4_5

A_SD4_6

A_SD4_7

A_SD5_0

A_SD5_1

A_SD5_2

A_SD5_3

A_DQS5_0

A_DQS5_1

A_SD5_4

A_SD5_5

A_SD5_6

A_SD5_7

A_SD6_0

A_SD6_1

A_SD6_2

A_SD6_3

A_DQS6_0

A_DQS6_1

A_SD6_4

A_SD6_5

A_SD6_6

A_SD6_7

A_SD7_0

A_SD7_1

A_SD7_2

A_SD7_3

A_DQS7_0

A_DQS7_1

A_SD7_4

A_SD7_5

A_SD7_6

A_SD7_7

A_SD8_0

A_SD8_1

A_SD8_2

A_SD8_3

A_DQS8_0

A_DQS8_1

A_SD8_4

A_SD8_5

A_SD8_6

A_SD8_7

SUB*_78020

C326

.01UF

12

50V-20%

SUB*_78020

C327

12

50V-20%

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

.01UF

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,12

4,7,8

4,7,8

4,7,12

4,7,12

4,7,8

4,7,12

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

4,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

3,7,8

VCC25

C328

12

50V-20%

SUB*_78020

4,7,8

4,7,8

3,7,8

3,7,8

.01UF

50V-20%

2-7,9,11,13,14,16

2,11

2,11

VOLTAGE LEVEL CONVERSION FOR SPDs (2.5V I2C)

5-7,9,13

FAST SCL EDGE REQUIRED BY REMC rev 2.0s

VTT_SSTL

2

1

C322

+80%-20%

.22uF 16V

5-7,9,14

1

C332

12

48

43

41

130

37

32

125

29

122

27

141

118

115

59

52

157

158

154

65

63

137

138

21

111

167

1

184

82

92

91

181

182

183

90

102

101

10

9

173

163

71

76

75

17

16

113

103

168

148

120

108

85

70

46

38

7

136

180

156

112

164

143

128

104

96

172

77

62

54

30

22

15

SUB*_78020

C333

.01UF

12

50V-20%

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

BA0

BA1

CS

CS1

RAS

CAS

WE

CLK0_P

CLK0_N

CLKE0

CLKE1

FETEN

VREF

VDDSPD

VDDID

SCL

SDA

SA0

SA1

SA2

WP

NC1

NC2

RESET

NC4

NC5

CS3_NU

CS2_NU

CLK2_N_DU

CLK2_P_DU

CLK1_N_DU

CLK1_P_DU

BA2_NU

A13_NU

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD10

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

C334

.01UF

50V-20%

SUB*_78020

A_MA0

A_MA1

A_MA2

A_MA3

A_MA4

A_MA5

A_MA6

A_MA7

A_MA8

A_MA9

R0_MA10

A_MA11

A_MA12

R0_BA0_0

2,6

R0_BA1_0

2,6

A_CS_1

2,6

R0_RAS_0

2,6

R0_CAS_0

2,6

R0_WE_0

2,6

CLK_J2_P

11

CLK_J2_N

11

2,7,12

NC_FETEN_J2

SSTLREF_D1

NC_VDDID_J2

ASCLK_2P5V

ASDATA_2P5V

NC_WP_J2

NC_NC1_J2

NC_NC2_J2

A_RESET

NC_NC4_J2

NC_NC5_J2

NC_CS3_J2

NC_CS2_J2

NC_CLK2_N_J2

NC_CLK2_P_J2

NC_CLK1_N_J2

NC_CLK1_P_J2

NC_BA2_J2

NC_A13_J2

VCC25

A_CKE

STAKE PIN FOR TEST

2,6

2

2-7,9,11,13,14,16

A_CS_0

NP*

J14

1

VCC25

5-7,9,13

3-7,9,13

6,7,9,13

2-7,9,11,13,14,16

2,7,12

2,7,12

2,7,12

2,7,12

2,7,12

2,7,12

2,7,12

2,7,12

2,7,12

2,7,12

2,6

2,7,12

2,7,12

5-7,9,14

3

2-7,9,11,13,14,16

22uF 10V

1

2

4 4

VCC25

BE USED ON NEW DESIGNS.

BE USED ON NEW DESIGNS.

THIS PART IS NOT TO

C571

Substitution for p/n consolidation

THIS PART IS NOT TO

SUB*_78020

22uF 10V

C480

1

2

C331

.01UF

12

50V-20%

SUB*_78020

CA

ASCLK_3P3V

ASDATA_3P3V

ASCLK_2P5V

2,3,6,8,10,12-14

VCC25

2-7,9,11,13,14,16

Q8

2N7002

G

1

D

S

2

3

R613

12

0-5%

NP*

VCC25

2-7,9,11,13,14,16

Q9

2N7002

G

1

D

S

2

3

R614

12

0-5%

NP*

NP*

R627

12

0-5%

VCC25

2-7,9,11,13,14,16

NP*

U95

14

74HC126

32

1

R622

NP*

12

8.2K-5%

R608

12

ASCLK_2P5V

R609

12

8.2K-5% 8.2K-5%

ASDATA_2P5V

FSTEDG_ASCLK_2P5V

VCC25

2-7,9,11,13,14,16

6-15-2004_13:22

5-7,9,13

3-7,9,13

3,4

J2

1

2

3

Put one 22 uF cap at each end of DIMM

A B

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

COMPUTER

CORPORATION

TITLE

AUSTIN,TEXAS

SCHEM,MEM-CRD,6DIMM,PE4600

DWG NO.

DATE

8Y810

6/15/2004

SHEET

DC

REV.

5 OF 18

A02

B D

CA

6-15-2004_13:23

5-7,9,14

SSTLREF_D1

1

C378

2

1

C379

2

+80%-20%

.22uF 16V

2

1

C737

+80%-20%

.22uF 16V

1

C738

2

+80%-20%

.22uF 16V

.22uF 16V

+80%-20%

1

.01UF

50V-20%

J1

DDR SDRAM DIMM

SUB*_726NT

SUB*_78020

C371

.01UF

12

SUB*_78020

C372

12

50V-20%

DM0_DQS9

DM1_DQS10

DM2_DQS11

DM3_DQS12

DM4_DQS13

DM5_DQS14

DM6_DQS15

DM7_DQS16

DM8_DQS17

SUB*_78020

C373

.01UF

.01UF

12

50V-20%

SUB*_78020

D0

D1

D2

D3

DQS0

D4

D5

D6

D7

D8

D9

D10

D11

DQS1