Page 1

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

A

B

PEREGRINE - PASS 1

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

Contents:

Son of Harrier

1. TITLE

2. CHANGE LOG

C

3. PEREGRINE BLOCK DIAGRAM

4. 405GP INTERFACE TO SDRAM & PCI

5. PPC405 MISC

D

6. 405GP PWR/GND & JTAG

7. 405GP BOOTSTRAP

C

D

8. 405GP SDRAM (16MB)

9. 405GP PERIPHERAL BUS

E

10. FLASH / RTC

E

11. CLOCK OSCILLATOR & DRIVER

12. UART

13. RS485 DRIVERS

F

14. I2C SEEPROM AND SWITCHES

F

15. ETHERNET PHY

16. USB & SMP CONNECTOR

17. VIDEO COMPRESSOR

18. COMPRESSOR SDRAM 1MX16X4b

G

G

19. POWER

20. SPARE PARTS

H

H

I

J

73P9323

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

1 2 3 4 5 6 7 9 108

OUTSIDE MAX

INSIDE MAX

PART NO.

TITLE

SCALE: 1/1

0.13

2.0 APPROVED

73P9323

TITLE

DESIGNER

CHECKED

SHEET

IBM CONFIDENTIAL

PEREGRINE

9-16-2003_15:54

JAD

???

???

1

SEPTEMBER 2003

???

???

OF

I

J

20

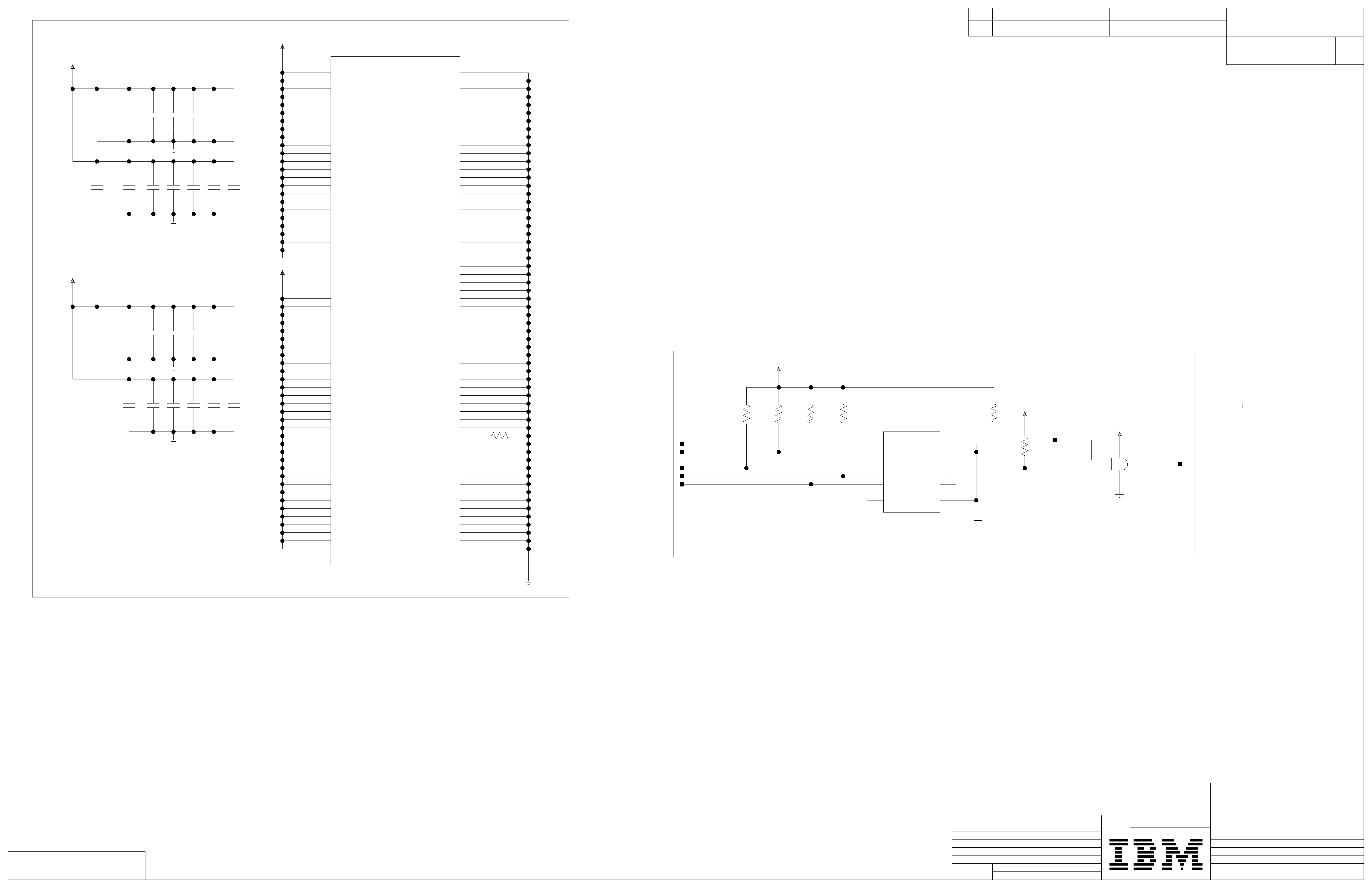

Page 2

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

A

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

Change Log:

* THIS DESIGN IS A DERIVATIVE OF THE HARRIER PASS 5D DESIGN

Therefore, this design is started with ALL the changes through Harrier Pass 5D. If you need to see

any of the changelog before this on Harrier, please refer to the Harrier Pass 5D schematics (73P9313).

B

09/16/03 - JAD - (Page 8) Added MEM_ADD11 net to U83.21

B

C

D

E

C

D

E

F

G

F

G

H

I

J

73P9323

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

1 2 3 4 5 6 7 9 108

OUTSIDE MAX

INSIDE MAX

PART NO.

CHANGE LOG

TITLE

SCALE: 1/1

0.13

2.0 APPROVED

DESIGNER

CHECKED

SHEET

IBM CONFIDENTIAL

73P9323

PEREGRINE

9-16-2003_17:24

JAD

???

???

2

SEPTEMBER 2003

???

???

OF

20

H

I

J

Page 3

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

A

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

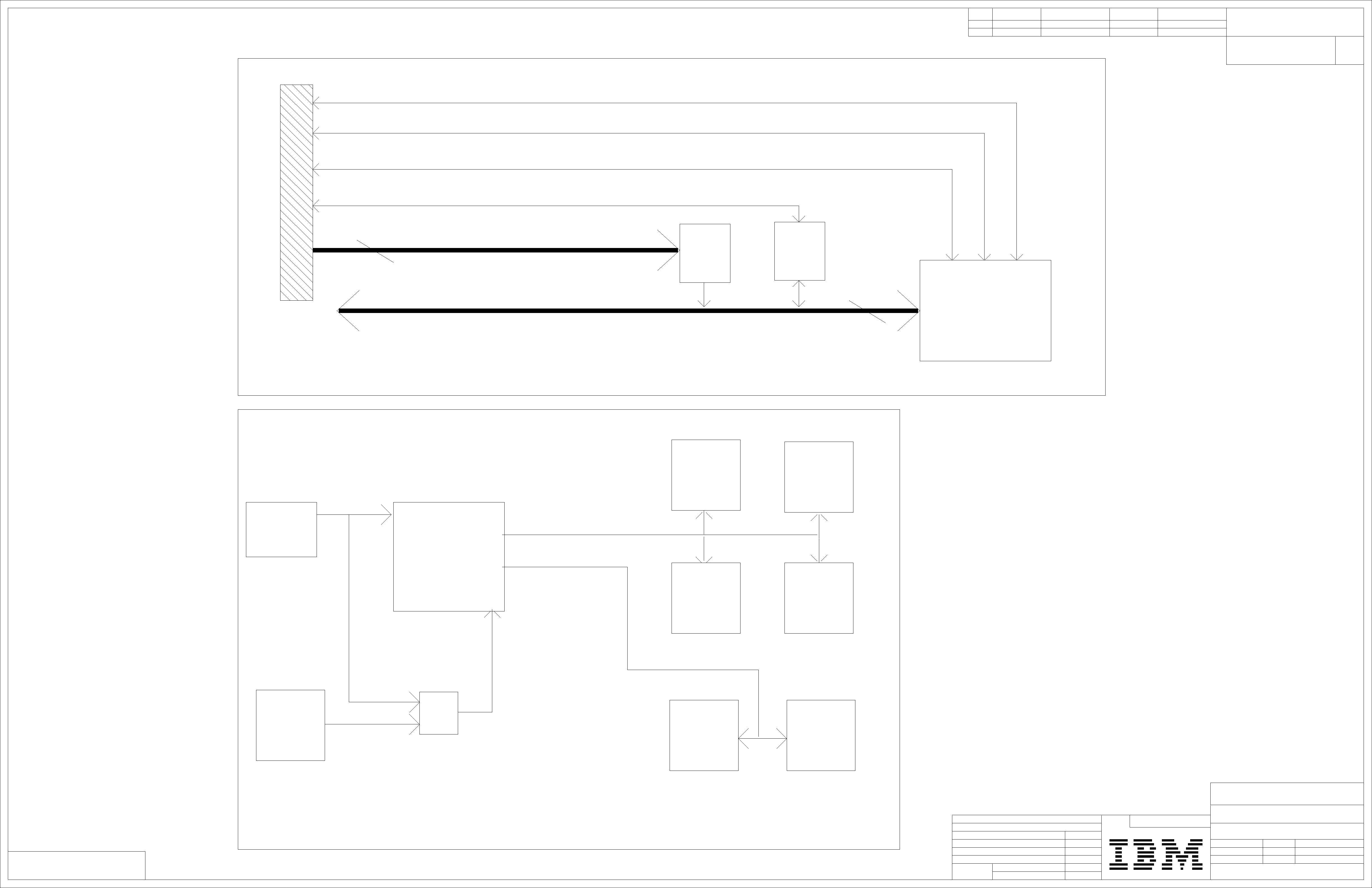

I2C/SMBus

Ethernet

B

SMP

RS485/RS232

B

USB

C

28.6 MHz

FPGA

USB

16

C

50 MHz

CPU

D

32

D

E

F

USBFPGA

E

F

PPC_RESET_N

SYSTEM

MAX6315

G

CPU

PERIPHERAL_RESET_N

PPC_NOT_READY_N

G

I2C

JTAG

DUART

HOST ID

H

TRST_N

I

JTAG

OR

JTAG_RST_N

FLASH

ETHERNET

H

I

J

73P9323

PEREGRINE BLOCK DIAGRAM

MUST CONFORM TO ENG

RESET

1 2 3 4 5 6 7 9 108

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

PART NO.

73P9323

TITLE

SCALE: 1/1

0.13

2.0 APPROVED

DESIGNER

CHECKED

SHEET

IBM CONFIDENTIAL

PEREGRINE

9-12-2003_13:07

JAD

???

???

3

SEPTEMBER 2003

???

???

OF

J

20

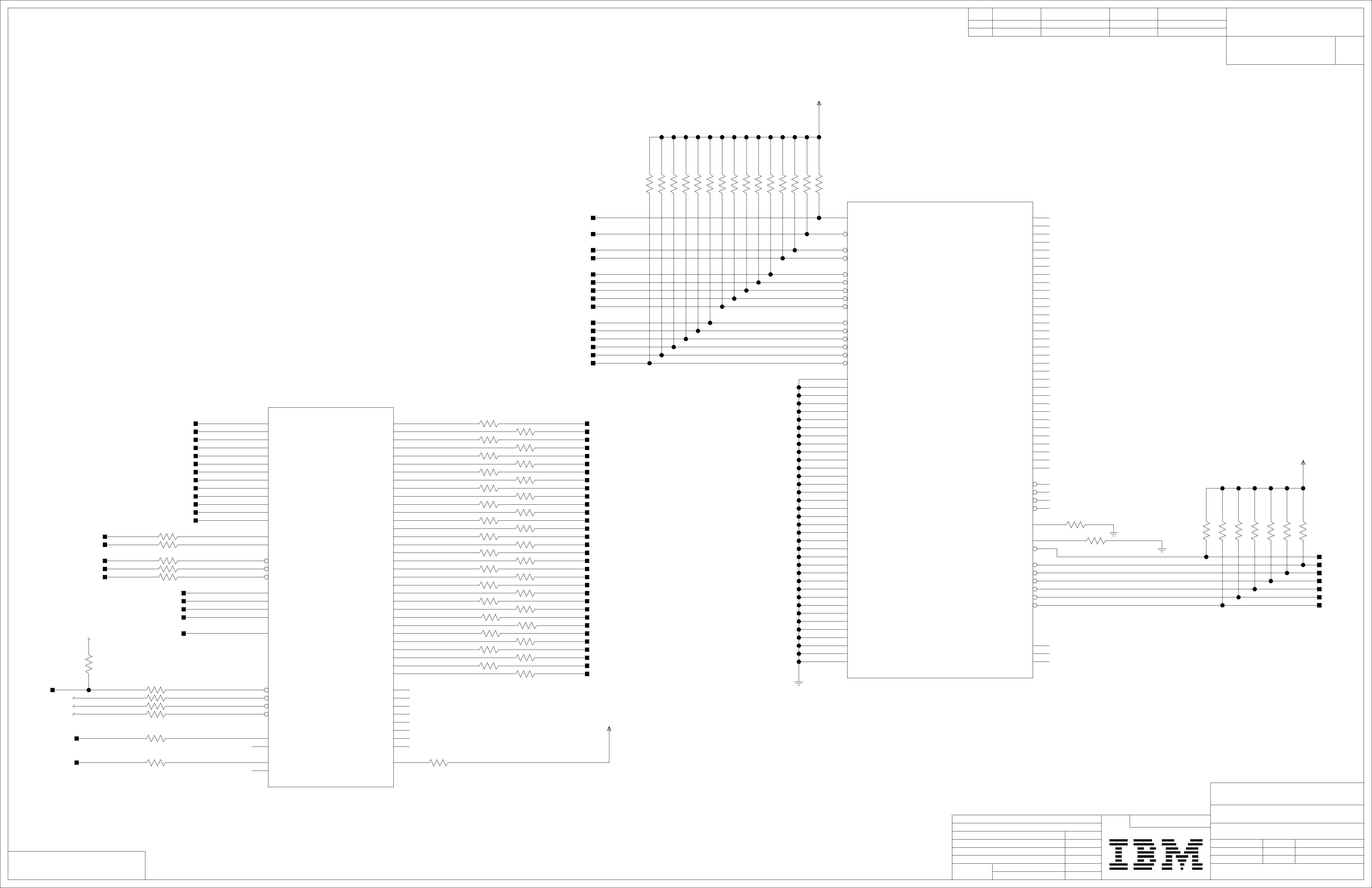

Page 4

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

A

3.3VC

B

R552

R553

R554

8.2K

R555

8.2K

R556

8.2K

R557

8.2K

R558

8.2K

R559

8.2K

R560

8.2K

R561

8.2K

R562

8.2K

R563

8.2K

R564

8.2K

R565

8.2K

R566

8.2K

8.2K

8.2K

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

U53

PCI_PAR

PCI_FRAME#

C

PCI_IRDY#

PCI_TRDY#

PCI_STOP#

PCI_DEVSEL#

PCI_SERR#

PCI_PERR#

5

Using PCI_RESET# for manufacturing test of insane LED

D

E

PPC405GP-3BE200C

8 MEM_ADD0

8

8

8

8

8

8

F

8

8

8

G

DQM Lines swapped to match Data Lines

H

R110

MEM_CS0#

8

I

8

8

8

8

3.3K

NOPOP

MEM_CS1#

MEM_CS2#

MEM_CS3#

MEM_CLKEN0

MEM_CLK0

MEM_BA0

MEM_BA1

MEM_RAS#

MEM_CAS#

MEM_WE#

Up to 4 banks possible - Only using 1

NOPOP resistors to allow for hot wiring later if needed.

NOPOP

NOPOP

NOPOP

R98

R97

R95

R91

R55

R99

R104

R105

R106

R102

R103

8

8

8

8

8

22

22

22

22

22

8

8

8

8

22

RES_MEM_BSEL0#

22

RES_MEM_BSEL1#

22

RES_MEM_BSEL2#

22

RES_MEM_BSEL3#

22

22

MEM_ADD1

MEM_ADD2

MEM_ADD3

MEM_ADD4

MEM_ADD5

MEM_ADD6

MEM_ADD7

MEM_ADD8

MEM_ADD9

MEM_ADD10

MEM_ADD11

MEM_ADD12

RES_MEM_BA0

RES_MEM_BA1

RES_MEM_RAS#

RES_MEM_CAS#

RES_MEM_WE#

MEM_DQM3

MEM_DQM2

MEM_DQM1

MEM_DQM0

MEM_DQM_CB

RES_MEM_CLKEN0

RES_MEM_CLK0

AE22

AC21

AE21

AD21

AF22

AE20

AC19

AE19

AD19

AC18

AF19

AD18

AC17

AB24

AC24

AF24

AB23

AC16

AC12

AC10

AC6

AA3

AC15

AD17

AF17

AE15

AC14

AB25

AC25

AC26

AA23

M_ADDR0

M_ADDR1

M_ADDR2

M_ADDR3

M_ADDR4

M_ADDR5

M_ADDR6

M_ADDR7

M_ADDR8

M_ADDR9

M_ADDR10

M_ADDR11

M_ADDR12

M_BA0

M_BA1

M_RAS_N

M_CAS_N

M_WE_N

M_DQM0

M_DQM1

M_DQM2

M_DQM3

M_DQM_CB

M_BANKSEL0_N

M_BANKSEL1_N

M_BANKSEL2_N

M_BANKSEL3_N

M_CLKEN0

M_CLKEN1

M_CLKOUT0

M_CLKOUT1

U53

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_ECC0

M_ECC1

M_ECC2

M_ECC3

M_ECC4

M_ECC5

M_ECC6

M_ECC7

M_CLK_IN

AC13

AE12

AD11

AC11

AF10

AE11

AD10

AF9

AD9

AE9

AD8

AF7

AC8

AD7

AE6

AE5

AE4

AD5

AD4

AC5

AD1

AB2

AA4

AA2

AB1

Y2

W4

W2

W3

V4

W1

V3

AE14

AF15

AF14

AD13

AF13

AF12

AE13

AD12

AF4

RN14

1 8

RES_MEM_DATA30 MEM_DATA30

RES_MEM_DATA29

RES_MEM_DATA28

RES_MEM_DATA27

RES_MEM_DATA26

RES_MEM_DATA25

RES_MEM_DATA24

RES_MEM_DATA23

RES_MEM_DATA22

RES_MEM_DATA20

RES_MEM_DATA18

RES_MEM_DATA16 MEM_DATA16

RES_MEM_DATA14

RES_MEM_DATA12

RES_MEM_DATA10

RES_MEM_DATA8

RES_MEM_DATA7

RES_MEM_DATA6

RES_MEM_DATA5

RES_MEM_DATA4

RES_MEM_DATA3

RES_MEM_DATA2

RES_MEM_DATA1

RES_MEM_DATA0

R365

10K

Listed as Reserved in Datasheet

RN14

3 6

RN21

1 8

RN21

3 6

RN15

1 8

RN15

3 6

RN20

1 8

RN20

3 6

RN16

1 8

RN16

3 6

RN19

1 8

RN19

3 6

RN17

1 8

RN17

3 6

RN18

1 8

RN18

3 6

22RES_MEM_DATA31

2 7

22

4 5

22

2 7

22

4 5

22

2 7

22RES_MEM_DATA21

4 5

22RES_MEM_DATA19

2 7

22RES_MEM_DATA17

4 5

22RES_MEM_DATA15

2 7

22RES_MEM_DATA13

4 5

22RES_MEM_DATA11

2 7

22RES_MEM_DATA9

4 5

22

2 7

22

4 5

22

2 7

22

4 5

RN14

RN14

RN21

RN21

RN15

RN15

RN20

RN20

RN16

RN16

RN19

RN19

RN17

RN17

RN18

RN18

MEM_DATA31

22

MEM_DATA29

22

MEM_DATA28

MEM_DATA27

22

MEM_DATA26

MEM_DATA25

22

MEM_DATA24

MEM_DATA23

22

MEM_DATA22

MEM_DATA21

22

MEM_DATA20

MEM_DATA19

22

MEM_DATA18

MEM_DATA17

22

MEM_DATA15

22

MEM_DATA14

MEM_DATA13

22

MEM_DATA12

MEM_DATA11

22

MEM_DATA10

MEM_DATA9

22

MEM_DATA8

MEM_DATA7

22

MEM_DATA6

MEM_DATA5

22

MEM_DATA4

MEM_DATA3

22

MEM_DATA2

MEM_DATA1

MEM_DATA0

22

PCI_RESET#

PCI_GNT0#

PCI_GNT1#

PCI_GNT2#

PCI_GNT3#

PCI_GNT4#

PCI_GNT5#

PCI_GNT0# when Internal Arbiter is Used

PCI_REQ# when using External Arbiter

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

3.3VC

E26

J24

J23

G26

H23

H25

G24

G25

B24

U23

T23

F23

H26

N23

M24

L11

L12

L13

L14

L15

L16

M11

M12

M13

M14

M15

M16

N11

N12

N13

N14

N15

N16

P11

P12

P13

P14

P15

P16

R11

R12

R13

R14

R15

R16

T11

T12

T13

T14

T15

T16

PCI_PAR

PCI_FRAME_N

PCI_IRDY_N

PCI_TRDY_N

PCI_STOP_N

PCI_DEVSEL_N

PCI_SERR_N

PCI_PERR_N

PCI_RESET_N

PCI_GNT0_REQ_N

PCI_GNT1_N

PCI_GNT2_N

PCI_GNT3_N

PCI_GNT4_N

PCI_GNT5_N

HS_RTN1

HS_RTN2

HS_RTN3

HS_RTN4

HS_RTN5

HS_RTN6

HS_RTN7

HS_RTN8

HS_RTN9

HS_RTN10

HS_RTN11

HS_RTN12

HS_RTN13

HS_RTN14

HS_RTN15

HS_RTN16

HS_RTN17

HS_RTN18

HS_RTN19

HS_RTN20

HS_RTN21

HS_RTN22

HS_RTN23

HS_RTN24

HS_RTN25

HS_RTN26

HS_RTN27

HS_RTN28

HS_RTN29

HS_RTN30

HS_RTN31

HS_RTN32

HS_RTN33

HS_RTN34

HS_RTN35

HS_RTN36

PPC405GP-3BE200C

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

PCI_C_BE0_N

PCI_C_BE1_N

PCI_C_BE2_N

PCI_C_BE3_N

PCI_IDSEL

PCI_CLK

P_WE_PCI_INT_N

PCI_REQ0_GNT_N

PCI_REQ1_N

PCI_REQ2_N

PCI_REQ3_N

PCI_REQ4_N

PCI_REQ5_N

SPARE_D20

SPARE_Y23

SPARE_Y26

A17

B16

C17

A18

D17

C18

B18

A20

B21

A23

D21

B22

B23

C22

C26

F25

K26

L23

M25

M23

N25

M26

N26

P24

R24

R23

P23

R25

T24

U26

T25

V26

D19

F24

K24

R26

P26

B20

C23

C19

C21

B19

A24

G23

J25

D20

Y23

Y26

R373

5.1K

PCI_REQ0#

PCI_REQ1#

PCI_REQ2#

PCI_REQ3#

PCI_REQ4#

PCI_REQ5#

From Walnut

R366

10K

P_WE#

PCI_REQ0# when Internal Arbiter is Used

PCI_GNT# when using External Arbiter

Asynch Mode Use

R94

R579

8.2K

R587

8.2K

PART NO.

R586

8.2K

R585

8.2K

3.3VC

R584

8.2K

R92

8.2K

8.2K

16,17

IBM CONFIDENTIAL

C

D

E

F

G

H

I

J

73P9323

405GP INTERFACE TO SDRAM & PCI

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

1 2 3 4 5 6 7 9 108

OUTSIDE MAX

INSIDE MAX

73P9323

TITLE

SCALE: 1/1

0.13

2.0 APPROVED

DESIGNER

CHECKED

SHEET

PEREGRINE

9-16-2003_17:24

JAD

???

???

4

SEPTEMBER 2003

???

???

OF

J

20

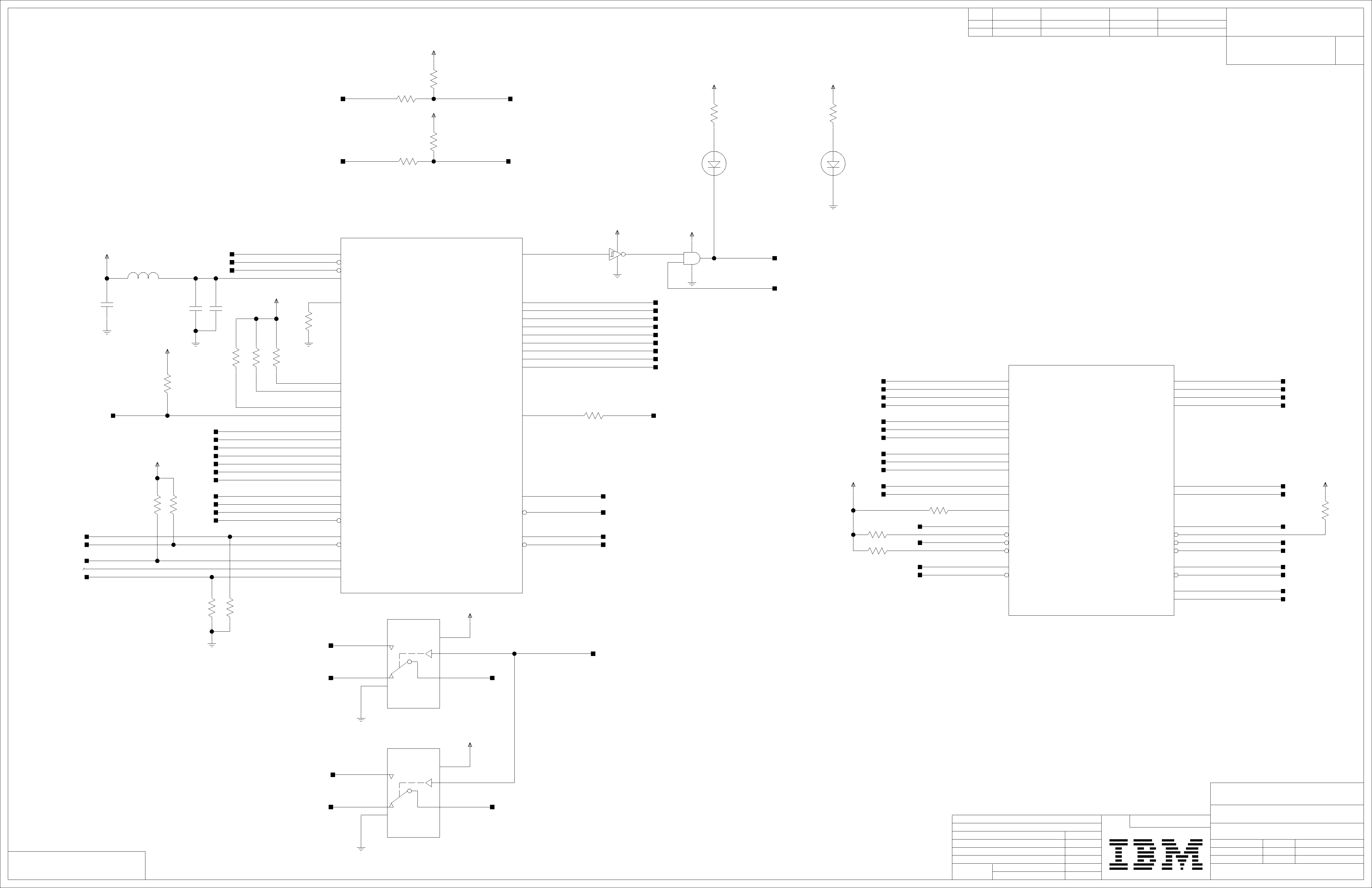

Page 5

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

3.3VC

R597

A

HOST_PWR#

5

B

5

HOST_RST#

R594

0

R551

R595

0

3.3VC

1MEG

HOST_PWR_REQ#

1MEG

HOST_PWRGD/RST#

16

Consider bi-directional buffers for next pass.

16

R610

10 mA

330

2CR2

+

VEN_P/D_NUM=597-2401-213

VENDOR=DIALIGHT

COLOR=YELLOW

1

-

R611

10 mA

3.3VC3.3VC

330

2CR3

+

VEN_P/D_NUM=597-2301-213

VENDOR=DIALIGHT

COLOR=GREEN

1

PowerInsane

-

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

3.3VC

U53

C

2_5V

C523

100N

D

E

F

G

Internal Timer Input

Not currently used.

SYS_TIMER_CLK

P_HOLD_REQ

P_EXT_REQ#

P_HOLD_PRIORITY

P_BUS_REQ

P_ERROR

Peripheral Bus Controls

NEEDED?

PULLUP to 2.5V for PLL

BLM31A700S

L43

FERRITE

3.3VC

R522

3.3VC

R90

R578

3.3K

3.3K

3.3K

C522

C534

100N

16

R87

16

5

16

16

12

11 33MHZ_405GP

6,10

10U

R520

5

6

6

6

6

R88

1K

PPC_RESET_N

RISCWATCH_HALT#

6

R518

3.3K

USB_HUB_INT

HOST_RST#

HOST_PCI_RST_N

SER_CLK

USB_LATCH_EMPTY

RS232_DETECT

RTC_DUART_INT_N

JTAG_TDI

JTAG_TMS

JTAG_TCK

JTAG_RST_N

1K

R519

3.3K

3.3VC

3.3K

R521

3.3K

A25

D22

AB26

D25

D26

C25

E23

E24

D24

AA24

Y25

Y24

W25

W24

V23

V25

AE24

AC22

AD22

AE26

V1

Y4

T2

R3

B1

SYS_CLOCK

SYS_RESET_N

SYS_HALT_N

SYS_PLL_VDDA

CE0_TEST

DI1

Symbol is wrong on these three pins

DI2

DI1 DI2 RI - All test pins - No biggie.

RI

SYS_TIMER_CLK

IRQ6

GPIO23

IRQ5

GPIO22

IRQ4

GPIO21

IRQ3

GPIO20

IRQ2

GPIO19

IRQ1

GPIO18

IRQ0

GPIO17

JTAG_TDI

JTAG_TMS

JTAG_TCK

JTAG_TRST_N

P_HOLD_REQ

P_EXT_REQ_N

P_HOLD_PRIORITY

P_BUS_REQ

P_ERROR

U88

PPC405GP-3BE200C

SYS_ERROR

JTAG_TDO

P_EXT_RESET_N

P_HOLD_ACK

P_EXT_ACK_N

3.3VC

GPIO9

GPIO8

GPIO7

GPIO6

GPIO5

GPIO4

GPIO3

GPIO2

GPIO1

P_CLK

AD25

AB3

AC7

AF5

AE8

AC9

AF18

A22

C20

D18

E4

AD23

T3

U2

Y3

ERROR_LED

FPGA = 0, RTC = 1

All GPIO's are high impedance while in reset. refer to 405gp user manual sec 23.5.1

JTAG_TDO

PPC_NOT_READY_N

Output reset to external devices.

P_HOLD_ACK

P_EXT_ACK#

Strapping Pins

PERIPHERAL_RESET_N

U75

HOST_PWR#

X_DONE

I2C_SELECT

R649

49.9

Place close to 405GP

14

7

SER_DATA

FPGA_RTC

X_INIT

X_PROG

GPIO1

6

10,15

7

7,16

ERROR_LED#

43

PERCLK

5

17

5

14

12,14,16,17

5,7,10

17

7,17

7,16

17

3.3VC

U1

14

12

13

LVC08_TSSOP14_65MM

11

7

ERROR_LED_BUF

PCI_reset is being used as a GPIO

PCI_RESET#

16

4

3.3VC

R647

R646

15

15

15

15

15

15

15

15

15

15

15

15

ENET_PHY_RXD3

ENET_PHY_RXD2

ENET_PHY_RXD1

ENET_PHY_RXD0

ENET_PHY_RX_ERR

ENET_PHY_RX_CLK

ENET_PHY_RX_DV

ENET_PHY_CRS

ENET_PHY_TX_CLK

ENET_PHY_COL

ENET_PHY_MDC

ENET_PHY_MDIO

4.7K

4.7K

12 COM1_RX

12 COM1_CTS#

13 COM2_RX

13

UART_DSR_N = UART1_DSR_N

COM2 - DSR = CTS RTS = DTR

R517

3.3K

COM1_DCD#

COM1_RI#

UART_RX = UART1_RX

SERCLK

COM2_CTS#

U53

PPC405GP-3BE200C

AD20

AC20

AF23

AE23

U24

AF20

V24

W23

E25

AA25

H24

AD26

AE17

AE16

AE18

AB4

AD15

AC1

AC3 AD2

EMC_PHY_RXD3

EMC_PHY_RXD2

EMC_PHY_RXD1

EMC_PHY_RXD0

EMC_PHY_RX_ER

EMC_PHY_RX_CLK

EMC_PHY_RX_DV

EMC_PHY_CRS

EMC_PHY_TX_CLK

EMC_PHY_COL

EMC_MDC

EMC_MDIO

UART_SERCLK

UART0_RX

UART0_DCD_N

UART0_CTS_N

UART0_RI_N

UART_RX

UART_DSR_N UART1_DTR_N

EMC_TXD3

EMC_TXD2

EMC_TXD1

EMC_TXD0

EMC_TX_ER

EMC_TX_EN

UART0_TX

UART0_DSR_N

UART0_DTR_N

UART0_RTS_N

UART1_TX

IIC_SCL

IIC_SDA

P25

L24

L25

J26

K25

K23

AF3

AE3

AF2

AD16

AC2

AD6

AE7

Strapping Pins

ENET_PHY_TX_EN

Strapping Pins

COM1_TX

COM1_DSR#

COM1_DTR#

COM1_RTS#

COM2_TX

COM2_RTS#

I2C_SCL

I2C_SDA

7,15ENET_PHY_TXD3

7,15ENET_PHY_TXD2

7,15ENET_PHY_TXD1

7,15ENET_PHY_TXD0

7,15ENET_PHY_TX_ERR

7,15

7,12

7

7,12

7,13

7,13

14

14

3.3VC

4.7K

C

D

E

F

R648

G

VCC

5

H

I

10

17

10

CLK

X_CCLK

DIO

S1ININ = 1

1

6

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

U87

S1ININ = 1

1

4

VCC

5

6

FPGA_RTC

5,7,10

FPGA = 0, RTC = 1

D

SER_CLK 5

3.3VC

H

I

IBM CONFIDENTIAL

PART NO.

J

73P9323

17

1 2 3 4 5 6 7 9 108

X_DOUT 5SER_DATA

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

D

4

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

PPC405 MISC

SCALE: 1/1

0.13

2.0 APPROVED

73P9323

TITLE

DESIGNER

CHECKED

SHEET

PEREGRINE

9-16-2003_17:24

JAD

???

???

5

SEPTEMBER 2003

???

???

OF

J

20

Page 6

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

? ?

73P9323

405GP POWER

2_5V

U53

2_5V

A

B

C

3.3VC

D

E

F

Place one set of THREE (100nF, 10nF, 2.2nF)

per side within 25mils of 405GP

Place 10uF within 100mils of 405GP

C7

10U

C8

10U

Place one set of THREE (100nF, 10nF, 2.2nF)

per side within 25mils of 405GP

Place 10uF within 100mils of 405GP

C9

10U

C59

C61

C66

C69

100N

100N

100N

100N

C60

C62

C65

C68

C328

100N

C330

100N

C332

100N

C334

100N

C329

10N

C331

10N

C333

10N

C335

10N

10N

C494

10N

10N

C496

10N

C63

C64

C72

2.2N

C495

2.2N

C67

2.2N

C497

2.2N

2.2N

2.2N

2.2N

2.2N

3.3VC

AB10

AB11

AB12

AB15

AB16

AB17

E10

E11

E12

E15

E16

E17

K22

K5

L22

L5

M22

M5

R22

R5

T22

T5

U22

U5

AA5

F5

G5

H5

W5

Y5

AB19

AB20

AB21

AB6

AB7

AB8

AA22

F22

G22

H22

W22

Y22

E19

E20

E21

E6

E7

E8

K2

P3

AE10

AD14

U25

N24

B17

C13

P2_5V_AB10

P2_5V_AB11

P2_5V_AB12

P2_5V_AB15

P2_5V_AB16

P2_5V_AB17

P2_5V_E10

P2_5V_E11

P2_5V_E12

P2_5V_E15

P2_5V_E16

P2_5V_E17

P2_5V_K22

P2_5V_K5

P2_5V_L22

P2_5V_L5

P2_5V_M22

P2_5V_M5

P2_5V_R22

P2_5V_R5

P2_5V_T22

P2_5V_T5

P2_5V_U22

P2_5V_U5

P3_3V_AA5

P3_3V_F5

P3_3V_G5

P3_3V_H5

P3_3V_W5

P3_3V_Y5

P3_3V_AB19

P3_3V_AB20

P3_3V_AB21

P3_3V_AB6

P3_3V_AB7

P3_3V_AB8

P3_3V_AA22

P3_3V_F22

P3_3V_G22

P3_3V_H22

P3_3V_W22

P3_3V_Y22

P3_3V_E19

P3_3V_E20

P3_3V_E21

P3_3V_E6

P3_3V_E7

P3_3V_E8

P3_3V_K2

P3_3V_P3

P3_3V_AE10

P3_3V_AD14

P3_3V_U25

P3_3V_N24

P3_3V_B17

P3_3V_C13

PPC405GP-3BE200C

GND_A1

GND_AE1

GND_AF1

GND_A2

GND_B2

GND_AE2

GND_C3

GND_AD3

GND_D4

GND_A11

GND_A16

GND_A21

GND_AC4

GND_E5

GND_A6

GND_J5

GND_AA1

GND_P5

GND_AA26

GND_V5

GND_AB14

GND_AB5

GND_AB18

GND_AB22

GND_AF11

GND_E9

GND_AB9

GND_AF16

GND_AF21

GND_E13

GND_AB13

GND_AF25

GND_AF6

GND_E14

GND_E18

GND_E22

GND_F1

GND_F26

GND_L1

GND_L26

GND_N22

GND_N5

GND_T1

GND_T26

GND_J22

GND_H1

GND_P22

GND_AF8

GND_V22

GND_W26

GND_D23

GND_A19

GND_AC23

GND_C24

GND_AD24

GND_B25

GND_AE25

GND_AF26

GND_A26

GND_B26

A1

AE1

AF1

A2

B2

AE2

C3

AD3

D4

A11

A16

A21

AC4

E5

A6

J5

AA1

P5

AA26

V5

AB14

AB5

AB18

AB22

AF11

E9

AB9

AF16

AF21

E13

AB13

AF25

AF6

E14

E18

E22

F1

F26

L1

L26

N22

N5

T1

T26

J22

H1

P22

AF8

V22

W26

D23

A19

AC23

C24

AD24

B25

AE25

AF26

A26

B26

3.3VC

R583

10K

0

R628

JTAG_TDO

5

JTAG_TDI

5

JTAG_TCK

5

JTAG_TMS

5

RISCWATCH_HALT#

5

R582

10K

R581

10K

R580

10K

NC

NC

NC

1

9

13

NOPOP

J5

C1

C9

C13

CONN2x8HDR_KEY

42F6867

79282-516

C10

C12C11

KEY

C16C15

C2

C4C3

C6C5

C8C7

2

43

65

87

10

1211

1615

NC

NC

R226

1K

R117

10K

3.3VC

PPC_RESET_N

5,10

DEBUG PORT405 RISCWatch and JTAG

TRST_N

3.3VC

U1

14

1

2

LVC08_TSSOP14_65MM

3

7

JTAG_RST_N

5

DEVELOPMENT NO.

Q/M

A

B

C

D

E

F

G

H

I

G

H

I

J

73P9323

405GP PWR/GND & JTAG

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

1 2 3 4 5 6 7 9 108

OUTSIDE MAX

INSIDE MAX

PART NO.

73P9323

TITLE

SCALE: 1/1

0.13

2.0 APPROVED

DESIGNER

CHECKED

SHEET

IBM CONFIDENTIAL

PEREGRINE

9-16-2003_17:24

JAD

???

???

6

SEPTEMBER 2003

???

???

OF

J

20

Page 7

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

A

3.3VC 3.3VC 3.3VC3.3VC3.3VC 3.3VC 3.3VC 3.3VC 3.3VC

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

405GP BOOTSTRAP #1

R64

B

C

PLL Tuning TX DTR RTS

Choice 3 (6 <= M <=7) 0 1 0

Choice 5 (7 < M <=12) 1 0 0

Choice 6 (12 < M <= 32) 1 0 1

PLL Forward Divide Ack0 Ack1

Bypass 0 0

DIV 3 0 1

DIV 4 1 0

DIV 6 1 1

PLL Feedback Divide Ack2 Ack3

DIV 1 0 0

DIV 2 0 1

DIV 3 1 0

DIV 4 1 1

5,12

5

5,12

9

9

9

9

COM1_TX

COM1_DTR#

COM1_RTS#

P_DMA_ACK0

P_DMA_ACK1

P_DMA_ACK2

P_DMA_ACK3

R65

3.3K

POP

R66

3.3K

NOPOP

3.3K

POP

R71

R67

3.3K

NOPOP

3.3K

POP

R68

3.3K

POP

R72

3.3K

NOPOP

R73

R69

3.3K

NOPOP

3.3K

POP

NOPOP

POP

NOPOP

POP

NOPOP

NOPOP

POP

R40

R48

R41

R47

R42

R43

R46

1K

1K

1K

1K

1K

1K

1K

Strap: 1

Strap: 0

Strap: 1

Strap: 0

Strap: 1

Strap: 1

Strap: 0

From Users Guide - Section 7

33 MHz Reference Clock

FWD Divide = 3

PLB Divider from CPU = 2

PLL Feedback Divide = 3

____

M = 18

VCO Stable (MHz) = 600

CPU Speed (MHz) = 200

PLB Speed (MHz) = 100

OPB Speed (MHz) = 50

EPB Speed (MHz) = 50

B

C

PLB Divider from CPU TxD3 TxD2

DIV 1 0 0

D

E

DIV 2 0 1

DIV 4 1 1

5,15

5,15

ENET_PHY_TXD3

POP

ENET_PHY_TXD2

NOPOP

R45

3.3VC

Strap: 0

Strap: 1

D

E

R44

3.3VC3.3VC3.3VC3.3VC3.3VC3.3VC3.3VC 3.3VC3.3VC3.3VC

1K

1K

405GP BOOTSTRAP #2

R85

3.3K

POP

R70

3.3K

POP

POP

NOPOP

NOPOP

NOPOP

R49

R50

R51

R53

1K

1K

1K

1K

Strap: 0

Strap: 1

Strap: 1

Strap: 0

F

3.3K

POP

R80

R86

3.3K

POP

R76

OPB Divider from PLB TxD1 TxD0

DIV 1 0 0

F

DIV 2 0 1

DIV 3 1 0

DIV 4 1 1

PCI Divide from PLB GPIO1 X_PROG

DIV 1 0 0

DIV 2 0 1

DIV 3 1 0

DIV 4 1 1

5,15

5,15

5,16

5,17

ENET_PHY_TXD1

ENET_PHY_TXD0

GPIO1

X_PROG

R74

3.3K

NOPOP

3.3K

POP

R75

R81

3.3K

NOPOP

3.3K

NOPOP

R82

R83

3.3K

NOPOP

3.3K

NOPOP

R84

3.3K

NOPOP

External Bus Divider from PLB TxErr TxEn

G

H

DIV 2 0 0

DIV 3 0 1

DIV 4 1 0

DIV 5 1 1

ROM Width TX DTR#

DIV 8 0 0

DIV 16 0 1

DIV 32 1 0

Reserved 1 1

ROM Location P_HOLD_ACK

Peripheral 0

PCI 1

PCI Synchronous Mode P_EXT_ACK#

Synch 0

Asynch 1

5,15

5,15

5,13

5,13

5

5,16

ENET_PHY_TX_ERR

POP

ENET_PHY_TX_EN

POP

COM2_TX

POP

COM2_RTS#

POP

P_HOLD_ACK

POP

P_EXT_ACK#

NOPOP

R61

R54

R56

R57

R58

R59

1K

1K

1K

1K

1K

1K

Strap: 0

G

Strap: 0

Strap: 0

Strap: 0

H

Strap: 0

Strap: 0

I

J

73P9323

PCI Arbititer Enable FPGA_RTC

Internal Disable 0

Internal Enable 1

1 2 3 4 5 6 7 9 108

5,10

FPGA_RTC

NOPOP

R60

1K

Strap: 1

405GP BOOTSTRAP

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

PART NO.

73P9323

TITLE

SCALE: 1/1

0.13

2.0 APPROVED

DESIGNER

CHECKED

SHEET

IBM CONFIDENTIAL

PEREGRINE

9-16-2003_17:24

JAD

???

???

7

SEPTEMBER 2003

???

???

OF

I

J

20

Page 8

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

09/16/03 - JAD - Added MEM_ADD11 net to U83.21

SDRAM Addresssing Mode = 2 (page 15-7 in User's Guide)

12 Bit Row Address

A

B

9 Bit Column Address

2 Bit Bank Selection

Page Size = 2kb

12 bit addressing mode.

3.3VC

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

U83

1

15

29

43

C

MEM_ADD04

D

E

4

4

4

4

4

4

4

4

4

4

4

4

MEM_ADD1

MEM_ADD2

MEM_ADD3

MEM_ADD4

MEM_ADD5

MEM_ADD6

MEM_ADD7

MEM_ADD8

MEM_ADD9

MEM_ADD10

MEM_BA0

MEM_BA1

MEM_DQM04

MEM_DQM14

MEM_DQM24

MEM_DQM34

3

9

35

41

49

55

75

81

25

26

27

60

61

62

63

64

65

66

24

22

23

16

71

28

59

SDRAM2MX32

VCC0

VCC1

VCC2

VCC3

VCCQ1

VCCQ2

VCCQ3

VCCQ4

VCCQ5

VCCQ6

VCCQ7

VCCQ8

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

BA0

BA1

DQM0

DQM1

DQM2

DQM3

8nS

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

2

4

5

7

8

10

11

13

74

76

77

79

80

82

83

85

31

33

34

36

37

39

40

42

45

47

48

50

51

53

54

56

MEM_DATA0

MEM_DATA1

MEM_DATA2

MEM_DATA3

MEM_DATA4

MEM_DATA5

MEM_DATA6

MEM_DATA7

MEM_DATA8

MEM_DATA9

MEM_DATA10

MEM_DATA11

MEM_DATA12

MEM_DATA13

MEM_DATA14

MEM_DATA15

MEM_DATA16

MEM_DATA17

MEM_DATA18

MEM_DATA19

MEM_DATA20

MEM_DATA21

MEM_DATA22

MEM_DATA23

MEM_DATA24

MEM_DATA25

MEM_DATA26

MEM_DATA27

MEM_DATA28

MEM_DATA29

MEM_DATA30

MEM_DATA31

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

C

D

E

4

F

G

4

4

4

4

4

MEM_RAS#

MEM_CS0#

MEM_CAS#

MEM_WE#

MEM_CLK0

MEM_CLKEN0

3.3VC

19

RAS_N

20

CS_N

18

CAS_N

17

WE_N

68

CLK

67

CKE

44

GND1

58

GND2

72

GND3

86

GND4

P/D_NUM=???????

VENDOR=SAMSUNG

VEN_P/D_NUM=??????????

A11/

GNDQ1

GNDQ2

GNDQ3

GNDQ4

GNDQ5

GNDQ6

GNDQ7

GNDQ8

NC

21

6

12

32

38

46

52

78

84

MEM_ADD11

4

F

G

H

I

J

73P9323

3.3VC

C341

Place one set of THREE (100nF, 10nF, 2.2nF)

per side within 25mils of module

C340

10N

C75

10N

C76

100N

C502

100N

C503

2.2N

2.2N

C11

place within 50 mils

10U

405GP SDRAM (16MB)

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

1 2 3 4 5 6 7 9 108

OUTSIDE MAX

INSIDE MAX

PART NO.

73P9323

TITLE

SCALE: 1/1

0.13

2.0 APPROVED

DESIGNER

CHECKED

SHEET

IBM CONFIDENTIAL

PEREGRINE

9-16-2003_17:24

JAD

???

???

8

SEPTEMBER 2003

???

???

OF

H

I

J

20

Page 9

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

A

B

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

ROM_DATA[0:31]

10,12,16,17

ROM_DATA0

ROM_DATA1

ROM_DATA2

C

D

3.3VC

E

F

17

17

17

17

P_WBE0#

P_WBE1#

P_WBE2#

P_WBE3#

R572

R577

3.3K

R576

3.3K

R575

R574

3.3K

R573

3.3K

3.3K

3.3K

ROM_DATA3

ROM_DATA4

ROM_DATA5

ROM_DATA6

ROM_DATA7

ROM_DATA8

ROM_DATA9

ROM_DATA10

ROM_DATA11

ROM_DATA12

ROM_DATA13

ROM_DATA14

ROM_DATA15

ROM_DATA16

ROM_DATA17

ROM_DATA18

ROM_DATA19

ROM_DATA20

ROM_DATA21

ROM_DATA22

ROM_DATA23

ROM_DATA24

ROM_DATA25

ROM_DATA26

ROM_DATA27

ROM_DATA28

ROM_DATA29

ROM_DATA30

ROM_DATA31

U4

U3

U1

T4

R2

P4

R4

P2

R1

P1

N3

N1

M1

N2

M3

M4

N4

M2

L3

L4

K1

L2

K3

J1

K4

J3

J2

J4

H3

G1

H2

H4

D2

E2

F4

D1

P_DATA0

P_DATA1

P_DATA2

P_DATA3

P_DATA4

P_DATA5

P_DATA6

P_DATA7

P_DATA8

P_DATA9

P_DATA10

P_DATA11

P_DATA12

P_DATA13

P_DATA14

P_DATA15

P_DATA16

P_DATA17

P_DATA18

P_DATA19

P_DATA20

P_DATA21

P_DATA22

P_DATA23

P_DATA24

P_DATA25

P_DATA26

P_DATA27

P_DATA28

P_DATA29

P_DATA30

P_DATA31

P_WBE0_N

P_WBE1_N

P_WBE2_N

P_WBE3_N

PPC405GP-3BE200C

U53

P_ADDR0

P_ADDR1

P_ADDR2

P_ADDR3

P_ADDR4

P_ADDR5

P_ADDR6

P_ADDR7

P_ADDR8

P_ADDR9

P_ADDR10

P_ADDR11

P_ADDR12

P_ADDR13

P_ADDR14

P_ADDR15

P_ADDR16

P_ADDR17

P_ADDR18

P_ADDR19

P_ADDR20

P_ADDR21

P_ADDR22

P_ADDR23

P_ADDR24

P_ADDR25

P_ADDR26

P_ADDR27

P_ADDR28

P_ADDR29

P_ADDR30

P_ADDR31

P_PAR0

P_PAR1

P_PAR2

P_PAR3

D5

A3

B4

B5

D6

B6

C6

D7

A5

B7

C7

D8

B8

C8

D9

A8

C9

D10

C10

A10

D11

B12

D13

D12

B13

A12

A13

C14

A14

A15

C15

D15

D3

G4

G3

E1

ROM_ADDR0

ROM_ADDR1

ROM_ADDR2

ROM_ADDR3

ROM_ADDR4

ROM_ADDR5

ROM_ADDR6

ROM_ADDR7

ROM_ADDR8

ROM_ADDR9

ROM_ADDR10

ROM_ADDR11

ROM_ADDR12

ROM_ADDR13

ROM_ADDR14

ROM_ADDR15

ROM_ADDR16

ROM_ADDR17

ROM_ADDR18

ROM_ADDR19

ROM_ADDR20

ROM_ADDR21

ROM_ADDR22

ROM_ADDR23

ROM_ADDR24

ROM_ADDR25

ROM_ADDR26

ROM_ADDR27

ROM_ADDR28

ROM_ADDR29

ROM_ADDR30

ROM_ADDR31

Parity Pins - Not Used

AD31

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

P_PAR0

P_PAR1

P_PAR2

P_PAR3

ROM_ADDR[0:31]

3.3VC

R621

3.3VC

R571

3.3K

10,12,16,17

3.3VC

3.3VC

R62

R77

3.3K

3.3K

R2

3.3K

R16

3.3K

3.3VC3.3VC 3.3VC

R22

10K

3.3VC3.3VC

R5

3.3K

R9

3.3K

C

D

E

F

3.3K

10,12,16,17

10,17

G

H

P_R_W#

P_READY

P_BLAST#

P_DMAREQ0

P_DMAREQ1

P_DMAREQ2

P_DMAREQ3

R71KR201KR21

R6

1K

DMA Channels - Not Used

1K

C1

E3

F2

C16

D14

C11

A7

P_R_W_N

P_READY

P_BLAST_N

P_DMAREQ0

P_DMAREQ1

P_DMAREQ2

P_DMAREQ3

P_CS0_N

P_CS1_N

P_CS2_N

P_CS3_N

P_CS4_N

P_CS5_N

P_CS6_N

P_CS7_N

P_OE_N

P_DMA_ACK0

P_DMA_ACK1

P_DMA_ACK2

P_DMA_ACK3

P_DMA_EOT_TC0

P_DMA_EOT_TC1

P_DMA_EOT_TC2

P_DMA_EOT_TC3

B3

C4

C5

A4

B9

B10

A9

B11

C2

D16

B15

B14

C12

F3

G2

V2

Y1

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

SMI#

I2C_INT#

CABLE_DET#

DMA Acks are strapping

DMA Channels - Not Used

NOPOP

NOPOP

P_OE#

P_DMA_ACK0

P_DMA_ACK1

P_DMA_ACK2

P_DMA_ACK3

P_DMA_EOT_TC0

P_DMA_EOT_TC1

P_DMA_EOT_TC2

P_DMA_EOT_TC3

0

0

10,16,17

7

7

7

7

R542

R603

R543

0

8 bit

P_CS0#

8 bit

P_CS1#

RS232_SELECT

32 bit

P_CS3#

HOST_SMI#

HOST_I2C_INT#

CABLE_DETECT# 16

GPIO16 16

10

12,16

13,16

17

16

16

Bank 0 = Boot ROM

Bank 1 = USB / DUART

Bank 3 = Video Compressor

G

H

I

J

73P9323

R568

R567

1K

R569

1K

R570

1K

1K

405GP PERIPHERAL BUS

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

1 2 3 4 5 6 7 9 108

OUTSIDE MAX

INSIDE MAX

PART NO.

73P9323

TITLE

SCALE: 1/1

0.13

2.0 APPROVED

DESIGNER

CHECKED

SHEET

IBM CONFIDENTIAL

PEREGRINE

9-16-2003_17:24

JAD

???

???

9

SEPTEMBER 2003

???

???

OF

I

J

20

Page 10

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

3.3VC

3.3VC

A

R618

3.3K

SW1

2

1

MH2

MH3

B

MH1

POP

MAX6315US29D3-T

3

M_R_N

1 2

GND RESET_N

Vth=2.93

P/D_NUM=29L2394

U90

VCC

140 mS

4

R619

3.3K

POP

PPC_RESET_N

5,6

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

3V_BAT

C

R596

Place caps within 25mils of module near power pin

2K

3.3VC

3.3VC

R598

V1=3.0V

V2=3.3v

R599

100K

3.3VC

U27

D

9,12,16,17

E

3.3VC

F

5,15

PPC_NOT_READY_N

R122

4.7K

R458

4.7K

ROM_ADDR[0:31]

ROM_ADDR31

ROM_ADDR30

ROM_ADDR29

ROM_ADDR28

ROM_ADDR27

ROM_ADDR26

ROM_ADDR25

ROM_ADDR24

ROM_ADDR23

ROM_ADDR22

ROM_ADDR21

ROM_ADDR20

ROM_ADDR19

ROM_ADDR18

ROM_ADDR17

ROM_ADDR16

ROM_ADDR15

ROM_ADDR14

ROM_ADDR13

ROM_ADDR12

ROM_ADDR11

ROM_ADDR10

FLASHWP_N

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

45

DQ15_A1

25

A0

24

A1

23

A2

22

A3

21

A4

20

A5

19

A6

18

A7

8

A8

7

A9

6

A10

5

A11

4

A12

3

A13

2

A14

1

A15

48

A16

17

A17

16

A18

9

A19

10

A20

13

NC

12

RESET_N

14

WP_N

FEPROM4MX8

(BYTE MODE data)

(A0)

(A1)

(A2)

(A3)

(A4)

(A5)

(A6)

(A7)

(A8)

(A9)

(A10)

(A11)

(A12)

(A13)

(A14)

(A15)

(A16)

(A17)

(A18)

(A19)

(A20)

(A21)

(UNDEFINED)

VCC

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

BYTE_N

RY_BY_N

37

29

31

33

35

38

40

42

44

30

32

34

36

39

41

43

15

47

ROM_DATA7

ROM_DATA6

ROM_DATA5

ROM_DATA4

ROM_DATA3

ROM_DATA2

ROM_DATA1

ROM_DATA0

P_READY

ROM_DATA[0:31]

8 bit Data Bus - Per Shane's Request

9,17

C93

C349

100N

R52

100

C507

10N

2.2N

9,12,16,17

12

5,7

R623

2K

AIRQ_INT_N

RTC_INT_N

FPGA_RTC

CLK

5

5

DIO

The forward bias voltage of these diodes is less than 200mV.

There shouldn't be any curent drain from the battery when the system is powered since diode 13 is reverse bias.

1K

V13= -100mV

CR1

1

2

DIO_BAT54C

V23=200mV

C551

100K

R602

3

100N

100K

V3=3.1V

V

30

C552

PWR_RTC

100N

Place caps as close as possible

U89R622

1

VDD2

2

VEX

10

VDD

4

AIRQ_N

5

TIRQ_N

6

CE

7

CLK

8

DI

9

DO

VENDOR=EPSON

VEN_P/D_NUM=RTC-9701JEB-0

RTC-9701JE

VSOJ20

GND_13

GND_12

FOUT

FOE

13

12

3

11

0.8uA @ 3V Typ. (6.85 Years with 48mAh battery)

C

D

E

F

P_CS0#

9,16,17

9

C493

P_OE#

P_R_W#

3.3VC

Place within 100 mils of flash

10U

R232

G

Pin 14 hi = 16K boot block not protected

Pin 14 Low = 16K boot block protected

User Guide - Section 16.6.2 - Boot ROM must be attached to Bank 0.

H

1K

9,12,16,17

NOPOP

26

CE_N

28

OE_N

11

WE_N

VENDOR=ST_MICRO

VEN_P/D_NUM=M29W320DB70N6

GND0

GND1

FLASH

46

27

G

SOCKET_P/N=0782822

SOCKET_DESC=MERITEC-980020-48-02

SOCKET_QTY=0

P/D_NUM=73P9309

CODED_P/N=73P9310

H

I

J

73P9323

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

1 2 3 4 5 6 7 9 108

OUTSIDE MAX

INSIDE MAX

PART NO.

FLASH / RTC

SCALE: 1/1

0.13

2.0 APPROVED

73P9323

TITLE

DESIGNER

CHECKED

SHEET

IBM CONFIDENTIAL

PEREGRINE

9-16-2003_17:24

JAD

???

???

10

SEPTEMBER 2003

???

???

OF

I

J

20

Page 11

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

A

B

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

C

3.3VC

L1

D

BLM21P300S

C3

0.1U

E

C4

0.1U

R36

R32 10K

R23 10K

PWR3_3VC_CY2292

11

11

10K

10KR35

25MHZ_XTALIN

25MHZ_XTALOUT

RES_2292_OE

RES_CY2292_S0

RES_CY2292_S1

RES_CY2292_S2

U7

2

VCC2

14

VCC14

4

XTALIN

5

XTALOUT

16

SHUTDOWN_N_OE

12

S0

13

S1

15

S2_SUSPEND_N

XBUF

CPUCLK

CLKA

CLKB

CLKC

CLKD

GND3

GND11

6

8

10

9

1

7

3

11

RES_CLK25M

RES_CLK33M

RES_CLK12M

RES_CLK23.5M

C558

C21

C14

C19

R38

R37 40.2

R39 40.2

R637 40.2

40.2

NOPOP

CLK_25MHZ_BCM

33MHZ_405GP

USB_12MHZ

DUART_XTAL1

405GP CLOCK = 33.1776MHz

15

5

16

12

(1.8432MHz*2*9)

DUART_XTAL1 = 23.5 MHz

C

D

E

CY2292

P/D_NUM=77P0247

CY2292ASL-019

15P

15P

NOPOP

15P

NOPOP

15P

NOPOP

NOPOP

3.3VC

F

R4

11

G

25MHZ_XTALIN

100K

NOPOP

Y1

1 4

R63

150

NOPOP

25MHZ_XTALOUT

11

F

G

Keep crystal circuit close to CY2292

25M

Hz

EPSON

MA-306_25.0000M-C

C6

C10

33P

NOPOP

H

I

33P

NOPOP

H

I

IBM CONFIDENTIAL

PART NO.

J

73P9323

CLOCK OSCILLATOR & DRIVER

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

1 2 3 4 5 6 7 9 108

OUTSIDE MAX

INSIDE MAX

73P9323

TITLE

SCALE: 1/1

0.13

2.0 APPROVED

DESIGNER

CHECKED

SHEET

PEREGRINE

9-16-2003_17:24

JAD

???

???

11

SEPTEMBER 2003

???

???

OF

J

20

Page 12

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

3.3VC

A

R630

2K

R631

POP

11,12

B

DUART_XTAL1

1MEG

Y2

1 2

14.7456M Hz

VEN_P/D_NUM=CS1014.7456MABJTR

VENDOR=CITIZEN

NOPOP

DUART_XTAL2

12

Make DUART_XTAL* nodes as short as possible!!!

Keep crystal circuit close to DUART

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

C556

33P

C

D

E

C557

9,10,12,16,17

33P

ROM_ADDR[0:31]

ROM_ADDR12 = 0, selects duart

= 1, selects USB

9,16

9,10,12,16,17

ROM_ADDR12

P_CS1#

9,10,16,17

U79

12

13

3.3VC

14

7

ROM_ADDR[0:31]

ROM_DATA[0:31]

11

9,10,16,17

12

3.3VC

ROM_ADDR31

ROM_ADDR30

ROM_ADDR29

ROM_ADDR28

ROM_DATA7

ROM_DATA6

ROM_DATA5

ROM_DATA4

ROM_DATA3

ROM_DATA2

ROM_DATA1

ROM_DATA0

DUART_CS#

P_R_W#

DUART_INT_N

U99

42

19

28

27

26

11

44

45

46

47

48

1

2

3

10

15

30

VCC_42

VCC_19

A0

A1

A2

A3

D0

D1

D2

D3

D4

D5

D6

D7

CS#

R/W#

IRQ#

COM4

DUART

TXA

RXA

RTSA#

CTSA#

DTRA#

DSRA#

CDA#

RIA#

OP2A#

7

5

33

38

34

39

40

41

32

COM4_TX

COM4_RX

COM4_RTS#

COM4_CTS#

COM4_DTR#

COM4_DSR#

COM4_CD#

COM4_RI#

16

16

16

16

16

16

16

3.3VC

4.7K

C

R640

D

E

3.3VC

3.3VC3.3VC

F

RTC_DUART_INT_N

5

LVC08_TSSOP14_65MM

G

3.3VC

14

8

U1

9

10

7

R632

3.3K

DUART_INT_N

RTC_INT_N

12

10

5,14,16,17

POP

4.7K

NOPOP

4.7K

POP

R633

4.7K

NOPOP

R634

4.7K

PERIPHERAL_RESET_N

11,12

R635

R636

12

DUART_XTAL1

DUART_XTAL2

R644

0

R645

0

43

TXRDYA#

31

RXRDYA#

6

TXRDYB#

18

RXRDYB#

13

XTAL1

14

XTAL2

12

PWRSAVE

25

CLKSEL

37

HDCNTL#

36

RESET#

24

16/68#

17

GND

VENDOR=EXAR

VEN_P/D_NUM=XR16L2751CM

COM5

TXB

RXB

RTSB#

CTSB#

DTRB#

DSRB#

CDB#

RIB#

OP2B#

8

4

22

23

35

20

16

21

9

COM5_TX

COM5_RX

COM5_RTS#

COM5_CTS#

COM5_DTR#

COM5_DSR#

COM5_CD#

COM5_RI#

13

13

13

13

16

16

16

16

5,7

5,7

5

5

3.3VC

COM1_TX

COM1_RTS#

COM1_RX

COM1_CTS#

J28

1

C1

2

C2

3

C3

4

C4

5

C5

6

C6

VENDOR=MOLEX

VEN_P/D_NUM=53780-0690

F

G

H

I

J

73P9323

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

1 2 3 4 5 6 7 9 108

OUTSIDE MAX

INSIDE MAX

PART NO.

UART

SCALE: 1/1

0.13

2.0 APPROVED

73P9323

TITLE

DESIGNER

CHECKED

SHEET

IBM CONFIDENTIAL

PEREGRINE

9-16-2003_17:24

JAD

???

???

12

SEPTEMBER 2003

???

???

OF

H

I

J

20

Page 13

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

A

B

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

C

9,16

D

12

12

12

E

12

May be able to second source with Pericom PI3B3257

F

RS232_SELECT

3.3VC

16

PWR

COM5_RX

COM5_CTS#

COM5_RTS#

COM5_TX

VEN_P/D_NUM=SN74CBTLV3257PWR

12

4

1A

7

2A

9

3A

4A

OE

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

GND

8

VENDOR=TI

U96

15

1

S

COM5_232RX

2

3

COM5_232CTS#

5

6

COM5_232RTS#

11

10

COM5_232TX

14

13

16

16

16

16

R237

R650

1K

R485_A_RTS_N

3.3VC

10K

SIGNAL=3.3VC;14

SIGNAL=GND;7

R485

U34

1

AHC04sop

3.3VC

R457

27K

3.3VC

U5

NOPOP

485_A_RX

0

2

485_A_CTS_N

485_A_RTS

485_A_TX

RO VCC

1 8

RE_N

2

DE

3

DI

4

RS485DRIVER

SOIC8

B

A

GND

-

7

+

6

5

C96

100N

R456

27K

R158

120

C52

4.7N

C246

220P

485_N_BUS_A

485_P_BUS_A

RS 485 Bus A

16

16

C

D

E

F

ST_MICRO

ST14800ABDR

G

3.3VC

R454

27K

H

3.3VC

G

H

U6

C51

4.7N

C241

220P

485_N_BUS_B

485_P_BUS_B

RS 485 Bus B

16

16

5,7

COM2_RTS#

R483

U34

NOPOP

5

0

5

43

COM2_RX

COM2_CTS#

RO VCC

1 8

RE_N

2

DE

3

RS485DRIVER

B

-

7

A

+

6

R157

120

I

J

73P9323

AHC04sop

SIGNAL=3.3VC;14

SIGNAL=GND;7

1 2 3 4 5 6 7 9 108

5,7

COM2_TX

R238

1K

DI

4

ST_MICRO

ST14800ABDR

SOIC8

GND

5

C97

100N

R455

27K

Keep inductor/capacitor filter near connector

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

RS485 DRIVERS

SCALE: 1/1

0.13

2.0 APPROVED

PART NO.

73P9323

TITLE

PEREGRINE

9-16-2003_17:24

DESIGNER

CHECKED

SHEET

JAD

???

???

IBM CONFIDENTIAL

SEPTEMBER 2003

???

???

13

OF

20

I

J

Page 14

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

3.3VC

A

10K

R514

I2C_SELECT

5

SEEPROM = 0, HOST = 1

3.3VC

B

3.3VC

U92

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

VCC

R495

POP

C

I2C_SCL

5

D

5

I2C_SDA

10K

R17

10K

POP

3.3VC

FROM 405GP

3.3VC

J1

1

C1

E

2

C2

3

C3

4

C4

CONN1X4

MAIN I2C BUS Debug Connector

5

IN

6

D

4

VEN_P/D_NUM=STG3157CTR

VCC

5

IN

6

D

4

VEN_P/D_NUM=STG3157CTR

SCL

IN = 1

IN = 0

VENDOR=ST_MICRO

S1

1

S2

3

2

GND

U93

SDA

IN = 1

IN = 0

VENDOR=ST_MICRO

S1

1

S2

3

2

GND

TO HOST

HOST_I2C_SCL

HOST_I2C_SDA

16

16

R609

POP

3.3VC

100K

R608

POP

100K

SEEPROM_SCL

SEEPROM_SDA

VEN_P/D_NUM=M24C64-WMN6T

3.3VC

EEPROM

VCC A0

8 1

WP

7

SDA

5

SERIAL-I2C

VENDOR=ST_MICRO

A1

A2SCL

GND

C

D

100N

U91

C553

2

36

4

E

3.3VC3.3VC3.3VC3.3VC

NOPOP

3.3VC

U3

PCA9557

TSSOP16

IO_OVCC

IO_1

IO_2

IO_3

IO_4

IO_5

IO_6

IO_7

GND

616

7

9

10

11

12

13

14

8

R604

POP

3.3VC

2K

R605

POP

2K

3.3VC

VCC

IN

R638

0

5

6

SCL

NOPOP

IN = 1

1

U94

S1

R606

POP

3.3VC

R607

100K

POP

100K

5,12,16,17

PERIPHERAL_RESET_N

15

3

A0

4

A1

5

A2

RESET_N

1

SCL

2

SDA

F

G

R79

POP

R78

100K

POP

R93

100K

POP

R89

100K

POP

R109

100K

POP

R96

100K

POP

R112

100K

POP

R111

100K

POP

100K

HOST_ID0

HOST_ID1

HOST_ID2

HOST_ID3

HOST_ID4

HOST_ID5

HOST_ID6

HOST_ID7

16

16

16

16

16

16

16

16

These pins are used identify the host that harrier is plugged into.

F

G

Each host will have a unique ID

D

4

IN = 0

S2

3

2

GND

Crows = 0

Magpie = 1

VENDOR=ST_MICRO

H

16

16

USB_SCL

USB_SDA

3.3VC

FROM EZUSB

I

VEN_P/D_NUM=STG3157CTR

VCC

5

IN

6

D

4

VEN_P/D_NUM=STG3157CTR

SDA

IN = 1

IN = 0

VENDOR=ST_MICRO

S1

1

S2

3

2

GND

H

U95

I

IBM CONFIDENTIAL

PART NO.

J

73P9323

R639

0

1 2 3 4 5 6 7 9 108

NOPOP

I2C SEEPROM AND SWITCHES

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

73P9323

TITLE

SCALE: 1/1

0.13

2.0 APPROVED

DESIGNER

CHECKED

SHEET

PEREGRINE

9-16-2003_17:24

JAD

???

???

14

SEPTEMBER 2003

???

???

OF

J

20

Page 15

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

A

B

3.3VC

+1%/-1%

49.9

+1%/-1%

49.9

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

B

1N

1N

3

20

2

55

27

28

22

46

8

1

32

29

24

40

54

63

45

7

R34

+5%/-5%

+1%/-1%

49.9

R33

+5%/-5%

R612

0

3.3VC

100N

C5

Place all power caps as close to BCM5221 as possible.

3.3VC

100N

C20

3.3VC

C518

ENET_PHY_RX_CLK

5

C13

5

5

5

5

5

100P

place within one inch of BCM5221

10U

NOPOP

C17

5

2.2U

C1

C15

100N

MATCHING LENGTHS, SAME LAYER FOR PAIRS (50 Ohm SE, 100 Ohm Diff)

R613

0

C18

2.2UC2100N

10N

R615

0

R614

0

C16

10N

ENET_PHY_TX

ENET_PHY_TX_N

ENET_PHY_RX

ENET_PHY_RX_N

16

16

16

16

Please refer to "General Layout Notes" pg17 of BCM5221_apnote.pdf in /harrier/reference/

C

D

E

F

G

R15

C520

C

D

+1%/-1%

R8

1.27K

E

Place RDAC resistor as close as possible to BCM5221

3.3VC

NOPOP

F

NOPOP

G

4.7K

4.7K

NOPOP

R26

NOPOP

R27

4.7K

4.7K

NOPOP

R25

NOPOP

R24

4.7K

4.7K

R28

R29

PPC_NOT_READY_N

5,10

ENET_PHY_LNK_LED_N

16

ENET_PHY_SPD_TP

ENET_PHY_ACT_LED_N

16

JTAG_EN_TP

3.3VC

CLK_25MHZ_BCM

11

ENET_PHY_TX_CLK

5

NOPOP

RECEIVE_TP

ENET_PHY_RDAC

XMT_LED_TP

4.7K

R30

4.7K

R31

NOPOP

NOPOP

C12

ENET_PHY_TXD3

5,7

ENET_PHY_TXD2

5,7

ENET_PHY_TXD1

100P

5,7

ENET_PHY_TXD0

5,7

ENET_PHY_TX_EN

5,7

ENET_PHY_TX_ERR

5,7

----68 Ohm characteristic impedance-----

U2

9

RESET_N

17

ENERGY_DET

23

RDAC

35

LNKLED_N

36

SPDLED_N

34

XMTLED_N

33

RCVLED_N

64

JTAG_EN

10

PHYAD0

11

PHYAD1

12

PHYAD2

13

PHYAD3

14

PHYAD4

39

FDX

37

F100

38

ANEN

21

SD+

19

SD-

15

TESTEN

18

MII_EN

16

LOW_PWR

BCM5221KPT TQFP64_5MM

ENET_PHY_MDC

5

ENET_PHY_MDIO

5

ENET_PHY_COL

5

ENET_PHY_CRS

5

R11

33.2

52565758596053

TXER

TXEN

TXD0

TXD1

TXD2

TXD3

place 1nF capacitors as close as possible to 49.9 ohm resistors

R511

4.7K

4

5

TXC

6

REF_CLK

XTALO

XTALI

TD+

31

30

TD-

26

RD+

25

RD-

BCM5221

MDC

MDIO

COL

CRS/CRS_DV

RXER

RXDV

RXD0

RXD1

RXD2

RXD3

RXC

4241616251494847444350

3.3VC

-------------68 Ohm characteristic impedance--------------

R19

1.5K

POP

R1

22.1

49.9 ohm resistors close to PHY

+1%/-1%

49.9

R18

REGDVDD

REGAVDD

DVDD_2

DVDD_55

AVDD_27

AVDD_28

BIASVDD

OVDD_46

OVDD_8

OVDD_1

AGND_32

AGND_29

BIASGND

DGND_40

DGND_54

DGND_63

DGND_45

XTALGND

R12

33.2

ENET_PHY_RXD3

ENET_PHY_RXD2

ENET_PHY_RXD1

ENET_PHY_RXD0

ENET_PHY_RX_DV

ENET_PHY_RX_ERR

3.3VC

C519

H

I

J

73P9323

R13

1 2 3 4 5 6 7 9 108

R14

10K

NOPOP

10K

NOPOP

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

ETHERNET PHY

SCALE: 1/1

0.13

2.0 APPROVED

PART NO.

73P9323

TITLE

PEREGRINE

9-16-2003_17:24

DESIGNER

CHECKED

SHEET

JAD

???

???

IBM CONFIDENTIAL

SEPTEMBER 2003

???

???

15

OF

20

H

I

J

Page 16

4321 5

DATE EC NO.

108 976

EC NO.DATE

PART NO.

REL

3.3VC

U97

VCC

5

16

USB_EXT_N

A

16

USB_INT_N

S1ININ = 1

1

S2

3

IN = 0

2

Internal = 0, External = 1

6

D

4

USBD_N

16

? ?

73P9323

DEVELOPMENT NO.

Q/M

A

GND

EXT_USB_PWR_GOOD

J27

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

B

3.3VC

16

USB_EXT_P

J25

U98

S1ININ = 1

1

VCC

5

6

3.3VC

R627

5.1K

16

16

USB_EXT_N

USB_EXT_P

1

VBUS SH1

2

D-

3

D+

4

ID

5

GND

SH2

SH3

SH4

SH1

SH2

SH3

SH4

B

KEY

71

16

16

C

16

16

COM3_RX

COM3_TX

COM3_CTS#

COM3_RTS#

HOST_ID0

14

HOST_ID1

14

HOST_ID2

14

HOST_ID3

14

D

14

HOST_ID4

HOST_ID5

14

HOST_ID6

14

HOST_ID7

14

12

COM4_RTS#

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

E

16

16

USB_INT_P

USB_INT_N

RS232_SELECT9,13

93

94

95

96

97

10-30-02-JWD-P_EXT_ACK# is used to detect BIST mode after reset.

5

HOST_PCI_RST_N

P_EXT_ACK#5,7

IRQ4

98

99

100

101

5

RS232_DETECT

102

103

F

GPIO's 1 and 16 can be used for system specific requirements.

5,7

9

GPIO1

GPIO16

104

105

106

12

12

13

13

13

12

12

G

13

12

COM5_DTR#

COM5_DSR#

COM5_232TX

COM5_232CTS#

COM5_232RX

COM5_RI#

COM5_CD#

COM5_232RTS#

COM4_TX

107

108

109

110

111

112

113

114

115

116

117

12

COM4_RX

118

119

3.3VC

14

14

R544

H

5

10K

5

POP

9

9

HOST_I2C_SDA

HOST_I2C_SCL

HOST_PWRGD/RST#

HOST_PWR_REQ#

HOST_I2C_INT#

CABLE_DETECT#

120

121

122

123

124

125

126

127

128

129

130

131

12

12

I

16

NOPOP

SYS_ON

R3

9

COM4_CTS#

COM4_DTR#

HOST_SMI#

PCI3_3V

1K

12

COM4_DSR#

132

133

134

135

136

137

138

139

140

C71

C72

C73

C74

C75

C76

C77

C78

C79

C80

C81

C82

C83

C84

C85

C86

C87

C88

C89

C90

C91

C92

C93

C94

C95

C96

C97

C98

C99

C100

C101

C102

C103

C104

C105

C106

C107

C108

C109

C110

C111

C112

C113

C114

C115

C116

C117

C118

C119

C120

C121

C122

C123

C124

C125

C126

C127

C128

C129

C130

C131

C132

C133

C134

C135

C136

C137

C138

C139

C140

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C20

C21

C22

C23

C24

C25

C26

C27

C28

C29

C30

C31

C32

C33

C34

C35

LCD Port (Raw Digital Video)

C36

C37

C38

C39

C40

C41

C42

C43

C44

C45

C46

C47

C48

C49

C50

C51

C52

C53

C54

C55

C56

C57

C58

C59

C60

C61

C62

C63

C64

C65

C66

C67

C68

C69

C70

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

67

68

69

70

1

2

3

4

5

6

7

8

9

65

66

RN62

RN62

RN62

RN62

RN63

RN63

RN63

RN63

RN64

RN64

RN64

RN64

4

3

2

1

4

3

2

1

4

3

2

1

5

220

6

220

7

220

8

220

5

220

6

220

7

220

8

220

5

220

6

220

7

220

8

220

R536

220

RN65

RN65

RN65

RN65

RN66

RN66

RN66

RN66

RN67

RN67

RN67

RN67

4

3

2

1

4

3

2

1

4

3

2

1

5

220

6

220

7

220

8

220

5

220

6

220

7

220

8

220

5

220

6

220

7

220

8

220

485_N_BUS_B

485_P_BUS_B

485_N_BUS_A

485_P_BUS_A

ERROR_LED_BUF

COM4_CD#

ENET_PHY_RX_N

ENET_PHY_RX

ENET_PHY_TX_N

ENET_PHY_TX

ENET_PHY_LNK_LED_N

ENET_PHY_ACT_LED_N

DV_RED6

DV_RED7

DV_RED2

DV_RED3

DV_RED4

DV_RED5

DV_GRN6

DV_GRN7

DV_BLU7

DV_HSYNC

DV_VSYNC

DV_DE

DV_CLK

DV_RED1

DV_GRN3

DV_GRN4

DV_GRN5

DV_BLU1

DV_BLU4

DV_GRN1

DV_GRN2

DV_BLU3

DV_BLU6

DV_BLU2

DV_BLU5

13

13

13

13

5

12

15

15

15

15

15

15

17

17

17

17

17

17

17

17

17

17

17

17

17,18

17

17

17

17

17

17

17

17

17

17

17

17

3V_BAT

9,10,12,17

16

USB_INT_P

ROM_DATA[0:31]

16

16

16

16

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

ROM_DATA7

ROM_DATA6

ROM_DATA5

ROM_DATA4

ROM_DATA3

ROM_DATA2

ROM_DATA1

ROM_DATA0

COM3_RX

COM3_TX

COM3_CTS#

COM3_RTS#

RN57

RN57

RN57

RN57

RN56

RN56

RN56

RN56

16

**Select PE[7..0] alternate function and make PE[7..0] outputs. (per data sheet pg25)

***Turn off the CLKOE bit in firmware so the CPU clock is not driven on CLKOUT

5

0

6

0

7

0

8

0

5

0

6

0

7

0

8

0

5

0

6

0

7

0

8

0

5

0

6

0

7

0

8

0

4

3

2

1

4

3

2

1

8

0

7

6

0

0

5

0

8

10K

7

10K

6

10K

5

10K

SYS_ON

****

D

4

USBD

16

10K

U78

4

RN59

3

RN59

2

RN59

1

RN59

4

RN58

3

RN58

2

RN58

1

RN58

4

RN61

3

RN61

2

RN61

1

RN61

4

RN60

3

RN60

2

RN60

1

RN60

5

0

6

0

7

0

8

0

5

0

6

0

7

0

8

0

1

RN54

2

RN54

3

RN54

4

RN54

1

RN55

2

RN55

3

RN55

4

RN55

R527

B_OUT_FLAG

**

0

11

PA0

12

PA1

13

PA2

14

PA3

15

PA4

16

PA5

17

PA6

18

PA7

47

PB0

D0

48

PB1

D1

49

PB2

D2

50

PB3

D3

51

PB4

D4

52

PB5

D5

53

PB6

D6

54

PB7

D7

68

PC0

69

PC1

70

PC2

71

PC3

73

PC4

74

PC5

75

PC6

76

PC7

30

PD0

31

PD1

32

PD2

33

PD3

34

PD4

35

PD5

36

PD6

37

PD7

B_OUT_FLAG

55

PE0

44

NC_44

45

NC_45

46

NC_46

56

NC_56

66

NC_66

67

NC_67

77

NC_77

78

NC_78

79

NC_79

VENDOR=CYPRESS

VEN_P/D_NUM=CY7C64613-80NC

****If system is off, Remove power from USB pull-up.

KEY

R624

CY7C64613-80NC

FIFO "A"

A_IN_FLAG

B_IN_FLAG

A_OUT_FLAG

ASEL

BSEL

AOE

SLRW

SLRD

RESERVED_9

RESERVED_22

RESERVED_24

PQFP_80

AVCC

VCC_21

VCC_41

VCC_61

VCC_1

SCL

SDA

USBD

USBD_N

XIN

XOUT

WAKEUP_N

CLKOUT

XCLK

XCLKSEL

DISCON_N

RESET_N

CTL0

CTL1

CTL2

RDY0

RDY1

RDY2

RDY3

RDY4

RDY5

AGND

GND_10

GND_20

GND_29

GND_40

GND_43

GND_60

GND_72

GND_80

USB Mini-B

VEN_P/D_NUM=440247-2

VENDOR=AMP

3.3VC

C542

100N

5

21

41

61

1

2

3

39

38

6

7

4

19

***

59

23

28

42

62

57

58

63

64

65

25

26

27

9

22

24

8

10

20

29

40

43

60

72