Page 1

ABC

Acknowledge: This Design Is Leveraged From Mark Shelton's Landrover 1x2 BP Design

REVISIONS

REV

X00 INITIAL PROTOTYPE

X01 PROTOTYPE UNIT TEST BUILD

X02 PROTOTYPE PRODUCT TEST BUILD

DESCRIPTIONECO DATE

D

APPROVED

7/28/03

8/21/03

12/10/03

1

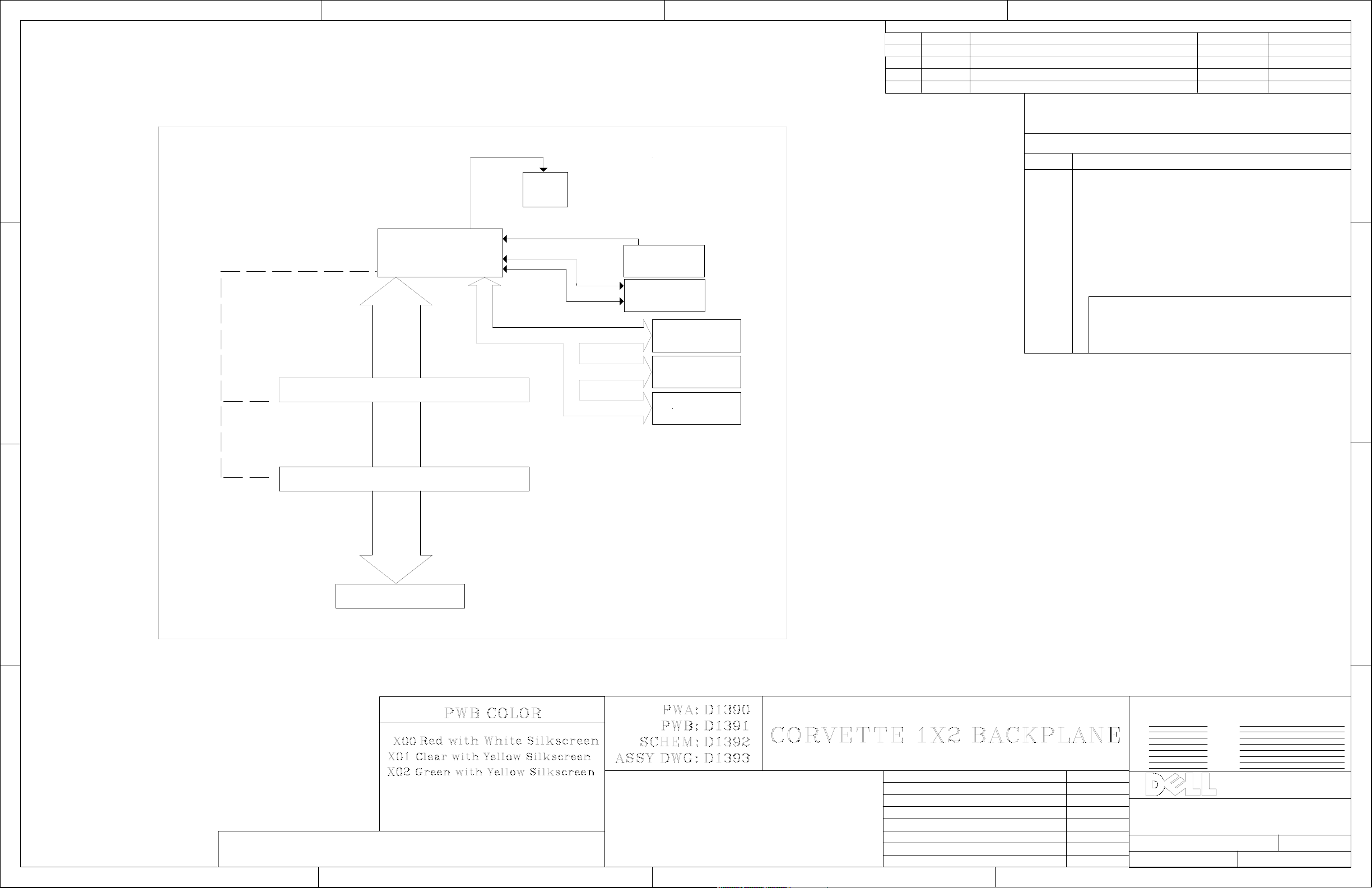

Corvette 1x2 SCSI BP

1

TABLE OF CONTENTS

I2C

FRU

IPMB

PWRGOOD

12V and 5V

POWER

CONNECTOR

SIGNAL

DRIVE PRESENCE<0..1>

BACKPLANE/DTR

MATING

CONNECTOR

SCSI BUS A

CONNECTOR

2

FAULT

LEDS

PAGE DESCRIPTION

1 BLOCK DIAGRAM

2

ROUTING & OTHER RULES, STACKUP

3

BP/DTR MATING & SCSI CONNECTORS

LVD SCSI SLOTS 0 - 1

4

5

I2C CIRCUITRY and 3.3V LDO

6

PWRCONN and SIGCONN

7

IMP. COUPONS,GND CLIPS,CPTV SCREWS

SCHEMATIC IS CONFIGURED TO USE

THE XLBOM UTILITY:

BUILD0 IS PROTOTYPE BUILD

BUILD1 IS PRODUCTION BUILD

2

ACTIVITY

LEDS

SCSI ID0

ONLINE

LEDS

SCSI ID1

3

3

LVD SCSI

CONNECTOR A

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

4

THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER

CORP., EXCEPT AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN

ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE

REPRODUCED IN WHOLE OR IN PART AND MUST BE RETURNED TO DELL

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION

OF THE PURPOSE OF THE LOAN. NEITHER THIS ITEM NOR THE

INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS

NOT HAVING A NEED FOR SUCH USE OR DISCLOSURE CONSISTENT WITH

THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF

DELL COMPUTER CORPORATION.

PROPRIETARY NOTE

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

Mark Shelton/Dan Rao

M. Shelton/D. Rao/J. Melanson/R. Hemingway

ECO

TITLE

SCHEM, BKPLN, 1X2, PE2800

DWG NO.

DATE

D1392

12/5/2003 1 OF 7

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

COMPUTER

CORPORATION

AUSTIN,TEXAS

SHEET

REV.

X02

4

-03

DCBA

Page 2

ABC

D

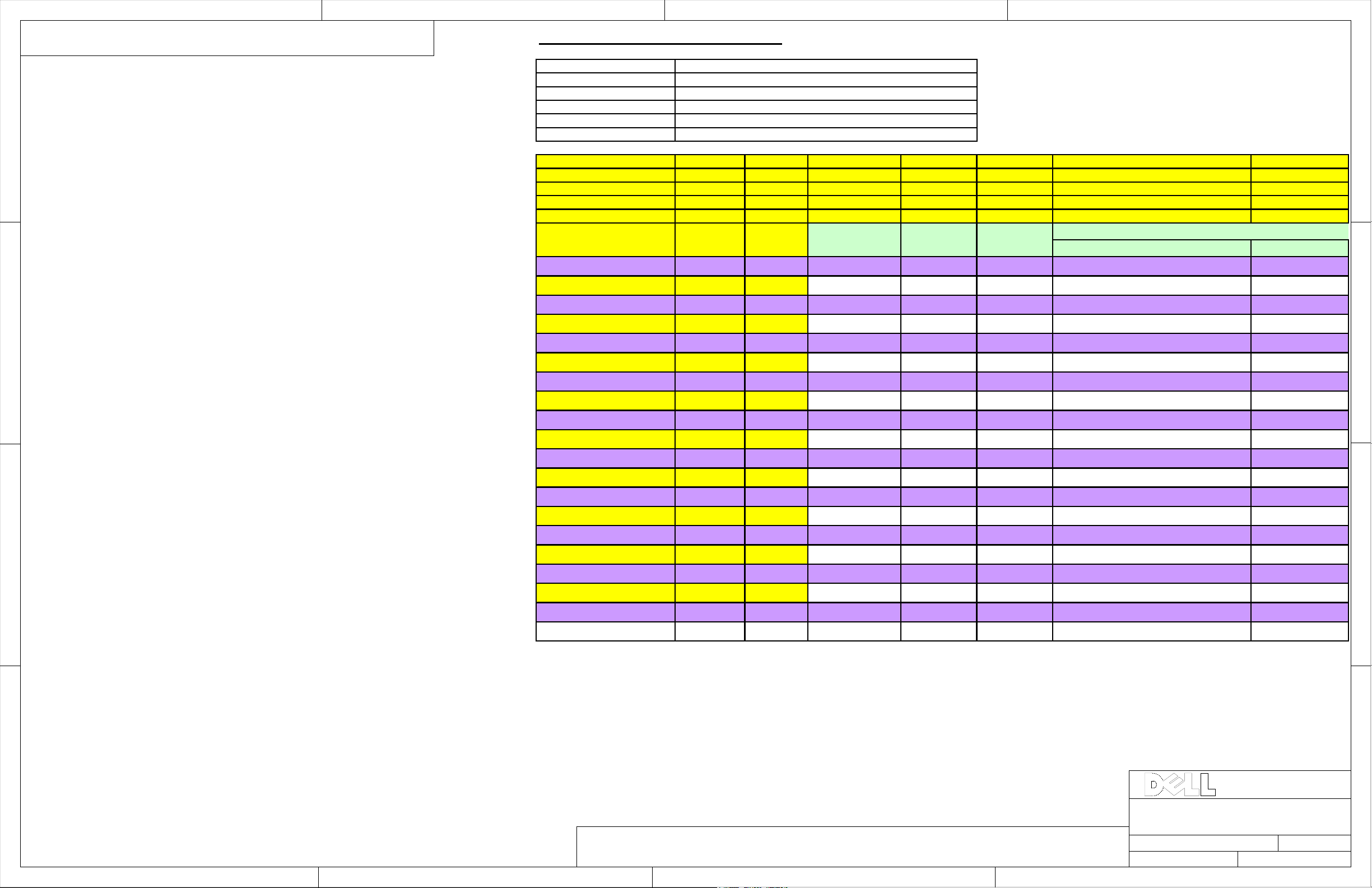

STACKUP AND ROUTING RULES

1

NOTE ON COMPONENT PLACEMENT:

--> ALL COMPONENTS SHOULD BE PLACED ON THE TOP SIDE IF POSSIBLE EXCEPT:

SCSIA, PWRCONN, SIGCONN CONNECTORS

NOTE ON SCSI ROUTING RULES:

--> SCSI SIGNALS ARE NAMED SCSI_D_*. THERE ARE 27 DIFFERENTIAL PAIRS.

THEY HAVE FIRST PRIORITY WHEN ROUTING.

--> AVOID VIAS WHENEVER POSSIBLE. USE THE SAME NUMBER OF VIAS BETWEEN PAIRS

IF UNAVOIDABLE.

--> ROUTE SCSI_D_SREQ* AND SCSI_D_SACK* FIRST. ISOLATION FROM OTHER PAIRS IS

1.5X (22MIL) SINCE THEY ARE MORE SUSCEPTIBLE TO CROSSTALK.

--> TRY TO ROUTE ALL THE ± DIFFERENTIAL SIGNALS ON INNER LAYERS (IN1-2 & IN5-6)

IF POSSIBLE AS EDGE COUPLED DIFFERENTIAL PAIRS.

--> ALL SCSI SIGNALS SHALL BE LENGTH MATCHED TO WITHIN 100MILS ~17PS WITHIN BUS

AND VARIATION WITHIN PAIR SHALL BE < 5 MILS. RULE FILE WILL BE PROVIDED

TO ACHIEVE THIS.

--> SCSI TRACE WIDTH AND SPACING MUST BE MAINTAINED AS IN THE TABLE. THE ONLY

2

ACCEPTABLE DEVIATION FROM THE SPACING IS WHERE THE SIGNALS MUST ROUTE

THROUGH THE Z-PACK CONNECTOR

PWB Impedance Reference Table

PWB PN: D1391

Program Name: Corvette

PWB Name: Corvette 1x2 SCSI Backplane

PWB Revision: x00

PWB Thickness: 0.100"

Date: 10/21/2003 PWC

Bus

Z Type

Freq.(MHz)

Target Z (ohms)

Z tolerance

Finished Dielect Tolerance

Layer Lyr Type Cu Wt Thickness

1 Top 1.5 oz 2.1 5/11/5/30 (120.5) Ref L2 Allowed

Prepreg 8.0 +/-2 mil 4.3

2 GND 1 oz 1.4

Core 7.0 +/-1 mil 4.3

3 IN1 1/2 oz 0.7

Prepreg 20.0 +/-3 mil 4.3

Er

1

SCSI Clocks

Differential

120

+/- 10%

Trace/ Space / Trace/space_to_other pair Layer Restrictions

GND GND

2

4/10/4/15 (119.1) Ref L2&L5 Allowed

GENERAL (NON-SCSI) ROUTING RULES:

--> FOR EXTERNAL LAYERS (TOP AND BOTTOM), USE 6 MIL TRACE,

6MIL SPACING FOR 60 OHM SIGNALS.

--> FOR INTERNAL LAYERS (IN1 AND IN2), USE 6 MIL TRACE

12MIL SPACING FOR 60 OHM SIGNALS.

--> ALL NON-SCSI TRACES SHALL BE ISOLATED FROM LVD SCSI SIGNALS BY 50MILS.

--> I2C SIGNALS SHOULD BE ROUTED SERIALLY. THERE SHOULD NOT BE ANY LONG

STUBS OR BRANCHES.

TRY TO KEEP THESE SIGNALS AWAY FROM SCSI LVD SIGNALS.

POWER SIGNALS ROUTING RULES:

--> TRY TO USE ISLANDS FOR ALL POWER SIGNALS WITH NO POWER PLANE.

IF ISLANDS ARE NOT POSSIBLE, USE AT LEAST 30 MIL TRACES.

--> USE MULTIPLE VIAS WHERE THE POWER SIGNALS CHANGE LAYERS,

3

I.E. FROM THE POWER SOURCE ON THE TOP/BOTTOM LAYER

TO THE POWER PLANE ON THE INNER LAYER

--> FOR LARGE CERAMIC CAP PACKAGE, I.E. 1210 PACKAGE, USE MULTIPLE VIAS AND MAKE SURE

THE TRACE IS KEPT AS SHORT AS POSSIBLE.

--> SHORTEN THE PATH FROM THE CAPACITOR PADS TO THE GROUND VIAS (10MIL < L < 20MIL)

AND KEEP THE TRACE AT LEAST 20MILS WIDE TO REDUCE INDUCTANCE.

--> DO NOT SHARE POWER OR GROUND VIAS FOR DECOUPLING CAPS.

TESTABILITY AND TOOLING HOLE:

--> REFER TO SEPERATE TESTABILITY DOCUMENT TEST POINT PLACEMENT REQUIREMENT.

--> AT LEAST THREE TOOLING HOLES MUST BE INCLUDED ON THE BOARD.

4 IN2 1/2 oz 0.7

Core 7.0 +/-1 mil 4.3

5 VCC 1 oz 1.4

Prepreg 5.0 +/-2 mil 4.3

6 Gnd2 1 oz 1.4

Core 7.0 +/-1 mil 4.3

7 IN5 1/2 oz 0.7

Prepreg 20.0 +/-3 mil 4.3

8 IN6 1/2 oz 0.7

Core 7.0 +/-1 mil 4.3

9 VC2 1 oz 1.4

Prepreg 8.0 +/-2 mil 4.3

10 Bot 1.5 oz 2.1

Total Thickness 101.6 +/- 10mil

4/10/4/15 (119.1) Ref L2&L5 NOT ALLOWED

VCC VCC

Gnd2 Gnd2

4/10/4/15 (119.1) Ref L6&L9 Allowed

4/10/4/15 (119.1) Ref L6&L9 NOT ALLOWED

3

VC2 VC2

5/11/5/30 (120.5) Ref L9 NOT ALLOWED

SILKSCREEN:

--> ALL COMPONENTS SHOULD HAVE PIN 1 LABELED.

--> ON MANY PIN COMPONENTS AND CONNECTORS, THERE SHOULD BE A TICK MARK EVERY 10 PINS.

--> ALL REFERENCE DESIGNATORS SHALL BE VISIBLE WHEN THE PARTS ARE PLACED.

4

IMPEDANCE COUPON:

--> PLEASE FOLLOW THE SEPERATE IMPEDANCE COUPON DOCUMENT FOR SPECIFIC REQUIREMENT.

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

COMPUTER

CORPORATION

TITLE

SCHEM, BKPLN, 1X2, PE2800

DWG NO.

DATE

D1392

12/5/2003 2 OF 7

AUSTIN,TEXAS

SHEET

DCBA

REV.

4

X02

Page 3

ABC

D

BP/DTR CONNECTOR AND SCSI CONNECTOR

+3.3V

BACKPLANE/DAUGHTER BOARD MATING

1

R8

21

2

3

4

CONNECTOR (110 PIN)

+5V

GEM_I2C_ADDR0

NC_LEDFALT4_N

NC_LEDONLN4_N

220

SCSI_D_SD10-

3,4

SCSI_D_SD10+

3,4

SCSI_D_SD8-

3,4

SCSI_D_SD8+

3,4

SCSI_D_SREQ-

3,4

SCSI_D_SREQ+

3,4

SCSI_D_SSEL-

3,4

SCSI_D_SSEL+

3,4

SCSI_D_SRST-

3,4

SCSI_D_SRST+

3,4

SCSI_D_SBSY-

3,4

SCSI_D_SBSY+

3,4

3

3

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

4

+3.3V

HD_PRES3_N

HD_PRES4_N

SCSI_D_SDP0SCSI_D_SDP0+

SCSI_D_SD6SCSI_D_SD6+

SCSI_D_SD4SCSI_D_SD4+

SCSI_D_SD2SCSI_D_SD2+

SCSI_D_SD0SCSI_D_SD0+

SCSI_D_SD15SCSI_D_SD15+

SCSI_D_SD13SCSI_D_SD13+

HD_PRES1_N

LEDONLN0_N

4

I2C1_CLK_DC

5

LEDFALT0_N

4

I2C1_SDA_DC

5

NC_JTAG_TDO

IPMB_RST_N

6

+3.3V

C2

12

22uF 10V

12

C5

6/12/03 Match pin out v2.0

12

C3

0.1uF 16V

E10

D10

E11

D11

E15

D15

E16

D16

E17

D17

E18

D18

E19

D19

E20

D20

E21

D21

E22

D22

E23

D23

E24

D24

E25

D25

12

C6

0.1uF 16V

DTRCONN

MALE

A10

B10

C10

A11

B11

C11

A15

B15

C15

A16

B16

C16

A17

B17

C17

A18

B18

C18

A19

B19

C19

A20

B20

C20

A21

B21

C21

A22

B22

C22

A23

B23

C23

A24

B24

C24

A25

B25

C25

A1

B1

C1

A2

B2

C2

A3

B3

C3

A4

B4

C4

A5

B5

C5

A6

B6

C6

A7

B7

C7

A8

B8

C8

A9

B9

C9

E1

E1

D1

D1

E2

E2

D2

D2

E3

E3

D3

D3

E4

E4

D4

D4

E5

E5

D5

D5

E6

E6

D6

D6

E7

E7

D7

D7

E8

E8

D8

D8

E9

E9

D9

D9

E10

D10

E11

D11

E15

D15

E16

D16

E17

D17

E18

D18

E19

D19

E20

D20

E21

D21

E22

D22

E23

D23

E24

D24

E25

D25

VERTICAL PLUG

HM CONN

DPN: 3729R

PRESS FIT

ROOM=DTRCONN

0.1uF 16V

A1

B1

C1

A2

B2

C2

A3

B3

C3

A4

B4

C4

A5

B5

C5

A6

B6

C6

A7

B7

C7

A8

B8

C8

A9

B9

C9

A10

B10

C10

A11

B11

C11

A15

B15

C15

A16

B16

C16

A17

B17

C17

A18

B18

C18

A19

B19

C19

A20

B20

C20

A21

B21

C21

A22

B22

C22

A23

B23

C23

A24

B24

C24

A25

B25

C25

C2_PRES_N

NC_LEDONLN3_N

NC_LEDONLN2_N

DC_PWRGOOD

LEDONLN1_N

CONNB_PRES_N

CONNA_PRES_N

C2_HAS_ID_0_N

SCSI_D_DIFFSENS

SCSI_D_SD11+

SCSI_D_SD11-

NC_GEM_I2C_ADDR1

SCSI_D_SD9+

SCSI_D_SD9-

SCSI_D_SIO+

SCSI_D_SIO-

SCSI_D_SCD+

SCSI_D_SCD-

SCSI_D_SMSG+

SCSI_D_SMSG-

SCSI_D_SACK+

SCSI_D_SACK-

SCSI_D_SATN+

SCSI_D_SATN-

SCSI_D_SD7+

SCSI_D_SD7NC_BUS_SPLIT_N

SCSI_D_SD5+

SCSI_D_SD5-

SCSI_D_SD3+

SCSI_D_SD3-

SCSI_D_SD1+

SCSI_D_SD1-

SCSI_D_SDP1+

SCSI_D_SDP1-

SCSI_D_SD14+

SCSI_D_SD14-

SCSI_D_SD12+

SCSI_D_SD12-

HD_PRES0_N

PCI_RESET_N

NC_JTAG_TMS

ISO_IPMB_DATA

ISO_IPMB_CLK

NC_JTAG_TCK

NC_JTAG_TDI

NC_LEDFALT2_N

DC_SERIAL_ID_LATCH

DC_SERIAL_ID_DATA

DC_SERIAL_ID_CLOCK

NC_LEDFALT3_N

LEDFALT1_N

HD_PRES2_N

+5V

21

C1

12

C4

22uF 10V

12

C7

0.1uF 16V

R10

4.7K

12

6

4

3

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

4

6

6

6

4

3

12

C8

0.1uF 16V

+3.3V

R6

12

R211

21

R1

R3

220

21

21

0.1uF 16V

4.7K

220

220

R4

220

21

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

ADD1=ADD*_D1391_PWB

ADD2=ADD*_D1392_SCH

ADD3=ADD*_D1393_ASSY_DWG

ADD4=ADD*_42610_BAR

ADD5=ADD*_42753_REV

DTRCONN

COMPONENT

FRONT VIEW

WIDE

123 11

E

D

C

B

A

A

B

C

D

E

123 11

3

3

3

HD_PRES2_N

HD_PRES3_N

HD_PRES4_N

15 25

KEY

NARROW

KEY

DTRCONN

COMPONENT

BOTTOM VIEW

MOUNTING

PEG

+3.3V

R7

4.7K

12

15 25

R11

4.7K

12R912

4.7K

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

PLACE NEAR BACKPLANE/DAUGHTER BOARD

MATING CONNECTOR (DTRCONN)

--- AVOID PLACING DECOUPLING CAPS TO CONNECTOR PINS WITH LONG TRACES (>25MILS)

--- INSTEAD, PLACE CAPS AS CLOSE TO CONNECTOR AS POSSIBLE, AND TIE THEM

DIRECTLY TO POWER PLANE WITH VERY SHORT TRACES

--- EACH CAP SHOULD HAVE ITS OWN POWER/GND PAIR. AVOID SHARING VIAS.

SCSI_D_SD12+

SCSI_D_SD13+

SCSI_D_SD14+

SCSI_D_SD15+

SCSI_D_SDP1+

SCSI_D_SD0+

SCSI_D_SD1+

SCSI_D_SD2+

SCSI_D_SD3+

SCSI_D_SD4+

SCSI_D_SD5+

SCSI_D_SD6+

SCSI_D_SD7+

SCSI_D_SDP0+

SCSI_D_DIFFSENS

NC_TRMPWR_D_17

NC_TRMPWR_D_18

NC_A_19

SCSI_D_SATN+

CONNA_PRES_N

3

SCSI_D_SBSY+

SCSI_D_SACK+

SCSI_D_SRST+

SCSI_D_SMSG+

SCSI_D_SSEL+

SCSI_D_SCD+

SCSI_D_SREQ+

SCSI_D_SIO+

SCSI_D_SD8+

SCSI_D_SD9+

SCSI_D_SD10+

SCSI_D_SD11+

SCSI 68-PIN CONNECTOR A

SCSIA

RCPT

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

SCSI_D_SD12SCSI_D_SD13SCSI_D_SD14SCSI_D_SD15SCSI_D_SDP1SCSI_D_SD0SCSI_D_SD1SCSI_D_SD2SCSI_D_SD3SCSI_D_SD4SCSI_D_SD5SCSI_D_SD6SCSI_D_SD7SCSI_D_SDP0-

CONNA_PRES_N

NC_TRMPWR_D_51

NC_TRMPWR_D_52

NC_M_53

SCSI_D_SATN-

SCSI_D_SBSYSCSI_D_SACKSCSI_D_SRSTSCSI_D_SMSGSCSI_D_SSELSCSI_D_SCDSCSI_D_SREQSCSI_D_SIOSCSI_D_SD8SCSI_D_SD9SCSI_D_SD10SCSI_D_SD11-

TITLE

SCHEM, BKPLN, 1X2, PE2800

DWG NO.

DATE

D1392

12/5/2003

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

ROOM=SCSIA

Mechanical Parts:

ADD6=ADD*_Y2657_FORMEX

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

COMPUTER

CORPORATION

AUSTIN,TEXAS

+3.3V

R5

4.7K

12

REV.

SHEET

3 OF 7

1

3

2

3

4

X02

DCBA

Page 4

ABC

D

SLOT1

+12V

0.1uF 16V

1

C110

12

0.1uF 16V

C109

12

ROOM=SLOT1

+12V

0.1uF 16V

C116

12

0.1uF 16V

C115

12

SLOT0

ROOM=SLOT0

1

+3.3V

+5V

+3.3V

R116

4.7K

12

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

+12V

16V 10%

10uF

C107

1

2

10uF

1

2

C106

10uF

16V 10%

16V 10%

+5V

0.1uF 16V

C112

12

+5V

4

22uF 10V

22uF 10V

12

C123

+12V

R207

+12V

16V 10%

10uF

C104

1

2

16V 10%

10uF

C103

1

2

16V 10%

10uF

C105

1

2

2.2-5%

0.1uF 16V

C117

12

+5V

2

0.1uF 16V

C113

12

+5V

R208

22uF 10V

12

C121

22uF 10V

12

C122

0.1uF 16V

C118

12

21

2.2-5%

MIN_LINE_WIDTH=30MIL

21

MIN_LINE_WIDTH=28MIL

21

R134

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

220

12VCHARGE_1

NC_3V3_1_S1

NC_3V3_2_S1

SCSI_D_SD11SCSI_D_SD10SCSI_D_SD9SCSI_D_SD8SCSI_D_SIOSCSI_D_SREQSCSI_D_SCDSCSI_D_SSELSCSI_D_SMSGSCSI_D_SRSTSCSI_D_SACKSCSI_D_SBSYSCSI_D_SATNSCSI_D_SDP0SCSI_D_SD7SCSI_D_SD6SCSI_D_SD5SCSI_D_SD4SCSI_D_SD3SCSI_D_SD2SCSI_D_SD1SCSI_D_SD0SCSI_D_SDP1SCSI_D_SD15SCSI_D_SD14SCSI_D_SD13SCSI_D_SD12-

5VCHARGE_1

NC_SYNC_1

RMT_START_1

SCSI_ID0_1

NC_SCSI_ID2_1

21

220

R136

SLOT1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

VERT RCPT

BLINDMATE

81

82

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

HD_PRES1_N

NC_3V3_3_S1

SCSI_D_DIFFSENS

SCSI_D_SD11+

SCSI_D_SD10+

SCSI_D_SD9+

SCSI_D_SD8+

SCSI_D_SIO+

SCSI_D_SREQ+

SCSI_D_SCD+

SCSI_D_SSEL+

SCSI_D_SMSG+

SCSI_D_SRST+

SCSI_D_SACK+

SCSI_D_SBSY+

SCSI_D_SATN+

SCSI_D_SDP0+

SCSI_D_SD7+

SCSI_D_SD6+

SCSI_D_SD5+

SCSI_D_SD4+

SCSI_D_SD3+

SCSI_D_SD2+

SCSI_D_SD1+

SCSI_D_SD0+

SCSI_D_SDP1+

SCSI_D_SD15+

SCSI_D_SD14+

SCSI_D_SD13+

SCSI_D_SD12+

HD_PRES1_N

LEDACT1_N

NC_DLYD_START_1

NC_SCSI_ID1_1

NC_SCSI_ID3_1

3

C108

1

2

12

C124

+12V

0.1uF 16V

C120

12

0.1uF 16V

C119

12

R210

2.2-5%

R209

2.2-5%

R131

MIN_LINE_WIDTH=30MIL

21

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

MIN_LINE_WIDTH=28MIL

21

21

220

12VCHARGE_0

NC_3V3_1_S0

NC_3V3_2_S0

SCSI_D_SD11SCSI_D_SD10SCSI_D_SD9SCSI_D_SD8SCSI_D_SIOSCSI_D_SREQSCSI_D_SCDSCSI_D_SSELSCSI_D_SMSGSCSI_D_SRSTSCSI_D_SACKSCSI_D_SBSYSCSI_D_SATNSCSI_D_SDP0SCSI_D_SD7SCSI_D_SD6SCSI_D_SD5SCSI_D_SD4SCSI_D_SD3SCSI_D_SD2SCSI_D_SD1SCSI_D_SD0SCSI_D_SDP1SCSI_D_SD15SCSI_D_SD14SCSI_D_SD13SCSI_D_SD12-

5VCHARGE_0

NC_SYNC_0

RMT_START_0

NC_SCSI_ID0_0

NC_SCSI_ID2_0

SLOT0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

VERT RCPT

BLINDMATE

81

82

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

HD_PRES0_N

NC_3V3_3_S0

SCSI_D_DIFFSENS

SCSI_D_SD11+

SCSI_D_SD10+

SCSI_D_SD9+

SCSI_D_SD8+

SCSI_D_SIO+

SCSI_D_SREQ+

SCSI_D_SCD+

SCSI_D_SSEL+

SCSI_D_SMSG+

SCSI_D_SRST+

SCSI_D_SACK+

SCSI_D_SBSY+

SCSI_D_SATN+

SCSI_D_SDP0+

SCSI_D_SD7+

SCSI_D_SD6+

SCSI_D_SD5+

SCSI_D_SD4+

SCSI_D_SD3+

SCSI_D_SD2+

SCSI_D_SD1+

SCSI_D_SD0+

SCSI_D_SDP1+

SCSI_D_SD15+

SCSI_D_SD14+

SCSI_D_SD13+

SCSI_D_SD12+

HD_PRES0_N

LEDACT0_N

NC_DLYD_START_0

NC_SCSI_ID1_0

NC_SCSI_ID3_0

+5V

R115

4.7K

12

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

2

4

3

4

3

3

4

DLYD_START RMT_START FUNCTION

OPEN OPEN Motor spins at DC Power-on

OPEN* GND* Motor spins at START UNIT command

GND OPEN Motor spins after Power-on plus

GND GND Reserved

delay based on SCSI ID

LEDACT1_N

LEDONLN1_N

LEDFALT1_N

R198

12

RLEDACT1

220-5%

R197

12

RLEDONLN1

220-5%

R196

12

RLEDFALT1

220-5%

R165

4.7K

12

DS11

12

GRN LED

DS14

1

34

2

G

Y

GRN / YEL LEDS

+5V

LEDACT0_N

4

LEDONLN0_N

3

LEDFALT0_N

3

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

R195

12

RLEDACT0

220-5%

R193

12

RLEDONLN0

220-5%

R194

12

RLEDFALT0

220-5%

R159

4.7K

12

GRN LED

DS13

1

2

G

43

Y

GRN / YEL LEDS

+5V

DS12

21

LVD SCSI SLOTS 0 - 1

TITLE

SCHEM, BKPLN, 1X2, PE2800

DWG NO.

DATE

D1392

12/5/2003 4 OF 7

DCBA

COMPUTER

CORPORATION

AUSTIN,TEXAS

REV.

SHEET

4

X02

Page 5

ABC

3.3V LDO & FRU DEVICE

D

+3.3V

1

3.3V POWER

+5V

+3.3V

U_LDO

32

IN OUT

41

TAB GND

LT1085CM

SUB=SUB*_P4636

2

C13

12

22uF 10V

6.3V-20%

C9

NET_PHYSICAL_TYPE=PLANE

6.3V-20%

12

22uF

22uF

C14

12

0.1uF 16V

C15

12

R212

220-5%

12

NP

NP

+3.3V

NP

R143

R139

4.7K

12

12

NP

220

R142

R140

21

21

NP

R141

4.7K

4.7K

12

FRU_A0

FRU_A1

FRU_A2

NP

220

220

R138

21

FRU DEVICE

FRU

NP

1

A0

2

A1

36

A2 SCL

4

GND1

24C02

ROOM=BPFRU

TOP VIEW

1 8(VCC)

(GND)4

DPN: 1E161

GND2

FRU

PINOUT

VCC

SDA

8

7

FRU_PD7

5

NP

R151

5

0.1uF 16V

C74

12

PLACE C74 AS CLOSE TO

FRU.8 AS POSSIBLE

I2C_SCL_R

I2C_SDA1_R

21

220

R191

NP

12

0-5%

R192

NP

12

0-5%

I2C1_CLK_DC

I2C1_SDA_DC

3

3

1

2

ADDRESS: 1010 110x = ACh

3

3

I2C BUS DEVICES AND LDO

4

TITLE

COMPUTER

CORPORATION

AUSTIN,TEXAS

4

SCHEM, BKPLN, 1X2, PE2800

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

DWG NO.

DATE

D1392

SHEET

REV.

X02

5 OF 712/5/2003

DCBA

Page 6

ABC

D

POWER/SIGNAL CONNECTORS

1

1

PIN OUT MATCH WIRING DIAGRAM VER 1.1

SIGCONN

1

2

3

4

5

6

POCKET SHR

EXT. SOLDER TAIL

SUB=SUB*_G3247

2

PCI_RESET_N

IPMB_RST_N

ISO_IPMB_DATA

ISO_IPMB_CLK

3

1X2_RESET_N

3

3

3

R2

12

0-5%

DC_PWRGOOD

3

2

+5V

+5V

3

+12V

PWRCONN

1

2

3

4

PWR CONN

SUB=SUB*_8G518

16V 10%

10uF

1

C19

2

16V 10%

10uF

C40

21

+12V

16V 10%

10uF

1

C20

2

16V 10%

10uF

21

16V 10%

10uF

1

2

0.1uF 16V

21

C41

16V 10%

10uF

C21

0.1uF 16V

C16

0.1uF 16V

1

C18

2

21

C10

21

C11

3

ROOM=PWRCONN

PLACE NEAR POWER/PLANAR CONNECTOR (PWRCONN)

--- AVOID PLACING DECOUPLING CAPS TO CONNECTOR PINS WITH LONG TRACES (>25MILS)

--- INSTEAD, PLACE CAPS AS CLOSE TO CONNECTOR AS POSSIBLE, AND TIE THEM

DIRECTLY TO POWER PLANE WITH VERY SHORT TRACES

4

--- EACH CAP SHOULD HAVE ITS OWN POWER/GND PAIR. AVOID SHARING VIAS.

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

POWER/SIGNAL CONNECTOR

COMPUTER

CORPORATION

TITLE

AUSTIN,TEXAS

SCHEM, BKPLN, 1X2, PE2800

DWG NO.

DATE

D1392

12/5/2003 6 OF 7

SHEET

REV.

4

X02

DCBA

Page 7

ABC

D

ROOM=IMPTST

1

+5V

+12V

LYR4

1

RX

3

RY

NP*

ZDI4PINS2R

COUPON TEST

1

RX

3

RY

NP*

ZDI4PINS2R

COUPON TEST

LYR8

+

-

2

4

2

+

4

-

Z_SCSI_P_L4

Z_SCSI_N_L4

Z_SCSI_P_L8

Z_SCSI_N_L8

ZEP5

1

1

NP*

ZEP

COUPON TEST

ZEP6

1

1

NP*

ZEP

COUPON TEST

ZEP9

1

1

NP*

ZEP

COUPON TEST

ZEP10

1

1

NP*

ZEP

COUPON TEST

+5V

+12V

LYR3

1

RX

3

RY

NP*

ZDI4PINS2R

COUPON TEST

1

RX

3

RY

NP*

ZDI4PINS2R

COUPON TEST

LYR7

+

-

2

4

2

+

4

-

Z_SCSI_P_L3

Z_SCSI_N_L3

Z_SCSI_P_L7

Z_SCSI_N_L7

ZEP3

1

1

NP*

ZEP

COUPON TEST

ZEP4

1

1

NP*

ZEP

COUPON TEST

ZEP7

1

1

NP*

ZEP

COUPON TEST

ZEP8

1

1

NP*

ZEP

COUPON TEST

MH1

2

3

4

5

6

7

8

9

NP*

.145 DRILL

.330 PAD

8 GND VIAS

MH3

2

3

4

5

6

7

8

9

NP*

.145 DRILL

.330 PAD

8 GND VIAS

2

MH2

2

3

4

5

6

7

8

9

NP*

.145 DRILL

.330 PAD

8 GND VIAS

MH4

2

3

4

5

6

7

8

9

NP*

.145 DRILL

.330 PAD

8 GND VIAS

1

2

Mounting Holes

X00 SCHEMATICS REV CHANGE TRACKER

X00-01 Initial ECAD schematics release

X00-02 Change SCSI connector back to solder tail connector on 5/19/03

X00-03 Change SCSI SCA-2 connectors to DPN 10519 on 5/21/03

X00-04 On page 6, change power connector to 8G518 on 5/21/03

X00-05 On page 5, Removed LM75 footprint and added 3.3V LDO on 5/22/03

On page 4, Consolidated resistor values on 5/22/03

X00-06, changes made based on CDR on 5/27/03

On Page 3, changed ground symbol to make it consistent

On Page 5, consolidate resistor values, add decoupling cap on 3.3V LDO. Add 0ohm resistors on FRU I2C signals.

NOTES ON ROUTING FOR COUPONS:

--> HOLES TO BE ARRANGED ON 100 MIL CENTERS FOR PROBE

--> FINISHED HOLE DIAMETER = 0.029"

--> TRACES NEED TO BE AT LEAST 6" LONG, THE LONGER THE BETTER

3

--> MIRROR PLACEMENT OF HOLES SO THAT SIGNAL ROUTING IS PRIORITY

--> BRING SIGNALS TOGETHER AS SOON AS POSSIBLE AND AS SIMILARLY AS POSSIBLE

--> AVOID VIAS, PLATED HOLES, AND COPPER EDGE OF PCB BY MIN 50 MILS

--> FOLLOW SAME ROUTING CONSTRAINTS AS THAT SPECIFIED FOR THE LAYER

--> CHECK LAYOUT ONE LAYER AT A TIME, AND WITH THERMAL VIEW

X00-10, Changed 68 pin SCSI connector to through hole connector J2042 to save cost on 7/2/03

X00-11, Changed LDO to LM1085 on 7/9/03

X00-12, On page 4, changed 5VCHARGE_0 property to MIN_LINE_WIDTH=25mil to match layout. Changed on 7/24/03

X01 SCHEMATICS REV CHANGE TRACKER

NOTES ON SILKSCREEN FOR COUPONS:

--> DO SILKSCREEN BOX AND LABELING AT ONE END ONLY, EG. "A" EN

--> SILKSCREEN NEEDS TO BE LEGIBLE AND EASY TO SEE

X01-02 On page 4,Changed all Y5V 0.1uF caps 78087 to X7R caps 05735 on 8/21/03

On Page 7, corrected impedance coupon routing connection

On Page 4, change SCA-2 drive connectors to solder tail connectors DPN 2E846 on 5/27/03

X00-07, changes made based on manufacturing feedback on 5/30/03

X00-08, change SIGCONN pin out to match wiring diagram ver 1.1 on 6/4/03

X00-09, change 12V decoupling cap from 48JCT to 2832P to save cost on 6/17/03

X01-01 Removed R9 on 8/15/03

On Page 3, change DTRCONN pin out to match pin out ver 1.7 on 6/9/03

On page 5, added one 0.1uF decoupling cap on 7/2/03

General, changed VCC symbol to +5V on 7/2/03

On Page 6, Removed extra 3.3V decoupling caps on 7/2/03

On Page 4, Changed HD_PRES*_N pull up to 3.3V on 7/2/03

Change DTRCONN.C15 to GND and changed DTRCONN.A1 signal name to C2_PRES_N on 8/15/03

Change SIGCONN to G3247 to ensure proper protrusion length on 8/15/03

Removed R11 and R12 at the input of LDO on 8/15/03

Removed C111 and C114 on 8/15/03

Removed R7 on 8/15/03

On page 3,Added mechanical part formex Y2657 on 8/21/03

Power connection per SI request

VOLTAGE = XX

+5V

VOLTAGE=5

VOLTAGE=0

+12V

VOLTAGE=12

+3.3V

VOLTAGE=3.3

3

X02 SCHEMATICS REV CHANGE TRACKER

EXAMPLE PLACEMENT/ROUTING:

4

REF

REF

BUS NAME

Layer #

+

-

NOTE: IT IS NECESSARY ONLY TO INCLUDE IMPEDANCE COUPONS

ON THOSE LAYERS THAT CONTAIN SCSI BUS DIFFERENTIAL PAIRS

X02-00 Added R7, R9, R11 pull up resistor on HD_PRES2-4_N on 11/24/03

X02-01 Updated stackup on page 2 on 12/2/03

X02-01 Updated mounting holes to mh145s330 on 12/2/03

X02-02 Changed U_LDO part number to P4636 on 12/3/03

X02-02 Added VOLTAGE attribute to power nets on 12/3/03

X02-03 Added load resistor R212 on the output of LDO 12/5/03

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

COMPUTER

CORPORATION

TITLE

AUSTIN,TEXAS

SCHEM, BKPLN, 1X2, PE2800

DWG NO.

DATE

D1392

12/5/2003

SHEET

REV.

X02

7 OF 7

4

DCBA

Loading...

Loading...