Page 1

A B C

Dell Controlled Print

D

REVISIONS

Mechanical adds are on pages 4, 6, 13, 16, 35

REV

A00

DESCRIPTIONECO DATE

Production by Ross Amans164200

06/22/04

APPROVED

Randy Hemingway

Corvette 5U Riser

Part number subs on pages 10, 14, 30, 36

Programmables on pages 10 (U16), 14 (U14), and 36 (U31)

With Hot Plug PCI Express Slots

Debug parts on pages 10, 13, 27, 36

1

ROMB DDR2 DIMM

A01

A02

A03

A04

A05

A06

Spin by Ross Amans167100

166975 Spin by Ross Amans 09/08/04 Randy Hemingway

170371 New schematic for M8938 & M8871 PWAs

Changed CPLD to D-Rev (dell p/n: W8714) 10/21/04 Scott Ramsey171598

171436

177371

Added Xilinx Glitch workaround 10/29/04

Added current limit resistor on the 3.3V_RSR to the dimm SPD voltage

Page 1.

Page 2.

Page 3.

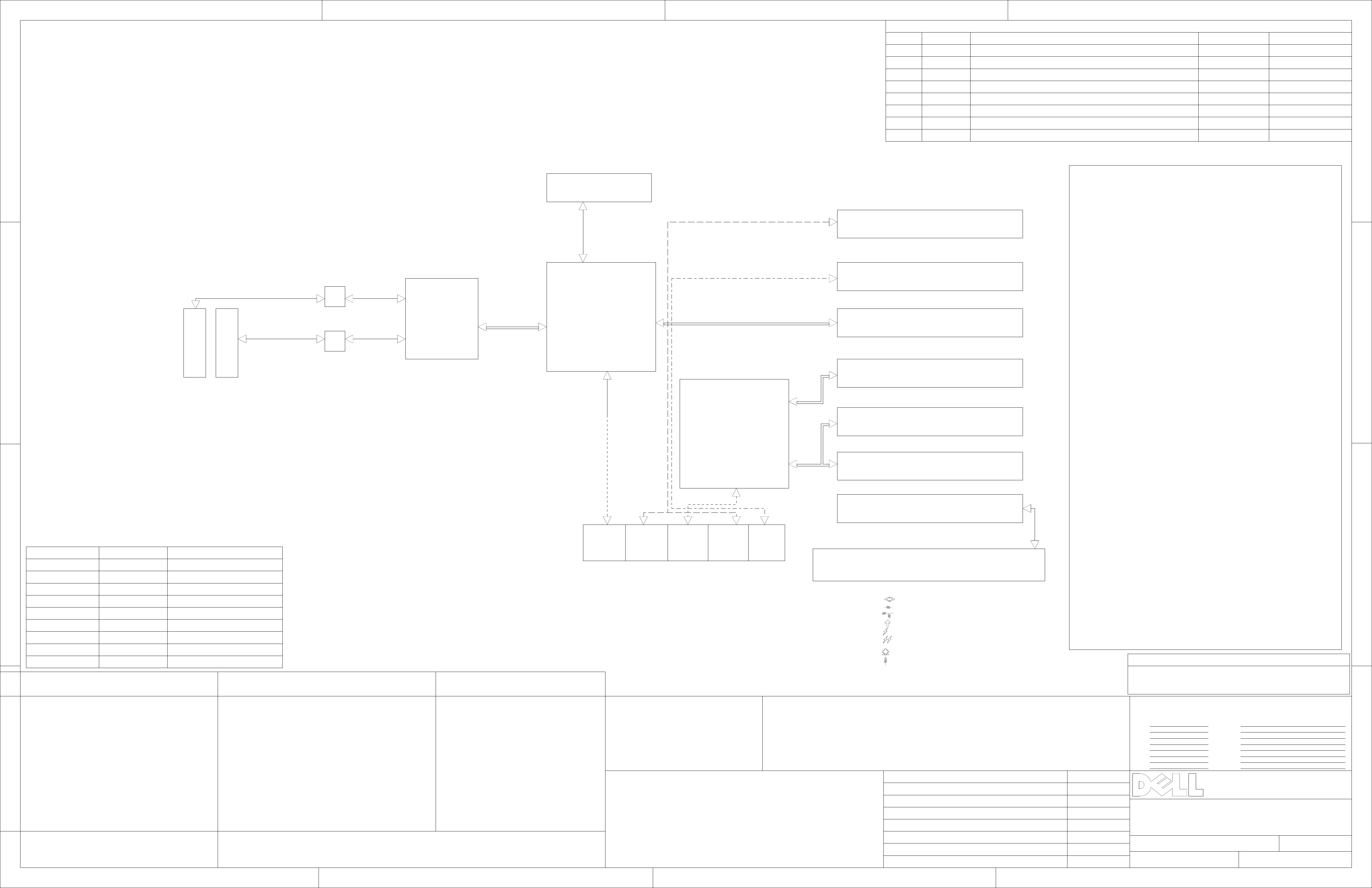

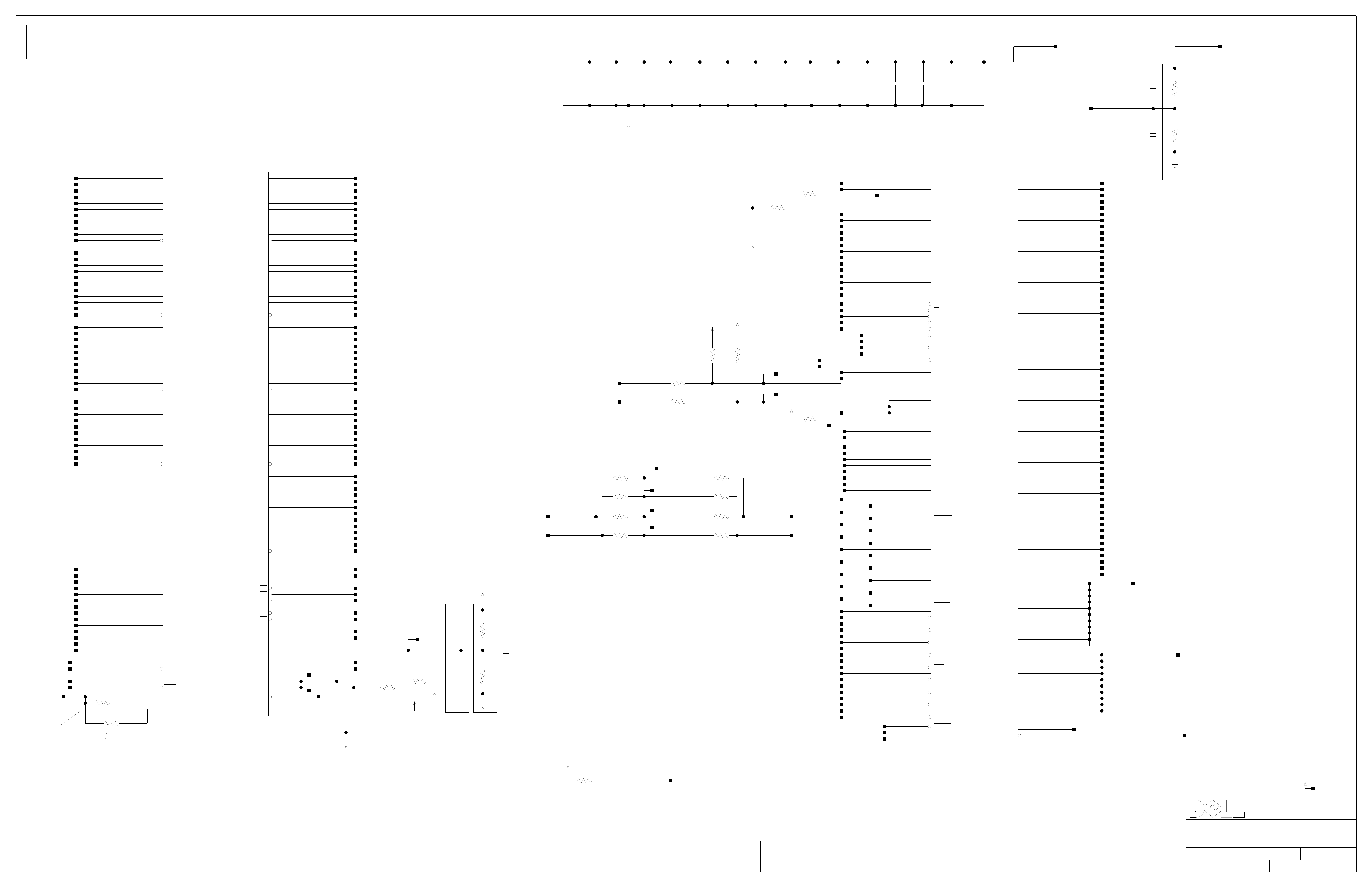

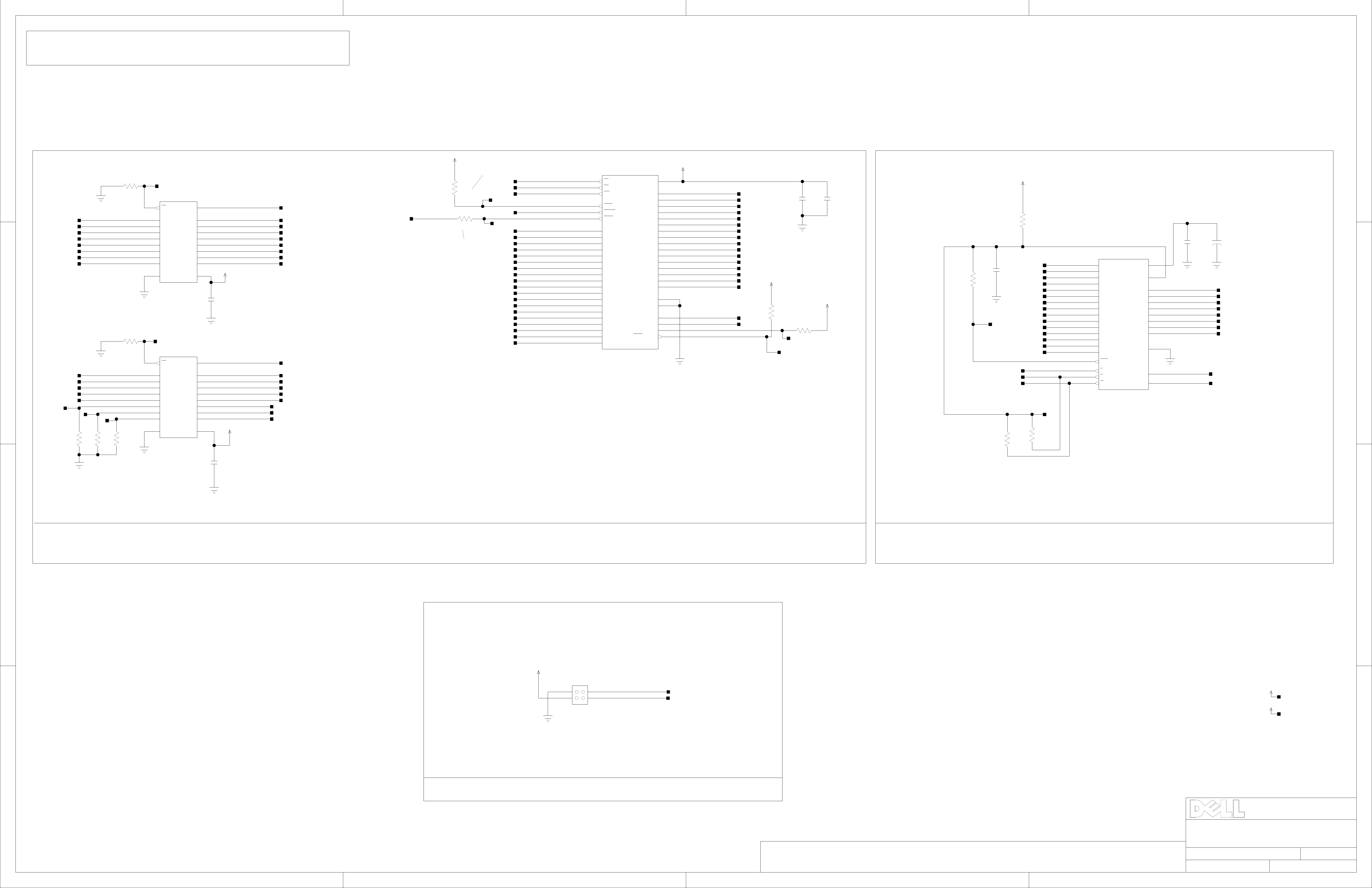

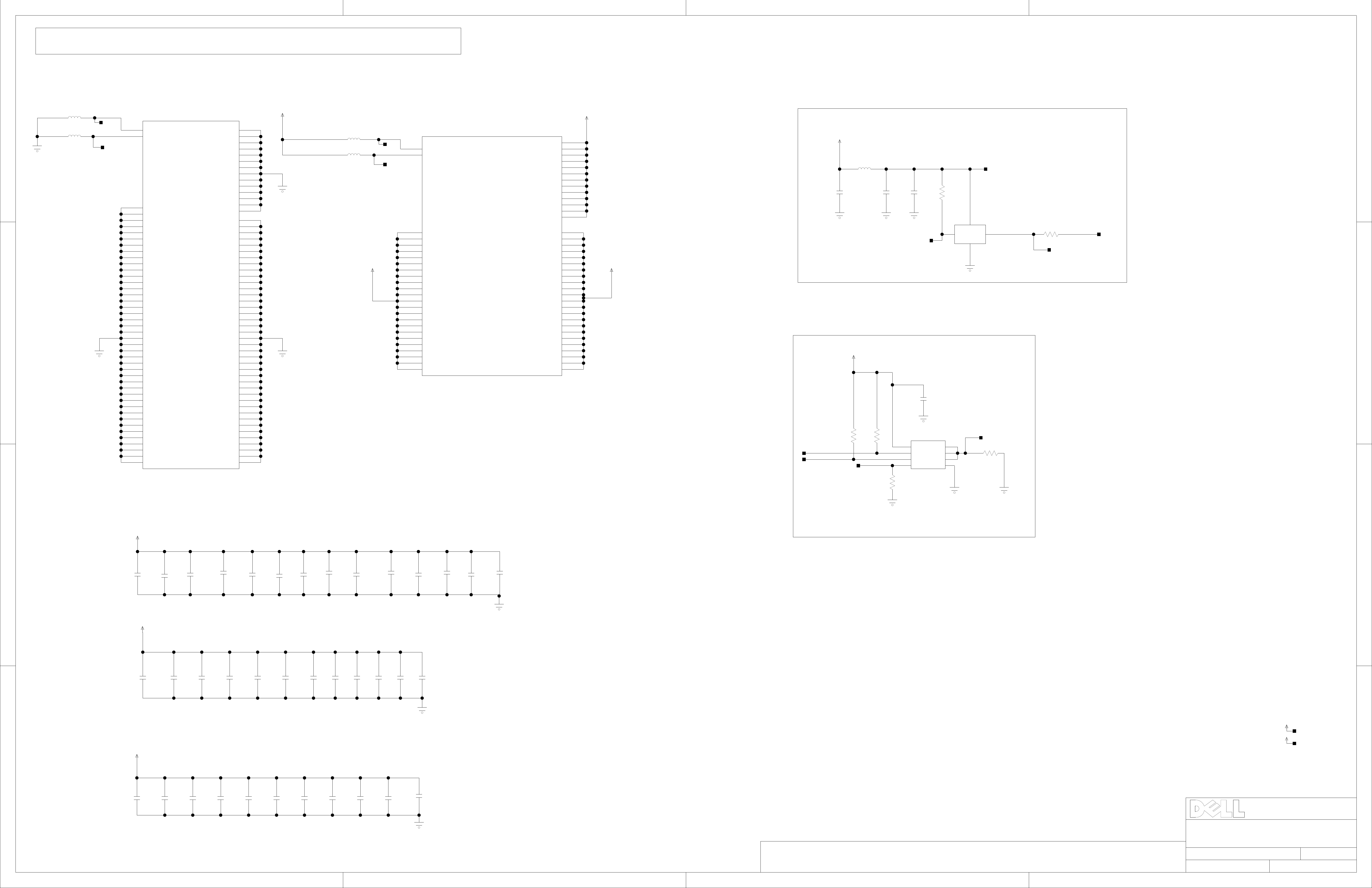

BLOCK DIAGRAM, INDEX

IDSEL/REQ/GNT/INT TABLE

Blank

08/11/04

10/10/04 Scott Ramsey

02/22/05

Randy Hemingway

Scott Ramsey

Neeraja Gedela

1

Page 4.

Page 5.

Page 6.

Page 7.

Page 8.

Page 9.

Page 10.

Page 11.

Page 12.

Page 13.

Page 14.

Page 15.

Page 16.

Page 17.

Page 18.

SCSI B (U320)

DDR2 400

PCI EXPRESS x8

x8 SLOT

PCI EXPRESS x4

x8 SLOT

C

HOT PLUG

B lo

Chassis Slot 7

Chassis Slot 6

PCIE Slot 7

PCIE Slot 6

DOBSON

Differential

Terminators

2

SCSI A (U320)

LSI1030

(SCSI)

CHNL A

A_PCIX

80332

500MHz

CHNL B

PCIX1

PCIX 1.0 (133MHz)

64bit, 3.3V

PCI Slot 5

Chassis Slot 5

6X25 HS3 CONNECTOR TO PLANAR

GOLD FINGERS TO PLANAR, SCSI CONNS TO BP

DOBSON MEMORY INTERFACE

DOBSON PCIX INTERFACE

DOBSON PCI EXPRESS

DOBSON GND POWER BATT

DOBSON FLASH NVRAM

ROMB BATT CNTRL CKT

ROMB MISC

SCSI LSI 1030

SCSI LSI 1030

SCSI TERM

PXH PCI INTERFACE

PXH POWER

PXH PCI EXPRESS, GND, PXH DECOUPLING

2

A Lo

SCSI B

SCSI A

x4 PCI Express

CHNL A

PCIX3

PCIX 1.0 (133 MHz)

64bit, 3.3V

PCI Slot 4

Chassis Slot 4

Page 19.

Page 20.

Page 21.

Page 22.

5V 32BIT LEGACY PCI SLOT 1

5V 32BIT LEGACY PCI SLOT LEVEL SHIFTERS

PCIX SLOT 2

PCIX SLOT 3

Page 23.

Page 24.

PXH

PCIX 1.0 (133 MHz)

64bit, 3.3V

PCIX 1.0 (133 MHz)

64bit, 3.3V

LEGACY PCI

32b/33M 5V

Part

Intel Part #

Dell P/N

x4 PCI Express

ACA

Lo Hi

Lo

A hi

I6700

C

Hi

CHNL B

PCIX2

B

Lo

3

Lindenhurst

Tumwater

Dobson

PXH

PXH-D

LSI 1030

PXH, Dobson Heatsink, Clip F2085, Y1978

/ LSI 1020 / D4195 C0Y3556 C0

E7520, NQ82001

E7525, NQE7525MCH R1806 C2

IOP332, NQ80332

I6700, NQ80000

???, NQ80001

53C1030, 62036A1

R7626 C4, W6123 C2, N1312 C2, U5928 C1

M6627 C1, F5290 C0

Y5218 C1

C5604 C0

NEW PWAs:

M8871 - A00 PWB w/ Xilinx Rework

M8938 - A01 PWB w/ Xilinx Rework

6x25 HS3 Connector

T8384 - New PWA which has PWB A02 (includes FET for Xilinx workaround)

202 pin Gold Fingers Card Edge

Input/Output

Series resistor

Series resistor with pull-down

Defaults high

VAux rail

VBat rail

Chassis Slot 3

Chassis Slot 2

Chassis Slot 1

PCI Slot 3

PCI Slot 2

PCI Slot 1

Page 25.

Page 26.

Page 27.

Page 28.

Page 29.

Page 30.

Page 31.

Page 32.

Page 33.

Page 34.

Page 35.

Page 36.

Page 37.

Page 38.

Page 39.

Page 40.

Page 41.

Page 42.

Page 43.

Page 44.

Page 45.

PCIX SLOT 4

PCIX SLOT 5

PCI EXPRESS SLOT 6

PCI EXPRESS SLOT 7

DEBUG HEADERS

LINEARS, INVERTOR

DC2DCs

INTRUSION/FRU/TEMP SENSOR

PCI EXPRESS HOT PLUG SWITCHES, LEDS

PCI EXPRESS HOT PLUG LOGIC

PCI EXPRESS HOT PLUG LOGIC

Virtual points for PCI-X shared slot simulation, Spare Gates

COUPONS, HARDWARE

CPLD

POWERGOOD BLOCK DIAGRAM

I2C ISOLATION, I2C BLOCK DIAGRAM, I2C ADDRESS CHART

PME BLOCK DIAGRAM

RESET BLOCK DIAGRAM

POWER DISTRIBUTION BLOCK DIAGRAM

CLOCK BLOCK DIAGRAM

INT BLOCK DIAGRAM

JTAG BLOCK DIAGRAM

HOT PLUG BLOCK DIAGRAM

3

8C288LSI SCSI Heatsink

ROMB Battery G3399

Clear

A1, A2

XLBOM Build Options

1U, Production

2U/5U Production

0A0 RedRed

1

GC654 - New PWA - Changes to limit the current to the ROMB SPD

PWB/Silk ColorPWB Color Chipset Rev

x00White

PWA:

PWB:

GC654

DC876

x01WhiteRed

SCHEM:

F1314

Corvette 5U RISER

Clear White x01

Green

B0, C0, C1

4

1U, Debug 2

2U/5U Debug 3

Clear White x02

Green Yellow x03

WhiteGreen

x04

Green White a00

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

ASSY DWG:

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY

OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN

WHOLE OR IN PART AND MUST BE RETURNED TO DELL INC.

UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE

OF THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED

FOR SUCH USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE

LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

HC375

PROPRIETARY NOTE

OD/Output

Pullup

2-24-2005_14:21

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

Ross Amans

Ross Amans

Randy Hemingway

Randy Hemingway

21 June, 2004

21 June, 2004

21 June, 2004

21 June, 2004

XLBOM Build option table

0 Production Build

9 Prototype Build

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

TITLE

DWG NO.

164200 06/22/04

166975 09/08/04

170371 10/10/04

171436

177371

SCHEM, RSR, PE2800, SV

SUB=POP0

SUB=POP9

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

INC.

F1314

DATE

2/23/2005

08/11/04167100

10/29/04

02/22/05

4

ROUND ROCK,TEXAS

REV.

A06-00

SHEET

1 OF 45

DCBA

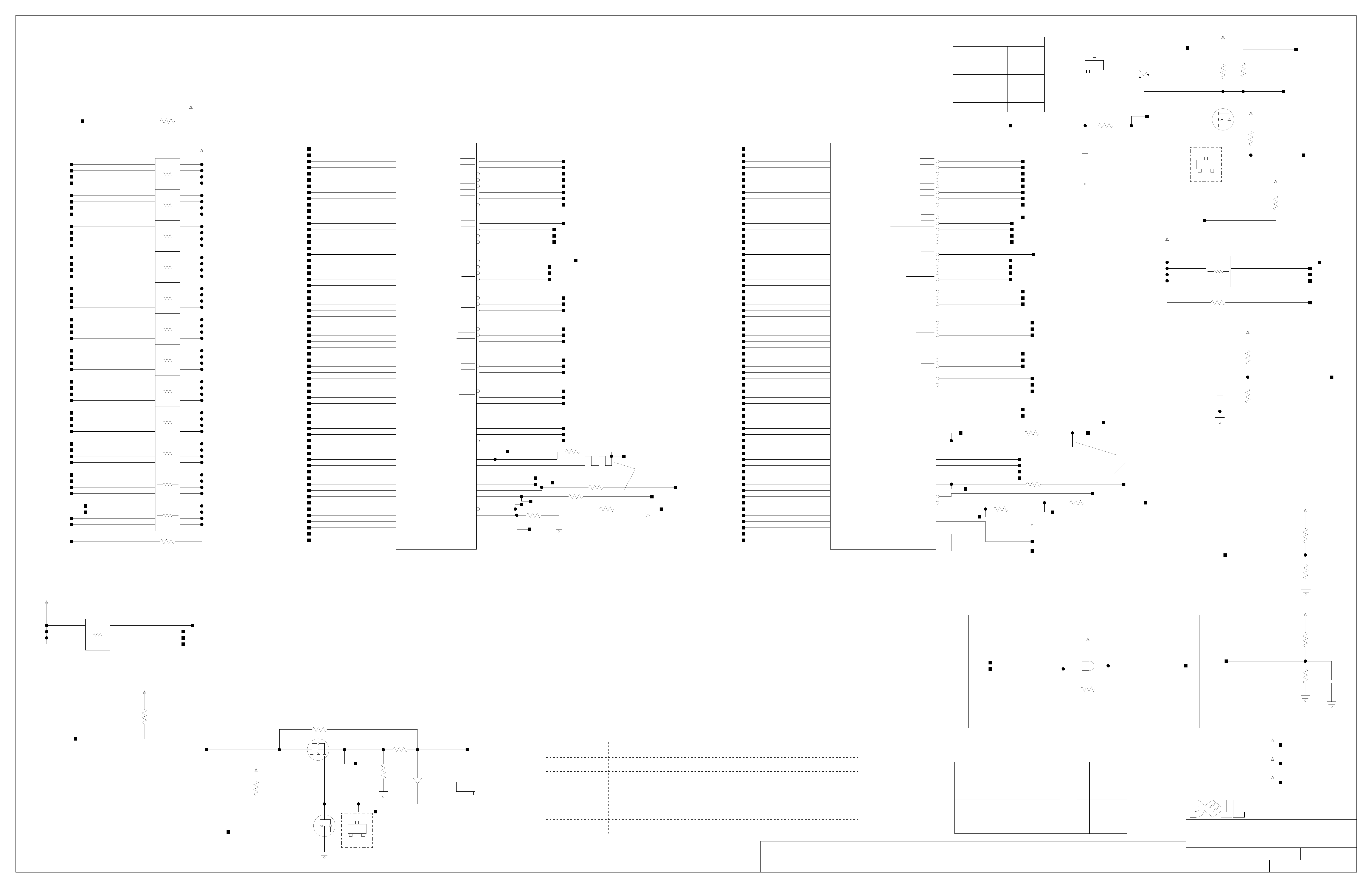

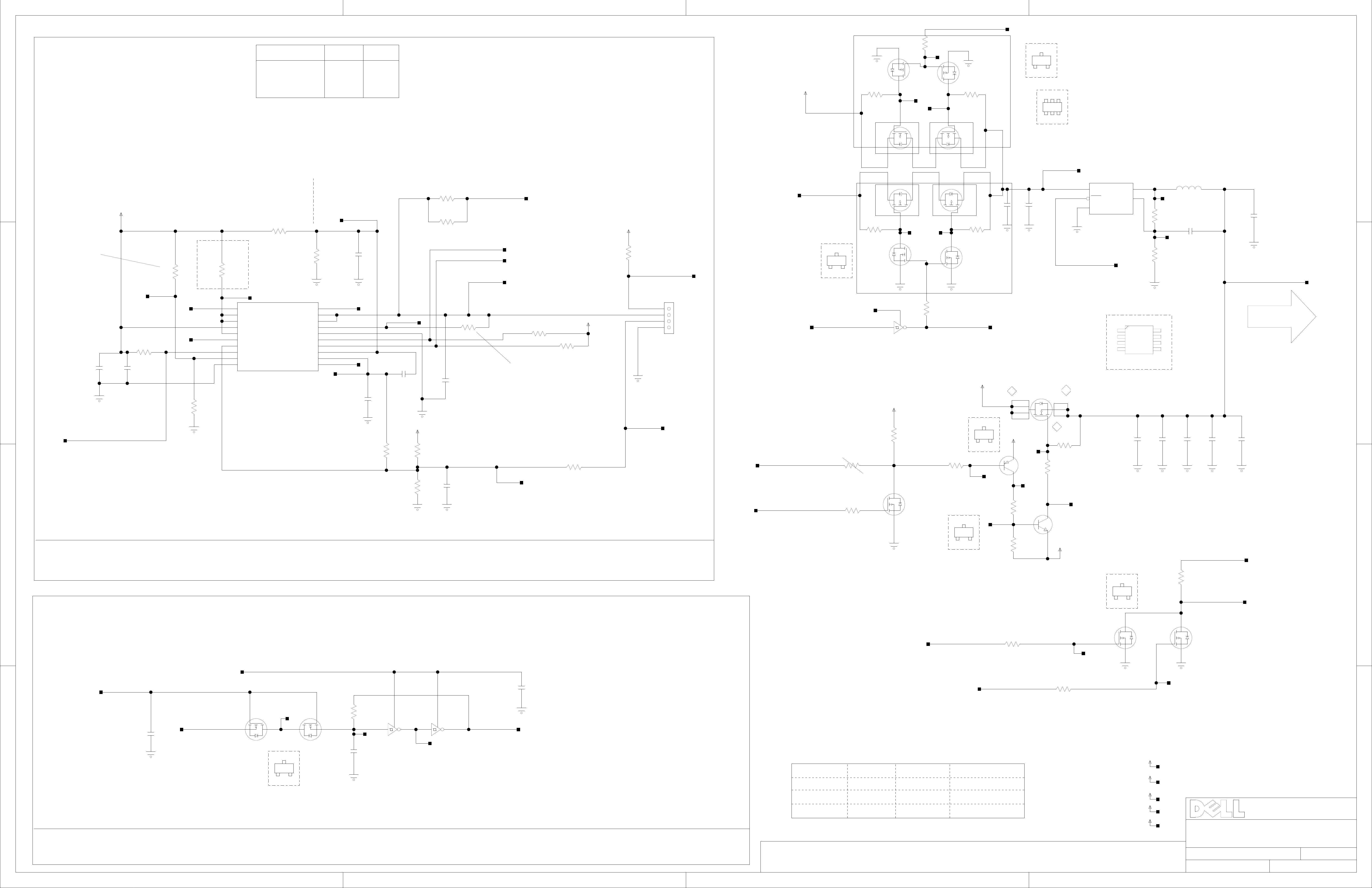

Page 2

Corvette 5U RISER PCI DEVICE CHART

B D

CA

Device#

Function#

Device

Device#

IDSEL IRQD#IRQB# IRQC# REQ#IRQA#

GNT#

IRQA IRQB IRQC IRQD

Used On

1

Bus / Default Bus Number

BUS 0X09h

--

5U PCIX Slot 5

IOP DEVICE B

AD27

INT

IOPIOPIOPIOPIOP

XINT7XINT6XINT5

XINT4

REQ0#

IOP

GNT0#

1U, 2U, 5U

5U PG 8,24

A

B

C

IDSEL XINT

16, 20, 24, 28

17, 21, 25, 29

18, 22, 26, 30

0, 4

1, 5

2, 6

1

A.Lo B / 3

19, 23, 27, 31

3, 7

IOP

D

IOP IOP IOP IOP

1U

BUS 0X0Bh

--

(IOP SLOT_1)

(AD28)

XINT4

XINT5XINT7XINT6

(REQ1#)

(GNT1#)

A.Lo B

Dobson IOP

(fixed)

(fixed)

IOP

BUS 0X0Ah

A.Lo / 2

0,1

IOP DEVICE E

AD30

(internal)

XINT2

(internal)

INT0

(Debug)

1U, 2U, 5U

U320 SCSI

BUS 0X08h

0,1

IOP DEVICE 5

AD21

XINT1XINT2

REQ0#

GNT0#

1U, 2U, 5U

A.Lo A / 2

PXHPXHPXHPXHPXHPXH

BUS 0X04h

2

A.Hi A

--

5U PCIX Slot 4

AD20

A_IRQ8A_IRQ11A_IRQ10

A_IRQ9

GNT0#REQ0#

2U, 5U

2

BUS 0X05h

A.Hi B

BUS 0X06h

A.Hi B

BUS 0X07h

ICH (planar)

--

--

--

5U PCIX Slot 3

5U PCIX Slot 2

5U PCI Slot 1

5V 32b

AD19

AD18

AD17

PXH PXH PXH PXH PXH PXH

A_IRQ7A_IRQ6A_IRQ5

A_IRQ4

REQ1# GNT1#

PXH PXH PXH PXH PXH PXH

GNT2#REQ2#

PIRQA

ICH (planar)ICH (planar)

PIRQB

A_IRQ2A_IRQ31A_IRQ0

A_IRQ3

ICH ICH ICH ICH

PIRQA

PIRQB

REQ?# GNT?#

2U, 5U

2U, 5U

5U

BUS 0X01h

--

Ethernet A

PXH (planar)PXH (planar)

4

AD23

A_IRQ0

PXHPXHPXHPXH

Planar

GNT?#REQ?#

B.Hi A

PXH (planar)PXH (planar)

PXH PXH PXH PXH

BUS 0X02h

3

B.Hi B

--

Ethernet B

4

AD24

BUS 0X0Eh

A_IRQ1

GNT?#REQ?#

ICH (planar)ICH (planar)

ICHICHICHICH

Planar

3

Planar

ICH (planar)

--

Video

AD29

INT? INT? INT? INT? REQ?# GNT?#

BUS 0X0Ch

ICH (planar)

BUS 0X0Dh

ICH (planar)

--

--

Rac

Agilent SP2

RAC - IDE

Debug Slot

AD21

AD22

AD19

ICH (planar)ICH (planar)

ICH ICH ICH ICH

INT? INT? INT? INT? REQ?# GNT?#

ICH (planar)ICH (planar)

ICHICHICHICH

GNT?#REQ?#INT?INT?INT?INT?

Planar

Planar

B.LoMCH (planar)

MCH (planar)

MCH (planar)

4 4

B.Lo

C

MCH (planar)

MCH (planar)

MCH (planar)

MCH (planar)

B.Lo

A.hi

A.Lo

B.hi

Slot 6

Slot 7C

6Slot 7MCH (planar)

PXH (Planar) PXH (Planar)

PXH

Dobson

Slot 6

4

3

2

5

N/A

N/A

in the IOP, AD16-25 goes public or private as a group, not individuallyA.8 B key: Express Lane.width PCIX buss

MCH

MCH

MCH5

MCH

PXH

Dobson

MCH

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

2-23-2005_9:36

TITLE

DWG NO.

DATE

INC.

SCHEM, RSR, PE2800, SV

F1314

2/23/2005

SHEET

ROUND ROCK,TEXAS

REV.

2 OF 45

A06-00

A B

DC

Page 3

B D

CA

1

1

2

2

This Page Left Blank Intentionally

3

3

4 4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

INC.

TITLE

SCHEM, RSR, PE2800, SV

DWG NO.

F1314

DATE

2/23/2005

ROUND ROCK,TEXAS

REV.

A06-00

SHEET

3 OF 45

DC

A B

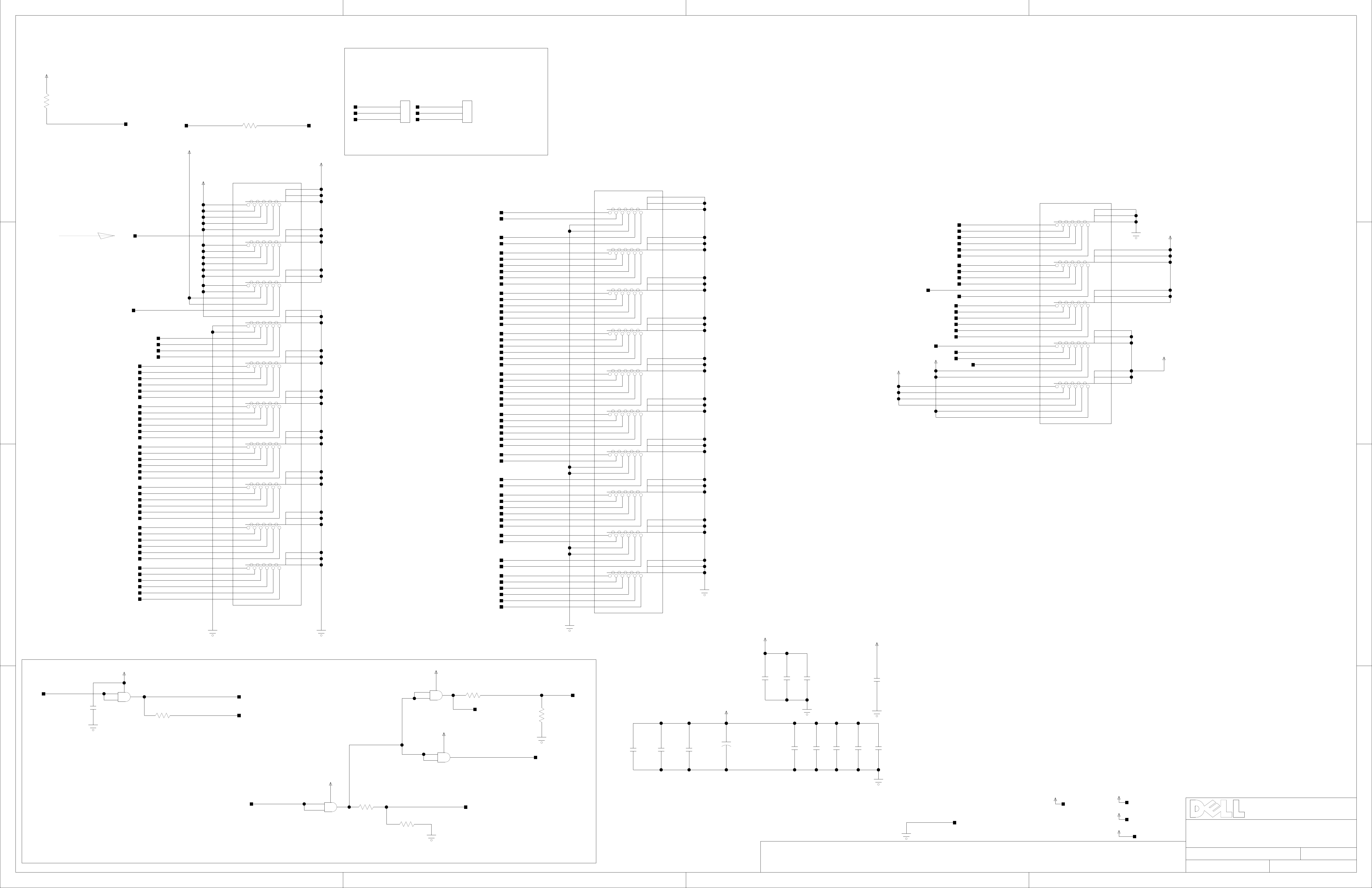

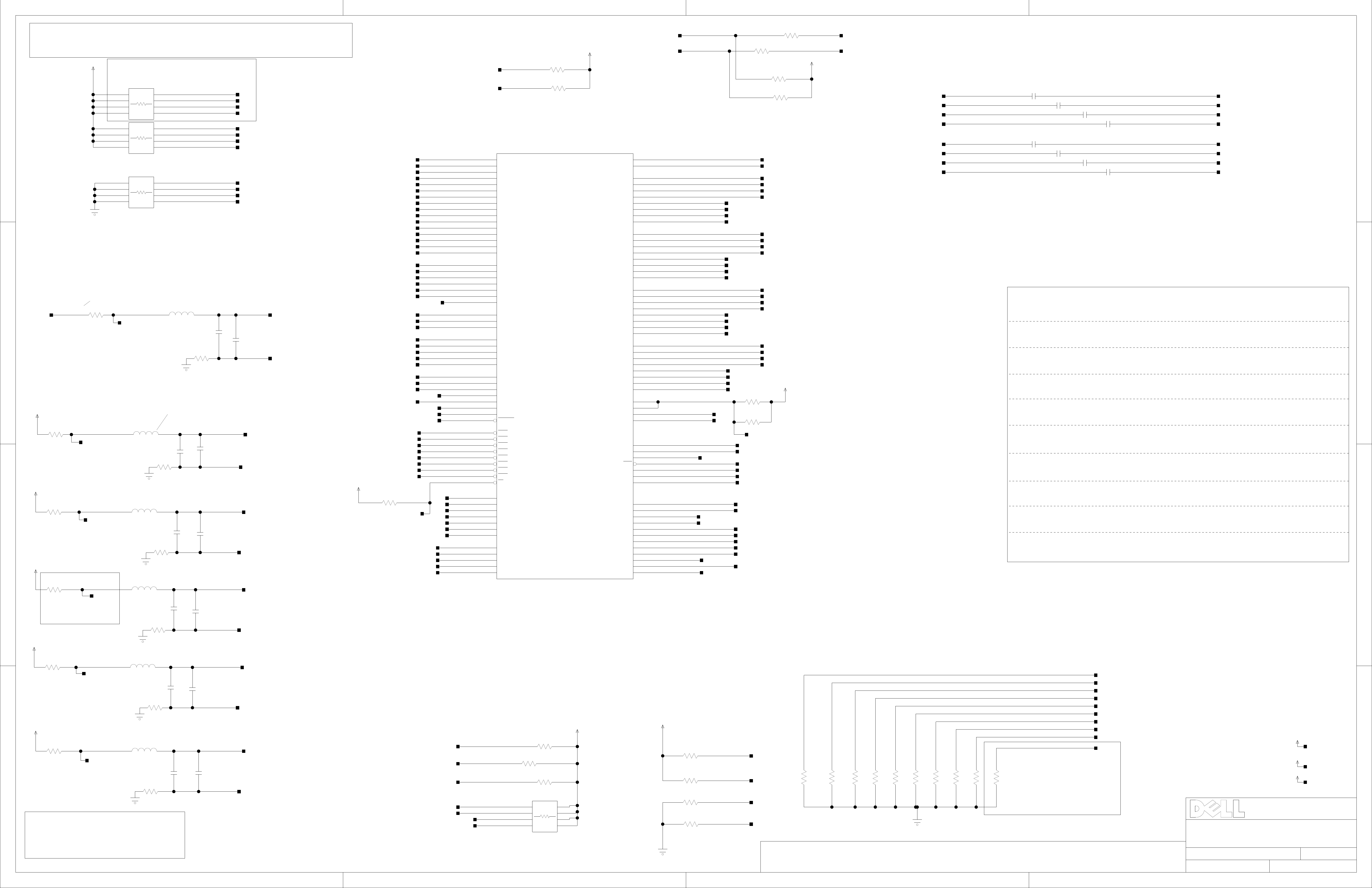

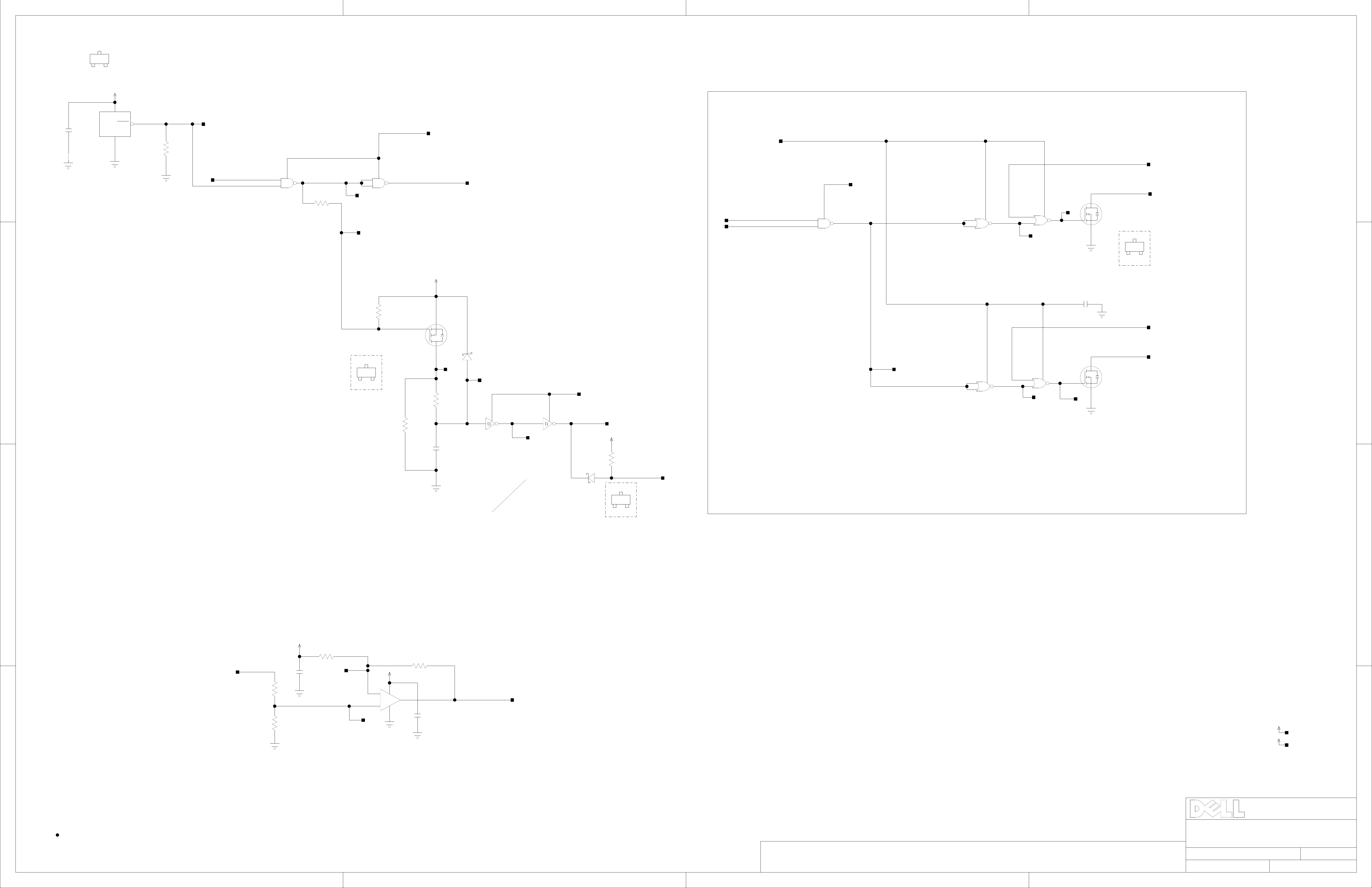

Page 4

B D

CA

ADD1=ADD*_0585R_RIVET

ADD2=ADD*_0585R_RIVET

ADD3=ADD*_0585R_RIVET

ADD1=ADD*_T6977_SCREW_GUIDE

ADD2=ADD*_T6977_SCREW_GUIDE

2-24-2005_11:43

ADD4=ADD*_F2670_GASKET

these should be floating

+3.3V

CONN2_GUIDE

MH1

NC1

MH2

R335

1 2

0-5%

NC_CONN1_GUIDE_MH1

NC_CONN1_GUIDE_MH2

CONN1_GUIDE

MH1

NC1

MH2

NC_CONN2_GUIDE_MH1

NC_CONN2_GUIDE_MH2

1

1

3P3V_RISER_SENSE

R365

4

RISER_PRES1_N

4

1 2

RISER_PRES_N

5

0-5%

+3.3V_AUX

NC_CONN1_GUIDE_MH3

CONN,. FEMALE GUIDE BLOCK

UNIVERSAL PWR MOD

MH3

NC2

NC3

NC_CONN2_GUIDE_MH3

CONN,. FEMALE GUIDE BLOCK

NC2

MH3

NC3

UNIVERSAL PWR MOD

PLANAR TO RISER TO PLANAR HS3

ROOM=RISER_CONN

+3.3V

+3.3V

A1

A1

B1

B1

C1

C1

D1

D1

E1

E1

F1

RISER_PRES1_N

4

This is other part of RISER_PRES_N

3P3V_RISER_SENSE

4

2

TD3 == TDO

TD2 == TDI

CK_100M_DOBSON_P

8

CK_100M_DOBSON_N

8

CK_100M_EXP_SPARE_P

27

CK_100M_EXP_SPARE_N

27

CK_100M_PXH_P

16

CK_100M_PXH_N

16

8,27

8,27

8,27

8,27

8,27

8,27

8,27

8,27

26

26

26

26

26

26

26

26

26

26

26

26

26

26

EXP_A_UP_7N

EXP_A_UP_7P

EXP_A_UP_3N

EXP_A_UP_3P

EXP_A_UP_6N

EXP_A_UP_6P

EXP_A_UP_2N

EXP_A_UP_2P

EXP_A_UP_5P

EXP_A_UP_5N

EXP_A_UP_1N

EXP_A_UP_1P

EXP_A_UP_4P

EXP_A_UP_4N

EXP_A_UP_0N

EXP_A_UP_0P

EXP_C_UP_5P

EXP_C_UP_5N

EXP_C_UP_4P

EXP_C_UP_4N

EXP_C_UP_6P

EXP_C_UP_6N

EXP_C_UP_7P

EXP_C_UP_7N

EXP_C_DN_5P

EXP_C_DN_5N

EXP_C_DN_4P

EXP_C_DN_4N

EXP_C_DN_6P

EXP_C_DN_6N

18,27

18,27

18,27

18,27

18,27

18,27

18,27

18,27

3

36

36

36

36

CPLD_TCK

CPLD_TD3

CPLD_TD2

CPLD_TMS

F1

A2

B2

C2

D2

E2

F2

A3

B3

C3

D3

E3

F3

A4

B4

C4

D4

E4

F4

A5

B5

C5

D5

E5

F5

A6

B6

C6

D6

E6

F6

A7

B7

C7

D7

E7

F7

A8

B8

C8

D8

E8

F8

A9

B9

C9

D9

E9

F9

A10

B10

C10

D10

E10

F10

A2

B2

C2

D2

E2

F2

A3

B3

C3

D3

E3

F3

A4

B4

C4

D4

E4

F4

A5

B5

C5

D5

E5

F5

A6

B6

C6

D6

E6

F6

A7

B7

C7

D7

E7

F7

A8

B8

C8

D8

E8

F8

A9

B9

C9

D9

E9

F9

A10

B10

C10

D10

E10

F10

6 ROW RECEPTACLE ASSEMBLY

RISER_CONN1

Z-PACK HS3

G1

H1

J1

G2

H2

J2

G3

H3

J3

G4

H4

J4

G5

H5

J5

G6

H6

J6

G7

H7

J7

G8

H8

J8

G9

H9

J9

G10

H10

J10

G1

H1

J1

G2

H2

J2

G3

H3

J3

G4

H4

J4

G5

H5

J5

G6

H6

J6

G7

H7

J7

G8

H8

J8

G9

H9

J9

G10

H10

J10

16,27

16,27

8,27

8,27

16,27

16,27

8,27

8,27

8,27

8,27

16,27

16,27

8,27

8,27

16,27

16,27

CK_100M_SLOT7_P

26

CK_100M_SLOT7_N

26

EXP_C_DN_7N

26

EXP_C_DN_7P

26

EXP_A_DN_7N

EXP_A_DN_7P

EXP_A_DN_3N

EXP_A_DN_3P

EXP_A_DN_6N

EXP_A_DN_6P

EXP_A_DN_2N

EXP_A_DN_2P

EXP_A_DN_1P

EXP_A_DN_1N

EXP_A_DN_5N

EXP_A_DN_5P

EXP_A_DN_0N

EXP_A_DN_0P

EXP_A_DN_4N

EXP_A_DN_4P

EXP_C_DN_0P

26

EXP_C_DN_0N

26

EXP_C_DN_3N

26

EXP_C_DN_3P

26

EXP_C_DN_2P

26

EXP_C_DN_2N

26

EXP_C_DN_1N

26

EXP_C_DN_1P

26

EXP_C_UP_1N

26

EXP_C_UP_1P

26

EXP_C_UP_3P

26

EXP_C_UP_3N

26

EXP_C_UP_0N

26

EXP_C_UP_0P

26

CK_100M_SLOT6_P

25

CK_100M_SLOT6_N

25

SLOT6

EXP_C_UP_2N

26

EXP_C_UP_2P

26

EXP_B_DN_1P

25

EXP_B_DN_1N

25

EXP_B_DN_3N

25

EXP_B_DN_3P

25

EXP_B_DN_2P

25

EXP_B_DN_2N

25

EXP_B_DN_0P

25

EXP_B_DN_0N

25

EXP_B_UP_3P

25

EXP_B_UP_3N

25

EXP_B_UP_2P

25

EXP_B_UP_2N

25

EXP_B_UP_1P

25

EXP_B_UP_1N

25

EXP_B_UP_0P

25

EXP_B_UP_0N

25

SLOT7

RISER_CONN2

A1

A1

B1

B1

C1

C1

D1

D1

E1

E1

F1

F1

A2

A2

B2

B2

C2

C2

D2

D2

E2

E2

F2

F2

A3

A3

B3

B3

C3

C3

D3

D3

E3

E3

F3

F3

A4

A4

B4

B4

C4

C4

D4

D4

E4

E4

F4

F4

A5

A5

B5

B5

C5

C5

D5

D5

E5

E5

F5

F5

A6

A6

B6

B6

C6

C6

D6

D6

E6

E6

F6

F6

A7

A7

B7

B7

C7

C7

D7

D7

E7

E7

F7

F7

A8

A8

B8

B8

C8

C8

D8

D8

E8

E8

F8

F8

A9

A9

B9

B9

C9

C9

D9

D9

E9

E9

F9

F9

A10

A10

B10

B10

C10

C10

D10

D10

E10

E10

F10

F10

6 ROW RECEPTACLE ASSEMBLY

G1

H1

J1

G2

H2

J2

G3

H3

J3

G4

H4

J4

G5

H5

J5

G6

H6

J6

G7

H7

J7

G8

H8

J8

G9

H9

J9

G10

H10

J10

G1

H1

J1

G2

H2

J2

G3

H3

J3

G4

H4

J4

G5

H5

J5

G6

H6

J6

G7

H7

J7

G8

H8

J8

G9

H9

J9

G10

H10

J10

RISER_PRES_N for 1U

+5V

16,31

16,31

6,8

6,8

36

36

4

31

4

7,16,31

NC_HS3_E2

7,16

SHIFTY_RISER_CLK

36

SHIFTY_RISER_LATCH

36

SHIFTY_RISER_DATA_DN

36

SHIFTY_RISER_DATA_UP

36

INTRUSION_COVER_N

30

LI_BAT_PACK_P

11

NC_1U_RISER_PRSNT_N

I2C_SEG3_VAUX_SDA

30

+12V

I2C_SEG3_VAUX_SCL

30

ICH_SEG0_SCL

ICH_SEG0_SDA

ICH_SEG3_SCL

ICH_SEG3_SDA

SYSTEM_PWRGOOD_RISER

RISER_PWRGOOD

3P3VAUX_PWRGOOD_RISER

MCH_EXPHPINTR_N

PCI_RST_RISER_N

RISER_EXP_PME_N

RISER_PCI_PME_N

NC_RISER_CONN_D24

RISER_CONN3

A1

A1

B1

B1

C1

C1

D1

D1

E1

E1

F1

F1

A2

A2

B2

B2

C2

C2

D2

D2

E2

E2

F2

F2

A3

A3

B3

B3

C3

C3

D3

D3

E3

E3

F3

F3

A4

A4

B4

B4

C4

C4

D4

D4

E4

E4

F4

F4

A5

A5

B5

B5

C5

C5

D5

D5

E5

E5

F5

F5

6 ROW RECPTACLE ASSEMBLY

Z-PACK HS3

G1

H1

J1

G2

H2

J2

G3

H3

J3

G4

H4

J4

G5

H5

J5

G1

H1

J1

G2

H2

J2

G3

H3

J3

G4

H4

J4

G5

H5

J5

+12V

2

+5V

3

Z-PACK HS3

PCI_RST_RISER_N

4

C589

1 2

9

10

0.1uF 16V

+3.3V_AUX

148U10

74VHC08

R455

1 2

22-5%

BUFFERS

CPLD p36

PCI_RST_RISER_BUF_N

Slot1 p20

PCI_RST_RISER_BUF3_N

Pull up 2.2k on p20

+3.3V

+5V

+3.3V_AUX

21

ROMB p11

14

12

36

13

U10

11

74VHC08

20

R492

1 2

22-5%

I_U10_P11

stub

3P3VAUX_PWRGOOD_ROMB_BUF2

R723

4.7K

11

+12V

C69

21

C70

0.1uF 16V

21

C92

0.1uF 16V

0.1uF 16V

21

C299

0.1uF 16V

1 2

I_3P3VAUX_PWRGD_RISER

+3.3V_AUX

14

4

5

U10

C66

1

2

22uF

16V 20%

1

C67

2

6

3P3VAUX_PWRGOOD_CPLD_BUF

36

22uF

C62

16V 20%

1

2

22uF

16V 20%

16V-20%

270uF

1

+

C534

2

21

C344

21

C354

0.1uF 16V

21

C510

0.1uF 16V

21

C511

0.1uF 16V

21

C522

0.1uF 16V

0.1uF 16V

74VHC08

4 4

3P3VAUX_PWRGOOD_RISER

4

+3.3V_AUX

143U10

1

2

74VHC08

R447

22-5%

21

3P3VAUX_PWRGOOD_ROMB_BUF

Pull up 4.7k on p11

R449

ROMB p11

11

1 2

4.7K

VHC schmitt trigger inputs family avoids issues

CPLD p36

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

VOLTAGE=0

+3.3V

5,19,31-33,36

VOLTAGE=3.3

RATSNEST_SCHEDULE=MIN_TREE

29

+3.3V_AUX

+5V

+12V

RATSNEST_SCHEDULE=MIN_TREE

VOLTAGE=3.3

7-3W,8-2X,11-2U,16-2U,19-3W

21-3W,22-3W,23-3W,24-3W,30-2W

31-3W,32-2T,33-3V,36-3W

RATSNEST_SCHEDULE=MIN_TREE

VOLTAGE=5

5,19,20,31

RATSNEST_SCHEDULE=MIN_TREE

VOLTAGE=12

5,7,19,21-24,28,29,33

TITLE

DWG NO.

DATE

INC.

SCHEM, RSR, PE2800, SV

F1314

2/23/2005

ROUND ROCK,TEXAS

REV.

A06-00

SHEET

4 OF 45

DC

A B

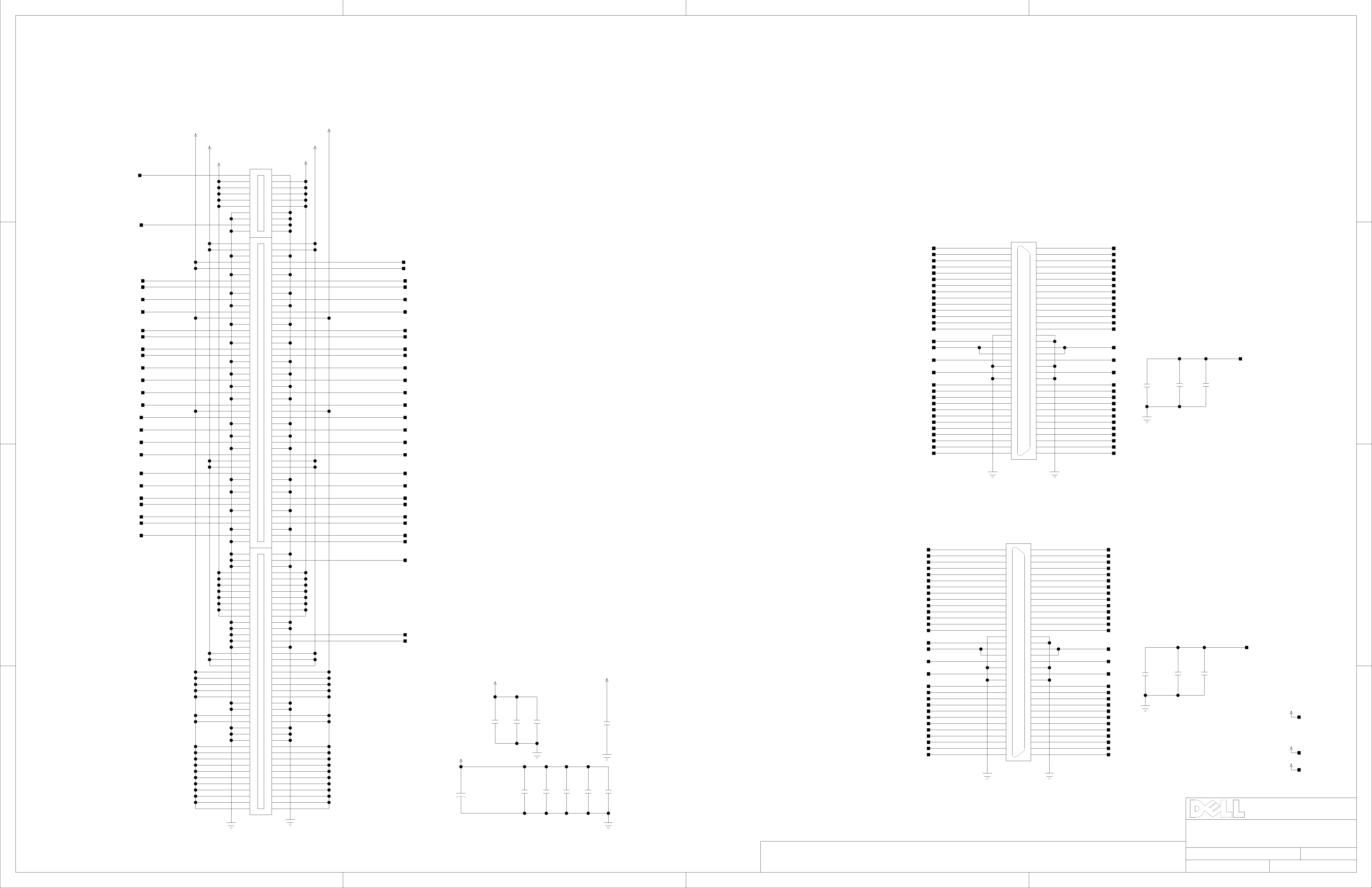

Page 5

B D

GOLD FINGERS TO PLANAR. PCI CONN ON PLANAR. NO GOLD FINGERS ON 1U RISER

CA

1

1

CONN2_PLNR

+3.3V

We could shorten RISER_PRES_N pad for last mate, first break

RISER_PRES_N

4

CK_33M_SLOT1

19

+3.3V

+5V

+12V

Side B Side A

NO_PKG

CONN2_PLNR

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

+5V

+12V

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

SCSI Connectors to Backplane

These SCSI connectors support external devices

SCSIA

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

1

2

3

4

5

6

7

8

9

SCSIA

RCPT

SCSIB

RCPT

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

SCSI_A_SD12_N

SCSI_A_SD13_N

SCSI_A_SD14_N

SCSI_A_SD15_N

SCSI_A_SDP1_N

SCSI_A_SD0_N

SCSI_A_SD1_N

SCSI_A_SD2_N

SCSI_A_SD3_N

SCSI_A_SD4_N

SCSI_A_SD5_N

SCSI_A_SD6_N

SCSI_A_SD7_N

SCSI_A_SDP0_N

SCSI_TRMPWR

NC_A_53

SCSI_A_SATN_N

SCSI_A_SBSY_N

SCSI_A_SACK_N

SCSI_A_SRST_N

SCSI_A_SMSG_N

SCSI_A_SSEL_N

SCSI_A_SCD_N

SCSI_A_SREQ_N

SCSI_A_SIO_N

SCSI_A_SD8_N

SCSI_A_SD9_N

SCSI_A_SD10_N

SCSI_A_SD11_N

SCSI_B_SD12_N

SCSI_B_SD13_N

SCSI_B_SD14_N

SCSI_B_SD15_N

SCSI_B_SDP1_N

SCSI_B_SD0_N

SCSI_B_SD1_N

SCSI_B_SD2_N

SCSI_B_SD3_N

SCSI_B_SD4_N

SCSI_B_SD5_N

SCSI_B_SD6_N

SCSI_B_SD7_N

SCSI_B_SDP0_N

SCSI_TRMPWR

NC_B_53

SCSI_B_SATN_N

SCSI_B_SBSY_N

SCSI_B_SACK_N

SCSI_B_SRST_N

SCSI_B_SMSG_N

SCSI_B_SSEL_N

SCSI_B_SCD_N

SCSI_B_SREQ_N

SCSI_B_SIO_N

SCSI_B_SD8_N

SCSI_B_SD9_N

SCSI_B_SD10_N

SCSI_B_SD11_N

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

5,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

5,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

NP

C576

X

NP

21

C575

X

SCSI_TRMPWR

NP

470pF

1 2

50V-10%

X

2 1

C990

NP

4.7uF

16V-10%

NP

C991

X

NP

1 2

0.1uF 16V

SCSI_TRMPWR

5,15

5,15

21

C993

470pF

50V-10%

X

C992

4.7uF

2 1

X

16V-10%

0.1uF 16V

+3.3V

4,19,31-33,36

+5V

4,19,20,31

+12V

4,7,19,21-24,28,29,33

B11 A11

B12

B13

B14

B15

B16

20

20

PCI0_AD31

PCI0_AD29

B17

B18

B19

20

PCI0_AD27

B20

B21

20

PCI0_AD25

B22

B23

B24

PCI0_AD23

2

20

20

PCI0_AD21

B25

B26

B27

20

20

PCI0_AD20

PCI0_AD19

B28

B29

B30

20

PCI0_AD17

B31

B32

PCI0_CBE2_N

20

B33

B34

20

PCI0_IRDY_N

B35

B36

PCI0_DEVSEL_N

20

B37

B38

PCI0_LOCK_N

20

B39

B40

PCI0_PERR_N

20

B41

B42

PCI0_SERR_N

20

B43

B44

PCI0_CBE1_N

20

B45

B46

B47

20

PCI0_AD14

B48

B49

20

PCI0_AD12

B50

B51

20

20

PCI0_AD10

PCI0_AD8

B52

B53

B54

20

20

PCI0_AD7

PCI0_AD5

B55

X

B56

B57

20

PCI0_AD3

B58

B59

B60 A60

3

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

B83

B84

B85

B86

B87

B88

B89

B90

B91

B93

B94

B95

4 4

B96

B97

B98

B99

B100

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

A83

A84

A85

A86

A87

A88

A89

A90

A91

A92B92

A93

A94

A95

A96

A97

A98

A99

A100

ICH_PIRQ_SLOT_AC_N

ICH_PIRQ_SLOT_BD_N

PCI0_AD30

PCI0_AD28

PCI0_AD26

PCI0_CBE3_N

PCI0_AD24

PCI0_AD22

PCI0_AD18

PCI0_AD16

PCI0_FRAME_N

PCI0_TRDY_N

PCI0_STOP_N

PCI0_PAR

PCI0_AD15

PCI0_AD13

PCI0_AD11

PCI0_AD9

PCI0_CBE0_N

PCI0_AD6

PCI0_AD4

PCI0_AD2

PCI0_AD0

PCI0_AD1

PCI0_REQ_SLOT_N

PCI0_GNT_SLOT_N

PCIL_5V_PME_N

SLOT6_PWRGD

SLOT7_PWRGD

13,15

13,15

19

19

20

20

20

20

20

20

20

20

20

20

20

20

20

20

20

20

20

20

20

20

20

20

20

20

19

32

32

+3.3V

21

C523

21

C524

0.1uF 16V

21

C525

0.1uF 16V

0.1uF 16V

+5V

21

C528

0.1uF 16V

+12V

16V-20%

270uF

1

+

C535

21

C529

2

21

C530

0.1uF 16V

21

C531

0.1uF 16V

21

C532

0.1uF 16V

21

C533

0.1uF 16V

0.1uF 16V

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

5,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

13,15

SCSI_A_SD12_P

SCSI_A_SD13_P

SCSI_A_SD14_P

SCSI_A_SD15_P

SCSI_A_SDP1_P

SCSI_A_SD0_P

SCSI_A_SD1_P

SCSI_A_SD2_P

SCSI_A_SD3_P

SCSI_A_SD4_P

SCSI_A_SD5_P

SCSI_A_SD6_P

SCSI_A_SD7_P

SCSI_A_SDP0_P

SCSI_A_DIFFSENSE

SCSI_TRMPWR

5,15

NC_A_19

SCSI_A_SATN_P

SCSI_A_SBSY_P

SCSI_A_SACK_P

SCSI_A_SRST_P

SCSI_A_SMSG_P

SCSI_A_SSEL_P

SCSI_A_SCD_P

SCSI_A_SREQ_P

SCSI_A_SIO_P

SCSI_A_SD8_P

SCSI_A_SD9_P

SCSI_A_SD10_P

SCSI_A_SD11_P

SCSI_B_SD12_P

SCSI_B_SD13_P

SCSI_B_SD14_P

SCSI_B_SD15_P

SCSI_B_SDP1_P

SCSI_B_SD0_P

SCSI_B_SD1_P

SCSI_B_SD2_P

SCSI_B_SD3_P

SCSI_B_SD4_P

SCSI_B_SD5_P

SCSI_B_SD6_P

SCSI_B_SD7_P

SCSI_B_SDP0_P

SCSI_B_DIFFSENSE

SCSI_TRMPWR

NC_B_19

SCSI_B_SATN_P

SCSI_B_SBSY_P

SCSI_B_SACK_P

SCSI_B_SRST_P

SCSI_B_SMSG_P

SCSI_B_SSEL_P

SCSI_B_SCD_P

SCSI_B_SREQ_P

SCSI_B_SIO_P

SCSI_B_SD8_P

SCSI_B_SD9_P

SCSI_B_SD10_P

SCSI_B_SD11_P

SCSIB

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

B101 A101

INC.

ROUND ROCK,TEXAS

202MCA PCI EDG

FOXCONN LOW PROFILE

TITLE

2-24-2005_11:43

2

3

A B

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DWG NO.

DATE

DC

SCHEM, RSR, PE2800, SV

F1314

2/23/2005

REV.

A06-00

SHEET

5 OF 45

Page 6

B D

CA

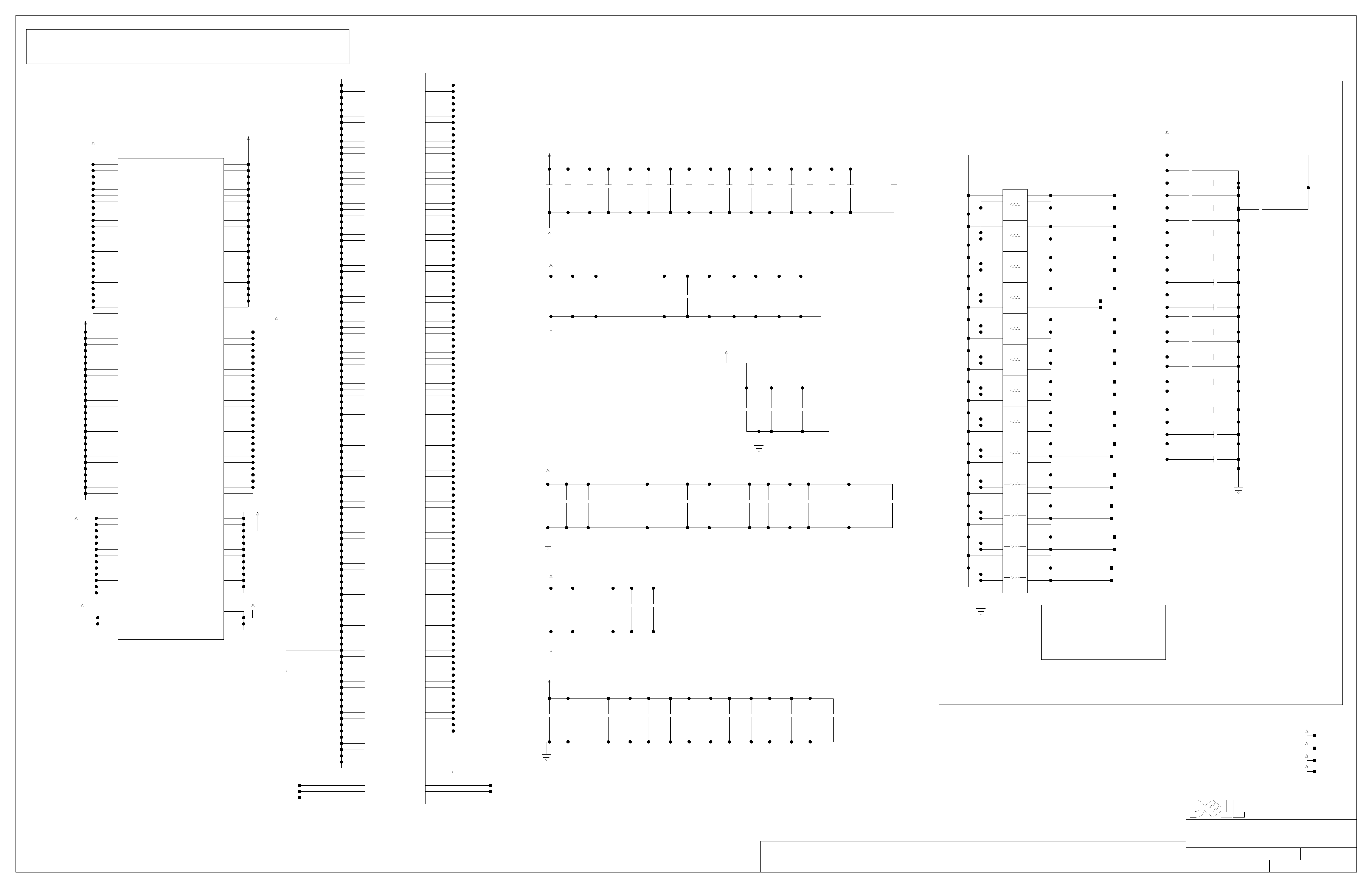

DOBSON MEMORY INTERFACE

Put one 22 uF cap at each end of DIMM

VBAT_RAID

6,11,12

VBAT_RAID

6,11,12

MUST BE 10% CAPS

C272

1

2

22uF 10V

C274

1 2

0.1uF 16V

C536

1 2

0.1uF 16V

C291

1 2

0.1uF 16V

C275

1 2

0.1uF 16V

C276

1 2

0.1uF 16V

C277

1 2

0.1uF 16V

C283

1 2

0.1uF 16V

C278

1 2

0.1uF 16V

C296

1 2

0.1uF 16V

C279

1 2

0.1uF 16V

C280

1 2

0.1uF 16V

C281

1 2

0.1uF 16V

C282

1 2

0.1uF 16V

C295

1 2

0.1uF 16V

0.1uF 16V 0.1uF 16V

C30

2 1

R142

1.5K-1%1.5K-1%

1 2

1uF 6.3V

Dobson Operating Limits

Supplies

2

C273

1

22uF 10V

3.3V == 3.0 to 3.6V, +- 10%

ROMB_DIMM_VREF

1

1.8V == 1.7 to 1.9V, +- 5%

6

C264

12

1

1.5V == 1.425 to 1.575V, +- 5%

1.35V == 1.282 to 1.418V, +- 5%

2 1

C25

PLL == 1.425 to 1.575V, +- 5%

DDR Vref == .49*Vcc1.1, .51*Vcc1.8, +- 2%

R144

1 2

BG Vref == 2.375 to 2.625V, +- 5%

U_DOBSON

RAID_DIMM

DDR_SD0_0

6

DDR_SD0_1

6

DDR_SD0_2

6

DDR_SD0_3

6

DDR_SD0_4

6

DDR_SD0_5

6

DDR_SD0_6

6

DDR_SD0_7

6

DDR_DM0

6

DDR_DQS0_P

6

DDR_DQS0_N

6

DDR_SD1_0

6

DDR_SD1_1

6

DDR_SD1_2

6

DDR_SD1_3

6

DDR_SD1_4

6

DDR_SD1_5

6

DDR_SD1_6

6

DDR_SD1_7

6

DDR_DM1

6

DDR_DQS1_P

6

DDR_DQS1_N

6

DDR_SD2_0

6

DDR_SD2_1

2

6

DDR_SD2_2

6

DDR_SD2_3

6

DDR_SD2_4

6

DDR_SD2_5

6

DDR_SD2_6

6

DDR_SD2_7

6

DDR_DM2

6

DDR_DQS2_P

6

DDR_DQS2_N

6

DDR_SD3_0

6

DDR_SD3_1

6

DDR_SD3_2

6

DDR_SD3_3

6

DDR_SD3_4

6

DDR_SD3_5

6

DDR_SD3_6

6

DDR_SD3_7

6

DDR_DM3

6

DDR_DQS3_P

6

DDR_DQS3_N

6

AD5

AD4

AF3

AG2

AD2

AD1

AF1

AF2

AE1

AE4

AE3

AE7

AF6

AJ7

AG7

AD8

AE6

AH6

AJ6

AG5

AJ5

AJ4

AG8

AJ8

AG10

AD11

AH7

AF8

AD10

AE10

AJ9

AF9

AE9

AH12

AJ12

AE13

AD14

AJ11

AF12

AF14

AG14

AJ13

AG13

AH13

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DM0

DQS0

DQS0

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DM1

DQS1

DQS1

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DM2

DQS2

DQS2

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DM3

DQS3

DQS3

MEMORY INTERFACE

DQS_N8

M_CK0

M_CK0

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DM4

DQS4

DQS4

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DM5

DQS5

DQS5

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DM6

DQS6

DQS6

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DM7

DQS7

DQS7

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DM8

DQS8

AF18

AE18

AG20

AJ21

AJ18

AH18

AJ20

AH20

AJ19

AF19

AG19

AJ22

AG22

AG23

AF23

AH21

AF21

AJ24

AH24

AE21

AH23

AJ23

AF24

AF25

AG26

AG27

AE24

AE23

AH26

AH27

AG25

AJ26

AJ25

AF28

AE26

AD29

AD28

AG28

AF27

AD25

AD26

AE27

AE29

AF29

AE15

AF15

AD17

AC16

AC15

AC14

AD16

AE17

AH15

AG16

AF16

AJ16

AJ17

DDR_SD4_0

DDR_SD4_1

DDR_SD4_2

DDR_SD4_3

DDR_SD4_4

DDR_SD4_5

DDR_SD4_6

DDR_SD4_7

DDR_DM4

DDR_DQS4_P

DDR_DQS4_N

DDR_SD5_0

DDR_SD5_1

DDR_SD5_2

DDR_SD5_3

DDR_SD5_4

DDR_SD5_5

DDR_SD5_6

DDR_SD5_7

DDR_DM5

DDR_DQS5_P

DDR_DQS5_N

DDR_SD6_0

DDR_SD6_1

DDR_SD6_2

DDR_SD6_3

DDR_SD6_4

DDR_SD6_5

DDR_SD6_6

DDR_SD6_7

DDR_DM6

DDR_DQS6_P

DDR_DQS6_N

DDR_SD7_0

DDR_SD7_1

DDR_SD7_2

DDR_SD7_3

DDR_SD7_4

DDR_SD7_5

DDR_SD7_6

DDR_SD7_7

DDR_DM7

DDR_DQS7_P

DDR_DQS7_N

DDR_SD8_0

DDR_SD8_1

DDR_SD8_2

DDR_SD8_3

DDR_SD8_4

DDR_SD8_5

DDR_SD8_6

DDR_SD8_7

DDR_DM8

DDR_DQS8_P

DDR_DQS8_N

CK_DDR_MCLK0_P_R

CK_DDR_MCLK0_N_R

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

R10

1 2

1K-5%

R9

1 2

1K-5%

+3.3V_RSR

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

CK_DDR_MCLK0_P_R

6

CK_DDR_MCLK0_N_R

6

NP

NP

ICH_SEG3_SDA

4,8

ICH_SEG3_SCL

4,8

R693

1 2

0-5%

R692

1 2

0-5%

R65

1 2

0-5%

R53

1 2

0-5%

Place close to Dobson

1 2

1 2

stub

I_CK_DDR_MCLK0_P_R2

X

2.8" long

stub

I_CK_DDR_MCLK0_N_R1

X

stub

stub

I_CK_DDR_MCLK0_N_R2

I_CK_DDR_MCLK0_P_R1

4" long

R220

0-5%

R219

0-5%

Pull-up at planar

+3.3V_RSR

NP

R179

X

1 2

R691

NP

1 2

0-5%

R690

NP

1 2

0-5%

R689

1 2

0-5%

R688

1 2

0-5%

NP

8.2K-5%

X

X

R180

X

1 2

8.2K-5%

DIMM_SDA

DIMM_SCL

CK_DDR_MCLK0_P

CK_DDR_MCLK0_N

stub

stub

+3.3V_RSR

6

6

R1003

220

CK_DDR_MCLK0_N

6

CK_DDR_MCLK0_P

6

6,9,12

6,9,12

21

6

DDR_BA1

6,9

DDR_BA0

6,9

DDR_MA15

DDR_MA14

DDR_MA13

6,9

DDR_MA12

6,9

DDR_MA11

6,9

DDR_MA10

6,9

DDR_MA9

6,9

DDR_MA8

6,9

DDR_MA7

6,9

DDR_MA6

6,9

DDR_MA5

6,9

DDR_MA4

6,9

DDR_MA3

6,9

DDR_MA2

6,9

DDR_MA1

6,9

DDR_MA0

6,9

DDR_CS1_N

6,9

DDR_CS0_N

6,9

DDR_RAS_N

6,9

DDR_CAS_N

6,9

DDR_WE_N

6,9

DDR_CKE1

DDR_CKE0

DIMM1A_SA

6

ROMB_DIMM_VREF

DDR_ODT1

6,9

DDR_ODT0

6,9

DDR_SD8_7

6

DDR_SD8_6

6

DDR_SD8_5

6

DDR_SD8_4

6

DDR_SD8_3

6

DDR_SD8_2

6

DDR_SD8_1

6

DDR_SD8_0

6

DDR_DM8

6

DDR_DM7

6

DDR_DM6

6

DDR_DM5

6

DDR_DM4

6

NC_DDR_DIMM_BA2

NC_CK_DDR_MCLK2_N

NC_CK_DDR_MCLK2_P

NC_CK_DDR_MCLK1_N

NC_CK_DDR_MCLK1_P

NC_DDR_DIMM_165

NC_DDR_DIMM_233

NC_DDR_DIMM_224

NC_DDR_DIMM_212

NC_DDR_DIMM_203

190

71

54

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

76

193

192

74

73

221

220

138

137

186

185

171

52

119

120

101

240

239

238

1

77

195

168

167

162

161

49

48

43

42

164

165

232

233

223

224

211

212

202

203

BA1

BA0

A16/BA2

A15

A14

A13

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

S1

S0

RAS

CAS

WE

CK2

CK2

CK1

CK1

CK0

CK0

CKE1

CKE0

SDA

SCL

SA2

SA1

SA0

VDDSPD

VREF

ODT1

ODT0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

DM8/DQS17/NC

DQS17/NC

DM7/DQS16

DQS16/NC

DM6/DQS15

DQS15/NC

DM5/DQS14

DQS14/NC

DM4/DQS13

DQS13/NC

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

236

235

230

229

117

116

111

110

227

226

218

217

108

107

99

98

215

214

209

208

96

95

90

89

206

205

200

199

87

86

81

80

159

158

153

152

40

39

34

33

150

149

144

143

31

30

25

24

141

140

132

131

22

21

13

12

129

128

123

122

10

DDR_SD7_7

DDR_SD7_6

DDR_SD7_5

DDR_SD7_4

DDR_SD7_3

DDR_SD7_2

DDR_SD7_1

DDR_SD7_0

DDR_SD6_7

DDR_SD6_6

DDR_SD6_5

DDR_SD6_4

DDR_SD6_3

DDR_SD6_2

DDR_SD6_1

DDR_SD6_0

DDR_SD5_7

DDR_SD5_6

DDR_SD5_5

DDR_SD5_4

DDR_SD5_3

DDR_SD5_2

DDR_SD5_1

DDR_SD5_0

DDR_SD4_7

DDR_SD4_6

DDR_SD4_5

DDR_SD4_4

DDR_SD4_3

DDR_SD4_2

DDR_SD4_1

DDR_SD4_0

DDR_SD3_7

DDR_SD3_6

DDR_SD3_5

DDR_SD3_4

DDR_SD3_3

DDR_SD3_2

DDR_SD3_1

DDR_SD3_0

DDR_SD2_7

DDR_SD2_6

DDR_SD2_5

DDR_SD2_4

DDR_SD2_3

DDR_SD2_2

DDR_SD2_1

DDR_SD2_0

DDR_SD1_7

DDR_SD1_6

DDR_SD1_5

DDR_SD1_4

DDR_SD1_3

DDR_SD1_2

DDR_SD1_1

DDR_SD1_0

DDR_SD0_7

DDR_SD0_6

DDR_SD0_5

DDR_SD0_4

DDR_SD0_3

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

MUST BE 1%

2

3

3

DQ2

DQ1

DQ0

NC

9

4

3

197

189

187

184

178

172

69

67

64

59

53

194

191

181

175

170

78

75

72

62

56

51

19

18

NC_DDR_DIMM_19

DDR_SD0_2

DDR_SD0_1

DDR_SD0_0

6

6

6

VBAT_RAID

6,11,12

DDR_DIMM_RST_N

VBAT_RAID

6,11,12

36

DDR_MA0

6,9

DDR_MA1

6,9

DDR_MA2

6,9

DDR_MA3

6,9

DDR_MA4

6,9

DDR_MA5

6,9

DDR_MA6

6,9

DDR_MA7

6,9

DDR_MA8

6,9

DDR_MA9

6,9

DDR_MA10

6,9

DDR_MA11

6,9

DDR_MA12

6,9

DDR_MA13

6,9

NC_CK_DDR_MCLK1_P_R

NC_CK_DDR_MCLK1_N_R

NC_CK_DDR_MCLK2_P_R

NC_CK_DDR_MCLK2_N_R

DDRCRES0

stub

DDR-2 - use 976 ohm

MUST BE 1%

R167 can be 825 or 976 ohms 1%

R167

1 2

976-1%

R242

1 2

287-1%

DDR-2 - use 285 ohm

DDRSLWCRES

DDRIMPCRES

AC13

MA0

AE12

MA1

AC12

MA2

AF11

MA3

AG11

MA4

AH10

MA5

AH9

MA6

AD7

MA7

AJ10

MA8

AC9

MA9

AC18

MA10

AC8

MA11

AF5

MA12

AD22

MA13

AJ14

M_CK1

AJ15

M_CK1

AH17

M_CK2

AG17

M_CK2

AC27

DDRCRES0

AC28

DDRSLWCRES

AC29

DDRIMPCRES

INTEL DOBSON IOP MEM

POWER_DRAW=P3.3V@1.2A

POWER_DRAW=P1.8V@0.9A

POWER_DRAW=P1.5V@6.4A

POWER_DRAW=P1.35V@0.5A

VER C0

HETERO 1 OF 6

SUB=SUB*_M6627

BA0

BA1

CAS

RAS

WE

CS0

CS1

CKE0

CKE1

DDR_VREF

ODT0

ODT1

DDRRES1

DDRRES2

M_RST

AD18

AD13

AC21

AC19

AD20

AE20

AD23

AG4

AH4

AC1

AC22

AB20

AB28

AB29

AH3

stub

NC_DDR_RST_N

DDR_BA0

DDR_BA1

DDR_CAS_N

DDR_RAS_N

DDR_WE_N

DDR_CS0_N

DDR_CS1_N

DDR_CKE0

DDR_CKE1

DDR_ODT0

DDR_ODT1

0.1uF 16V

C416

2 1

C399

6,9

6,9

6,9

6,9

6,9

6,9

6,9

6,9,12

6,9,12

6,9

6,9

DDR_RES1

DDR_RES2

0.1uF 16V

12

DDR_DOBSON_VREF

R140

40.2-0.5%

MUST BE 10% CAPS

stub

R141

1 2

21

40.2-0.5%

+1.8V

MUST BE 0.5%

C18

0.1uF 16V0.1uF 16V

C36

+1.8V

2 1

R145

1.5K-1%1.5K-1%

1 2

2 1

R143

1 2

MUST BE 1% RES

1uF 6.3V

12

C263

DDR_DM3

6

DDR_DM2

6

DDR_DM1

6

DDR_DM0

6

DDR_DQS8_P

6

DDR_DQS8_N

6

DDR_DQS7_P

6

DDR_DQS7_N

6

DDR_DQS6_P

6

DDR_DQS6_N

6

DDR_DQS5_P

6

DDR_DQS5_N

6

DDR_DQS4_P

6

DDR_DQS4_N

6

DDR_DQS3_P

6

DDR_DQS3_N

6

DDR_DQS2_P

6

DDR_DQS2_N

6

DDR_DQS1_P

6

DDR_DQS1_N

6

DDR_DQS0_P

6

DDR_DQS0_N

6

NC_DDR_DIMM_156

NC_DDR_DIMM_147

NC_DDR_DIMM_135

NC_DDR_DIMM_126

NC_DDR_DIMM_ERR

NC_DDR_DIMM_PAR

NC_DDR_DIMM_TEST

155

DM3/DQS12

156

DQS12/NC

146

DM2/DQS11

147

DQS11/NC

134

DM1/DQS10

135

DQS10/NC

125

DM0/DQS9

126

DQS9/NC

46

DQS8/NC

45

DQS8/NC

114

DQS7

113

DQS7

105

DQS6

104

DQS6

93

DQS5

92

DQS5

84

DQS4

83

DQS4

37

DQS3

36

DQS3

28

DQS2

27

DQS2

16

DQS1

15

DQS1

7

DQS0

6

DQS0

55

ERR_OUT

68

PAR_IN

102

TEST

POWER_DRAW=P1.8V@7.5A

VDD10

VDD9

VDD8

VDD7

VDD6

VDD5

VDD4

VDD3

VDD2

VDD1

VDD0

VDDQ10

VDDQ9

VDDQ8

VDDQ7

VDDQ6

VDDQ5

VDDQ4

VDDQ3

VDDQ2

VDDQ1

VDDQ0

RESET

240 PIN DDR II DIMM

ADD=ADD*_D2614_HEATSINK_DOBSON

4 4

M6627 = C1 Dobson

+3.3V_RSR

4.7K

R339

12

DIMM1A_SA

ROOM = ROMB_DIMM

6

+3.3V_RSR

7-18,21-24,28,29

F5290 = C0 Dobson

INC.

ROUND ROCK,TEXAS

REV.

A06-00

SHEET

6 OF 45

ROOM = DOBSON

A B

Set DIMM SPD = AE

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

SCHEM, RSR, PE2800, SV

DWG NO.

F1314

DATE

2/23/2005

DC

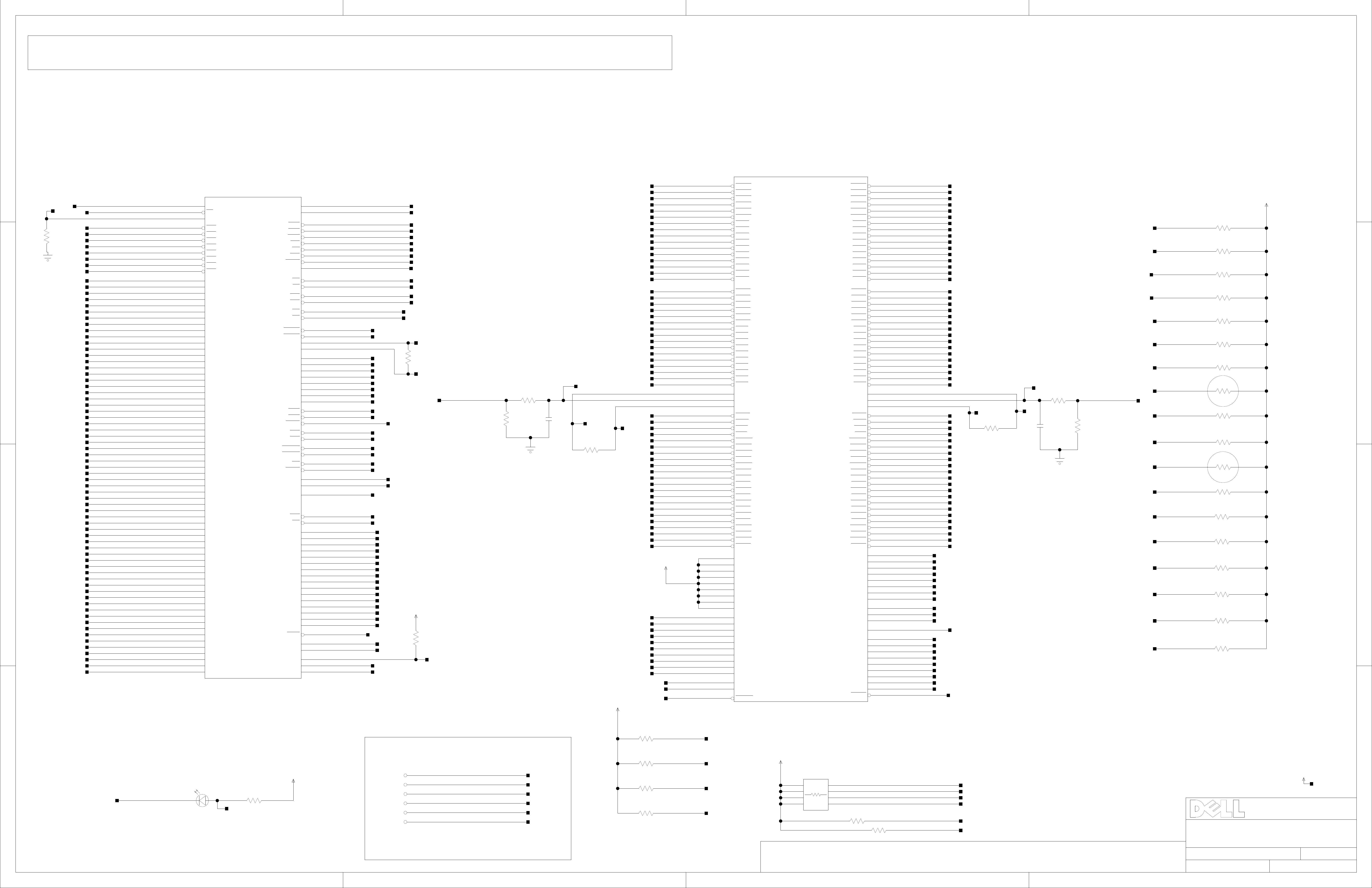

Page 7

DOBSON PCI INTERFACE

B D

CA

PME PULLUP POP'D ON PLANAR

OPTION 2 POP'D

ROOM = DOBSON

Q16

R278

R262

IOP PME B

Option 1 Option 2

Nopop

Nopop

Pop

Pop

Pop

Nopop

K (Cathode)

1 2

A (Anode)

P

N

3

BAR43

BAR43

RISER_EXP_PME_N

D8

31

4,16,31

+3.3V_AUX

21

R369

NP

R425

X

22K-5%

RISER_PCI_PME_N

21

0-5%

4,16

R425

DOBSON CH A (IOP BUS) to LSI

R369

+3.3V_RSR

1

7,13,27

IOP_PCIX_A_SERR_N

NP

1 2

8.2K-5%

R218

X

U_DOBSON

+3.3V_RSR

NP

NP

NP

NP

NP

NP

NP

NP

NP

NP

NP

NP

1

RN40

2

3

4

8.2K

1

RN32

2

3

4

8.2K

1

RN33

2

3

4

8.2K

1

RN39

2

3

4

8.2K

1

RN34

2

3

4

8.2K

1

RN35

2

3

4

8.2K

1

RN36

2

3

4

8.2K

1

RN28

2

3

4

8.2K

1

RN41

2

3

4

8.2K

1

RN37

2

3

4

8.2K

1

RN38

2

3

4

8.2K

1

RN30

2

3

4

8.2K

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

2

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

IOP_PCIX_A_ACK64_N

IOP_PCIX_A_SERR_N

IOP_PCIX_A_STOP_N

IOP_PCIX_A_FRAME_N

IOP_PCIX_A_AD46

IOP_PCIX_A_AD45

IOP_PCIX_A_AD40

IOP_PCIX_A_AD44

IOP_PCIX_A_AD34

IOP_PCIX_A_AD35

IOP_PCIX_A_AD32

IOP_PCIX_A_AD33

IOP_PCIX_A_AD54

IOP_PCIX_A_AD51

IOP_PCIX_A_AD52

IOP_PCIX_A_AD48

IOP_PCIX_A_AD39

IOP_PCIX_A_AD38

IOP_PCIX_A_AD36

IOP_PCIX_A_AD37

IOP_PCIX_A_AD50

IOP_PCIX_A_AD57

IOP_PCIX_A_AD58

IOP_PCIX_A_AD60

IOP_PCIX_A_AD62

IOP_PCIX_A_AD61

IOP_PCIX_A_CBE6_N

IOP_PCIX_A_CBE4_N

IOP_PCIX_A_AD56

IOP_PCIX_A_AD53

IOP_PCIX_A_AD63

IOP_PCIX_A_AD59

IOP_PCIX_A_AD43

IOP_PCIX_A_AD47

IOP_PCIX_A_AD55

IOP_PCIX_A_AD49

IOP_PCIX_A_PERR_N

IOP_PCIX_A_DEVSEL_N

IOP_PCIX_A_TRDY_N

IOP_PCIX_A_IRDY_N

IOP_PCIX_A_REQ64_N

IOP_PCIX_A_PAR64

IOP_PCIX_A_CBE7_N

IOP_PCIX_A_CBE5_N

NC_RN30_P1

NC_RN30_P2

IOP_PCIX_A_AD42

IOP_PCIX_A_AD41

8

7

6

5

X

8

7

6

5

X

8

7

6

5

X

8

7

6

5

X

8

7

6

5

X

8

7

6

5

X

8

7

6

5

X

8

7

6

5

X

8

7

6

5

X

8

7

6

5

X

8

7

6

5

X

8

7

6

5

X

R658

NP

IOP_PCIX_A_LOCK_N

7

1 2

8.2K-5%

X

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

7,13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

IOP_PCIX_A_AD0

IOP_PCIX_A_AD1

IOP_PCIX_A_AD2

IOP_PCIX_A_AD3

IOP_PCIX_A_AD4

IOP_PCIX_A_AD5

IOP_PCIX_A_AD6

IOP_PCIX_A_AD7

IOP_PCIX_A_AD8

IOP_PCIX_A_AD9

IOP_PCIX_A_AD10

IOP_PCIX_A_AD11

IOP_PCIX_A_AD12

IOP_PCIX_A_AD13

IOP_PCIX_A_AD14

IOP_PCIX_A_AD15

IOP_PCIX_A_AD16

IOP_PCIX_A_AD17

IOP_PCIX_A_AD18

IOP_PCIX_A_AD19

IOP_PCIX_A_AD20

IOP_PCIX_A_AD21

IOP_PCIX_A_AD22

IOP_PCIX_A_AD23

IOP_PCIX_A_AD24

IOP_PCIX_A_AD25

IOP_PCIX_A_AD26

IOP_PCIX_A_AD27

IOP_PCIX_A_AD28

IOP_PCIX_A_AD29

IOP_PCIX_A_AD30

IOP_PCIX_A_AD31

IOP_PCIX_A_AD32

IOP_PCIX_A_AD33

IOP_PCIX_A_AD34

IOP_PCIX_A_AD35

IOP_PCIX_A_AD36

IOP_PCIX_A_AD37

IOP_PCIX_A_AD38

IOP_PCIX_A_AD39

IOP_PCIX_A_AD40

IOP_PCIX_A_AD41

IOP_PCIX_A_AD42

IOP_PCIX_A_AD43

IOP_PCIX_A_AD44

IOP_PCIX_A_AD45

IOP_PCIX_A_AD46

IOP_PCIX_A_AD47

IOP_PCIX_A_AD48

IOP_PCIX_A_AD49

IOP_PCIX_A_AD50

IOP_PCIX_A_AD51

IOP_PCIX_A_AD52

IOP_PCIX_A_AD53

IOP_PCIX_A_AD54

IOP_PCIX_A_AD55

IOP_PCIX_A_AD56

IOP_PCIX_A_AD57

IOP_PCIX_A_AD58

IOP_PCIX_A_AD59

IOP_PCIX_A_AD60

IOP_PCIX_A_AD61

IOP_PCIX_A_AD62

IOP_PCIX_A_AD63

3

E24

F23

E23

H22

G22

F22

H21

G21

D21

F20

E20

H19

G19

F19

H18

G18

B27

C26

B26

A26

D25

C25

A25

D24

A24

C23

B23

D22

C22

A22

B21

A21

P23

P24

N24

N22

M25

M23

M22

L23

L24

L22

K22

K24

J26

J25

J23

J22

U29

T26

T27

R26

R28

R29

P26

P27

P29

N28

N29

N27

M29

M28

M26

L29

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_AD32

A_AD33

A_AD34

A_AD35

A_AD36

A_AD37

A_AD38

A_AD39

A_AD40

A_AD41

A_AD42

A_AD43

A_AD44

A_AD45

A_AD46

A_AD47

A_AD48

A_AD49

A_AD50

A_AD51

A_AD52

A_AD53

A_AD54

A_AD55

A_AD56

A_AD57

A_AD58

A_AD59

A_AD60

A_AD61

A_AD62

A_AD63

PRIMARY PCI-X BUS

A_PCIXCAP

INTEL DOBSON IOP PCI A

VER C0

HETERO 2 OF 6

A_C/BE0

A_C/BE1

A_C/BE2

A_C/BE3

A_C/BE4

A_C/BE5

A_C/BE6

A_C/BE7

A_REQ0

A_REQ1

A_REQ2

A_REQ3

A_GNT0

A_GNT1

A_GNT2

A_GNT3

A_TRDY

A_STOP

A_LOCK

A_IRDY

A_FRAME

A_DEVSEL

A_PAR

A_PERR

A_SERR

A_REQ64

A_ACK64

A_PAR64

A_M66EN

A_PME

A_CLKOUT

A_CLKIN

A_CLKO3

A_CLKO2

A_CLKO1

A_CLKO0

A_RST

A_RCOMP

H20

H17

C27

D27

K27

K28

L26

L27

N25

F28

E21

K25

A23

B24

P22

U25

E28

D28

E27

E29

C28

F29

F26

G29

E26

J29

J28

K29

C20

R21

R25

G25

G27

H23

F25

G24

H24

R22

T29

NC_IOP_PCIX_A_GNT1_N

NC_IOP_PCIX_A_GNT2_N

NC_IOP_PCIX_A_GNT3_N

stub

CK_IOP_PCIX_A_CKOUT_R

CK_IOP_PCIX_A_CKIN

NC_A_CLKO3

NC_A_CLKO2

CK_IOP_PCIX_A_DBG_R

CK_IOP_PCIX_A_LSI_R

PD_A_RCOMP

0.750 V

IOP_PCIX_A_CBE0_N

IOP_PCIX_A_CBE1_N

IOP_PCIX_A_CBE2_N

IOP_PCIX_A_CBE3_N

IOP_PCIX_A_CBE4_N

IOP_PCIX_A_CBE5_N

IOP_PCIX_A_CBE6_N

IOP_PCIX_A_CBE7_N

IOP_PCIX_A_REQ0_N

PU_IOP_PCIX_A_REQ1_N

PU_IOP_PCIX_A_REQ2_N

PU_IOP_PCIX_A_REQ3_N

IOP_PCIX_A_GNT0_N

IOP_PCIX_A_TRDY_N

IOP_PCIX_A_STOP_N

IOP_PCIX_A_LOCK_N

IOP_PCIX_A_IRDY_N

IOP_PCIX_A_FRAME_N

IOP_PCIX_A_DEVSEL_N

IOP_PCIX_A_PAR

IOP_PCIX_A_PERR_N

IOP_PCIX_A_SERR_N

IOP_PCIX_A_REQ64_N

IOP_PCIX_A_ACK64_N

IOP_PCIX_A_PAR64

IOP_PCIX_A_M66EN

IOP_PCIX_A_PCIXCAP

PU_IOP_PCIX_A_PME_N

stub

1 2

100-1%

stub

R250

13,27

13,27

13,27

13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7

7

7

13,27

7,13,27

7,13,27

7

7,13,27

7,13,27

7,13,27

13,27

7,13,27

7,13,27

7,13,27

7,13,27

7,13,27

7

7

7

R71

1 2

22-5%

stub

Length Match!!

stub

R342

1 2

R67

1 2

I_IOP_PCIX_A_RST_N IOP_PCIX_A_RST_N

22-5%

22-5%

CK_IOP_PCIX_A_LSI

R506

21

22-5%

CK_IOP_PCIX_A_DBG

13

13,27

To LSI 1030

IOP_PCIX_B_AD0

24

IOP_PCIX_B_AD1

24

IOP_PCIX_B_AD2

24

IOP_PCIX_B_AD3

24

IOP_PCIX_B_AD4

24

IOP_PCIX_B_AD5

24

IOP_PCIX_B_AD6

24

IOP_PCIX_B_AD7

24

IOP_PCIX_B_AD8

24

IOP_PCIX_B_AD9

24

IOP_PCIX_B_AD10

24

IOP_PCIX_B_AD11

24

IOP_PCIX_B_AD12

24

IOP_PCIX_B_AD13

24

IOP_PCIX_B_AD14

24

IOP_PCIX_B_AD15

24

IOP_PCIX_B_AD16

24

IOP_PCIX_B_AD17

24

IOP_PCIX_B_AD18

24

IOP_PCIX_B_AD19

24

IOP_PCIX_B_AD20

24

IOP_PCIX_B_AD21

24

IOP_PCIX_B_AD22

24

IOP_PCIX_B_AD23

24

IOP_PCIX_B_AD24

24

IOP_PCIX_B_AD25

24

IOP_PCIX_B_AD26

24

IOP_PCIX_B_AD27

24

IOP_PCIX_B_AD28

24

IOP_PCIX_B_AD29

24

IOP_PCIX_B_AD30

24

IOP_PCIX_B_AD31

24

IOP_PCIX_B_AD32

24

IOP_PCIX_B_AD33

24

IOP_PCIX_B_AD34

24

IOP_PCIX_B_AD35

24

IOP_PCIX_B_AD36

24

IOP_PCIX_B_AD37

24

IOP_PCIX_B_AD38

24

IOP_PCIX_B_AD39

24

IOP_PCIX_B_AD40

24

IOP_PCIX_B_AD41

24

IOP_PCIX_B_AD42

24

IOP_PCIX_B_AD43

24

IOP_PCIX_B_AD44

24

IOP_PCIX_B_AD45

24

IOP_PCIX_B_AD46

24

IOP_PCIX_B_AD47

24

IOP_PCIX_B_AD48

24

IOP_PCIX_B_AD49

24

IOP_PCIX_B_AD50

24

IOP_PCIX_B_AD51

24

IOP_PCIX_B_AD52

24

IOP_PCIX_B_AD53

24

IOP_PCIX_B_AD54

27

24

IOP_PCIX_B_AD55

24

IOP_PCIX_B_AD56

24

IOP_PCIX_B_AD57

24

IOP_PCIX_B_AD58

24

IOP_PCIX_B_AD59

24

IOP_PCIX_B_AD60

24

IOP_PCIX_B_AD61

24

IOP_PCIX_B_AD62

24

IOP_PCIX_B_AD63

24

DOBSON CH B to PCI SLOT

U_DOBSON

H1

B_AD0

H3

B_AD1

H4

B_AD2

G1

B_AD3

G2

B_AD4

G3

B_AD5

F1

B_AD6

F2

B_AD7

F4

B_AD8

E4

B_AD9

D1

B_AD10

D2

B_AD11

D3

B_AD12

C2

C3

B3

A4

C5

A5

D6

B6

A6

C7

B7

D8

C8

A8

D9

B9

A9

C10

B10

K8

L8

L7

L6

M8

M7

M5

N8

N6

N5

P8

P7

P6

R5

R7

R8

J2

J1

K1

L4

L3

L1

M4

M2

M1

N3

N2

N1

P1

P3

P4

R1

B_AD13

B_AD14

B_AD15

B_AD16

B_AD17

B_AD18

B_AD19

B_AD20

B_AD21

B_AD22

B_AD23

B_AD24

B_AD25

B_AD26

B_AD27

B_AD28

B_AD29

B_AD30

B_AD31

B_AD32

B_AD33

B_AD34

B_AD35

B_AD36

B_AD37

B_AD38

B_AD39

B_AD40

B_AD41

B_AD42

B_AD43

B_AD44

B_AD45

B_AD46

B_AD47

B_AD48

B_AD49

B_AD50

B_AD51

B_AD52

B_AD53

B_AD54

B_AD55

B_AD56

B_AD57

B_AD58

B_AD59

B_AD60

B_AD61

B_AD62

B_AD63

INTEL DOBSON IOP PCI B

VER C0

HETERO 3 OF 6

B_REQ2_N/B_HPCIXCAP1

B_REQ3_N/B_HPCIXCAP2

B_REQ4/B_HM66EN

B_GNT2/B_HBUSEN

B_GNT3/B_HCLKEN

SECONDARY PCI-X BUS

B_C/BE0

B_C/BE1

B_C/BE2

B_C/BE3

B_C/BE4

B_C/BE5

B_C/BE6

B_C/BE7

B_REQ0

B_REQ1

B_GNT0

B_GNT1

B_GNT4/B_HRST

B_TRDY

B_STOP

B_LOCK

B_IRDY

B_FRAME

B_DEVSEL

B_PAR

B_PERR

B_SERR

B_REQ64

B_ACK64

B_PAR64

B_M66EN

B_PCIXCAP

B_PME

B_CLKOUT

B_CLKIN

B_CLKO4

B_CLKO3

B_CLKO2

B_CLKO1

B_CLKO0

RSTIN

B_RST

B_RCOMP

B_VIOSEL

B_VREF

E1

B4

D5

A7

U1

U2

T3

U3

R4

K5

G12

K3

K2

T6

T4

H11

F11

H12

H10

G6

J7

F5

E6

G5

C4

J4

J5

G11

H6

R2

E3

W4

H13

E7

G9

H7

H9

H8

J8

F7

AB6

V8

V1

K6

Y1

D8

stub

CK_IOP_PCIX_B_CKOUT_R

CK_IOP_PCIX_B_CKIN

CK_IOP_PCIX_B_CLK0_R

stub

PD_B_RCOMP

0.750 V

Pop Nopop

Nopop

Nopop

11,16,36

IOP_PCIX_B_CBE0_N

IOP_PCIX_B_CBE1_N

IOP_PCIX_B_CBE2_N

IOP_PCIX_B_CBE3_N

IOP_PCIX_B_CBE4_N

IOP_PCIX_B_CBE5_N

IOP_PCIX_B_CBE6_N

IOP_PCIX_B_CBE7_N

IOP_PCIX_B_REQ0_N

PU_IOP_PCIX_B_REQ1_N

PU_IOP_PCIX_B_REQ2_N

PU_IOP_PCIX_B_REQ3_N

PU_IOP_PCIX_B_REQ4_N

IOP_PCIX_B_GNT0_N

NC_IOP_PCIX_B_GNT1_N

NC_IOP_PCIX_B_GNT2_N

NC_IOP_PCIX_B_GNT3_N

NC_IOP_PCIX_B_GNT4_N

IOP_PCIX_B_TRDY_N

IOP_PCIX_B_STOP_N

IOP_PCIX_B_LOCK_N

IOP_PCIX_B_IRDY_N

IOP_PCIX_B_FRAME_N

IOP_PCIX_B_DEVSEL_N

IOP_PCIX_B_PAR

IOP_PCIX_B_PERR_N

IOP_PCIX_B_SERR_N

IOP_PCIX_B_REQ64_N

IOP_PCIX_B_ACK64_N

IOP_PCIX_B_PAR64

IOP_PCIX_B_M66EN

IOP_PCIX_B_PCIXCAP

NC_IOP_B_CLK04

NC_IOP_B_CLK03

NC_IOP_B_CLK02

NC_IOP_B_CLK1

1 2

100-1%

stub

R246

NC_B_VIOSEL

VREF_PCI_IOP

For PCIX mode 1

Nopop

Pop

SYSTEM_PWRGOOD_RISER_BUF_5V

24

24

24

24

24

24

24

24

7,24

7

7

7

7

24

24

24

24

24

24

24

24

24

24

24

24

24

24

7,24

IOP_PCIX_B_PME_N

R70

1 2

22-5%

R60

1 2

22-5%

I_IOP_PCIX_B_RST_N

PCI_RST_RISER_BUF1_N

stub

7

R507

1 2

22-5%

R278

21

470

C72

1 2

330pF 50V

7

CK_IOP_SLOT5_PCICLK0

36

IOP_PCIX_B_RST_N

stub

I_SYSTEM_PWRGOOD_RISER_BUF_R2

+3.3V_RSR

Length Match !!

24

7

133 Mhz PCI B bus, pullup by external card

SLOT5_PME_N

D

Q16

2N7002

3

1

G

S

2

D

3

2N7002

1 2

G S

PU_IOP_PCIX_A_PME_N

7

+3.3V_RSR

21

R262

22K-5%

IOP_PCIX_B_PME_N

+3.3V_RSR

R343

1 2

PME not used for PCI-X A on IOP

NP

RN42

1

2

3

4

8.2K

8

7

6

5

PU_IOP_PCIX_B_REQ1_N

PU_IOP_PCIX_B_REQ2_N

PU_IOP_PCIX_B_REQ3_N

X

R168

NP

1 2

C271

21

X

0.1uF 16V

+1.5V

R269

1 2

R664

1 2

150-1%

150-1%

8.2K-5%

133EN lo limits bus to 100MHz max

IOP_PCIX_B_PCIXCAP

7,24

PU_IOP_PCIX_B_REQ4_N

24

7

4.7K

IOP_PCIX_B_REQ0_N

VREF_PCI_IOP

0.75V

+3.3V_RSR

21

R54

NP

21

R134

X

1

7,24

7

7

7

7

2

7

3.3K-5%3.3K-5%

3

220

+3.3V_RSR

NP

+3.3V_RSR

RN29

1

2

3

4

8.2K

8

7

6

5

IOP_PCIX_A_REQ0_N

PU_IOP_PCIX_A_REQ1_N

PU_IOP_PCIX_A_REQ2_N

PU_IOP_PCIX_A_REQ3_N

7,13,27

7

7

7

PCI Reset glitch fix

U799 p11

+3.3V_AUX

R40

X

1 2

U799

+3.3V_RSR

R334

1 2

4.7K

In SCSI mode, BIOS can enable / disable SCSI if fet option is pop'd

R327

1 2

16,36

SYSTEM_PWRGOOD_RISER_RST_BUF

IOP_PCIX_B_RST_N

7

12

13

74VHC08

NP

1 2

14

R798

0-5%

11

X

IOP_PCIX_B_RST_SLOT5_N

24

IOP_PCIX_A_PCIXCAP

7

133 Mhz PCI bus A

NP

21

R136

X

220

C538

1 2

0.1uF 16V

+3.3V_RSR

6,8-18,21-24,28,29

+3.3V_AUX

4-2U,8-2X,11-2U,16-2U,19-3W

21-3W,22-3W,23-3W,24-3W,30-2W

31-3W,32-2T,33-3V,36-3W

+12V

4,5,19,21-24,28,29,33

ROUND ROCK,TEXAS

3

D

NP

1

G

100-1%

2N7002

Q6

1

G

D

3

2

I_PCIX_SCSI_IDSEL_R

S

X

1 2

stub

D

3

2N7002

NP

8.2K-5%

X

stub

1 2

NP

100-1%

R181

12

R197

X

NP

1N914

X

Card resistor Card resistor

PCIX_SCSI_IDSEL

1 3

D5

A (Anode)

N

K (Cathode)

3

1N914

1 2

P

13

X133EN PCIXCAP PCIBUSMODE FREQUENCY

N/A

N/A

N/A

M66EN

GROUND

NO CONNECT

N/A

GROUND

GROUND

PCI CONVENTION

PCI CONVENTION

PULL-DOWN PCIX

33 MHz

66 MHz

66 MHz

PCIXCAP

card pulldown

open

10k

133 / 100

66

comp

threshold

%bus freq

88

Voltage

%

100

75

2-24-2005_11:43

62

GROUND

N/A

N/A

NO CONNECT

PCIX

PCIX

100 MHz

133 MHzNO CONNECT NO CONNECT

3.16k 1%

1.02k 1%

GND (100 ohms)

266

533

PCI

36

11.5

48.5

24

0

INC.

TITLE

IOP_PCIX_A_M66EN

7

7,13,27

4 4

OnDieTerminated Signals, 8.33kohm ±40%.

IOP_PCIX_A_AD21

+12V

NP

1 2

2.7K-5%

R244

NP

X

PxDEVSEL#

PxFRAME#

PxIRDY#

PxTRDY#

PxLOCK#

PxSTOP#

PxAD[63:32]

PxCBE_[7:4]#

XINT[7:0]#

PxM66EN

PxREQ[]#

PxPAR64

GPO_SCSI_IDSEL_DIS

36

PU_SCSI_DIS_CKT

Q1

2N7002

SCHEM, RSR, PE2800, SV

PxSERR#

PxPERR#

PxREQ64#

PxACK64#

Pull-up resistors for PxAD[31:0] and PxCBE_[3:1]# are not required by the PCI Specification.

X

S

2

G S

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DWG NO.

DATE

F1314

2/23/2005

REV.

A06-00

SHEET

7 OF 45

A B

DC

Page 8

DOBSON PCI Express bus and Strapping

B D

R221

+3.3V_RSR

I2C_DOBSON_SDA

8

I2C_DOBSON_SCL

8

R222

21

1 2

0-5%

ICH_SEG3_SDA

ICH_SEG3_SCL

CA

4,6

PCI EXPRESS x4

4,6

0-5%

+3.3V_RSR

NP

1

NP

RN44

1

2

3

4

8.2K

RN43

1

2

3

4

8.2K

8

7

6

5

X

8

7

6

5

Dobson Errata # 51

pop RN44 for B0 Dobson

SCSI_INTB_N

SCSI_INTA_N

IOP_PCIX_B_INT0_N

IOP_PCIX_B_INT1_N

IOP_PCIX_B_INT4_N

IOP_PCIX_B_INT5_N

IOP_PCIX_B_INT7_N

IOP_PCIX_B_INT6_N

8,13,27