Page 1

8

7

6

5

4

3

2

1

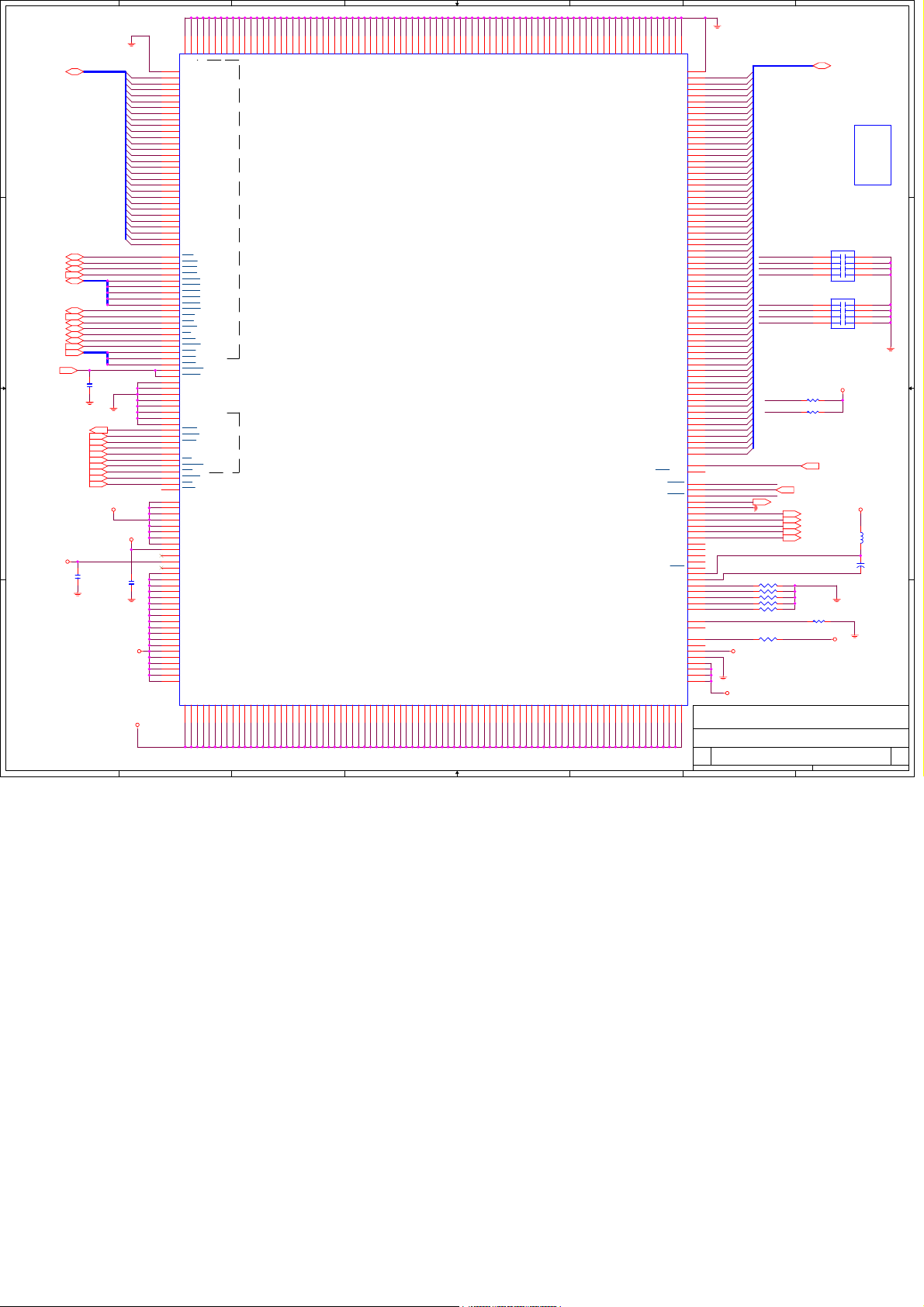

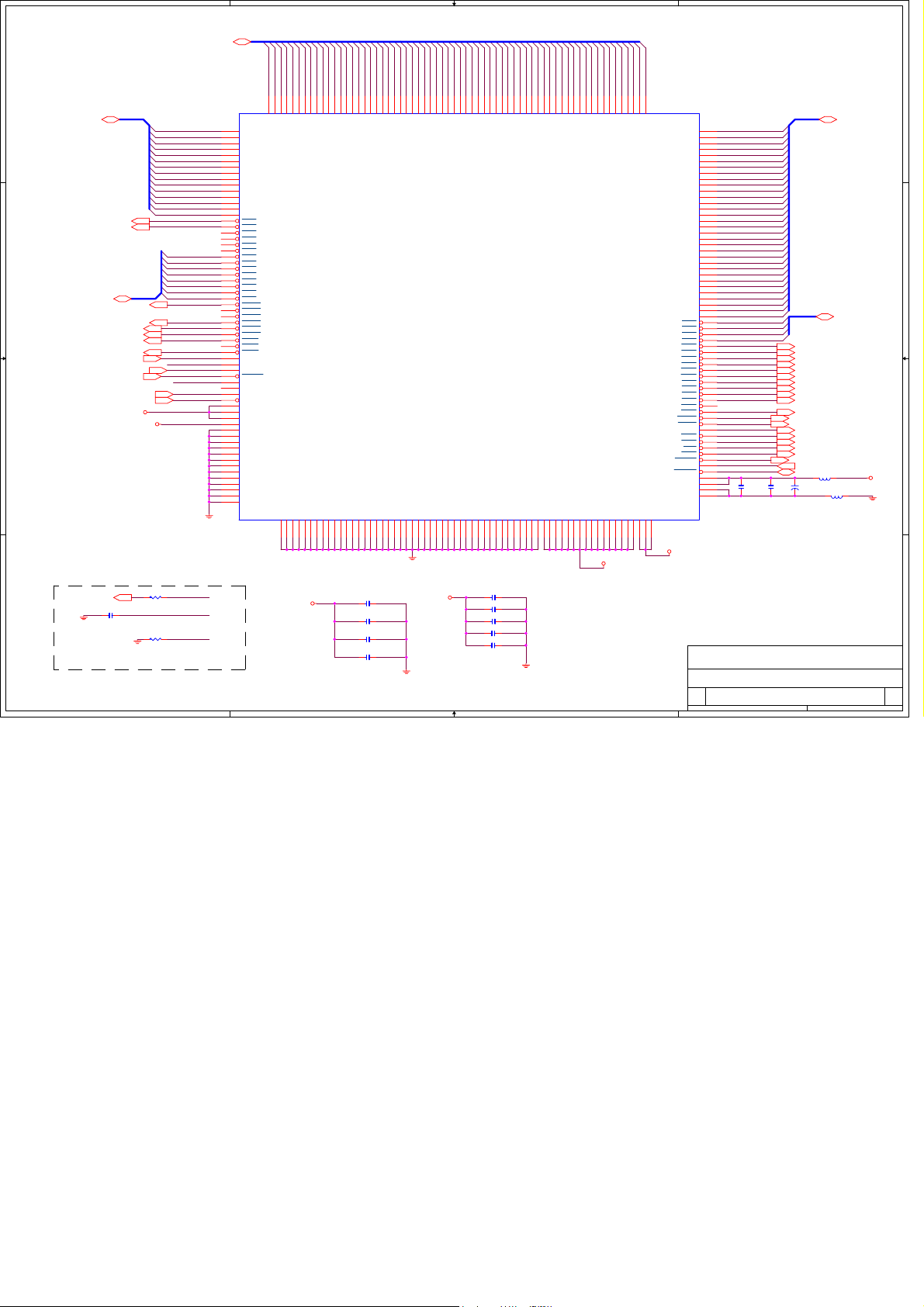

MS-9108 SCHEMATIC

REV0.A

D D

VIA VT8601/82C686B CHIPSET PLATFORM DESIGN

C3 Processor / ONE DIMM Small Form-Factor(CD-ROM size)

REFERENCEPAGE

01

02

03

C C

04

05

06

07

08

09

10

B B

11

12

13

14

15

16

17

A A

18

19

20

8

7

CONVER

BLOCK DIAGRAM

C3 Processor 1

C3 Processor 2

CLOCK

VT8601 A

VT8601 B

DIMM 1

VT82C686B A

VT82C686B B

VT82C686B C

CONNECTORS

FAN-DOC-IDE

PCI SLOT

POWER

LAN1

LAN2

LAN CONNECTORS

IDE

IDE CONNECTORS

6

5

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

4

3

Date: Sheet

2

COVER

MS-9108

0A

of

122Friday, September 21, 2001

1

Page 2

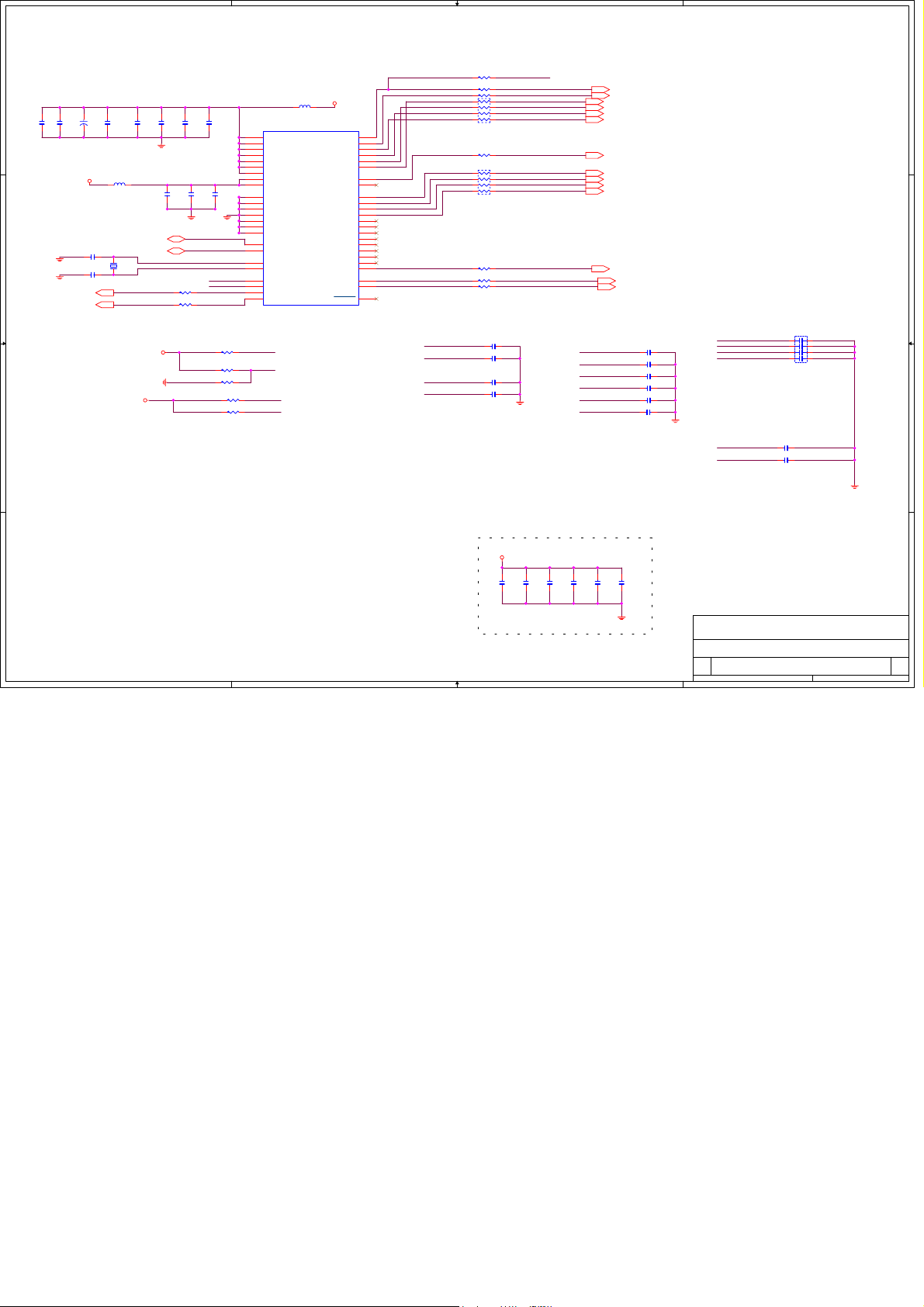

Block Diagram

1

VRM Clock

RGB Video

HEADER

For TEST

A A

UltraDMA 33/66/100

VIA C3 Processor BGA

ADDR

CTRL

ADDR

CTRL

VIA PLE133

(8601)

DATA

DATA

PCI CNTRL

PCI ADDR/DATA

1 DIMM

Modules

Term

PCI Slot

LAN1

LAN2

LAN1

LAN 10/100

LAN2

IDE

IDE1

IDE2

VIA 686B

UltraDMA 33/66/100

Keyboard

Mouse

HEADER

Mouse

ISA Bus

1

Disk On Chip

Serial

IDE3

IDE4

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

Date: Sheet of

Block Diagram

MS-9108

222Friday, September 21, 2001

0A

Page 3

8

A[3..31]<4,6>

D D

C102

-ADS

-HDRDY

-HDBSY

-HTRDY

-HREQ0

-HREQ1

-HREQ2

-HREQ3

-HREQ4

-BREQ0

-BPRI

-BNR

-HLOCK

-HIT

-HITM

-DEFER

-RS0

-RS1

-RS2

-CPURST

0.1u

-FERR

-IGNNE

-A20M

INTR

NMI

-SMI

-STPCLK

-CPUSLP

-FLUSH

-HINIT

CPUVREF

VTT

C29

0.1u

VTT

-ADS<4,6>

-HDRDY<4,6>

-HDBSY<4,6>

-HTRDY<4,6>

-HREQ[0..4]<4,6>

C C

-BREQ0<4,6>

-BPRI<4,6>

-BNR<4,6>

-HLOCK<4,6>

-HIT<4,6>

-HITM<4,6>

-DEFER<4,6>

-RS[0..2]<4,6>

-CPURST<4,6>

-FERR<4,9>

-IGNNE<4,9>

-A20M<4,9>

INTR<4,9>

NMI<4,9>

-SMI<4,9>

-STPCLK<4,9>

-CPUSLP<4,9>

-FLUSH<4>

B B

A A

-HINIT<4,9>

VTT

C28

0.1u

8

7

AF7

AF11

AF15

AF19

AF26

AE2

AE25

AE5

AE1

AF23

U3

GND

GND

GND

GND

GND

GND

GND

GND

AF1

GND

A3

AD6

A3

A4

AD9

A4

A5

AD5

A5

A6

AD7

A6

A7

AF10

A7

A8

AE8

A8

A9

AF6

A9

A10

AE3

A10

A11

AE9

A11

A12

AD4

A12

A13

AF5

A13

A14

AE10

A14

A15

AF4

A15

A16

AE6

A16

A17

AA2

A17

A18

U2

A18

A19

AB3

A19

A20

Y3

A20

A21

AC1

A21

A22

AB1

A22

A23

Y2

A23

A24

W3

A24

A25

AC3

A25

A26

T2

A26

A27

V1

A27

A28

AF2

A28

A29

U1

A29

A30

V2

A30

A31

AA1

A31

AE20

ADS

AF18

DRDY

AD19

DBSY

AE16

TRDY

AE13

REQ[0]

AD11

REQ[1]

AE12

REQ[2]

AE14

REQ[3]

AE11

REQ[4]

AD20

BREQ0

AD12

BPRI

AF9

BNR

AF14

LOCK

AE17

HIT

AD16

HITM

AF13

DEFER

AE18

RS[0]

AD15

RS[1]

AE19

RS[2]

T3

RESET2(RSV)

AD1

RESET

B25

GND

B26

GND

A1

GND

A8

GND

A12

GND

A16

GND

A20

GND

A26

GND

T24

FERR

Y25

IGNNE

W24

A20M

H25

INTR

H24

NMI

AA25

SMI

Y24

STPCLK

AD21

SLP

U25

FLUSH

AA26

INIT

V25

IERR(RSV)

D23

VREF0

D16

VREF1

G4

VREF2

L4

VREF3

R4

VREF4

AA4

VREF5

AC9

VREF6

AC15

VREF7

W26

VCC_1.5V

U26

VCC_2.5V(RSV)

V26

VCC_CMOS

C20

VCOREDET(RSV)

AE15

VTT

AD8

VTT

AD13

VTT

AD22

VTT

AA3

VTT

U3

VTT

T25

VTT

P3

VTT

G2

VTT

G25

VTT

E24

VTT

C10

VTT

C13

VTT

C18

VTT

C21

VTT

E9

VTT

E18

VTT

J5

VTT

J22 AB18

VTT VTT

VIA-C3

VCC2

VCCP

AF3

7

GND

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

AF8

AF12

AF16

AF20

AE4

AE7

AE24

AD2

AE22

AE26

AD3

GND

GND

GTL

CMOS I/O

VCC2

VCC2

AD10

AD14

GND

VCC2

AD17

AD18

GND

VCC2

AD24

AD26

GND

VCC2

6

AC5

AC7

AC12

AC13

AC16

AC17

AC20

AC21

AB23

AC8

GND

GND

GND

GND

GND

AB25Y4Y26W1W4

AB2

AB8

AB13

GND

GND

GND

GND

GND

GND

GND

GND

GND

5

W23

V23

V24U4T4

T26R1P23

W5

W22

GND

GND

GND

GND

GND

GND

GND

P24N3N4M4L1

P22

N5

P25

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

N25

GND

GND

L23

L26J3J4H4G1

GND

GND

GND

GND

4

G23

F23E2E4D6D7

J25

H5

H26

G24

F25

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

D10

D11

E25

E14

E19

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VIA EBGA 376

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

AC14

AC18

AC19

AC23

AC25

VCC2

VCC2

AA23

Y23W2W25V3V4

AB14

AB19

AB4

VCC2

AC4

AC6

AC10

AC11

AC2

6

U23

U24T1R2

VCC2

VCC2

R25P4N24M1L2K3K4

P5

N22

5

VCC2

K25

J24H1H23F3F4

K26

VCC2

VCC2

VCC2

VCC2

J26

VCC2

VCC2

E23D2D4D5D8D9D12

E1

H22

E8

E13

F24

4

VCC2

VCC2

D13

D17

D20

D21C1C9

D24

D14

GND

VCC2

C17

3

D15

D18

GND

VCC2

C25B3B16

3

GND

VCC2

D19

D22C3C14B2B5

D25

GND

GND

GND

GND

GND

BCLK

BCLK(RSV)

BSEL0

PWRGOOD

BSEL1

THERMDP

THERMDN

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

TRST

RTTCTRL

SLEWCTRL(RSV)

NCHCTRL

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

B23A4A7

A11

A15

2

B22

GND

GND

GND

Y1

GND

R3

D0

N1

D1

H3

D2

F2

D3

P1

D4

M2

D5

N2

D6

D3

D7

M3

D8

J1

D9

K1

D10

G3

D11

K2

D12

F1

D13

H2

D14

P2

D15

C4

D16

L3

D17

J2

D18

B1

D19

E3

D20

A3

D21

B9

D22

A2

D23

D1

D24

C5

D25

B4

D26

B12

D27

B7

D28

C7

D29

C2

D30

A6

D31

A5

D32

C6

D33

C8

D34

B6

D35

B10

D36

A10

D37

A9

D38

C11

D39

C15

D40

A14

D41

B13

D42

B8

D43

C12

D44

B11

D45

B20

D46

B15

D47

B18

D48

A13

D49

A22

D50

B14

D51

B17

D52

A21

D53

B19

D54

A18

D55

A23

D56

C19

D57

B21

D58

A17

D59

C23

D60

B24

D61

C22

D62

C16

D63

M23

N23

AF24

AF17

AF22

AF21

AE21

AC24

AC26

AB24

AA24

AB26

AC22

TCK

AE23

TDI

AD25

TDO

AD23

TMS

AF25

T23

PLL1

R23

PLL2

R26

BR0

P26

BR1

N26

BR2

M26

BR3

E26

BR4

J23

C24

NCHCTRL

K24

L24

RSV

A25

C26

GND

V5

VTT

V22

VTT

AB9

VTT

VCC2

VCC2

VCC2

A19

A24

Title

Size Document Number Rev

Date: Sheet

D[0..63]

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

-SMI

D31

-STPCLK

D32

-IGNNE

D33

-A20M

D34

D35

D36

D37

D38

-HINIT

D39

-CPUSLP

D40

-FERR

D41

INTR

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CPU_PWGD

VID0

VID1

VID2

VID3

VID4

Reserved Pins on C3

Processor

BR0

BR1

BR2

BR3

BR4

RTTCTRL

BSEL0

BSEL1

CPUCLK

BSEL0

BSEL1

CPU_IN <11>

R36 X_0

R35 X_0

R34 X_0

R33 X_0

R30 X_0

R32 X_15-1%

VCCP

C26 : Report 133MHz FSB CPU in MSR 18&19

register.(Since VIA EBGA are all 133MHz FSB)

VTT

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R47 10K

R48 10K

CPUCLK <5>

CPU_PWGD <15>

VID0 <15>

VID1 <15>

VID2 <15>

VID3 <15>

VID4 <15>

R31 110

D[0..63] <4,6>

CN3

47p

CN2

47p

VCC2_5

VTT

MICRO-STAR INT'L CO., LTD.

Samuel 2 EBGA 368-1

2

MS-9108

322Saturday, September 22, 2001

1

VCCP

1

U1_X1

CPU FAN

EC5

47u

of

L2

22u_1008

0A

Page 4

8

S

CPU DECOUPLING CAPACITORS

D D

VCCP

C C

B B

VCCP VTTVCCP

C25

4.7u-0805

C36

4.7u-0805

C30

4.7u-0805

C18

4.7u-0805

C24

4.7u-0805

C103

4.7u-0805

C214

4.7u-1206

C211

4.7u-1206

C212

4.7u-1206

C223

4.7u-1206

C200

4.7u-1206

C221

1u-0805

C215

1u-0805

C208

1u-0805

C207

1u-0805

C204

1u-0805

C217

0.1u

C213

1u-0805

PROCESSOR REFERENCE VOLTAGE GENERATOR

C37

0.1u

B

A A

C210

0.1u

C227

0.1u

C226

0.1u

NEAR BGA368

Use 0603 Packages and

distribute within 500

mils of CPUVREF inputs

(1 cap for every 1 inputs)

Place at solder side of EBGA

8

C225

0.1u

C222

0.1u

C224

0.1u

C209

0.1u

C205

1u-0805

C201

4.7u-1206

C218

0.1u

C216

0.1u

C206

0.1u

C202

0.1u

C220

0.1u

C219

1u-0805

Solder Side

CPUVREF

7

C48

0.1u

C61

0.1u

C76

0.1u

C86

0.1u

C98

0.1u

C107

0.1u

C108

0.1u

C106

0.1u

VTT

C99

0.1u

C87

0.1u

C75

0.1u

C60

0.1u

C45

0.1u

C27

0.1u

C38

0.1u

C26

0.1u

VTTCPUVREF CPUVREF

R46

75-1%

R39

150-1%

7

6

VTT

C41

0.1u

C15

0.1u

C40

0.1u

C16

0.1u

D[0..63]<3,6>

A[3..31]<3,6>

6

5

VTT

RN20

A27

A18

A29

A26

A20

A23

A24

A30

A21

A22

A17

A31

A10

A25

A19

A28

D13

D20

D7

D24

D30

D19

D23

D21

D29

D43

D34

D22

D38

D36

D37

D39

D33

D31

D35

D28

D16

D26

D25

D32

D45

D44

D27

D42

D49

D51

D41

D40

D47

D63

D52

D59

D48

D55

D57

D54

D46

D58

D53

D62

D50

D56

D60

D61

5

51

2

10

3

4

6

7

8

9

56

RN18

51

2

10

3

4

6

7

8

9

56

RN17

51

2

10

3

4

6

7

8

9

56

RN13

51

2

10

3

4

6

7

8

9

56

RN15

51

2

10

3

4

6

7

8

9

56

RN10

51

2

10

3

4

6

7

8

9

56

RN9

51

2

10

3

4

6

7

8

9

56

RN7

51

2

10

3

4

6

7

8

9

56

4

CPU GTL+ PULL-UP RESISTORS

-BNR<3,6>

-HREQ1<3,6>

-HREQ4<3,6>

4

A4

A11

-BNR

A8

-HREQ1

-HREQ4

A14

A7

A5

A13

A15

A12

A6

A16

A9

A3

D1

D5

D8

D17

D0

D15

D4

D6

D2

D14

D11

D3

D12

D10

D18

D9

3

VTT

RN14

51

2

10

3

4

6

7

8

9

56

RN16

51

2

10

3

4

6

7

8

9

56

RN19

51

2

10

3

4

6

7

8

9

56

RN21

51

2

10

3

4

6

7

8

9

56

2

-HREQ0<3,6>

-DEFER<3,6>

-BPRI<3,6>

-HREQ2<3,6>

-HTRDY<3,6>

-RS1<3,6>

-HREQ3<3,6>

-HLOCK<3,6>

-RS0<3,6>

-HDRDY<3,6>

-HIT<3,6>

-HITM<3,6>

-BREQ0<3,6>

-ADS<3,6>

-HDBSY<3,6>

-RS2<3,6>

-CPURST<3,6>

-HREQ0

-DEFER

-BPRI

-HREQ2

-HTRDY

-RS1

-HREQ3

-HLOCK

-RS0

-HDRDY

-HIT

-HITM

-BREQ0

-ADS

-HDBSY

-RS2

-CPURST

RN11

2

3

4

6

7

8

9

56

RN8

2

3

4

6

7

8

9

56

R73 56

1

VTT

51

10

51

10

CPU CMOS PULL-UP RESISTORS

-HINIT

-HINIT<3,9>

-CPUSLP

-CPUSLP<3,9>

-FERR

-FERR<3,9>

INTR

INTR<3,9>

-SMI

-SMI<3,9>

-STPCLK<3,9>

3

-STPCLK

-IGNNE

-IGNNE<3,9>

-A20M

-A20M<3,9>

NMI

-FLUSH

-FLUSH<3>

NMI<3,9>

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

Date: Sheet of

Samuel 2 EBGA 368-2

2

RN2330

RN3330

R37 330

R29 330

NMI

MS-9108

12

34

56

78

12

34

56

78

C14 47p

VTT

422Saturday, September 22, 2001

0A

1

Page 5

1

2

3

4

1

3

5

7

1

3

5

7

C20 10P

C21 10P

C19 22P

C71 22P

10K

22

22

2

4

6

8

0

8P4R-10

2

4

6

8

22

22

22

CK_VDD1

SBCLK

PCICLK

IDECLK

LAN2CLK

LAN1CLK

DCLK0

DCLK1

DCLK2

DCLK4

DCLKI

NBPCLK

SBCLK

LAN1CLK

LAN2CLK

IDECLK

PCICLK

SBCLK <9>

NBPCLK <7>

PCICLK <14>

IDECLK <19>

LAN2CLK <17>

LAN1CLK <16>

DCLK0 <7>

DCLK1 <8>

DCLK2 <8>

DCLK3 <8>

DCLK4 <8>

DCLKI <7>

NBCLK

CPUCLK <3>

C79

22P

C78

22P

C80

22P

C81

22P

C82

22P

C83 X_22P

DCLK1

DCLK3

DCLK4

DCLKI

DCLK0

1

3

5

7

C22 22P

C84

close to NB

CN1

X_8P4C-10P

X_10P

2

4

6

8

R61

A A

EC6

C72

C58

10U/16V/S

104P

47P

VCC2_5

B B

C C

C47 12P

YCRY14.31818H16P

C42 12P

GUICLK<6>

686OSC<10>

C73

C70

104P

104P

L3

CK_VDD2 DCLK3

0/0805

SMBDATA<8,11>

SMBCLK<8,11>

X1

1 2

GUICLK

686OSC

VCC3

VCC3

CK_VDD1

CK_VDD1

C35

C44

104P

R60

R40

C34

104P

104P

C32

C33

104P

104P

SMBDATA

SMBCLK

22

22

R38 10K

R65 10K

R66 X_10K

R44 10K

R45 10K

U2

1

VDD1

6

VDD2

14

VDD2

19

VDD3

30

VDD3

36

VDD3

27

VDD4

48

VDDL1

42

VDDL2

C31

3

104P

GND

9

GND

16

GND

22

GND

33

GND

39

GND

45

GND

23

SDATA

24

SCLK

4

X1

5

X2

FS1 NBCLK

25

24M/FS1

FS0 CPUCLK

26

48M/FS0

2

REF0/PCI_SP

46

REF1/FS2

FS2

ICW-W144H

FS2

FS3

FS0

FS1

L4

0/0805

VCC3

MODE/PCI_F

PCI0/FS3

BUFFER IN

IOAPIC

SDRAM0

SDRAM1

SDRAM2

SDRAM3

SDRAM4

SDRAM5

SDRAM6

SDRAM7

SDRAM8

SDRAM9

SDRAM10

SDRAM11

SDRAM_F

CPU0

CPU1

CPU_SP

PCI1

PCI2

PCI3

PCI4

FS3 NBPCLK

7

8

10

11

12

13

15

47

38

37

35

34

32

31

29

28

21

20

18

17

40

44

43

41

R64

R62

RN12 8P4R-22

R58

RN6

R43

R41

R42

NBCLK DCLK2

CPUCLK

686OSC

GUICLK

VCC3

C91

C17

C59

C93

C74

X_104P

X_104P

X_104P

D D

X_104P

Place around clock for EMI.

1

2

3

X_104P

C92

X_104P

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

Date: Sheet

Clock

MS-9108

4

522Friday, September 21, 2001

of

0A

Page 6

1

D[0..63]<3,4>

A A

B B

C C

-ADS<3,4>

-BNR<3,4>

-BPRI<3,4>

-HDBSY<3,4>

-DEFER<3,4>

-HDRDY<3,4>

-HLOCK<3,4>

-HITM<3,4>

-HIT<3,4>

-BREQ0<3,4>

-HTRDY<3,4>

-RS[0..2]<3,4>

D D

-CPURST<3,4>

-HREQ[0..4]<3,4>

R69

VTT

75RST

1

R70

150RST

-ADS

-BNR

-BPRI

-DBSY

-DEFER

-DRDY

-HLOCK

-HITM

-HIT

-BREQ0

-HTRDY

-CPURST

-RS0

-RS1

-RS2

-HREQ0

-HREQ1

-HREQ2

-HREQ3

-HREQ4

GTLVREF

Under NB

A[3..31]<3,4>

A10

A11

A12

A3A4A5A6A7A8A9

A25

D24

B25

U8A

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CN4

C90

105P

104P

C89

X_104P

A3A4A5A6A7A8A9

E19

HD0

B18

HD1

B16

HD2

A16

HD3

C18

HD4

C17

HD5

D18

HD6

D15

HD7

D17

HD8

C16

HD9

B17

HD10

D16

HD11

A17

HD12

A15

HD13

E16

HD14

D19

HD15

A14

HD16

E18

HD17

E17

HD18

B14

HD19

C15

HD20

E14

HD21

B11

HD22

D14

HD23

B15

HD24

D13

HD25

C13

HD26

E9

HD27

C12

HD28

D12

HD29

E15

HD30

A13

HD31

B12

HD32

B13

HD33

A12

HD34

E13

HD35

D11

HD36

D10

HD37

A11

HD38

E10

HD39

E8

HD40

C9

HD41

D9

HD42

C11

HD43

B10

HD44

A10

HD45

E7

HD46

D8

HD47

B8

HD48

C10

HD49

B6

HD50

B9

HD51

F8

HD52

D6

HD53

D7

HD54

C7

HD55

E5

HD56

A7

HD57

E6

HD58

B7

HD59

C6

HD60

D5

HD61

A6

HD62

A8

HD63

J24

ADS

D26

BNR

E26

BPRI

H26

DBSY

F26

DEFER

J23

DRDY

G23

HLOCK

G26

HITM

G24

HIT

J25

BREQ0

G25

HTRDY

A19

CPURST

H23

RS0

K23

RS1

H25

RS2

E24

HREQ0

F23

HREQ1

F24

HREQ2

F25

HREQ3

E25

HREQ4

E12

GTLVREF

E21

GTLVREF

VIA-VT8601

VTT

A13

B26

E23

C26

C24

A23

C25

D22

B24

A10

A11

A12

A13

VTT

VTT

GND

GND

GND

GND

GND

F19

E11

L11

N11

P11

T11

M12

C88

104P

2

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

D25

F22

C23

D21

A20

C22

A21

B23

A22

B21

E20

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

GND

GND

GND

GND

VCC

VCC

VCC

VCC

VCC

N12

P12

VCC

R12

L13

M11

R11

L12

T12

L15

T15

M16

VCC3

ADVDD_V2

AVDD_V1

AVDD_V2

2

A25

B22

A24

VCC

R16F7F10

A25

VCC

A26

B19

A26

VCC

A27

A28

C20

A24

A27

A28

VCC

VCC

F12W1W2Y1Y2

GND_V1

A29

A30

B20

D20

A29

A30

ADVDD_V2

AVDD_V1

GND_V2

VCC2_5

A31

C21

V21

AA18

A31

VDD

AGND_V1

AVDD_V2

AA1A1B1C1D1A5B5C5A4B4C4A3B3C3A2

VCC3

AA9V6J6Y5AB1

VDD

VDD

VDD

VDD

AGND_V2

AGND_V4

AGND_V3

AVDD_V3

AVDD_V3

GND_V3

GND_V4

8P4R-4.7K

AA4

VMD49

VMD50

VMD51

ADVDD_V1

VMD32

VMD33

ADVDD_V1

AA5

RN22

7

5

3

1

AA3

VMD52

VMD34

AB2

VMD53

VMD35

AB3

VMD54

VMD36

AB4

VMD55

VMD37

8

6

4

2

AC1

VMD56

VMD38

AC2

VMD57

VMD39

AC3

AD1

AD2

AD3

VMD58

VMD59

VMD60

VMD61

TVD0/VMD44

TVD1/VMD45

TVD2/VDQM4

TVD3/VMD46

TVD4/VDQM5

TVD5/VMD42

TVD6/VDQM7

TVD7/VDQM6

TVHS//VMD43

TVVS/VMD48

TVCLK/VMD47

SUSPEND

IMIO/VMD22

IMIIN/VMD26

CAPD0/VSWE

CAPD1/VDQM2

CAPD2/VDQM1

CAPD3/VSRAS

CAPD4/VMA1

CAPD5/VSCAS

CAPD6/VMA0

CAPD7/VMA2

CAPD8/VMA10

CAPD9/VMA5

CAPD10/VMA3

CAPD11/VMA4

CAPD12/VMA9

CAPD13/VMA6

CAPD14/VMA7

CAPD15/VMA8

CAPHS/VMDCLK

CAPVS/VDQM0

CAPCLK/VDQM3

ENPBLT/VMD1

ENPVEE/VMD2

ENPVDD/VMD0

SFCLK/VMD13

DE/VMD11

FLM/VMD3

LP/VMD15

PD0/VMD14

PD1/VMD12

PD2/VMD4

PD3/VMD10

PD4/VMD6

PD5/VMD9

PD6/VMD28

PD7/VMD7

PD8/VMD5

PD9/VMD27

PD10/VMD8

PD11/VMD31

PD12/VMD16

PD13/VMD17

PD14/VMD20

PD15/VMD29

PD16/VMD18

PD17/VMD19

PD18/VMD21

PD19/VMD23

PD20/VMD30

PD21/VMD24

PD22/VMA11

PD23/VMD25

VMD40

VMD41

VMD62

AE1

AA15

RED

GND

GREEN

VMD63

BLUE

HSYNC

VSYNC

COMP

IRSET

VLF1

VLF2

XTLO

INTA

ENTEST

5VSF

3

1

TP2

1

TP1

1

TP3

F16

C2

GND

D3

D2

HSYNC

E2

VSYNC

E1

DDCDATA

F2

SDA

DDCCLK

F3

SCL

COMP

E4

IRSET

E3

V1

V2

U5

V3

T5

U4

T6

U2

V5

W3

V4

VLF1

Y3

VLF2

AA2

Y4

XTLI

W4

W5

-SUSPEND

F5

-ENTEST

F4

U6

M2

IMIIN

M3

R6

T2

T1

R5

R2

R4

R1

R3

P5

P2

P3

P4

N5

N2

N1

N4

T3

U1

U3

G1

H5

F1

G4

H3

G3

G5

G2

H2

H1

J2

J1

H4

K6

J4

J3

L5

K2

J5

K1

K3

L6

L2

K5

L1

L3

M6

K4

M4

M5

M1

3

R89

TVOUT EMI

L15

360RST

C142 560P

C146 560P

-PIRQA

R88

VCC5

RED

GREEN

BLUE

104P

GUICLK

RED <12>

GREEN <12>

BLUE <12>

HSYNC <12>

VSYNC <12>

DDCDATA <12>

DDCCLK <12>

AVDD_V3

GND_V3

GND_V1

GND_V2

GUICLK <5>

-PIRQA <14>

4.7K

VCC3

R92

IMIIN

-SUSPEND

VCC3

4.7K

VCC3

R87

4.7K

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

Date: Sheet

North Bridge VT8601-1

80S/0805

80S/0805

L19

80S/0805

GND_V4

MS-9108

L13

80S/0805

80S/0805

L17

VCC2_5

C137

104P

GND_V2

L20

0/0805

4

L14

4

C132

104P

C129

104P

GND_V3

L18

C138

104P

GND_V1

L16

0/0805

VCC2_5

ADVDD_V1

VCC2_5

AVDD_V3

L12

0/0805

VCC2_5

C145

104P

VCC2_5

AVDD_V2

C135

1000p

L11

80S/0805

ADVDD_V1

C130

1000p

C131

1000p

ADVDD_V2

C133

1000p

AVDD_V1

C136

1000p

EC15

10U/16V/S

EC13

10U/16V/S

AVDD_V3

EC14

10U/16V/S

EC12

10U/16V/S

622Friday, September 21, 2001

EC11

10U/16V/S

of

0A

Page 7

1

MD[0..63]<8>

MD2

MD3

MD1

MD0

MD4

2

MD5

MD11

MD7

MD9

MD8

MD6

MD10

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

3

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

4

MD63

A A

MA[0..14]<8>

-MCS0<8>

-MCS1<8>

B B

MDQM[0..7]<8>

C C

VCC3

-MRAS<8>

-MCAS<8>

CKE3

CKE1<8>

-MWE<8>

CKE0<8>

NBCLK

DCLKI<5>

-SUSTATE<11>

PW_GD<11,15>

-PCIRST<9>

VCC2_5

-MCS0

-MCS1

NBCLK

DCLKO_

DCLKI

-SUSTATE

PLLTEST

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

MDQM0

MDQM1

MDQM2

MDQM3

MDQM4

MDQM5

MDQM6

MDQM7

-MRAS

-MCAS

CKE3

CKE1

-MWE

CKE0

PW_GD

-PCIRST

AA23

AB23

AB26

AB25

AB24

AC26

AC25

AC24

AD26

AD25

AE26

AD24

AE24

AE25

AF25

AF24

AE23

AD23

AF23

AA24

AA25

AA26

AC22

AD14

AE15

AB22

AA22

Y26

Y25

Y24

Y23

Y22

W21

V23

W23

W26

W25

U22

V25

V24

U24

U25

U26

G22

J22

K22

K24

E22

V22

W22

M21

M13

N13

P13

R13

T13

L14

M14

N14

P14

R14

T14

T21

U8B

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

RAS0

RAS1

RAS2

RAS3

RAS4

RAS5

CAS0

CAS1

CAS2

CAS3

CAS4

CAS5

CAS6

CAS7

SRASA

SRASB/CKE5

SRASC/CKE4

SCASA

SCASB/CKE3

SCASC/CKE1

SWEA

SWEB/CKE2

SWEC/CKE0

CCLK

DCLKO

DCLKI

SUS_ST

PLLTEST

CRESET

POWORK

RESETX

VSUS33

VSUS33

VSUS33

VSUS25

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VIA-VT8601

M23

K25

L26

L25

M26

M24

N26

N24

P23

P25

R23

R25

P22

T23

T25

T22

AD22

AF22

AB21

AE21

AB20

AD20

AE20

AC19

AF19

AC18

AE18

AD17

AF17

AB17

AE16

AC16

K26

L23

M22

L24

M25

N23

N25

N22

P26

P24

R26

R24

R22

T26

T24

U23

AE22

AC21

AD21

AF21

AC20

AF20

AB19

AE19

AB18

AD18

AA19

AE17

AC17

AD16

AF16

AB16

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

GND

GND

GND

GND

GND

GND

GND

M15

N15

P15

R15

L16

N16

P16

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

T16P1AF1B2N3D4AC4F6N6P6AA6C8AD8A9AF9

GND

MD23

GND

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE0

CBE1

CBE2

CBE3

REQ0

REQ1

REQ2

REQ3

REQX

PREQ

GNT0

GNT1

GNT2

GNT3

GNTX

PGNT

FRAME

PLOCK

PAR

SERR

TRDY

IRDY

STOP

DEVSEL

PCLK

CLKRUN

AVDD

AVDD

AGND

AGND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VDD

VDD

F13

AA13

AD13

C14

F14

AA14

A18

AF18

C19

AD19

F21

N21

P21

AA21

D23

AC23

H24

W24

A26

J26

V26

AF26G6H6W6Y6

AA7

AA10

F17

AA17

F20

AA20

G21

VCC3

K21

U21

Y21L4T4F9F18

VDD

J21

VCC2_5

AF14

AE14

AE13

AF13

AC14

AB14

AC13

AB13

AE12

AD12

AB12

AC12

AF11

AE11

AD11

AC11

AA8

AC9

AF8

AE8

AE7

AB8

AF7

AC8

AC7

AB7

AF6

AE6

AD6

AC6

AB6

AF5

AF12

AB11

AD9

AD7

AC5

AD5

AE4

AD4

AF2

AC15

AB5

AF4

AF3

AE3

AE2

AD15

AE9

AE5

AB10

AF10

AD10

AC10

AE10

AB9

AB15

AF15

H22

H21

L22

L21

C_-BE0

C_-BE1

C_-BE2

C_-BE3

-PREQ0

-PREQ1

-PREQ2

-PREQ3

-PREQ4

-PCIREQ

-PGNT0

-PGNT1

-PGNT2

-PGNT3

-PCIGNT

-FRAME

-PLOCK

PAR

-SERR

-TRDY

-IRDY

-STOP

-DEVSEL

NBPCLK

-CLKRUN

C111

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

102P

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

-FRAME <9,14,16,17,19>

-PLOCK <14>

-DEVSEL <9,14>

C112

104P

AGND

AD[0..31] <9,14,16,17,19>

C_-BE[0..3] <9,14,16,17,19>

-PREQ0 <14>

-PREQ1 <14,16>

-PREQ2 <14,17>

-PREQ3 <14>

-PREQ4 <14>

-PCIREQ <9>

-PGNT0 <14>

-PGNT1 <14>

-PGNT2 <14>

-PGNT3 <14,19>

-PCIGNT <9>

PAR <9,14>

-SERR <9,14>

-TRDY <9,14,16,17,19>

-IRDY <9,14,16,17,19>

-STOP <9,14>

NBPCLK <5>

-CLKRUN <11>

80S/0805

L7

EC8

10U/16V/S

L8

80S/0805

VCC2_5

R75

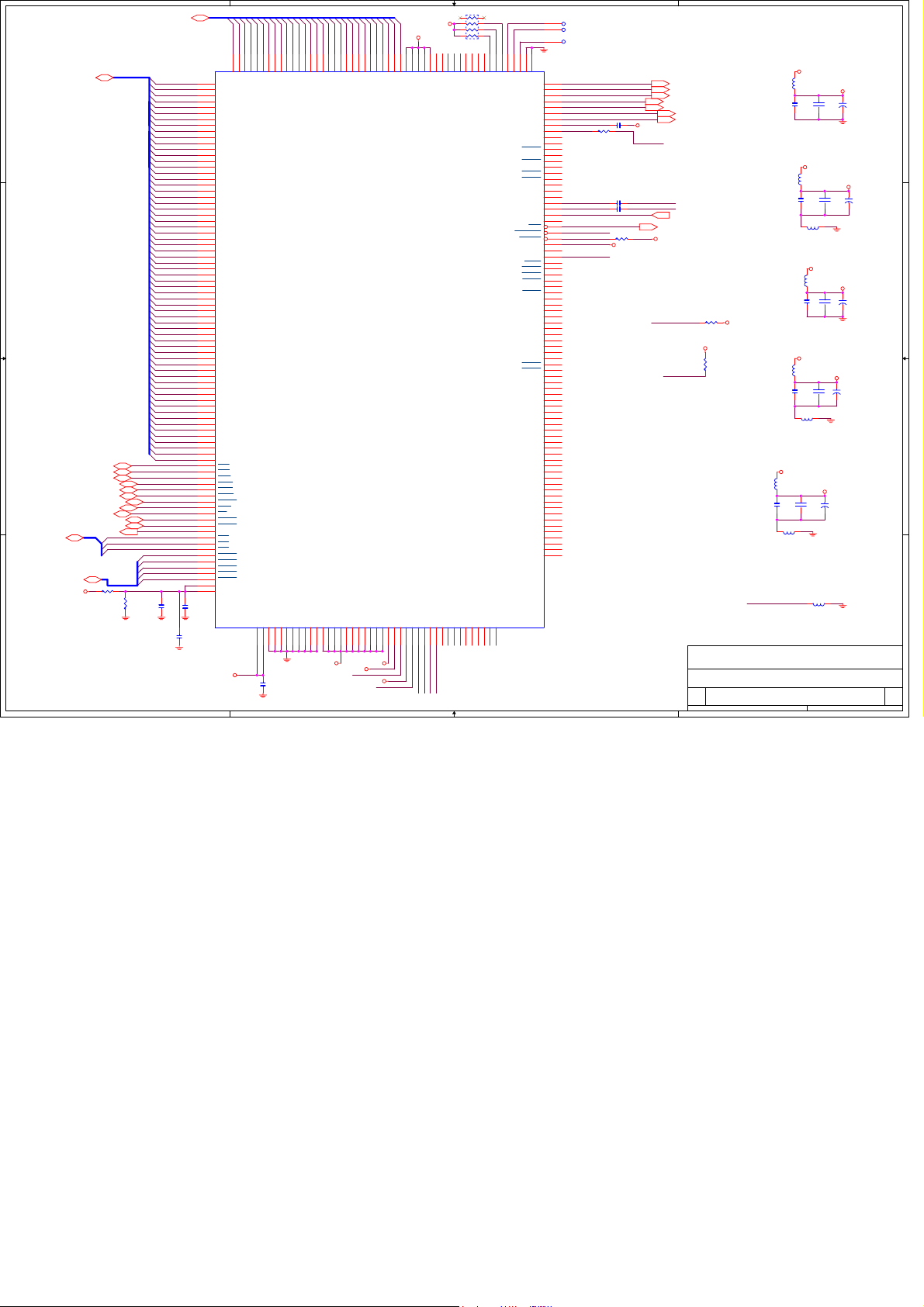

DCLK0<5>

D D

C104 10P

PLACE THESE COMPONENTS NEAR NB

1

DCLKO_

22

DCLKI

R76

PLLTEST

4.7K

VCC2_5

C231 X_105P

C229 X_105P

C228 X_104P

C230 X_104P

2

VCC3

C126 104P

C95 105P

C119 104P

C120 105P

C43 105P

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

3

Date: Sheet

North Bridge VT8601-2

MS-9108

4

722Friday, September 21, 2001

0A

of

Page 8

5

4

3

2

1

DIMM1

DIM1

MD63

MD[0..31]<7>

D D

MA[0..14]<7>

C C

-MRAS<7>

-MCAS<7>

-MCS0<7>

-MCS1<7>

MDQM[0..7]<7>

B B

-MWE<7>

DCLK1<5>

DCLK2<5>

DCLK3<5>

DCLK4<5>

-MCS0

-MCS1

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA13

MA14

MA11

MA12

MDQM7

MDQM6

MDQM5

MDQM4

MDQM3

MDQM2

MDQM1

MDQM0

2

3

4

5

7

8

9

10

11

13

14

15

16

17

19

20

55

56

57

58

60

65

66

67

69

70

71

72

74

75

76

77

33

117

34

118

35

119

36

120

37

121

38

123

126

132

122

39

115

111

30

114

45

129

28

29

46

47

112

113

130

131

27

48

42

125

79

163

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11/A13

A12/DU

A13/DU

BA0/A11

BA1/A12

-RAS

-CAS

-RAS0/S0

-RAS1/S1

-RAS2/S2

-RAS3/S3

DQM0/-CAS0

DQM1/-CAS1

DQM2/-CAS2

DQM3/-CAS3

DQM4/-CAS4

DQM5/-CAS5

DQM6/-CAS6

DQM7/-CAS7

-WE0

-WE2

CLK0

CLK1

CLK2

CLK3

DIMM 25 degree

ADDR.=1010000B

A A

MDP0

MDP1

MDP2

MDP3

MDP4

MDP5

MDP6

MDP7

REGE

CKE0

CKE1

MD31

86

D32

MD30

87

D33

MD29

88

D34

MD28

89

D35

MD27

91

D36

MD26

92

D37

MD25

93

D38

MD24

94

D39

MD23

95

D40

MD22

97

D41

MD21

98

D42

MD20

99

D43

MD19

100

D44

MD18

101

D45

MD17

103

D46

MD16

104

D47

MD15

139

D48

MD14

140

D49

MD13

141

D50

MD12

142

D51

MD11

144

D52

MD10

149

D53

MD9

150

D54

MD8

151

D55

MD7

153

D56

MD6

154

D57

MD5

155

D58

MD4

156

D59

MD3

158

D60

MD2

159

D61

MD1

160

D62

MD0

161

D63

21

22

52

53

105

106

136

137

147

VCC3

CKE0

128

CKE1

63

83

SDL

82

SDA

165

SA0

166

SA1

167

SA2

31

NC

44

NC

62

NC

146

NC

6

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VCC3

18

26

40

41

49

59

73

84

90

102

110

124

133

143

157

168

CKE0 <7>

CKE1 <7>

SMBCLK <5,11>

SMBDATA <5,11>

MD[32..63] <7>

MA12

R93 X_10K

R90 10K

MA14

All power on strapping default are

Low. Only MA11 defalut is High.

MA14,MA12 - CPU Bus Frequency Select

00 : 66MHz, 01 : 100MHz, 10 : AUTO, 11 : 133MHz

VCC3

C150

104P

C159

104P

C166

104P

C162

104P

VCC3

VCC3

VCC3

C148

104P

C170

104P

C169

104P

C39

104P

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

DIMM

MS-9108

822Friday, September 21, 2001

1

0A

Page 9

8

-FRAME<7,14,16,17,19>

-IRDY<7,14,16,17,19>

-TRDY<7,14,16,17,19>

-STOP<7,14,16,17,19>

-DEVSEL<7,14,16,17,19>

C_-BE[0..3]7,14,16,17,19>

D D

PAR<7,14,16,17,19>

-SERR<7,14,16,17>

-PIRQA<14>

-PIRQB<14>

-PIRQC<14>

-PIRQD<14>

-PCIRST

,13,14,16,17,19>

SBCLK<5>

-PCIREQ<7>

-PCIGNT<7>

PDD[0..15]<13>

C C

PIDE_IN3<12>

PIDE_IN4<12>

LCD6<12>

LCD7<12>

B B

INTR<3,4>

NMI<3,4>

-A20M<3,4>

-FERR<3,4>

-IGNNE<3,4>

C_-BE0

C_-BE1

C_-BE2

C_-BE3

AD18

-PCIRST

-PCIGNT

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

BITCLK

SDIN0

SDIN1

PIDE_IN3

PIDE_IN4

INTR

NMI

-A20M

-FERR

-IGNNE

F18

F19

F20

G17

G16

J19

G20

F17

C19

C20

G19

G18

A16

D17

C17

B17

B16

E16

L18

L19

P16

P18

P20

R17

R19

T16

T18

T20

T19

T17

R20

R18

R16

P19

P17

N20

W18

V17

Y17

V16

Y16

U15

W15

U14

Y15

V15

T15

W16

U16

W17

Y18

Y19

U7

Y7

V7

Y8

7

U11A

FRAME#

IRDY#

TRDY#

STOP#

DEVSEL#

C_BE0#

C_BE1#

C_BE2#

C_BE3#

IDSEL

PAR

SERR#

PIRQA#

PIRQB#

PIRQC#

PIRQD#

PCIRST#

PCICLK

PREQ#

PGNT#

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

BITCLK

SDIN0

SDIN1

SYNC

SDOUT

ACRST#

JBY/GPI22

JBX/GPI23

JAY/GPO22

JAX/GPO23

JAB2

JAB1

JBB2

JBB1

MSO

MSI

NMI

A20M#

FERR#

IGNNE#

VT82C686B

PCI INTERFACE

IDE INTERFACE

AC97

MIDI

GAME

CPU INTERFACE

6

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

PDIOR#

PDIOW#

PIORDY

PDREQ

PDACK#

PDCS1#

PDCS3#

PDA0

PDA1

PDA2

SDIOR#

SDIOW#

SIORDY

SDREQ

SDACK#

SDCS1#

SDCS3#

SDA0

SDA1

SDA2

CPURSTINTR

SMI#

STPCLK#

GPO7/SLP#

5

AD0

L17

AD0

AD1

L16

AD1

AD2

K20

AD2

AD3

K19

AD3

AD4

K18

AD4

AD5

K17

AD5

AD6

K16

AD6

AD7

J20

AD7

AD8

J18

AD8

AD9

J17

AD9

AD10

J16

AD11

H20

AD12

H19

AD13

H18

AD14

H17

AD15

H16

AD16

F16

AD17

E20

AD18

E19

AD19

E18

AD20

E17

AD21

D20

AD22

D19

AD23

D18

AD24

B20

AD25

A20

AD26

A19

AD27

B19

AD28

A18

AD29

B18

AD30

C18

AD31

A17

N17

N18

N16

N19

M20

L20

M16

M17

M19

M18

W19

W20

V20

Y20

V19

U17

U18

U19

V18

U20

V8W8

-HINIT

T6

INIT

-SMI

U6

-STPCLK

W7

-CPUSLP

T7

AD[0..31] <7,14,16,17,19>

-PDIOR <13>

-PDIOW <13>

PIORDY <13>

PDDREQ <13>

-PDDACK <13>

-PDCS1 <13>

-PDCS3 <13>

PDA0 <13>

PDA1 <13>

PDA2 <13>

-SDIOR <13>

-SDIOW <13>

SIORDY <13>

SDDREQ <13>

-SDDACK <13>

-SDCS1 <13>

-SDCS3 <13>

SDA0 <13>

SDA1 <13>

SDA2 <13>

-HINIT <3,4>

-SMI <3,4>

-STPCLK <3,4>

-CPUSLP <3,4>

4

3

2

1

-PCIREQ

R98 4.7K

-PCIGNT

R99 4.7K

A A

8

7

SDIN0

SDIN1

R101 10K

R103 10K

VCC3

MICRO-STAR INT'L CO., LTD.

Title

South Bridge VT82C686B-1

Size Document Number Rev

6

5

4

3

Date: Sheet of

MS-9108

2

922Friday, September 21, 2001

0A

1

Page 10

8

-MEMR<13>

D D

C C

B B

-MEMW<13>

RESDRV<13>

BTN_IN1<12>

BTN_IN2<12>

BTN_IN3<12>

BTN_IN4<12>

PIDE_IN1<12>

PIDE_IN2<12>

LCD0<12>

LCD1<12>

LCD2<12>

LCD3<12>

LCD4<12>

LCD5<12>

686OSC<5>

IRQ14<13>

IRQ15<13>

SOUT1<12>

-DTR1<12>

-RTS1<12>

-CTS1<12>

-DSR1<12>

-DCD1<12>

-RI1<12>

SIN1<12>

KBCLK<12>

KBDATA<12>

7

U11B

B2

AEN

ISA INTERFACE

H2

-SBHE

-REFRESH

-IOR

-IOW

-IOCS16

-MEMCS16

IOCHRDY

-IOCHCK

BTN_IN1

BTN_IN2

BTN_IN3

BTN_IN4

PIDE_IN1

PIDE_IN2

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ9

IRQ10

IRQ11

IRQ14

IRQ15

BALE

F2

SBHE#

E3

REFRESH#

D1

IOR#

C2

IOW#

U4

MEMR#

V4

MEMW#

A1

SMEMR#

B1

SMEMW#

F3

IOCS16#

F1

MEMCS16#

A2

IOCHRDY

F4

IOCHCK/GPI0

H1

TC

J1

RSTDRV

L3

DREQ0/GPI16

E2

DREQ1/GPI17

D3

DREQ3/GPI18

M1

DREQ5/GPI19

M5

DREQ6/GPI20

N4

DREQ7/GPI21

L2

DACK0#/GPO16

E1

DACK1#/GPO17

D2

DACK3#/GPO18

L4

DACK5#/GPO19

M3

DACK6#/GPO20

N2

DACK7#/GPO21

E4

OSC

H5

BCLK

G4

IRQ3

G3

IRQ4

G2

IRQ5

G1

IRQ6/GPI4/SLPBTN#

F5

IRQ7

H4

IRQ9

K3

IRQ10

K4

IRQ11

L1

IRQ14

K5

IRQ15

FLOPPY INTERFACE

D9

DRVDEN0

D6

DRVDEN1

D7

INDEX#

E9

MTR0#

A8

DS1#

B8

DS0#

C8

MTR1#

PARALLEL PORT

B13

ACK#

C13

BUSY

D13

PE

E13

SLCT

A15

ERROR#

C15

PINIT#

C16

AUTOFD#

E15

SLCTIN#

D16

STROBE#

SERIAL PORT 1 & 2

A11

TXD1

D11

DTR1#

B11

RTS1#

C11

CTS1#

C12

DSR1#

A12

DCD1#

E11

RI1#

B12

RXD1

PS2 KB/MS PORT

E5

KBCK

A5

KBDT/KBRC

IRDA INTERFACE

D12 E12

IRRX/GPO15 IRTX/GPO14

VT82C686B

6

SA0/SDD0

SA1/SDD1

SA2/SDD2

SA3/SDD3

SA4/SDD4

SA5/SDD5

SA6/SDD6

SA7/SDD7

SA8/SDD8

SA9/SDD9

SA10/SDD10

SA11/SDD11

SA12/SDD12

SA13/SDD13

SA14/SDD14

SA15/SDD15

SA16

SA17

SA18

SA19

LA20

LA21

LA22

LA23

SD10

SD11

SD12

SD13

SD14

SD15

XDIR/PCS0#/GPO12

XOE#/GPO13

ROMCS#

DIR#

STEP#

WDATA#

WGATE#

TRAK0#

WRTPRT#

RDATA#

HDSEL#

DSKCHG#

TXD2

DTR2#

RTS2#

CTS2#

DSR2#

DCD2#

RI2#

RXD2

MSCK/IRQ1

MSDT/IRQ12

5

SDD0

W1

SDD1

V2

SDD2

V1

SDD3

U3

SDD4

U2

SDD5

U1

SDD6

T4

SDD7

T3

SDD8

T2

SDD9

T1

SDD10

R5

SDD11

R4

SDD12

R3

SDD13

R2

SDD14

R1

SDD15

P5

SA16

P4

SA17

P3

SA18

K2

SA19

K1

SA20

J5

SA21

J4

SA22

J3

SA23

J2

SD0

Y1

SD0

SD1

Y2

SD1

SD2

W2

SD2

SD3

Y3

SD3

SD4

W3

SD4

SD5

V3

SD5

SD6

Y4

SD6

SD7

W4

SD7

SD8

L5

SD8

SD9

M2

SD9

SD10

M4

SD11

N1

SD12

N3

SD13

N5

SD14

P1

SD15

P2

T5

U5

C1

D8

E8

A7

B7

E7

A6

B6

C7

C6

B15

PD0

D15

PD1

A14

PD2

B14

PD3

C14

PD4

D14

PD5

E14

PD6

A13

PD7

D10

B9

E10

A9

C10

A10

C9

B10

D5

C5

-CTS2

-DSR2

-DCD2

-RI2

RXD2

SDD[0..15] <13>

SD[0..15] <13>

-LCD_RD <12>

-LCD_WR <12>

-ROMCS <13>

MSCLK <12>

MSDATA <12>

LCD_A0 <12>-LCD_CS<12>

4

-MEMCS16

-SBHE

-IOCS16

-IOR

IRQ9

IRQ3

IRQ5

IRQ4

IRQ6

-IOW

IOCHRDY

SA20

-IOCHCK

IRQ7

-REFRESH

IRQ11

SD3

SD4

SD5

SD1

SD7

SD6

SDD6

SDD10

SDD7

SDD14

SDD13

SDD12

SDD9

SDD8

SDD11

SD15

SA21

SD8

SD10

SA19

SA18

IRQ10

SA23

SA22

-CTS2

-DSR2

-DCD2

-RI2

RXD2

RN38

1

1

2

2

3

3

4

4

6

6

7

7

8

8

9510

9510

4.7K

RN33

1

1

2

2

3

3

4

4

6

6

7

7

8

8

9510

9510

4.7K

RN37

1

1

2

2

3

3

4

4

6

6

7

7

8

8

9510

9510

4.7K

RN36

1

1

2

2

3

3

4

4

6

6

7

7

8

8

9510

9510

4.7K

RN34

1

1

2

2

3

3

4

4

6

6

7

7

8

8

9510

9510

4.7K

RN26

1

1

2

2

3

3

4

4

6

6

7

7

8

8

9510

9510

4.7K

VCC5

VCC5

VCC5

VCC5

VCC5

VCC5

3

-ROMCS

SA17

SD9

SD12

SD11

SDD15

SA16

SD13

SD14

SD0

SDD0

SD2

SDD1

SDD2

SDD3

SDD4

SDD5

2

R131 4.7K

RN35

1

1

2

2

3

3

4

4

6

6

7

7

8

8

9510

9510

4.7K

RN40

1

1

2

2

3

3

4

4

6

6

7

7

8

8

9510

9510

4.7K

1

VCC3

VCC5

VCC5

A A

MICRO-STAR INT'L CO., LTD.

Title

South Bridge VT82C686B-2

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet of

MS-9108

2

10 22Friday, September 21, 2001

0A

1

Page 11

5

4

3

2

1

U11C

USB INTERFACE

C3

USBCLK

B3

USBP0-

A3

USBP0+

D4

D D

-RSMRST<15>

PW_GD<7,15>

VCC5

R120 10K

C164

SUSCLK

104P

SMBCLK<5,8>

SMBDATA<5,8>

-EXT_SMI<12>

-CLKRUN<7>

C C

CPU_FAN<13>

SYS_FAN<13>

B B

SMBCLK

SMBDATA -SUSTATE

-EXTSMI

-CLKRUN

10P

C176

C172 10P

R130

5.6M

X3

VCC3

TMP_VREF

VCC3

YCRY32.768C

+-20PPM

32pF

USBP1-

C4

USBP1+

IDE INTERFACE

V6

RSMRST#

W6

PWRGOOD

Y11

PWRBTN#

Y9

SUSC#

T10

SUSCLK

SUSA#/APICACK#/GPO1

U9

SMBCLK

T9

V5

Y10

W12

Y5

W5

R12

R13

T13

T12

U12

N6

F7

F10

F12

F13

F14

H6

J6

K6

M6

R11

H15

J15

K15

M15

N15

R7

R8

R14

F11

G6

F6

R6

P6

SUSB#/APICCS#/GPO2

SMBDATA

MISC.

SPKR

EXTSMI#

CLKRUN#

XTALI

DRQ2/OC1#/SERIRQ/GPIOE

XTALO

VDD_HWM

VSS_HWM

VREF_5V

FAN1

FAN2/GPIOB/GPIO9

POWER & GROUND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

GND

GND

GND

GND

GND

VT82C686B

LID/APICREQ#/GPI3

PME#/THRM#/GPI5

DACK2#/OC0#/GPIOF

CHAS/GPIOC/GPIO10

USB_VDD

USB_GND

USBP2USBP2+

USBP3USBP3+

IRQ8#/GPI1

BATLOW#/GPI2

SMBALRT#/GPI6

RING#/GPI7

GPO0

SUSST1#/GPO3

CPUSTP#/GPO4

PCISTP#/GPO5

GPIOA/GPIO8

GPIOD

VSENSE_20

VSENSE_30

VSENSE_25

VSENSE_12

T_SENSE1

T_SENSE2

VBAT

VCCSUS

VCCSUS

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GNDGND

F9

VCC5

F8

B4

A4

E6

B5

PIDE_DET

W11

SIDE_DET

U11

GPI3 CPU_IN

U10

GPI5

T11

GPI6

W10

GPI7

V11

WDI

T8

V9

W9

V10

CPU_CTRL

Y12

SYS_CTRL

V12

-EN_SMI

T14

GPIOD

U8

LCD_BLK

H3

LCD_BLA

G5

VSENSE1

U13

VSENSE2

W14

VSENSE3

V13

VSENSE4

Y14

CPU_IN

W13

STEM

Y13

-LCD_RST

V14

VCC3

2

C168

C23

104P

X_103P

Y6

R9

R10

J9

J10

J11

J12

K9

K10

K11

K12

L6

L9

L10

L11

L12

M9

M10

M11

M12

L15

P15

G15

R15F15

PIDE_DET <13>

SIDE_DET <13>

WDI <15>

-SUSTATE <7>

CPU_CTRL <13>

SYS_CTRL <13>

-EN_SMI <12>

LCD_BLK <12>

LCD_BLA <12>

CPU_IN <3>

-LCD_RST <12>

JBIOS1

YJ103

BPOWER

1

3

R137

1K

C186

104P

BTN[1.4](GPO3,4,5,6)

Connect to front panel

push button

YDI1N4148S

D6

D5

1N5817-S-DO-241AC-1mA

VCC3

AC

R112

1K

NEAR VT82C686A

1. VSENSE1 FOR CPU CORE VOLTAGE

DETECTION NOMIAL 1.6V

2. VSENSE2 FOR POWER SUPPLY 5V

12

3

BAT1

BH-D2

DETECTION

3. VSENSE3 FOR CPU LEVEL II CACHE

VOLTAGE DETECTION, NORMAIL 2.5V

4. VSENSE4 FOR POWER SUPPLY 12V

DETECTION

THERMAL RESISTOR BLOCK

TMP_VREF

CPU_IN <3>

R113

10KST

RT1

YT103S-1N

R115

30K-1%

VOLATEG MONITOR CIRCUIT

VSENSE1

VSENSE2

VSENSE3

VSENSE4

STEM

C203

102P

R106 16.2KST

R105 10KST

C156

102P

R110 53.6KST

R108 10KST

VCCP

VCC5

VCC2_5

+12V

GPI7

-CLKRUN

R117 100

A A

5

-EN_SMI

GPI6

GPI5

DIS_WDO

SMBCLK

SMBDATA

GPIOD

WDI

SUSCLK

-SUSTATE

GPI3

-LCD_RST

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

R104 4.7K

RN27

8P4R-4.7K

RN30

8P4R-4.7K

RN31

8P4R-4.7K

4

VCC3

3

VT82C686B DECOUPLING CAPACITORS

Place at backside of 686B

VCC3

C233

104P

C232

104P

C234

104P

C235

104P

2

Title

Size Document Number Rev

Date: Sheet of

NEAR VT82C686 TWO CONER

VCC3 VCC3

C147

1U/0805

C163

1U/0805

C175

104P

VCC3

MICRO-STAR INT'L CO., LTD.

South Bridge VT82C686B-3

MS-9108

1

C149

104P

11 22Saturday, September 22, 2001

0A

Page 12

8

7

6

5

4

3

2

1

PS2 KEYBOARD & MOUSE CONNECTOR

Reserved for Debugging & Testing

135

7

RN28

8P4R-4.7K

246

MSDATA<10>

D D

MSCLK<10>

KBDATA<10>

KBCLK<10>

C C

8

785634

12

1

3

5

7

9

CN7

180p

J1

1

3

5

7

9

D2x5-BK

VCC5

BTN2

VCC3

LCD_BLK1

LCD7

LCD5

LCD3

LCD1

-LCD_RW

-LCD_CS

2

2

4

4

6

6

8

8

10

10

LCD7<9>

LCD5<10>

LCD3<10>

LCD1<10>

-LCD_WR<10>

-LCD_CS<10>

HEADER 11X2_2MM

C173

0.1u

JP1

LCD CONNECTOR

2122

19

182017

1516

1314

1112

910

78

56

4

3

1

2

BTN3BTN4

BTN1

LCD_BLA1

-LCD_RST

LCD6

LCD4

LCD2

LCD0

-LCD_RD

LCD_A0

-LCD_RST <11>

LCD6 <9>

LCD4 <10>

LCD2 <10>

LCD0 <10>

-LCD_RD <10>

LCD_A0 <10>

LCD_BLA1

C161

X_104P

LCD_BLK1

C158

X_104P

RN29 100

Q10

YTR2N3904S

Ic=200mA

Vebo=6V

Vceo=40V

RN25 100

Q8

YTR2N3904S

Ic=200mA

Vebo=6V

Vceo=40V

VCC5

78

56

34

12

R118 1K

Q9

YTR2N3904S

Ic=200mA

Vebo=6V

Vceo=40V

VCC5

78

56

34

12

R121 1K

R123 1K

VCC5

LCD_BLA <11>

LCD_BLK

<11>

SERIAL PORT 1

DTR1

RTS1

1 2

3 4

5

7 8

9 10

COM1

COM_PORT

+12V

-DCD1 <10>

SIN1 <10>

-RI1 <10>

-CTS1 <10>

-DSR1 <10>

DSR1

CTS1

6

RT1

INPUT PORT INTERNAL PULL

HIGH

-EN_SMI<11>

PIDE1<13>

PIDE2<13>

PIDE3<20>

PIDE4<20>

BTN1

BTN2

BTN3

BTN4

INPUT DEBOUNCE

U12

1

2

3

4

5

6

7

8

9

10 11

EN

IN1

OUT1

IN2

OUT2

IN3

OUT3

IN4

OUT4

IN5

OUT5

IN6

OUT6

IN7

OUT7

IN8

OUT8

GND CH

MAX6818

20

VDD

19

18

17

16

15

14

13

12

VCC3

C174

0.1u

BTN_IN1 <10>

BTN_IN2 <10>

BTN_IN3 <10>

BTN_IN4 <10>

PIDE_IN1 <10>

PIDE_IN2 <10>

PIDE_IN3 <9>

PIDE_IN4 <9>

-EXT_SMI <11>

VCC5

C155 104P C152 104P

DCD1

RXD1

RT1

CTS1

DSR1

-DTR1

-DTR1<10>

-RTS1

-RTS1<10>

SOUT1 TXD1

SOUT1<10>

DCD1

DSR1

RXD1

RTS1

TXD1

CTS1

B B

RT1

DTR1

1

2

CN5

3

4

8P4C-180P

5

6

7

8

1

2

CN6

3

4

8P4C-180P

5

6

7

8

U10

20

2

3

4

7

9

16

15

13

11

VCC

RIN1

RIN2

RIN3

RIN4

RIN5

DIN1

DIN2

DIN3

GND

75232-1

V+

ROUT1

ROUT2

ROUT3

ROUT4

ROUT5

DOUT1

DOUT2

DOUT3

V-

C154 104P

D3 YDI1N4148S

V+

1

19

18

17

14

12

R107 33

5

R100 33

6

R111 33

8

10

D4 YDI1N4148S

V-

DCD1

RXD1 RTS1

TXD1

DTR1

-DCD1

SIN1

-RI1

-CTS1

-DSR1

VGA CONNECTOR

Reserved for Debugging & Testing

VCC5

JVGA1

1

2

1

RED<6>

GREEN<6>

BLUE<6>

A A

8

3

3

5

5

7

7

9

9

D2x5-BK_2MM

2

4

4

6

6

8

8

10

10

7

CONNECTOR

TOP VIEW

C122

120p

4.7K

C123

120p

VCC5

R86

MH3

X_150 Drill / 300 Pad

R85

4.7K

R83 47

R84 47

6

DDCDATA <6>

HSYNC <6>

VSYNC <6>

DDCCLK <6>

5

FM8

X_FIDUCIAL

FM5

X_FIDUCIAL

FM2

X_FIDUCIAL

FM3

X_FIDUCIAL

FM7

X_FIDUCIAL

FM1

X_FIDUCIAL

FM4

X_FIDUCIAL

FM6

X_FIDUCIAL

4

9

2

3

(NPTH)

4

1

MH1

X_150 Drill / 300 Pad

9

2

3

(NPTH)

4

1

MH4

X_150 Drill / 300 Pad

9

2

3

4

MH2

X_150 Drill / 300 Pad

9

2

3

4

5

6

7

(NPTH)

8

1

5

6

7

(NPTH)

8

1

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

Date: Sheet of

2

Connectors

MS-9108

12 22Friday, September 21, 2001

1

0A

5

6

7

8

5

6

7

8

3

Page 13

8

VCC3

CPU_CTRL<11>

D D

CHASSIS FAN CONNECTOR (CLOSE IDE CONNECTER)

VCC3

SYS_CTRL<11>

7

PROCESSOR 1 FAN CONNECT (CPU)

Q3

S

SI2303DS-S-SOT23

D

C8

0.1u

Q12

S

SI2303DS-S-SOT23

D

C189

0.1u

+12V

+12V

R28

10K

R116

10K

R27

4.7K

R114

4.7K

B

B

C9 0.1u

R22 4.7K

G

R19 1K

C

Q4

E

NPN-3904LT1-S-SOT23

C157 0.1u

R119 4.7K

G

R144 1K

C

Q7

E

NPN-3904LT1-S-SOT23

6

VCC3

CPUFAN1

3

2

1

YJ103BO

VCC3

SYSFAN1

3

2

1

YJ103BO

R109

10K

R124

10K

5

CPU_FAN <11>

SYS_FAN <11>

4

3

2

1

ATA33/66/100 PRIMARY IDE CONNECTOR

PDD[0..15]<9>

-HDRESET

RN59D 8P4R-22

RN59B 8P4R-22

RN60D 8P4R-22

RN60B 8P4R-22

RN61D 8P4R-22

RN61B 8P4R-22

RN62D 8P4R-22

RN62B 8P4R-22

PDDREQ<9>

-PDIOW<9>

-PDIOR<9>

PIORDY<9>

-PDDACK<9>

IRQ14<10>

PDA1<9>

PDA0<9>

-PDCS1<9>

R204 22

R184 22

R185 22

R186 22

R200 22

R201 22

RN57A

RN57B

RN57D

8P4R-22

R202

5.6K

R165 22

7 8

PDD6

3 4

PDD5

7 8

PDD4

3 4

PDD3 PDD12

7 8

PDD2

3 4

PDD1

7 8

PDD0

3 4

HP_DRQ

-HP_IOW

-HP_IOR

-HPDACK

HP_IRQ

C198

220P

R187

1K

HP_DA1

HP_DA0

-HP_CS1

1 2

3 4

7 8

R203

4.7K

HPD7PDD7

HPD6

HPD4

HPD3

HPD2

HPD1

HPD0

VCC5

IDE1

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

YJ220-CB-1

HPD8

HPD9

HPD10HPD5

HPD11

HPD12

HPD13

HPD14

HPD15

HP_DA2

-HP_CS3

C165

X_472P

DO NOT STUFF

56

12

56

12

56

12

56

12

R188

RN57C

RN47A

8P4R-22

PDD8

PDD9

PDD10

PDD11

PDD13

PDD14

PDD15

RN59C 8P4R-22

RN59A 8P4R-22

RN60C 8P4R-22

RN60A 8P4R-22

RN61C 8P4R-22

RN61A 8P4R-22

RN62C 8P4R-22

RN62A 8P4R-22

330

56

12

R122

15K

PIDE_DET <11>

PDA2 <9>

-PDCS3 <9>

PIDE1 <12>

16M BYTE TSOP-I DISK ON CHIP

C C

U17

SDD0

19

SDD[0..12]<10>

-PCIRST<9>

R153 10K

VCC5

R152 10K

B B

R151 X_10K

DOC_BUSY

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

A0

18

A1

17

A2

16

A3

15

A4

14

A5

11

A6

10

A7

9

A8

8

A9

7

A10

6

A11

5

A12

1

RSTIN

26

ID1

24

ID0

22

IF_CFG

23

LOCK

BUSY

20

BHE

GND

13

12

37

VDD

GND

GND

252736

48

D0

VDD

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

CE

OE

WE

REV

REV

REV

GND

MD-2211-D16-V3

VCC3

28

29

30

31

32

33

34

35

39

40

41

42

43

44

45

46

2

4

3

21

38

47

C190

104P

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

-ROMCS

-ROMCS <10>

-MEMR <10>

-MEMW <10>

SD[0..15] <10>

ATA33/66/100 SECONDARY IDE CONNECTOR

SDD[0..15]<10>

SDDREQ<9>

-SDIOW<9>

-SDIOR<9>

SIORDY<9>

-SDDACK<9>

IRQ15<10>

SDA1<9>

SDA0<9>

-SDCS1<9>

-HDRESET

RN47B 8P4R-22

RN47D 8P4R-22

RN48B 8P4R-22

RN48D 8P4R-22

RN49B 8P4R-22

RN49D 8P4R-22

RN50B 8P4R-22

RN50D 8P4R-22

R170

R168 22

R171 22

R172 22

R175 22

RN51A

RN51B

RN51C

8P4R-22

R169

5.6K

R166 22

SDD7

SDD6

SDD5

SDD2

SDD1

SDD0

22

HS_DRQ

-HS_IOW

-HS_IOR

-HSDACK

HS_IRQ

12

HS_DA1

34

HS_DA0

56

-HS_CS1

R173

1K

C194

220P

IDE2

R167

4.7K

1 2

HSD7

34

3 4

HSD6

78

5 6

HSD5

34

7 8

HSD4SDD4

78

9 10

HSD3SDD3

34

11 12

HSD2

78

13 14

HSD1

34

15 16

HSD0

78

17 18

19

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

VCC5

YJ220-CB-1

HSD8

HSD9

HSD12

C195

X_472P

5 6

1 2

5 6

1 2

5 6

1 2

5 6

R179 22

HS_DA2

-HS_CS3

DO NOT STUFF

SDD8

SDD9

SDD10HSD10

SDD11HSD11

SDD12

SDD13HSD13

SDD14HSD14

SDD15HSD15

R174 330

RN51D

7 8

R177 22R178 22

RN47C 8P4R-22

RN48A 8P4R-22

RN48C 8P4R-22

RN49A 8P4R-22

RN49C 8P4R-22

RN50A 8P4R-22

RN50C 8P4R-22

R176

15K

SIDE_DET <11>

SDA2 <9>

-SDCS3 <9>

PIDE2 <12>

8M BYTE TSOP-II DISK ON CHIP

U16

SDD0

SDD[0..15]<10>

A A

VCC5

R133 10K

-PCIRST<9>

VCC5

8

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

DOC_BUSY

SDD11

SDD12

12

11

10

9

8

7

6

5

27

26

23

25

4

28

29

3

2

30

X_MD2810

A0

A1

A2

A3

A4

A5

A6

A7

A8

REV

BUSY

A11

A12

REV

RSTIN

ID1

ID0

VDD

SYS_5V

7

SD0

13

D0

SD1

14

D1

SD2

15

D2

SD3

17

D3

SD4

18

D4

SD5

19

D5

SD6

20

D6

SD7

21

D7

1

-ROMCS

22

CE

24

OE

31

WE

VCC3

32

VDD

C177

16

GND

104P

-MEMR <10>

-MEMW <10>

6

SD[0..7] <10>

5

IDE RESET GENERATOR CIRCUIT

RESDRV<10>

4

R136 1K

3

VCC5

R138

1K

Q11

YTR2N3904S

Ic=200mA

Vebo=6V

Vceo=40V

-HDRESET

MICRO-STAR INT'L CO., LTD.

Title

Size Document Number Rev

Date: Sheet of

2

FAN-DOC-IDE

MS-9108

13 22Friday, September 21, 2001

0A

1

Page 14

8

7

6

5

4

3

2

1

PCI SLOT

PCI1

B1

-12V

B2

TCK

B3

GND

B4

TDO

B5

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B52

B53

B54

B55

B56

B57