Page 1

1

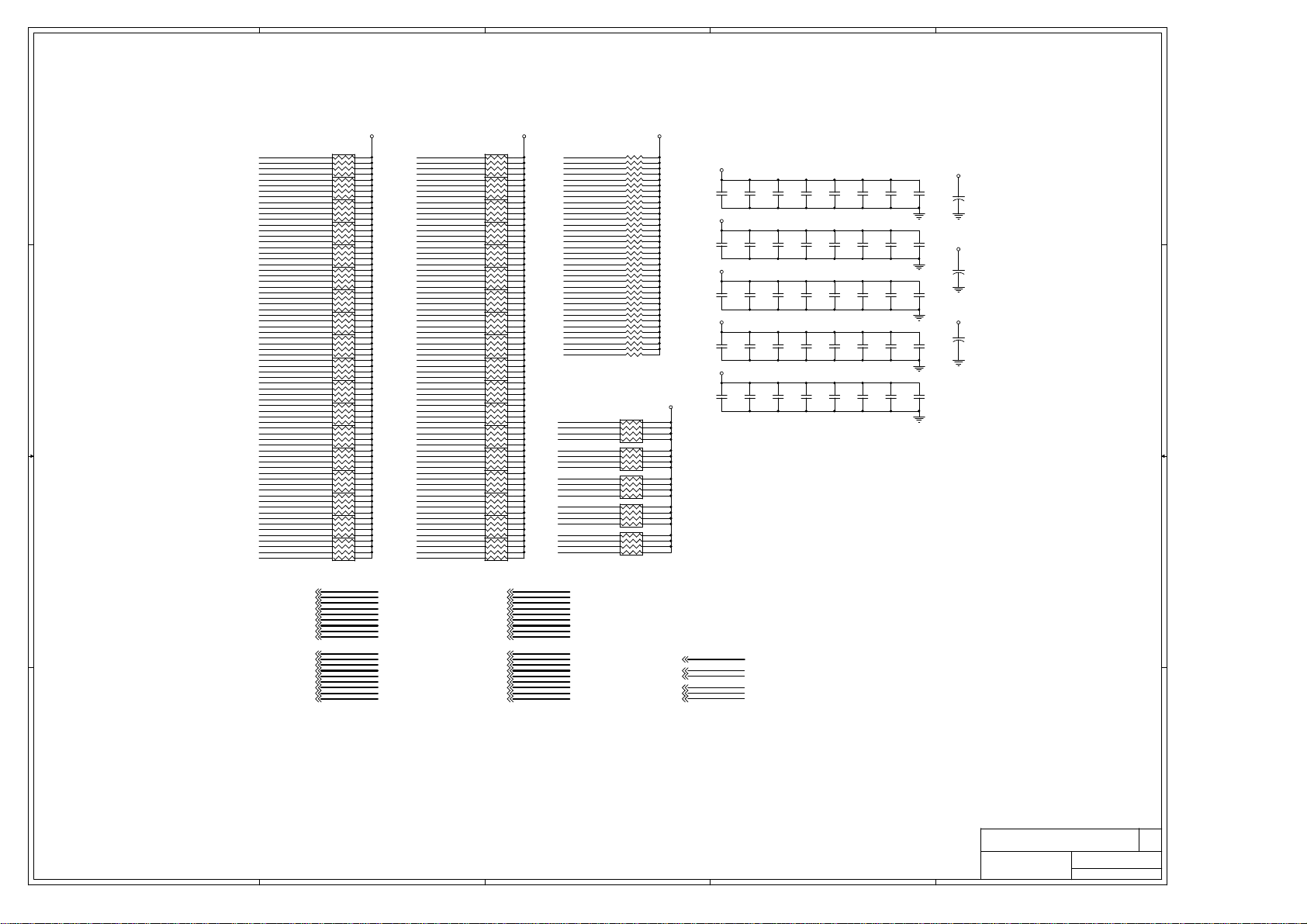

MS-9102 0D

Dual Intel Foster Processor

ServerWorks GCLE + CIOB-X2 + CIOB-G + CSB5 Chipset

National Semiconductor PC87417 LPC IO Chip

Cover Sheet 1

Block Diagram

Clock & Reset Map

2

3

4,5,6,7Foster CPU #1 & #2

CPU GTLREF & SMBus Address 8

ITP Connector

A A

Ratio & Level Shift Circuit

CPU Level Shift & SMI Circuit

CMIC-LE

9

10

11

12,13,14,15,16

DDR Module 1/2/3/4/5/6 17,18,19

Memory Termination #1 & #2

Clock Synthesizer

PCI 33 Clock Buffer

DDR Clock Buffer

CIOB-X2

20,21

22

23

24,25,26

27,28CIOB-G

HW/AUDIO

PCI 64 Slot 1/3 (66MHz/64Bit)

29

31

30

32PCI 64 Slot 2 (66MHz/64Bit)

SCSI AIC7899W/7902

AGP Pro Slot

PCI-X Slot 1/2

33-37

38

39

CSB5

INT MAPING

LAN BCM5702

USB Connector

ATA-HDD Connector

NS PC87417 SIO & NVRAM & IO CONN

XAD Bus/Flash ROM

IO COM /PS2

Hardware Monitor & CPU FAN

Hardware Monitor 2 & SYS FAN

POWER RESUME STATUS

I2C Switching & BOSS

VCC25 & AVTT

VRM 9.x for CPU1 & CPU2

VDD_AGP & VAGP_CARD & V_IMB

Front Panel

Power OK Circuit

Reset Ckt & 3VSB/USB Power

Note

40,41

42

43,44

45

46

47-48

49

50

51

52

53

54

55

56

57

58

59

60

61Manual Part

62-68

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

1

http://www.msi.com.tw

Micro Star Restricted Secret

Cover Sheet

Last Revision Date:

Thursday, March 21, 2002

Sheet

1 68

Rev

0D

of

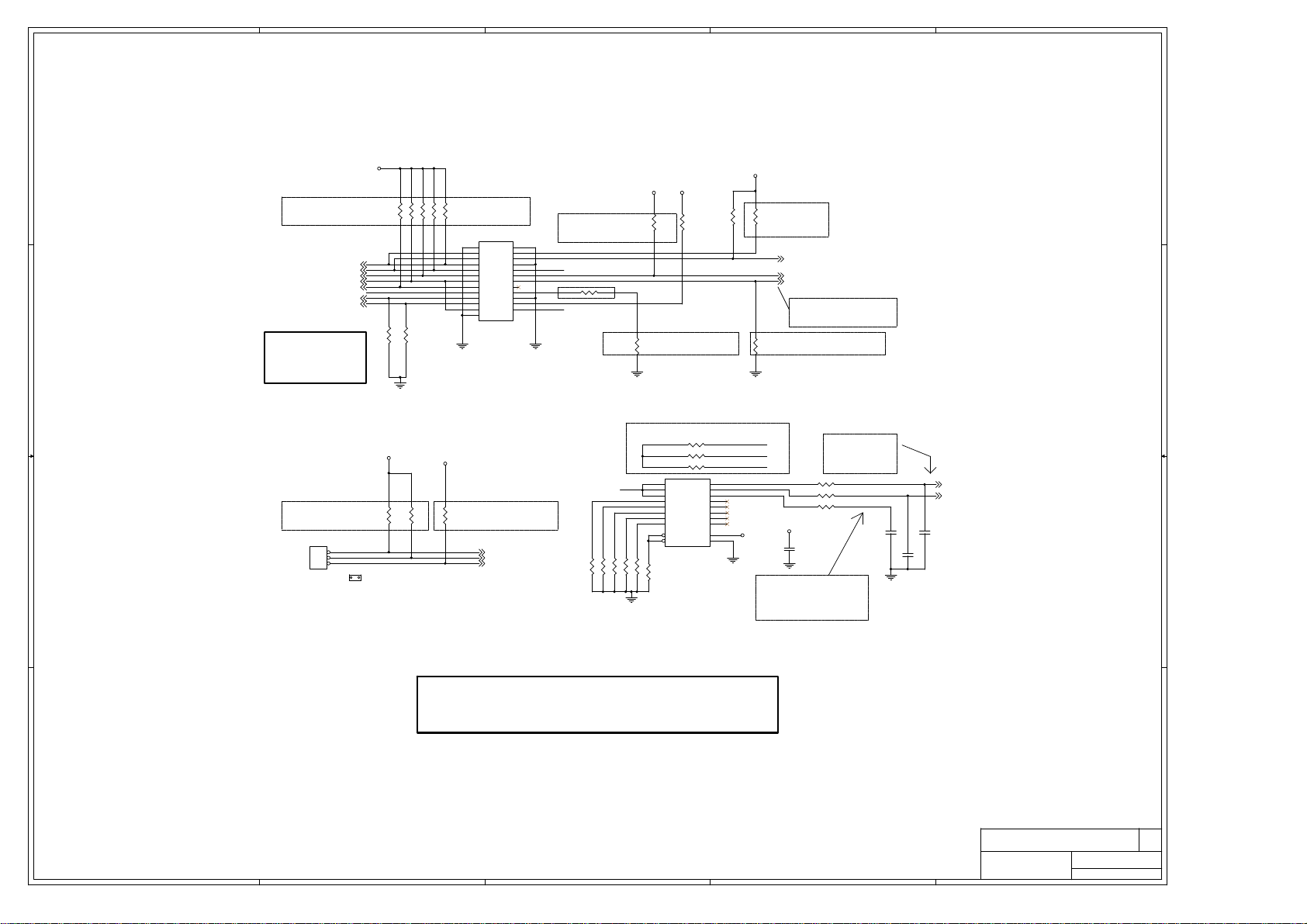

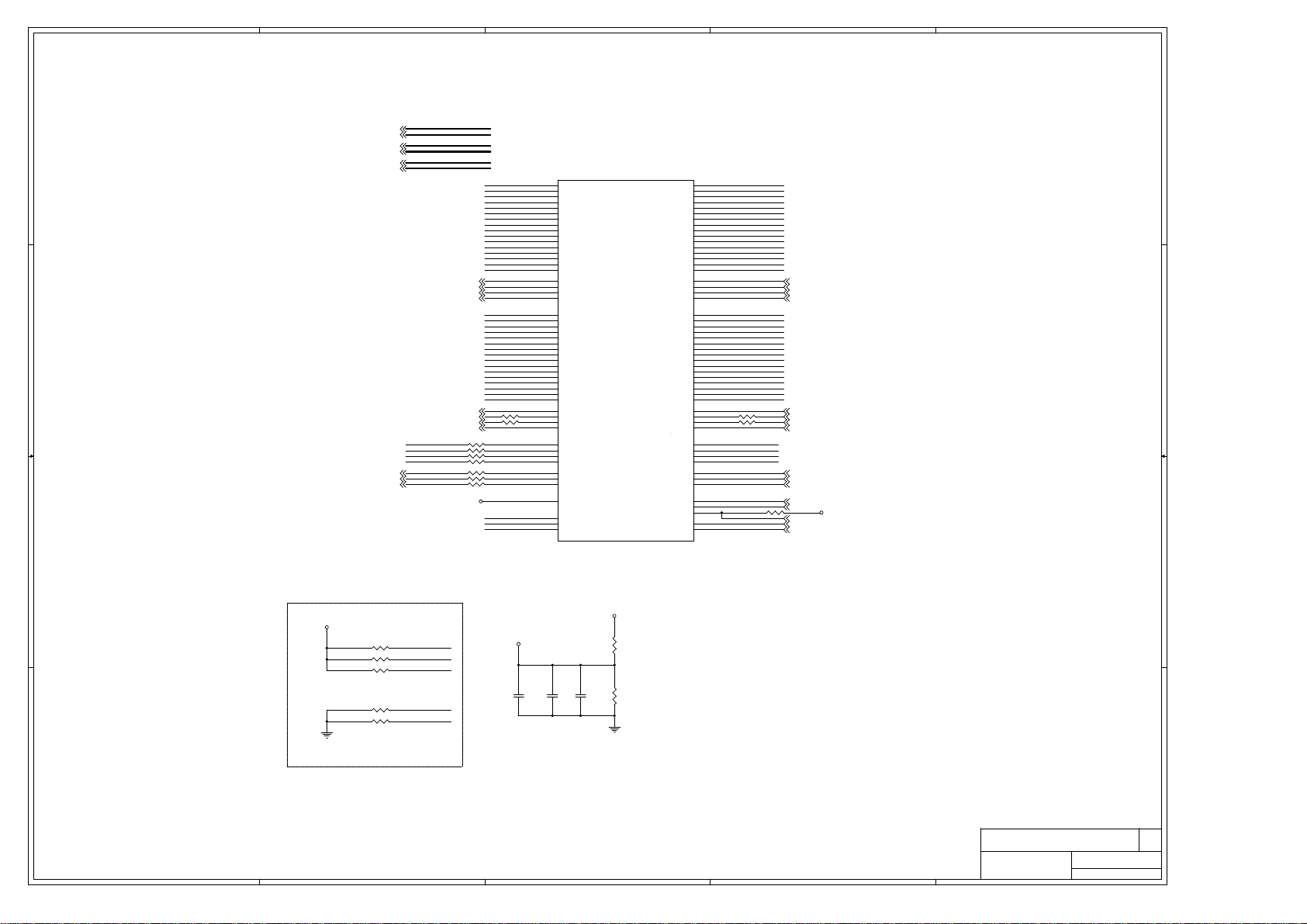

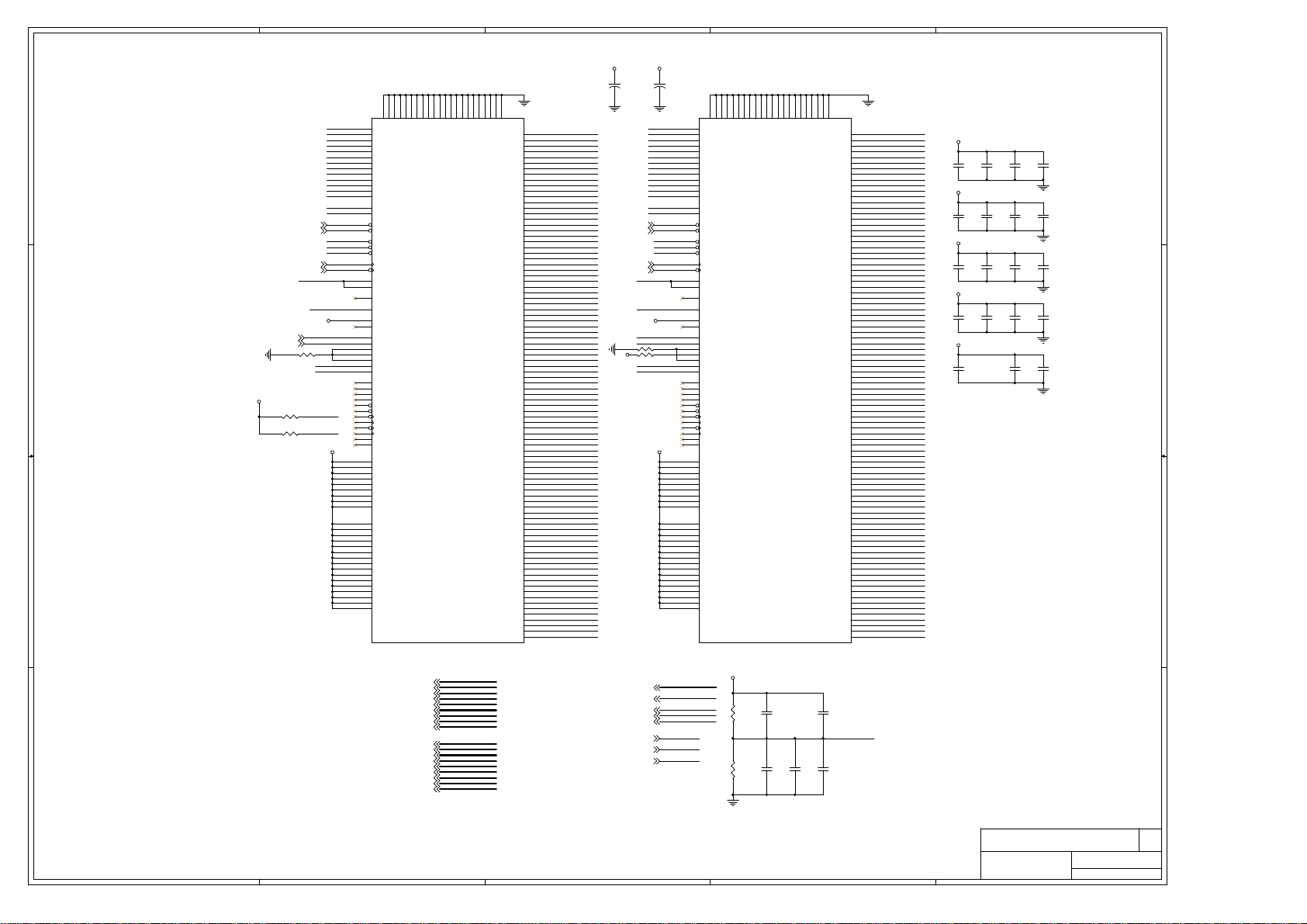

Page 2

MS-9102 Block Diagram

Full ATX - 12"*13"*8 Layers (10 MTHole)

BLOCK DIAGRAM

Scoket 604 CPU1

CTRL

ADDR

DATA

ADDR

CTRL

1

Scoket 604 CPU2 VRM

CTRL

ADDR

GTL BUS

DATA

FSB Suport 100/133MHz Foster/Gullatin CPU Support VRM9.0

DATA

6 DDR

DIMM

Modules

Support Register ECC DDR

DIMM Only (Up to 12GB)

66MHz/64Bit or 33MHz/32Bit Support

P64 PCI CONN

2

P64 PCI CONN

1

P64 PCI CONN

3

PCI 66MHz/64Bit Bus

ServerWorks

CIOB-X2

A-IMB Bus

SM BUS

ServerWorks

CMIC-LE

Dual Channel

AIC 7899W/7902

Ultra160/320 SCSI

Ultra 160/320

EMRL

Ultra 160/320

PCI-X Bus

PCI-X CONN

1

PCI-X Bus (Up to 133MHz)

PCI-X CONN

2

Thin IMB

Bus

B-IMB Bus

ServerWorks

CIOB-G

CTRL

ADDR

DATA

AGP Pro Slot

A A

IDE Primary

IDE Secondary

USB Port 1/2/3

USB Port 4

W83782D HWM

W8378785R HWM

Ultra DMA100

USB 1.1

SM BUS

SM BUS

ServerWorks

CSB5 2.0

LPC

LPC

LPC

XAD Bus

FLASH ROM

PCI32 Bus

CREATIVE 5880

H/W AUDIO

BCM 5702

GIGA LAN

Floopy

NS

PC87417

Keyboard

Mouse

Serial 1

Serial 2

1

Parallel

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

Block Diagram

Last Revision Date:

Thursday, March 21, 2002

Sheet

2 68

Rev

0D

of

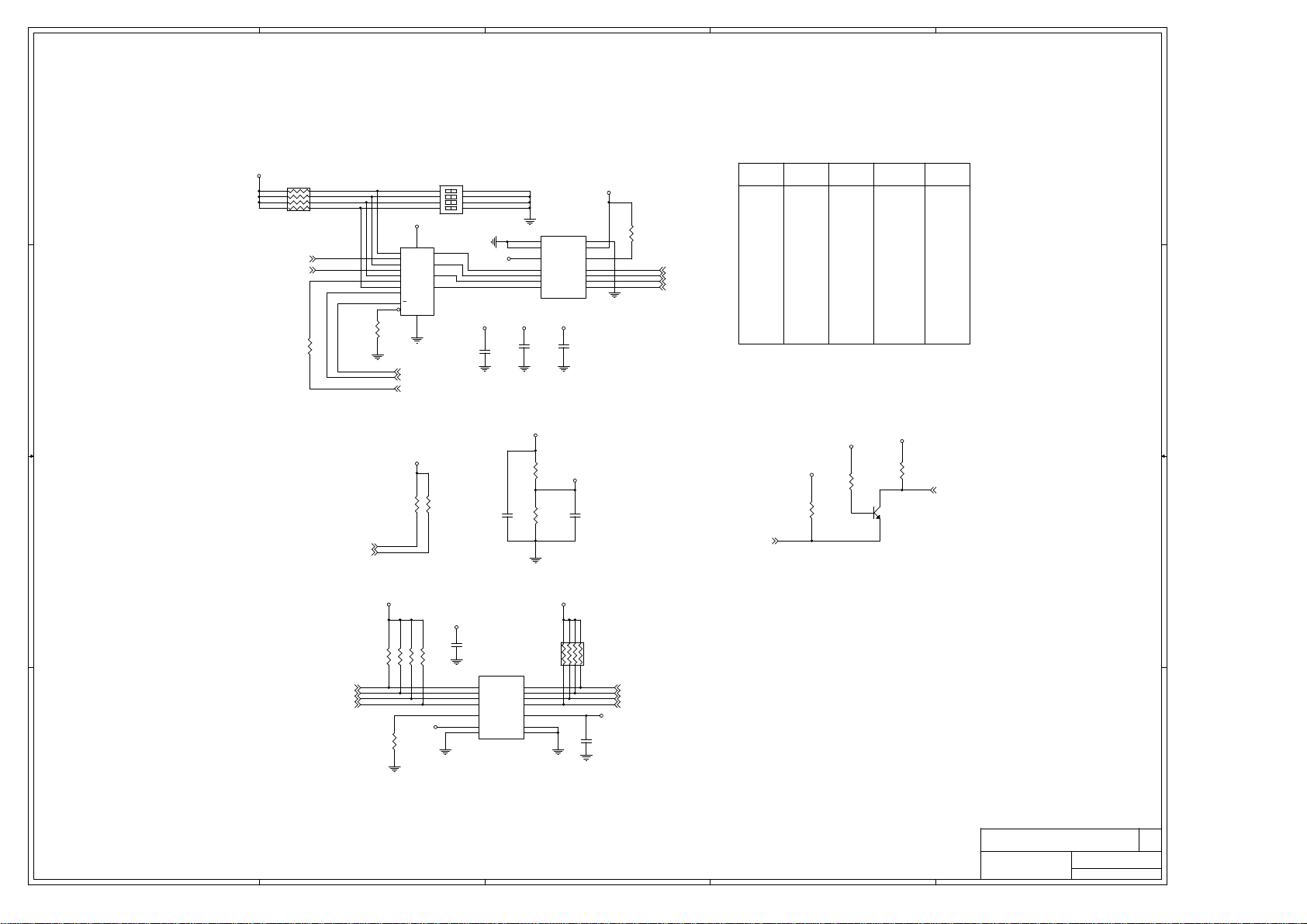

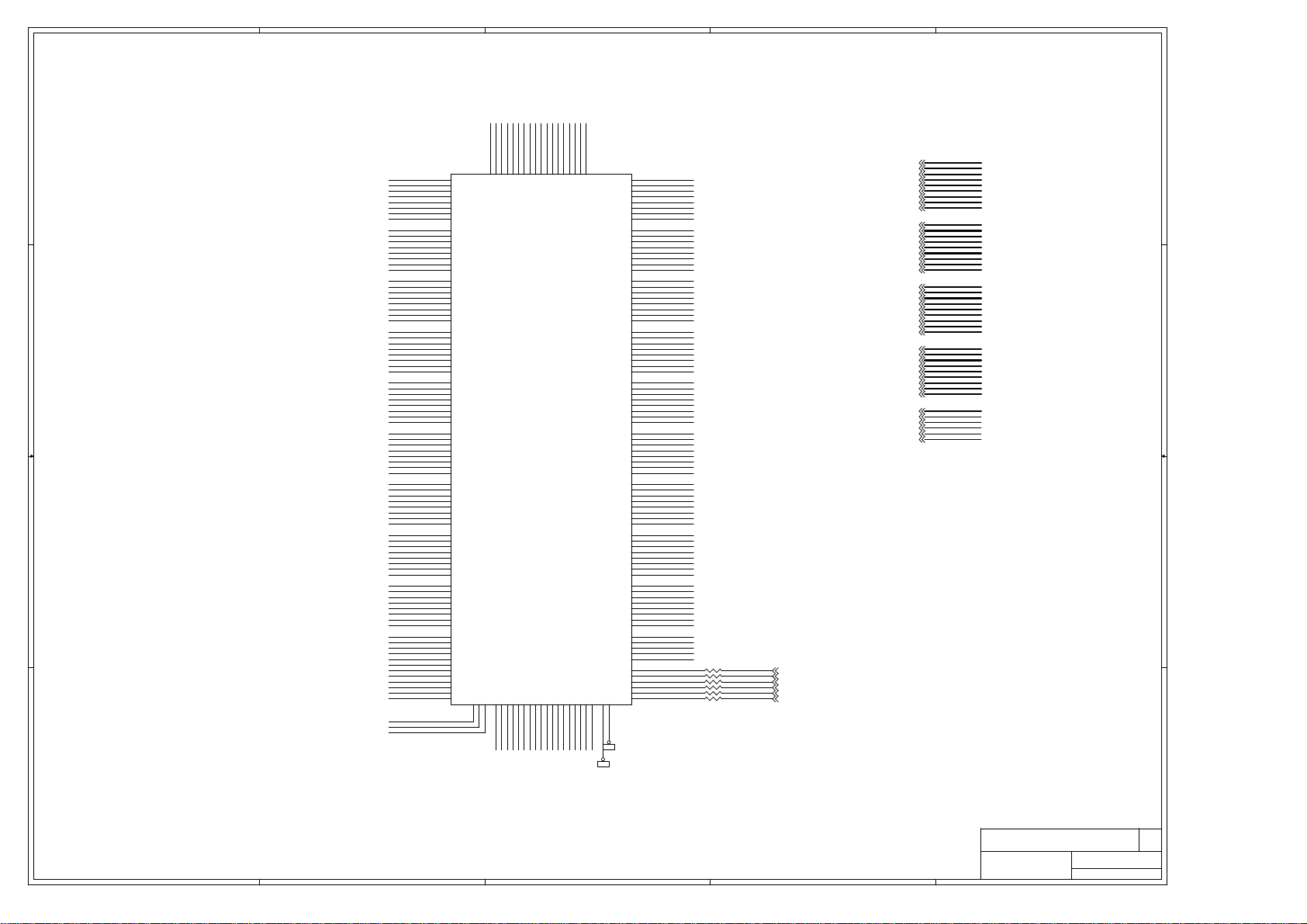

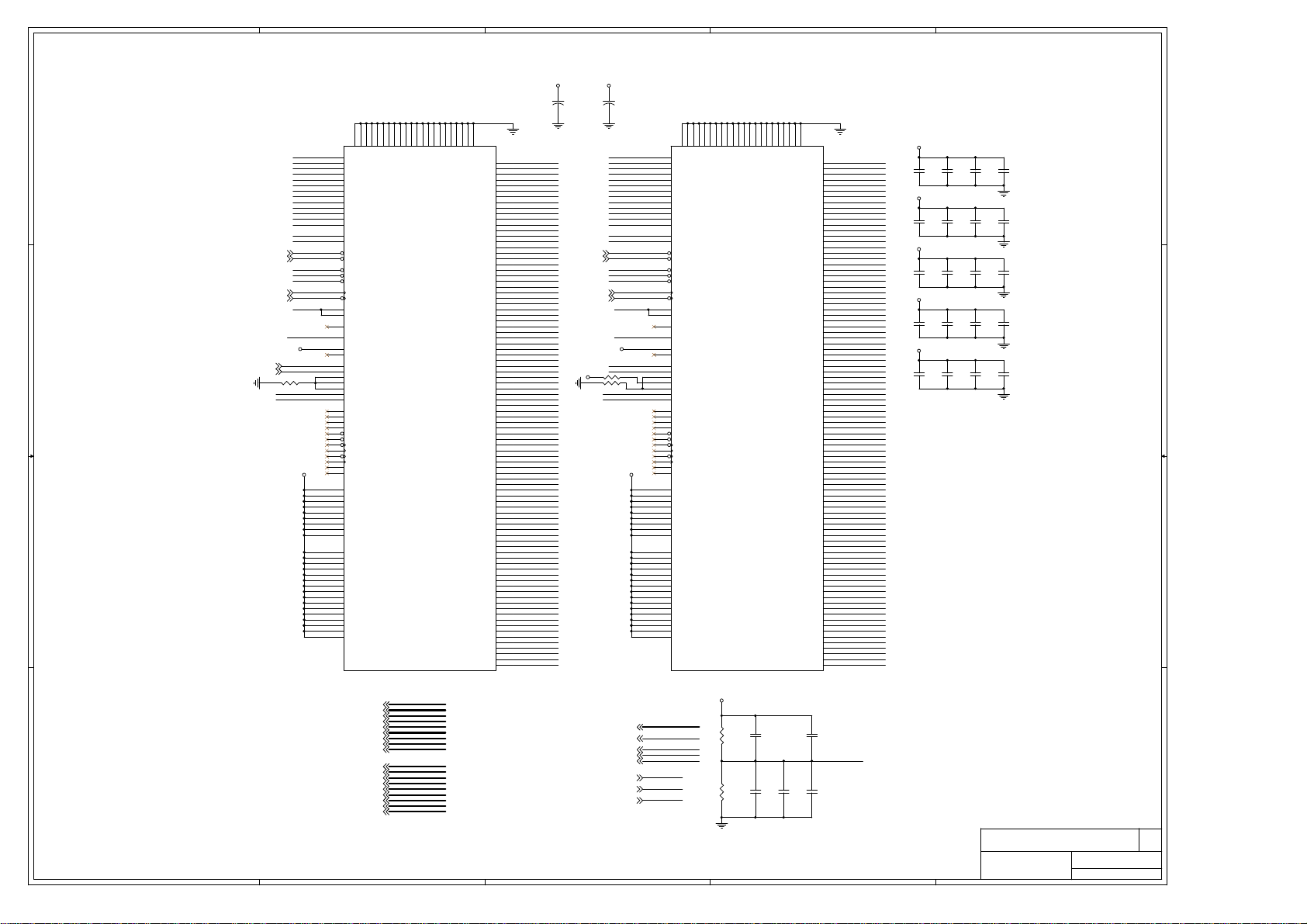

Page 3

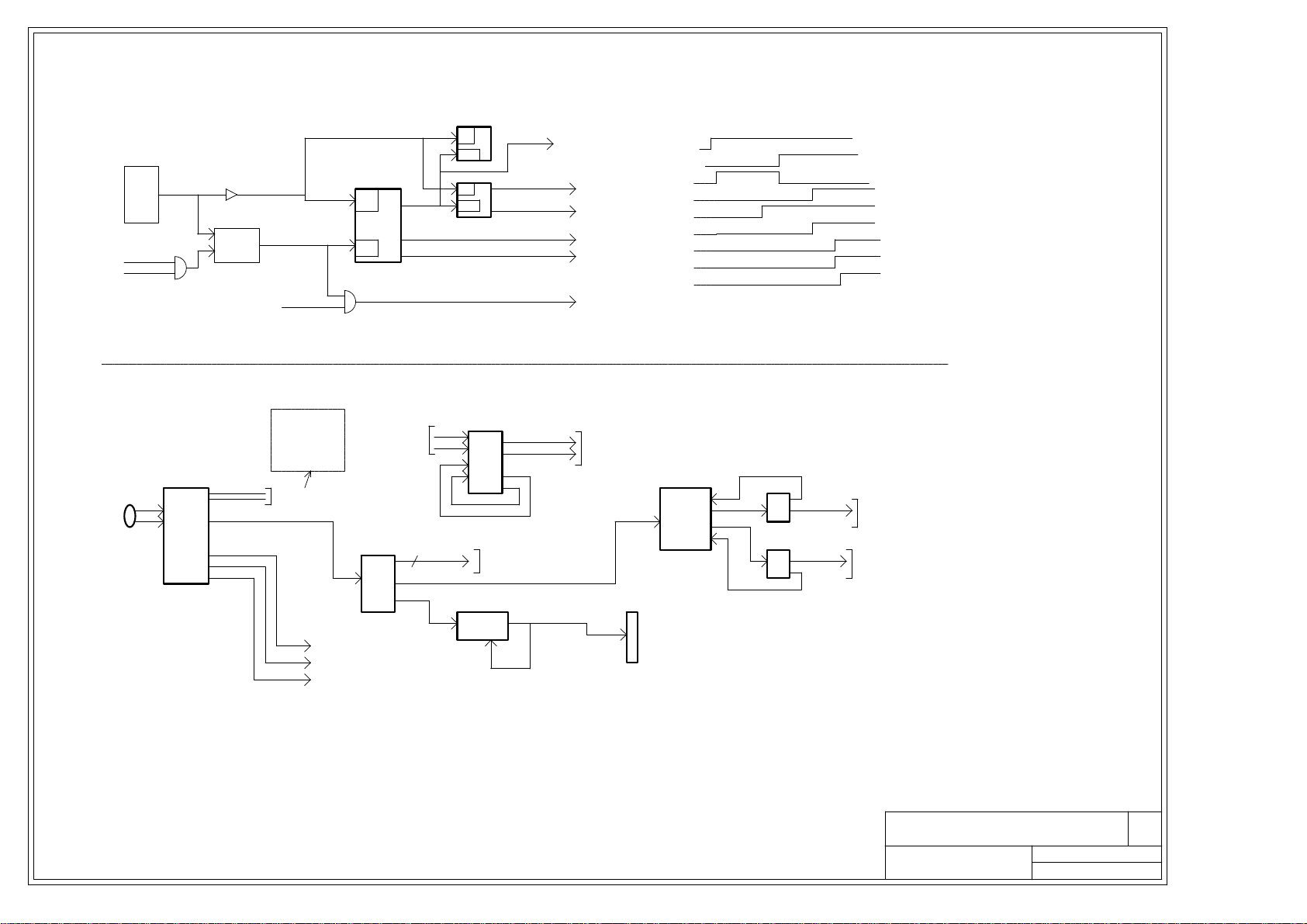

1

RESET SCHEME

WTX

POWER

PS_PWRGD

SUPPLY

CONN.

RESET SWITCH

ITP_RESET#

AND

INVERTER

RESET GEN

140mS PERIOD

RESET Vth =

4.5V

PS_PWRGD#

CPU_VRM_PWRGD

POWERGOOD

PS_PWRGD#

PLLRST

PCIRST#

CMIC CIOB'S

SRESET#

AND

RSB5

PLLRST

PCIRST#

PLLRST

PCIRST#

PCIRST#

P1/P2_PCIRST#

S1/S2_PCIRST#

RESET FOR RSB

PCI BUS

RESETS FOR PCI

BUSES

PROC_RESET# CPU RESET

RESETDLY# Config RESET - 4

BCLK delay w.r.t.

PROC_RESET#

CPU_PWRGD

POWER

t0

PSU PWR GOOD

PLL RST

t0+100mS

POWERGOOD

VRM POWERGOOD

PROCESSOR POWERGOOD

PROCESSOR RESET

PCI RESET

CONFIG RESET

t0+100mS

t0+50mS

t0+120mS

t0+120mS

t0+120mS+1mS

t0+120mS+1mS

t0+120mS+1mS+4 clocks

CLOCKING SCHEME

- CPU 0

- CPU1

- CMIC

- DIMM PLL

A A

14.318 MHz

X-TAL

CLK SYNTH.

BCLK

BCLK#

33MHz

48MHz

48MHz

14MHz

- ITP Connector

- PROBE Header

6 Pairs of 100MHz

Differential

CLOCKs

From CLK

SYNTH.

33MHz Low Skew

Buffer

DIMM PLL

BCLK

BCLK#

FBOUT#

FBOUT

8 Pairs of 100MHz

Differential CLOCKs

for 8 DIMMs

33MHz

CIOB

P1_CLKO

S1_CLKO

P1_FBCLK

TO PCI

CONNs.

PCI-X PLLs

n

33MHz CLOCK TO RSB and

DEVICES behind it.

S1_FBCLK

TO PCI

CONNs.

48MHz USB CLK to RSB

48MHz CLK to SIO

14 MHz CLK to RSB

33MHz

CIOB-G

FBCLK

66MHz

AGP CONN.

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

1

http://www.msi.com.tw

Micro Star Restricted Secret

Clock & Reset Map

Last Revision Date:

Thursday, March 21, 2002

Sheet

3 68

Rev

0D

of

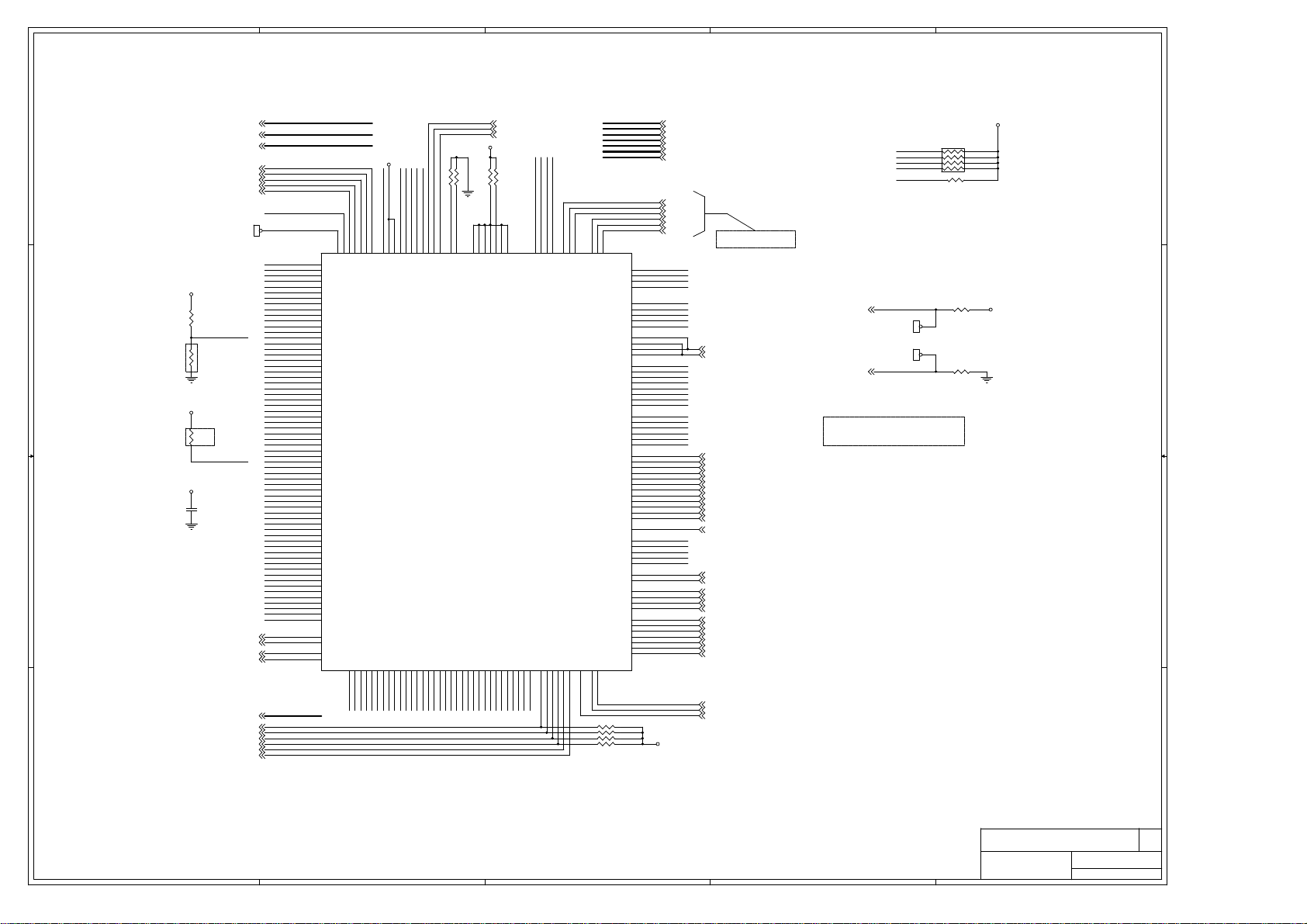

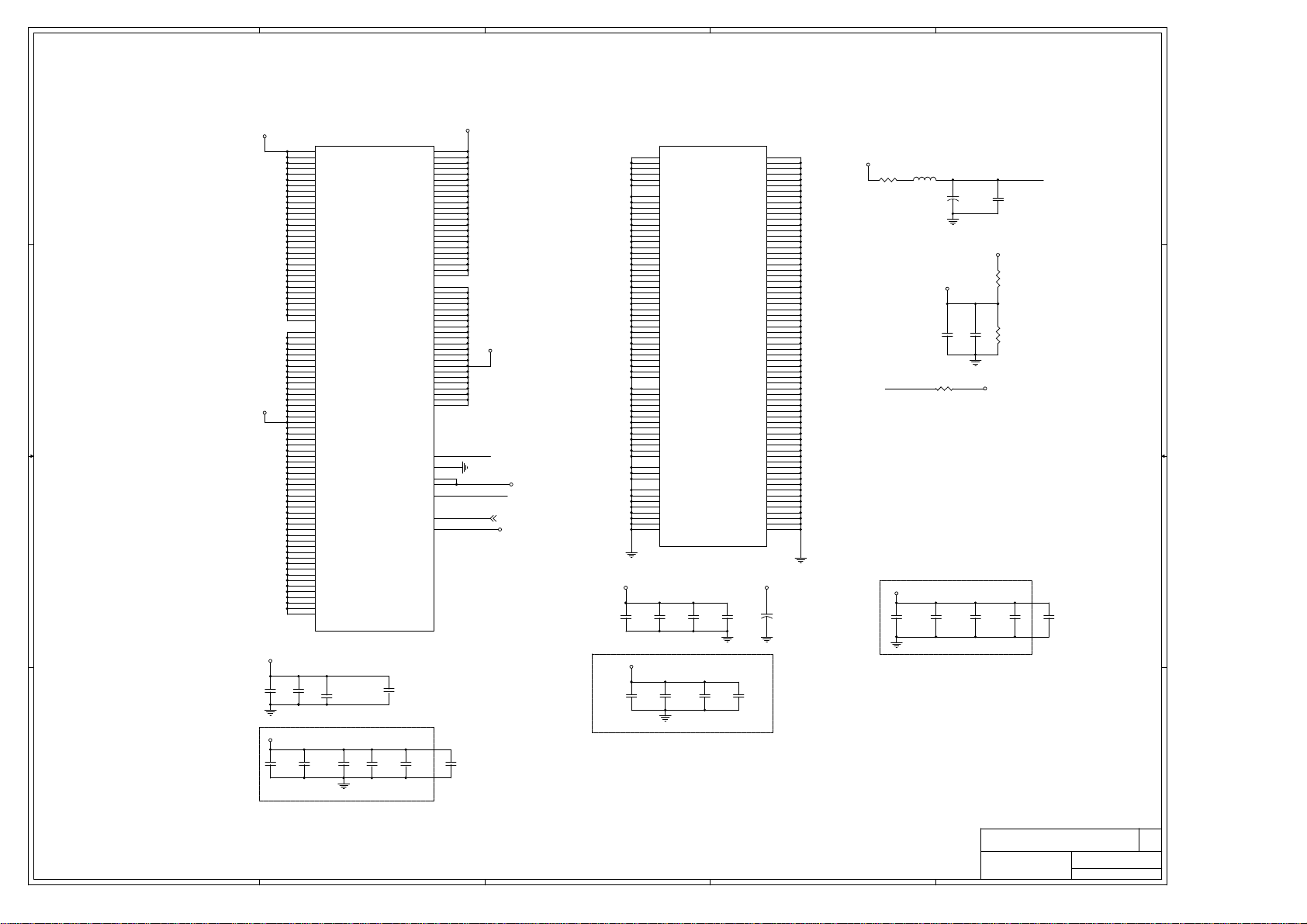

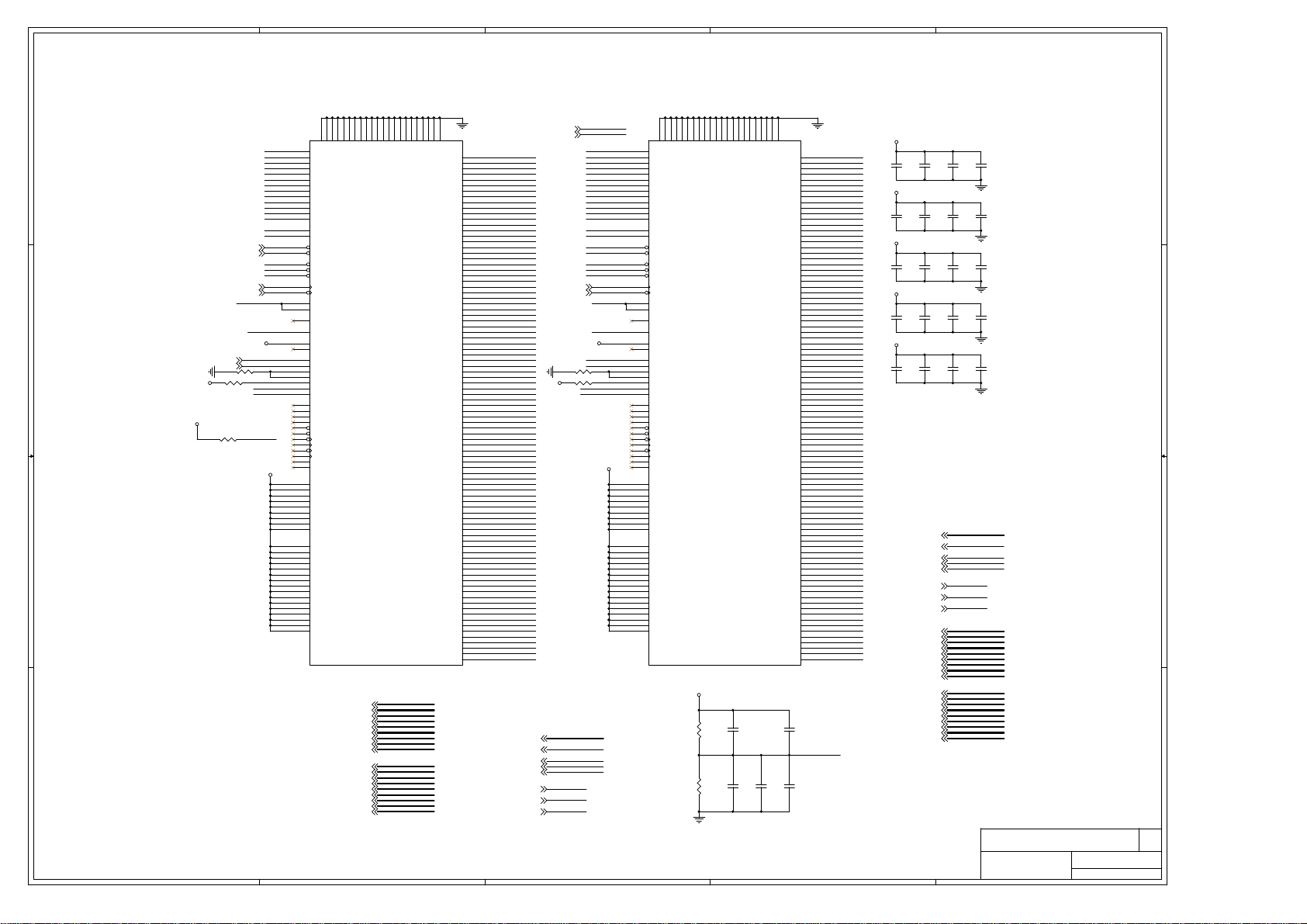

Page 4

A

B

C

D

E

P1_SM_ADDR[0..2]8 CPU_SDA 6,51,54

VCC_P

VCC3

VCC3

P1_SM_TS_ADDR[0..1]8

R752

1K

R745

X_R

R535

X_R

C395

1000P-0805

P1_VCCIOPLL11

FSB_VCC_SENSE6

FSB_GND_SENSE6

Enable

P1_ODTEN

Disable

OnDie

Termination

P1_SM_WP

4 4

3 3

2 2

1 1

P1_SM_ADDR[0..2]

P1_SM_TS_ADDR[0..1]

PD#[0..63]

PD#[0..63]6,12

P1_VCCA11

P1_VSSA11

P1_ODTEN

TP6

1

CPU1A

PD#0

Y26

PGA-S603

AA27

AA25

AD27

AA24

AB26

AB25

AB23

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD11

AC12

AE10

AC11

AD10

AA13

AA14

AC14

AB12

AB13

AA11

AA10

AB10

D0#

D1#

Y24

D2#

D3#

D4#

Y23

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

AE9

D44#

D45#

AD8

D46#

AC9

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

AC8

D56#

AD7

D57#

AE7

D58#

AC6

D59#

AC5

D60#

AA8

D61#

Y9

D62#

AB6

D63#

E10

AP0#

D9

AP1#

Y4

BCLK0

W5

BCLK1

PD#1

PD#2

PD#3

PD#4

PD#5

PD#6

PD#7

PD#8

PD#9

PD#10

PD#11

PD#12

PD#13

PD#14

PD#15

PD#16

PD#17

PD#18

PD#19

PD#20

PD#21

PD#22

PD#23

PD#24

PD#25

PD#26

PD#27

PD#28

PD#29

PD#30

PD#31

PD#32

PD#33

PD#34

PD#35

PD#36

PD#37

PD#38

PD#39

PD#40

PD#41

PD#42

PD#43

PD#44

PD#45

PD#46

PD#47

PD#48

PD#49

PD#50

PD#51

PD#52

PD#53

PD#54

PD#55

PD#56

PD#57

PD#58

PD#59

PD#60

PD#61

PD#62

PD#63

AP#0

AP#06,12

AP#1

AP#16,12

HCLK1

HCLK122

HCLK1_N

HCLK1_N22

PA#[3..35]

PA#[3..35]6,12

BREQ#06,12

BREQ#16

BREQ#26

BREQ#36

BNR#6,11,12

BPRI#6,12

A3B5D26

ODTEN

SKTOCC#

AA5

B27

VSSA

VSSSENSE

A3#

A4#

A22

A20

B18

PA#3

PA#4

PA#5

AD4

AB4

VCCA

VCCIOPLL

VCCSENSE

A5#

A6#

A7#

C18

A19

PA#6

PA#7

VCC3

P1_SM_WP

AD29

SMB_WP

A8#

A9#

C17

D17

PA#8

PA#9

P1_SM_TS_ADDR0

P1_SM_TS_ADDR1

AE29

AE28

Y29

AA28

SM_VCC

SM_VCC1

SM_TS_A1

SM_TS_A0

A10#

A11#

A12#

A13#

A13

B16

B14

B13

PA#10

PA#11

PA#12

PA#13

P1_SM_ADDR0

P1_SM_ADDR1

P1_SM_ADDR2

AB28

AB29

AA29

AC29

AC28

AD28

SM_CLK

SM_DAT

SM_EP_A2

SM_EP_A1

SM_EP_A0

SM_ALERT

FOSTER

A14#

A15#

A16#

A17#

A18#

A19#

A12

C15

C14

D16

D15

F15

A10

PA#14

PA#15

PA#16

PA#17

PA#18

PA#19

PA#20

R748 43

E16

A20#

B10

R537 43

P1_COMP0

P1_COMP1

AD16

COMP1

COMP0

A21#

A22#

A23#

B11

C12

PA#21

PA#22

PA#23

VCC_P

W6W7W8Y6AA7

TESTHI0

TESTHI1

A24#

A25#

A26#

E14

D13A9B8

PA#24

PA#25

PA#26

R539 180

TESTHI2

A27#

E13

PA#27

CPU_SCL 6,51,54

CPU1_SMBALERT# 51

R538 180

DP#3

AE17

AD5

AE5

TESTHI3

TESTHI4

TESTHI5

TESTHI6

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

D12

C11B7A6A7C9C8D20

PA#28

PA#29

PA#30

PA#31

PA#32

PA#33

PA#34

PA#35

DP#2

AC15

DP3#

BREQ#0

DP#1

AE19

DP2#

BR0#

F12

BREQ#1

DP#0

AC18

DP1#

BR1#

E11

BREQ#2

DP0#

BR2#

E25

TDO

BR3#

BNR#

D10

F20

BREQ#3

E19

C24

E24

TDI

TCK

TRDY#

BPRI#

BINIT#

DBSY#

D23

F11

F18

BINIT#

DBSY#

R747 39.2

R749 39.2

R750 39.2

R751 39.2

PLACE AT PROC 1

HREQ#[0..4]

DSTBP#[0..3]

DSTBN#[0..3]

BPM#[2..5]

VRM_VID[0..4]

DINV#[0..3]

DP#[0..3]

F24

A25

TMS

TRST#

DBI3#

DBI2#

DBI1#

DBI0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

STPCLK#

THERMTRIP#

PWRGD

PR0CH0T#

LINIT1

LINIT0

FERR#

IGNNE#

A20M#

RESET#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

LOCK#

MCERR#

RSP#

RS2#

RS1#

RS0#

IERR#

DEFER#

HITM#

ADS#

ADSTB0#

ADSTB1#

DRDY#

E18

DRDY#

HREQ#[0..4] 6,12

DSTBP#[0..3] 6,12

DSTBN#[0..3] 6,12

BPM#[2..5] 6,9,11

VRM_VID[0..4] 6,51,56

DINV#[0..3] 6,12

DP#[0..3] 6,12

P1_TDO 6,9

P1_TDI 9

P1_TCK 9

P_TRDY# 6,12

ITP_TRST# 6,9

TMS 6,9

DINV#3

AB9

DINV#2

AE12

DINV#1

AD22

DINV#0

AC27

VRM_VID0

F3

VID0

E3

VID1

VRM_VID2

D3

VID2

VRM_VID3

C3

VID3

VRM_VID4

B3

VID4

F9

F23

W9

W23

DSTBP#3

Y11

DSTBP#2

Y14

DSTBP#1

Y17

DSTBP#0

Y20

DSTBN#3

Y12

DSTBN#2

Y15

DSTBN#1

Y18

DSTBN#0

Y21

BPM#2

F6

BPM#3

F8

BPM#2

E7

BPM#3

F5

BPM#4

E8

BPM#5

E4

AE6

SLP#

D4

C27

SMI#

F26

AB7

B25

D6

INIT#

G23

B24

E27

C26

F27

Y8

HREQ#0

B19

HREQ#1

B21

HREQ#2

C21

HREQ#3

C20

HREQ#4

B22

A17

D7

C6

F21

D22

E21

P1_IERR#

E5

DEFER#

C23

HITM#

A23

HIT#

E22

HIT#

ADS#

D19

ADSTB#0

F17

ADSTB#1

F14

VCC_P

Check Which CPU is

close to ITP

P1_GTLREF1 8

P1_GTLREF0 8

SLP# 6,11

CPU_STPCLK# 6,11

SMI# 6,11

P1_THERMTRIP# 10,41

CPU1_PWRGD 59

P1_PROCHOT# 10

INIT# 6,11

LINT1 6,10,11

LINT0 6,10,11

FERR# 6,10,11

IGNNE# 6,10,11

A20M# 6,10,11

PROC_RESET# 6,9,11,13

LOCK# 6,11,12

MCERR# 6,11

RSP# 6,12

RS#2 6,12

RS#1 6,12

RS#0 6,12

P1_IERR# 10

DEFER# 6,12

HITM# 6,11,12

HIT# 6,11,12

ADS# 6,12

ADSTB#0 6,12

ADSTB#1 6,12

DRDY# 6,12

DBSY# 6,12

BINIT# 6,11,12

PLACE NEAR CENTER OF VCC_FSB PLANES

FSB_VCC_SENSE6

FSB_GND_SENSE6

ALL SENSE LINES MEET AT CENTRES OF PLANES

Route FSB_VCC/GND_SENSE,

VRM_ISHARE signals in 25/50

Mils trace width

VRM_VID0

VRM_VID1

VRM_VID2

VRM_VID3

VRM_VID4

FSB_VCC_SENSEVRM_VID1

FSB_GND_SENSE

RN105 1K

R746 1K

Philips/Vishay Iz=5mA

R732 0

TP8

1

TP7

1

R731 0

VCC3

12

34

56

78

VCC_P

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

Foster CPU #1

E

Last Revision Date:

Thursday, March 21, 2002

Sheet

4 68

of

Rev

0D

Page 5

A

B

C

D

E

4 4

3 3

2 2

VCC_P

A14

A18

A24

A28

B12

B20

B26

B29

C10

C16

C22

C28

D14

D18

D24

D29

E12

E20

E26

E28

F10

F16

F22

F29

G24

G26

G28

H23

H25

H27

H29

J24

J26

J28

K23

K25

K27

K29

L24

L26

L28

M23

M25

M27

M29

N23

N25

N27

N29

P24

P26

P28

R23

R25

R27

W27

W25

PGA-S603

A2

A8

B6

C2

C4

D8

E2

E6

F4

G2

G4

G6

G8

H3

H5

H7

H9

J2

J4

J6

J8

K3

K5

K7

K9

L2

L4

L6

L8

M3

M5

M7

M9

N3

N5

N7

N9

P2

P4

P6

P8

R3

R5

R7

R9

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

GN33

GN34

GN35

GN36

GN37

GN38

GN39

EMI_GND1

EMI_GND2

EMI_GND3

EMI_GND4

EMI_GND5

EMI_GND6

EMI_GND7

FOSTER_PWR

EMI_GND10

EMI_GND11

EMI_GND12

EMI_GND13

EMI_GND14

EMI_GND15

GN42

GN43

GN44

GN45

GN46

GN47

GN40

GN41

EMI_GND8

EMI_GND9

EMI_GND16

GN48

CPU1C

GN21

GN22

GN23

GN24

GN25

MTG_GND21

MTG_GND22

MTG_GND1

MTG_GND2

MTG_GND3

GN1

GN2

GN3

MTG_GND23

MTG_GND24

MTG_GND25

MTG_GND4

MTG_GND5

MTG_GND6

GN4

GN5

GN6

GN26

MTH_GND26

MTG_GND7

GN7

A5

VSS

A11

VSS

A21

VSS

A27

VSS

A29

VSS

B2

VSS

B9

VSS

B15

VSS

B17

VSS

B23

VSS

B28

VSS

C7

VSS

C13

VSS

C19

VSS

C25

VSS

C29

VSS

D2

VSS

D5

VSS

D11

VSS

D21

VSS

D27

VSS

D28

VSS

E9

VSS

E15

VSS

E17

VSS

E23

VSS

E29

VSS

F2

VSS

F7

VSS

F13

VSS

F19

VSS

F25

VSS

F28

VSS

G3

VSS

G5

VSS

G7

VSS

G9

VSS

G25

VSS

G27

VSS

G29

VSS

H2

VSS

H4

VSS

H6

VSS

H8

VSS

H24

VSS

H26

VSS

H28

VSS

J3

VSS

J5

VSS

W29

VCC

Y2

VCC

Y10

VCC

Y16

VCC

Y22

VCC

AA4

VCC

AA6

VCC

AA12

VCC

AA20

VCC

AA26

VCC

AB2

VCC

AB8

VCC

AB14

VCC

AB18

VCC

AB24

VCC

AC3

VCC

AC4

VCC

AC10

VCC

AC16

VCC

AC22

VCC

AD2

VCC

AD6

VCC

AD12

VCC

AD20

VCC

AD26

VCC

AE3

VCC

AE8

VCC

AE14

VCC

AE18

VCC

AE24

VCC

R29

VCC

T2

VCC

T4

VCC

T6

VCC

T8

VCC

T24

VCC

T26

VCC

T28

VCC

U3

VCC

U5

VCC

U7

VCC

U9

VCC

U23

VCC

U25

VCC

U27

VCC

U29

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC_P

V2

V4

V6

V8

V24

V26

V28

J7

VSS

J9

VSS

J23

VSS

J25

VSS

J27

VSS

J29

VSS

K2

VSS

K4

VSS

K6

VSS

K8

VSS

K24

VSS

K26

VSS

K28

VSS

L3

VSS

L5

VSS

L7

VSS

L9

VSS

L23

VSS

L25

VSS

L27

VSS

L29

VSS

M2

VSS

M4

VSS

M6

VSS

M8

VSS

M24

VSS

M26

VSS

M28

VSS

N2

VSS

N4

VSS

N6

VSS

N8

VSS

N24

VSS

N26

VSS

N28

VSS

P3

VSS

P5

VSS

P7

VSS

P9

VSS

P23

VSS

P25

VSS

P27

VSS

P29

VSS

R2

VSS

R4

VSS

R6

VSS

R8

VSS

R24

VSS

R26

VSS

R28

VSS

T3

VSS

T5

VSS

T7

VSS

T9

VSS

T23

VSS

T25

VSS

T27

VSS

T29

VSS

U2

VSS

U4

VSS

U6

VSS

U8

VSS

U24

VSS

U26

VSS

U28

VSS

V3

VSS

V5

VSS

V7

VSS

V9

VSS

V23

VSS

V25

VSS

V27

VSS

V29

VSS

W2

VSS

W4

VSS

W24

VSS

W26

VSS

W28

VSS

Y5

VSS

Y7

VSS

Y13

VSS

Y19

VSS

Y25

VSS

AA2

VSS

AA9

VSS

AA15

VSS

AA17

VSS

AA23

VSS

AB5

VSS

AB11

VSS

AB21

VSS

AB27

VSS

AC2

VSS

AC7

VSS

AC13

VSS

AC19

VSS

AC25 AD3

VSS VSS

PGA-S603

GN27

GN28

GN29

MTG_GND27

MTG_GND28

MTG_GND29

MTG_GND8

MTG_GND9

MTG_GND10

GN8

GN9

GN10

GN30

GN31

GN32

MTG_GND30

MTG_GND31

MTG_GND32

FOSTER_PWR

MTG_GND11

MTG_GND12

MTG_GND13

MTG_GND14

GN11

GN12

GN13

GN14

A1

A4

GAL_VDD1

GAL_VDD2

GAL_VDD3

RSVD1

RSVD2

GAL_VDD4

GAL_VDD5

GAL_VDD6

GAL_VDD7

GAL_VDD8

GAL_VDD9

GAL_VDD10

GAL_VDD11

GAL_VDD12

GAL_VDD13

GAL_VDD14

GAL_VDD15

GAL_VDD16

GAL_VDD17

GAL_VDD18

GAL_VDD19

GAL_VDD20

GAL_VDD21

GAL_VDD22

GAL_VDD23

GAL_VDD24

GAL_VDD25

GAL_VDD26

GAL_VDD27

GAL_VDD28

GAL_VDD29

GAL_VDD30

GAL_VDD31

GAL_VDD32

GAL_VDD33

GAL_VDD34

GAL_VDD35

GAL_VSS1

GAL_VSS2

GAL_VSS3

GAL_VSS4

GAL_VSS5

GAL_VSS6

GAL_VSS7

GAL_VSS8

GAL_VSS9

GAL_VSS10

GAL_VSS11

GAL_VSS12

GAL_VSS13

GAL_VSS14

GAL_VSS15

GAL_VSS16

GAL_VSS17

GAL_VSS18

GAL_VSS19

GAL_VSS20

GAL_VSS21

GAL_VSS22

GAL_VSS23

GAL_VSS24

GAL_VSS25

GAL_VSS26

GAL_VSS27

GAL_VSS28

GAL_VSS29

GAL_VSS30

GAL_VSS31

GAL_VSS32

GAL_VSS33

GAL_VSS34

MTG_GND15

MTG_GND16

MTG_GND17

GN15

GN16

GN17

GN18

RSVD13

RSVD17

RSVD63

RSVD67

RSVD68

RSVD69

RSVD73

RSVD77

RSVD80

RSVD83

RSVD86

RSVD87

RSVD88

MTG_GND18

GN19

RSVD3

RSVD4

RSVD5

RSVD8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MTG_GND19

MTG_GND20

GN20

A30

B4

B31

C30

D1

D31

E30

F1

F31

G30

H1

H31

J30

K1

K31

L30

M1

M31

N1

N31

P30

R1

R31

T30

U1

U31

V30

W1

W31

Y30

AA1

AA31

AB30

AC31

AD30

A31

B30

C1

C31

D30

E1

E31

F30

G1

G31

H30

J1

J31

K30

L1

L31

M30

N30

P1

P31

R30

T1

T31

U30

V1

V31

W30

Y1

Y31

AA30

AB1

AB31

AC30

AD31

A15

A16

A26

B1

C5

D25

W3

Y3

Y27

Y28

AA3

AB3

AC1

AD1

AE4

AE15

AE16

AE27

AE21

AE11

AE2

AD23

AD17

AD15

AD9

VCC_P

BSEL0

BSEL1

R620

X_R

DON'T STUFF

BSEL0 22

R972

X_R

CPU1 CORE DECOUPLING

22U

C396

22U

22U

C439

C453

22U

22U

C584

C550

22U

22U

C527

C517

PLACE AROUND P1 SOCKET

C457

1U

C462

C459

1U

1U

22U

22U

C469

C397

22U

22U

C477

C460

22U

22U

C583

C582

22U

22U

C479

C487

C483

C492

1U

1U

C458

0.1U

CPU1_THERMDA1 51

CPU1_THERMDC1 51

VCC_P

22U

C398

22U

22U

C400

C399

VCC_P

22U

22U

C488

22U

C518

C526

VCC_P

22U

C470

22U

22U

C580

C581

VCC_P

22U

22U

C456

22U

C452

C438

VCC_P

C494

C463

1U

C484

1U

1U

VCC_P

C493

C468

0.1U

C471

0.1U

0.1U

1 1

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

Foster CPU #1 PWR

Last Revision Date:

Thursday, March 21, 2002

Sheet

E

5 68

of

Rev

0D

Page 6

A

B

C

D

E

4 4

3 3

2 2

1 1

VCC_P

VCC3

VCC3

P2_SM_ADDR[0..2]8

P2_SM_TS_ADDR[0..1]8

FSB_VCC_SENSE4

FSB_GND_SENSE4

R532

X_R

DON'T STUFF

P2_ODTEN

R530

1K

OnDie

Termination

R742

X_R

DON'T STUFF

P2_SM_WP

1000P-0805

C576

P2_VCCIOPLL11

Enable

Disable

P2_SM_ADDR[0..2]

P2_SM_TS_ADDR[0..1]

PD#[0..63]

PD#[0..63]4,12

P2_VCCA11

P2_VSSA11

P2_ODTEN

TP18

1

CPU2A

PD#0

Y26

PD#1

PD#2

PD#3

PD#4

PD#5

PD#6

PD#7

PD#8

PD#9

PD#10

PD#11

PD#12

PD#13

PD#14

PD#15

PD#16

PD#17

PD#18

PD#19

PD#20

PD#21

PD#22

PD#23

PD#24

PD#25

PD#26

PD#27

PD#28

PD#29

PD#30

PD#31

PD#32

PD#33

PD#34

PD#35

PD#36

PD#37

PD#38

PD#39

PD#40

PD#41

PD#42

PD#43

PD#44

PD#45

PD#46

PD#47

PD#48

PD#49

PD#50

PD#51

PD#52

PD#53

PD#54

PD#55

PD#56

PD#57

PD#58

PD#59

PD#60

PD#61

PD#62

PD#63

AP#0

AP#04,12

AP#1

AP#14,12

HCLK2

HCLK222

HCLK2_N

HCLK2_N22

D0#

AA27

D1#

Y24

D2#

AA25

D3#

AD27

D4#

Y23

D5#

AA24

D6#

AB26

D7#

AB25

D8#

AB23

D9#

AA22

D10#

AA21

D11#

AB20

D12#

AB22

D13#

AB19

D14#

AA19

D15#

AE26

D16#

AC26

D17#

AD25

D18#

AE25

D19#

AC24

D20#

AD24

D21#

AE23

D22#

AC23

D23#

AA18

D24#

AC20

D25#

AC21

D26#

AE22

D27#

AE20

D28#

AD21

D29#

AD19

D30#

AB17

D31#

AB16

D32#

AA16

D33#

AC17

D34#

AE13

D35#

AD18

D36#

AB15

D37#

AD13

D38#

AD14

D39#

AD11

D40#

AC12

D41#

AE10

D42#

AC11

D43#

AE9

D44#

AD10

D45#

AD8

D46#

AC9

D47#

AA13

D48#

AA14

D49#

AC14

D50#

AB12

D51#

AB13

D52#

AA11

D53#

AA10

D54#

AB10

D55#

AC8

D56#

AD7

D57#

AE7

D58#

AC6

D59#

AC5

D60#

AA8

D61#

Y9

D62#

AB6

D63#

E10

AP0#

D9

AP1#

Y4

BCLK0

W5

BCLK1

PGA-S603

PA#[3..35]

PA#[3..35]4,12

BREQ#14

BREQ#04,12

BREQ#24

BREQ#34

BNR#4,11,12

BPRI#4,12

A3B5D26

ODTEN

SKTOCC#

AA5

B27

VSSA

VSSSENSE

A3#

A4#

A22

A20

B18

PA#3

PA#4

PA#5

AD4

AB4

VCCA

VCCIOPLL

VCCSENSE

A5#

A6#

A7#

C18

A19

C17

PA#6

PA#7

VCC3

P2_SM_WP

AD29

SMB_WP

A8#

A9#

D17

PA#8

PA#9

P2_SM_ADDR2

P2_SM_TS_ADDR1

P2_SM_TS_ADDR0

AE29

AE28

Y29

AA28

AB28

SM_VCC

SM_VCC1

SM_TS_A1

SM_TS_A0

A10#

A11#

A12#

A13#

A13

B16

B14

B13

A12

PA#10

PA#11

PA#12

PA#13

PA#14

P2_SM_ADDR1

AB29

SM_EP_A2

A14#

C15

PA#15

CPU_SDA 4,51,54

CPU_SCL 4,51,54

CPU2_SMBALERT# 51

R533 43

R740 43

P2_SM_ADDR0

P2_COMP0

P2_COMP1

AA29

AC29

AC28

AD28

E16

AD16

COMP1

COMP0

SM_CLK

SM_DAT

SM_EP_A1

SM_EP_A0

SM_ALERT

FOSTER

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

C14

D16

D15

F15

A10

B10

B11

C12

PA#16

PA#17

PA#18

PA#19

PA#20

PA#21

PA#22

PA#23

W6W7W8Y6AA7

A23#

A24#

E14

D13A9B8

PA#24

PA#25

VCC_P

TESTHI0

TESTHI1

A25#

A26#

PA#26

R738 180

TESTHI2

A27#

PA#27

R739 180

AD5

AE5

TESTHI3

TESTHI4

TESTHI5

TESTHI6

A28#

A29#

A30#

A31#

A32#

E13

D12

C11B7A6A7C9C8D20

PA#28

PA#29

PA#30

PA#31

PA#32

A33#

PA#33

A34#

PA#34

A35#

PA#35

DP#3

AE17

DP#2

AC15

DP3#

BREQ#1

DP#1

AE19

DP2#

BR0#

F12

BREQ#0

DP1#

BR1#

DP#0

AC18

DP0#

BR2#

E11

D10

BREQ#2

BREQ#3

BR3#

E25

TDO

BNR#

F20

BNR#

C24

D23

BPRI#

TDI

BPRI#

E24

TCK

HREQ#[0..4]

DSTBP#[0..3]

DSTBN#[0..3]

BPM#[2..5]

VRM_VID[0..4]

DINV#[0..3]

DP#[0..3]

E19

F24

TRST#

TRDY#

THERMTRIP#

BINIT#

DBSY#

DRDY#

F11

F18

E18

DRDY#

BINIT#

DBSY#

HREQ#[0..4] 4,12

DSTBP#[0..3] 4,12

DSTBN#[0..3] 4,12

BPM#[2..5] 4,9,11

VRM_VID[0..4] 4,51,56

DINV#[0..3] 4,12

DP#[0..3] 4,12

P2_TDO 9

P1_TDO 4,9

P2_TCK 9

P_TRDY# 4,12

ITP_TRST# 4,9

TMS 4,9

A25

TMS

AB9

DBI3#

AE12

DBI2#

AD22

DBI1#

AC27

DBI0#

F3

VID0

E3

VID1

D3

VID2

C3

VID3

B3

VID4

F9

GTLREF3

F23

GTLREF2

W9

GTLREF1

W23

GTLREF0

Y11

DSTBP3#

Y14

DSTBP2#

Y17

DSTBP1#

Y20

DSTBP0#

Y12

DSTBN3#

Y15

DSTBN2#

Y18

DSTBN1#

Y21

DSTBN0#

F6

BPM0#

F8

BPM1#

E7

BPM2#

F5

BPM3#

E8

BPM4#

E4

BPM5#

AE6

SLP#

D4

STPCLK#

C27

SMI#

F26

AB7

PWRGD

B25

PR0CH0T#

D6

INIT#

G23

LINIT1

B24

LINIT0

E27

FERR#

C26

IGNNE#

F27

A20M#

Y8

RESET#

B19

REQ0#

B21

REQ1#

C21

REQ2#

C20

REQ3#

B22

REQ4#

A17

LOCK#

D7

MCERR#

C6

RSP#

F21

RS2#

D22

RS1#

E21

RS0#

E5

IERR#

C23

DEFER#

A23

HITM#

E22

HIT#

D19

ADS#

F17

ADSTB0#

F14

ADSTB1#

Place these close to CPU2

R531 40.2

R649 40.2

Check Which CPU is

close to ITP

DINV#3

DINV#2

DINV#1

DINV#0

VRM_VID0

VRM_VID1

VRM_VID2

VRM_VID3

VRM_VID4

DSTBP#3

DSTBP#2

DSTBP#1

DSTBP#0

DSTBN#3

DSTBN#2

DSTBN#1

DSTBN#0

BPM#2

BPM#3

BPM#2

BPM#3

BPM#4

BPM#5

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

P2_IERR#

DEFER#

HITM#

HIT#

ADS#

ADSTB#0

ADSTB#1

P2_GTLREF1 8

P2_GTLREF0 8

SLP# 4,11

CPU_STPCLK# 4,11

SMI# 4,11

P2_THERMTRIP# 10,41

CPU2_PWRGD 59

P2_PROCHOT# 10

INIT# 4,11

LINT1 4,10,11

LINT0 4,10,11

FERR# 4,10,11

IGNNE# 4,10,11

A20M# 4,10,11

PROC_RESET# 4,9,11,13

LOCK# 4,11,12

MCERR# 4,11

RSP# 4,12

RS#2 4,12

RS#1 4,12

RS#0 4,12

P2_IERR# 10

DEFER# 4,12

HITM# 4,11,12

HIT# 4,11,12

ADS# 4,12

ADSTB#0 4,12

ADSTB#1 4,12

VCC_P

DRDY# 4,12

DBSY# 4,12

BINIT# 4,11,12

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

Foster CPU #2

E

Last Revision Date:

Thursday, March 21, 2002

Sheet

6 68

of

Rev

0D

Page 7

A

VCC_P

CPU2B

GN33

GN34

GN35

GN36

GN37

GN38

GN39

GN40

EMI_GND1

EMI_GND2

EMI_GND3

EMI_GND4

EMI_GND5

EMI_GND6

EMI_GND7

FOSTER_PWR

EMI_GND10

EMI_GND11

EMI_GND12

EMI_GND13

EMI_GND14

EMI_GND15

GN42

GN43

GN44

GN45

GN46

GN47

GN41

EMI_GND8

EMI_GND9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

EMI_GND16

GN48

A5

VSS

A11

VSS

A21

VSS

A27

VSS

A29

VSS

B2

VSS

B9

VSS

B15

VSS

B17

VSS

B23

VSS

B28

VSS

C7

VSS

C13

VSS

C19

VSS

C25

VSS

C29

VSS

D2

VSS

D5

VSS

D11

VSS

D21

VSS

D27

VSS

D28

VSS

E9

VSS

E15

VSS

E17

VSS

E23

VSS

E29

VSS

F2

VSS

F7

VSS

F13

VSS

F19

VSS

F25

VSS

F28

VSS

G3

VSS

G5

VSS

G7

VSS

G9

VSS

G25

VSS

G27

VSS

G29

VSS

H2

VSS

H4

VSS

H6

VSS

H8

VSS

H24

VSS

H26

VSS

H28

VSS

J3

VSS

J5

VSS

W29

Y2

Y10

Y16

Y22

AA4

AA6

AA12

AA20

AA26

AB2

AB8

AB14

AB18

AB24

AC3

AC4

AC10

AC16

AC22

AD2

AD6

AD12

AD20

AD26

AE3

AE8

AE14

AE18

AE24

R29

T2

T4

T6

T8

T24

T26

T28

U3

U5

U7

U9

U23

U25

U27

U29

V2

V4

V6

V8

V24

V26

V28

A2

VCC

A8

VCC

PGA-S603

A14

VCC

A18

VCC

A24

VCC

A28

VCC

B6

VCC

B12

VCC

B20

VCC

B26

VCC

B29

VCC

C2

VCC

C4

VCC

C10

VCC

C16

VCC

C22

VCC

C28

VCC

D8

VCC

D14

VCC

D18

VCC

D24

VCC

D29

VCC

E2

VCC

E6

VCC

E12

VCC

E20

VCC

E26

VCC

E28

VCC

F4

VCC

F10

VCC

F16

VCC

F22

VCC

F29

VCC

G2

VCC

G4

VCC

G6

VCC

G8

VCC

G24

VCC

G26

VCC

G28

VCC

H3

VCC

H5

VCC

H7

VCC

H9

VCC

H23

VCC

H25

VCC

H27

VCC

H29

VCC

J2

VCC

J4

VCC

J6

VCC

J8

VCC

J24

VCC

J26

VCC

J28

VCC

K3

VCC

K5

VCC

K7

VCC

K9

VCC

K23

VCC

K25

VCC

K27

VCC

K29

VCC

L2

VCC

L4

VCC

L6

VCC

L8

VCC

L24

VCC

L26

VCC

L28

VCC

M3

VCC

M5

VCC

M7

VCC

M9

VCC

M23

VCC

M25

VCC

M27

VCC

M29

VCC

N3

VCC

N5

VCC

N7

VCC

N9

VCC

N23

VCC

N25

VCC

N27

VCC

N29

VCC

P2

VCC

P4

VCC

P6

VCC

P8

VCC

P24

VCC

P26

VCC

P28

VCC

R3

VCC

R5

VCC

R7

VCC

R9

VCC

R23

VCC

R25

VCC

R27

VCC

W27

VCC

W25

VCC

4 4

3 3

2 2

VCC_P

B

CPU2C

GN21

GN22

GN23

GN24

GN25

GN26

GN27

GN28

GN29

GN30

GN31

MTG_GND24

MTG_GND25

MTG_GND26

MTG_GND5

MTG_GND6

MTG_GND7

GN5

GN6

GN7

GN8

MTG_GND27

MTG_GND28

MTG_GND29

MTG_GND30

MTG_GND8

MTG_GND9

MTG_GND10

MTG_GND11

GN9

GN10

GN11

GN32

MTG_GND31

MTG_GND32

MTG_GND12

MTG_GND13

GN12

GN13

J7

VSS

J9

VSS

J23

VSS

J25

VSS

J27

VSS

MTG_GND21

MTG_GND22

J29

K2

K4

K6

K8

K24

K26

K28

L23

L25

L27

L29

M2

M4

M6

M8

M24

M26

M28

N2

N4

N6

N8

N24

N26

N28

P3

P5

P7

P9

P23

P25

P27

P29

R2

R4

R6

R8

R24

R26

R28

T3

T5

T7

T9

T23

T25

T27

T29

U2

U4

U6

U8

U24

U26

U28

V3

V5

V7

V9

V23

V25

V27

V29

W2

W4

W24

W26

W28

Y5

Y7

Y13

Y19

Y25

AA2

AA9

AA15

AA17

AA23

AB5

AB11

AB21

AB27

AC2

AC7

AC13

AC19

AC25 AD3

PGA-S603

MTG_GND23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L3

VSS

L5

VSS

L7

VSS

L9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VSS

MTG_GND1

MTG_GND2

MTG_GND3

MTG_GND4

GN1

GN2

GN3

GN4

A1

A4

GAL_VDD1

GAL_VDD2

GAL_VDD3

RSVD1

RSVD2

GAL_VDD4

GAL_VDD5

GAL_VDD6

GAL_VDD7

GAL_VDD8

GAL_VDD9

GAL_VDD10

GAL_VDD11

GAL_VDD12

GAL_VDD13

GAL_VDD14

GAL_VDD15

GAL_VDD16

GAL_VDD17

GAL_VDD18

GAL_VDD19

GAL_VDD20

GAL_VDD21

GAL_VDD22

GAL_VDD23

GAL_VDD24

GAL_VDD25

GAL_VDD26

GAL_VDD27

GAL_VDD28

GAL_VDD29

GAL_VDD30

GAL_VDD31

GAL_VDD32

GAL_VDD33

GAL_VDD34

GAL_VDD35

GAL_VSS1

GAL_VSS2

GAL_VSS3

GAL_VSS4

GAL_VSS5

GAL_VSS6

GAL_VSS7

GAL_VSS8

GAL_VSS9

GAL_VSS10

GAL_VSS11

GAL_VSS12

GAL_VSS13

GAL_VSS14

GAL_VSS15

GAL_VSS16

GAL_VSS17

GAL_VSS18

GAL_VSS19

GAL_VSS20

FOSTER_PWR

GAL_VSS21

GAL_VSS22

GAL_VSS23

GAL_VSS24

GAL_VSS25

GAL_VSS26

GAL_VSS27

GAL_VSS28

GAL_VSS29

GAL_VSS30

GAL_VSS31

GAL_VSS32

GAL_VSS33

GAL_VSS34

RSVD3

RSVD4

RSVD5

RSVD8

RSVD13

RSVD17

RSVD63

RSVD67

RSVD68

RSVD69

RSVD73

RSVD77

RSVD80

RSVD83

RSVD86

RSVD87

RSVD88

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MTG_GND14

MTG_GND15

MTG_GND16

MTG_GND17

MTG_GND18

MTG_GND19

MTG_GND20

GN14

GN15

GN16

GN17

GN18

GN19

GN20

A30

B4

B31

C30

D1

D31

E30

F1

F31

G30

H1

H31

J30

K1

K31

L30

M1

M31

N1

N31

P30

R1

R31

T30

U1

U31

V30

W1

W31

Y30

AA1

AA31

AB30

AC31

AD30

A31

B30

C1

C31

D30

E1

E31

F30

G1

G31

H30

J1

J31

K30

L1

L31

M30

N30

P1

P31

R30

T1

T31

U30

V1

V31

W30

Y1

Y31

AA30

AB1

AB31

AC30

AD31

A15

A16

A26

B1

C5

D25

W3

Y3

Y27

Y28

AA3

AB3

AC1

AD1

AE4

AE15

AE16

AE27

AE21

AE11

AE2

AD23

AD17

AD15

AD9

VCC_P

C

R736

X_R

DON'T STUFF

CPU2 CORE

DECOUPLING

22U

C575

22U

C544

22U

C389

PLACE AROUND P2 SOCKET

C515

C513

1U

1U

CPU2_THERMDA1 51

CPU2_THERMDC1 51

D

E

VCC_P

22U

C574

22U

22U

C572

C573

22U

22U

C570

C498

VCC_P

22U

22U

C519

C522

22U

22U

C478

C486

22U

22U

C448

C454

VCC_P

22U

22U

C391

C390

22U

22U

C499

C392

22U

22U

C394

C393

VCC_P

22U

22U

C450

22U

C455

C489

22U

22U

C541

C523

VCC_P

C503

C481

1U

C507

1U

1U

C476

C482

1U

C474

1U

1U

VCC_P

C475

C514

0.1U

C495

0.1U

C497

0.1U

0.1U

1 1

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

Foster CPU #2 PWR

Last Revision Date:

Thursday, March 21, 2002

Sheet

E

7 68

of

Rev

0D

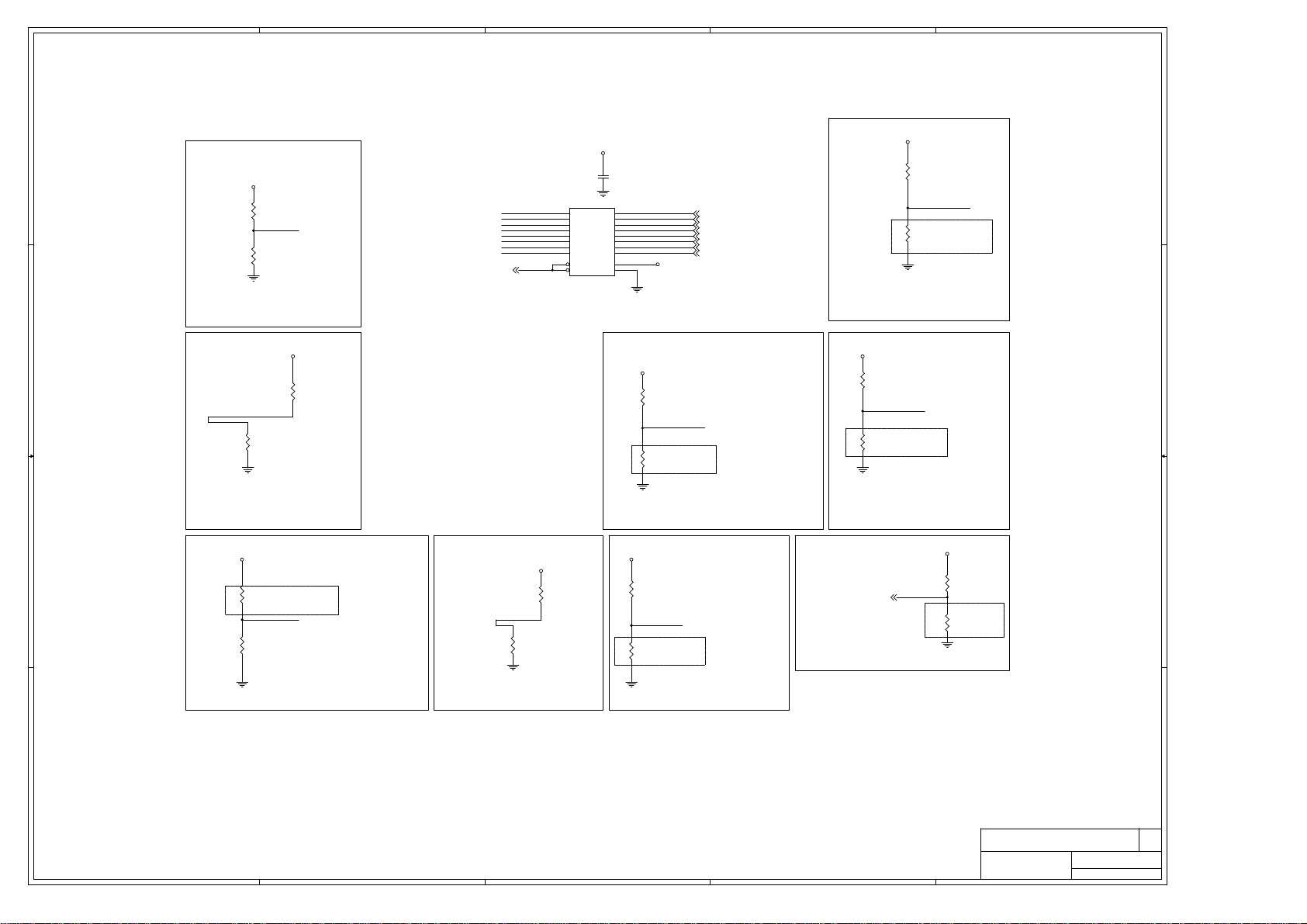

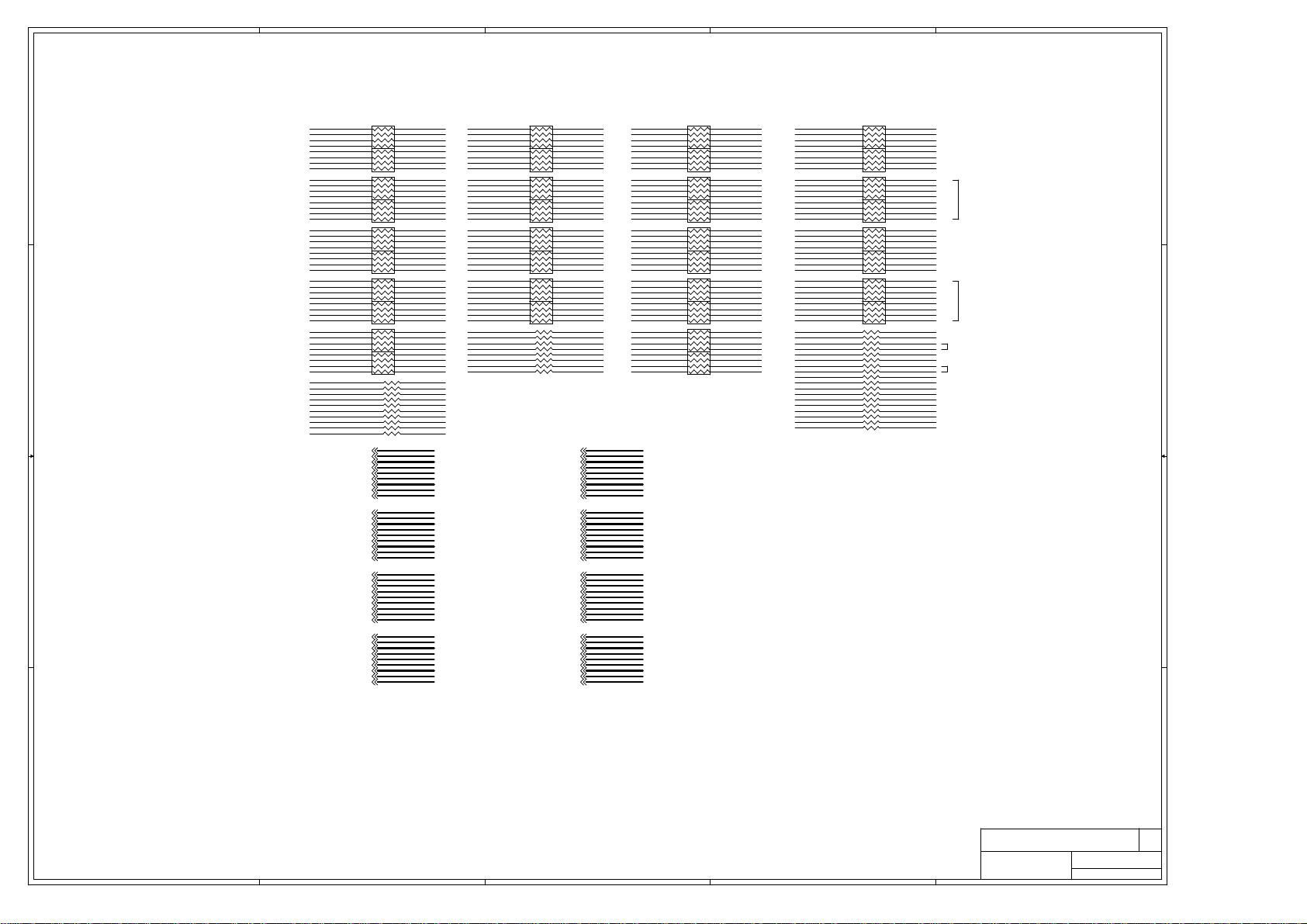

Page 8

A

4 4

B

C

D

E

DON'T STUFF

VCC3

R568

X_R

R569

1K

VCC3

R718

X_R

R719

1K

R576

X_R

R5771KR605

R708

X_R

R709

1K

VCC_P

R561

51

C426

C418

0.1U

0.1U

R604

X_R

DON'T STUFF

P1_SM_ADDR0

P1_SM_ADDR1P1_SM_TS_ADDR0

P1_SM_ADDR2

1K

Addr._0 : 1010 000Z

Z = R/W bit

R696

1K

P2_SM_ADDR0

P2_SM_ADDR1

P2_SM_ADDR2

R697

X_R

DON'T STUFF

P1_GTLREF1

C414

R585

1U

100

P1_SM_ADDR[0..2]

P2_SM_ADDR[0..2]

P1_SM_TS_ADDR[0..1]

P2_SM_TS_ADDR[0..1]

Addr._1 : 1010 001Z

P1_GTLREF1 4P1_GTLREF0 4

P1_SM_ADDR[0..2] 4

P2_SM_ADDR[0..2] 6

P1_SM_TS_ADDR[0..1] 4

P2_SM_TS_ADDR[0..1] 6

Z = R/W bit

CPU_0 Thermal Sensor SM Bus

Addr._0 : 0011X00Z

: 1001X00Z

: 0101X00Z

3 3

CPU_1 Thermal Sensor SM Bus

Addr._1 : 0011X01Z

: 1001X01Z

: 0101X01Z

2 2

OR

OR

OR

OR

R687

X_R

DON'T STUFF

R688

1K

VCC3

R615

X_R

R6141KR589

1K

VCC3

1K

VCC_P

R543

51

C383

0.1U

R588

DON'T STUFF

X_R

P1_SM_TS_ADDR1

R700

P2_SM_TS_ADDR0

P2_SM_TS_ADDR1

R701

X_R

DON'T STUFF

C384

R536

0.1U

100

P1_GTLREF0

C385

1U

VCC_P

R737

51

P2_GTLREF0 P2_GTLREF1

C587

R741

C586

0.1U

0.1U

1 1

A

B

C585

1U

100

PLACE EACH 220pf OF

GTLREF NEAR PROC

PIN

C

VCC_P

R690

51

P2_GTLREF1 6P2_GTLREF0 6

C551

C557

R707

0.1U

C562

0.1U

100

1U

Micro Star Restricted Secret

Title

CPU GTLREF & SM Bus Slave Address

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

D

http://www.msi.com.tw

E

Last Revision Date:

Thursday, March 21, 2002

Sheet

8 68

of

Rev

0D

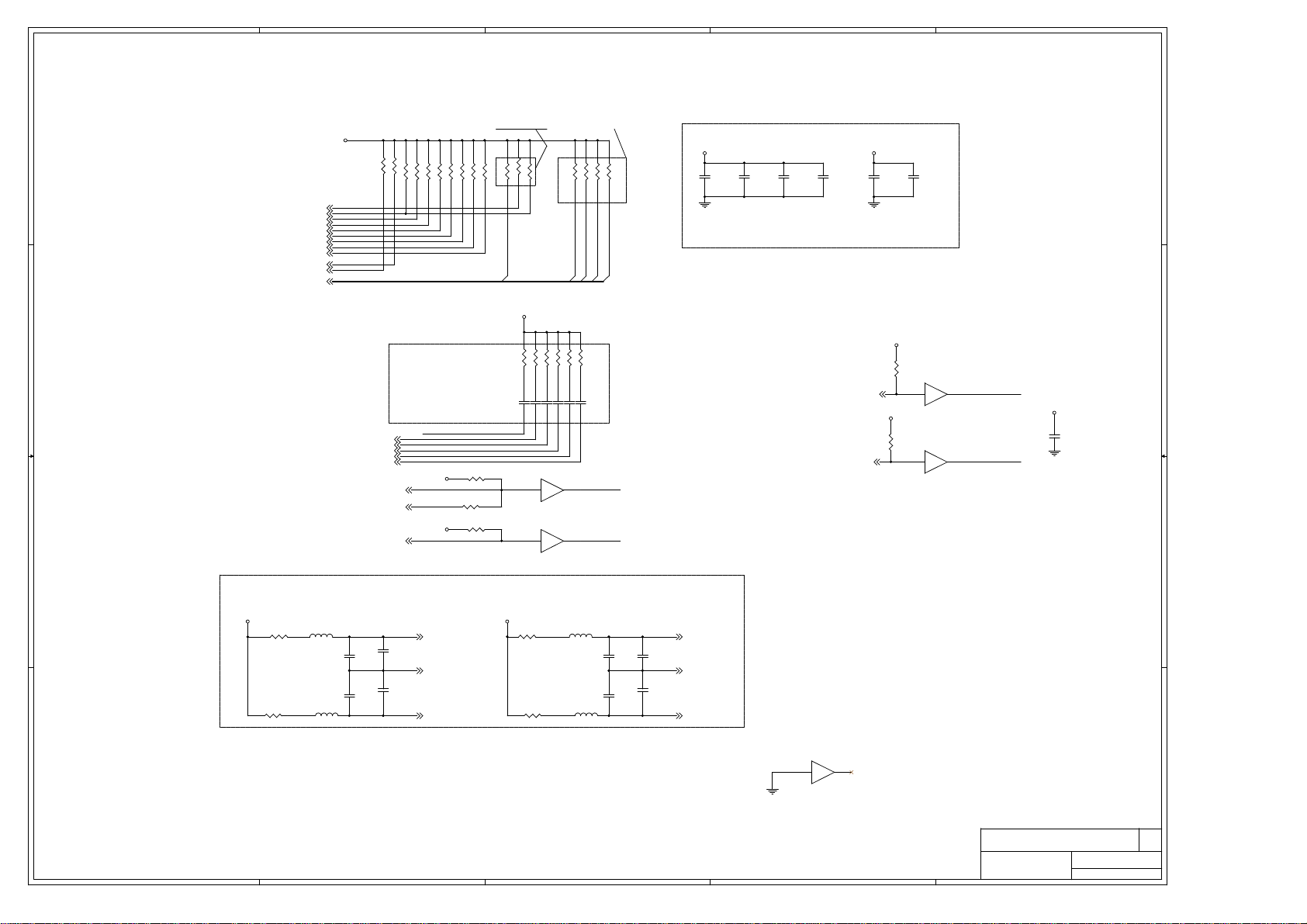

Page 9

A

4 4

B

C

D

E

VCC_P

VCC_P

VCC_P

RES. TO BE WITHIN

1" OF ITP CONN.

R480 40.2

BPM#24,6,11

BPM#34,6,11

BPM#44,6,11

BPM#54,6,11

PROC_RESET#4,6,11,13

CLK_100M_ITP022

CLK_100M_ITP122

3 3

2 2

CLK_100M_ITP = BCLK (to

processors) + Length of

BPM# trace from ITP

connector to first CPU.

RES. TO BE WITHIN

1" OF ITP CONN.

JP8

1

2

3

D1X3-BK

Place this HDR next to the

CPU nearest to ITP conn.

JP8_23

JC-D2-GN

FBO

R505

X_R

VCC_P

R441

150

PLACE NEAR CPU1

R495 40.2

R541 40.2

R542 40.2

R540 40.2

R506

X_R R493

R418

330

P1_TDI

P1_TDO

P2_TDO

VCC_P

R393

75

J3

1

2

1

2

3

4

3

4

5

6

5

6

7

8

7

8

9

10

9

10

11

13

15

17

19

21

23

25

12

11

12

14

13

14

16

15

16

18

17

18

20

19

20

22

21

22

24

23

24

25

X_CON25A_1

RES. TO BE WITHIN

1" OF ITP CONN.

P1_TDI 4

P1_TDO 4,6

P2_TDO 6

RES. TO BE WITHIN

1" OF ITP CONN.

DBA#

P1_TDI

R494 0

Place it as close to

P2_TDO

ITP Conn. as

possible

R400 1K

R499 1K

TCK

R497

680

TCK

R397 1K

R399 1K

R496

39.2

RES. TO BE WITHIN

1" OF ITP CONN.

TCK

R943 0

R944 0

R945 0

U26

2

1A1

4

1A2

6

1A3

8

1A4

11

2A1

13

2A2

15

2A3

17

2A4

1

1G

19

2G

X_74LVC244A-SO20

R396 1K

R484 330

R498

1K

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

VCC

GND

VCC3

R_P1_TCK

R_P2_TCK

R_FBO

R_P1_TCK

R_P2_TCK

R_FBO

VCC_P

R516

DON'T STUFF

X_R

ITP_RESET# 59

TMS 4,6

ITP_TRST# 4,6

THIS NET TO BE DAISY

CHAINED ALONG PROCS.

Within 1" of the last

150

device on this Net

R403 22

R404 22

R398 22

VCC_P

C308

0.1U

FBO = TCK (to

processors) + Length of

BPM# trace from ITP

connector to first CPU.

Length of

P1_TCK =

P2_TCK

FBO

P1_TCK 4

P2_TCK 6

C340

C352

X_22P

X_22P

C351

X_22P

R517

150

18

16

14

12

9

7

5

3

20

10

Look at Routing guidelines while

Placing components from this

sheet

LAYOUT NOTE:

1 1

A

B

BPM#[0..5], RST#, FBO, BCKN, BCKP, TCK, AND FBI

ARE CRITICAL ROUTES.

C

Micro Star Restricted Secret

Title

CPU GTLREF & SM Bus Slave Address

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

D

http://www.msi.com.tw

E

Last Revision Date:

Thursday, March 21, 2002

Sheet

9 68

of

Rev

0D

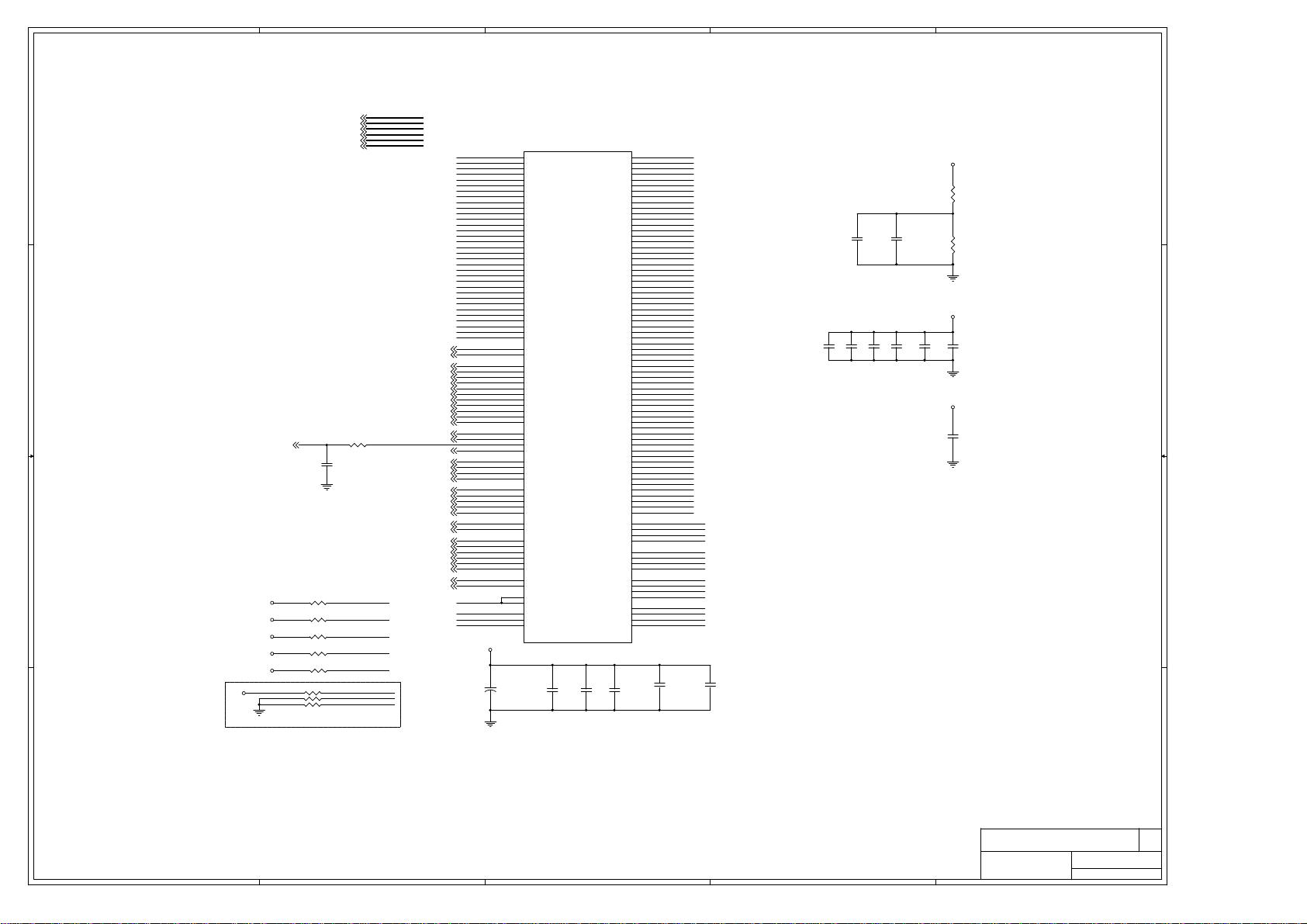

Page 10

5

D D

4

3

2

1

VCC3

RN108

12

34

56

78

330

INTR

INTR41

RSB_IGNNE#

RSB_IGNNE#41

R762

C C

B B

0

P1_THERMTRIP#4,41

P2_THERMTRIP#6,41

P1_PROCHOT#4

P2_PROCHOT#6

P1_IERR#4

P2_IERR#6

NMI

RESETDLY#

RSB_A20M#

P6_CGF1

P6_CGF3

P6_CGF2

P6_CGF4

R727

330

VCC_P

11

10

14

13

15

R689 51

VCC

168

2

1A

3

VCCGND

1B

5

2A

6

2B

3A

3B

4A

4B

1

A/B

G

RESETDLY# 12

NMI 40

RSB_A20M# 41

VCC_P

R683 51

R679 51

R684 51

R680 51

VCC3

R695

330

SW1

B1

B2

B3

B4

D4P-D-SB

U45

4

1Y

7

2Y

9

3Y

12

4Y

74F157-SOIC16

R626 51

VCC3

A1

A2

A3

A4

LINT0_3V

IGNNE#_3V

A20M#_3V

LINT1_3V

GTLREF_1

C549

1000P-0805

U38

2

3

5

6

14

7

GTLREF_1

A1

A2

A3

A4

VDD

GND

GTL2005

C558

1000P-0805

GTLREFDIRB-A

GND

GND

11

8

4 1

9

10

12

13

C577

1000P-0805

VCC_P

C559

0.1U

13

B1

12

B2

10

B3

9

B4

41

8

11

U39

GND

GND

GTLREF DIRB-A

B4

B3

B2

B1

GTL2005

VCC3VCC

R699

51

GTLREF_1

100

VCC3

123456

GTLREF_1

GND

VDD

A4

A3

A2

A1

C566

1000P-0805

78

7

14

6

5

3

2

C556

0.1U

VCC3

RN104

1K

C545

1000P-0805

GTLREF_1

R711

1K

LINT0

LINT0 4,6,11

IGNNE#

IGNNE# 4,6,11

A20M#

A20M# 4,6,11

LINT1

LINT1 4,6,11

RSB_P1_PROCHOT# 41

RSB_P2_PROCHOT# 41

RSB_P1_IERR# 41

RSB_P2_IERR# 41

NMI A20M# IGNNE# INTR

LINT1

LINT0

X8 H H H H

X9/X23 H H H L

X20 H H L H

X10 H H L L

X12 H L H H

X13 H L H L

X14 H L L H

X15 H L L L

X16 L H H H

X17 L H H L

X18 L H L H

X19 L H L L

X20 L L H H

X21 L L H L

X22 L L L H

X24 L L L L

R717

330

VCC3

R725

330

Q45

NPN-PMBT2369-SOT23

VCC_P

VCC_P

R712

330R694

FERR#4,6,11

RSB_FERR# 40

A A

Micro Star Restricted Secret

Title

Ratio & Level Shift Circuit

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

1

Last Revision Date:

Thursday, March 21, 2002

Sheet

10 68

of

Rev

0D

Page 11

A

B

C

D

E

DON'T STUFF PLACE NEAR CPU2

40.2

40.2

40.2

40.2

X_R

X_R

R715

R706

R1042

180

R1129 X_0

R730

180

R629

R724

R704

R607

BPM#4

VCC_P

150

R622

1U

X_R

R691

150

R599

R586

C779

C780

1U

U46C

5 6

DM7407-SOIC14

U46D

9 8

DM7407-SOIC14

150

150

R621

C7811UC782

1U

VCC_P VCC_P

40.2

40.2

40.2

40.2

R616

R606

R623

R617

BPM#2

BPM#3

BPM#4

BPM#5

150

150

R609

R598

C783

C784

1U

1U

SMI#

INIT#

C432

C436

0.1U

PLACE THE TERM CAPS NEAR THE TERMINATION

RESISTORS

C427

0.1U

C419

0.1U

0.1U

RSB_STPCLK#41

RSB_SLP#41MCERR#4,6

C440

0.1U

VCC3

VCC3

R744

150

R753

150

C382

0.1U

U46A

1 2

DM7407-SOIC14

U46B

3 4

DM7407-SOIC14

CPU_STPCLK#

SLP#

VCC

C579

0.1U

4 4

3 3

2 2

VCC_P

PROC_RESET#4,6,9,13

FERR#4,6,10

BINIT#4,6,12

SMI#

SMI#4,6

IGNNE#4,6,10

INIT#

INIT#4,6

CPU_STPCLK#4,6

CPU_STPCLK#

LINT04,6,10

LINT14,6,10

A20M#4,6,10

SLP#

SLP#4,6

BPM#[2..5]4,6,9

40.2

R642

BNR#4,6,12

HIT#4,6,12

HITM#4,6,12

LOCK#4,6,12

EXT_SMI#41

SIO_SMI#41,47

CMIC_PINIT#12,41,48

PLACE NEAR CPU1

40.2

40.2

40.2

40.2

40.2

R713

R685

R720

R698

R702

PLACE THESE

CLOSE TO

CPU2

BINIT#

VCC3

VCC25

(Make small Cu Islands for P1/P2_VCCA, P1/P2_VSSA and P1/P2_VCCIOPLL nets )

Place these Close to CPU1

VCC_P VCC_P

R524 0

R551 0

1 2

L23 4.7U_1206

1 2

L24 4.7U_1206

22U

C722

22U

C724

C380

1U

C387

1U

P1_VCCA 4

P1_VSSA 4

P1_VCCIOPLL 4

Place these Close to CPU2

1 2

R758 0

R759 0

L32 4.7U_1206

1 2

L33 4.7U_1206

22U

C594

1U

C723

C595

22U

1U

C725

P2_VCCA 6

P2_VSSA 6

P2_VCCIOPLL 6

U46F

1 1

A

B

C

13 12

DM7407-SOIC14

D

Micro Star Restricted Secret

Title

CPU Level Shift Circuit

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

E

Last Revision Date:

Thursday, March 21, 2002

Sheet

11 68

Rev

0D

of

Page 12

A

4 4

3 3

PCIRST_X#60

2 2

R306

VCC25

R299

VCC25

R307

VCC25

R308

VCC25

R310

VCC25

VCC_P

R373 100

R346 255

R343 20

*** Difference

with Rev:A1.0

Ckt

DSTBN#[0..3]4,6

DSTBP#[0..3]4,6

PA#[3..35]4,6

PD#[0..63]4,6

DINV#[0..3]4,6

DP#[0..3]4,6

R305

C240

22p

4.7K

10K

4.7K

4.7K

4.7K

MEMOFFACK#

WRMRST#

CMIC_FATAL#

MEMOFF#

CMIC_ALERT#

GTL_COMP_PD

GTL_COMP_PU

GTL_RCOMP

B

PA#[3..35]

PD#[0..63]

DINV#[0..3]

DP#[0..3]

DSTBN#[0..3]

DSTBP#[0..3]

22

C

AE25

AE24

AF26

AE26

AF27

AF23

AD27

AE27

AG25

AG24

AG26

K15

A17

A19

B18

A18

B19

A20

G16

C19

E19

H17

H16

D19

F18

H18

G19

F19

A23

B23

A22

A21

F20

B20

A24

A25

D20

B21

E20

B25

B27

A26

C22

D22

D18

C20

H19

G2

K17

H5

C1

D1

G3

F23

G1

D24

E16

G15

F15

C16

H15

E23

C24

F21

H9

K18

G21

F22

H20

F1

F4

E1

B1

F2

U20A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

ADSTB0#

ADSTB1#

ADS#

BNR#

BPRI#

DBSY#

DRDY#

HIT#

HITM#

LOCK#

TRDY#

DEFER#

BREQ0#

PLLRST

DLYRST

PCIRST#

WRMRST#

RS0#

RS1#

RS2#

RSP#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

AP0#

AP1#

ALERT#

BINIT#

HINIT#

BCLKP

BCLKN

FATAL#

MEMOFF#

MEMOFFACK#

GTL_VREF

GTL_VREF

GTL_COMP_PU

GTL_COMP_PD

GTL_RCOMP

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DP0#

DP1#

DP2#

DP3#

PD#0

C2

D0#

PD#1

E3

D1#

PD#2

B3

D2#

PD#3

C3

D3#

PD#4

F3

D4#

PD#5

D4

D5#

PD#6

A2

D6#

PD#7

D2

D7#

PD#8

D3

D8#

PD#9

A3

D9#

PD#10

H6

PD#11

F6

PD#12

G8

PD#13

F5

PD#14

H8

PD#15

H10

PD#16

F7

PD#17

G9

PD#18

E7

PD#19

E6

PD#20

A4

PD#21

B4

PD#22

D7

PD#23

A5

PD#24

G10

PD#25

K11

PD#26

B7

PD#27

C6

PD#28

F8

PD#29

C7

PD#30

E9

PD#31

K12

PD#32

D8

PD#33

C8

PD#34

D9

PD#35

B9

PD#36

E10

PD#37

A7

PD#38

A10

PD#39

A8

PD#40

B12

PD#41

A11

PD#42

F12

PD#43

A12

PD#44

G13

PD#45

F13

PD#46

K13

PD#47

H12

PD#48

B13

PD#49

D12

PD#50

A13

PD#51

E13

PD#52

C13

PD#53

C14

PD#54

A15

PD#55

B15

PD#56

D15

PD#57

E14

PD#58

E15

PD#59

H14

PD#60

K14

PD#61

C15

PD#62

A16

PD#63

G14

DINV#0

G5

DINV#1

A6

DINV#2

C10

DINV#3

H13

DP#0

C26

DP#1

B26

DP#2

E21

DP#3

E25

DSTBN#0

G6

DSTBN#1

F9

DSTBN#2

C9

DSTBN#3

D13

DSTBP#0

H7

DSTBP#1

H11

DSTBP#2

A9

DSTBP#3

A14

CMIC-WS

+

EC50

470u/4V

C262

1000p-0805

C274

1000p-0805

C901

4.7u

C902

4.7u

C251

1u

PA#3

PA#4

PA#5

PA#6

PA#7

PA#8

PA#9

PA#10

PA#11

PA#12

PA#13

PA#14

PA#15

PA#16

PA#17

PA#18

PA#19

PA#20

PA#21

PA#22

PA#23

PA#24

PA#25

PA#26

PA#27

PA#28

PA#29

PA#30

PA#31

PA#32

PA#33

PA#34

PA#35

ADSTB#0

ADSTB#04,6

ADSTB#1

ADSTB#14,6

ADS#

ADS#4,6

BNR#

BNR#4,6,11

BPRI#

BPRI#4,6

DBSY#

DBSY#4,6

DRDY#

DRDY#4,6

HIT#

HIT#4,6,11

HITM#

HITM#4,6,11

LOCK#

LOCK#4,6,11

P_TRDY#

P_TRDY#4,6

DEFER#

DEFER#4,6

BREQ#0

BREQ#04,6

PS_PWRGD#25,27,41,59

RESETDLY#10

CMIC_ALERT#16,41

CMIC_PINIT#11,41,48

HCLK_CMIC22

HCLK_CMIC_N22

CMIC_FATAL#16,41

MEMOFFACK#16

RESETDLY#

R_PCIRST_X#

WRMRST#

WRMRST#16

RS#0

RS#04,6

RS#1

RS#14,6

RS#2

RS#24,6

RSP#

RSP#4,6

HREQ#0

HREQ#04,6

HREQ#1

HREQ#14,6

HREQ#2

HREQ#24,6

HREQ#3

HREQ#34,6

HREQ#4

HREQ#44,6

AP#0

AP#04,6

AP#1

AP#14,6

CMIC_ALERT#

BINIT#4,6,11

CMIC_FATAL#

MEMOFF#

MEMOFF#16,40

MEMOFFACK#

GTL_VREF_CMIC

GTL_COMP_PU

GTL_COMP_PD

GTL_RCOMP

VCC25

12

D

E

VCC_P

R349

GTL_VREF_CMIC

C2711uC269

0.1u

51

R347

100

VCC25

C241

0.1u

C238

C242

C236

0.1u

0.1u

C237

0.1u

C256

0.1u

0.1u

VCC25

C259

1u

PUT THESE C AS CLOSE CMIC AS POSSIBLE

1 1

Micro Star Restricted Secret

Title

CMIC Foster Interface

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

E

Last Revision Date:

Thursday, March 21, 2002

Sheet

12 68

of

Rev

0D

Page 13

A

B

C

D

E

B_IMB_D_R[0..15]27

4 4

3 3

2 2

B_IMB_D_T[0..15]27

A_IMB_D_R[0..15]25

A_IMB_D_T[0..15]25

T_IMB_D_R[0..3]41

T_IMB_D_T[0..3]41

T_IMB_CLK_T41

T_IMB_CON_T41

T_IMB_PAR_T41

B_IMB_D_R[0..15]

B_IMB_D_T[0..15]

A_IMB_D_R[0..15]

A_IMB_D_T[0..15]

T_IMB_D_R[0..3]

T_IMB_D_T[0..3]

T_IMB_D_T0

T_IMB_D_T1

T_IMB_D_T3

B_IMB_CON_R27

B_IMB_CLK_R_P27

B_IMB_CLK_R_N27

B_IMB_PAR_R27

B_IMB_CON_T27

B_IMB_CLK_T_P_R27

B_IMB_CLK_T_N_R27

B_IMB_PAR_T27

R322 33

R314 33

R325 33

R335 33

R323 33

R326 33

R311 33

IMB_VREF_CMIC

B_IMB_D_R0

B_IMB_D_R1

B_IMB_D_R2

B_IMB_D_R3

B_IMB_D_R4

B_IMB_D_R5

B_IMB_D_R6

B_IMB_D_R7

B_IMB_D_R8

B_IMB_D_R9

B_IMB_D_R10

B_IMB_D_R11

B_IMB_D_R12

B_IMB_D_R13

B_IMB_D_R14

B_IMB_D_R15

B_IMB_D_T0

B_IMB_D_T1

B_IMB_D_T2

B_IMB_D_T3

B_IMB_D_T4

B_IMB_D_T5

B_IMB_D_T6

B_IMB_D_T7

B_IMB_D_T8

B_IMB_D_T9

B_IMB_D_T10

B_IMB_D_T11

B_IMB_D_T12

B_IMB_D_T13

B_IMB_D_T14

B_IMB_D_T15

R930 0

R932 0

R_TIMB_D_T0

R_TIMB_D_T1

R_TIMB_D_T2T_IMB_D_T2

R_TIMB_D_T3

R_TIMB_CLKT

R_TIMB_CONT

R_TIMB_PART

IMB_VREF_CMIC

CMIC_IMB_COMP_PD

CMIC_IMB_COMP_PU

CMIC_IMB_RCOMP

U20B

R25

BIMBD_R0

T23

B IMBD_R1

R26

BIMBD_R2

R27

BIMBD_R3

R22

BIMBD_R4

P23

BIMBD_R5

R24

BIMBD_R6

R23

BIMBD_R7

N25

BIMBD_R8

N22

BIMBD_R9

P21

BIMBD_R10

N23

BIMBD_R11

N24

BIMBD_R12

P20

BIMBD_R13

R18

BIMBD_R14

R17

BIMBD_R15

N20

BIMBCON_R

P25

BIMBCLK_R_P

P27

BIMBCLK_R_N

N21

BMBPAR_R

U21

BIMBD_T0

U23

BIMBD_T1

T20

BIMBD_T2

U18

BIMBD_T3

U17

BIMBD_T4

V20

BIMBD_T5

U20

BIMBD_T6

T22

BIMBD_T7

T21

BIMBD_T8

R21

BIMBD_T9

T25

BIMBD_T10

U27

BIMBD_T11

T24

BIMBD_T12

U25

BIMBD_T13

T27

BIMBD_T14

T26

BIMBD_T15

R20

BIMBCON_T

W26 L25

BIMBCLK_T_P AIMBCLK_T_P

W27

BIMBCLK_T_N

V27

BIMBDPAR_T

Y22

T_IMBD_T0

AA25

T_IMBD_T1

Y21

T_IMBD_T2

Y24

T_IMBD_T3

P18

IMB_VREF

D27

IMB_COMP_PD

H21

IMB_COMP_PU

G22

IMB_RCOMP

AIMBD_R0

AIMBD_R1

AIMBD_R2

AIMBD_R3

AIMBD_R4

AIMBD_R5

AIMBD_R6

AIMBD_R7

AIMBD_R8

AIMBD_R9

AIMBD_R10

AIMBD_R11

AIMBD_R12

AIMBD_R13

AIMBD_R14

AIMBD_R15

AIMBCON_R

AIMBCLK_R_P

AIMBCLK_R_N

AIMBPAR_R

AIMBD_T0

AIMBD_T1

AIMBD_T2

AIMBD_T3

AIMBD_T4

AIMBD_T5

AIMBD_T6

AIMBD_T7

AIMBD_T8

AIMBD_T9

AIMBD_T10

AIMBD_T11

AIMBD_T12

AIMBD_T13

AIMBD_T14

AIMBD_T15

AIMBCON_T

AIMBCLK_T_N

AIMBPAR_T

T_IMBD_R0

T_IMBD_R1

T_IMBD_R2

T_IMBD_R3

T_IMBCLK_RT_IMBCLK_T

T_IMBCON_RT_IMBCON_T

T_IMBPAR_RT_IMBPAR_T

CPURST#

SRESET#

TESTMODE#

SCLK

SDA

CMIC-WS

L20

L17

L18

K20

J24

H23

H22

J22

H26

F27

G24

G27

G25

E27

F24

J20

F25

H25

H24

F26

M26

M25

N27

N18

N17

M24

N26

L27

M27

L21

M22

H27

J27

K27

J26

M21

M20

M23

L23

Y26

W24

AA26

W22

Y27AA24

AA27AA23

W20AB25

C27

AF25

AD26

AE23

AG23

A_IMB_D_R0

A_IMB_D_R1

A_IMB_D_R2

A_IMB_D_R3

A_IMB_D_R4

A_IMB_D_R5

A_IMB_D_R6

A_IMB_D_R7

A_IMB_D_R8

A_IMB_D_R9

A_IMB_D_R10

A_IMB_D_R11

A_IMB_D_R12

A_IMB_D_R13

A_IMB_D_R14

A_IMB_D_R15

A_IMB_D_T0

A_IMB_D_T1

A_IMB_D_T2

A_IMB_D_T3

A_IMB_D_T4

A_IMB_D_T5

A_IMB_D_T6

A_IMB_D_T7

A_IMB_D_T8

A_IMB_D_T9

A_IMB_D_T10

A_IMB_D_T11

A_IMB_D_T12

A_IMB_D_T13

A_IMB_D_T14

A_IMB_D_T15

R931 0

R933 0

T_IMB_D_R0

T_IMB_D_R1

T_IMB_D_R2

T_IMB_D_R3

R318 1K

A_IMB_CON_R 25

A_IMB_CLK_R_P 25

A_IMB_CLK_R_N 25

A_IMB_PAR_R 25

A_IMB_CON_T 25

A_IMB_CLK_T_P_R 25

A_IMB_CLK_T_N_R 25

A_IMB_PAR_T 25

T_IMB_CLK_R 41

T_IMB_CON_R 41

T_IMB_PAR_R 41

PROC_RESET# 4,6,9,11

POWERGOOD_CMIC 16,59

VCC25

TESTMODE# 16

RCC_SDA 16,25,27,49,51,52,54

RCC_SCL 16,25,27,49,51,52,54

VDD_IMB

CMIC_IMB_COMP_PD

R372 X_255

CMIC_IMB_RCOMP

R350 100

CMIC_IMB_COMP_PU

R883 100

CMIC_IMB_COMP_PD

R884 255

CMIC_IMB_COMP_PU

R358 X_255

*** Difference with

Rev:A1.0 Ckt

1 1

A

B

IMB_VREF_CMIC

IMB_VREF_CMIC

C2701uC273

VDD_IMB

R340

100

C277

1000p-0805

C

R334

100

Micro Star Restricted Secret

Title

CMIC IMB Interface

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

D

http://www.msi.com.tw

E

Last Revision Date:

Thursday, March 21, 2002

Sheet

13 68

of

Rev

0D

0.1u

Page 14

A

B

C

D

E

4 4

R_A_SD0_0

AA22

R_A_SD0_1

AD22

R_A_SD0_2

AC19

R_A_SD0_3

AA18

R_A_SD0_4

AB23

R_A_SD0_5

AB19

R_A_SD0_6

AD19

R_A_SD0_7

Y16

R_A_SD1_0

V15

R_A_SD1_1

AG22

R_A_SD1_2

AB15

R_A_SD1_3

AD16

R_A_SD1_4

AG21

R_A_SD1_5

AF19

R_A_SD1_6

AG17

R_A_SD1_7

AB16

R_A_SD2_0

AG14

R_A_SD2_1

Y14

R_A_SD2_2

AF13

R_A_SD2_3

AG12

R_A_SD2_4

AE14

R_A_SD2_5

V14

R_A_SD2_6

AG13

R_A_SD2_7

AE13

R_A_SD3_0

Y13

R_A_SD3_1

AF9

R_A_SD3_2

AE8

R_A_SD3_3

3 3

2 2

1 1

R_A_SD3_4

R_A_SD3_5

R_A_SD3_6

R_A_SD3_7

R_A_SD4_0

R_A_SD4_1

R_A_SD4_2

R_A_SD4_3

R_A_SD4_4

R_A_SD4_5

R_A_SD4_6

R_A_SD4_7

R_A_SD5_0

R_A_SD5_1

R_A_SD5_2

R_A_SD5_3

R_A_SD5_4

R_A_SD5_5

R_A_SD5_6

R_A_SD5_7

R_A_SD6_0

R_A_SD6_1

R_A_SD6_2

R_A_SD6_3

R_A_SD6_4

R_A_SD6_5

R_A_SD6_6

R_A_SD6_7

R_A_SD7_0

R_A_SD7_1

R_A_SD7_2

R_A_SD7_3

R_A_SD7_4

R_A_SD7_5

R_A_SD7_6

R_A_SD7_7

R_A_SD8_0

R_A_SD8_1

R_A_SD8_2

R_A_SD8_3

R_A_SD8_4

R_A_SD8_5

R_A_SD8_6

R_A_SD8_7

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

AD10

AA12

AG8

AG6

AG5

T10

Y4

R11

T7

W5

Y3

U6

U1

T3

R2

R4

R5

T5

R1

K8

R6

N3

N1

M2

M4

N8

N4

L1

M3

H1

H2

L6

M10

J5

J3

L8

K10

AF3

AG2

AB10

AA9

AE6

AF5

AC8

AB9

AD5

AE5

Y10

AA8

Y9

Y7

AF1

AE2

AD3

AE3

AF2

Y8

CMIC-WS

U20C

A_SD0_0

A_SD0_1

A_SD0_2

A_SD0_3

A_SD0_4

A_SD0_5

A_SD0_6

A_SD0_7

A_SD1_0

A_SD1_1

A_SD1_2

A_SD1_3

A_SD1_4

A_SD1_5

A_SD1_6

A_SD1_7

A_SD2_0

A_SD2_1

A_SD2_2

A_SD2_3

A_SD2_4

A_SD2_5

A_SD2_6

A_SD2_7

A_SD3_0

A_SD3_1

A_SD3_2

A_SD3_3

A_SD3_4

A_SD3_5

A_SD3_6

A_SD3_7

A_SD4_0

A_SD4_1

A_SD4_2

A_SD4_3

A_SD4_4

A_SD4_5

A_SD4_6

A_SD4_7

A_SD5_0

A_SD5_1

A_SD5_2

A_SD5_3

A_SD5_4

A_SD5_5

A_SD5_6

A_SD5_7

A_SD6_0

A_SD6_1

A_SD6_2

A_SD6_3

A_SD6_4

A_SD6_5

A_SD6_6

A_SD6_7

A_SD7_0

A_SD7_1

A_SD7_2

A_SD7_3

A_SD7_4

A_SD7_5

A_SD7_6

A_SD7_7

A_SD8_0

A_SD8_1

A_SD8_2

A_SD8_3

A_SD8_4

A_SD8_5

A_SD8_6

A_SD8_7

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8