Page 1

5

4

3

2

1

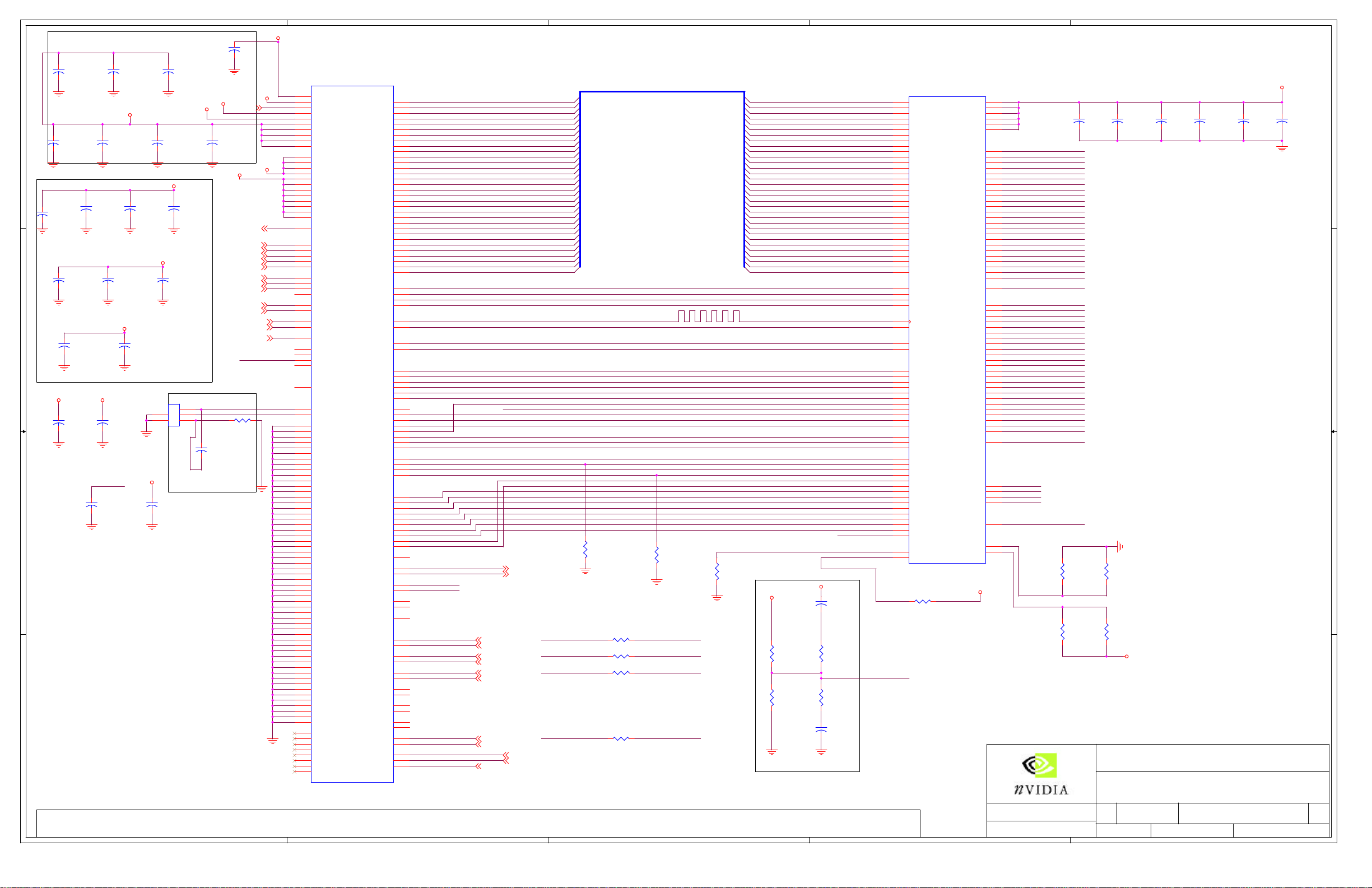

NV28M-P138, DAC, TMDS, LVDS, TVout, 64MB 4MX32 BGA DDR, AGP4X, Dell Mobile

X00

1. Schematics taken from E153-A00.

X17

1. Use RUNPWRGD for all PS enabling.

D D

A01:

X40

1. Corrected serial ROM hookup.

A02:

X42

1. Corrected I2C2 hookup at U9 (CH7009).

2. Changed R254 to 1.5K 1%. This raises

NVVDD to 1.25V.

3. Connect GPIO1 to 90C387 PD, and disconnect

SUS_STAT- from motherboard.

4. Change Q2 to FDS6982.

X44

5. Change R287 to 2.67K and R254 to 1.1K when NVVDDSW stuff

option is employed, with R254 = 1.5K when no NVVDDSW is used

(NOSW stuff option).

6. Removed TP606 to allow better guard trace on thermal

sensor D+ and D- lines.

7. Connected CH_GPIO0 to NSM_DUAL to select single or

dual link panels.

C C

B B

140-10138-0000-A01

A A

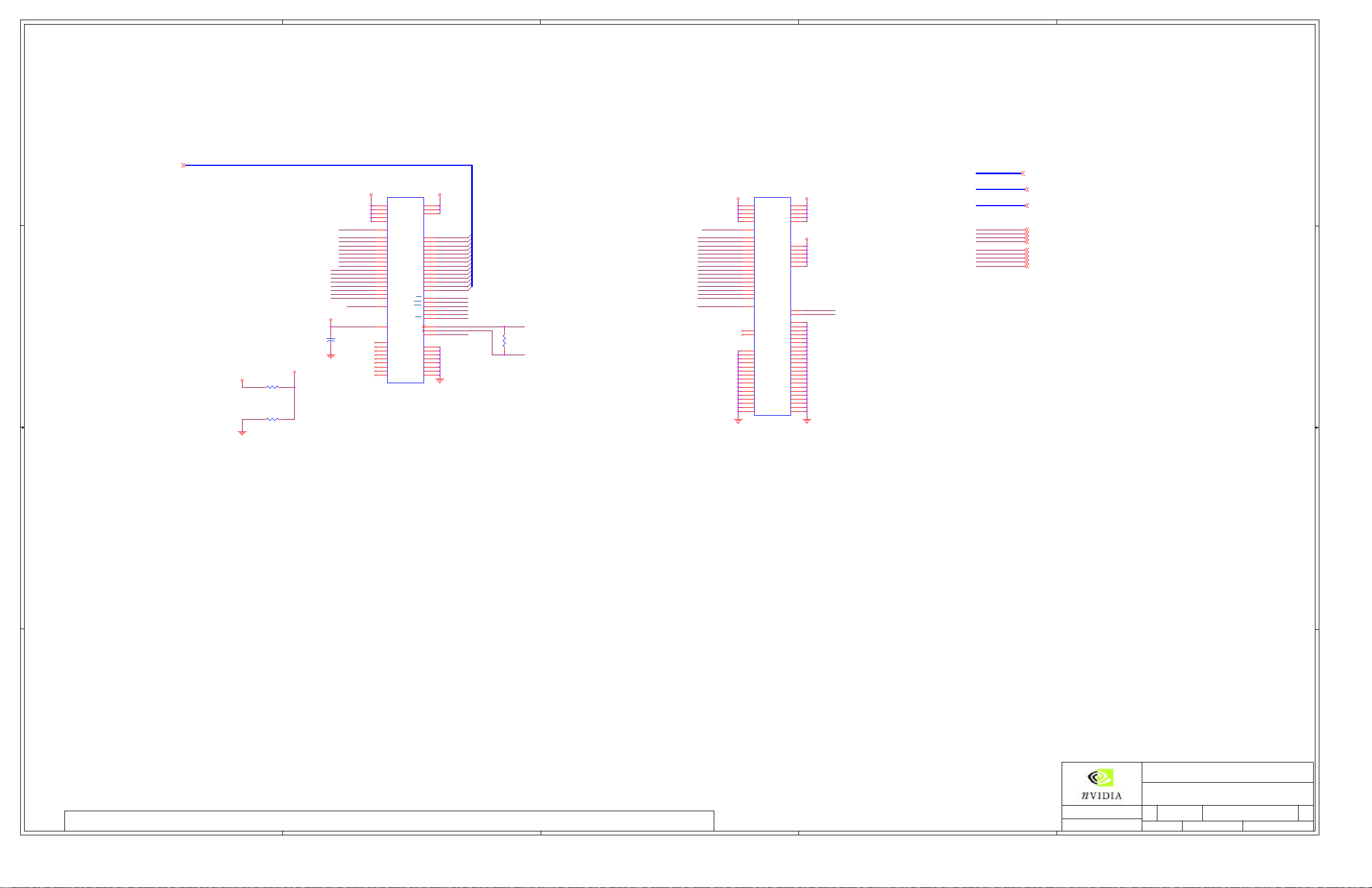

1.1 TOP PAGE

NVIDIA Corporation

2701 San Tomas Expressway

Santa Clara, CA 95050, USA

602-10138-0000-A01

P138 L/K Module

Size

"ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO

WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE."

5

4

3

CAGE Code

Custom

2

Thursday, October 24, 2002

Scale

DWG NO

Sheet

1

1 16

Rev

of

Page 2

5

Place close

to the AGP

connector

12

C166

0.047uF

X7R

SMD0402

COMMON

GND

D D

12

C165

0.047uF

X7R

SMD0402

COMMON

GND

12

C118

4u7

10%

X5R

6.3V

SMD0805

COMMON

GND

12

C101

0.1uF

X7R

SMD0603

COMMON

GND

C C

B B

A A

12

C169

0.1uF

X7R

SMD0603

COMMON

GND

5VSUS

12

C173

0.1uF

X7R

SMD0603

COMMON

GND

"ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO

WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE."

GND

10%

25V

12

10%

25V

10%

25V

GND

10%

25V

GND

C170

0.1uF

X7R

SMD0402

COMMON

10%

25V

3VSUS

GND

12

12

GND

12

C110

0.047uF

X7R

SMD0402

COMMON

10%

10V

12

GND

PWR_SRC

12

C174

0.1uF

X7R

SMD0603

COMMON

5VALW

C164

0.1uF

X7R

SMD0402

COMMON

C175

0.047uF

X7R

SMD0402

COMMON

AGPVDDQ

12

GND

C157

0.1uF

X7R

SMD0603

COMMON

12

GND

10%

25V

10%

10V

10%

25V

10%

25V

C171

0.1uF

X7R

SMD0402

COMMON

10%

25V

C168

0.1uF

X7R

SMD0603

COMMON

5VRUN

GND

12

GND

12

C111

0.047uF

X7R

SMD0402

COMMON

GND

3VRUN

10%

10V

GND

PWR_SRC

12

GND

10%

25V

J1

4

5

CON3

COMMON

12

C163

0.1uF

X7R

SMD0402

COMMON

5

C176

0.047uF

X7R

SMD0402

COMMON

10%

25V

12

C167

0.1uF

X7R

SMD0402

COMMON

C100

0.1uF

10%

X7R

25V

SMD0603

COMMON

Place close

to the

respective

pins on the

AGP

connector

1

2

3

Place C172 near J1.

Place R101 near

J10.41

10%

10V

10%

25V

3VSUS

GND

10%

10V

FGND

12

C172

0.1UF

SMD0402

COMMON

12

GND

5VSUS

C112

0.047uF

X7R

SMD0402

COMMON

PWR_SRC

DAC_VSYNC10

DAC_HSYNC10

FAN_5V

1 2

R101

12

5VALW14

VDDEN

SMB_CLK14

SMB_DAT14

RUNPWROK16

0R

SMD0402

COMMON

C161

1uF

25V

SMD0805

5VRUN

10%

25V

3VRUN

RED10

GREEN10

BLUE10

TVY12

TVC12

CVBS12

DDC_CLK10

DDC_DAT10

AGPDBI_LO

FAN_TACH

5%

12V

5VALW

5VSUS

3VSUS

J10

184

12V

188

5VRUN

200

5VALW

183

5VSUS

154

3VSUS

48

VDDQ1

69

VDDQ2

109

VDDQ3

148

VDDQ4

182

VDDQ5

38

3VRUN1

176

3VRUN2

178

3VRUN3

190

3VRUN4

185

PWR_SRC1

189

PWR_SRC2

193

PWR_SRC3

194

PWR_SRC4

195

PWR_SRC5

196

PWR_SRC6

197

PWR_SRC7

199

PWR_SRC8

186

FPVCC

145

VSYNC

149

HSYNC

153

VGA_RED

157

VGA_GRN

161

BGA_BLU

165

TV_Y

169

TV_C

173

TV_CVBS

177

TV_DAC4

174

SMB_CLK

172

SMB_DAT

166

CLK_DDC2

164

DAT_DDC2

67

RUNPWROK

35

AGP8X_DET_CG

37

AGP8X_DT_GC

108

DBI_LO

107

DBI_HI

158

NC1

44

VID_FAN_5V

42

VID_FAN_TACH

1

GND1

2

GND2

9

GND3

10

GND4

17

GND5

18

GND6

25

GND7

26

GND8

33

GND9

34

GND10

41

GND11

45

GND12

46

GND13

52

GND14

53

GND15

59

GND16

60

GND17

71

GND18

72

GND19

81

GND20

82

GND21

87

GND22

88

GND23

93

GND24

94

GND25

101

GND26

102

GND27

113

GND28

114

GND29

119

GND30

120

GND31

127

GND32

128

GND33

133

GND34

134

GND35

141

GND36

142

GND37

143

GND38

147

GND39

150

GND40

151

GND41

155

GND42

159

GND43

160

GND44

163

GND45

167

GND46

168

GND47

171

GND48

175

GND49

179

GND50

180

GND51

187

GND52

191

GND53

192

GND54

198

GND55

5

DVI_NC1

6

DVI_NC2

13

DVI_NC3

14

DVI_NC4

21

DVI_NC5

22

DVI_NC6

29

DVI_NC7

30

DVI_NC8

QT01200A-2120L

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE0#

C/BE1#

C/BE2#

C/BE3#

CLK66_AGP

RST#

GNT#

REQ#

FRAME#

IRDY#

TRDY#

DEVSEL#

STOP#

PAR

INTB#

INTA#

RBF#

WBF#

PIPE#

ST0

ST1

ST2

ADSTB1

ADSTB1#

ADSTB0

ADSTB0#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SBSTB

SBSTB#

ICH_SUS_STAT#

AGP_BUSY#

STP_AGP#

VREFGC

VREFCG

GC_SUSPEND#

M_ID2#

M_SEN#

DVI_TX0+

DVI_TX0-

DVI_TX1+

DVI_TX1-

DVI_TX2+

DVI_TX2-

DVI_TX3+

DVI_TX3-

DVI_TX4+

DVI_TX4-

DVI_TX5+

DVI_TX5-

DVI_CLK+

DVI_CLK-

DVI_SCLK

DVI_SDAT

DVI_DETECT

4

138

139

136

137

132

135

130

125

126

123

124

121

122

117

118

115

106

104

98

105

96

103

92

100

90

97

86

95

84

85

80

83

140

116

99

79

43

68

146

47

78

73

75

66

77

144

39

40

74

76

70

49

50

51

91

89

131

129

54

56

61

58

63

62

65

64

55

57

181

110

156

112

111

152

170

162

3

7

11

15

19

23

27

31

4

8

12

16

20

24

28

32

36

AGPVREFGC

AGPVREFCG

4

AGP_BUSY

AGP_STOP

DVI_TX0+

DVI_TX0-

DVI_TX1+

DVI_TX1-

DVI_TX2+

DVI_TX2-

Single link only - pairs 3-5 not used.

DVI_CLK-

DVI_CLK

DVI_DETECT

DVI_DAT

3

PCIAD[31:0]

PCIAD0

PCIAD1

PCIAD2

PCIAD3

PCIAD4

PCIAD5

PCIAD6

PCIAD7

PCIAD8

PCIAD9

PCIAD10

PCIAD11

PCIAD12

PCIAD13

PCIAD14

PCIAD15

PCIAD16

PCIAD17

PCIAD18

PCIAD19

PCIAD20

PCIAD21

PCIAD22

PCIAD23

PCIAD24

PCIAD25

PCIAD26

PCIAD27

PCIAD28

PCIAD29

PCIAD30

PCIAD31

PCICBE2 PCICBE2

TESTEN

12

R104

10K

SMD0603

COMMON

PCICLK

5%

AGPVDDQ

12

R105

1.5K

1%

SMD0402

COMMON

12

R107

1.5K

1%

SMD0402

COMMON

GND

PCIRST PCIRST

PCIFRAME PCIFRAME

PCIIRDY PCIIRDY

PCITRDY PCITRDY

PCISTOP PCISTOP

PCIPAR PCIPAR

AGPST0 AGPST0

AGPST1 AGPST1

AGPST2 AGPST2

AGPSBA3 AGPSBA3

AGP_BUSY 10

AGP_STOP 10

DVI_TX0+ 12

DVI_TX0- 12

DVI_TX1+ 12

DVI_TX1- 12

DVI_TX2+ 12

DVI_TX2- 12

DVI_CLK+ 12

DVI_CLK- 12

DVI_CLK 10

DVI_DAT 10

GPIO1

DVI_TX0+

DVI_TX1+

DVI_TX2+

DVI_CLK+

AGPADSTB1F

AGPADSTB1S

AGPADSTB0F

AGPADSTB0S

AGPSBSTBS AGPSBSTBS

12

R102

220K

SMD0402

COMMON

GND

R111

1 2

TMDSTERM

R112

1 2

TMDSTERM

R115

1 2

TMDSTERM

R117

1 2

TMDSTERM

PCICLK

GND

300R

SMD0402

300R

SMD0402

300R

SMD0402

300R

SMD0402

12

R103

220K

COMMON

SMD0402

5%

5%

5%

5%

GND

DVI_TX0-

DVI_TX1-

DVI_TX2-

DVI_CLK-DVI_CLK+

3

PCIDEVSELPCIDEVSEL

PCIINTAPCIINTA

AGPRBFAGPRBF

AGPWBFAGPWBF

AGPVDDQ

12

AGPREFHI

12

12

AGPREFLO

12

GND

PCIAD0

PCIAD1

PCIAD2

PCIAD3

PCIAD4

PCIAD5

PCIAD6

PCIAD7

PCIAD8

PCIAD9

PCIAD10

PCIAD11

PCIAD12

PCIAD13

PCIAD14

PCIAD15

PCIAD16

PCIAD17

PCIAD18

PCIAD19

PCIAD20

PCIAD21

PCIAD22

PCIAD23

PCIAD24

PCIAD25

PCIAD26

PCIAD27

PCIAD28

PCIAD29

PCIAD30

PCIAD31

PCICBE0PCICBE0

PCICBE1PCICBE1

PCICBE3PCICBE3

PCIGNTPCIGNT

PCIREQPCIREQ

AGPDBI_HIAGPDBI_HI

AGPDBI_LOAGPDBI_LO

AGPADSTB1F

AGPADSTB1S

AGPADSTB0F

AGPADSTB0S

AGPSBSTBFAGPSBSTBF

AGPSBA0AGPSBA0

AGPSBA1AGPSBA1

AGPSBA2AGPSBA2

AGPSBA4AGPSBA4

AGPSBA5AGPSBA5

AGPSBA6AGPSBA6

AGPSBA7AGPSBA7

AGPVREFCG

AGP-MBDET

C105

470pF

NPO5%50V

SMD0402

COMMON

R106

75R

1%

SMD0402

COMMON

R108

75R

1%

SMD0402

COMMON

C106

470pF

NPO5%50V

SMD0402

COMMON

AP33

AN32

AP32

AN31

AP31

AN30

AN29

AP29

AN27

AM26

AN26

AN25

AM24

AP24

AN24

AN23

AL28

AL26

AL27

AJ25

AL25

AJ24

AK24

AL23

AJ22

AL22

AK21

AJ20

AK20

AK19

AL19

AL20

AM28

AM22

AK26

AL24

AM13

AK16

AL16

AN12

AN20

AP20

AN21

AM20

AM21

AN22

AK18

AJ19

AL17

AL15

AL18

AN13

AK17

AM14

AK22

AJ23

AP28

AN28

AN17

AN16

AM15

AN14

AP15

AN15

AN18

AM17

AN19

AM18

AM29

AK15

R94

COMMON

AGPVREFGC

Place near

AGP interface

of GPU

2

U100A

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

PCI_CnBE0

PCI_CnBE1

PCI_CnBE2

PCI_CnBE3

PCI_CLK

PCI_RESET

PCI_GNT

PCI_REQ

PCI_FRAME

PCI_IRDY

PCI_TRDY

PCI_DEVSEL

PCI_STOP

PCI_PAR

AGP_DBI_HI

AGP_DBI_LO

PCI_INTA

AGP_RBF

AGP_WBF

AGP_ST0

AGP_ST1

AGP_ST2

AGP_AD_STB1F

AGP_AD_STB1S

AGP_AD_STB0F

AGP_AD_STB0S

AGP_SB_STBF

AGP_SB_STBS

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_VREF

R4

TESTMODE

AGP_MBDET

IC_NV28_GPU_BGA816_P10_SKT

BGA816_P10_NV28

1 2

10k 5%

SMD0402

2

D1_DATA0

D1_DATA1

D1_DATA2

D1_DATA3

D1_DATA4

D1_DATA5

D1_DATA6

D1_DATA7

D1_DATA8

D1_DATA9

D1_DATA10

D1_DATA11

D1_DATA12

D1_DATA13

D1_DATA14

D1_DATA15

D1_DATA16

D1_DATA17

D1_DATA18

D1_DATA19

D1_DATA20

D1_DATA21

D1_DATA22

D1_DATA23

D1_STROBE

D2_DATA0

D2_DATA1

D2_DATA2

D2_DATA3

D2_DATA4

D2_DATA5

D2_DATA6

D2_DATA7

D2_DATA8

D2_DATA9

D2_DATA10

D2_DATA11

D2_DATA12

D2_DATA13

D2_DATA14

D2_DATA15

D2_DATA16

D2_DATA17

D2_DATA18

D2_DATA19

D2_DATA20

D2_DATA21

D2_DATA22

D2_DATA23

D2_STROBE

BPCI_CLK

AGPCALPU

AGPCALPD

1

AD21

VDDQ

AH23

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

NC1

NC2

NC3

NC4

3VRUN

AF22

AH20

AF18

AH16

C4

D6

A2

D5

D4

E5

C3

F5

E4

F4

D3

C2

D2

B1

G4

F3

C1

E2

G3

H4

D1

F2

K5

E1

G5

J4

J6

G2

K4

L5

J3

H2

J2

L4

K3

K6

K2

M4

L2

N5

M3

N4

M2

N3

P5

M6

N2

N6

P4

L6

A1

F15

F26

R29

AB3

AJ17

AJ18

TPNC-NC1

TPNC-NC2

TPNC-NC3

TPNC-NC4

AGPCALPU

AGPCALPD

D1_DATA0

D1_DATA1

D1_DATA2

D1_DATA3

D1_DATA4

D1_DATA5

D1_DATA6

D1_DATA7

D1_DATA8

D1_DATA9

D1_DATA10

D1_DATA11

D1_DATA12

D1_DATA13

D1_DATA14

D1_DATA15

D1_DATA16

D1_DATA17

D1_DATA18

D1_DATA19

D1_DATA20

D1_DATA21

D1_DATA22

D1_DATA23

D1_STROBE

D2_DATA0

D2_DATA1

D2_DATA2

D2_DATA3

D2_DATA4

D2_DATA5

D2_DATA6

D2_DATA7

D2_DATA8

D2_DATA9

D2_DATA10

D2_DATA11

D2_DATA12

D2_DATA13

D2_DATA14

D2_DATA15

D2_DATA16

D2_DATA17

D2_DATA18

D2_DATA19

D2_DATA20

D2_DATA21

D2_DATA22

D2_DATA23

D2_STROBE

TP_BPCI_CLK

12

R80

49.9R

SMD0402

COMMON

12

R82

56.2R

SMD0402

COMMON

C103

12

2200PF

SMD0402

COMMON

1%

1%

10VX7R

20%

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

TPNC

12

12

C914

12

2200PF

SMD0402

COMMON

GND

R81

100R

5%

SMD0402

NO_STUFF

R83

100R

5%

SMD0402

NO_STUFF

20%

10VX7R

AGPVDDQ

C915

12

220PF

X7R 10%

SMD0402

COMMON

C921

12

2200PF

16V

SMD0402

COMMON

1.2 AGP Interface to NV28

NVIDIA Corporation

2701 San Tomas Expressway

Santa Clara, CA 95050, USA

P138 L/K Module

Size

Thursday, October 24, 2002

Scale

Custom

CAGE Code

DWG NO

1

AGPVDDQ

C922

12

20%

220PF

10VX7R

X7R 10%

SMD0402

COMMON

Sheet

C1428

12

4.7uF

16V

6.3V

SMD0805

COMMON

GND

2 16

of

10%

X5R

Rev

Page 3

NVVDD

5

4

3

2

1

C1429

12

4.7uF

6.3V

SMD0805

GND

FBVDD

GND

FBVDD

GND

COMMON

C1312

12

470pF

10V X7R

SMD0603

COMMON

C1336

12

2200PF

20%

50V X7R

SMD0603

COMMON

D D

C C

10%

X5R

20%

C1337

12

0.01UF

10%

50V X7R

SMD0603

COMMON

12

C1314

12

0.01UF

10%

50V X7R

SMD0603

COMMON

C1430

4.7uF

6.3V

SMD0805

COMMON

10%

X5R

C1338

12

0.1UF

16V X7R

SMD0603

COMMON

12

C1316

12

470pF

10V X7R

SMD0603

COMMON

10%

C881

4.7uF

6.3V

SMD0805

COMMON

10%

X5R

20%

C1339

12

470pF

16V X7R

SMD0603

COMMON

C1317

12

470pF

10V X7R

SMD0603

COMMON

10%

C906

12

220pF

X7R 10%

SMD0402

COMMON

20%

C1340

12

2200PF

20%

50V X7R

SMD0603

COMMON

16V

C908

12

2200PF

20%

10V X7R

SMD0402

COMMON

C1329

12

470pF

10V X7R

SMD0603

COMMON

20%

C875

12

470pF

X7R 10%

SMD0402

COMMON

12

C909

220pF

16V

X7R 10%

SMD0402

COMMON

C1330

12

2200PF

20%

50V X7R

SMD0603

COMMON

16V

C876

12

2200PF

20%

10V X7R

SMD0402

COMMON

C910

12

2200PF

20%

10V X7R

SMD0402

COMMON

C1331

12

0.01UF

10%

50V X7R

SMD0603

COMMON

C877

12

470pF

X7R 10%

SMD0402

COMMON

C913

12

220pF

X7R 10%

SMD0402

COMMON

16V

16V

C1332

12

0.1UF

16V X7R

SMD0603

COMMON

12

12

10%

C878

470pF

X7R 10%

SMD0402

COMMON

C1415

220pF

X7R 10%

SMD0402

COMMON

16V

16V

C1333

12

470pF

10V X7R

SMD0603

COMMON

C879

12

470pF

X7R 10%

SMD0402

COMMON

C1416

12

220pF

X7R 10%

SMD0402

COMMON

20%

16V

16V

12

C880

12

470pF

X7R 10%

SMD0402

COMMON

12

C1334

2200PF

20%

50V X7R

SMD0603

COMMON

16V

C1413

220pF

X7R 10%

SMD0402

COMMON

C911

12

470pF

X7R 10%

SMD0402

COMMON

16V

C1335

12

470pF

10V X7R

SMD0603

COMMON

C1414

12

220pF

X7R 10%

SMD0402

COMMON

16V

20%

C886

12

470pF

X7R 10%

SMD0402

COMMON

16V

C882

12

220pF

X7R 10%

SMD0402

COMMON

16V

16V

C890

12

470pF

X7R 10%

SMD0402

COMMON

C883

12

2200PF

20%

10V X7R

SMD0402

COMMON

16V

C894

12

470pF

X7R 10%

SMD0402

COMMON

C884

12

220pF

X7R 10%

SMD0402

COMMON

16V

16V

C904

12

2200PF

20%

10V X7R

SMD0402

COMMON

C887

12

2200PF

20%

10V X7R

SMD0402

COMMON

C888

12

220pF

X7R 10%

SMD0402

COMMON

16V

12

C889

2200PF

20%

10V X7R

SMD0402

COMMON

C891

12

220pF

X7R 10%

SMD0402

COMMON

C895

2200PF

20%

10V X7R

SMD0402

COMMON

C896

12

2200PF

20%

10V X7R

SMD0402

COMMON

12

C892

12

12

16V

220pF

16V

X7R 10%

SMD0402

COMMON

C897

2200PF

20%

10V X7R

SMD0402

COMMON

C898

12

220pF

X7R 10%

SMD0402

COMMON

C899

220pF

X7R 10%

SMD0402

COMMON

16V

C900

12

2200PF

20%

10V X7R

SMD0402

COMMON

12

12

16V

C902

2200PF

20%

10V X7R

SMD0402

COMMON

C903

12

2200PF

20%

10V X7R

SMD0402

COMMON

C905

12

220pF

X7R 10%

SMD0402

COMMON

16V

2200PF

20%

10V X7R

SMD0402

COMMON

220pF

X7R 10%

SMD0402

COMMON

16V

C931

C930

12

12

3VRUN

C907

C893

12

12

2200PF

20%

10V X7R

SMD0402

B B

A A

COMMON

GND

470pF

X7R 10%

SMD0402

COMMON

C918

C919

C920

12

12

16V

470pF

16V

X7R 10%

SMD0402

COMMON

2200PF

20%

10V X7R

SMD0402

COMMON

12

470pF

X7R 10%

SMD0402

COMMON

C901

12

16V

470pF

X7R 10%

SMD0402

COMMON

16V

C104

12

470pF

X7R 10%

SMD0402

COMMON

C917

12

2200PF

16V

20%

10V X7R

SMD0402

COMMON

C1347

12

470pF

10V X7R

SMD0603

COMMON

20%

C1350

12

0.01UF

10%

50V X7R

SMD0603

COMMON

C1352

12

470pF

10V X7R

SMD0603

COMMON

20%

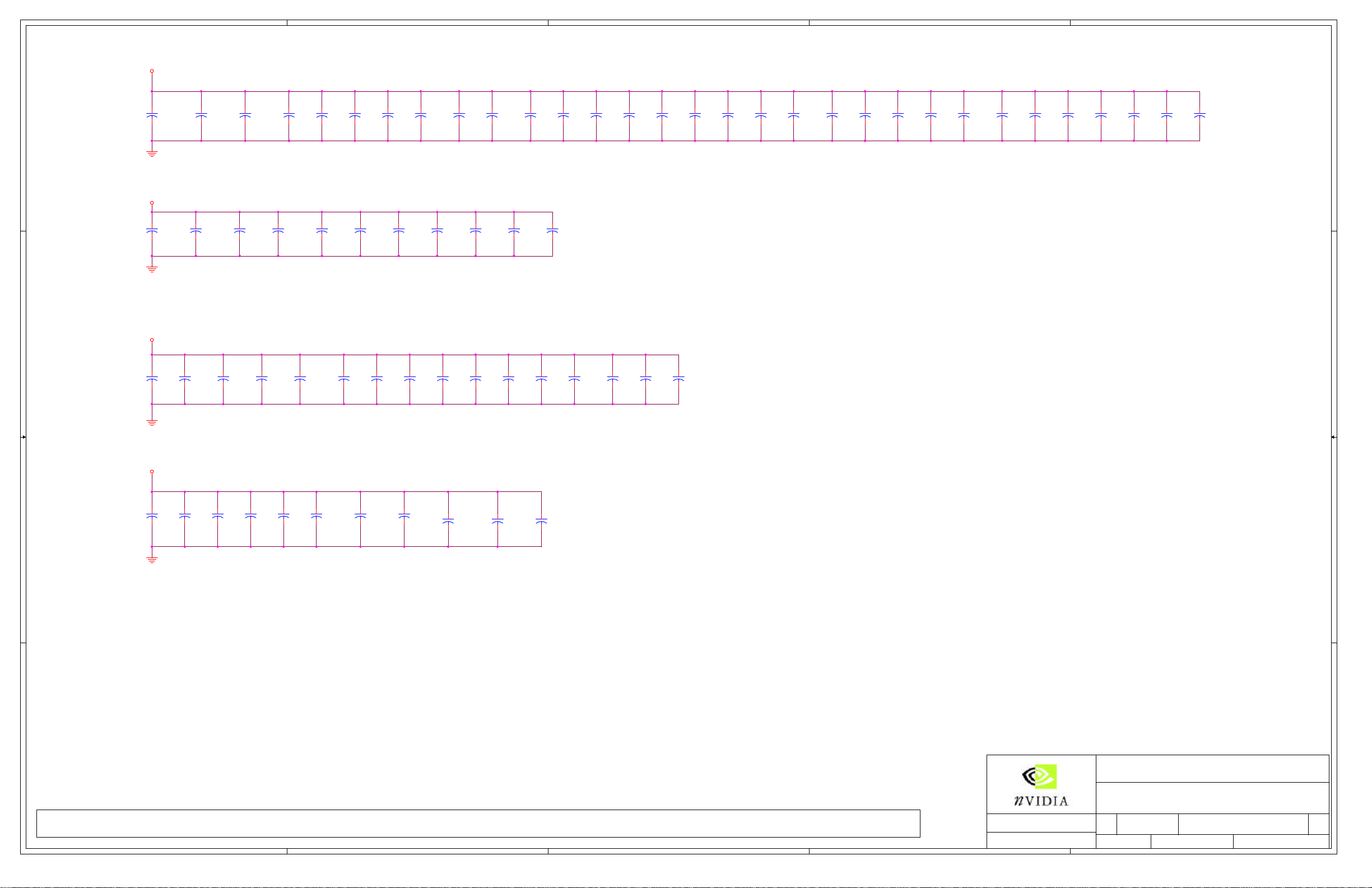

2.0 NV DECOUPLING

NVIDIA Corporation

2701 San Tomas Expressway

Santa Clara, CA 95050, USA

"ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO

WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE."

5

4

3

P138 L/K Module

Size

CAGE Code

Custom

2

Wednesday, October 23, 2002

Scale

DWG NO

Sheet

1

3 16

Rev

of

Page 4

A

4 4

B

C

D

FBA_DATA[31:0] 5

FBB_DATA[31:0] 6

FBC_DATA[31:0] 7

FBD_DATA[31:0] 8

FBA_ADR[13:0] 5

FBB_ADR[13:0] 6

FBC_ADR[13:0] 7

FBD_ADR[13:0] 8

E

FBD_DATA0

FBD_DATA1

FBD_DATA2

FBD_DATA3

FBD_DATA4

FBD_DATA5

FBD_DATA6

FBD_DATA7

FBD_DATA8

FBD_DATA9

FBD_DATA10

FBD_DATA11

FBD_DATA12

FBD_DATA13

FBD_DATA14

FBD_DATA15

FBD_DATA16

FBD_DATA17

FBD_DATA18

FBD_DATA19

FBD_DATA20

FBD_DATA21

FBD_DATA22

FBD_DATA23

FBD_DATA24

FBD_DATA25

FBD_DATA26

3 3

2 2

FBVDD

12

R400

1%

1K

COMMON

SMD0603

12

R461

1%

1K

COMMON

SMD0603

GND GND

12

FB_VREF

C1182

0.01UF

COMMON

SMD0603

X7R

10%50V

FBD_DATA27

FBD_DATA28

FBD_DATA29

FBD_DATA30

FBD_DATA31

FBD_ADR0

FBD_ADR1

FBD_ADR2

FBD_ADR3

FBD_ADR4

FBD_ADR5

FBD_ADR6

FBD_ADR7

FBD_ADR8

FBD_ADR9

FBD_ADR10

FBD_ADR11

FBD_ADR12

FBD_ADR13

FBD_DQM0

FBD_DQM1

FBD_DQM2

FBD_DQM3

FBD_DQS0

FBD_DQS1

FBD_DQS2

FBD_DQS3

FBD_RAS_

FBD_CAS_

FBD_WE_

FBD_CS0_

FBD_CLK0

FBD_CLK0B

FBD_CLK1

FBD_CLK1B

FBD_CKE

U100D

C19

FBD_DATA0

B19

FBD_DATA1

E18

FBD_DATA2

C18

FBD_DATA3

B17

FBD_DATA4

C17

FBD_DATA5

D17

FBD_DATA6

E17

FBD_DATA7

F17

FBD_DATA8

B16

FBD_DATA9

C16

FBD_DATA10

D16

FBD_DATA11

B15

FBD_DATA12

C15

FBD_DATA13

D15

FBD_DATA14

B14

FBD_DATA15

B7

FBD_DATA16

D9

FBD_DATA17

A6

FBD_DATA18

B6

FBD_DATA19

D8

FBD_DATA20

C7

FBD_DATA21

E8

FBD_DATA22

B5

FBD_DATA23

A4

FBD_DATA24

C6

FBD_DATA25

D7

FBD_DATA26

E7

FBD_DATA27

B4

FBD_DATA28

B3

FBD_DATA29

E6

FBD_DATA30

F7

FBD_DATA31

B13

FBD_ADR0

D14

FBD_ADR1

C13

FBD_ADR2

B12

FBD_ADR3

E14

FBD_ADR4

B10

FBD_ADR5

D11

FBD_ADR6

C10

FBD_ADR7

B9

FBD_ADR8

F12

FBD_ADR9

E11

FBD_ADR10

C9

FBD_ADR11

B8

FBD_ADR12

E10

FBD_ADR13

B18

FBD_DQM0

E16

FBD_DQM1

A5

FBD_DQM2

A3

FBD_DQM3

F18

FBD_DQS0

F16

FBD_DQS1

F9

FBD_DQS2

F8

FBD_DQS3

C12

FBD_RAS_

D13

FBD_CAS_

B11

FBD_WE_

E13

FBD_CS0_

D12

FBD_CS1_

F10

FBD_CLK0

F11

FBD_CLK0_

F13

FBD_CLK1

F14

FBD_CLK1_

D10

FBD_CKE

A33

FB_VREF

IC_NV28_GPU_BGA816_P10_SKT

BGA816_P10_NV28

FBC_DATA0

FBC_DATA1

FBC_DATA2

FBC_DATA3

FBC_DATA4

FBC_DATA5

FBC_DATA6

FBC_DATA7

FBC_DATA8

FBC_DATA9

FBC_DATA10

FBC_DATA11

FBC_DATA12

FBC_DATA13

FBC_DATA14

FBC_DATA15

FBC_DATA16

FBC_DATA17

FBC_DATA18

FBC_DATA19

FBC_DATA20

FBC_DATA21

FBC_DATA22

FBC_DATA23

FBC_DATA24

FBC_DATA25

FBC_DATA26

FBC_DATA27

FBC_DATA28

FBC_DATA29

FBC_DATA30

FBC_DATA31

FBC_ADR0

FBC_ADR1

FBC_ADR2

FBC_ADR3

FBC_ADR4

FBC_ADR5

FBC_ADR6

FBC_ADR7

FBC_ADR8

FBC_ADR9

FBC_ADR10

FBC_ADR11

FBC_ADR12

FBC_ADR13

FBC_DQM0

FBC_DQM1

FBC_DQM2

FBC_DQM3

FBC_DQS0

FBC_DQS1

FBC_DQS2

FBC_DQS3

FBC_RAS_

FBC_CAS_

FBC_WE_

FBC_CS0_

FBC_CS1_

FBC_CLK0

FBC_CLK0_

FBC_CLK1

FBC_CLK1_

FBC_CKE

D32

C33

F30

E31

C32

D31

E30

B34

B32

C31

D30

E29

A32

B31

D29

E28

D24

B24

D23

C23

E22

D22

C22

B22

E21

F21

B21

D21

C20

B20

E19

D19

A31

B30

C29

D28

E27

B28

D26

B27

F24

C26

B26

C25

E24

B25

A34

F27

B23

D20

J29

F28

F20

F19

B29

A30

C28

D27

A29

F22

F23

E25

F25

D25

FBC_DATA0

FBC_DATA1

FBC_DATA2

FBC_DATA3

FBC_DATA4

FBC_DATA5

FBC_DATA6

FBC_DATA7

FBC_DATA8

FBC_DATA9

FBC_DATA10

FBC_DATA11

FBC_DATA12

FBC_DATA13

FBC_DATA14

FBC_DATA15

FBC_DATA16

FBC_DATA17

FBC_DATA18

FBC_DATA19

FBC_DATA20

FBC_DATA21

FBC_DATA22

FBC_DATA23

FBC_DATA24

FBC_DATA25

FBC_DATA26

FBC_DATA27

FBC_DATA28

FBC_DATA29

FBC_DATA30

FBC_DATA31

FBC_ADR0

FBC_ADR1

FBC_ADR2

FBC_ADR3

FBC_ADR4

FBC_ADR5

FBC_ADR6

FBC_ADR7

FBC_ADR8

FBC_ADR9

FBC_ADR10

FBC_ADR11

FBC_ADR12

FBC_ADR13

FBC_DQM0

FBC_DQM1

FBC_DQM2

FBC_DQM3

FBC_DQS0

FBC_DQS1

FBC_DQS2

FBC_DQS3

FBC_RAS_

FBC_CAS_

FBC_WE_

FBC_CS0_

FBC_CS1_FBD_CS1_

FBC_CLK0

FBC_CLK0B

FBC_CLK1

FBC_CLK1B

FBC_CKE

FBB_DATA0

FBB_DATA1

FBB_DATA2

FBB_DATA3

FBB_DATA4

FBB_DATA5

FBB_DATA6

FBB_DATA7

FBB_DATA8

FBB_DATA9

FBB_DATA10

FBB_DATA11

FBB_DATA12

FBB_DATA13

FBB_DATA14

FBB_DATA15

FBB_DATA16

FBB_DATA17

FBB_DATA18

FBB_DATA19

FBB_DATA20

FBB_DATA21

FBB_DATA22

FBB_DATA23

FBB_DATA24

FBB_DATA25

FBB_DATA26

FBB_DATA27

FBB_DATA28

FBB_DATA29

FBB_DATA30

FBB_DATA31

FBB_ADR0

FBB_ADR1

FBB_ADR2

FBB_ADR3

FBB_ADR4

FBB_ADR5

FBB_ADR6

FBB_ADR7

FBB_ADR8

FBB_ADR9

FBB_ADR10

FBB_ADR11

FBB_ADR12

FBB_ADR13

FBB_DQM0

FBB_DQM1

FBB_DQM2

FBB_DQM3

FBB_DQS0

FBB_DQS1

FBB_DQS2

FBB_DQS3

FBB_RAS_

FBB_CAS_

FBB_WE_

FBB_CS0_

FBB_CS1_

FBB_CLK0

FBB_CLK0B

FBB_CLK1

FBB_CLK1B FBA_CLK1B

FBB_CKE

U100C

AA30

FBB_DATA0

W33

FBB_DATA1

W32

FBB_DATA2

W31

FBB_DATA3

V34

FBB_DATA4

V33

FBB_DATA5

V32

FBB_DATA6

V31

FBB_DATA7

U34

FBB_DATA8

U33

FBB_DATA9

U32

FBB_DATA10

T33

FBB_DATA11

R32

FBB_DATA12

R33

FBB_DATA13

M33

FBB_DATA14

U30

FBB_DATA15

K31

FBB_DATA16

G33

FBB_DATA17

L30

FBB_DATA18

K30

FBB_DATA19

F33

FBB_DATA20

G32

FBB_DATA21

E34

FBB_DATA22

H31

FBB_DATA23

F32

FBB_DATA24

E33

FBB_DATA25

D34

FBB_DATA26

H30

FBB_DATA27

C34

FBB_DATA28

D33

FBB_DATA29

F31

FBB_DATA30

G30

FBB_DATA31

T31

FBB_ADR0

N33

FBB_ADR1

P33

FBB_ADR2

R31

FBB_ADR3

T30

FBB_ADR4

M32

FBB_ADR5

N31

FBB_ADR6

P30

FBB_ADR7

K32

FBB_ADR8

L31

FBB_ADR9

M31

FBB_ADR10

P29

FBB_ADR11

H33

FBB_ADR12

J32

FBB_ADR13

W30

FBB_DQM0

T32

FBB_DQM1

J31

FBB_DQM2

G31

FBB_DQM3

W29

FBB_DQS0

V29

FBB_DQS1

L29

FBB_DQS2

K29

FBB_DQS3

L33

FBB_RAS_

N32

FBB_CAS_

P31

FBB_WE_

K33

FBB_CS0_

J33

FBB_CS1_

M29

FBB_CLK0

N29

FBB_CLK0_

U29

FBB_CLK1

T29

FBB_CLK1_

N30

FBB_CKE

IC_NV28_GPU_BGA816_P10_SKT

BGA816_P10_NV28

FBA_DATA0

FBA_DATA1

FBA_DATA2

FBA_DATA3

FBA_DATA4

FBA_DATA5

FBA_DATA6

FBA_DATA7

FBA_DATA8

FBA_DATA9

FBA_DATA10

FBA_DATA11

FBA_DATA12

FBA_DATA13

FBA_DATA14

FBA_DATA15

FBA_DATA16

FBA_DATA17

FBA_DATA18

FBA_DATA19

FBA_DATA20

FBA_DATA21

FBA_DATA22

FBA_DATA23

FBA_DATA24

FBA_DATA25

FBA_DATA26

FBA_DATA27

FBA_DATA28

FBA_DATA29

FBA_DATA30

FBA_DATA31

FBA_ADR0

FBA_ADR1

FBA_ADR2

FBA_ADR3

FBA_ADR4

FBA_ADR5

FBA_ADR6

FBA_ADR7

FBA_ADR8

FBA_ADR9

FBA_ADR10

FBA_ADR11

FBA_ADR12

FBA_ADR13

FBA_DQM0

FBA_DQM1

FBA_DQM2

FBA_DQM3

FBA_DQS0

FBA_DQS1

FBA_DQS2

FBA_DQS3

FBA_RAS_

FBA_CAS_

FBA_WE_

FBA_CS0_

FBA_CS1_

FBA_CLK0

FBA_CLK0_

FBA_CLK1

FBA_CLK1_

FBA_CKE

AK27

AM31

AL29

AK28

AL30

AK29

AJ28

AM32

AL31

AK30

AN34

AM33

AK31

AJ30

AM34

AL33

AD29

AE32

AE33

AD30

AD33

AC31

AC32

AC33

AB31

AB30

AB32

AB33

AA31

Y31

Y33

Y32

AJ31

AJ32

AH30

AJ33

AH32

AF29

AH33

AF32

AG33

AF31

AE29

AF33

AE30

AE31

AP34

AL32

AD31

AA33

AG29

AH29

AA29

Y29

AG30

AK34

AH31

AK33

AL34

AB29

AC29

AJ27

AJ26

AG31

FBA_DATA0

FBA_DATA1

FBA_DATA2

FBA_DATA3

FBA_DATA4

FBA_DATA5

FBA_DATA6

FBA_DATA7

FBA_DATA8

FBA_DATA9

FBA_DATA10

FBA_DATA11

FBA_DATA12

FBA_DATA13

FBA_DATA14

FBA_DATA15

FBA_DATA16

FBA_DATA17

FBA_DATA18

FBA_DATA19

FBA_DATA20

FBA_DATA21

FBA_DATA22

FBA_DATA23

FBA_DATA24

FBA_DATA25

FBA_DATA26

FBA_DATA27

FBA_DATA28

FBA_DATA29

FBA_DATA30

FBA_DATA31

FBA_ADR0

FBA_ADR1

FBA_ADR2

FBA_ADR3

FBA_ADR4

FBA_ADR5

FBA_ADR6

FBA_ADR7

FBA_ADR8

FBA_ADR9

FBA_ADR10

FBA_ADR11

FBA_ADR12

FBA_ADR13

FBA_DQM0

FBA_DQM1

FBA_DQM2

FBA_DQM3

FBA_DQS0

FBA_DQS1

FBA_DQS2

FBA_DQS3

FBA_RAS_

FBA_CAS_

FBA_WE_

FBA_CS0_

FBA_CS1_

FBA_CLK0

FBA_CLK0B

FBA_CLK1

FBA_CKE

FBA_DQS[3:0] 5

FBB_DQS[3:0] 6

FBC_DQS[3:0] 7

FBD_DQS[3:0] 8

FBA_DQM[3:0] 5

FBB_DQM[3:0] 6

FBC_DQM[3:0] 7

FBD_DQM[3:0] 8

FBA_RAS_ 5

FBA_CAS_ 5

FBA_WE_ 5

FBA_CS0_ 5

FBA_CLK0

FBA_CLK0B

FBA_CLK1 5

FBA_CLK1B 5

FBA_CKE 5

FBB_RAS_ 6

FBB_CAS_ 6

FBB_WE_ 6

FBB_CS0_ 6

FBB_CLK0

FBB_CLK0B

FBB_CLK1 6

FBB_CLK1B 6

FBB_CKE 6

FBC_RAS_ 7

FBC_CAS_ 7

FBC_WE_ 7

FBC_CS0_ 7

FBC_CLK0

FBC_CLK0B

FBC_CLK1 7

FBC_CLK1B 7

FBC_CKE 7

FBD_RAS_ 8

FBD_CAS_ 8

FBD_WE_ 8

FBD_CS0_ 8

FBD_CLK0

FBD_CLK0B

FBD_CLK1 8

FBD_CLK1B 8

FBD_CKE 8

1 1

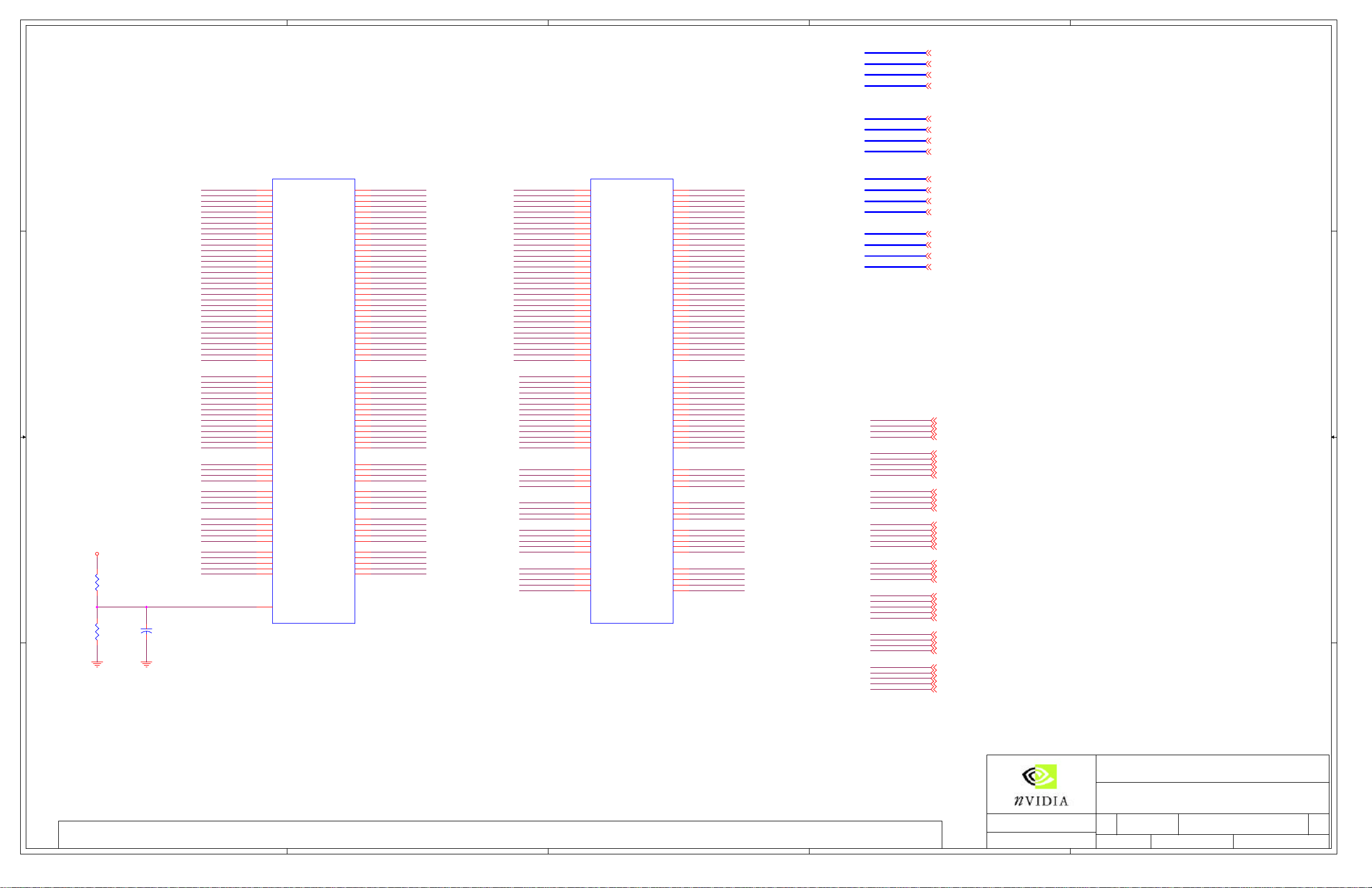

2.1 NV FBA/B/C/D

NVIDIA Corporation

2701 San Tomas Expressway

Santa Clara, CA 95050, USA

P138 L/K Module

Size

"ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO

WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE."

A

B

C

CAGE Code

Custom

D

Thursday, October 24, 2002

Scale

DWG NO

Sheet

E

4 16

Rev

of

Page 5

5

D D

4

3

2

1

B2

VDDQ

B4

VDDQ

B6

VDDQ

B7

VDDQ

B9

VDDQ

A1

DQS0

A6

DQ0

B5

DQ1

A5

DQ2

A4

DQ3

B1

DQ4

C2

DQ5

C1

DQ6

D1

DQ7

J12

DQ8

J11

DQ9

H12

DQ10

H11

DQ11

F12

DQ12

F11

DQ13

E12

DQ14

E11

DQ15

G12

DQS1

M12

VREF

M2

NC

B3

NC

B10

NC

G3

NC

G10

NC

K11

NC

K12

NC

L2

NC

L3

NC

MEM 4MX32 DDR-3.3

64BIT:128BIT

FBA_ADR[13:0]

U804A

VDD

VDD

VDD

A0

A1

A2

A3

A4

A5

A6

A7

A8(AP)

A9

A10

A11

BA0

BA1

CS

RAS

CAS

DQM0

DQM1

WE

CLK#

CLK

CKE

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

FBA_DATA[31:0]

FBVDD

C6

C7

D3

FBA_ADR0

M4

FBA_ADR1

M5

FBA_ADR2

L5

FBA_ADR3

M6

FBA_ADR4

M7

FBA_ADR5

L8

FBA_ADR6

M8

FBA_ADR7

M9

FBA_ADR8

M10

FBA_ADR9

L7

FBA_ADR10

K5

FBA_ADR11

L6

FBA_ADR12

M3

FBA_ADR13

L4

FBA_CS0_

M1

FBA_RAS_

L1

FBA_CAS_

K1

FBA_DQM2

A2

FBA_DQM0

G11

FBA_WE_

K2

FBA_CLK1B

L11

FBA_CLK1

L10

FBA_CKE

M11

D6

D7

D9

A3

A10

C3

C4

C5

GND

R889

100R

COMMON

Part A, Top side memory

5%

SMD0603

1 2

FBVDD

B11

D2

D11

E3

FBA_DQS3

FBA_DATA26

FBA_DATA30

FBA_DATA28

FBA_DATA31

FBA_DATA25

FBA_DATA27

FBA_DATA29

FBA_DATA24

FBA_DATA15

FBA_DATA14

FBA_DATA10

FBA_DATA11

FBA_DATA8

FBA_DATA9

FBA_DATA12

FBA_DATA13

FBA_DQS1

E10

G1

E2

E1

F2

F1

H2

H1

D12

C12

C11

B12

A9

A8

B8

A7

A12

L9

K8

L12

F9

G4

G9

H4

H9

G5

G6

G7

G8

H5

H6

H7

H8

GND GND

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

DQS2

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

J1

DQ22

J2

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQS3

RFU

RFU

MCL

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

J4

VSSQ

J9

VSSQ

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

MEM 4MX32 DDR-3.3

64BIT:128BIT

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

DQM2

DQM3

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

U804B

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

FBVDD

D10

K3

K6

K7

K10

FBVDD

F3

F10

H3

H10

J3

J10

FBA_DQM3

G2

FBA_DQM1

A11

J5

J6

J7

J8

K4

K9

D4

C8

C9

C10

D5

D8

E4

E9

F4

E5

E6

E7

E8

F5

F6

F7

F8

FBA_DATA[31:0] 4

FBA_DQS[3:0] 4

FBA_DQM[3:0] 4

FBA_RAS_ 4

FBA_CAS_ 4

FBA_WE_ 4

FBA_CS0_ 4

FBA_CLK0 4

FBA_CLK0B 4

FBA_CLK1 4

FBA_CLK1B 4

FBA_CKE 4

FBA_ADR[13:0]4

FBVDD

FBA_DQS2

FBA_DATA17

FBA_DATA16

FBA_DATA21

FBA_DATA19

FBA_DATA23

FBA_DATA22

FBA_DATA20

FBA_DATA18

FBA_DATA2

FBA_DATA7

FBA_DATA1

FBA_DATA4

FBA_DATA6

FBA_DATA0

FBA_DATA3

FBA_DATA5

FBA_DQS0

C C

FBVDD

GND

R425

1 2

1K

COMMON

R427

1 2

1K

COMMON

MVREFA0

1%

1%

MVREFA0

12

GND

C1020

0.1UF

SMD0402

COMMON

X7R

10%10V

B B

A A

2.2 FBA DDR 4MX32 SDRAM

NVIDIA Corporation

2701 San Tomas Expressway

Santa Clara, CA 95050, USA

P138 L/K Module

Size

"ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO

WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE."

5

4

3

CAGE Code

D

2

Thursday, October 24, 2002

Scale

DWG NO

Sheet

1

5 16

of

Rev

Page 6

5

D D

FBB_DQS1

FBB_DATA14

FBB_DATA12

FBB_DATA13

FBB_DATA11

FBB_DATA8

FBB_DATA9

FBB_DATA10

FBB_DATA15

FBB_DATA18

FBB_DATA19

FBB_DATA16

FBB_DATA17

FBB_DATA20

FBB_DATA21

FBB_DATA23

FBB_DATA22

FBB_DQS2

MVREFB0

12

C C

FBVDD

R426 1K

1%

1 2

COMMON

R428 1K

1%

1 2

COMMON

GND

MVREFB0

GND

C1045

0.1UF

COMMON

FBVDD

10%

4

B2

VDDQ

B4

VDDQ

B6

VDDQ

B7

VDDQ

B9

VDDQ

A1

DQS0

A6

DQ0

B5

DQ1

A5

DQ2

A4

DQ3

B1

DQ4

C2

DQ5

C1

DQ6

D1

DQ7

J12

DQ8

J11

DQ9

H12

DQ10

H11

DQ11

F12

DQ12

F11

DQ13

E12

DQ14

E11

DQ15

G12

DQS1

M12

VREF

M2

NC

B3

NC

B10

NC

G3

NC

G10

NC

K11

NC

K12

NC

L2

NC

L3

NC

MEM 4MX32 DDR-3.3

128BIT

U805A

A8(AP)

DQM0

DQM1

CLK#

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

3

FBVDD

C6

VDD

C7

VDD

D3

VDD

FBB_ADR0

M4

A0

FBB_ADR1

M5

A1

FBB_ADR2

L5

A2

FBB_ADR3

M6

A3

FBB_ADR4

M7

A4

FBB_ADR5

L8

A5

FBB_ADR6

M8

A6

FBB_ADR7

M9

A7

FBB_ADR8

M10

FBB_ADR9

L7

A9

FBB_ADR10

K5

A10

FBB_ADR11

L6

A11

FBB_ADR12

M3

BA0

FBB_ADR13

L4

BA1

CS

RAS

CAS

WE

CLK

CKE

VSS

VSS

VSS

FBB_CS0_

M1

FBB_RAS_

L1

FBB_CAS_

K1

FBB_DQM1

A2

FBB_DQM2

G11

FBB_WE_

K2

FBB_CLK1B

L11

FBB_CLK1

L10

FBB_CKE

M11

D6

D7

D9

A3

A10

C3

C4

C5

GND

R899

100R

5%

COMMON

SMD0603

1 2

FBVDD

B11

D2

D11

E10

FBB_DQS0

FBB_DATA4

FBB_DATA5

FBB_DATA1

FBB_DATA6

FBB_DATA2

FBB_DATA7

FBB_DATA3

FBB_DATA0

FBB_DATA27

FBB_DATA31

FBB_DATA30

FBB_DATA24

FBB_DATA28

FBB_DATA29

FBB_DATA26

FBB_DATA25

FBB_DQS3

G1

H2

H1

D12

C12

C11

B12

A12

L12

G4

G9

H4

H9

G5

G6

G7

G8

H5

H6

H7

H8

GND GND

VDDQ

VDDQ

VDDQ

E3

VDDQ

VDDQ

DQS2

E2

DQ16

E1

DQ17

F2

DQ18

F1

DQ19

DQ20

DQ21

J1

DQ22

J2

DQ23

DQ24

DQ25

DQ26

DQ27

A9

DQ28

A8

DQ29

B8

DQ30

A7

DQ31

DQS3

L9

RFU

K8

RFU

MCL

F9

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

J4

VSSQ

J9

VSSQ

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

MEM 4MX32 DDR-3.3

128BIT

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

DQM2

DQM3

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

U805B

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

FBVDD

D10

K3

K6

K7

K10

FBVDD

F3

F10

H3

H10

J3

J10

FBB_DQM0

G2

FBB_DQM3

A11

J5

J6

J7

J8

K4

K9

D4

C8

C9

C10

D5

D8

E4

E9

F4

E5

E6

E7

E8

F5

F6

F7

F8

2

FBB_DATA[31:0] 4

FBB_ADR[13:0] 4

FBB_DQS[3:0] 4

FBB_DQM[3:0] 4

FBB_RAS_ 4

FBB_CAS_ 4

FBB_WE_ 4

FBB_CS0_ 4

FBB_CLK0 4

FBB_CLK0B 4

FBB_CLK1 4

FBB_CLK1B 4

FBB_CKE 4

1

B B

A A

2.3 FBB DDR 4MX32 SDRAM

NVIDIA Corporation

2701 San Tomas Expressway

Santa Clara, CA 95050, USA

P138 L/K Module

Size

"ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO

WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE."

5

4

CAGE Code

D

3

2

Thursday, October 24, 2002

Scale

DWG NO

Sheet

1

6 16

of

Rev

Page 7

A

4 4

COMMON

C865

0.1UF

10%

X7R

10V

MVREFC0

3 3

FBVDD

R453

1 2

1K COMMON1%

R455

1 2

1K COMMON1%

GND

MVREFC0

FBC_DQS2

FBC_DATA17

FBC_DATA18

FBC_DATA16

FBC_DATA19

FBC_DATA23

FBC_DATA20

FBC_DATA21

FBC_DATA22

FBC_DATA1

FBC_DATA3

FBC_DATA2

FBC_DATA6

FBC_DATA0

FBC_DATA4

FBC_DATA7

FBC_DATA5

FBC_DQS0

12

GND

FBVDD

B

B2

B4

B6

B7

B9

A1

A6

B5

A5

A4

B1

C2

C1

D1

J12

J11

H12

H11

F12

F11

E12

E11

G12

M12

M2

B3

B10

G3

G10

K11

K12

L2

L3

U802A

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

DQS0

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

A8(AP)

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQS1

DQM0

DQM1

VREF

NC

NC

NC

NC

VSSQ

NC

VSSQ

NC

VSSQ

NC

VSSQ

NC

VSSQ

NC

MEM 4MX32 DDR-3.3

64BIT:128BIT

CLK#

C

FBVDD

C6

VDD

C7

VDD

D3

VDD

FBC_ADR0

M4

A0

FBC_ADR1

M5

A1

FBC_ADR2

L5

A2

FBC_ADR3

M6

A3

FBC_ADR4

M7

A4

FBC_ADR5

L8

A5

FBC_ADR6

M8

A6

FBC_ADR7

M9

A7

FBC_ADR8

M10

FBC_ADR9

L7

A9

FBC_ADR10

K5

A10

FBC_ADR11

L6

A11

FBC_ADR12

M3

BA0

FBC_ADR13

L4

BA1

FBC_CS0_

M1

CS

FBC_RAS_

L1

RAS

FBC_CAS_

K1

CAS

FBC_DQM2

A2

FBC_DQM0

G11

FBC_WE_

K2

WE

FBC_CLK1B

L11

FBC_CLK1

L10

CLK

FBC_CKE

M11

CKE

D6

VSS

D7

VSS

D9

VSS

A3

A10

C3

C4

C5

GND

R906

100R

5%

COMMON

SMD0603

1 2

FBVDD

B11

D11

E10

FBC_DQS3

FBC_DATA29

FBC_DATA26

FBC_DATA31

FBC_DATA30

FBC_DATA28

FBC_DATA25

FBC_DATA24

FBC_DATA27

FBC_DATA9

FBC_DATA8

FBC_DATA13

FBC_DATA12

FBC_DATA10

FBC_DATA15

FBC_DATA14

FBC_DATA11

FBC_DQS1

D12

C12

C11

B12

A12

L12

GND GND

VDDQ

D2

VDDQ

VDDQ

E3

VDDQ

VDDQ

G1

DQS2

E2

DQ16

E1

DQ17

F2

DQ18

F1

DQ19

H2

DQ20

H1

DQ21

J1

DQ22

J2

DQ23

DQ24

DQ25

DQ26

DQ27

A9

DQ28

A8

DQ29

B8

DQ30

A7

DQ31

DQS3

L9

RFU

K8

RFU

MCL

F9

VSSQ

G4

VSSQ

G9

VSSQ

H4

VSSQ

H9

VSSQ

J4

VSSQ

J9

VSSQ

G5

VSS-TH

G6

VSS-TH

G7

VSS-TH

G8

VSS-TH

H5

VSS-TH

H6

VSS-TH

H7

VSS-TH

H8

VSS-TH

MEM 4MX32 DDR-3.3

64BIT:128BIT

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

DQM2

DQM3

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

U802B

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

FBVDD

D10

K3

K6

K7

K10

FBVDD

F3

F10

H3

H10

J3

J10

FBC_DQM3

G2

FBC_DQM1

A11

J5

J6

J7

J8

K4

K9

D4

C8

C9

C10

D5

D8

E4

E9

F4

E5

E6

E7

E8

F5

F6

F7

F8

D

FBC_DATA[31:0] 4

FBC_ADR[13:0] 4

FBC_DQS[3:0] 4

FBC_DQM[3:0] 4

FBC_RAS_ 4

FBC_CAS_ 4

FBC_WE_ 4

FBC_CS0_ 4

FBC_CLK0 4

FBC_CLK0B 4

FBC_CLK1 4

FBC_CLK1B 4

FBC_CKE 4

E

2 2

1 1

2.4 FBC DDR 4MX32 SDRAM

NVIDIA Corporation

2701 San Tomas Expressway

Santa Clara, CA 95050, USA

P138 L/K Module

Size

"ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO

WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE."

A

B

CAGE Code

D

C

D

Thursday, October 24, 2002

Scale

DWG NO

Sheet

E

7 16

of

Rev

Page 8

A

4 4

B

C

D

E

FBVDD FBVDD

B2

VDDQ

B4

VDDQ

B6

VDDQ

B7

VDDQ

B9

VDDQ

A1

DQS0

A6

DQ0

B5

DQ1

A5

DQ2

A4

DQ3

B1

DQ4

C2

DQ5

C1

DQ6

D1

DQ7

J12

DQ8

J11

DQ9

H12

DQ10

H11

DQ11

F12

DQ12

F11

DQ13

E12

DQ14

E11

DQ15

G12

DQS1

M12

VREF

M2

NC

B3

NC

B10

NC

G3

NC

G10

NC

K11

NC

K12

NC

L2

NC

L3

NC

MEM 4MX32 DDR-3.3

128BIT

IC_BGA144_DDR

U803A

A8(AP)

DQM0

DQM1

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

CLK#

C6

VDD

C7

VDD

D3

VDD

FBD_ADR0

M4

A0

FBD_ADR1

M5

A1

FBD_ADR2

L5

A2

FBD_ADR3

M6

A3

FBD_ADR4

M7

A4

FBD_ADR5

L8

A5

FBD_ADR6

M8

A6

FBD_ADR7

M9

A7

FBD_ADR8

M10

FBD_ADR9

L7

A9

FBD_ADR10

K5

A10

FBD_ADR11

L6

A11

FBD_ADR12

M3

BA0

FBD_ADR13

L4

BA1

FBD_CS0_

M1

CS

FBD_RAS_

L1

RAS

FBD_CAS_

K1

CAS

FBD_DQM1

A2

FBD_DQM3

G11

FBD_WE_

K2

WE

FBD_CLK1B

L11

FBD_CLK1

L10

CLK

FBD_CKE

M11

CKE

D6

VSS

D7

VSS

D9

VSS

A3

A10

C3

C4

C5

GND

1 2

R913

100R

COMMON

SMD0603

5%

FBVDD

FBD_DQS1

FBD_DATA15

FBD_DATA13

FBD_DATA14

FBD_DATA12

FBD_DATA10

FBD_DATA9

FBD_DATA8

FBD_DATA11

FBD_DATA24

FBD_DATA28

FBD_DATA29

FBD_DATA31

FBD_DATA30

FBD_DATA26

FBD_DATA27

FBD_DATA25

SMD0402

10%

10V

X7R

FBD_DQS3

MVREFD0

12

GND

C873

0.1UF

COMMON

3 3

COMMON

COMMON

MVREFD0

1%

1%

FBVDD

GND

R454 1K

1 2

SMD0402

R456 1K

1 2

SMD0402

FBVDD

B11

D2

D11

E3

E10

FBD_DQS0

FBD_DATA4

FBD_DATA6

FBD_DATA1

FBD_DATA5

FBD_DATA7

FBD_DATA2

FBD_DATA0

FBD_DATA3

FBD_DATA16

FBD_DATA18

FBD_DATA19

FBD_DATA23

FBD_DATA21

FBD_DATA20

FBD_DATA22

FBD_DATA17

FBD_DQS2

G1

E2

E1

F2

F1

H2

H1

D12

C12

C11

B12

A9

A8

B8

A7

A12

L9

K8

L12

F9

G4

G9

H4

H9

G5

G6

G7

G8

H5

H6

H7

H8

GND GND

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

DQS2

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

J1

DQ22

J2

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQS3

RFU

RFU

MCL

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

J4

VSSQ

J9

VSSQ

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

MEM 4MX32 DDR-3.3

128BIT

IC_BGA144_DDR

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

DQM2

DQM3

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

VSS-TH

U803B

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D10

K3

K6

K7

K10

FBVDD

F3

F10

H3

H10

J3

J10

FBD_DQM0

G2

FBD_DQM2

A11

J5

J6

J7

J8

K4

K9

D4

C8

C9

C10

D5

D8

E4

E9

F4

E5

E6

E7

E8

F5

F6

F7

F8

FBD_DATA[31:0] 4

FBD_ADR[13:0] 4

FBD_DQS[3:0] 4

FBD_DQM[3:0] 4

FBD_RAS_ 4

FBD_CAS_ 4

FBD_WE_ 4

FBD_CS0_ 4

FBD_CLK0 4

FBD_CLK0B 4

FBD_CLK1 4

FBD_CLK1B 4

FBD_CKE 4

2 2

1 1

2.5 FBD DDR 4MX32 SDRAM

NVIDIA Corporation

2701 San Tomas Expressway

Santa Clara, CA 95050, USA

P138 L/K Module

Size

"ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO

WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE."

A

B

CAGE Code

D

C

D

Thursday, October 24, 2002

Scale

DWG NO

Sheet

E

8 16

of

Rev

Page 9

A

B

C

D

E

FBVDD

12

4 4

3 3

2 2

C1133

470pF

XRAMCAP

SMD0402

GND GND

FBVDD

12

FBVDD

12

GND GND

FBVDD

12

FBVDD

12

GND GND

FBVDD

12

GND

FBVDD

12

GND

FBVDD

12

GND

C452

2200PF

XRAMCAP

SMD0402

C445

0.01uF

COMMON

SMD0402

C456

2200PF

XRAMCAP

SMD0402

C1150

0.01uF

XRAMCAP

SMD0402

C408

2200PF

COMMON

SMD0402

C850

0.01uF

COMMON

SMD0402

C856

2200PF

XRAMCAP

SMD0402

12

12

12

12

12

C449

0.022UF

COMMON

SMD0402

C443

0.022UF

XRAMCAP

SMD0402

C491

2200PF

COMMON

SMD0402

C849

0.1UF

COMMON

SMD0402

C454

0.1UF

XRAMCAP

SMD0402

12

12

C1141

0.022UF

XRAMCAP

SMD0402

C473

0.1UF

COMMON

SMD0402

12

C1142

470pF

XRAMCAP

SMD0402

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

C1007

470pF

XRAMCAP

SMD0402

C1006

2200PF

XRAMCAP

SMD0402

C1043

470pF

XRAMCAP

SMD0402

C1031

2200PF

COMMON

SMD0402

C988

470pF

COMMON

SMD0402

C994

2200PF

XRAMCAP

SMD0402

C867

470pF

XRAMCAP

SMD0402

C858

2200PF

COMMON

SMD0402

12

12

12

12

12

12

12

12

C1009

470pF

XRAMCAP

SMD0402

C1008

2200PF

COMMON

SMD0402

C1041

470pF

XRAMCAP

SMD0402

C1033

2200PF

XRAMCAP

SMD0402

C985

470pF

COMMON

SMD0402

C987

2200PF

XRAMCAP

SMD0402

C859

470pF

XRAMCAP

SMD0402

C860

2200PF

COMMON

SMD0402

12

12

12

12

12

12

12

12

C1012

470pF

XRAMCAP

SMD0402

C1010

2200PF

XRAMCAP

SMD0402

C1034

470pF

COMMON

SMD0402

C1038

2200PF

XRAMCAP

SMD0402

C986

470pF

COMMON

SMD0402

C992

2200PF

XRAMCAP

SMD0402

C861

470pF

COMMON

SMD0402

C862

2200PF

COMMON

SMD0402

12

12

12

12

12

12

C1146

470pF

XRAMCAP

SMD0402

12

C1014

470pF

COMMON

SMD0402

C1011

2200PF

COMMON

SMD0402

C1035

470pF

XRAMCAP

SMD0402

C1042

2200PF

XRAMCAP

SMD0402

C413

0.01uF

COMMON

SMD0402

C1147

2200PF

XRAMCAP

SMD0402

12

12

12

12

12

12

12

GNDGND

12

12

GNDGND

12

12

GND

12

GND

12

GND

C1015

470pF

COMMON

SMD0402

C1019

2200PF

XRAMCAP

SMD0402

C1143

0.1UF

XRAMCAP

SMD0402

C1044

2200PF

XRAMCAP

SMD0402

C871

0.1UF

COMMON

SMD0402

12

12

C1016

470pF

COMMON

SMD0402

C1017

2200PF

XRAMCAP

SMD0402

12

C1013

2200PF

XRAMCAP

SMD0402

12

C1313

0.1UF

16V X7R

SMD0603

XRAMCAP

C1315

12

2200PF

10%

20%

50V X7R

SMD0603

XRAMCAP

12

C1320

0.1UF

16V X7R

SMD0603

XRAMCAP

C1323

12

470pF

10%

10V X7R

SMD0603

XRAMCAP

C1324

12

20%

2200PF

20%

50V X7R

SMD0603

XRAMCAP

12

C1325

0.01UF

10%

50V X7R

SMD0603

XRAMCAP

FBVDD

12

C1005

0.01uF

XRAMCAP

SMD0402

GND

1 1

12

C979

4.7UF

XRAMCAP

SMD0805

GND GND GND GND

12

C1004

0.01uF

XRAMCAP

SMD0402

FBVDD FBVDDFBVDDFBVDD

12

C1029

0.01uF

XRAMCAP

SMD0402

12

C1435

0.01uF

X5R

6.3V

SMD0402

XRAMCAP

10%

2.6 BGA MEMORY DECOUPLING

NVIDIA Corporation

2701 San Tomas Expressway

Santa Clara, CA 95050, USA

P138 L/K Module

Size

"ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO

WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE."

A

B

C

CAGE Code

D

D

Wednesday, October 23, 2002

Scale

DWG NO

Sheet

E

9 16

of

Rev

Page 10

A

R91

GPU_XTALIN

ICS_XTALIN

4 4

22R

1 2

SMD0402

COMMON

R92

22R

1 2

SMD0402

COMMON

B

Y1

43

VCCOUT

21

GNDE/D

OSC_27.000MHz_10PPM

OSC_SMD_5X7MM

COMMON

A3.3V

12

R93

10R

SMD0603

COMMON

GND GND

12

C33

0.047uF

SMD0402

COMMON

12

R601

10K

SMD0402

COMMON

5%

C

3VRUN3VRUN

12

R602

10K

SMD0402

COMMON

5%

D

E

U8

1 8

XIN/CLKIN PD#

3

GND

4

CLKOUT

ICS91720

COMMON

CFOUT

R605 22R

DAC_VDD

5%

50VNPO

GND

C1115

12

0.01UF

10%

50VX7R

SMD0603

COMMON

GND

5%

50VNPO

SCLKVDD

SDATA

REFOUT

32 mA max power supply current

1 2

C210

12

0.01UF

SMD0603

COMMON

GND GND

R1115 0R

DAC2_VDD

DAC2_VREF

DAC2_RSET

12

R927

102R

SMD0603

COMMON

GND

R1116 0R

A3.3V

12

L200

150-220R_100MHZ

SMD0603

COMMON

C206

12

0.022UF

SMD0603

COMMON

GND

C1112

12

150PF

SMD0603

COMMON

C208

12

0.022UF

SMD0603

COMMON

ICS_XTALIN

12

GND

10%

25VX7R

5%

50VNPO

10%

25VX7R

C701

470pF

COMMON

GND

C207

12

150PF

SMD0603

COMMON

C209

12

150PF

SMD0603

COMMON

GND

3VRUN

R185

12

4R7

COMMON

GND

GND

3 3

2 2

FBVDD

12

R200

2.2K

SMD0402

COMMON

Q208-B

1

Q208

MMBT2222A

IC_SOT23_123

COMMON

A3.3V

12

R1176

10K

SMD0402

COMMON

1 2

3

2

GND

Please route

using 12mil

trace.

R1178

220R

SMD0402

COMMON

C710

4.7uF

COMMON

Q207-BQ208-C

12

2

1

3

C712

0.1uF

COMMON

Q207

MMBT4403LT1

IC_SOT23_123

COMMON

PLL_VDD_IN

12

12

C713

0.1uF

COMMON

R1177

0R

SMD0603

NO_STUFF

CLK_VDD

Place C601 adjacent to U8 pin 2

A3.3V

12

L710

150-220R_100MHZ

SMD0603

COMMON

C1111

12

0.022UF

10%

25VX7R

SMD0603

COMMON

L809

1 2

150-220R_100MHZ

SMD0603

COMMON

GND

ICSPD

I2C2SCL

72

I2C2SDA

6

ICS_REFOUT

5

COMMON

Place this resistor

close to U8

DAC_VREF

DAC_RSET

12

10%

1 2

1 2

R207

105R

SMD0603

COMMON

12

50VX7R

1%

1%

5%

COMMONSMD0603

C1114

0.01UF

SMD0603

COMMON

5%

COMMONSMD0603

C205

12

0.01UF

SMD0603

COMMON

10%

50VX7R

GPU_XTALIN

SSFOUT

GND

10%

50VX7R

DAC_COMP

IDUMPA

DAC2_COMP

IDUMPB

PLL_VDD

I2C2SCL 11,12,14

I2C2SDA 11,12,14

12

Minimize stub to

R603

10K

this resistor from

SMD0402

SSFOUT

COMMON

5%

U100F

CRTHSYNC

CRTVSYNC

AN11

DACVDD

AK14

DACVREF

AJ12

DACRSET

AK13

DACCOMP

AJ14

DACGND

CRT2HSYNC/AGP_STOP

CRT2VSYNC/AGP_BUSY

AN9

DAC2VDD

AN10

DAC2VREF

AL10

DAC2RSET

AL11

DAC2COMP

AJ13

DAC2GND

AL13

PLLVDD

AP2 AJ5

XTALIN XTALOUT

IC_NV28_GPU_BGA816_P10_SKT

BGA816_P10_NV28

DACRED

DACGREEN

DACBLUE

I2C1SCL

I2C1SDA

DAC2RED

DAC2GREEN

DAC2BLUE

I2C0SCL

I2C0SDA

SSFOUT 11

HSYNC

AP1

VSYNC

AG5

AL12

AJ15

AM12

AE6

AN1

AL4

AM3

AJ11

AM10

AK11

AF6

AH4

C_I2C_SCL1

C_I2C_SDA1

AGP_STOP

AGP_BUSY

C_I2C_SCL0

RED

GREEN

BLUE

C_I2C_SDA0

Decoupling

sync

driver

5VRUN

147

U14B

3 4

TSSOP14

GND

5VRUN

147

U14D

9 8

TSSOP14

GND

R303

COMMON

R301

COMMON

R307

COMMON

R305

COMMON

5VRUN

12

GND

BHSYNC

1 2

1 2

1 2

1 2

C303

0.1uF

X7R

SMD0402

COMMON

33R

SMD0402

33R

SMD0402

10%

25V

33R

SMD0402

33R

SMD0402

5VRUN

147

U14A

1 2

TSSOP14

GND

BVSYNC

5%

5%

5%

5%

5VRUN

147

U14E

11 10

TSSOP14

GND

5VRUN

5VRUN

I2C1PDAT

I2C0PSCL

I2C0PDAT

HSYNCR

VSYNCR

5VRUN

5VRUN

I2C1PSCL

Q7

1

2

BSS138

SOT23

Q13

1

2

BSS138

SOT23

Q12

1

2

BSS138

SOT23

R132

COMMON

R134

COMMON

3

3

3

1 2

1 2

1

2

BSS138

SOT23

Q8

3

33R

SMD0402

33R

SMD0402

5%

5%

DVI_CLK

DVI_DAT

5VRUN

HSYNCQ

5VRUN

VSYNCQ

DDC_CLK

DDC_DAT

1

2

1

2

Q14

BSS138

SOT23

Q15

BSS138

SOT23

DAC_HSYNC

3

DAC_VSYNC

3

RED 2

GREEN 2

BLUE 2

DDC_CLK 2

DDC_DAT 2

AGP_STOP 2

AGP_BUSY 2

DVI_CLK 2

DVI_DAT 2

DAC_HSYNC 2

DAC_VSYNC 2

1 1

GND

3.1 NV DAC/PLL/I2C

NVIDIA Corporation

2701 San Tomas Expressway

Santa Clara, CA 95050, USA

P138 L/K Module

Size

"ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO

WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE."

A

B

C

CAGE Code

Custom

D

Thursday, October 24, 2002

Scale

DWG NO

Sheet

E

10 16

Rev

of

Page 11

A

B

C

D

E

NVVDD

GND

AA11

AA13

AA22

AA24

AA26

AA9

AB14

AB18

AB21

AD14

AE10

AF13

K10

K25

L14

L21

N14

N17

N21

P13

P11

P22

P24

P26

U13

V22

V26

H27

H29

G12

G15

G20

G23

G27

M28

AC28

A12

A15

A20

A23

A27

AA34

AD34

AH34

G34

L34

P34

T28

W28

AH8

AH12

AG8

AE25

AG27

AH27

G29

E32

F29

F34

G11

G19

G24

G28

G16

H28

H32

J13

J17

J22

P9

U9

H6

H8

G8

A8

M7

G1

L1

P1

P2

G6

E3

E9

F1

F6

G7

H3

H7

3VRUN3VRUN

12

12

R1105

2.2K

5%

R211 10R

5%

C1431

4.7UF

10%

X5R

6.3V

SMD0805

COMMON

SMD0603

COMMON

VIP_HAD0

VIP_HAD1

VIP_HAD2

VIP_HAD3

VIP_HAD4

VIP_HAD5

VIP_HAD6

VIP_HAD7

12

C1432

4.7UF

X5R

SMD0805

COMMON

1 2

10%

6.3V

4 4

DVODE12

DVOD[23:0]12,15

TMDS/VO

CH7009

3 3

2 2

5VRUN

12

C204

0.1UF

COMMON

SMD0603

GND

DVOHSYNC12

DVOVSYNC12

DVOCLK_IN12

DVOCLK_OUT12

BUFFRST_12

3VRUN 3VRUN

12

DVOD[23:0]

R1147

10K

5%

SMD0603

NO_STUFF

VIP_HAD[7:0]15

DVOD0

DVOD1

DVOD2

DVOD3

DVOD4

DVOD5

DVOD6

DVOD7

DVOD8

DVOD9

DVOD10

DVOD11

DVOD12

DVOD13

DVOD14

DVOD15

DVOD16

DVOD17

DVOD18

DVOD19

DVOD20

DVOD21

DVOD22

DVOD23

GND

I2C2SCL

ROM_CS_

R1148

10K

SMD0603

NO_STUFF

1 2

I2C2SCL10,12,14

I2C2SDA10,12,14

ROM_CS_15

PLACE THESE RESISTORS NEAR U100

3VRUN

12

R1106

2.2K

5%

SMD0603

COMMON

R1107 33R

1 2

R1108 33R

1 2

3VRUN

RDVOHSYNC

RDVOVSYNC

C_DVOCLK_OUT

5%

COMMONSMD0603

R1211

10K