Page 1

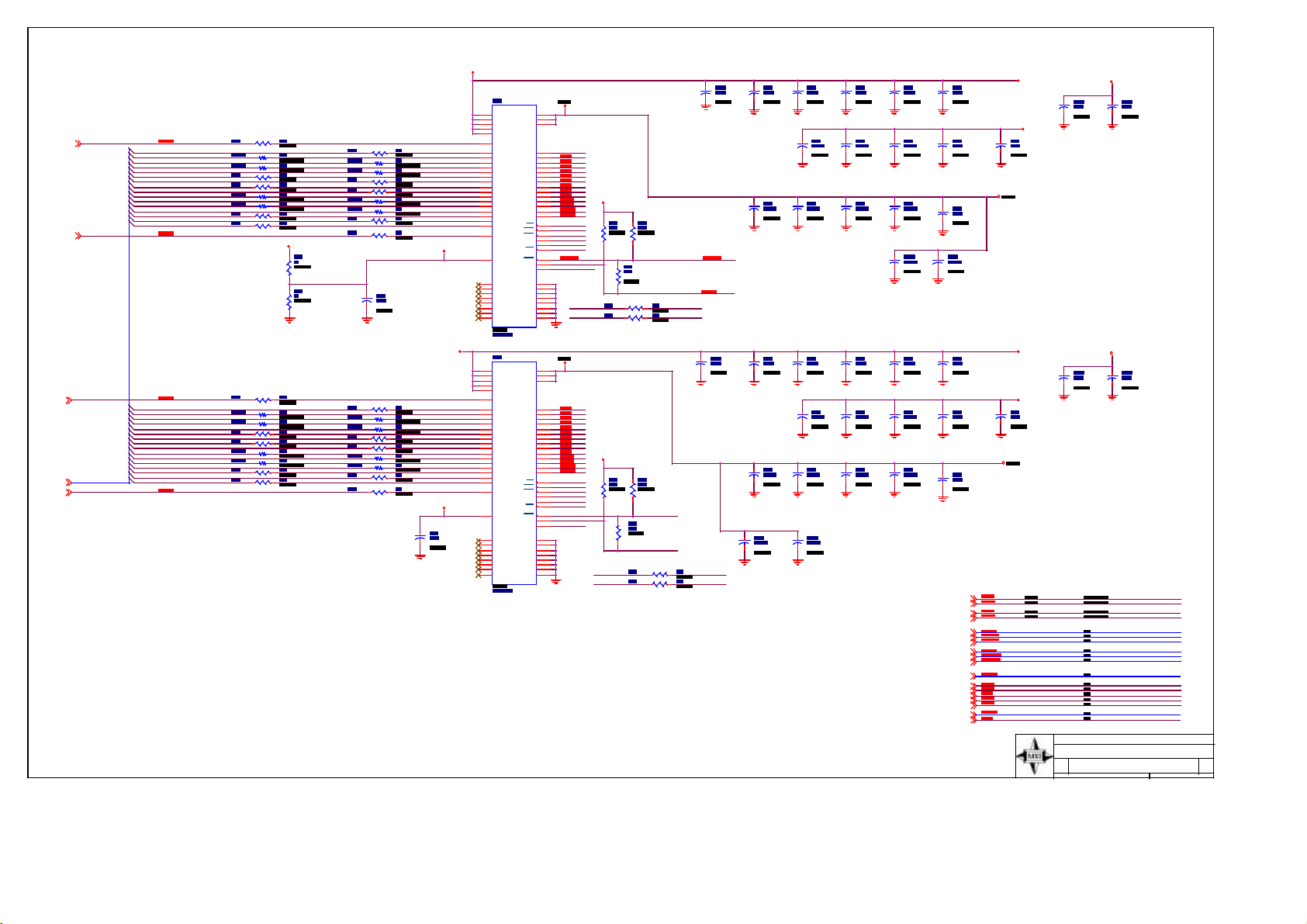

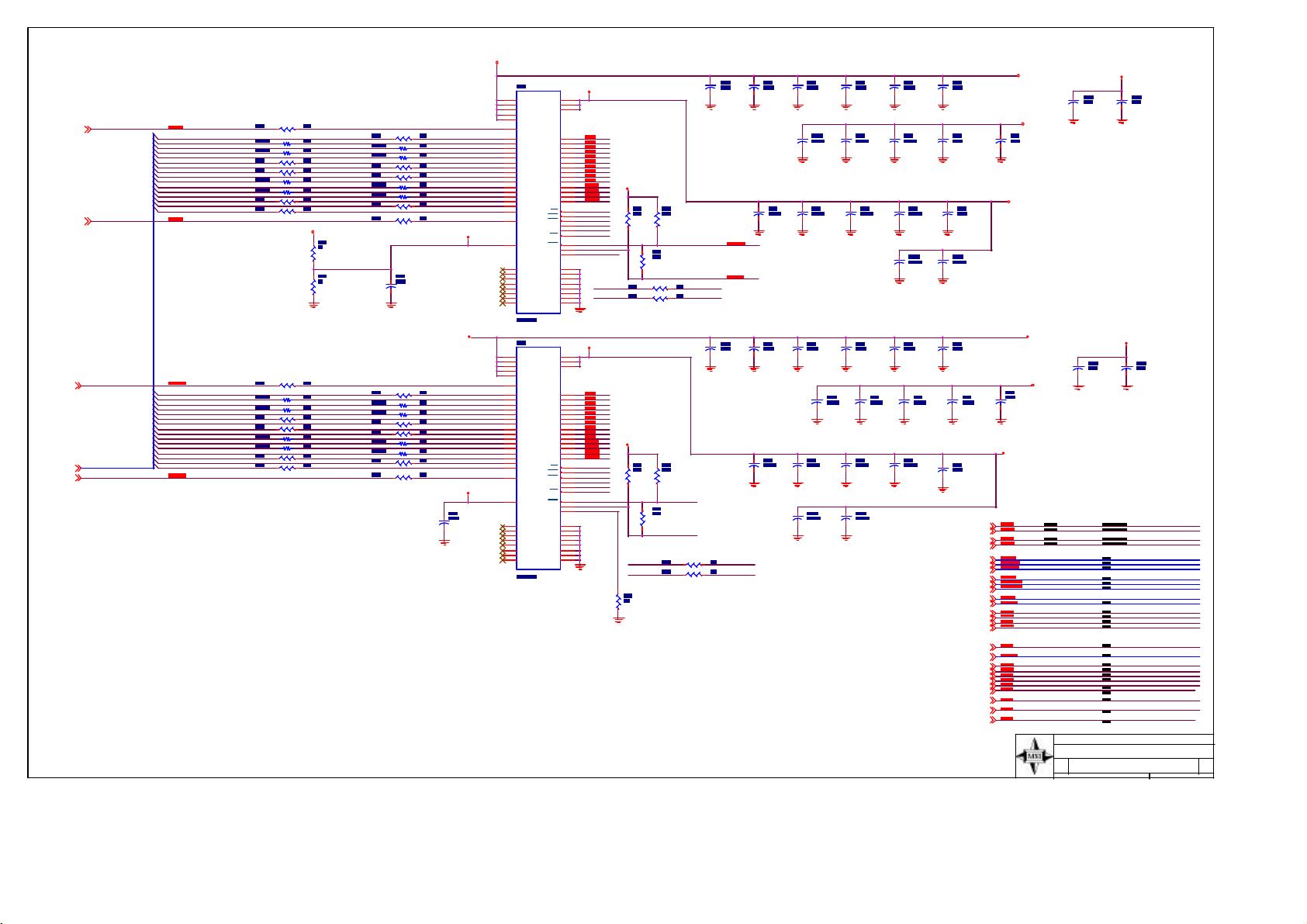

C116, NV18, 8MX16DDR, 128MB, Video IN/OUT, DVI-I, VGA

Page Overview

1 18P112 OVERVIEW

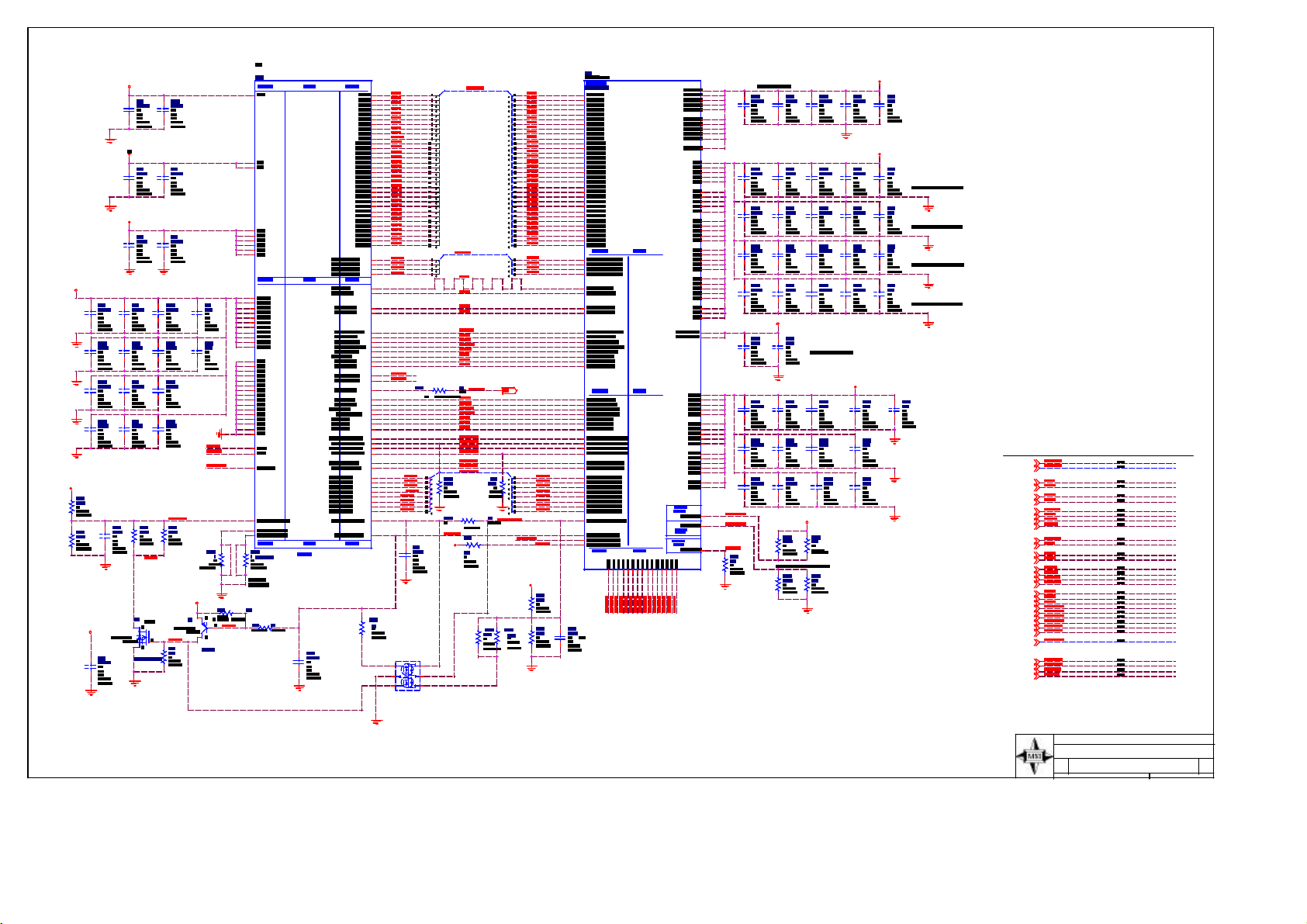

2 NV18 AGP Section and AGP connector

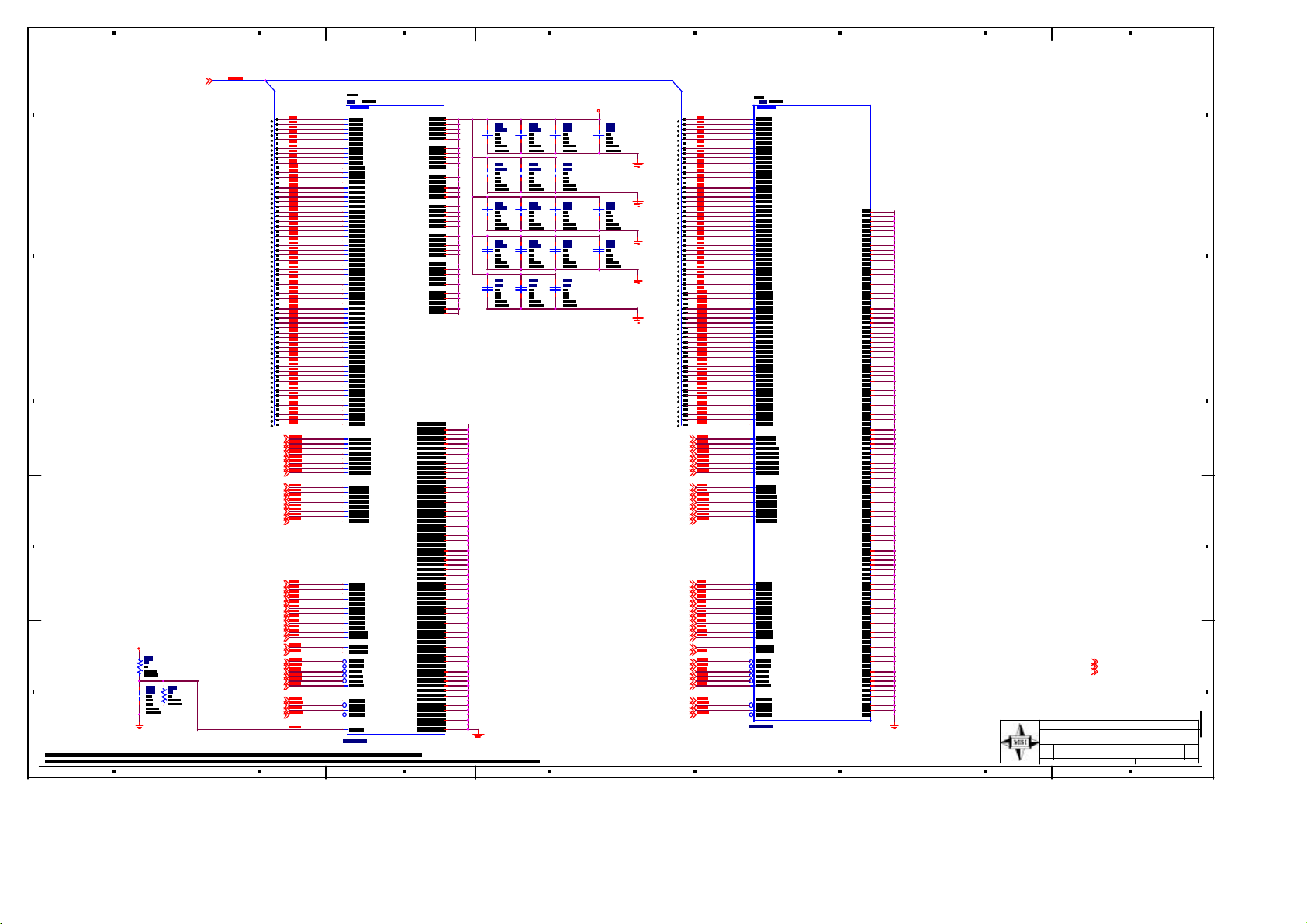

3 NV18 FRAMEBUFFER Interface

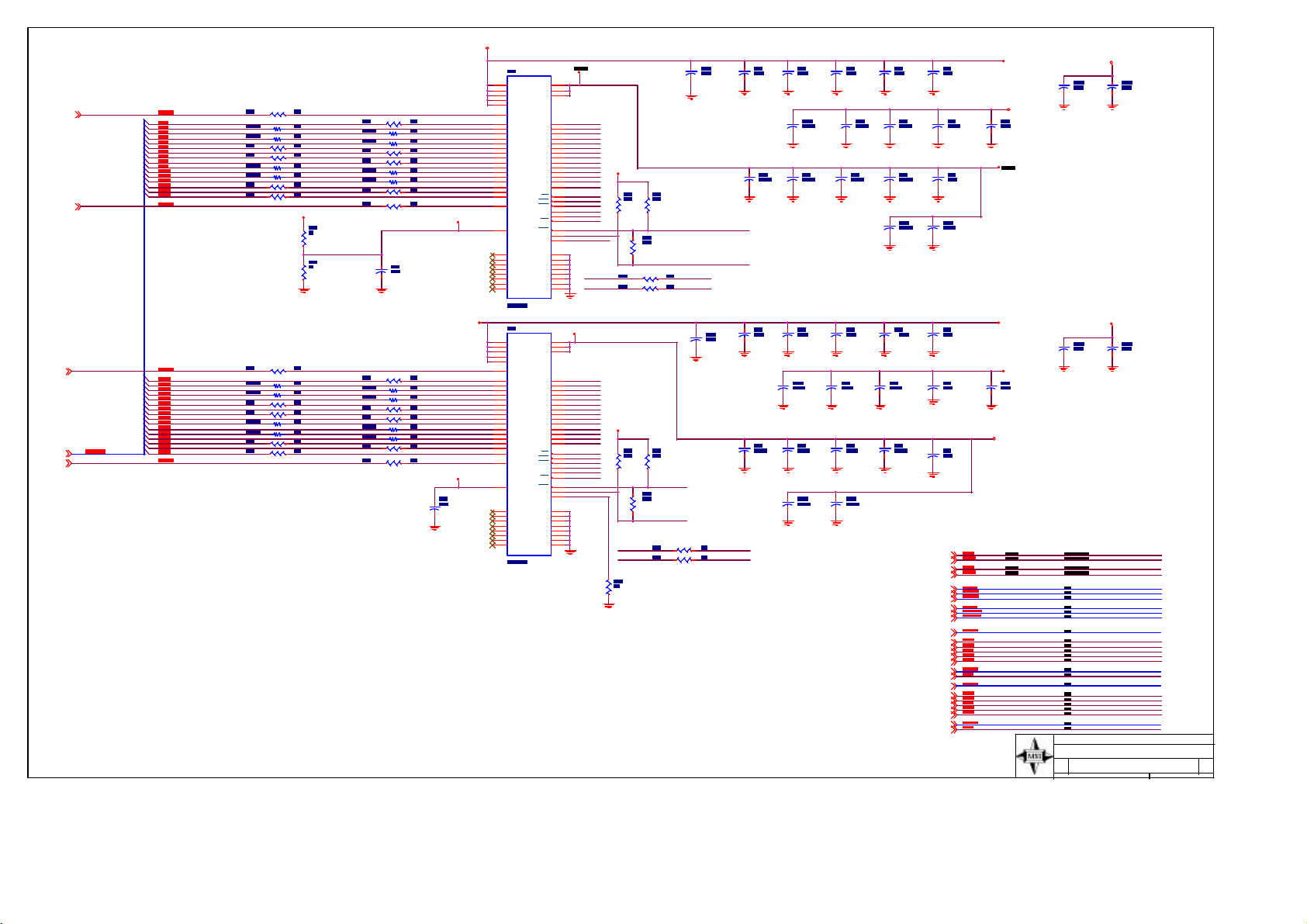

4 MEMORY 128MB, 8Mx16DDR Bits 0..31

5 MEMORY 128MB, 8Mx16DDR Bits 32..63

6 MEMORY 128MB, 8Mx16DDR Bits 64..95

7 MEMORY 128MB, 8Mx16DDR Bits 96..127

8 NV18 STRAPPING, I/O Interface

BIOS, FAN CONTROL, THERMAL SENSOR

9 NV18 DACA, DACB output, SYNC amplifier

PLL Section

10 DACB MULTIPLEXER

11 PRIMARY DISPLAY Filter and Connector

12 SECONDARY DISPLAY Filter and Connector

13 NV18 INTERNAL TMDS Power and Output

TMDS Backdrive circuit

14 PRIMARY DISPLAY DVI-I option

Hotplug detection and Connector

15 VIDEO CAPTURE Philips 7114 I/O

16 VIDEO IN/OUT, Filter and Connector

17 VIDEO INTERNAL Input

Filter and Connector

18 1394 TEXAS TSB41AB2, PowerRails,

I/O, Internal and external connector

19 POWER SUPPLY

NVVDD, MEM_VDD, A3V3, TMDS3V3, TMDSPLL

20 MECHANICS, and FBVDD

A00

HISTORY:

X00:

INITIAL VERSION

X01

Remove R117, C87, C131, C143 for CKE

Change C736, C743 to 18pf capacitors.

Remove C1099 - additional Capacitor for AGPVREFcg

Changed AGPVREFcg circuit.

C116 Base on P112 to Modify.

1. Change page 4~7 & page 18 Reference.

2. Change J1 foot print from silm type to stand D-SUB.

3. Remove I1394 function.

4.Page 2, change voltage C75.1 & Q2.E from 3V3 to A3V3.

5.Page 8, Add Twin Bios for MSI function.

6.Page 16 ,replace INTERNAL VIDEO CAPTURE CONNECTOR.

7.Page 17 ,ADD C874 & C1098 ALE CAP. (DUAL-LAY)

8.Page 18 , Add H/W Monitor founction for MSI .

9.Page 2 change Q508, Q509 footprint from SOT23 to SOT-6 U200 package.

00A change to version 100.

1. DACA and DACB signal swap.

600-10116-000X-A00

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

Date:

TOP PAGE

Tuesday, September 03, 2002

1 18

Sheet of

100

Page 2

NV18 AGP SECTION AND AGP CONNECTOR

AGPVDDQ

GND

GND

GND

GND

AGPVDDQ

12

12

12V

12

12

GND

12

12

GND

3V3

12

12

GND

GND

12

12

12

12

12

GND

3V3

12

GND

12

12

12

12

12

12

3

2

GND

12

12

12

12

12

12

3V3

2

3

1

12

GND

1 2

A1

B2

B3

B9

A9

B16

A16

B28

A28

B34

A34

B40

A40

B47

B52

A52

B58

A58

B64

A64

B5

A5

B13

A13

B19

A19

B31

A31

B37

A37

B49

A49

B55

A55

B61

A61

B4

A4

B1

A66

A2

A3

12

12

GND

1 2

1

12

GND

1 2

MBDET_G

GND

A65

B65

A63

B63

A62

B62

A60

B60

B57

A56

B56

A54

B54

A53

B53

A51

A39

B38

A38

B36

A36

B35

A35

B33

A30

B30

A29

B29

A27

B27

A26

B26

A57

B51

B39

A33

B7

A7

B8

A8

A41

B41

A46

B46

A47

A50

A6

B6

B48

B50

A48

AFRWR_PME

B12

A14

A12

B14

B10

A10

B11

B59

A59

B32

A32

B18

A18

B15

A15

B17

A17

B20

A20

B21

A21

B66

A11

IC_SUPERSOT-6

AGPVREFCG

12

GND

U200

1

2

3

FDC6301N

COMMON

1 2

12

GND

6

5

4

1 2

3V3

1 2

12

GND

AGPVDDQ

1 2

1 2

AJ28

AK28

AH27

AK27

AJ27

AH26

AJ26

AH25

AH23

AJ23

AH22

AJ22

AJ21

AK21

AH20

AJ20

AG26

AE24

AG25

AG24

AF24

AG23

AE22

AF22

AE21

AG20

AG19

AF19

AE19

AF18

AG18

AE18

AJ24

AH19

AF25

AG22

AE12

AF15

AF13

AE15

AK16

AG16

AJ17

AJ16

AH17

AK18

AG15

AF12

AG14

AG17

AJ18

AJ19

AG13

AE16

AE13

AK24

AJ25

AG21

AF21

AK13

AJ13

AJ11

AH11

AJ12

AH12

AJ14

AH14

AJ15

AH15

AK29

AF16

AA14

AA13

C1

A1

12

12

12

GND

C2D2E2E3F2F3F4G4G5

AE14

AE11

AE17

AE20

AE23

AD11

AD14

AD23

AD20

AG12

AE25

J7

M7

L20

Y20

L13

Y13

N20

P20

U20

V20

L11

N11

P11

U11

V11

Y11

L14

Y14

L17

Y17

L18

Y18

G19

G12

M24

W24

Y7

AB7

P6

AE9

AD17

AE10

G6

P7

U6

L6

H7

L7

AD19

AD22

AC7

AD12

G22

G9

J24

AB24

W7

AA18

AA17

AE5

12

G14

G17

P24

U24

GND

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

5V

12

GND

12

12

12

12

12

12

AGPVDDQ

12

12

12

12

GND

AGPVDDQ

12

12

GND

NVVDD

12

12

12

12

12

12

3V3

12

12

12

GND

12

GND

12

GND

GND

12

GND

GND

GND

AGP spacing rules

PCIAD[31..0]

PCICBE[3..0]

PCICLK

PCIRST*

PCIREQ

PCIGNT

PCIFRAME

PCIIRDY

PCITRDY

PCISTOP

PCIDEVSEL

PCIPAR

PCIINTA

PCIINTB

AGPRBF

AGPWBF

AGPDBI_HI

AGPDBI_LO

AGPST0

AGPST1

AGPST2

AGPADSTB0F

AGPADSTB0S

AGPADSTB1F

AGPADSTB1S

AGPSBSTBF

AGPSBSTBS

AGPSBA[7..0]

AGPVREFCG

AGPVREFGC

AGPMBDET

AGPSTOP

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Numb er Rev

Custom

AGP INTERFACE

Date:

Tuesday, September 03, 2002

Sheet of

2 18

100

Page 3

NV18 FRAMEBUFFER INTERFACE AND DECOUPLING

FBD[127..0]{4,5,6,7}

AJ29

AJ30

AH29

AH30

AF29

AE29

AD29

AC28

AG28

AF27

AE27

AE28

AD27

AB25

AB26

AA25

AD30

AC29

AB28

AB29

Y29

W28

W29

V29

AC27

AB27

AA27

AA26

W25

V26

V27

V25

N25

N27

N26

M25

K26

K27

J27

H27

N29

M29

M28

L29

J29

J28

H29

G30

K25

J26

J25

G26

F28

F26

E27

D27

H28

G29

F29

E29

C30

C29

B30

A30

AF28

AD26

AA30

AG30

AD25

AA29

Y27

L27

K29

G25

E28

W27

M27

K30

G27

D30

V30

U28

U29

T28

T29

T27

T30

T26

T25

R27

R25

R30

R26

R29

P28

P29

R28

U27

P27

N30

V21

U21

N21

P21

C28

FBVDDQ

GND

FBDQM0{4}

FBDQM1{4}

FBDQM2{4}

FBDQM3{4}

FBDQM4{5}

FBDQM5{5}

FBDQM6{5}

FBDQM7{5}

FBDQS0{4}

FBDQS1{4}

FBDQS2{4}

FBDQS3{4}

FBDQS4{5}

FBDQS5{5}

FBDQS6{5}

FBDQS7{5}

FBAA0{4,5}

FBAA1{4,5}

FBAA2{4,5}

FBAA3{4,5}

FBAA4{4,5}

FBAA5{4,5}

FBAA6{4,5}

FBAA7{4,5}

FBAA8{4,5}

FBAA9{4,5}

FBAA10{4,5}

FBAA11{4,5}

1212

12

FBABA0{4,5}

FBABA1{4,5}

FBARAS*{4,5}

FBACAS*{4,5}

FBAWE*{4,5}

FBACS0*{4,5}

FBACS1*

FBACKE{4,5}

FBACLK0{4}

FBACLK0*{4}

FBACLK1{5}

FBACLK1*{5}

D3

E4

F5

L28

AE26

Y28

F27

W26

M26

F17

G11

G8

F8

L25

Y25

F11

F14

F20

F23

Y24

L24

G20

G23

H24

AC24

H25

P25

U25

AC25

C11

D6

C20

E19

E12

D25

N13

P13

U13

V13

M14

N14

P14

R14

T14

U14

V14

W14

M15

N15

P15

R15

T15

U15

V15

W15

M16

N16

P16

R16

T16

U16

V16

W16

M17

N17

P17

R17

T17

U17

V17

W17

M18

N18

P18

R18

T18

U18

V18

W18

M19

N19

P19

R19

T19

U19

V19

W19

P12

N12

V12

U12

M12

R12

T12

W12

M13

R13

T13

W13

FBVDDQ

GND

GND

12 12 12

GND

12 12 12 12 12

12 12 12 12 12

12 12 12 12 12

GND

GND

GND

FBDQM8{6}

FBDQM9{6}

FBDQM10{6}

FBDQM11{6}

FBDQM12{7}

FBDQM13{7}

FBDQM14{7}

FBDQM15{7}

FBDQS8{6}

FBDQS9{6}

FBDQS10{6}

FBDQS11{6}

FBDQS12{7}

FBDQS13{7}

FBDQS14{7}

FBDQS15{7}

FBBA0{6,7 }

FBBA1{6,7 }

FBBA2{6,7 }

FBBA3{6,7 }

FBBA4{6,7 }

FBBA5{6,7 }

FBBA6{6,7 }

FBBA7{6,7 }

FBBA8{6,7 }

FBBA9{6,7 }

FBBA10{6,7 }

FBBA11{6,7 }

FBBBA0{6,7}

FBBBA1{6,7}

FBBRAS*{6,7} FBD[127..0] {4,5,6,7}

FBBCAS*{6,7}

FBBWE*{6,7}

FBBCS0*{6,7}

FBBCS1*

FBBCKE{6,7}

FBBCLK0{6}

FBBCLK0*{6}

FBBCLK1{7}

FBBCLK1*{7}

FBBBA0

B29

A29

B28

A28

B26

B25

B24

C23

E26

D26

E25

C25

E24

F22

E22

F21

A24

B23

C22

B22

B20

C19

B19

B18

D23

D22

D21

E21

F19

E18

D18

F18

F13

D13

E13

F12

E10

D10

D9

D8

B13

B12

C12

B11

B9

C9

B8

A7

F10

E9

F9

F7

C6

E6

D5

C4

C8

B7

B6

B5

A3

B3

A2

B2

C26

F24

B21

D20

D11

B10

D7

C5

A27

D24

A21

D19

D12

A10

E7

A4

A18

C17

B17

C16

B16

D16

A16

E16

F16

D15

F15

A15

E15

B15

C14

B14

C15

D17

D14

A13

K18

K17

K13

K14

AF9

AF10

AG11

AK30

B1

D1

N6

N5

U7

H6

A25

AK25

AA5

B4

B27

L5

AC6

D29

AG29

AF20

AH16

AK15

AF11

AH21

U26

AD28

AH18

F25

C18

E14

AF8

Y8

K3

G3

F6

AF17

AF23

AH24

AH28

AG27

AF26

AF14

AH13

L8

P26

G28

K28

N28

V28

AA28

F30

J30

M30

W30

AB30

AE30

H26

L26

Y26

AC26

E17

D28

C27

C7

E8

A9

C10

E11

C13

E20

C21

E23

C24

A6

A12

AH10

AK12

C3

D4

E5

AG4

AH3

AK6

AH7

AF5

AE6

AK9

N3

H11

AC11

H20

AC20

L23

Y23

F1

J1

M1

T1

W1

AB1

AE1

A19

AK19

A22

AK22

FBDQM[7..0] {4,5}

FBDQS[7..0] {4,5}

GND

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

FRAMEBUFFER INTERFACE

Tuesday, September 03, 2002

Date:

3 18

Sheet of

100

Page 4

FBDQS2{3}

FBD[127..0]

FBDQS3{3}

FBVDDQ

12

GND

GND

GND

12

12

C0402MS

12

12

12

C0402MS

C0402MS

C0402MS

C0402MS

C0402MS

C0402MS

12

C0402MS

GND

12

C0402MS

GND

12

C0805MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0805MS

GND

FBACLK0{3}

FBACLK0*{3}

FBACLK1{3,5}

FBACLK1*{3,5}

FBD[127..0]{3,5,6,7}

FBDQM[7..0]{3,5}

FBDQS[7..0]{3,5}

FBD[127..0]{3,5,6,7}

MFBDQM[7..0]{5}

MFBDQS[7..0]{5}

FBAA[11..0]{3,5}

FBARAS*{3,5}

FBACAS*{3,5}

FBAWE*{3,5}

FBACS0*{3,5}

FBACS1*{3}

FBABA[1..0]{3,5}

FBACKE{3,5}

FBAA[11..0]{3,5}

FBARAS*{3,5}

FBACAS*{3,5}

FBAWE*{3,5}

FBACS0*{3,5}

FBACS1*{3}

FBABA[1..0]{3,5}

FBACKE{3,5}

12

61

55

15

9

3

12

<P_mat> <P_volt>

C0402MS

GND

Place

component

to memory

MFBDQS0

MFBD0

MFBD1

MFBD2

MFBD3

MFBD4

MFBD5

MFBD6

MFBD7

MFBD8

MFBD9

MFBD10

MFBD11

MFBD12

MFBD13

MFBD14

MFBD15

MFBDQS1

FBA_MVREF0

FBVDDQ

MFBDQS2

MFBD16

MFBD17

MFBD18

MFBD19

MFBD20

MFBD21

MFBD22

MFBD23

MFBD24

MFBD25

MFBD26

MFBD27

MFBD28

MFBD29

MFBD30

MFBD31

MFBDQS3

FBA_MVREF0

16

2

4

5

7

8

10

11

13

54

56

57

59

60

62

63

65

51

49

17

14

19

25

53

50

42

43

TSOP66

61

55

15

9

3

16

2

4

5

7

8

10

11

13

54

56

57

59

60

62

63

65

51

49

17

14

19

25

53

50

42

43

TSOP66

FBDQS0{3}

FBDQS1{3}

FBD[127..0]

1 2

R0402MS

1 8

RN0402_8P4R

3 6

RN0402_8P4R

1 2

R0402MS

1 2

R0402MS

1 8

RN0402_8P4R

3 6

RN0402_8P4R

1 2

R0402MS

1 2

R0402MS

FBVDDQ

12

12

GND GND

1 2

R0402MS

1 8

RN0402_8P4R

3 6

RN0402_8P4R

1 2

R0402MS

1 2

R0402MS

1 8

RN0402_8P4R

3 6

RN0402_8P4R

1 2

R0402MS

1 2

R0402MS

R0402MS

FBA_MVREF0

R0402MS

1 2

2 7

4 5

1 2

1 2

2 7

4 5

1 2

1 2

Place

component

to memory

12

<P_mat>

C0402MS

1 2

2 7

4 5

1 2

1 2

2 7

4 5

1 2

1 2

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

<P_volt>

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

DQSL

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQSU

VREF

NC

NC

NC

NC

NC

NC

NC

NC

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

DQSL

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQSU

VREF

NC

NC

NC

NC

NC

NC

NC

NC

1

VCC

18

VCC

33

VCC

29

FBAA0

A0

30

FBAA1

A1

31

FBAA2

A2

FBAA3

32

A3

35

FBAA4

A4

36

FBAA5

A5

37

FBAA6

A6

38

FBAA7

A7

FBAA8

39

A8

40

FBAA9

A9

28

FBAA10

A10/AP

DMU

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

A10/AP

DMU

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

41

A11

26

BA0

27

BA1

24

CS

23

RAS

22

CAS

20

DML

47

21

WE

46

CLK

45

CLK

44

CKE

34

VSS

48

VSS

66

VSS

6

12

52

58

64

1

VCC

18

VCC

33

VCC

29

A0

30

A1

31

A2

32

A3

35

A4

36

A5

37

A6

38

A7

39

A8

40

A9

28

41

A11

26

BA0

27

BA1

24

CS

23

RAS

22

CAS

20

DML

47

21

WE

46

CLK

45

CLK

44

CKE

34

VSS

48

VSS

66

VSS

6

12

52

58

64

FBVDDQ

FBAA11

FBABA0

FBABA1

12

FBACS0*

FBARAS*

FBACAS*

MFBDQM0

MFBDQM1

FBAWE*

BACLK0* FBACLK0*

BACLK0

FBACKE

FBVDD

FBAA0

FBAA1

FBAA2

FBAA3

FBAA4

FBAA5

FBAA6

FBAA7

FBAA8

FBAA9

FBAA10

FBAA11

FBABA0

FBABA1

FBACS0*

FBARAS*

FBACAS*

MFBDQM2

MFBDQM3

FBAWE*

FBACLK0*

FBACLK0

FBACKE

FBDQM0

FBDQM1

FBVDDQ

12

GND

12

FBDQM2

FBDQM3

R0402MS

R0402MS

R0402MS

R0603MS

1 2

1 2

1 2

R0603MS

1 2

12

12

R0402MS

R0402MS

R0402MS

R0402MS

FBACLK0*

FBACLK0

1 2

1 2

GND

MFBDQM0

MFBDQM1

GND

12

C0402MS

C0402MS

R0402MS

R0402MS

FBACLK0

GND

GND

MFBDQM2

MFBDQM3

12

12

C0402MS

GND

12

C0402MS

GND

GND

12

12

C0402MS

GND

12

GND

12

12

C0402MS

GND

12

GND

C0402MS

12

C0402MS

Memory decoupling

12

C0402MS

C0402MS

C0402MS

GND

Memory decoupling

C0402MS

C0402MS

12

C0402MS

GNDGND

GND

12

GND

GND

GNDGND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

Place in

memory

section

12

GND

Place in

memory

section

12

GND

FBVDD

FBVDDQ

FBVDDQ

C0805MS

FBVDDQ

FBVDDQ

C0805MS

Diffpair NET_SPACING_RULENET

Size Document Numb er Rev

Date:

FBVDDQ

C0402MS

By-pass caps

for core

transition

FBVDDQ

C0402MS

By-pass caps

for core

transition

12

C0402MS

GND

12

C0402MS

GND

12

GND

12

GND

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Custom

8x16 DDR 0..31 128 bit

Tuesday, September 03, 2002

Sheet of

4 18

100

Page 5

FBDQS6{3}

FBD[127..0]

FBDQS7{3}

FBVDDQ

<P_mat><P_volt>

<P_mat> <P_volt>

<P_mat> <P_volt>

12

GND

12

GND

12

GND

12

GND

12

12

GND

12

GNDGND

<P_mat><P_volt>

<P_mat> <P_volt>

<P_mat> <P_volt>

GND

GND

GND

12

GND

GND

GND

GND

12

12

12

12

<P_mat> <P_volt>

12

<P_mat> <P_volt>

12

<P_mat><P_volt>

FBACLK0{3,4}

FBACLK0*{3,4}

FBACLK1{3}

FBACLK1*{3}

FBD[127..0]{3,4,6,7}

FBDQM[7..0]{3,4}

FBDQS[7..0]{3,4}

FBD[127..0]{3,4,6,7}

MFBDQM[7..0]{4}

MFBDQS[7..0]{4}

FBAA[11..0]{3,4}

FBARAS*{3,4}

FBACAS*{3,4}

FBAWE*{3,4}

FBACS0*{3,4}

FBACS1*{3}

FBABA[1..0]{3,4}

FBACKE{3,4}

12

61

55

15

9

3

FBVDDQ

<P_volt>

MFBDQS4

MFBD32

MFBD33

MFBD34

MFBD35

MFBD36

MFBD37

MFBD38

MFBD39

MFBD40

MFBD41

MFBD42

MFBD43

MFBD44

MFBD45

MFBD46

MFBD47

MFBDQS5

MFBDQS6

MFBD48

MFBD49FBD49

MFBD50

MFBD51

MFBD52

MFBD53

MFBD54

MFBD55

MFBD56

MFBD57

MFBD58

MFBD59

MFBD60

MFBD61

MFBD62

MFBD63

MFBDQS7

16

2

4

5

7

8

10

11

13

54

56

57

59

60

62

63

65

51

49

17

14

19

25

53

50

42

43

61

55

15

9

3

16

2

4

5

7

8

10

11

13

54

56

57

59

60

62

63

65

51

49

17

14

19

25

53

50

42

43

FBDQS4{3}

FBDQS5{3}

FBD[127..0]

FBD[127..0]

FBD32

FBD33

FBD34

FBD35

FBD36

FBD37

FBD38

FBD39

FBD40

FBD41

FBD42

FBD43

FBD44

FBD45

FBD46

FBD47

FBD48

FBD50

FBD51

FBD52

FBD53

FBD54

FBD55

FBD56

FBD57

FBD58

FBD59

FBD60

FBD61

FBD62

FBD63

1 2

1 8

3 6

1 2

1 2

1 8

3 6

1 2

1 2

1 2

1 8

3 6

1 2

1 2

1 8

3 6

1 2

1 2

FBVDDQ

GND

12

12

FBB_MVREF0

1 2

2 7

4 5

1 2

1 2

2 7

4 5

1 2

1 2

12

GND

1 2

2 7

4 5

1 2

1 2

2 7

4 5

1 2

1 2

Place

component

to memory

<P_volt>

<P_mat>

12

GND

FBB_MVREF0

FBB_MVREF0

<P_mat>

Place

component

to memory

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

DQSL

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQSU

VREF

NC

NC

NC

NC

NC

NC

NC

NC

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

DQSL

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQSU

VREF

NC

NC

NC

NC

NC

NC

NC

NC

A10/AP

DMU

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

A10/AP

DMU

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

1

VCC

18

VCC

33

VCC

FBAA0

29

A0

30

A1

31

A2

32

A3

35

A4

36

A5

37

A6

38

A7

39

A8

40

A9

28

41

A11

26

BA0

27

BA1

24

CS

23

RAS

22

CAS

20

DML

47

21

WE

46

CLK

45

CLK

44

CKE

34

VSS

48

VSS

66

VSS

6

12

52

58

64

1

VCC

18

VCC

33

VCC

29

A0

30

A1

31

A2

32

A3

35

A4

36

A5

37

A6

38

A7

39

A8

40

A9

28

41

A11

26

BA0

27

BA1

24

CS

23

RAS

22

CAS

20

DML

47

21

WE

46

CLK

45

CLK

44

CKE

34

VSS

48

VSS

66

VSS

6

12

52

58

64

FBACS0*

FBARAS*

FBACAS*

MFBDQM4

MFBDQM5

FBAWE*

FBACLK1

FBACKE

FBDQM4

FBDQM5

FBACS0*

FBARAS*

FBACAS*

MFBDQM6

MFBDQM7

FBAWE*

FBACLK1*

FBACLK1

FBACKE

FBVDDQ

FBVDDQ

FBDQM6

FBDQM7

12

12

1 2

1 2

1 2

12

12

FBACLK1*

FBACLK1

1 2

1 2

1 2

GND

MFBDQM4

MFBDQM5

12

GND GNDGND

MFBDQM6

MFBDQM7

<P_mat><P_volt>

GND

GND

GND

12

GND

12

12

<P_mat><P_volt>

12 12

<P_mat> <P_volt>

<P_mat> <P_volt>

12

GND

12

GND

12

GND

12

<P_mat><P_volt>

12

<P_mat> <P_volt>

GND

12

<P_mat> <P_volt>

GND

12

<P_mat> <P_volt>

GND

12

GND

12

GND

Memory decoupling

12

GND

12

GND

12

GND

Memory decoupling

12

GND

FBVDDQ

Place in

memory

section

12

GND

FBVDDQ

Place

component in

memory

section

FBVDDQ

12

<P_mat><P_volt>

GND

FBVDDQ

GND

GND

12

By-pass caps

for core

transition

12

<P_mat> <P_volt>

By-pass caps

for core

transition

NET_SPACING_RULEDiffpairNET

FBVDDQ

12

GND

FBVDDQ

12

<P_mat> <P_volt>

GND

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Numb er Rev

Custom

8x16 DDR 32..63 128 bit

Date:

Tuesday, September 03, 2002

Sheet of

5 18

100

Page 6

FBVDDQ

FBVDDQ

Place in

memory

section

FBVDDQ

12

C0805MS

GND

FBVDD

FBVDDQ

Place component

in memory

section

FBVDDQ

12

C0805MS

GND

FBVDD

NET Diffpair NET_SPACING_RULE

12

12

GND

C0402MS

C0402MS

C0402MS

C0402MS

C0402MS

12

C0402MS

C0402MS

12

C0402MS

GND

12

C0402MS

GND

12

C0805MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0805MS

GND

FBBCLK0{3}

FBBCLK0*{3}

FBBCLK1{3,7}

FBBCLK1*{3,7}

FBD[127..0]{3,4,5,7}

FBDQM[15..8]{3,7}

FBDQS[15..8]{3,7}

FBD[127..0]{3,4,5,7}

MFBDQM[15..8]{7}

MFBDQS[15..8]{7}

FBBA[7..4]{3,7}

FBBA[11..0]{3,7}

FBBRAS*{3,7}

FBBCAS*{3,7}

FBBWE*{3,7}

FBBCS0*{3,7}

FBBCKE{3,7}

FBBA[11..0]{3,7}

FBBRAS*{3,7}

FBBCAS*{3,7}

FBBWE*{3,7}

FBBCS0*{3,7}

FBBBA1{3,7}

FBBBA0{3,7}

FBBCKE{3,7}

FBBBA1{3,7}

FBBBA0{3,7}

12

C0402MS12C0402MS

GND

12

C0402MS

GND

GND

MFBDQM10

R0402MS

MFBDQM11

R0402MS

12

GND

12

C0402MS

GND GND

12

C0402MS

GND

12

C0402MS

GND

GND

GND

12

12

12

A10/AP

DMU

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

A10/AP

DMU

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

FBVDD

1

VCC

18

VCC

33

VCC

29

A0

30

A1

31

A2

32

A3

35

A4

36

A5

37

A6

38

A7

39

A8

40

A9

28

41

A11

26

BA0

27

BA1

24

CS

23

RAS

22

CAS

20

DML

47

21

WE

46

CLK

45

CLK

44

CKE

34

VSS

48

VSS

66

VSS

6

12

52

58

64

1

VCC

18

VCC

33

VCC

29

A0

30

A1

31

A2

32

A3

35

A4

36

A5

37

A6

38

A7

39

A8

40

A9

28

41

A11

26

BA0

27

BA1

24

CS

23

RAS

22

CAS

20

DML

47

21

WE

46

CLK

45

CLK

44

CKE

34

VSS

48

VSS

66

VSS

6

12

52

58

64

FBBRAS*

FBBCAS*

MFBDQM8

MFBDQM9

FBBWE*

FBBCLK0*

FBBCLK0

FBBCKE

FBVDD

FBBCS0*

FBBRAS*

FBBCAS*

MFBDQM10

MFBDQM11

FBBWE*

FBBCLK0*

FBBCLK0

FBBCKE

FBDQM8

FBDQM9

FBVDDQ

FBVDDQ

12

R0402MS

12

R0402MS

12

R0402MS

FBDQM10

FBDQM11

1 2

1 2

1 2

1 2

12

R0603MS

12

R0603MS

R0402MS

R0402MS

R0402MS

R0402MS

FBBCLK0*

FBBCLK0

1 2

1 2

GND

MFBDQM8

MFBDQM9

61

VCCQ

55

VCCQ

15

VCCQ

9

VCCQ

3

VCCQ

MFBDQS8

FBDQS8{3}

FBDQS9{3}

FBDQS10{3}

FBD[127..0]

FBD[127..0]{3,4,5,7}

FBDQS11{3}

FBD[127..0]

FBD64

FBD65

FBD66

FBD67

FBD68

FBD69

FBD70

FBD71

FBD72

FBD73

FBD74

FBD75

FBD76

FBD77

FBD78

FBD79

FBD80

FBD81

FBD82

FBD83

FBD84

FBD85

FBD86

FBD87

FBD88

FBD89

FBD90

FBD91

FBD92

FBD93

FBD94

FBD95

1 2

1 8

3 6

1 2

1 2

1 8

3 6

1 2

1 2

1 2

1 8

3 6

1 2

1 2

1 8

3 6

1 2

1 2

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

FBVDDQ

12

R0402MS

12

R0402MS

GND

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

FBC_MVREF0

1 2

2 7

4 5

1 2

1 2

2 7

4 5

1 2

1 2

12

C0402MS

GND

1 2

2 7

4 5

1 2

1 2

2 7

4 5

1 2

1 2

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

Place

component

to memory

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

12

GND

FBC_MVREF0

FBVDDQ

FBC_MVREF0

C0402MS

Place

component

to memory

16

DQSL

MFBD64

2

DQ0

4

MFBD65

DQ1

5

MFBD66

DQ2

7

MFBD67

DQ3

8

MFBD68

DQ4

MFBD69

10

DQ5

11

MFBD70

DQ6

13

MFBD71

DQ7

54

MFBD72

DQ8

56

MFBD73

DQ9

MFBD74

57

DQ10

59

MFBD75

DQ11

60

MFBD76

DQ12

62

MFBD77

DQ13

63

MFBD78

DQ14

MFBD79 FBBCS0*

65

DQ15

51

MFBDQS9

DQSU

49

VREF

17

NC

14

NC

19

NC

25

NC

53

NC

50

NC

42

NC

43

NC

TSOP66

61

VCCQ

55

VCCQ

15

VCCQ

9

VCCQ

3

VCCQ

16

MFBDQS10

DQSL

2

MFBD80

DQ0

4

MFBD81

DQ1

MFBD82

5

DQ2

7

MFBD83

DQ3

8

MFBD84

DQ4

10

MFBD85

DQ5

11

MFBD86

DQ6

MFBD87

13

DQ7

54

MFBD88

DQ8

56

MFBD89

DQ9

57

MFBD90

DQ10

59

MFBD91

DQ11

MFBD92

60

DQ12

62

MFBD93

DQ13

63

MFBD94

DQ14

65

MFBD95

DQ15

MFBDQS11

51

DQSU

49

VREF

17

NC

14

NC

19

NC

25

NC

53

NC

50

NC

42

NC

43

NC

TSOP66

C0402MS

12

C0402MS

Memory decoupling

12

C0402MS

C0402MS

12

C0402MS

GND

Memory decoupling

C0402MS

C0402MS

12

GND

12

GND

GND

12

GNDGND

12

GND

12

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

C0402MS

12

C0402MS

GND

By-pass caps

for core

transition

12

C0402MS

GND

By-pass caps

for core

transition

FBVDDQ

12

C0402MS

GND

FBVDDQ

12

C0402MS

GND

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Numb er Rev

Custom

8x16 DDR 64..95 128 bit

Date:

Tuesday, September 03, 2002

Sheet of

6 18

100

Page 7

FBDQS12{3}

FBDQS13{3}

FBDQS14{3}

FBD[127..0]

FBDQS15{3}

FBD[127..0]

FBD96

FBD97

FBD98

FBD99

FBD100

FBD101

FBD102

FBD103

FBD104

FBD105

FBD106

FBD107

FBD108

FBD109

FBD110

FBD111

FBD[127..0]

FBD112

FBD113

FBD114

FBD115

FBD116

FBD117

FBD118

FBD119

FBD120

FBD121

FBD122

FBD123

FBD124

FBD125

FBD126

FBD127

1 2

1 8

3 6

1 2

1 2

1 8

3 6

1 2

1 2

1 2

1 8

3 6

1 2

1 2

1 8

3 6

1 2

1 2

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

FBVDDQ

12

R0402MS

12

R0402MS

GND

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

FBD_MVREF0

1 2

2 7

4 5

1 2

1 2

2 7

4 5

1 2

1 2

12

GND

1 2

2 7

4 5

1 2

1 2

2 7

4 5

1 2

1 2

C0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

Place

component

to memory

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

RN0402_8P4R

RN0402_8P4R

R0402MS

R0402MS

12

GND

FBD_MVREF0

FBVDDQ

FBD_MVREF0

C0402MS

Place

component

to memory

MFBDQS12

MFBD96

MFBD97

MFBD98

MFBD99

MFBD100

MFBD101

MFBD102

MFBD103

MFBD104

MFBD105

MFBD106

MFBD107

MFBD108

MFBD109

MFBD110

MFBD111

MFBDQS13

MFBDQS14

MFBD112

MFBD113

MFBD114

MFBD115

MFBD116

MFBD117

MFBD118

MFBD119

MFBD120

MFBD121

MFBD122

MFBD123

MFBD124

MFBD125

MFBD126

MFBD127

MFBDQS15

FBVDDQ

12

12

12

12

12

C0402MS

C0402MS

C0402MS

C0402MS

C0402MS

12

C0402MS

GND

12

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

C0402MS

GND

Memory decoupling

GND

GND GND

12

C0402MS

GND

Memory decoupling

GND

GND

12

C0402MS

GND

12

C0402MS

GND

GND

12

C0402MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

A10/AP

DMU

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

A10/AP

DMU

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

FBVDD

1

VCC

18

VCC

33

VCC

29

A0

30

A1

31

A2

32

A3

35

A4

36

A5

37

A6

38

A7

39

A8

40

A9

28

41

A11

26

BA0

27

BA1

24

CS

23

RAS

22

CAS

20

DML

47

21

WE

46

CLK

45

CLK

44

CKE

34

VSS

48

VSS

66

VSS

6

12

52

58

64

1

VCC

18

VCC

33

VCC

29

A0

30

A1

31

A2

32

A3

35

A4

36

A5

37

A6

38

A7

39

A8

40

A9

28

41

A11

26

BA0

27

BA1

24

CS

23

RAS

22

CAS

20

DML

47

21

WE

46

CLK

45

CLK

44

CKE

34

VSS

48

VSS

66

VSS

6

12

52

58

64

FBBCS0*

FBBRAS*

FBBCAS*

MFBDQM12

MFBDQM13

FBBWE*

FBBCLK1*

FBBCLK1

FBBCKE

FBVDD

FBBCS0*

FBBRAS*

FBBCAS*

MFBDQM14

MFBDQM15

FBBWE*

FBBCLK1*

FBBCLK1

FBBCKE

FBDQM12

FBDQM13

FBVDD

FBVDDQ

FBVDDQ

12

R0402MS

12

R0402MS

FBDQM14

FBDQM15

R0603MS

1 2

1 2

1 2

R0603MS

1 2

12

12

R0402MS

R0402MS

R0402MS

R0402MS

FBBCLK1*

FBBCLK1

1 2

1 2

61

VCCQ

55

VCCQ

15

VCCQ

9

VCCQ

3

VCCQ

16

DQSL

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

54

DQ8

56

DQ9

57

DQ10

59

DQ11

60

DQ12

62

DQ13

63

DQ14

65

DQ15

51

DQSU

49

VREF

17

NC

14

NC

19

NC

25

NC

53

NC

50

NC

42

NC

43

NC

TSOP66

61

VCCQ

55

VCCQ

15

VCCQ

9

VCCQ

3

VCCQ

16

DQSL

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

54

DQ8

56

DQ9

57

DQ10

59

DQ11

60

DQ12

62

DQ13

63

DQ14

65

DQ15

51

DQSU

49

VREF

17

NC

14

NC

19

NC

25

NC

53

NC

50

NC

42

NC

43

NC

TSOP66

MFBDQM12

MFBDQM13

R0402MS

R0402MS

GND

12

GND

MFBDQM14

MFBDQM15

C0402MS

GND

GND

C0402MS

GND

GND

GND

12

12

C0402MS

12

C0402MS

12

C0402MS

12

C0402MS

12

C0402MS

GND

12

C0402MS

C0402MS

GND

12

C0402MS

GND

12

C0805MS

GND

12

C0402MS

GND

12

C0402MS

GND

12

12

C0402MS

C0402MS

GND

12

C0805MS

GND

FBBCLK0{3,6}

FBBCLK0*{3,6}

FBBCLK1{3}

FBBCLK1*{3}

FBD[127..0]{3,4,5,6}

FBDQM[15..8]{3,6}

FBDQS[15..8]{3,6}

FBD[127..0]{3,4,5,6}

MFBDQM[15..8]{6}

MFBDQS[15..8]{6}

FBBA[7..4]{3,6}

FBBA[11..0]{3,6}

FBBRAS*{3,6}

FBBCAS*{3,6}

FBBWE*{3,6}

FBBCS0*{3,6}

FBBCKE{3,6}

MFBBA[11..0]

MFBBRAS*

MFBBCAS*

MFBBWE*

MFBBCS0*

FBBBA1{3,6}

FBBBA0{3,6}

MFBBCKE

Place in

memory

section

12

GND

Place in

memory

section

12

GND

NET

FBVDDQ

FBVDDQ

C0805MS

FBVDD

FBVDDQ

FBVDDQ

C0805MS

FBVDD

Diffpair

12

C0402MS

GND

By-pass caps

for core

transition

12

C0402MS

GND

By-pass caps

for core

transition

FBVDDQ

12

C0402MS

GND

FBVDDQ

12

C0402MS

NET_SPACING_RULE

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Numb er Rev

Custom

8x16 DDR 96..127 128 bit

Date:

Tuesday, September 03, 2002

Sheet of

7 18

100

Page 8

NV18 STRAPPING, I/O INTERFACE, BIOS, FAN CONTROL AND TEMP SENSOR

AE8

AD8

AD9

G2

J3

K2

K1

L3

L2

M3

N2

N1

P3

P2

M4

M5

M6

AE7

AG7

AG1

AC5

AD4

AB5

STRAPPING OPTIONS

A3V3

VIPPCLK {15}

1 2

1 2

FRWR_PME {2}

FRWR_LNKON

FRWR_LPS

12

RESET_BUF* {15}

VIPD[7..0] {15}

VIPHAD[1..0]

12

12

12

5V

12

3V3

12

12

GND

DVOD[11..0]

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

DVOVSYNC

DVOCLKOUT

12

GND

DACA_VSYNC {9}

DACA_HSYNC {9}

DACB_VSYNC {9}

DACB_HSYNC {9}

AF2

R2

R1

AD5

AD6

AE4

AB6

AJ2

M2

AG2

AH1

AG3

AJ1

AH2

AK1

AJ3

AK3

AH4

AK4

AJ4

AH5

AF4

G1

J2

N4

AK2 AA6

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

3V3

3V3

12

GND

NVVDD

12

GND

I2CC_SCL {15,16,18}

I2CC_SDA{15,16,18}

BIOS (serial)

3V3

12

BIOS (alternative)

NV18 GPIO

FAN Control

FAN+{18}

FAN-{18}

TEMP Sensor

1

2

7 8

3

1

5

2

6

8

1

3

5

6

4

H3

12

C0603MS

FAN

FAN-

3V3

12

4

GND

3V3

2

7

GND

Place close

together

south-west

of GPU

GND

3

8

7

H5

DVI_HPD

H4

J4

J5

J6

K5

K4H2

K6

L4

12V 5V

132

SOT23

FAN

SOT23_1G1D1S

FAN

NET VOLTAGENET_PHYSICAL_TYPE

FAN_RETURN

THERM

THERM*

THERM

THERM*

DVOD[11..0]

DVOCLKOUT

DVODE

DVOHSYNC

DVOVSYNC

VIPD[7..0]{15}

VIPPCLK{15}

NET

Diffpair

NET_SPACING_RULE

Twin BIOS

DVOD0

DVOD1

DVOD2

DVOD3

DVOD4

DVOD5

DVOD6

DVOD7

DVOD8

DVOD9

DVOD10

DVOD11

DVOVSYNC

ROMA14

ROMA15

DVODE

1

1

2

2

3

3

GND

VIPD[7..0]

12

11

10

9

8

7

6

5

27

26

23

25

4

28

29

3

2

30

22

24

31

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

NC/A16

NC/A17

CE

OE

WE

13

VIPD0

O0

VIPD1

14

O1

VIPD2

15

O2

VIPD3

17

O3

VIPD4

18

O4

19

VIPD5

O5

VIPD6

20

O6

VIPD7

21

O7

1

NC

32

VDD

16

GND

GNDGND

3V3

12

DVI_HPD

LOAD_TEST{10}

SEL_2ND_DEV{9,10}

12

12

GND

GND

12

R0603MS

FAN

1 2

R0603MS

FAN_ON

12

FAN

3V3

12

12

4

6

12

5

DVODE

DVOD[11..0]

DVOHSYNC

ROMCS*

VIPHAD0

VIPHAD1

1 2

VIPHAD[1..0]

GND

GND

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

Strapping, I/O interface ,BIOS

Date:

Tuesday, September 03, 2002

Sheet of

8 18

100

Page 9

NV18 DAC_A, DAC_B, PLL, SYNC AMPL

NV18 DAC_A

A3V3

1 2

12

12

GND

NV18 DAC_B with RSet select

A3V3

1 2

12

12

GND

NV18 PLL

NET

DACA_VDD

DACA_VREF

DACA_RSET

DACB_VDD

DACB_VREF

DACB_RSET

PLLVDD

DACA_RED{12}

DACA_GREEN{12}

DACA_BLUE{12}

DACB_RED{10}

DACB_GREEN{10}

DACB_BLUE{10}

AG9

AH8

12

12

1212

12

GND

12

GND

1

AG8

1212

AB4

Y5

AD3

12

12

3

2

GND

AG6

AF7

AH9

AJ8

AK10

AJ10

AJ9

AG10

GND

AF6

AG5

AF3

AE3

AE2

AD2

AD1

AC4

GND

I2CA_SCL {12}

I2CA_SDA {12}

DACA_HSYNC {8}

DACA_VSYNC {8}

DACA_RED {12}

DACA_GREEN {12}

DACA_BLUE {12}

I2CB_SCL {11}

I2CB_SDA {11}

DACB_HSYNC {8}

DACB_VSYNC {8}

DACB_RED {10}

DACB_GREEN {10}

DACB_BLUE {10}

SYNC Amplifier

5V

12

GND

5V

1

3

2

7 14

GND

5V

4

5

7 14

GND

5V

13

12

7 14

GND

5V

10

9

7 14

GND

1 2

1 2

6

1 2

1 2

11

1 2

1 2

8

1 2

1 2

NET_PHYSICAL_TYPE

NET Diffpair

DACA_HSYNC_BUF {12}

DACA_VSYNC_BUF {12}

DACB_HSYNC_BUF {11}

DACB_VSYNC_BUF {11}

NET_SPACING_RULE

VOLTAGE

A3V3

1 2

12

GND

12

12

12

12

GND

AK7

AJ7

AJ6

12

GND

AJ5

AH6

12

12

GND

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

DAC_A,DAC_B,PLL,SYNC AMPL

Date:

Tuesday, September 03, 2002

Sheet of

9 18

100

Page 10

DACB SWITCH BETWEEN VGA OUT AND TV OUT

DACB_RED_SW{11}

DACB_GREEN_SW{11}

DACB_BLUE_SW{11}

MINIDIN_COUT{16}

MINIDIN_Y_CVBSOUT{16}

MINIDIN_PBOUT{16}

1 2

1 2

1 2

1 2

1 2

1 2

14

12

13

DACB_RED_SW{11}

DACB_GREEN_SW{11}

DACB_BLUE_SW{11}

11

9

10

5

7

6

A3V3

12

LOAD_TEST{8}

DACB_RED{9}

DACB_GREEN {9}

NET_SPACING_RULEDiffpairNET

MINIDIN_COUT{16}

MINIDIN_Y_CVBSOUT{16}

MINIDIN_PBOUT{16}

SEL_2ND_DEV{8,9}

2

4

3

16

1

12

GND

815

GND

12

1212

5V

121212

GND

12

GND

DACB_BLUE{9}

A3V3

12

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

SWITCH BETWEEN VGA AND TV-OUT

Date:

Tuesday, September 03, 2002

Sheet of

10 18

100

Page 11

DACA output

BRF

BGF

BBF

EMI-FILTER

I2CB_SDA

I2CB_SDA9

I2CB_SCL

I2CB_SCL9

DACB_VSYNC_BUF9

DACB_HSYNC_BUF9

DACB_GREEN_SW10

DACB_BLUE_SW10

DACB_VSYNC_BUF

DACB_HSYNC_BUF

DACB_RED_SW

DACB_RED_SW10

DACB_GREEN_SW

DACB_BLUE_SW

12

GND

12

GND

12

GND GND

1 2

1 2

GND

GND

GND

12

12

12

I2CB_SDA_T

I2CB_SCL_T

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

150-220R@100MHZ

150-220R@100MHZ

12

5V

12

ARF

NO_STUFF

AGF

12

NO_STUFF

GND

ABF

12

NO_STUFF

GND

5V

1212

3

GND

GND

GND

GND

GNDGND

GND

GND

1 2

GND

5V

3

1 2

GND

5V

12

3

1 2

GND

5V

12

3

1 2

GND

A3V3

12

3

1 2

GND

A3V3

12

3

1 2

GND

A3V3

12

3

1 2

I2CB_SDA_C

I2CB_SCL_C

DACB_VSYNC_C

DACB_HSYNC_C

1 2

DACB_RED_C

GND

DACB_GREEN_C

DACB_BLUE_C

DDC_5V

121212

12

GND

16

17

18

10

CGND

GND

12

GND

Place in output filter section!

NTP_B_MON_ID2

4

1

2

3

9

5

8

7

6

11

13

14

15

12

NTP_B_MON_ID0

DACB_RED_C

DACB_GREEN_C

DACB_BLUE_C

Diffpair NET_SPACING_RULENET

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

Date:

DAC A CONNECT

Tuesday, September 03, 2002

11 18

Sheet of

100

Page 12

DACB output

I2CA_SDA{9}

I2CA_SCL{9}

DACA_VSYNC_BUF{9}

DACA_HSYNC_BUF{9}

DACA_RED{9}

DACA_GREEN{9}

DACA_BLUE{9}

EMI-FILTER

1 2

1 2

1 2

12

12

GND

GND

12

12

GND GND

GND

12

12

GND GND

GND

1 2

12

1 2

GND

1 2

12

1 2

1 2

12

GND

1 2

12

5V

12

1 2

1 2

1 2

1 2

1 2

12

1 2

GND

1 2

12

GND

1 2

1 2

12

GND

ARF

AGF

ABF

DACA_RED_C

DACA_GREEN_C

DACA_BLUE_C

5V

12

3

GND

GND

GND

GND

GND

GND

GND

1 2

GND

5V

12

3

1 2

GND

5V

12

3

1 2

GND

5V

12

3

1 2

GND

12

3

1 2

GND

A3V3

12

3

1 2

GND

A3V3

12

3

1 2

GND

DDC_5V

1 2

1 2

12

GND

A3V3

GND

CGND

CGND

12

Place in output filter section!

16

1

2

3

9

17

5

10

8

7

6

GND

5V

12

GND

4

11

13

14

15

12

DiffpairNET

NET_SPACING_RULE

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

Date:

DAC B CONNECT

Tuesday, September 03, 2002

12 18

Sheet of

100

Page 13

INTERNAL TMDS POWER AND DECOUPLING

IFPABVREF

IFPABPLLVDD

IFPAIOVDD

IFPBIOVDD

IFPCVREF

IFPCPLLVDD

IFPCIOVDD

FAN_RETURN

TMDS_BACK

VOLTAGENET_PHYSICAL_TYPENET

3V3TMDS

12

12

3V3TMDS TMDSPLLVDD

12

12

3V3TMDS

1212

12

AA3

R6

P10

N10

R4

R5

T5

1212

12

TMDSPLLVDD

12

1212

1212

1212

T6

GND

AA4

V6

U10

V10

Y4

W5

GND

ATXC

P5

P4

T2

R3

T3

U2

V2

U3

W2

V1

U4

T4

AA1

Y2

W3

V3

U5

V4

AA2

Y3

W4

V5

AB3

AB2

W6

Y6

AC3

AC2

ATXC*

ATXD0

ATXD0*

ATXD1

ATXD1*

ATXD2

ATXD2*

ATXC

ATXC*

ATXD0

ATXD0*

ATXD1

ATXD1*

ATXD2

ATXD2*

TMDS backdrive prevention

12V

1212

12

3

1

2

3

1

2

1 2

121212

3V3TMDS

2

1

3

121212

GND

121212

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

TMDS POWER AND DECOUPING

Tuesday, September 03, 2002

Date:

13 18

Sheet of

100

Page 14

DVI_I OUTPUT

ATXD0

ATXD0*

ATXD1

ATXD1*

ATXD2

ATXD2*

ATXC

ATXC*

NET_SPACING_RULEDiffpairNET

DVI_HPD

1 2

1 2 1 2

12

GND GND GND

A3V3

12

3

1 2

ATXD0*{13}

ATXD0{13}

ATXD1*{13}

ATXD1{13}

ATXD2*{13}

ATXD2{13}

I2CB_SCL_C

I2CB_SDA_C

ATXC*

ATXC

12

GND

DACB_VSYNC_C

DACB_RED_C{11}

DACB_GREEN_C{11}

DACB_BLUE_C{11}

DACB_HSYNC_C

1 2

1 2

1 2

1 2

CGND

DDC_5V

GND

CGND

25

17

18

9

10

1

2

3

11

19

12

13

4

5

20

21

6

7

14

15

22

24

23

8

16

C1

C2

C3

C5

C5A

C4

26

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

DVI CONNECT

Date:

Tuesday, September 03, 2002

Sheet of

14 18

100

Page 15

VIDEO CAPTURE

22 23

CVBS_YIN{16}

CVBS_YIN*

CVBS_YIN*{16}

CIN{16}

CIN*

CIN*{16}

12

12

I2CC_SDA{8,16,18}

I2CC_SCL{8,16,18}

RESET_BUF*{8}

VIPD[7..0]{8}

GND

12

12

GND

NO STUFF

12

VIPPCLK{8}

12

12

NO STUFF

12

GND

12

GND

20

18

19

16

14

12

10

13

37

40

39

41

4

6

7

32

31

27

30

62

61

60

59

57

56

55

54

72

71

70

69

67

66

65

64

45

46

53

52

42

47

48

49

17

11

21

24

15

9

2

99

3

97

98

44

73

74

77

78

79

36

34

35

28

29

90

89

87

86

85

84

82

81

94

95

92

91

96

80

8

1

25

51

75

33

43

58

68

83

93

5

26

50

76

100

38

63

88

12

12

12

1212

12

GND

GND

1 2

12

GND

GND

1 2

1 2

GND GND

GND

GND

SAA 7114

I2C ADDRESS 0X42

12

121212

GND

GND

12

GND

12

GND

GND

1212

GND

GND GND

GND

GND

12

GND

GND

12

12

GND

1 2

12

12

GND

A3V3

12

GND

A3V3

1 2

12

GND

12

GND

12

GND

1 2

12

12

GNDGND

12

GND

12

GNDGND

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

Date:

VIDEO CAPTURE

Tuesday, September 03, 2002

15 18

Sheet of

100

Page 16

VIDEO IN/OUT CONNECTOR

MINIDIN_PBOUT{10}

MINIDIN_COUT{10}

CVBS_YIN{15}

INTERNAL VIDEO CAPTURE CONNECTOR

(option)

CVBS_YIN

CVBS_YIN*

CVBS_YIN*{15}

12

GND

12

GND

GND

1 2

1 2

1 2

GND

GND

A3V3

A3V3

12

GND

12

GND

CVBS_YIN-9

<P_current><P_volt>

SOT23

VIVO:TV_OUT

CVBS_YIN-4

<P_current><P_volt>

SOT23

VIVO:TV_OUT

5V

3

A3V3

3

1 2

7

GND

A3V3

9

8

GND

GND

1 2

5

1 2

101112

1 2

GND

CGND GND

3

3

12

3

12

GND

GND

5V

3

GND

A3V3

4

6

3

CIN-9CVBS_YIN-9

3

GND

CIN*{15}

1 2

12

1 2

GND

1 2

12

1 2

1 2

CIN{15}

CIN*

GND

GND

CIN

1 21 2

12

1 2

GND GND

12

GND

CIN-9

A3V3

GNDGND GND

CIN-4

A3V3

3

VIVO:TV_OUT

<P_current>

<P_volt>

3

VIVO:TV_OUT

<P_current>

<P_volt>

SOT23

I2CC_SCL {8,15,18}

I2CC_SDA{8,15,18}

MINIDIN_Y_CVBSOUT {10}

12

GND

SOT23

12

GND

CIN-4

CVBS_YIN-4

<P_volt>

<P_mat>

12

NO_STUFF

C0603MS

<P_tol>

<P_volt>

<P_mat>

12

NO_STUFF

C0603MS

<P_tol>

1

2

3

4

GND

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

VIDEO IN/OUT CONNECT

Tuesday, September 03, 2002

Date:

16 18

Sheet of

100

Page 17

POWER SUPPLY

ANALOG 3V3

5V

12

1 2

12

12

GND

GND GND

Vout = VRef * (1+Rbot/Rtop)

3.31V = 1.25V * (1+(165/100))

12V 5V

TMDS 3V3 Supply

13

3V3

12

12

GND

1 2

12

GND GND

23

4

1

12

A3V3

12

12

GND

5V

1 2

12

GND

12

GND

3.31V = 1.25V * (1+(165/100))

13

A3V3

12

23

4

12

1

12

12

GND

12

12

GND

GND

3V3TMDS

12

12

GND

GND

TMDS PLL Supply

5V

1

3 4

12

12

GND

GND GND GND

Vout = VRef * (1+Rtop/Rbot)Vout = VRef * (1+Rbot/Rtop)

3.31V = 1.175V * (1+(100/182))

3V3TMDS

12

5

12

2

12

TMDSPLLVDD

12

12

GND

GND

NVVDD A3V3 3V3

TMDSPLLVDD

3V3TMDS{13}

FBVDD{18}

3V3_F

12V_F

5V_FUSED

DDC_5V{11,12,1 4}

SW_12V

SW_5V

DR_HI

DR_LO

SW_FB

SW_COMP

A3V3_ADJ

3V3TMDS_ADJ

TMDSPLL_ADJ

DDC 5V

NET_PHYSICAL_TYPENET

12

12

12

12

VOLTAGE

DDC_5V

NVDD-SWITCHER / FBVDD-LDO CONTROLER ISL6529

12

FBVDDQ

12

GND

1

1

2

3

GND

ISL6529

GND GND

3V3

1

2

3

D

D

S

12

12

1

12

1

GND

GND

FBVDDQ = VRef * (1+Rtop/

Rbot)

2.5V = 0.800V * (1+2.4k/1.13k)

G

1 2

12

GND

1 2

1 2

1 2

1 2

3V3

12

12

GND

1 2

5V

GND

2.5V = 1.250V * (1+ 100/ 100)SC2610

ISL6529

2.8V = 0.800V * (1+2.67k/1.07k)

GND5VGND

12

GND

12

12V

4

5

6

2

3

7

8

11

12

2

1 2

13

14

1

9

10

1

3

GND

12

13

12

2

GND

1 2

1 2

4

8

7

1

6

5

3

GND

1 2

12

3V3

12

GND

1

12

1 2

R591

12

2.2

C4

2200p

GND

1 2

1 2

ISL6529

SC2610

5V

12

3

13

2

GND

NVVDD = VRef * (1+Rtop/ Rbot)

1.656V = 0.800V * (1+1070/1000)

1.656V = 0.800V * (1+1070/1000)

ALTERNATIVE TO ISL6529

5

2

10

12

12

12

3

1

2

1

12

12

12

1

12

12

12

1

12

GND

12

6

GND

GND

12

GND

12

GND

NVVDD

2

GND

2

GND

9

8

7

1

3

4

1

3

1

3

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

POWER SUPPLY

Date:

Tuesday, September 03, 2002

Sheet of

17 18

100

Page 18

MECHANICS

1

CGND

1 11

1

1

H/W Monitor Funtion

1

1

1

FBVDD

FBVDD_ADJ

3V3

FBVDD

5V

VOLTAGENET NET_PHYSICAL_TYPE

V1

V2

V3

VOLTAGE SENSORING CIRCUIT

3V3

FANIN1

1

FANIN1/GPIO1

2

FANIN2/GPIO2

PWMOUT1

3

PWMOUT1

4

PWMOUT2

5

GPIO5

6

GPIO6

7

SMI#/GPIO7

8

OVT#/GPIO8

9

I2CC_SCL

I2CC_SCL{8,15,16}

I2CC_SDA{8,15,16}

Place close

together

south-west

of GPU

3V3

PWMOUT1

PWM1 Circuit for FAN1 speed Control

FOR 12V FAN

I2CC_SDA

SCL

10

SDA

B

E C

GND

GND

GND

FBVDD

GND

VCC

VTIN1

VTIN2

VREF

VCORE/GPIO16

+1.5V/GPIO15

+2.5V/GPIO14

GPIO13

GND

TEMP_FAULT#/GPO11

EC

B

1

2

GND

3

12V

1

2

3

NVVDD

FBVDDQ

20

19

18

17

16

15

14

13

12

11

( 1.6V )

VTIN1

VREF

V1

V2

V3

GP13

GND

3V3

1 2

1 2

1 2

1 2

FBVDD Supply

3V3

3V3

GND

GND

5V

12

12

FBVDD = VRef * (1+Rbot/ Rtop)

FANIN1

FAN+ {8}

FAN- {8}

GND

GND

3.315V = 1.250V * (1+ 165/ 100)

3.300V = 1.250V * (1+ 187/ 115)

13

23

4

12

12

12 1

12

1

12

1

1

1

12

2

3

GNDGNDGND GNDGNDGND

GND

Micro-Star International Co., LTD.

MS-8891 base on C116 Modify

Size Document Number Rev

Custom

Date:

MECHANICS

Tuesday, September 03, 2002

18 18

Sheet of

100

Loading...

Loading...