Page 1

A

B

C

D

E

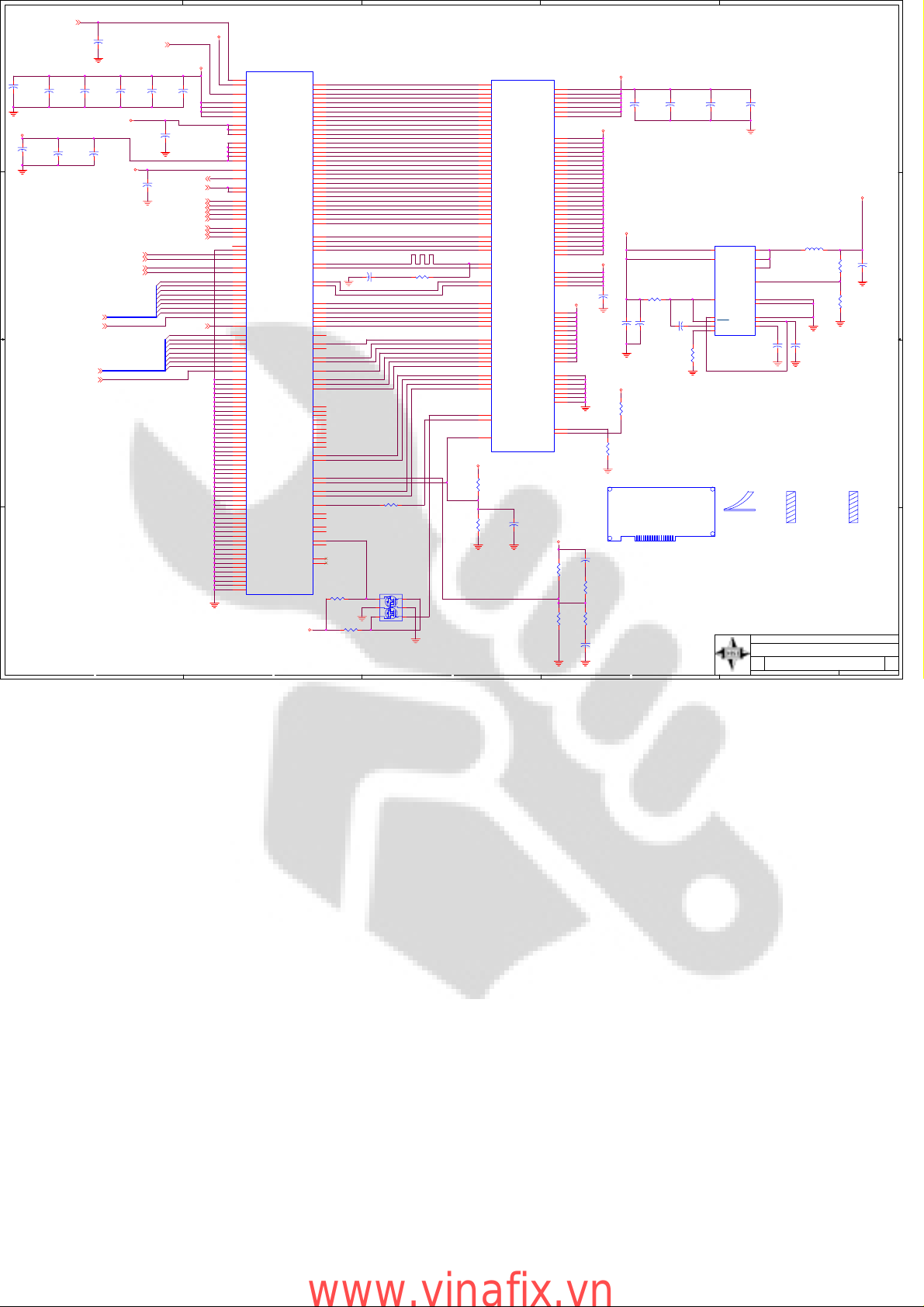

NV11, 1/2/4MX32 DDR, RGB, INTERNAL DVI-I, TV, AGP.

PCI DEVICE ID 0X0=0X112 FOR NV11.

4 4

01. List of Schematic sheets

02. HOST INTERFACE_NEW

03. FB(MEMORY)/NVXX DECOUPLING

04. NVXX BOOT STRAPS

05. DAC and MEDIA PORT

06. LOWER SDRAM FBI

07. BT & CH TV ENCODER

08. DFP/DVI/CLK_DVR

09. DC-DC CONVTR

3 3

STRAPS: AGP4X, SIDEBAND DIS, FAST WRITE ENA, ADP BIOS, NORMAL PCIAD, 14.318MHZ

STRAP_RAM_TYPE [5:2]=1011-1MX32 DDR SDRAM

5) E00:

- Implemented ECO change list "P41_D00_ECOs-X02.doc" in

current working directory:

\\nvcorp\applied\designs\working\nv11\XXX-P0041-0000-E00

- Sync'd up netlist with Layout.

- Connect the S0 input of the IMISM530 to 3.3VRUN instead of CLK_VDD

6) E02:

- Added 1000pf cap (C535) in parallel to R535 for EMI supression.

- Changed mem termination from +3.3VRUN to +3.3VSUS. Affects R183-R186, C416

6a) E02-X01: Change C279 to no stuff per Dell request.

7) E03: Added SMD0603 foot print to the backside of board, C536 to DVI, DFP page.

HISTORY REV. :

1) Based on P39-A00

2) Schematic changes; role rev to B00

-remove BT device

-strap resistor changes

-add/remove resistors and caps

-remove high dropout reg (u514)

- R502 changed from 20K to 10K

3) C00:

- Swapped LVDS signals back to "Rev A connections".

- Hi Freq. cap arrays Decoupled to GND:

1) SMB_CLK

2) SMB_DAT

3) PID2_I2C_CLK (aka I2CSCL)

4) PID3_I2C_DAT (aka I2CSDA)

5) PID3_I2CDAT (aka PID3)

6) PID2_I2CCLK (aka PID2)

2 2

7) PID1

8) PID0

- Added 10K, NO STUFF, from AGP_BUSY# to +3.3VSUS.

- Connected C279 to +5VSUS.

4) D00:

A) Power U513 from +3.3vsus instead of +3.3vrun.

B) Changed R68 to 10K. Change R69 to 9.09K (to decrease static current draw in +2.5v regulator circuit)

C) (layout change) Moved MVREF divider & caps (R172, R175, C424, C426) next to the RAMs

D) Added 0-Ohm STUFF OPTION resistors for memory core FBVDD to go from either +3.3VSUS or +2.5V.

E) Moved C836, C837, C247, C248, C270 to FBVDD

F) Removed R166 & R126 (DFPCLK is unused)

G) Moved pin 1 of R501 from +5vsus to +5vrun

H) (layout change) Split 5vsus bus into +5vrun and +5vsus

I) Added a NOSTUFF zero ohm resistor from DFP3.3V to +3.3VRUN (adds option to remove dfp regulator

J) Added a .022uF cap in parallel with R550 (Increase power sequencing delay)

K) Changed C57 to 330uF, d-size case

L) Changed C828 is 330uF, d-size case

M) (layout change) Moved IMI530 part (designator u1) to fix shorting problem

N) (layout change) Connected J1 connector shield to ground

O) (layout change) Connected mounting holes to ground. Don't plate inside of hole to allow for pimnut

Q) Route VDDEN (GPIO3) to pin 166 on connector J10 (FPVCC)

P) Added 2 Standoffs (1 metal, 1 plastic) and thermal pad per Dell's request.

R) Connected pin 24 of J10 (ZV_PCLK) to pin B4 (VIPPCLK) on U29 (NV11)

S) Created +5VRUN net, connect to pin 168 on J10 (+5VRUN)

1 1

T) R155 = 357ohm, R150 is no-stuff

U) Removed R152. Connected CHTVPIO_1 to CHTVPIO_0.

V) Adjusted PCB form factor

W) Changed R548 from 400K 5% to standard 390K 5%

X) Changed R550 from 600K 5% to standard 620K 5%

Y) Configured memory to 2Mx32-1001b (R524=NO STUFF, R523= STUFF

Z) Changed R154, R156 to 10K.

Micro-Star International Co., L TD .

MS8832,1/2/4MX32-DDR,TV

{Item}\t{Quantity}\t{Reference}\t{USR DFINE}\t{PN}\t{Assembly}\t{Value}

{Assembly}{Source Package} {Value}{PN}{AVL1}{AVL2}{AVL3}{AVL4}{AVL5}

A

B

C

D

Size Document Number Rev

C

Date:

Tuesday, April 30, 2002

List of schematic sheets

Sheet of

E

19

100

www.vinafix.vn

Page 2

8

7

6

5

4

3

2

1

U902

4

D_C

AVdd

5

STOP

DVdd

10

SSON

LF

6

S0

9

Fout

S1

14

S2

11

REFout

S3

17

R0

16

D D

R1

1

OVdd

OSCin

2

OVss

OSCout

AVss

DVss

IMISM530ATB

C C

B B

U900

3

4

12

5

10

7

6

15

9

14

20

11

17

16

19

1

18

2

8

13

IMISM530ATB

D_C

STOP

SSON

S0

S1

S2

S3

R0

R1

OSCin

OSCout

REFout

3

AVdd

12

DVdd

7

LF

15

Fout

20

19

OVdd

18

OVss

8

AVss

13

DVss

4

5

10

6

9

14

11

17

16

1

2

U901

D_C

STOP

SSON

S0

S1

S2

S3

R0

R1

OSCin

OSCout

IMISM530ATB

REFout

3

AVdd

12

DVdd

7

LF

15

Fout

20

19

OVdd

18

OVss

8

AVss

13

DVss

A A

Title

<Title>

Size Document Number Rev

<Doc> <RevCode>

C

8

7

6

5

4

3

Date: Sheet

2

11Tuesday, April 30, 2002

of

1

www.vinafix.vn

Page 3

A

+12V8

12

C141

+5VALW8

1uF

12

C94

4 4

10uF

+3.3VSUS

12

C79

10uF

In all cases each capacitor should be low

ESR/ESL and placed as close as possible to

the respective rail connector pin(s).

3 3

2 2

1 1

12

12

C85

C84

0.01UF

0.01UF

12

12

C82

C81

0.022uF

0.022uF

ZV_UV[7:0]5

ZV_VSYNC5

ZV_Y[7:0]5

ZV_HREF5

A

+5VSUS

+3.3VRUN

12

12

C92

C87

0.01UF

0.022uF

12

C83

0.022uF

SMB_CLK8

SMB_DAT8

DDC_CLK5

DDC_DAT5

+5VRUN

+5VALW

VDDQ

12

C93

0.01UF

12

C80

0.1uF

VDDEN8

PWR_SRC8

VSYNCR5

HSYNCR5

RED5

GREEN5

BLUE5

TVY7

TVC7

CVBS7

ZV_UV0

ZV_UV1

ZV_UV2

ZV_UV3

ZV_UV4

ZV_UV5

ZV_UV6

ZV_UV7

ZV_PCLK5

ZV_Y0

ZV_Y1

ZV_Y2

ZV_Y3

ZV_Y4

ZV_Y5

ZV_Y6

ZV_Y7

164

168

172

28

49

93

128

161

163

165

169

171

173

177

170

166

176

178

125

129

133

137

141

145

149

153

158

156

154

152

148

146

17

5

15

9

11

7

13

3

19

24

18

8

16

10

12

6

14

4

20

1

2

21

22

25

26

32

35

41

42

51

52

61

62

67

68

73

74

81

82

89

90

99

100

107

108

113

114

119

120

123

127

130

131

135

139

140

143

147

150

151

155

159

160

167

174

179

180

J10

+12V

+5VRUN

+5VALW

VDDQ0

VDDQ1

VDDQ2

VDDQ3

+5VSUS0

+5VSUS1

+5VSUS2

3.3VSUS0

3.3VSUS1

3.3VSUS2

3.3VSUS4

+3VRUN

FPVCC

PWR_SRC0

PWR_SRC1

VSYNC

HSYNC

VGA_RED

VGA_GRN

BGA_BLU

TV_Y

TV_C

TV_CVBS

PWR_OK

TYPE_DET#

SMB_CLK

SMB_DAT

CLK_DDC2

DAT_DDC2

ZV_UV0

ZV_UV1

ZV_UV2

ZV_UV3

ZV_UV4

ZV_UV5

ZV_UV6

ZV_UV7

ZV_VSYNC

ZV_PCLK

ZV_Y0

ZV_Y1

ZV_Y2

ZV_Y3

ZV_Y4

ZV_Y5

ZV_Y6

ZV_Y7

ZV_HREF

GND0

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

GND17

GND18

GND19

GND20

GND21

GND22

GND23

GND24

GND25

GND26

GND27

GND28

GND29

GND30

GND31

GND32

GND33

GND34

GND35

GND36

GND37

GND38

GND39

GND40

GND41

GND42

GND43

GND44

GND45

GND46

GND47

QT01NNNA-*120

B

GC_SUSPEND#

B

C/BE0#

C/BE1#

C/BE2#

C/BE3#

CLK66_AGP

FRAME#

TRDY#

DEVSEL#

STOP#

SBSTB

SBSTB#

ADSTB1

ADSTB1#

VREFGC

VREFCG

ADSTB0

ADSTB0#

STP_AGP#

GC_STNDBY#

M_ID2#

M_SEN#

AGP_BUSY#

CLKRUN#

+3.3VSUS

C

118

AD0

121

AD1

116

AD2

117

AD3

112

AD4

115

AD5

110

AD6

105

AD7

106

AD8

103

AD9

104

AD10

101

AD11

102

AD12

97

AD13

98

AD14

95

AD15

86175

AD163.3VSUS3

84

AD17

78

AD18

85

AD19

76

AD20

83

AD21

72

AD22

80

AD23

70

AD24

77

AD25

66

AD26

75

AD27

64

AD28

65

AD29

60

AD30

63

AD31

122

96

79

59

23

48

RST#

126

GNT#

27

REQ#

58

53

IRDY#

55

46

57

124

PAR

47

PME#

87

INTA#

88

INTB#

54

RBF#

56

WBF#

50

PIPE#

29

ST0

30

ST1

31

ST2

34

SBA0

36

SBA1

33

SBA2

38

SBA3

43

SBA4

40

SBA5

45

SBA6

44

SBA7

37

39

71

69

92

91

111

109

136

134

132

142

144

94

138

157

NC0

162

NC1

R553

1 2

10K

NO STUFF

R_AGPST0P_L

AGP_BUSY_L

R502

1 2

10K

C834

56pF

PCICLK_RC

12

PCIINTAJ

AGPRBFJ

AGPWBFJ

AGPPIPEJ

R507

300

U16

FDC6301N

413

5

6

R_3.3VSUS

PCIAD0

PCIAD1

PCIAD2

PCIAD3

PCIAD4

PCIAD5

PCIAD6

PCIAD7

PCIAD8

PCIAD9

PCIAD10

PCIAD11

PCIAD12

PCIAD13

PCIAD14

PCIAD15

PCIAD16

PCIAD17

PCIAD18

PCIAD19

PCIAD20

PCIAD21

PCIAD22

PCIAD23

PCIAD24

PCIAD25

PCIAD26

PCIAD27

PCIAD28

PCIAD29

PCIAD30

PCIAD31

PCICBE0J

PCICBE1J

PCICBE2J

PCICBE3J

PCICLK

PCIRSTJ

12

PCIGNTJ

PCIREQJ

R545

75

PCIFRAMEJ

PCIIRDYJ

PCITRDYJ

PCIDEVSELJ

PCISTOPJ

PCIPAR

AGPST0

AGPST1

AGPST2

AGPADSTB1

AGPADSTB1J

AGPADSTB0

AGPADSTB0J

AGPBUSY_L

AGPST0P_L

AGPVREFCG

12

AGPVREFGC

2

U29A

AJ28

PCIAD0

AH27

PCIAD1

AK26

PCIAD2

AJ27

PCIAD3

AG24

PCIAD4

AH26

PCIAD5

AK24

PCIAD6

AK27

PCIAD7

AH24

PCIAD8

AK23

PCIAD9

AK25

PCIAD10

AH23

PCIAD11

AG23

PCIAD12

AK22

PCIAD13

AH22

PCIAD14

AJ22

PCIAD15

AG19

PCIAD16

AH19

PCIAD17

AJ19

PCIAD18

AG18

PCIAD19

AJ18

PCIAD20

AK19

PCIAD21

AH18

PCIAD22

AJ16

PCIAD23

AK17

PCIAD24

AK16

PCIAD25

AH15

PCIAD26

AJ15

PCIAD27

AH14

PCIAD28

AG15

PCIAD29

AG14

PCIAD30

AK14

PCIAD31

AJ24

PCICBE#0

AG22

PCICBE#1

AK21

PCICBE#2

AK18

PCICBE#3

AG16

PCICLK

AK15

PCIRST#

AH11

PCIGNT#

AK11

PCIREQ#

AH20

PCIFRAME#

AG20

PCIIRDY#

AK20

PCITRDY#

AG21

PCIDEVSEL#

AH21

PCISTOP#

AJ21

PCIPAR

AH16

PCIINTA#

AH12

AGPRBF#

AH13

AGPWBF#

AG13

AGPPIPE#

AG12

AGPST0

AJ12

AGPST1

AK12

AGPST2

AG17

AGPADSTB1

AH17

AGPADSTB1#

AH25

AGPADSTB0

AJ25

AGPADSTB0#

AK13

AGPBUSY#

AJ13

AGPSTOP#

AK28

AGPVREF

A01

VDDQ

12

R78

301K

12

R77

221K

C

AE24

VDDQ

AF11

VDDQ

AF13

VDDQ

AF18

VDDQ

AF20

VDDQ

AF24

VDDQ

AG25

VDDQ

AA26

VDD

AF10

VDD

AF12

VDD

AF19

VDD

AF21

VDD

AF23

VDD

E10

VDD

E11

VDD

E12

VDD

E13

VDD

E18

VDD

E19

VDD

E20

VDD

E21

VDD

K5

VDD

K26

VDD

L5

VDD

L26

VDD

M5

VDD

M26

VDD

N26

VDD

V5

VDD

V26

VDD

W5

VDD

W26

VDD

Y5

VDD

Y26

VDD

AA5

VD50CLAMP

AB5

VD50CLAMP

AF8

VD50CLAMP

F6

VD50CLAMP

+3.3VSUS

AD5

VDD33

AD6

VDD33

AE4

VDD33

AE5

VDD33

AE7

VDD33

AF4

VDD33

AF6

VDD33

AF7

VDD33

AG5

VDD33

AG6

VDD33

G5

VDD33

H5

VDD33

N5

GND

P4

GND

P29

GND

U2

GND

U29

GND

Y2

GND

Y29

GND

AK2

TESTMODE0

AK29

TESTMODE1

12

C145

0.1uF

NO STUFF

VDDQ

12

R157

1.5K

12

R159

1.5K

NVVDD

+5VSUS

TEST0

TEST1

12

C320

470pF

AGPVREF1

12

R158

75

12

R160

75

AGPVREF2

12

C321

470pF

12

C423

0.1uF

C17

10uF

12

R65

10K

PCB1000

VDDQ

+3.3VSUS

+3.3VSUS

1 2

12

R171

10K

D

12

D

C127

0.1uF

R112

10

12

C324

0.1uF

(PER FAB DWG)

E

12

12

C128

0.1uF

REG5V

12

C325

CMP

1 2

TOFF

470pF

R168

180K

1 2

12

C130

C131

0.1uF

0.1uF

U4

2

IN_1

4

IN_2

12

VCC

11

FBSEL

1

SHDN

6

COMP

7

TOFF

MAX1644EAE

2A

THERMAL

INTERFACE PAD FOR P41

NVXX HOST INTERFACE

NVVDD_L

3

LX_1

14

LX_2

16

LX_3

ADJ

8

FB

13

PGND_1

15

PGND_2

9

GND

REF

10

REF

SS

5

SS

12

C326

0.01UF

M7

M5

STANDOFF

METAL FOR P41

Micro-Star International Co., L TD .

MS8832,1/2/4MX32-DDR,TV

Size Document Number Rev

C

Tuesday, April 30, 2002

Date:

Note: R11 18.2K = 1.5V

R11 36.5K = 1.9V

L29 6.8uH

1 2

R11

18.2K

R9

49.9K

12

C327

1uF

HOST INTERFACE_NEW

E

NVVDD

12

12

12

M6

STANDOFF

PLASTIC FOR P41

Sheet of

+

C57

330uF R040

29

100

www.vinafix.vn

Page 4

8

7

6

5

4

3

2

1

NV11 DECOUPLING

+2.5V +3.3VSUS

C430

1

8

2

7

3

6

4

D D

+2.5V

C C

5

0.1uF

+2.5V

C434

1

8

2

7

3

6

4

5

0.1uF

+2.5V+2.5V

C833

1

8

2

7

3

6

4

5

0.1uF

+3.3VSUS

12

C431

10uF

+3.3VSUS

C435

1

8

2

7

3

6

4

5

0.1uF

+3.3VSUS+3.3VSUS

C832

1

8

2

7

3

6

4

5

0.1uF

12

12

C432

C433

10uF

10uF

NVVDD

NVVDD

NVVDD

C428

1

2

3

4

0.1uF

C427

1

2

3

4

0.1uF

C429

1

2

3

4

0.1uF

NVVDD

8

7

6

5

NVVDD

8

7

6

5

8

7

6

5

NVVDD

NVVDD

12

NVVDD

C437

1

8

2

7

3

6

4

5

0.1uF

12

12

12

C439

C438

10uF

10uF

12

C246

0.1uF

C440

10uF

12

C264

C274

0.1uF

0.1uF

FB (MEMORY) DECOUPLING

+3.3VSUS

12

12

C252

C254

2200pF

0.1uF

12

B B

12

C261

C271

2200pF

0.1uF

FBVDD

12

12

12

C836

10uF

12

12

C837

0.1uF

10uF

C270

C247

C248

2200pF

0.1uF

+2.5V

12

12

12

12

12

12

12

12

C249

C250

C251

C253

C255

C256

2200pF

0.1uF

0.1uF

2200pF

0.1uF

12

C262

0.1uF

12

C275

2200pF

12

12

C265

C263

2200pF

0.1uF

12

12

C277

C276

0.1uF

2200pF

12

12

C267

C266

0.1uF

0.1uF

12

C278

0.1uF

C257

2200pF

0.1uF

12

12

C269

C268

2200pF

2200pF

12

C258

C260

0.1uF

0.1uF

12

C273

2200pF

12

12

C838

C839

10uF

10uF

A A

FB/NVXX DECOUPLING

8

7

6

5

4

3

Micro-Star International Co., L TD .

MS8832,1/2/4MX32-DDR,TV

Size Document Number Rev

C

Date:

2

Tuesday, April 30, 2002

FB/NVXX Decoupling

Sheet of

1

39

100

www.vinafix.vn

Page 5

5

D D

DFPD[11:0]8

4

R503 10K

1 2

NO STUFF

R505 10K

1 2

DFPD2

R504 10K

DFPD1

R506 10K

1 2

1 2

NO STUFF

+3.3VSUS

DFPD[2:1] PCI_DEV_ID

PCI_DEV_ID (0x0) = 0x112

3

2

1

TVED[11:0]5,7

C C

B B

A A

5

TVED11

R517 10K

1 2

NO STUFF

R519 10K

1 2

NO STUFF

R521 10K

1 2

R523 10K

1 2

R525 10K

1 2

NO STUFF

R527 10K

1 2

4

TVED1

R509 10K

TVED6

R518 10K

TVED5

R520 10K

TVED4

R522 10K

TVED3

R524 10K

TVED2

R526 10K

TVED0

R529 10K

1 2

1 2

1 2

1 2

NO STUFF

1 2

NO STUFF

1 2

1 2

TVED[11] STRAP_HOST=1 : AGP Mode

TVED[6] STRAP_CRYSTAL

STRAP_CRYSTAL=1 : 14.31818MHz

TVED[5:2] STRAP_RAM_TYPE

1001 = 2MX32 DDR SDRAM

TVED[1] STRAP_SUB_VENDOR

STRAP_SUB_VENDOR=0 : Adaptor BIOS

TVED[0] STRAP_AD_SWAP

STRAP_AD_SWAP=1 : PCIAD bus [31:0] normal

3

NVXX HOST STRAPS

2

Micro-Star International Co., L TD .

MS8832,1/2/4MX32-DDR,TV

Size Document Number Rev

C

Date:

Tuesday, April 30, 2002

NVXX BOOT STRAPS

Sheet of

1

49

100

www.vinafix.vn

Page 6

A

ZV_UV[7:0]2

ZV_Y[7:0]2

4 4

ZV_VSYNC2

ZV_HREF2

DACVDD

12

C143

3 3

2 2

0.01UF

BUFFRSTJ7

TVEVSYNC7

TVEHSYNC7

TVED[11:0]4,7

TVECLKOUT7

TVECLKIN7

REF_OUT7,8

FREQ_OUT8

ZV_UV2

ZV_UV3

ZV_UV4

ZV_UV5

ZV_UV6

ZV_UV7

12

C144

0.01UF

COMP

VREF

RSET

12

R75

113R

BUFFRSTJ

R90 33

TVECLKOUTR

12

U29D

AG7

DDCSCL

AH5

DDCSDA

AH6

I2CSCL

AK5

I2CSDA

A8

VIPHCLK

B7

VIPHCTL

A4 D1

VIPHAD0 VIPD6

C4

VIPHAD1

AC3

VIPHAD2

AC4

VIPHAD3

C8

VIPHAD4

AK3

VIPHAD5

AH1

VIPHAD6

AD4

VIPHAD7

AK9

DACVDD

AK8

PLLVDD

AG11

DACCOMP

AK10

DACVREF

AJ10

DACRSET

AJ9

DACGND

B10

BUF_RST#

AE1

TVVSYNC

AD3

TVHSYNC

TVED0

AJ4

TVD0

TVED1

AK4

TVD1

TVED2

AH4

TVD2

TVED3

AJ3

TVD3

TVED4

AG1

TVD4

TVED5

AG2

TVD5

TVED6

AE2

TVD6

TVED7

AE3

TVD7

TVED8

AF3

TVD8

TVED9

AF1

TVD9

TVED10

AG3

TVD10

TVED11

AH2

TVD11

AD1

TVCLKOUT

AD2

TVCLKIN

A01

VIPPCLK

DACRED

DACGREEN

DACBLUE

VIDHSYNC

VIDVSYNC

XTALSOUT

XTALSIN

XTALOUTXTALIN

DDC_DATR

VIPD0

VIPD1

VIPD2

VIPD3

VIPD4

VIPD5

VIPD7

VIPD8

VIPD9

B4

H3

F1

H4

G2

E1

G3

F2

F3

G4

AG10

AH10

AH9

AG8

AH7

AH8

AG9

AJ7AK7

DDC_CLKR

ZV_PCLK 2

B

C_I2CSDA

C_I2CSCL

ZV_Y0

ZV_Y1

ZV_Y2

ZV_Y3

ZV_Y4

ZV_Y5

ZV_Y6

ZV_Y7

ZV_UV0

ZV_UV1

C

+5VSUS

+5VSUS

12

12

R8

R7

2K

2K

Place close

to NV11

RP6

1

8

2

7

3

6

4

5

100R

+5VSUS +5VSUS +5VSUS +5VSUS

R27 33 NO STUFF

1 2

RED

GREEN

BLUE

HSYNC

VSYNC

147

U14E

11 10

TSSOP14

B_HSYNC

147

U14F

13 12

TSSOP14

147

U14A

1 2

TSSOP14

B_VSYNC

DDC_CLKS

DDC_DATS

147

U14B

3 4

TSSOP14

D

+5VSUS +5VSUS

Q7

12

1

2

HSYNCB

VSYNCB

1 2

R28 33 NO STUFF

R18

2K

1 2

1 2

R161 33

R162 33

3

BSS138

Q8

BSS138

12

1

R31

2K

3

2

DDC_DAT 2

DDC_CLK 2

I2CSDA 7,8

I2CSCL 7,8

HSYNCR

VSYNCR

E

HSYNCR 2

VSYNCR 2

RED 2

GREEN 2

BLUE 2

VCC+5VSUS

Single point connection to DAC

output reference GND

+3.3VRUN

L20

1 2

1 1

150-220R_100MHZ

12

C129

10uF

DACVDD

12

12

C142

C140

0.1uF

0.001UF

DAC and MEDIA PORT

A

B

C

D

+5VSUS

147

U14D

9 8

TSSOP14

Micro-Star International Co., L TD .

MS8832,1/2/4MX32-DDR,TV

Size Document Number Rev

C

Date:

Tuesday, April 30, 2002

DAC and MEDIA PORT

Sheet of

E

59

100

www.vinafix.vn

Page 7

A

FBD23

FBD22

FBD21

FBD20

FBD19

FBD18

FBD17

FBD16

FBD15

FBD14

FBD13

FBD12

FBD11

4 4

3 3

2 2

1 1

FBD10

FBD9

FBD8

FBD31

FBD30

FBD29

FBD28

FBD27

FBD26

FBD25

FBD24

FBD7

FBD2

FBD5

FBD4

FBD3

FBD6

FBD1

FBD0

FBD39

FBD38

FBD37

FBD36

FBD35

FBD34

FBD33

FBD32

FBD62

FBD63

FBD61

FBD60

FBD59

FBD58

FBD57

FBD56

FBD47

FBD46

FBD45

FBD44

FBD43

FBD42

FBD41

FBD40

FBD55

FBD53

FBD54

FBD52

FBD51

FBD50

FBD49

FBD48

U22

97

DQ0

98

DQ1

100

DQ2

1

DQ3

3

DQ4

4

DQ5

6

DQ6

7

DQ7

60

DQ8

61

DQ9

63

DQ10

64

DQ11

68

DQ12

69

DQ13

71

DQ14

72

DQ15

9

DQ16

10

DQ17

12

DQ18

13

DQ19

17

DQ20

18

DQ21

20

DQ22

21

DQ23

74

DQ24

75

DQ25

77

DQ26

78

DQ27

80

DQ28

81

DQ29

83

DQ30

84

DQ31

38

NC

39

NC

40

NC

41

NC

42

NC

43

NC

44

NC

87

NC

88

NC

89

NC

90

NC

91

NC

93

NC/RFU

DDR 6

U24

97

DQ0

98

DQ1

100

DQ2

1

DQ3

3

DQ4

4

DQ5

6

DQ6

7

DQ7

60

DQ8

61

DQ9

63

DQ10

64

DQ11

68

DQ12

69

DQ13

71

DQ14

72

DQ15

9

DQ16

10

DQ17

12

DQ18

13

DQ19

17

DQ20

18

DQ21

20

DQ22

21

DQ23

74

DQ24

75

DQ25

77

DQ26

78

DQ27

80

DQ28

81

DQ29

83

DQ30

84

DQ31

38

NC

39

NC

40

NC

41

NC

42

NC

43

NC

44

NC

87

NC

88

NC

89

NC

90

NC

91

NC

93

NC/RFU

DDR 6

A

FBD[63:0]

FBAA0

31

A0

FBAA1

32

A1

FBAA2

33

A2

FBAA3

34

A3

FBAA4

47

A4

FBAA5

48

A5

FBAA6

49

A6

FBAA7

50

A7

FBAA8

51

A8/AP

FBAA9

45

A9

FBAA10

36

A10

FBAA11

37

A11

FBABA0

29

BA0

FBABA1

30

BA1

FBDQM2

23

DQM0

FBDQM1

56

DQM1

FBDQM3

24

DQM2

FBDQM0

57

DQM3

FBACLK0

55

CLK

FBACLK0_

54

CLK_L

FBACKE

53

CKE

FBARASJ

27

RAS_L

FBACASJ

26

CAS_L

FBAWEJ

25

WE_L

FBACS0J

28

CS_L

52

DSF

58

Vref

FBDQSD1

94

DQS

15

VDD

3.3V

VDD

Power

VDD

VDD

VDDQ

2.5V

VDDQ

Power

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

3.3V

VSS

GND

VSS

VSS

VSSQ

2.5V

VSSQ

GND

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

A8/AP

DQM0

DQM1

DQM2

DQM3

CLK

CLK_L

CKE

RAS_L

CAS_L

WE_L

CS_L

DSF

DQS

VDD

3.3V

VDD

Power

VDD

VDD

VDDQ

2.5V

VDDQ

Power

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

3.3V

VSS

GND

VSS

VSS

VSSQ

2.5V

VSSQ

GND

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

FBVDD

35

65

96

2

+2.5V

8

14

22

59

67

73

79

86

95

16

46

66

85

5

11

19

62

70

76

82

92

99

FBAA0

31

A0

FBAA1

32

A1

FBAA2

33

A2

FBAA3

34

A3

FBAA4

47

A4

FBAA5

48

A5

FBAA6

49

A6

FBAA7

50

A7

FBAA8

51

FBAA9

45

A9

FBAA10

36

A10

FBAA11

37

A11

FBABA0

29

BA0

FBABA1

30

BA1

FBDQM4

23

FBDQM7

56

FBDQM5

24

FBDQM6

57

FBACLK1

55

FBACLK1_

54

FBACKE

53

FBARASJ

27

FBACASJ

26

FBAWEJ

25

FBACS0J

28

52

58

Vref

FBDQSD5

94

15

FBVDD

35

65

96

2

+2.5V

8

14

22

59

67

73

79

86

95

16

46

66

85

5

11

19

62

70

76

82

92

99

R187 15R

1 2

R190 15R

1 2

B

MVREFA0

12

C424

0.1uF

FBAA[11:0]

FBDQM[7:0]

12

C426

0.1uF

FBAWEJ

FBACS0J

FBACASJ

R183 270R

12

+3.3VSUS +3.3VSUS

NO STUFF

12

R185 270R

NO STUFF

R194 270R

NO STUFF

12

12

R195 270RNO STUFF

B

RP4 22R

4

3

2

1

6" LENGTH

ON PCB

FBAA0

FBAA1

FBAA2

FBAA3

FBAA5

FBAA4

FBAA6

FBAA7

FBAA8

FBAA9

FBAA10

FBABA0

FBABA1

5

6

7

8

R184 169R

R186 169R

R_CFBDQS1

R193 357R

R196 357R

+2.5V

R172

1 2

R175

1 2

RP1 22R

4

5

3

6

2

7

1

8

RP2 22R

4

5

3

6

2

7

1

8

4

5

3

6

2

7

1

8

RP3 22R

R178 22R

1 2

R179 22R

1 2

R539 22R

1 2

CFBAWEJ

CFBACS0J

CFBACASJ

CFBACKEFBACKE

12

12

R188 15R

1 2

R191 15R

1 2

12

12

C

1K

1K

CFBABA0

CFBABA1

R118 15R

1 2

R180 15R

1 2

R119 15R

1 2

R181 15R

1 2

12

C416

0.1uF

NO STUFF

C

MVREFA0

CFBACS1J

CFBDQS1

CFBDQS5R_CFBDQS5

CFBAA0

CFBAA1

CFBAA2

CFBAA3

CFBAA4

CFBAA5

CFBAA6

CFBAA7

CFBAA8

CFBAA9

CFBAA10

CFBAA11FBAA11

Place

Close to

NV11

FBDQM0

FBDQM1

FBDQM2

FBDQM3

FBDQM4

FBDQM5

FBDQM6

FBDQM7

FBD0

FBD1

FBD2

FBD3

FBD4

FBD5

FBD6

FBD7

FBD8

FBD9

FBD10

FBD11

FBD12

FBD13

FBD14

FBD15

FBD16

FBD17

FBD18

FBD19

FBD20

FBD21

FBD22

FBD23

FBD24

FBD25

FBD26

FBD27

FBD28

FBD29

FBD30

FBD31

FBD32

FBD33

FBD34

FBD35

FBD36

FBD37

FBD38

FBD39

FBD40

FBD41

FBD42

FBD43

FBD44

FBD45

FBD46

FBD47

FBD48

FBD49

FBD50

FBD51

FBD52

FBD53

FBD54

FBD55

FBD56

FBD57

FBD58

FBD59

FBD60

FBD61

FBD62

FBD63

CFBARASJ

CFBACASJ

CFBACKE

CFBACLK0

CFBACLK0_

CFBACLK1

CFBACLK1_

FBVREF

12

D

U29B

AE28

FBD0

AD27

FBD1

AE30

FBD2

AE29

FBD3

AC28

FBD4

AC27

FBD5

AB27

FBD6

AC30

FBD7

AA27

FBD8

AB30

FBD9

AA29

FBD10

AA28

FBD11

Y28

FBD12

Y27

FBD13

W27

FBD14

Y30

FBD15

H28

FBD16

G29

FBD17

H30

FBD18

H27

FBD19

G30

FBD20

F30

FBD21

F29

FBD22

F28

FBD23

D30

FBD24

E28

FBD25

D28

FBD26

D29

FBD27

A29

FBD28

B28

FBD29

A28

FBD30

C27

FBD31

B24

FBD32

C24

FBD33

C23

FBD34

D23

FBD35

C22

FBD36

D22

FBD37

A22

FBD38

B22

FBD39

D18

FBD40

A18

FBD41

C17

FBD42

C18

FBD43

D17

FBD44

B16

FBD45

A16

FBD46

C16

FBD47

C13

FBD48

A13

FBD49

B12

FBD50

D13

FBD51

C12

FBD52

A11

FBD53

D12

FBD54

C11

FBD55

B3

FBD56

A3

FBD57

D3

FBD58

A2

FBD59

E3

FBD60

B1

FBD61

D2

FBD62

C1

FBD63

U30

FBAA0

U28

FBAA1

T27

FBAA2

T30

FBAA3

T29

FBAA4

T28

FBAA5

R30

FBAA6

R29

FBAA7

N28

FBAA8

P30

FBAA9

N30

FBAA10

N29

FBAA11

M27

FBAA12

M28

FBAA13

AB28

FBDQM0

AD28

FBDQM1

C30

FBDQM2

E30

FBDQM3

B19

FBDQM4

B18

FBDQM5

D11

FBDQM6

G1

FBDQM7

M29

FBARAS#

N27

FBACAS#

P28

FBAWE#

P27

FBACSO#

M30

FBACS1#

R27

FBACLK0

R28

FBACLK0#

L28

FBACLK1

L30

FBACLK1#

L27

FBACKE

AD30

FBDQS0

AA30

FBDQS1

G28

FBDQS2

C29

FBDQS3

A23

FBDQS4

A17

FBDQS5

A12

FBDQS6

C2

FBDQS7

AJ1

ROMCS#

A24

FBVREF

A01

R560

1K

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

VDD25

+2.5V

AC26

AD25

AD26

AE26

AE27

AF25

AF27

AG26

D5

D6

D25

D26

E4

E6

E7

E8

E23

E24

E25

E27

F4

F5

F24

F26

F27

G6

G25

G26

H26

A1

GND

A30

GND

AB26

GND

AC2

GND

AC5

GND

AC29

GND

AE6

GND

AE25

GND

AF2

GND

AF5

GND

AF9

GND

AF22

GND

AF26

GND

AF29

GND

AG4

GND

AG27

GND

AH3

GND

AH28

GND

AJ2

GND

AJ5

GND

AJ8

GND

AJ11

GND

AJ14

GND

AJ17

GND

AJ20

GND

AJ23

GND

AJ26

GND

AJ29

GND

AK1

GND

AK30

GND

B2

GND

B5

GND

B8

GND

B11

GND

B14

GND

B17

GND

B20

GND

B23

GND

B26

GND

B29

GND

C3

GND

C28

GND

D4

GND

D27

GND

E2

GND

E5

GND

E9

GND

E22

GND

E26

GND

E29

GND

F7

GND

F25

GND

H2

GND

H29

GND

J5

GND

J26

GND

L2

GND

L29

GND

DDR RAM/FBI

Size Document Number Rev

C

D

Date:

E

U29C

AJ30

FBD64

AH29

FBD65

AG28

FBD66

AH30

FBD67

AF28

FBD68

AG30

FBD69

AG29

FBD70

AF30

FBD71

W28

FBD72

W29

FBD73

V27

FBD74

W30

FBD75

V28

FBD76

U27

FBD77

V30

FBD78

V29

FBD79

K28

FBD80

K27

FBD81

K30

FBD82

K29

FBD83

J27

FBD84

J30

FBD85

J29

FBD86

J28

FBD87

B27

FBD88

A27

FBD89

A26

FBD90

C26

FBD91

C25

FBD92

D24

FBD93

A25

FBD94

B25

FBD95

C21

FBD96

D21

FBD97

A21

FBD98

B21

FBD99

C20

FBD100

D20

FBD101

A19

FBD102

A20

FBD103

B15

FBD104

D16

FBD105

A15

FBD106

C15

FBD107

D15

FBD108

A14

FBD109

C14

FBD110

D14

FBD111

A7

FBD112

C7

FBD113

C5

FBD114

B6

FBD115

A5

FBD116

C6

FBD117

A6

FBD118

D7

FBD119

J3

FBD120

K4

FBD121

J2

FBD122

H1

FBD123

L4

FBD124

K3

FBD125

J1

FBD126

K2

FBD127

AD29

FBDQM8

AB29

FBDQM9

G27

FBDQM10

B30

FBDQM11

C19

FBDQM12

D19

FBDQM13

D8

FBDQM14

J4

FBDQM15

B13

FBBCLK0

A10

FBBCLK1

A01

Micro-Star International Co., L TD .

MS8832,1/2/4MX32-DDR,TV

Tuesday, April 30, 2002

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

GND(thermal)

DDR RAM/FBI

E

M12

M13

M14

M15

M16

M17

M18

M19

N12

N13

N14

N15

N16

N17

N18

N19

P12

P13

P14

P15

P16

P17

P18

P19

R12

R13

R14

R15

R16

R17

R18

R19

T12

T13

T14

T15

T16

T17

T18

T19

U12

U13

U14

U15

U16

U17

U18

U19

V12

V13

V14

V15

V16

V17

V18

V19

W12

W13

W14

W15

W16

W17

W18

W19

Sheet of

69

100

www.vinafix.vn

Page 8

A

B

C

D

E

4 4

TVC

3

D10

BAT54SLT1

2

VAA3.3V

TVY

D11

BAT54SLT1

2

VAA3.3V

Parts for Chrontel

3 3

TVECLKOUT5

TVECLKIN5

I2CSCL5,8

I2CSDA5,8

BUFFRSTJ5

TVEVSYNC5

TVEHSYNC5

TVED[11:0]

2 2

TVED[11:0]4,5

REF_OUT5,8

CH7008/8A only

TVECLKOUT

CHVREF

TVECLKIN

TVED0

TVED1

TVED2

TVED3

TVED4

TVED5

TVED6

TVED7

TVED8

TVED9

TVED10

TVED11

BUFFRSTJ

TVEVSYNC

TVEHSYNC

TQFP44

VAA3.3V

U28

5

16

25

30

38

40

XCLK

41

XCLK#

37

P-OUT

27

SCLK

26

SDATA

44

D0

1

D1

2

D2

3

D3

4

D4

6

D5

7

D6

9

D7

10

D8

11

D9

12

D10

13

D11

29

RESET#

43

V

42

H

32

XI/FIN

33

XO

DS/BCO

23

31

AVDD

VDD

DVDD

DVDD

DVDD

DVDD2

TVC

21

C/G

TVY

22

Y

CVBS

20

CVBS

CH_CSYNC

17

CSYNC

15

GPIO_1

14

GPIO_0

CHVREF

39

VREF

CH_RSET

24

ISET

DGND

DGND

GND

GND

DGND

AGND

DGND

8

18

19

28

343536

12

12

R155

357R

0.1uF

CHDACVDD

12

12

C314

0.1uF

1 2

R150

75

NO STUFF

1 2

R151

75

CHTVPIO_0CHTVPIO_0

VAA3.3V

R154

10K

1 2

R156

C319

10K

1 2

L27

1 2

150-220R_100MHZ

C315

0.01UF

1 2

R144

75

NO STUFF

1 2

R145

75

NO STUFF

R153 10K

1 2

12

C318

0.1uF

+5VSUS

12

C313

10uF

12

1

3

12

1

CVBS 2

TVC 2

C296

270pF

TVY 2

C300

270pF

VAA3.3V

12

12

12

C306

0.1uF

+3.3VSUS

150-220R_100MHZ

C307

0.1uF

L28

1 2

12

C308

C309

0.1uF

0.1uF

VAA3.3V

12

12

C316

C317

10uF

0.1uF

1 1

Chrontel TV ENCODER

A

B

C

D

Micro-Star International Co., L TD .

MS8832,1/2/4MX32-DDR,TV

Size Document Number Rev

C

Date:

Tuesday, April 30, 2002

Chrontel TV ENCODER

Sheet of

E

79

100

www.vinafix.vn

Page 9

A

+3.3VRUN

D_C

SSON

12

R551

10K

Y2

14.31818MHZ

4 4

3 3

2 2

12

1 2

12

C448

C536

1000PF

NO STUFF

U1_CLKIN

U1_CLKOUT

12

C449

27pF

27pF

12

R552

10K

NO STUFF

NV_SSON

GPIO1

BCKLT_ON

VDDEN2

VDDEN

LCD_PWRGD

12

R535

10K

DFPAVCC

12

R549

10K

DFPAVCC

DFPAVCC

12

C535

1000PF

10

14

11

17

16

D10

C10

AA2

AA3

AA4

U1

4

D_C

5

STOP

SSON

6

S0

9

S1

S2

S3

R0

R1

1

OSCin

2

OSCout

IMISM530ATB

D9

C9

A9

B9

W4

V3

U1

R4

V4

U29E

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

IFP1AVCC

IFP1VREF

IFP1_RSET

IFP1AGND

IFP0VCC

IFP0VREF

IFP0_RSET

IFP0AGND

A01

AVdd

DVdd

Fout

REFout

OVdd

OVss

AVss

DVss

DFPVSYNC

DFPHSYNC

LF

I2C2SDA

I2C2SCL

I2C2SDA

I2C2SCL

DFPCLK

DFPCLK#

DFPD10

DFPD11

CLK_Vdd

TXD2#

TXD2

TXD4#

TXD4

TXD1#

TXD1

TXD3#

TXD3

TXD0#

TXD0

TXD5#

TXD5

TXD6#

TXD6

TXD7#

TXD7

TXC0

TXC0#

TXC1

TXC1#

DFPDE

DFPD0

DFPD1

DFPD2

DFPD3

DFPD4

DFPD5

DFPD6

DFPD7

DFPD8

DFPD9

3

12

7

15

20

19

18

8

13

12

FOUT

REFOUT

+3.3VSUS +3.3VSUS

AJ6

AK6

V1

V2

Y3

Y4

U3

U4

W1

Y1

T3

T4

AA1

AB1

AC1

AB2

AB3

AB4

T2

T1

W3

W2

R3

P2

P3

M3

L1

M4

M2

M1

N4

N3

N1

N2

P1

R2

R1

K1

L3

B

12

C441

0.1uF

R546 22R

R547 22R

12

C446

0.1uF

12

R531

2K

DFPEN

DFPCLKR

12

C442

0.1uF

LOOP_FILTER

1 2

1 2

Place these components

close to U1

12

R532

2K

DFPD0

DFPD1

DFPD2

DFPD3

DFPD4

DFPD5

DFPD6

DFPD7

DFPD8

DFPD9

DFPD10

DFPD11

12

R562

10K

DFPVSYNC

DFPHSYNC

C443

22uF

R538

1 2

10

+3.3VSUS

12

1 2

C444

0.001UF

DFPD4

DFPD7

DFPD6

DFPD5

R530

1K

DFPD[11:0] 4

LF_C445

12

1

2

3

4

C445

0.01UF

TXA0TXA0+

TXA1TXA1+

TXA2TXA2+

TXCLK1TXCLK1+

TXB0TXB0+

TXB1TXB1+

TXB2TXB2+

TXCLK2TXCLK2+

RP5

10K

FREQ_OUT 5

REF_OUT 5,7

SMB_DAT2

SMB_CLK2

8

7

6

5

C

PWR_SRC2

Q4

2N7002

32

1

+5VSUS

876

5

C840

0.1uF

NO STUFF

123

4

EQUAL LENGTH PAIRS ON

ALL DIFFERENTIAL PAIRS

100 ohm differential pair

100 ohm differential pair

100 ohm differential pair

100 ohm differential pair

100 ohm differential pair

100 ohm differential pair

100 ohm differential pair

100 ohm differential pair

100 ohm differential pair

PID0

PID3

PID2

PID1

BCKLT_ON

+3.3VSUS

I2CSCL5,7

I2CSDA5,7

LCD_PWRGD

Trip Voltage: approx. 2.5v

PSRC_G

D

+5VALW2

IINV_PWR_SRC

3

782

8

7

6

5

1 2

LCD_VCC

R164

100K

PSRC_GR

1 2

1 2

C841

0.1uF

NO STUFF

VDDEN

12

1 6

SI4435DY

4

876

123

R561

2K

5

Q3

5

LCD_VCC

4

4

1

3

Q1

12

12

SI4410DY

C329

C328

0.1uF

10uF

+5VSUS

147

U14C

5 6

TSSOP14

12

C323

0.1uF

R165

75K

12

RP7 10K

1

2

3

4

PID3

PID2

PID1

PID0

R548

220K

12

R550

590K

C842

0.022UF

NO STUFF

PID3

PID2

PID1

PID0

+3.3VSUS

52

6

7

8

LCDVCC_GR

+3.3VSUS

C322

0.01UF

VDDENJ

E

J1

1

PWR_SRC0

2

PWR_SRC1

3

GND_0

4

5V_SUS

5

+5VALW

6

GND_1

7

SMB_DAT

8

SMB_CLK

9

GND_2

10

BKLT_ON

11

PWR_SRC2

12

GND_3

13

PID3_I2CDAT

14

PID2_I2CCLK

15

GND_4

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

FI-D50SB-E1500

32

12

PID1

PID0

GND_5

LCD_VCC0

LCD_VCC1

GND_6

+3V_SUS

NC_CLCD_P23

GND_7

PID2_I2C_CLK

PID3_I2C_DAT

GND_8

TXOUT_U0TXOUT_U0+

GND_9

TXOUT_U1TXOUT_U1+

GND_10

TXOUT_U2TXOUT_U2+

GND_11

TXCLK_UTXCLK_U+

GND_12

TXOUT_L0TXOUT_L0+

GND_13

TXOUT_L1TXOUT_L1+

GND_14

TXOUT_L2TXOUT_L2+

GND_15

TXCLKL_LTXCLK_L+

R163

100K

Q2

2N7002

1

12

MGND10

MGND11

MGND12

MGND1

MGND2

MGND3

MGND4

MGND5

MGND6

MGND7

MGND8

MGND9

+12V 2

51

52

53

54

55

56

57

58

59

60

61

62

1 1

+5VSUS VCC

DFP/DVI/CLK_DVR

A

B

C

D

Micro-Star International Co., L TD .

MS8832,1/2/4MX32-DDR,TV

Size Document Number Rev

C

Date:

Tuesday, April 30, 2002

DFP/DVI/CLK_DVR

Sheet of

E

89

100

www.vinafix.vn

Page 10

A

B

C

D

E

4 4

+5VRUN

3 3

+5VRUN

12

C279

10uF

NO STUFF

TL431CDR SO8 ADJ

NO STUFF

M1

1

R501

1 2

10R

NO STUFF

U25

+3.3VRUN

1

M2

M3

M4

1

1

1

R554

1 2

NO STUFF

DFP3.3V

5

4

NC

CATHODE

ADJ

ANODE

ANODE

ANODE

38267

R122

DFPADJ

1 2

1 2

261R

NO STUFF

R124

681R

NO STUFF

NC

ANODE

R563

0R

L22

1 2

150-220R_100MHZ

12

12

C280

C281

10uF

100pF

LCD_VCC

12

(PG8)

DFPAVCC

12

12

C455

C454

100pF

10uF

12

12

C452

C451

0.1uF

0.001UF

Single point connection

+3.3VSUS

R555 0R

1 2

R556 0R

1 2

12

+

C828

330uF R040

+2.5V

12

0.1uF

R557 0R

R558 0R

C809

1 2

1 2

2.5V@1.5A max

+3.3VSUS

2 2

12

C330

4.7uF

0.039UF

12

C829

Drop Out 350mV @ 1.5A

12

R68

2.2K

FBADJ

12

R69

2K

123

45

U513

Vo

EN

1.5A

Vin

ADJGND

GND

GND

GND

678

NO STUFF

NO STUFF

FBVDD

1 1

DC-DC CONTVR

A

B

C

D

Micro-Star International Co., L TD .

MS8832,1/2/4MX32-DDR,TV

Size Document Number Rev

C

Date:

Tuesday, April 30, 2002

DC-DC CONTVR

E

Sheet of

99

100

www.vinafix.vn

Loading...

Loading...