Page 1

CR-1 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE1

8

7

56

4

3

2

1

TABLE OF CONTENTS

D

1 TABLE OF CONTENTS

2 BLOCK DIAGRAM

3 MEMORY 0 - GDDR3

4 MEMORY 1 - GDDR3

C C

5 MEMORY 2 - GDDR3

6 MEMORY 3 - GDDR3

7 POWER PINS FOR THE ASIC

8 MEMORY 0 & MEMORY 1 - ATHENA ASIC

9 MEMORY 2 & MEMORY 3 - ATHENA ASIC

10 UART AND TEST MODE

B B

11 LOGIC ANALYSER CONNECTORS(MICTOR)

12 PCI INTERFACE -ATHENA ASIC

13 PCI CONNECTOR

20 DECAPS FOR M0 -GDDR3

21 DECAPS FOR M1 -GDDR3

22 DECAPS FOR M2 -GDDR3

23 DECAPS FOR M3 -GDDR3

24 DECAPS FOR 2.0V OF THE ASIC

25 DECAPS FOR 1.2V

26 DECAPS FOR 1.2V

27 DECAPS FOR 3.3V

28 LEVEL TRANSLATOR FOR PCI INTERFACE SIGNALS

29 LEVEL TRANSLATOR FOR PCI INTERFACE SIGNALS

30 LEVEL TRANSLATOR FOR PCI INTERFACE SIGNALS

31 RE-SPIN BUG FIXES [INTERRUPTS, STAR MEM]

32 BRACKET GROUNDED,AND ALL DISTRIBUTED CAPS

33 MULTI-PACKAGE CAPACITOR

D

14 JTAG CONNECTOR

15 GPIO , EEPROM AND FAN CONTROL

16 CLOCK CIRCUITRY

A A

17 1.2V GENERATION

18 IDE POWER CONN,2.0V AND 2.5V GENERATION

19 POWER SEQUENCING AND RESET CIRCUITRY

DATE:TITLE:

PAGE:

12-15-2005

1

1

AGEIA ARD

P/N 02-01-15-0009 REV01

8

7

6

45

ENGINEER:

3

2

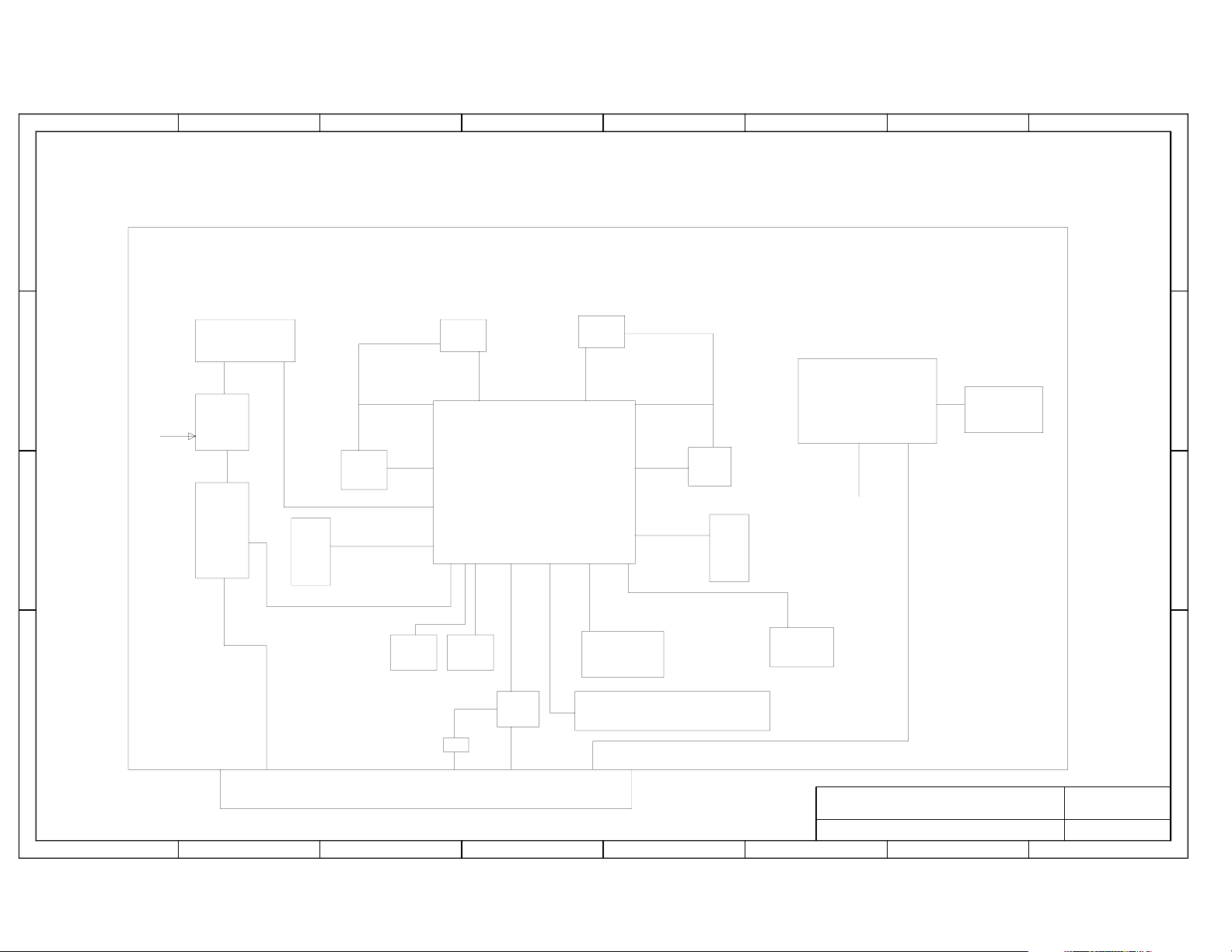

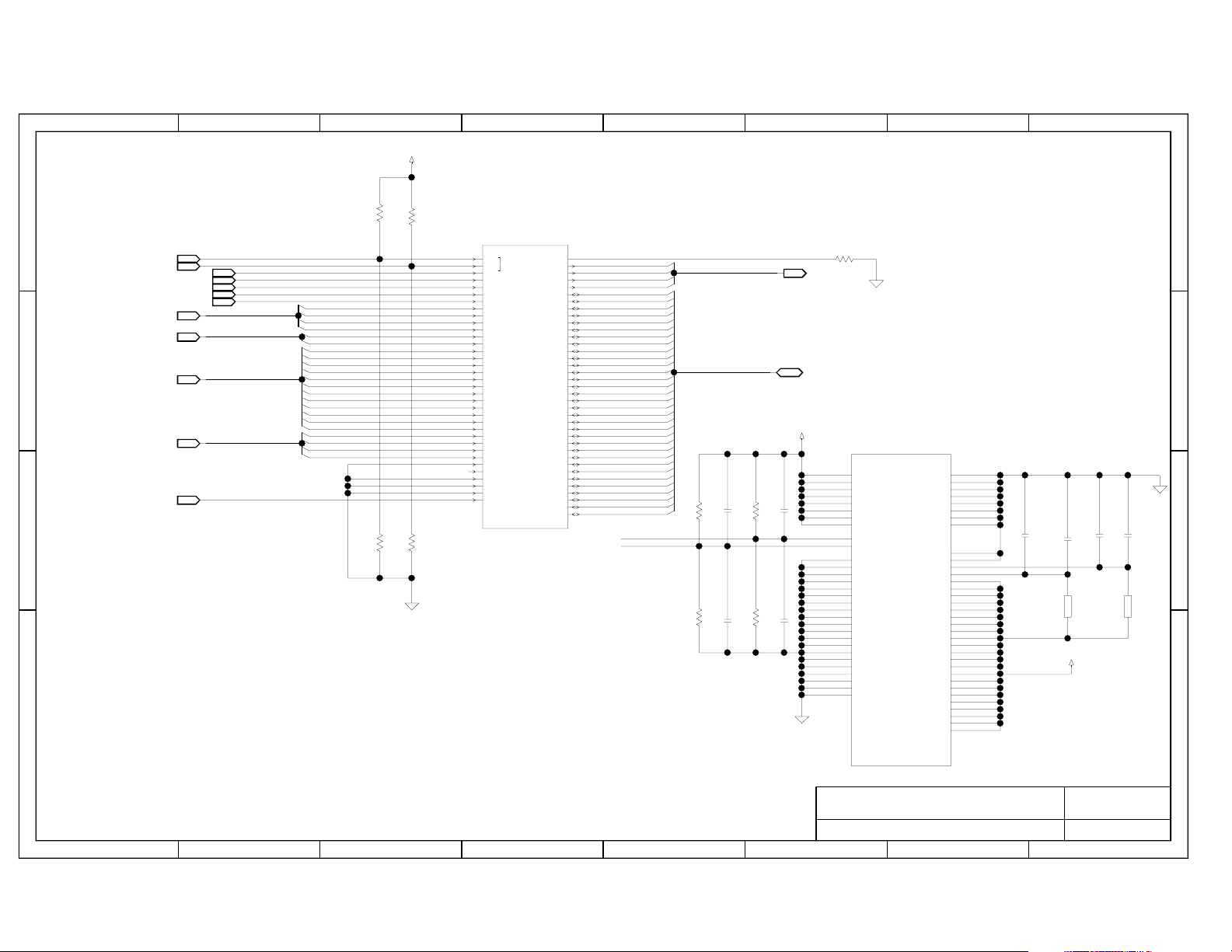

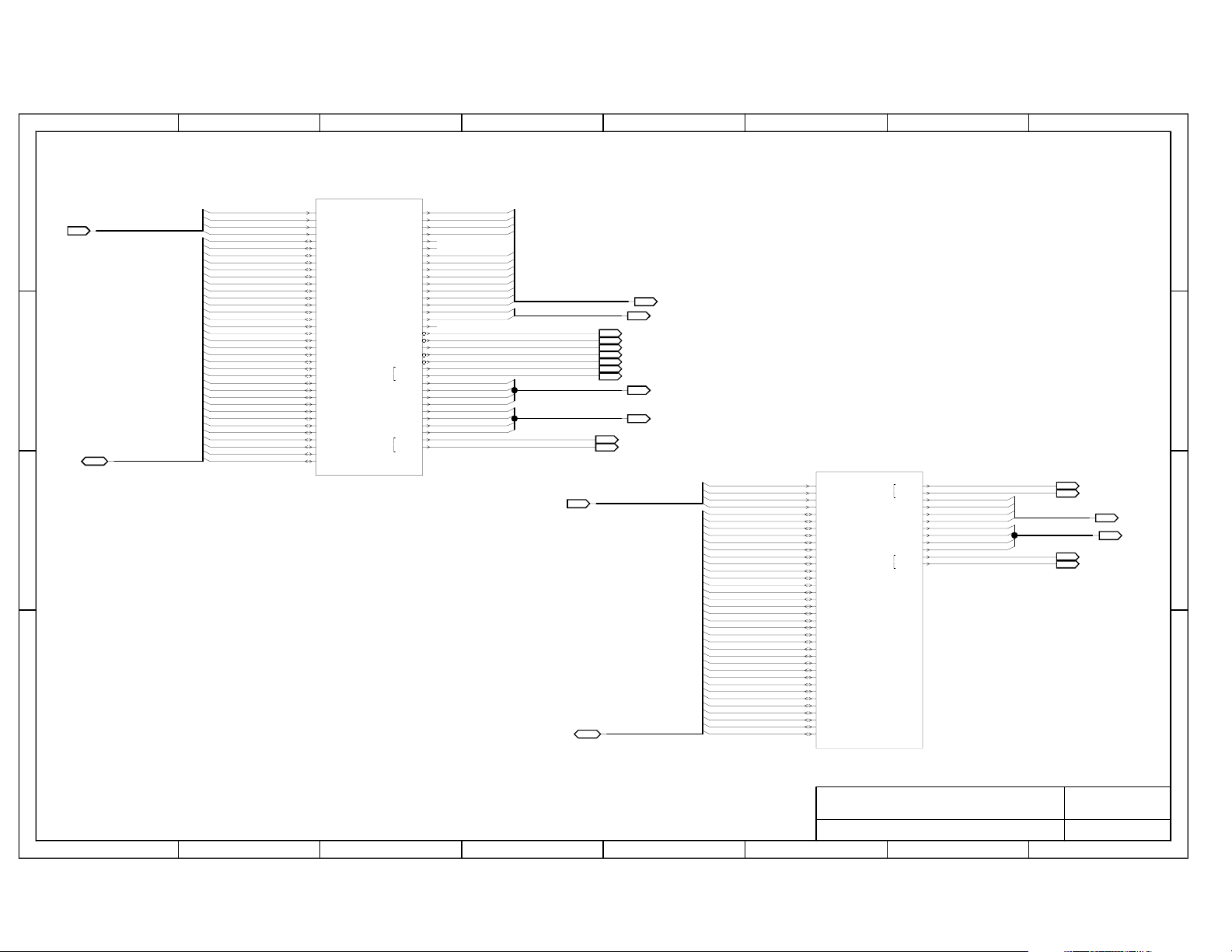

Page 2

CR-2 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE2

8

7

56

4

3

2

1

BLOCK DIAGRAM

D

EEPROM

C C

M0 ADDRESS

STAR MEM

CHIP

RESET

B B

BUG FIX

EJTAG

DEBUG

CONN

GDDR3

DATA

GDDR3

DATA

ATHENA

GDDR3

DATA

M2 ADDRESS

DATA

GDDR3

DEBUG

CONN

POWER GENERATION

POWER SEQUENCING ICS

AND MOSFETS

POWER FOR ALL THE I CS ON THE BOARD

IDE

CONNECTOR

D

UART1

JTAG SIGNALS

A A

8

7

CONN

UNIVERSAL PCI CONNECTOR

6

INTA

UART2

CONN

PCI INTERFACE

XLAT

TEST MODE

RESISTORS

66.66 MHZ CLOCK

OSCILLATORS

45

STRAP

OPTIONS

FOR

GPIO<0:3>

ENGINEER:

3

AGEIA ARD

09-05-2004

DATE:TITLE:

2

PAGE:

2

1

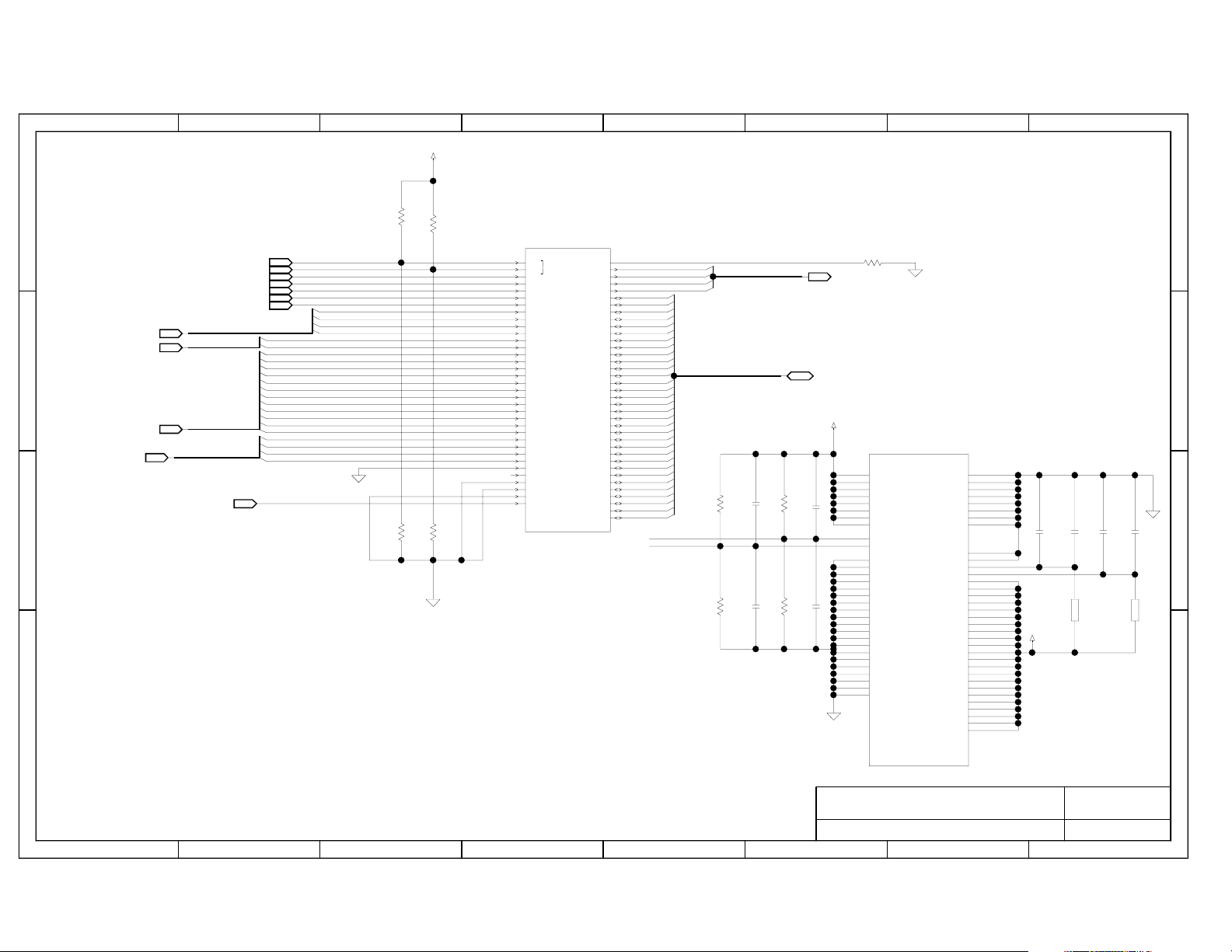

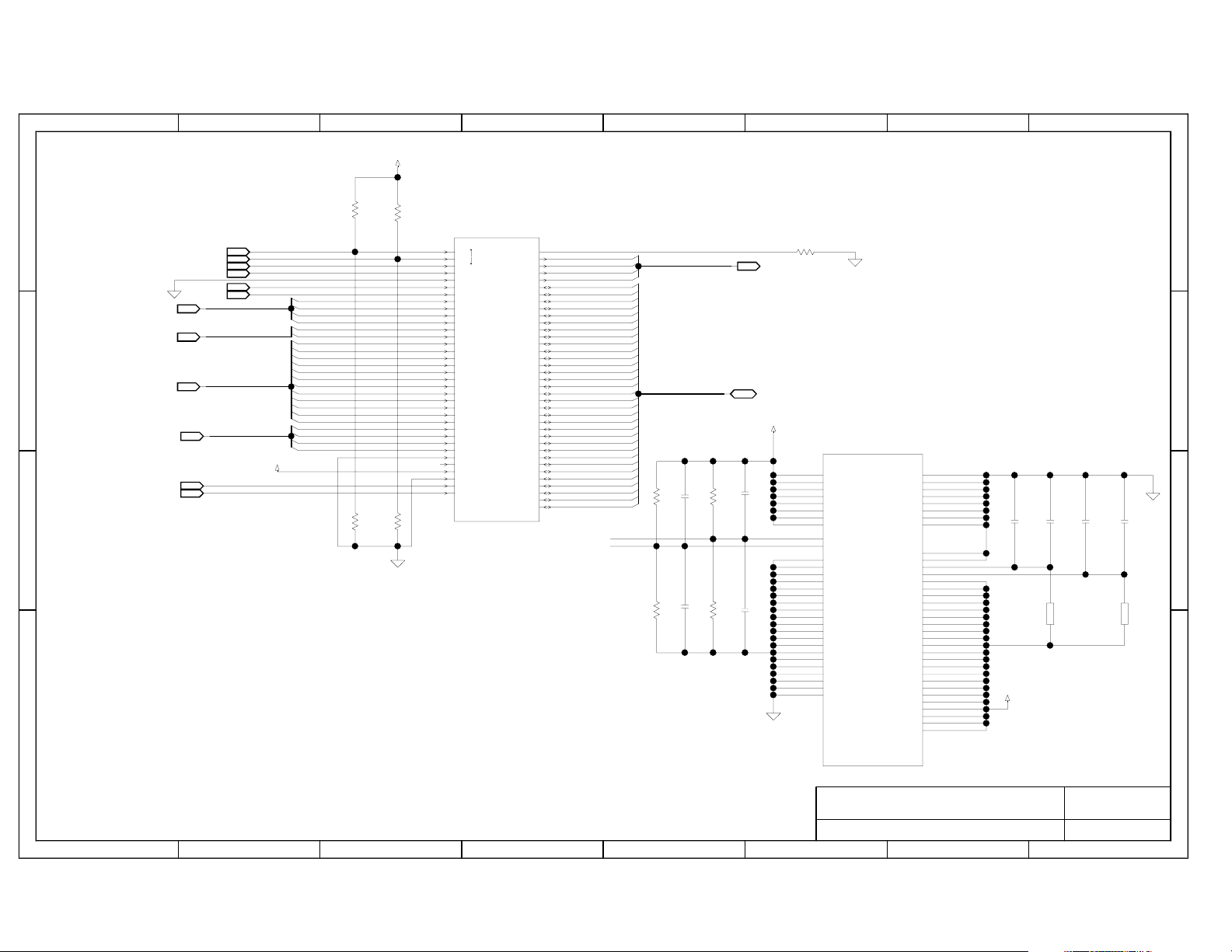

Page 3

CR-3 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE3

8

D

IN

IN

M0_DM[0:3]

M0_BA[0:1]

8C5>

4C7<

8C5>

C C

IN

6B8<

M0_A[0:11]

IN

M0_WDQS[0:3]

5B8<

4B7< 8D5>

4C7<

8C5>

8B5>

B B

7

VCCP_1_8

2

R1

8C5>

8C5>

8C5>

4D7<

8C5>

4D7<

8C5>

4D7<

4C7<

8C5>

4C7<

8C5>

M0_CK

IN

M0_CK_N

IN

M0_CKE

IN

M0_CS_N

IN

M0_RAS_N

IN

M0_CAS_N

IN

M0_WE_N

IN

0

1

0

1

2

3

4

5

6

7

8

9

10

11

0

3

2

1

0

3

2

1

IN

2

R2

71.5,1%

165,1%

71.5,1%

1

1

M_RES

2

2

165,1%

R9

1

1

R8

MF IS MIRROR FUNCTI ON PIN

PULL UP US E MIRROR FUNCTION

PULL DOWN NOT USE MIRROR FUNCTION

A/B WHEN MIRROR FUNCTIO N IS USED

PIN NAME B IS USED OTHERWISE A IS USED

56

U1

J11

CK

J10

CK#

H4

CKE/WE#

F9

CS#/CAS#

H3

RAS#/RFM/BA2

F4

CAS#/CS#

H9

WE#/CKE

E3

DM0

E10

DM1

N10

DM2

N3

DM3

G4

BA0/BA1

G9

BA1/BA0

K4

A0/A4

H2

A1/A5

K3

A2/A6

M4

A3/A9

K9

A4/A0

H11

A5/A1

K10

A6/A2

L9

A7/A11

K11

A8/A10

M9

A9/A3

K2

A10/A8

L4

A11/A7

D2

WDQS0

D11

P11

WDQS2

P2

WDQS3

J2

RFU1

J3

RFU2

A9

MF(MIRROR)

V4

SEN

H10

RFM/RAS#/BA2

V9

RESET

K4J55323QG

BODY:GDDR3

RDQS0

RDQS1

RDQS2

RDQS3

ZQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21WDQS1

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

THE TRACE I MPEDANCE IS 50OHMS F OR ALL GDDR3 SIGNALS.

A4

D3

D10

P10

P3

B2

B3

C2

C3

E2

F3

F2

G3

B11

B10

C11

C10

E11

F10

F11

G10

M11

L10

N11

M10

R11

R10

T11

T10

M2

L3

N2

M3

R2

R3

T2

T3

4

M0_ZQ

6

7

2

0

5

4

1

3

24

28

26

30

31

25

29

27

17

19

23

21

18

20

22

16

15

9

13

11

14

10

8

12

VREF_0_0

VREF_0_1

0

M0_RDQS[0:3]

3

2

1

FOR BE TTER R OUTING BYTE LANE IS I NTERCHANGED

BITS IN ONE BYTE LANE IS INTERCHANGED

M0_DQ[0:31]

1

2

R109

C309

220NF,10V,0402

1

2

118,1%,0402

1

2

R110

1

280,1%,0402

C310

2

100NF,6.3V,0402,X5R

A A

3

237,1%

2

1

R10

8D8<

OUT

8B8<>

BI

VCCP_1_8

U1

V11

VDD_8

V2

VDD_7

2

1

118,1%,0402

2

1

280,1%,0402

M12

1

R6

C15

220NF,10V,0402

2

1

C287

R7

2

100NF,6.3V,0402,X5R

VDD_6

M1

VDD_5

F12

VDD_4

F1

VDD_3

A11

VDD_2

A2

VDD_1

H12

VREF_2

H1

VREF_1

T12

VSSQ_20

T9

VSSQ_19

T4

VSSQ_18

T1

VSSQ_17

P12

VSSQ_16

P9

VSSQ_15

P4

VSSQ_14

P1

VSSQ_13

L11

VSSQ_12

L2

VSSQ_11

G11

VSSQ_10

G2

VSSQ_9

D12

VSSQ_8

D9

VSSQ_7

D4

VSSQ_6

D1

VSSQ_5

B12

VSSQ_4

B9

VSSQ_3

B4

VSSQ_2

B1

VSSQ_1

VDDQ_22

VDDQ_21

VDDQ_20

VDDQ_19

VDDQ_18

VDDQ_17

VDDQ_16

VDDQ_15

VDDQ_14

VDDQ_13

VDDQ_12

VDDQ_11

VDDQ_10

VDDQ_9

VDDQ_8

VDDQ_7

VDDQ_6

VDDQ_5

VDDQ_4

VDDQ_3

VDDQ_2

VDDQ_1

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSSA2

VSSA1

VDDA1

VDDA2

2

A3

A10

G1

G12

L1

L12

V3

V10

J12

J1

K1

K12

V12

V1

R12

R9

R4

R1

N12

N9

N4

N1

J9

J4

E12

E9

E4

E1

C12

C9

C4

C1

A12

A1

1

C538

2

VCCP_1_8

100NF,6.3V,0402,X5R

1

1

C359

2

100NF,6.3V,0402,X5R

1

A

B1

B

ferricbead

2

1

1

C539

C361

2

2

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

1

A

B2

B

ferricbead

2

D

K4J55323QG

VSSA,VDDA NEED TO BE DECOUPLE WITH ONE FERRIC BEAD AND ONE CAPACITOR

MEMORY 0 -GDDR3

8

7

6

45

ENGINEER:

3

BODY:POWER_BODY_1

AGEIA ARD

09-05-2004

DATE:TITLE:

PAGE:

3

2

1

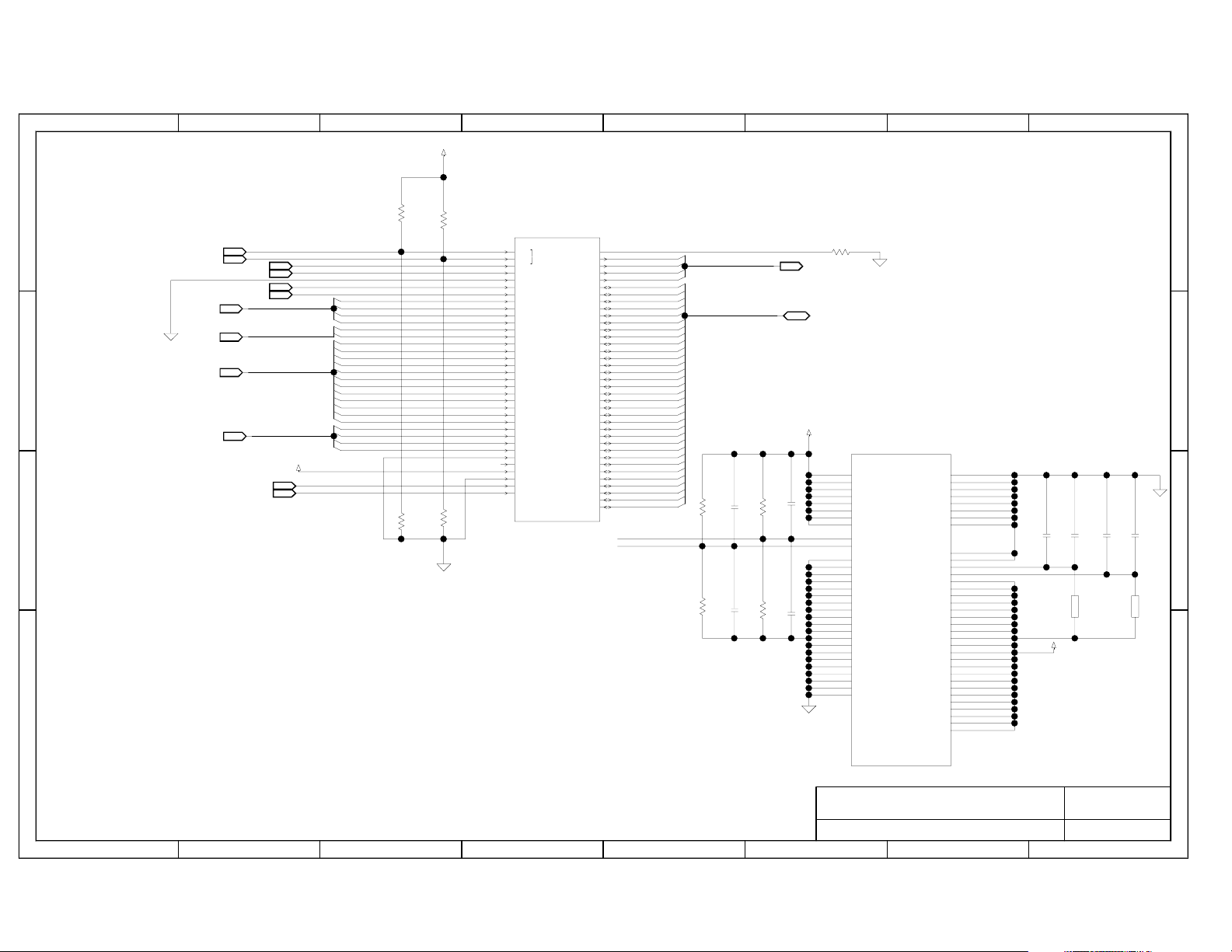

Page 4

CR-4 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE4

100NF,6.3V,0402,X5R

VCCP_1_8

1

1

1

1

C541

C365

C363

2

100NF,6.3V,0402,X5R

1

A

B3

B

ferricbead

2

2

2

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

1

A

B4

B

ferricbead

2

3

237,1%

2

1

R11

8B4<

OUT

8A4<>

BI

VCCP_1_8

U2

V11

VDD_8

V2

M12

F12

A11

H12

T12

P12

L11

G11

D12

B12

VDD_7

VDD_6

M1

VDD_5

VDD_4

F1

VDD_3

VDD_2

A2

VDD_1

VREF_2

H1

VREF_1

VSSQ_20

T9

VSSQ_19

T4

VSSQ_18

T1

VSSQ_17

VSSQ_16

P9

VSSQ_15

P4

VSSQ_14

P1

VSSQ_13

VSSQ_12

L2

VSSQ_11

VSSQ_10

G2

VSSQ_9

VSSQ_8

D9

VSSQ_7

D4

VSSQ_6

D1

VSSQ_5

VSSQ_4

B9

VSSQ_3

B4

VSSQ_2

B1

VSSQ_1

1

C290

R14

2

220NF,10V,0402100NF,6.3V,0402,X5R

1

R15

C291

2

VDDQ_22

VDDQ_21

VDDQ_20

VDDQ_19

VDDQ_18

VDDQ_17

VDDQ_16

VDDQ_15

VDDQ_14

VDDQ_13

VDDQ_12

VDDQ_11

VDDQ_10

VDDQ_9

VDDQ_8

VDDQ_7

VDDQ_6

VDDQ_5

VDDQ_4

VDDQ_3

VDDQ_2

VDDQ_1

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSSA2

VSSA1

VDDA1

VDDA2

2

A3

A10

G1

G12

L1

L12

V3

V10

J12

J1

K1

K12

V12

V1

R12

R9

R4

R1

N12

N9

N4

N1

J9

J4

E12

E9

E4

E1

C12

C9

C4

C1

A12

A1

1

C540

2

8B1>

8B1>

3D7< 8C5>

8B1>

5B8<

IN

IN

3C7<

3C7<

IN

IN

IN

IN

3C7<

3B7<

7

M1_CK

M1_CK_N

8C5>

IN

3D7<

IN

8C5>

IN

8C5>

IN

M1_DM[0:3]

M0_BA[0:1]

M0_A[0:11]

M1_WDQS[0:3]

8C5>

IN

8D5>

IN

M0_WE_N

M0_CAS_N

M0_CS_N

M0_CKE

VCCP_1_8

M0_RAS_N

M_RES

VCCP_1_8

2

2

71.5,1%

71.5,1%

R102

1

0

1

3

2

1

0

4

5

6

9

0

1

2

11

10

3

8

7

0

1

3

2

R106

1

J11

J10

E10

N10

H11

K10

K11

D11

P11

H10

2

2

165,1%

165,1%

1

R107

R103

1

MF I S MIRROR FUNCTI ON PIN

PULL UP US E MIRROR FUNCTION

PULL DOWN NOT USE MIRROR FUNCTI ON

A/B WHEN MIRROR FUNCTIO N IS USED

PIN NAME B I S USED OTHERWISE A IS USED

8

D

8B1>

3C8<

8C5>

C C

3C8<

8C5>

6B8<

B B

56

U2

CK

CK#

H4

CKE/WE#

F9

CS#/CAS#

H3

RAS#/RFM/BA2

F4

CAS#/CS#

H9

WE#/CKE

E3

DM0

DM1

DM2

N3

DM3

G4

BA0/BA1

G9

BA1/BA0

K4

A0/A4

H2

A1/A5

K3

A2/A6

M4

A3/A9

K9

A4/A0

A5/A1

A6/A2

L9

A7/A11

A8/A10

M9

A9/A3

K2

A10/A8

L4

A11/A7

D2

WDQS0

WDQS2

P2

WDQS3

J2

RFU1

J3

RFU2

A9

MF(MIRROR)

V4

SEN

RFM/RAS#/BA2

V9

RESET

K4J55323QG

BODY:GDDR3

RDQS0

RDQS1

RDQS2

RDQS3

A4

ZQ

D3

D10

P10

P3

B2

DQ0

B3

DQ1

C2

DQ2

C3

DQ3

E2

DQ4

F3

DQ5

F2

DQ6

G3

DQ7

B11

DQ8

B10

DQ9

C11

DQ10

C10

DQ11

E11

DQ12

F10

DQ13

F11

DQ14

G10

DQ15

M11

DQ16

L10

DQ17

N11

DQ18

M10

DQ19

R11

DQ20

R10

DQ21WDQS1

T11

DQ22

T10

DQ23

M2

DQ24

L3

DQ25

N2

DQ26

M3

DQ27

R2

DQ28

R3

DQ29

T2

DQ30

T3

DQ31

VREF_1_0

VREF_1_1

M1_ZQ

4

0

M1_RDQS[0:3]

1

3

2

5

2

1

4

M1_DQ[0:31]

3

7

6

0

12

FOR BETTER ROUTING BYTE LANE IS INTERCHANGED

11

15

9

BITS IN ONE BYTE LANE IS INTERCHANGED

13

14

8

10

25

24

30

26

28

31

27

29

17

19

20

21

22

23

16

18

1

2

118,1%,0402

R116

1

2

R117

1

280,1%,0402

2

118,1%,0402

C311

1

2

220NF,10V,0402

1

2

C312

1

2

280,1%,0402

100NF,6.3V,0402,X5R

A A

D

K4J55323QG

ENGINEER:

3

BODY:POWER_BODY_1

AGEIA_ARD

09-05-2004

DATE:TITLE:

4

PAGE:

2

1

VSSA,VDDA NEED TO BE DECOUPLE WITH ONE FERRIC BEAD AND ONE CAPACITOR

8

7

6

45

Page 5

CR-5 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE5

8

D

9C4>

IN

9C4>

IN

9C4>

6D7<

6D7<

9C4>

6D7<

9C4>

6C7<

9C4>

6C7<

9C4>

9C4>

IN

9C4>

6C8<

C C

4B7<

IN

6C8<

9C4>

IN

9C4>

IN

8D5>6B8<

3B7<

IN

B B

7

M2_CK

M2_CK_N

M2_CKE

IN

M2_CS_N

IN

M2_RAS_N

IN

M2_CAS_N

IN

M2_WE_N

IN

M2_DM[0:3]

M2_BA[0:1]

M2_A[0:11]

M2_WDQS[0:3]

M_RES

VCCP_1_8

2

2

R240

71.5,1%

71.5,1%

0

1

2

3

0

1

0

1

2

3

4

5

6

7

8

9

10

11

0

1

2

3

165,1%

R242

1

1

2

2

165,1%

R241

R243

1

1

PIN NAME B IS USED OTHERWISE A IS USED

U3

J11

J10

H4

F9

H3

F4

H9

E3

E10

N10

N3

G4

G9

K4

H2

K3

M4

K9

H11

K10

L9

K11

M9

K2

L4

D2

D11

P11

P2

J2

J3

A9

V4

H10

V9

K4J55323QG

BODY:GDDR3

MF IS MIRROR FUNCTION PIN

PULL UP USE MIRROR FUNCT ION

PULL DOWN NOT USE MIRROR FUNCTION

A/B WHEN MIRROR FUNCTION I S USED

CK

CK#

CKE/WE#

CS#/CAS#

RAS#/RFM/BA2

CAS#/CS#

WE#/CKE

DM0

DM1

DM2

DM3

BA0/BA1

BA1/BA0

A0/A4

A1/A5

A2/A6

A3/A9

A4/A0

A5/A1

A6/A2

A7/A11

A8/A10

A9/A3

A10/A8

A11/A7

WDQS0

WDQS2

WDQS3

RFU1

RFU2

MF(MIRROR)

SEN

RFM/RAS#/BA2

RESET

56

A4

D3

D10

P10

P3

B2

B3

C2

C3

E2

F3

F2

G3

B11

B10

C11

C10

E11

F10

F11

G10

M11

N11

M10

R11

R10

T11

T10

M2

N2

M3

R2

R3

T2

T3

M2_ZQ

L10

L3

VREF_2_0

VREF_2_1

RDQS0

RDQS1

RDQS2

RDQS3

ZQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21WDQS1

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

4

0

M2_RDQS[0:3]

1

2

3

1

5

2

FOR BE TTER R OUTING BYTE LANE IS I NTERCHANGED

0

7

BITS I N ONE BYTE LANE IS INTERCHAN GED

6

3

4

9

8

14

M2_DQ[0:31]

12

11

13

10

15

21

17

23

20

19

16

18

22

30

24

26

25

31

28

27

29

1

2

1

2

1

280,1%,0402 118,1%,0402

2

R121

C330

R104

118,1%,0402

1

2

220NF,10V,0402

2

1

R122

100NF,6.3V,0402,X5R

R105

C331

1

2

280,1%,0402

A A

3

237,1%

2

1

R12

9D8<

OUT

9B8<>

BI

VCCP_1_8

U3

V11

VDD_8

V2

VDD_7

M12

1

C294

2

220NF,10V,0402

1

C295

2

100NF,6.3V,0402,X5R

VDD_6

M1

VDD_5

F12

VDD_4

F1

VDD_3

A11

VDD_2

A2

VDD_1

H12

VREF_2

H1

VREF_1

T12

VSSQ_20

T9

VSSQ_19

T4

VSSQ_18

T1

VSSQ_17

P12

VSSQ_16

P9

VSSQ_15

P4

VSSQ_14

P1

VSSQ_13

L11

VSSQ_12

L2

VSSQ_11

G11

VSSQ_10

G2

VSSQ_9

D12

VSSQ_8

D9

VSSQ_7

D4

VSSQ_6

D1

VSSQ_5

B12

VSSQ_4

B9

VSSQ_3

B4

VSSQ_2

B1

VSSQ_1

VDDQ_22

VDDQ_21

VDDQ_20

VDDQ_19

VDDQ_18

VDDQ_17

VDDQ_16

VDDQ_15

VDDQ_14

VDDQ_13

VDDQ_12

VDDQ_11

VDDQ_10

VDDQ_9

VDDQ_8

VDDQ_7

VDDQ_6

VDDQ_5

VDDQ_4

VDDQ_3

VDDQ_2

VDDQ_1

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSSA2

VSSA1

VDDA1

VDDA2

2

A3

A10

G1

G12

L1

L12

V3

V10

J12

J1

K1

K12

V12

V1

R12

R9

R4

R1

N12

N9

N4

N1

J9

J4

E12

E9

E4

E1

C12

C9

C4

C1

A12

A1

1

C542

2

100NF,6.3V,0402,X5R

1

1

1

1

C543

C369

C367

2

1

A

B5

B

ferricbead

2

VCCP_1_8

2

2

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

1

A

B6

B

ferricbead

2

D

ENGINEER:

3

K4J55323QG

BODY:POWER_BODY_1

AGEIA_ARD

09-05-2004

DATE:TITLE:

PAGE:

5

2

1

MEMORY 2 - GDDR3

VSSA,VDDA NEED TO BE DECOUPLE WITH ONE FERRIC BEAD AND ONE CAPACITO R

8

7

6

45

Page 6

CR-6 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE6

1

1

1

C545

C373

2

2

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

1

A

B8

ferricbead

B

ferricbead

2

9B1>

IN

9B1>

IN

9C4>

IN

9C4>

IN

IN

9C4>

IN

M3_DM[0:3]

M2_BA[0:1]

M2_A[0:11]

M3_WDQS[0:3]

M2_RAS_N

M_RES

7

M3_CK

M3_CK_N

M2_WE_N

M2_CAS_N

M2_CS_N

M2_CKE

VCCP_1_8

VCCP_1_8

2

2

71.5,1%

71.5,1%

R248

1

1

2

3

0

1

0

4

5

6

9

0

1

2

11

10

3

8

7

1

2

3

0

2

165,1%

1

PIN NAME B IS USED OTHERWISE A IS USED

R250

1

U4

J11

CK

J10

CK#

H4

CKE/WE#

F9

CS#/CAS#

H3

RAS#/RFM/BA2

F4

CAS#/CS#

H9

WE#/CKE

E3

DM0

E10

DM1

N10

DM2

N3

DM3

G4

BA0/BA1

G9

BA1/BA0

K4

A0/A4

H2

A1/A5

K3

A2/A6

M4

A3/A9

K9

A4/A0

H11

A5/A1

K10

A6/A2

L9

A7/A11

K11

A8/A10

M9

A9/A3

K2

A10/A8

L4

A11/A7

D2

WDQS0

D11

P11

WDQS2

P2

WDQS3

J2

RFU1

J3

RFU2

A9

MF(MIRROR)

V4

SEN

H10

RFM/RAS#/BA2

V9

RESET

2

165,1%

R249

1

MF I S MIRROR FUNCTI ON PIN

PULL UP US E MIRROR FUNCTION

PULL DOWN NOT USE MIRROR FUNCTI ON

A/B WHEN MIRROR FUNCTIO N IS USED

K4J55323QG

BODY:GDDR3

R251

8

D

5D7<

5D7<

5C7< 9C4>

5C7<

9B1>

IN

5C8<

9C4>

IN

C C

5C8<

9C4>

IN

9B1>

IN

9C4>5C7<

IN

8D5>3B7<

4B7<

5B8<

IN

B B

RDQS0

RDQS1

RDQS2

RDQS3

56

A4

ZQ

D3

D10

P10

P3

B2

DQ0

B3

DQ1

C2

DQ2

C3

DQ3

E2

DQ4

F3

DQ5

F2

DQ6

G3

DQ7

B11

DQ8

B10

DQ9

C11

DQ10

C10

DQ11

E11

DQ12

F10

DQ13

F11

DQ14

G10

DQ15

M11

DQ16

L10

DQ17

N11

DQ18

M10

DQ19

R11

DQ20

R10

DQ21WDQS1

T11

DQ22

T10

DQ23

M2

DQ24

L3

DQ25

N2

DQ26

M3

DQ27

R2

DQ28

R3

DQ29

T2

DQ30

T3

DQ31

VREF_3_0

VREF_3_1

1

2

3

0

14

12

9

10

15

13

8

11

22

20

18

16

17

21

19

23

25

29

27

31

30

24

28

26

6

5

7

2

0

4

1

3

4

M3_ZQ

M3_RDQS[0:3]

OUT

9B5<

FOR BETTER ROUTING BYTE LANE IS INTERCHANGED

BITS IN ONE BYTE LANE IS INTERCHANGED

M3_DQ[0:31]

1

2

R126

1

2

118,1%,0402280,1%,0402

220NF,10V,0402

1

2

R127

2

1

100NF,6.3V,0402,X5R

2

C336

1

118,1%,0402

2

C337

1

280,1%,0402

9A5<>

BI

1

C298

R112

2

220NF,10V,0402100NF,6.3V,0402,X5R

1

C299

R113

2

A A

1

VCCP_1_8

237,1%

R13

V11

V2

M12

M1

F12

F1

A11

A2

H12

H1

T12

T9

T4

T1

P12

P9

P4

P1

L11

L2

G11

G2

D12

D9

D4

D1

B12

B9

B4

B1

3

2

2

U4

VDD_8

VDD_7

VDD_6

VDD_5

VDD_4

VDD_3

VDD_2

VDD_1

VREF_2

VREF_1

VSSQ_20

VSSQ_19

VSSQ_18

VSSQ_17

VSSQ_16

VSSQ_15

VSSQ_14

VSSQ_13

VSSQ_12

VSSQ_11

VSSQ_10

VSSQ_9

VSSQ_8

VSSQ_7

VSSQ_6

VSSQ_5

VSSQ_4

VSSQ_3

VSSQ_2

VSSQ_1

VDDQ_22

VDDQ_21

VDDQ_20

VDDQ_19

VDDQ_18

VDDQ_17

VDDQ_16

VDDQ_15

VDDQ_14

VDDQ_13

VDDQ_12

VDDQ_11

VDDQ_10

VDDQ_9

VDDQ_8

VDDQ_7

VDDQ_6

VDDQ_5

VDDQ_4

VDDQ_3

VDDQ_2

VDDQ_1

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSSA2

VSSA1

VDDA1

VDDA2

A3

A10

G1

G12

L1

L12

V3

V10

J12

J1

K1

K12

V12

V1

R12

R9

R4

R1

N12

N9

N4

N1

J9

J4

E12

E9

E4

E1

C12

C9

C4

C1

A12

A1

1

C544

2

VCCP_1_8

1

C371

2

100NF,6.3V,0402,X5R

1

A

B7

B

2

D

K4J55323QG

BODY:POWER_BODY_1

MEMORY 3 -GDDR3 WITH MIRROR FUNCTION

AGEIA_ARD

ENGINEER:

8

7

6

45

3

2

DATE:TITLE:

PAGE:

09-05-2004

6

1

Page 7

CR-7 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE7

100NF,6.3V,0402,X5R 220NF,6.3V,0402,X5R

VCCP_1_8

1

2

1

2

DATE:TITLE:

PAGE:

2

C202

1

2

C203

1

1

R63

220NF,6.3V,0402,X5R

280,1%,0402 118,1%,0402

R64

100NF,6.3V,0402,X5R

28-12-2004

7

1

1

2

C302

118,1%,0402

2

1

R162

1

2

280,1%,0402

C303

1

2

R163

A11

A15

A19

A23

A27

AG9

AH8

B10

B14

B18

B22

B26

C13

C17

C21

C25

C29

D12

D20

D28

C9

3

U9

G_VDDO_1

G_VDDO_2

G_VDDO_3

G_VDDO_4

G_VDDO_5

G_VDDO_6

G_VDDO_7

G_VDDO_8

G_VDDO_9

G_VDDO_10

G_VDDO_11

G_VDDO_12

G_VDDO_13

G_VDDO_14

G_VDDO_15

G_VDDO_16

G_VDDO_17

G_VDDO_18

G_VDDO_19

G_VDDO_20

G_VDDO_21

G_VDDO_22

G_VDDO_23

G_VDDO_24

G_VDDO_25

G_VDDO_26

G_VDDO_27

G_VDDO_28

G_VDDO_29

G_VDDO_30

G_VDDO_31

G_VDDO_32

G_VDDO_33

G_VDDO_34

G_VDDO_35

G_VDDO_36

G_VDDO_37

G_VDDO_38

G_VDDO_39

G_VDDO_40

G_VDDO_41

G_VDDO_42

G_VDDO_43

G_VDDO_44

G_VDDO_45

G_VDDO_46

G_VDDO_47

G_VDDO_48

G_VDDO_49

G_VDDO_50

G_VDDO_51

G_VDDO_52

G_VDDO_53

G_VDDO_54

G_VDDO_55

G_VDDO_56

G_VDDO_57

G_VDDO_58

G_VDDO_59

G_VDDO_60

G_VDDO_61

ATHENA_29X29

BODY:POWER2

ENGINEER:

3

G_VDDO_62

G_VDDO_63

G_VDDO_64

G_VDDO_65

G_VDDO_66

G_VDDO_67

G_VDDO_68

G_VDDO_69

G_VDDO_70

G_VDDO_71

G_VDDO_72

G_VDDO_73

G_VDDO_74

G_VDDO_75

G_VDDO_76

G_VDDO_77

G_VDDO_78

G_VDDO_79

G_VDDO_80

G_VDDO_81

G_VDDO_82

G_VDDO_83

G_VDDO_84

G_VDDO_85

G_VDDO_86

G_VDDO_87

G_VDDO_88

G_VDDO_89

G_VDDO_90

G_VDDO_91

G_VDDO_92

G_VDDO_93

G_VDDO_94

G_VDDO_95

G_VDDO_96

G_VDDO_97

G_VDDO_98

G_VDDO_99

G_VDDO_100

G_VDDO_101

G_VDDO_102

G_VDDO_103

G_VDDO_104

G_VDDO_105

G_VDDO_106

G_VDDO_107

G_VDDO_108

G_VDDO_109

G_VDDO_110

G_VDDO_111

G_VREF_1

G_VREF_2

G_VREF_3

G_VREF_4

G_VREF_5

G_VREF_6

G_VREF_7

G_VREF_8

AGEIA_ARD

D8

E11

E15

E19

E23

E27

F10

F14

F18

F22

F26

G13

G17

G21

G29

G9

H12

H16

H20

H24

H28

J13

J17

J20

J23

J27

K22

K26

L21

L25

L29

M24

M28

N23

N27

P22

P26

R21

R25

R29

T28

U23

U27

V22

V26

W21

W25

W29

Y24

Y28

AA10

AA14

AA18

J12

J16

K21

P21

V21

2

VCCP_1_8VCCP_1_8

VREF_ATHENA

2

VDD_64

VDD_65

VDD_66

VDD_67

VDD_68

VDD_69

VDD_70

VDD_71

VDDO_33_1

VDDO_33_2

VDDO_33_3

VDDO_33_4

VDDO_33_5

VDDO_33_6

VDDO_33_7

VDDO_33_8

VDDO_33_9

VDDO_33_10

VDDO_33_11

VDDO_33_12

VDDO_33_13

VDDO_33_14

VDDO_33_15

VDDO_33_16

VDDO_33_17

VDDO_33_18

VDDO_33_19

VDDO_CLK_33

VSSO_33_1

VSSO_33_2

VSSO_33_3

VSSO_33_4

VSSO_33_5

VSSO_33_6

VSSO_33_7

VSSO_33_8

VSSO_33_9

VSSO_33_10

VSSO_33_11

VSSO_33_12

VSSO_33_13

VSSO_33_14

VSSO_33_15

VSSO_33_16

VSSO_33_17

VSSO_33_18

VSSO_33_19

VSSO_33_20

VSSO_33_21

VSSO_33_22

VSSO_CLK_33

G_VDDI_1

G_VDDI_2

G_VDDI_3

G_VDDI_4

G_VDDI_5

G_VDDI_6

G_VDDI_7

G_VDDI_8

7

A13

A17

A21

A25

A29

A9

AA12

AA16

AA20

AA25

AA29

AB24

AB27

AC11

AC15

AC19

AC23

AC27

AD10

AD14

W20

W8

Y11

Y13

Y15

Y17

Y19L10

Y9

AA2L14

AA4

AD6

AH6

C3

C7

D2

F4

H2

H6

K4

M2

M6

P4

T2

T7

V4

Y6

AA8

G8

A7

AA1

AA3

AC8

AE8

AF6

AH7

C2

D1

E6

H4

K2

K6

L7

M4

P2

P6

T4

V2

V6

W7

Y5

H8

AA11

AA15

AA19

J11

J15

J19

N21

U21

AA6

NU1

AA7

NU2

AB6

NU3

AC7

NU4

N7

NU5

P7

NU6

V1

NU7

V7

NU8

Y7

NU9

R7

NU10

U7

NU11

M7

NU12

7

VCCP_3_3

VCCP_2_5

6

AD18

AD22

AD26

AE13

AE17

AE21

AE25

AE29

AF12

AF16

AF20

AF24

AF28

AG11

AG14

AG15

AG22

AG23

AG26

AH10

AH18

AH26

AJ13

AJ17

AJ21

AJ25

AJ29

AF8

AJ9

B12

B20

B28

C11

C15

C16

C19

C23

C24

C27

D10

D14

D18

D22

D26

E13

E17

E21

E25

E29

F12

F16

F20

F24

F28

G11

G15

G19

G23

G26

H22

H26

J10

J14

J18

J21

J25

J29

K24

K28

L23

L27

M21

B8

E9

H9

8

D

VCCP_1_2 VCCP_1_2

C C

B B

A A

K11

K13

K15

K17

K19

L12

L16

L18

L20

M11

M13

M15

M17

M19

N10

N12

N14

N16

N18

N20

P11

P13

P15

P17

P19

R10

R12

R14

R16

R18

R20

T11

T13

T15

T17

T19

U10

U12

U14

U16

U18

U20

V11

V13

V15

V17

V19

W10

W12

W14

W16

W18

K9

L8

M9

N8

P9

R8

T9

U8

V9

U9

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDD_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VDD_23

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDD_50

VDD_51

VDD_52

VDD_53

VDD_54

VDD_55

VDD_56

VDD_57

VDD_58

VDD_59

VDD_60

VDD_61

VDD_62

VDD_63

ATHENA_29X29

BODY:POWER1

8

56

U9

G_VSSO_1

G_VSSO_2

G_VSSO_3

G_VSSO_4

G_VSSO_5

G_VSSO_6

G_VSSO_7

G_VSSO_8

G_VSSO_9

G_VSSO_10

G_VSSO_11

G_VSSO_12

G_VSSO_13

G_VSSO_14

G_VSSO_15

G_VSSO_16

G_VSSO_17

G_VSSO_18

G_VSSO_19

G_VSSO_20

G_VSSO_21

G_VSSO_22

G_VSSO_23

G_VSSO_24

G_VSSO_25

G_VSSO_26

G_VSSO_27

G_VSSO_28

G_VSSO_29

G_VSSO_30

G_VSSO_31

G_VSSO_32

G_VSSO_33

G_VSSO_34

G_VSSO_35

G_VSSO_36

G_VSSO_37

G_VSSO_38

G_VSSO_39

G_VSSO_40

G_VSSO_41

G_VSSO_42

G_VSSO_43

G_VSSO_44

G_VSSO_45

G_VSSO_46

G_VSSO_47

G_VSSO_48

G_VSSO_49

G_VSSO_50

G_VSSO_51

G_VSSO_52

G_VSSO_53

G_VSSO_54

G_VSSO_55

G_VSSO_56

G_VSSO_57

G_VSSO_58

G_VSSO_59

G_VSSO_60

G_VSSO_61

G_VSSO_62

G_VSSO_63

G_VSSO_64

G_VSSO_65

G_VSSO_66

G_VSSO_67

G_VSSO_68

G_VSSO_69

G_VSSO_70

G_VSSO_71

G_VSSO_72

G_VSSO_73

G_VSSO_74

G_VSSO_75

G_VSSO_76

G_VSSO_77

G_VSSO_78

G_VSSO_79

G_VSSO_80

G_VSSO_81

G_VSSO_82

G_VSSO_83

G_VSSO_84

G_VSSO_85

G_VSSO_86

G_VSSO_87

G_VSSO_88

G_VSSO_89

G_VSSO_90

G_VSSO_91

G_VSSO_92

G_VSSO_93

G_VSSO_94

G_VSSO_95

ATHENA_29X29

BODY:POWER3

G_VSSO_96

G_VSSO_97

G_VSSO_98

G_VSSO_99

G_VSSO_100

G_VSSO_101

G_VSSO_102

G_VSSO_103

G_VSSO_104

G_VSSO_105

G_VSSO_106

G_VSSO_107

G_VSSO_108

G_VSSO_109

G_VSSO_110

G_VSSO_111

G_VSSO_112

G_VSSO_113

GND_10

GND_11

GND_12

GND_13

GND_14

GND_15

GND_16

GND_17

GND_18

GND_19

GND_20

GND_21

GND_22

GND_23

GND_24

GND_25

GND_26

GND_27

GND_28

GND_29

GND_30

GND_31

GND_32

GND_33

GND_34

GND_35

GND_36

GND_37

GND_38

GND_39

GND_40

GND_41

GND_42

GND_43

GND_44

GND_45

GND_46

GND_47

GND_48

GND_49

GND_50

GND_51

GND_52

GND_53

GND_54

GND_55

GND_56

GND_57

GND_58

GND_59

GND_60

GND_61

GND_62

GND_63

GND_64

GND_65

GND_66

GND_67

GND_68

GND_69

GND_70

GND_71

GND_72

GND_73

GND_1

GND_2

GND_3

GND_4

GND_5

GND_6

GND_7

GND_8

GND_9

M26

N25

N29

P24

P28

R23

R27

T21

T25

U25

U29

V24

V28

W23

W27

Y21

Y26

AF19

J9

K10

K12

K14

K16

K18

K20

K8

L11

L13

L15

L17

L19

L9

M10

M12

M14

M16

M18

M20

M8

N11

N13

N15

N17

N19

N9

P10

P12

P14

P16

P18

P20

P8

R11

R13

R15

R17

R19

R9

T10

T12

T14

T16

T18

T20

T8

U11

U13

U15

U17

U19

U9

V10

V12

V14

V16

V18

V20

V8

W11

W13

W15

W17

W19

W9

Y10

Y12

Y14

Y16

Y18

Y20

Y8

4

AA13

AA17

AA21

AA23

AA27

AB10

AB14

AB18

AB22

AC13

AC17

AC21

AC25

AC29

AD12

AD16

AD20

AD24

AD28

AE11

AE15

AE23

AE27

AF10

AF18

AF26

AG13

AG17

AG21

AG29

AH12

AH16

AH20

AH24

AH28

AJ11

AJ15

AJ19

AJ23

AJ27

45

D

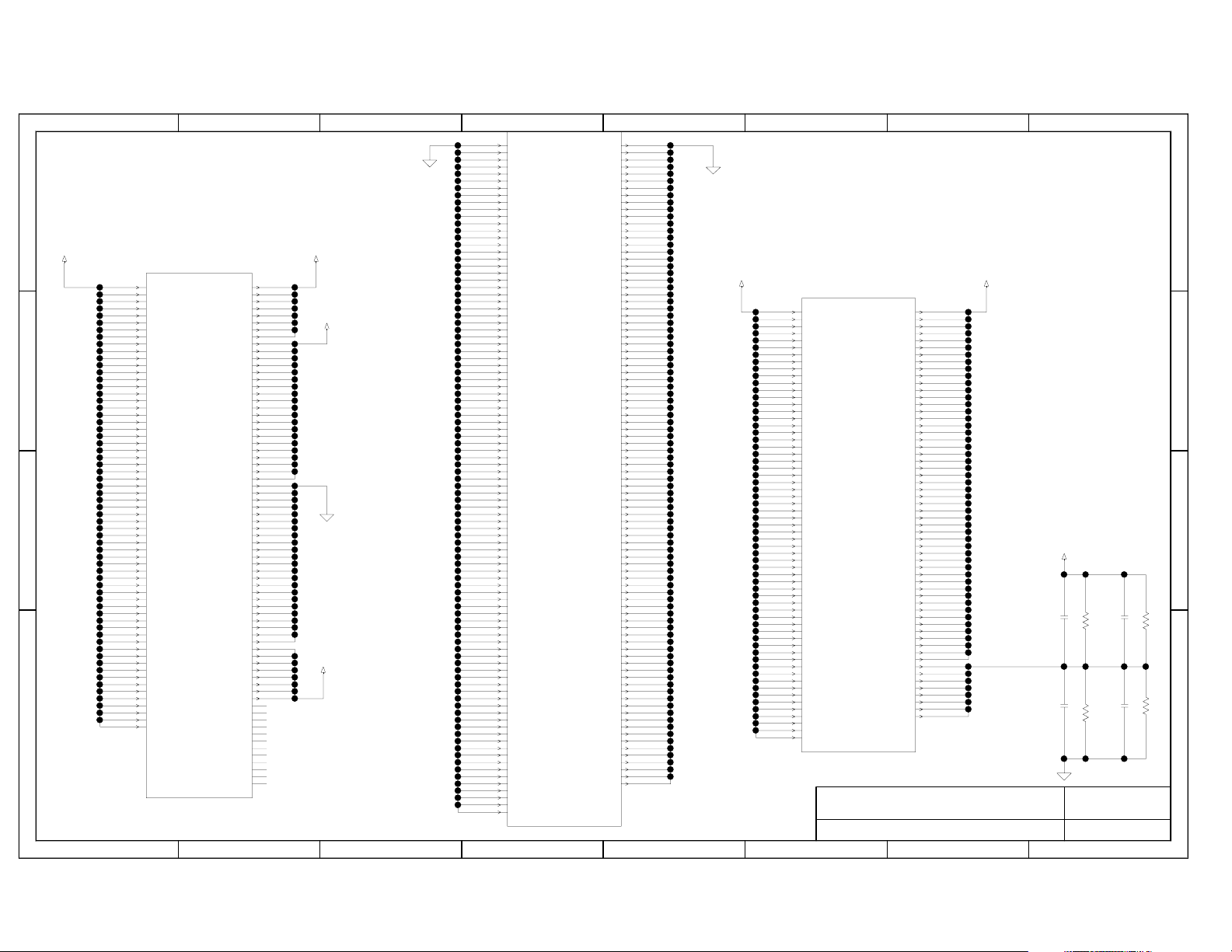

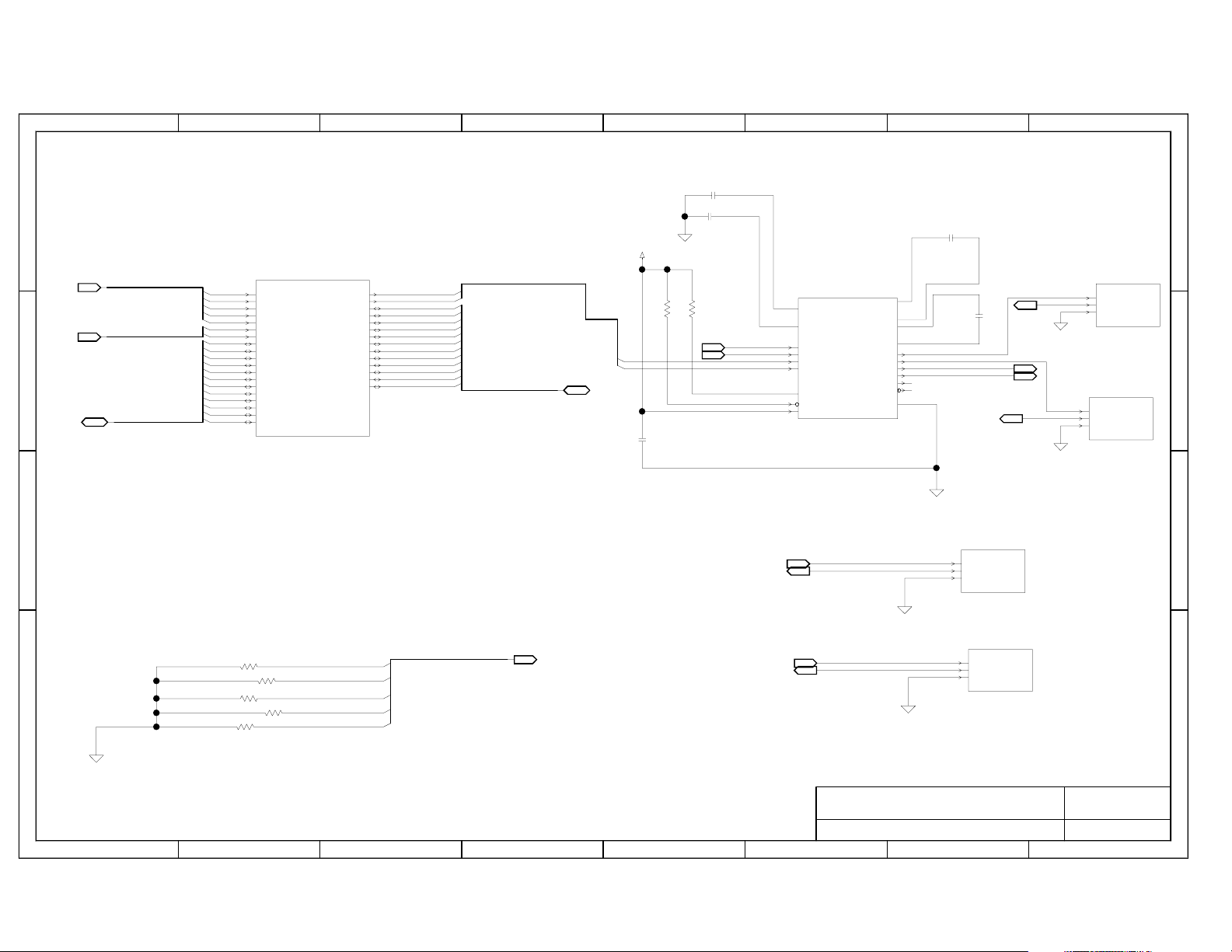

Page 8

CR-8 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE8

1

4D7<

4D7<

4C7<

OUT

4C7<

OUT

D29

E26

K29

M23

L22

H25

K25

D27

A28

F27

H23

E28

R24

M25

P29

H29

F29

N26

L28

P23

N28

J28

M22

M27

R22

N22

R26

J24

M29

N24

G27

G25

K23

J26

G24

F25

3

U9

M1_RDQS_0

M1_RDQS_1

M1_RDQS_2

M1_RDQS_3

M1_DQ_0

M1_DQ_1

M1_DQ_10

M1_DQ_11

M1_DQ_12

M1_DQ_13

M1_DQ_14

M1_DQ_15

M1_DQ_16

M1_DQ_17

M1_DQ_18

M1_DQ_19

M1_DQ_2

M1_DQ_20

M1_DQ_21

M1_DQ_22

M1_DQ_23

M1_DQ_24

M1_DQ_25

M1_DQ_26

M1_DQ_27

M1_DQ_28

M1_DQ_29

M1_DQ_3

M1_DQ_30

M1_DQ_31

M1_DQ_4

M1_DQ_5

M1_DQ_6

M1_DQ_7

M1_DQ_8

M1_DQ_9

ATHENA_29X29

BODY:MEM1

M1_CK

M1_CK_N

M1_DM_0

M1_DM_1

M1_DM_2

M1_DM_3

M1_WDQS_0

M1_WDQS_1

M1_WDQS_2

M1_WDQS_3

M5_CK

M5_CK_N

G28

H27

B29

C28

L24

R28

B27

J22

P27

P25

K27

L26

2

M1_CK

M1_CK_N

0

1

2

3

0

1

2

3

M5_CK

M5_CK_N

OUT

OUT

M1_DM[0:3]

M1_WDQS[0:3]

OUT

OUT

8

D

M0_RDQS[0:3]

3D3>

IN

C C

BI

M0_DQ[0:31]

3C3<>

0

1

2

3

0

1

10

11

12

13

14

15

16

17

18

19

2

20

21

22

23

24

25

26

27

28

29

3

30

31

4

5

6

7

8

9

7

H14

D15

D16

E12

H10

C12

F17

F15

C18

E16

B17

G16

C20

H15

H18

A14

E10

G18

A16

D19

H17

A12

D13

D11

G14

G10

C10

F11

A10

A20

E14

C8

D9

F9

B9

A8

U9

M0_RDQS_0

M0_RDQS_1

M0_RDQS_2

M0_RDQS_3

M0_DQ_0

M0_DQ_1

M0_DQ_10

M0_DQ_11

M0_DQ_12

M0_DQ_13

M0_DQ_14

M0_DQ_15

M0_DQ_16

M0_DQ_17

M0_DQ_18

M0_DQ_19

M0_DQ_2

M0_DQ_20

M0_DQ_21

M0_DQ_22

M0_DQ_23

M0_DQ_24

M0_DQ_25

M0_DQ_26

M0_DQ_27

M0_DQ_28

M0_DQ_29

M0_DQ_3

M0_DQ_30

M0_DQ_31

M0_DQ_4

M0_DQ_5

M0_DQ_6

M0_DQ_7

M0_DQ_8

M0_DQ_9

ATHENA_29X29

BODY:MEM0

M0_WDQS_0

M0_WDQS_1

M0_WDQS_2

M0_WDQS_3

M_ZQ_1

M_ZQ_2

M0_A_0

M0_A_1

M0_A_10

M0_A_11

M0_A_12

M0_A_13

M0_A_2

M0_A_3

M0_A_4

M0_A_5

M0_A_6

M0_A_7

M0_A_8

M0_A_9

M0_BA_0

M0_BA_1

M0_BA_2

M0_CAS_N

M0_CS_N

M0_CKE

M0_RAS_N

M0_WE_N

M0_CK_N

M0_DM_0

M0_DM_1

M0_DM_2

M0_DM_3

M4_CK_N

M_ODT

M_RES

M0_CK

M4_CK

AA9

H11

F21

AD21

A24

F19

A22

B21

A26

B25

B23

E20

D24

E24

H21

F23

D25

G22

D21

C22

C26

E22

H19

B24

G20

D23

D17

E18

F13

B15

B16

B11

H13

A18

B19

G12

C14

B13

M_ODT

M_RES

M_ZQ_1

M_ZQ_2

0

1

10

11

2

3

4

5

6

7

8

9

0

1

M0_CAS_N

M0_CS_N

M0_CKE

M0_RAS_N

M0_WE_N

M0_CK

M0_CK_N

0

1

2

3

0

1

2

3

M4_CK

M4_CK_N

M0_WDQS[0:3]

2

237,1%

R198

1

M0_A[0:11]

M0_BA[0:1]

M0_DM[0:3]

OUT

OUT

56

OUT

OUT

2

R222

237,1%

1

OUT

OUT

OUT

OUT

OUT

OUT

OUT

3B7< 6B8<

4B7<

5B8<

M0_BA2 AND M0_A12,M0_A13 NOT CONNEC TED

3B7< 3C8< 4C 7<

OUT

OUT

4C7<3C7<

3D7<

4D7<

3D7< 4D7<

3C7< 4D7<

3C7< 4C7<

3D7<

3D7<

3C8<

OUT

3B8<

OUT

4D3>

IN

B B

A A

4C3<>

BI

4

4C7<3C8<3B7<

M1_RDQS[0:3]

M1_DQ[0:31]

0

1

2

3

0

1

10

11

12

13

14

15

16

17

18

19

2

20

21

22

23

24

25

26

27

28

29

3

30

31

4

5

6

7

8

9

D

MEMORY 0 & 1 - ASIC

AGEIA_ARD

ENGINEER:

8

7

6

45

3

2

DATE:TITLE:

PAGE:

28-12-2004

8

1

Page 9

CR-9 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE9

AH11

AC16

AD15

AD13

AD11

AE10

AF17

AH15

AJ20

AG16

AE19

AB16

AD17

AE16

AE18

AF15

AB12

AC18

AH14

AH21

AJ14

AG10

AJ12

AG12

AB15

AC10

AC14

AB11

AE12

AC12

AF11

AJ16

AH17

AH9

AF9

AJ8

3

U9

M3_RDQS_0

M3_RDQS_1

M3_RDQS_2

M3_RDQS_3

M3_DQ_0

M3_DQ_1

M3_DQ_10

M3_DQ_11

M3_DQ_12

M3_DQ_13

M3_DQ_14

M3_DQ_15

M3_DQ_16

M3_DQ_17

M3_DQ_18

M3_DQ_19

M3_DQ_2

M3_DQ_20

M3_DQ_21

M3_DQ_22

M3_DQ_23

M3_DQ_24

M3_DQ_25

M3_DQ_26

M3_DQ_27

M3_DQ_28

M3_DQ_29

M3_DQ_3

M3_DQ_30

M3_DQ_31

M3_DQ_4

M3_DQ_5

M3_DQ_6

M3_DQ_7

M3_DQ_8

M3_DQ_9

ATHENA_29X29

BODY:MEM3

M3_CK

M3_CK_N

M3_DM_0

M3_DM_1

M3_DM_2

M3_DM_3

M3_WDQS_0

M3_WDQS_1

M3_WDQS_2

M3_WDQS_3

M7_CK

M7_CK_N

AG19

AH19

AJ10

AJ18

AH13

AF13

AB13

AB17

AG18

AG8

AF14

AE14

2

M3_CK

M3_CK_N

M7_CK

M7_CK_N

0

1

2

3

0

M3_WDQS[0:3]

1

2

3

M3_DM[0:3]

8

D

IN

M2_RDQS[0:3]

5D3>

C C

5C3<>

M2_DQ[0:31]

BI

7

U9

0

1

2

3

0

1

10

11

12

13

14

15

16

17

18

19

2

20

21

22

23

24

25

26

27

28

29

3

30

31

4

5

6

7

8

9

AC24

AG28

AE26

AG27

AD25

AB23

AA22

AH27

AD23

AB28

AF27

AB26

AF29

AA26

AE28

AA28

V23

W26

U24

U22

V29

U28

T29

Y27

T26

Y29

Y22

V25

W22

Y23

Y25

T27

W28

W24

T24

T22

M2_RDQS_0

M2_RDQS_1

M2_RDQS_2

M2_RDQS_3

M2_DQ_0

M2_DQ_1

M2_DQ_10

M2_DQ_11

M2_DQ_12

M2_DQ_13

M2_DQ_14

M2_DQ_15

M2_DQ_16

M2_DQ_17

M2_DQ_18

M2_DQ_19

M2_DQ_2

M2_DQ_20

M2_DQ_21

M2_DQ_22

M2_DQ_23

M2_DQ_24

M2_DQ_25

M2_DQ_26

M2_DQ_27

M2_DQ_28

M2_DQ_29

M2_DQ_3

M2_DQ_30

M2_DQ_31

M2_DQ_4

M2_DQ_5

M2_DQ_6

M2_DQ_7

M2_DQ_8

M2_DQ_9

ATHENA_29X29

BODY:MEM2

M2_CAS_N

M2_RAS_N

M2_WDQS_0

M2_WDQS_1

M2_WDQS_2

M2_WDQS_3

M2_A_0

M2_A_1

M2_A_10

M2_A_11

M2_A_12

M2_A_13

M2_A_2

M2_A_3

M2_A_4

M2_A_5

M2_A_6

M2_A_7

M2_A_8

M2_A_9

M2_BA_0

M2_BA_1

M2_BA_2

M2_CS_N

M2_CKE

M2_WE_N

M2_CK

M2_CK_N

M2_DM_0

M2_DM_1

M2_DM_2

M2_DM_3

M6_CK

M6_CK_N

AH25

AE20

AG20

AG24

AD19

AC20

AB19

AH23

AB20

AC22

AF25

AE22

AE24

AF22

AJ24

AG25

AH22

AF21

AB21

AJ26

AJ22

AF23

AD29

AC28

AB29

V27

AJ28

AH29

U26

T23

AC26

AD27

AA24

AB25

M6_CK

M6_CK_N

0

1

10

11

2

3

4

5

6

7

8

9

0

M2_BA[0:1]

1

M2_CAS_N

M2_CS_N

M2_CKE

M2_RAS_N

M2_WE_N

M2_CK

M2_CK_N

0

1

2

3

0

1

2

3

56

M2_A[0:11]

M2_DM[0:3]

M2_WDQS[0:3]

6D3>

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

M3_RDQS[0:3]

IN

B B

A A

BI

M3_DQ[0:31]

6C3<>

4

M2_BA2 AND M2_A12 AND M2_A13 ARE NOT CONNECTED

6C8<

6B8<

5C8<

OUT

OUT

5C7<

6C7<

5D7<

6D7<

5D7<

6D7<

5C7<

6D7<

5C7<

6C7<

5D8<

5D8<

OUT

OUT

6C8<

6B8<

5C8<

5C8<

5C8<

0

1

2

3

0

1

10

11

12

13

14

15

16

17

18

19

2

20

21

22

23

24

25

26

27

28

29

3

30

31

4

5

6

7

8

9

OUT

OUT

OUT

OUT

1

6D7<

6D7<

6C8<

OUT

6C8<

OUT

D

AGEIA_ARD

MEMORY 2 & 3 - ASIC

8

7

6

45

ENGINEER:

3

2

DATE:TITLE:

PAGE:

28-12-2004

9

1

Page 10

CR-10 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE10

UART_VP

16

13

12

14

20

19

3

7

9

3

LOAD=NO

ICL3225

U10

V+

V-

R_IN_0

R_IN_1

T_IN_0

T_IN_1

FORCEON

FORCEOFF

VCC

T_OUT_0

T_OUT_1

R_OUT_0

R_OUT_1

INVALID

READY

C1+

C1-

C2+

C2-

GND

0.1UF,16V,0603

UART_C1N

UART_C1P

2

4

5

6

UART_C2N

17

8

15

10

1

11

18

2

LOAD=NO

1

C4

UART_C2P

10C4<

T0OUT

T1OUT

UART_RX[0]

UART_RX[1]

2

1

OUT

R0IN

C6

2

0.1UF,16V,0603

LOAD=NO

10B3> 10C8<

OUT

10A3> 10C8<

OUT

OUT

R1IN

10C4<

8

7

56

D

10A5>

10C1>

10A3>

10B3>

TEST_MODE[0:4]

IN

UART_RX[0:1]

IN

C C

11C8<

11C4<

11C7<

SCAN_OUT[0:11]

BI

U9

H1

0

1

2

4

0

1

0

1

10

11

2

4

5

6

7

8

9

TEST_MODE_0

J8

TEST_MODE_1

G5

TEST_MODE_2

E7

3

TEST_MODE_3

F6

TEST_MODE_4

H3

UART_RX_0

H5

UART_RX_1

AB7

SCAN_OUT_0

AD9

SCAN_OUT_1

A3

SCAN_OUT_10

B4

SCAN_OUT_11

AC9

SCAN_OUT_2

AE9

3

SCAN_OUT_3

AE7

SCAN_OUT_4

AJ7

SCAN_OUT_5

D7

SCAN_OUT_6

A5

SCAN_OUT_7

A6

SCAN_OUT_8

B7

SCAN_OUT_9

ATHENA_29X29

BODY:MISC2

UART_TX_0

UART_TX_1

SCAN_IN_0

SCAN_IN_1

SCAN_IN_10

SCAN_IN_11

SCAN_IN_2

SCAN_IN_3

SCAN_IN_4

SCAN_IN_5

SCAN_IN_6

SCAN_IN_7

SCAN_IN_8

SCAN_IN_9

J7

G3

AB9

AB8

B6

C6

AD8

AG7

AF7

AD7

C5

B5

E8

A4

0

1

0

1

10

11

2

3

4

5

6

7

8

9

UART_TX[0:1]

SCAN_IN[0:11]

10C2>

10C2>

11B4<

11C3<

11B8<

BI

4

LOAD=NO

C2

2

1

0.1UF,16V,0603

C3

2

1

0.1UF,16V,0603

LOAD=NO

VCCP_3_3

R0IN

R1IN

UART_VN

2

2

4.7K

R40

4.7K

R5

1

1

LOAD=NO

LOAD=NO

IN

0

1

IN

1

C1

2

LOAD=NO

0.1UF,16V,0603

1

2

3

LOAD=NO

J6

1

2

3

REH_2TD_1130

BODY:REH_2TD_1130

1

LOAD=NO

J5

A1

A2

A3

REH_2TD_1130

BODY:REH_2TD_1130

A1

A2

A3

B B

J1

10C8<

10C1>

IN

OUT

UART_TX[0]

UART_RX[0]

1

A1

2

A2

3

A3

REH_2TD_1130

BODY:REH_2TD_1130

D

LOAD=NO

R34

1K

2

1

1K

2

1

R33

10M

2

A A

1

1K

R32

2

1

R31

1K

2

1

R30

0

1

2

3

4

TEST_MODE[0:4]

10C8<

OUT

UART AND TEST MODE

IN

10C1>10C8<

OUT

UART_TX[1]

UART_RX[1]

AGEIA_ARD

ENGINEER:

8

7

6

45

3

J4

1

2

3

REH_2TD_1130

BODY:REH_2TD_1130

2

A1

A2

A3

28-12-2004

DATE:TITLE:

PAGE:

10

1

Page 11

CR-11 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE11

8

D

C C

B B

7

56

4

3

2

1

D

A A

LOGIC ANALYSER CONN ECTORS(MICTOR)

28-12-2004

AGEIA_ARD

ENGINEER:

8

7

6

45

3

2

DATE:TITLE:

PAGE:

11

1

Page 12

CR-12 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE12

8

7

56

4

3

2

1

D

THE PCI S IGNALS HAVE TRACE IMPEDANCE OF 60OHMS

VCCP_3_3

2

4.7K

R28

1

PCI_PCIEXP_SEL

2

C C

4.7K

R21

1

LOAD=NO

IN

IN

PX_RXN[0]

PX_RXP[0]

14C3>

0

0

P_RST_N

IN

PX_CLK

IN

PX_CLK_N

IN

B B

A A

U9

K3

P_CLK

K1

P_GNT_N

N2

P_IDSEL

K5

P_RST_N

C4

PCI_PCIEXP_SEL

Y2

PX_CLK

Y3

PX_CLK_N

AG2

PX_RXN_0

AF5

PX_RXN_1

AD4

PX_RXN_2

AJ2

PX_RXN_3

AG1

PX_RXP_0

AF4

PX_RXP_1

AD5

PX_RXP_2

AJ1

PX_RXP_3

AB4

P_AD_0

AB3

P_AD_1

Y1

P_AD_10

U5

P_AD_11

V3

P_AD_12

T5

P_AD_13

U3

P_AD_14

U4

P_AD_15

P5

P_AD_16 P_C_BE_N_1

N4

P_AD_17

N5

P_AD_18

N6

P_AD_19

W5

P_AD_2

P1

P_AD_20

P3

P_AD_21

R1

P_AD_22

N1

P_AD_23

L1

P_AD_24

L2

P_AD_25

L3

P_AD_26

M1

P_AD_27

M3

P_AD_28

M5

P_AD_29

U6

P_AD_3

L4

P_AD_30

L5

P_AD_31

W6

P_AD_4

Y4

P_AD_5

W4

P_AD_6 PX_VAA_1

V5

P_AD_7 PX_VAA_2

W2

P_AD_8

T6

P_AD_9

ATHENA_29X29

BODY:PCI_PCIEX

P_REQ_N

PX_IREF

PX_TXN_0

PX_TXN_1

PX_TXN_2

PX_TXN_3

PX_TXP_0

PX_TXP_1

PX_TXP_2

PX_TXP_3

P_DEVSEL_N

P_FRAME_N

P_INTA_N

P_IRDY_N

P_PERR_N

P_SERR_N

P_STOP_N

P_TRDY_N

PX_CAL_RES

PXPLL_AGND

PXPLL_VAA

P_C_BE_N_0

P_C_BE_N_2

P_C_BE_N_3

PX_AGND_1

PX_AGND_2

PX_CGND_1

PX_CGND_2

PX_CGND_3

PX_CGND_4

PX_CGND_5

PX_CGND_6

PX_CGND_7

PX_CGND_8

PX_CGND_9

PX_CGND_10

PX_CGND_11

PX_CGND_12

PX_CGND_13

PX_CGND_14

PX_CGND_15

PX_VDDO_12_1

PX_VDDO_12_2

PX_VDDO_12_3

PX_VDDO_12_4

P_PAR

L6

AB5

2

AD1

AF1

100NF,6.3V,0402,X5R

AJ4

AG5

100NF,6.3V,0402,X5R

2

AD2

AF2

AJ5

AG4

T3

R3

J1

T1

R6

U2

R5

U1

R4

AA5

AB1

AB2

W3

W1

R2

N3

AC3

AC5

AC1

AC2

AE1

AE2

AE4

AE5

AE6

AF3

AG3

AG6

AH1

AH2

AH4

AH5

AJ6

AC4

FILTER2_VCCP25

AC6

AD3

AE3

AH3

AJ3

C7

C9

PX_CAL_RES

1

1

PX_VCCP_1_2

0

1

2

P_C_BE_N[0:3]

3

PX_AGND

0

0

PX_IREF

PX_TXN[0]

PX_TXP[0]

OUT

OUT

2

12K

R29

1

BI

30C7<>30B7<>29B7<>29A7<>

2

R164

200,1%

1

VCCP_2_5

0

2

VCCP_1_2

0

2

1

R25

1

1

C126

C149

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

2

2

100NF,6.3V,0402,X5R

1

R41

1

1

C16

C36

2

33UF,6V,3528

2

D

PX_AGND

PCI INTERFACE -ATHENA ASIC

8

7

6

45

ENGINEER:

3

AGEIA_ARD

DATE:TITLE:

28-12-2004

PAGE:

12

2

1

Page 13

CR-13 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE13

8

7

56

4

3

2

1

D

PCI_EXPRESS_CONN

J2

P_EJ_TDO

IN

PX_TXP[0]

IN

PX_TXN[0]

IN

A7

TDO

A16

PER0_P

A17

PER0_N

B11

WAKE_N

B5

SMCLK

B6

SMDAT

PRSNT2X1_N

C C

PRSNT1_N

TRST_N

REFCLK_P

REFCLK_N

RESET_N

PET0_P

PET0_N

RSVD0

RSVD1

A1

A5

TCK

A6

TDI

A8

TMS

B9

A13

A14

B3

B12

A11

B17

B14

B15

P_EJ_TCK

P_EJ_TDI

P_EJ_TMS

P_EJ_TRST_N

PX_CLK

PX_CLK_N

P_PX_RST_N

PX_RXP[0]

PX_RXN[0]

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

1

1

1

1

0.1UF,25V

C268

2

2

10UF,1206,16V

0.1UF,25V

0.1UF,25V

C260

C261

C262

2

2

PCI_VCCP_12_0

1

0.1UF,25V

C263

2

A3

A2

B2

B1

B10

PCI_EXPRESS_CONN

J2

VCC12_4

VCC12_3

VCC12_2

VCC12_1

VCC3_AUX_1

BODY:POWER_BODY_1

VCC3V3_1

VCC3V3_2

VCC3V3_3

GND_9

GND_8

GND_7

GND_6

GND_5

GND_4

GND_3

GND_2

GND_1

B18

A18

B16

A15

B13

A12

B7

B4

A4

A10

A9

B8

REG_VCCP_3_3

1

C264

2

1

1

1

1

C269

C267

C266

C265

2

2

2

2

10UF,6.3V,1206

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

B B

D

LOAD=NO

0

2

IN

IN

IN

IN

OUT

P_EJ_TDI

P_EJ_TMS

P_EJ_TCK

P_EJ_TRST_N

P_EJ_TDO

29C7>

29C7>

29C7>

A A

29C7>

29C7<

8

1

R17

R18

0

2

1

LOAD=NO

0

R16

2

1

LOAD=NO

R22

0

2

1

LOAD=NO

R19

0

2

1

LOAD=NO

0

1

R20

7

2

EJ_TDI

EJ_TMS

EJ_TCK

EJ_TRST_N

EJ_TDO

6

OUT

OUT

OUT

OUT

14B3>

15C8<

14B3>

15C8<

31B3>

14B3>

14B3>

15C4>

IN

15D8<

31B3>

15C8<

14B6<

PCI CONNECTOR

AGEIA_ARD

ENGINEER:

45

3

2

DATE:TITLE:

PAGE:

15-01-2005

13

1

Page 14

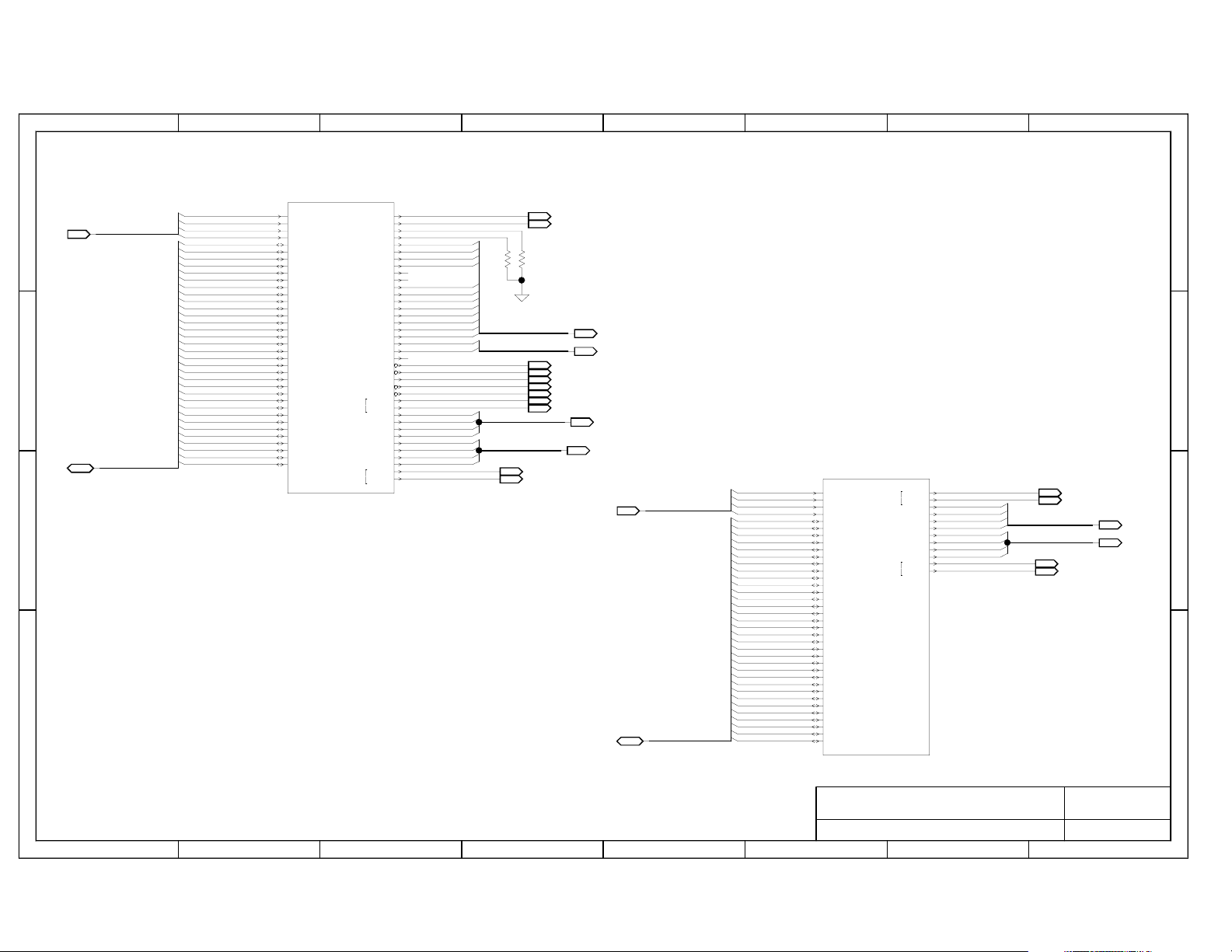

CR-14 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE14

8

7

56

4

3

2

1

D

U5

1

A

2

B

SN74LVC1G08

BODY:SYM1

1

EJ_TRST_N

3

EJ_TDI

7

EJ_TMS

9

EJ_TCK

11

C_RESET_N

13

EJ_DINT

8

6

10

2

4

12

4.7K

VCCP_3_3

2

1

R42

1

3

6

2

2

1K

R39

1

U8

A

B

C

GND

SN74LVC1G11DBVR

13A5>

OUT

OUT

OUT

13A5>

OUT

OUT

15D8<

OUT

19C2>

C C

IN

GPIO<4>

0

2

1

R3

2

4.7K

R35

1

1

2

5

VCCP_3_3

U7

NC

A

VCC

SN74LVC1G04

BODY:INVERTER

14B3>

29B7>

4

Y

3

GND

B B

15C4>13A5<

EJ_TDO

IN

VCCP_3_3

5

14

C_RESET_N

IN

P_PX_RST_N

IN

PX_HOT_RESET_N

LOAD=NO

TSW_EJTAG_CONN

J14

TDO

VIO

BODY:EJTAG

TRST_N

TDI

TMS

TCK

RST

DINT

GND1

GND2

GND3

GND4

GND5

KEY

4

P_RST_N

Y

3

GND

5

VCC

VCCP_3_3

VCCP_3_3

5

VCC

4

C_RESET_IN_N

Y

15C8<

31B3>

15C8<13A5>

15C8<13A5>

15D8<

31B3>

14C6<19C2>

OUT

12C6<

D

A A

8

7

6

JTAG CONNECTOR AND RESET GENERATION

45

ENGINEER:

3

AGEIA_ARD

DATE:TITLE:

28-12-2004

14

PAGE:

2

1

Page 15

CR-15 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE15

8

7

56

4

3

2

1

VCCP_3_3

2

2

2

1

LOAD=NO

NC

A

sn74lvc1g06

2

1K

1K

R234

R235

1

1

U9

IN

EE_DO

EJ_DINT

EJ_TCK

EJ_TDI

EJ_TMS

EJ_TRST_N

15D1>

2

A2A1

LOAD=NO

J15

CONN_2PIN

1

2

1K

R171

1

LOAD=NO

VCCP_3_3

2

100K

1

0

4

5

VCCYGND

U6

2

1

R4

VCCP_3_3

E4 D4

EE_DO

E3

EJ_DINT

F3

EJ_TCK

EJ_TDI

E1

EJ_TMS

G2

EJ_TRST_N

ATHENA_29X29

BODY:MISC1

PCI_VCCP_12_0

3

D5

1

2

1

R60

1

0.1UF,16V,0603

2

652

C304

SI1400DL

3

Q8

EE_DI

EE_CLK

EE_CS

EJ_TDO

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

FAN CONN ECTOR

B2B_XH_AM

J10

1

E5

D3

F2G4

J6

GPIO[0]

G1

GPIO[1]

J2

GPIO[2]

F1

GPIO[3]

K7

GPIO[4]

J4

GPIO[5]

J5

GPIO[6]

J3

GPIO[7]

A2A1

2

33

1

R178

GPIO[0]

2

EJ_TDO

OUT

OUT

15A4<

OUT

OUT

31C3<

OUT

OUT

OUT

OUT

GPIO[1]

2

2

470

470

R74

R59

1

1

LOAD=NO

LOAD=NO

1

1

1

1

led

led

2

LOAD=NO

2

DS2

DS1

2

LOAD=NO

2

15A8<

31C3<

2

0,1206

R36

1

LOAD=NO

4

D

1K

1K

R221

1

R233

14B3>

31B3> 14B3> 13A5>

14B3> 13A5>

14B3> 13A5>

31B3> 14B3> 13A5> 15A4<

IN

IN

IN

IN

IN

C C

B B

1

15C4>15B4<31C3<

GPIO[6]

IN

A A

2

3

FAN CONTROL

INTERNAL ORGANISATION CAN BE CONFIGURED AS X8 OR X16, HERE IT IS CONFIGURED AS X16

VCCP_3_3

2

R26

1

2

15D7<

4.7K 4.7K

R27

1

LOAD=NO

2

4.7K470

R37

1

2

R38

1

15A4<

OUT

2

470

1

LOAD=NO

1

1

led

2

LOAD=NO

2

15C4>

15C4>

15C4>

15C4>

15C4>

EE_DI

EE_CLK

EE_CS

14B6<13A5<

15A8< 15B4< 31C3<

GPIO[3]GPIO[2]

2

470

R75

1

LOAD=NO

1

1

led

DS3

2

LOAD=NO

2

IN

IN

IN

IN

IN

R76

DS4

GPIO[4]

2

470

1

LOAD=NO

1

1

led

2

LOAD=NO

2

GPIO[0]

GPIO[1]

GPIO[2]

GPIO[3]

GPIO[7]

VCCP_3_3

AT93C46

U15

3

DI

2

SK

1

CS

7

DC

8

VCC

1

0.1UF,16V,0603

C19

2

GPIO[5]

R77

LOAD=NO

DS5

LOAD=NO

BODY:EEPROM

GPIO[6]

2

2

470

470

R79

R78

1

1

LOAD=NO

1

1

1

1

led

led

2

2

DS7

DS6

2

LOAD=NO

2

2

4.7K

R48

4.7K

1

LOAD=NO

LOAD=NO

2

470

R49

470

1

LOAD=NO

LOAD=NO

LOAD=NO

LOAD=NO

2

1

2

1

GPIO[7]

2

470

1

1

1

led

2

2

R50

R51

6

ORG

5

GND

4

EE_DO

DO

R80

DS8

VCCP_3_3

2

4.7K

R52

1

LOAD=NO

2

470

R53

1

LOAD=NO

OUT

2

4.7K

R54

1

LOAD=NO

2

470

R55

1

LOAD=NO

LOAD=NO

D

DATE:TITLE:

PAGE:

28-12-2004

15

1

GPIO, EEPROM AND FAN CONTROL

AGEIA_ARD

ENGINEER:

8

7

6

45

3

2

Page 16

CR-16 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE16

8

7

56

4

3

2

1

D

VCCP_3_3

B9

2

1

A

B

ferricbead

C C

1

1

C53

C150

2

2

0.01UF,16V,0603

1UF,25V,0603

CSX-750ABB-66.66MHZ

U22

4

1

OE

OSC_SMD

BODY:OSCILLATOR

22

3

OUTPUTVDD

2

GND

1

R219

2

CLK_CORE

2

1M

1

16B6<

OUT

R58

B B

U9

31B6<

VCCP_3_3

3.3

2

1

R165

1

C21

2

A A

33UF,6V,3528

MEM_AGND

16C3>

1

C39

2

100NF,6.3V,0402,X5R

C_RESET_IN_N

IN

CLK_CORE

IN

CORE_BYPASS_EN

IN

CORE_BYPASS_VCO

IN

MEM_BYPASS_EN

IN

MEM_BYPASS_VCO

IN

FILTER_VCCP33

MIPS_BYPASS_EN

IN

MIPS_BYPASS_VCO

IN

PXPLL_BYPASS_EN

IN

B2

C1

H7

E2

D5

B1

F5

A1

G7

G6

D6

F7

C_RESET_IN_N

CLK_CORE

CORE_BYPASS_EN

CORE_BYPASS_VCO

CORE_VAA

MEM_BYPASS_EN

MEM_BYPASS_VCO

MEM_VAA

MIPS_BYPASS_EN

MIPS_BYPASS_VCO

MIPS_VAA

PXPLL_BYPASS_EN

ATHENA_29X29

BODY:CLOCK_CKT

CORE_AGND

MIPS_AGND

MEM_AGND

F8

B3

A2

MIPS_AGND

CORE_AGND

MEM_AGND

D

CLOCK CIRCUITRY

8

7

6

45

ENGINEER:

3

AGEIA_ARD

28-12-2004

DATE:TITLE:

16

PAGE:

2

1

Page 17

CR-17 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE17

8

7

56

4

3

2

1

D

IDE_VCCP_5_0

LOAD=NO

PCI_VCCP_12_0

LOAD=NO

1

1

1

C33

2

2

0.1UF,25V

C C

REG_VCCP_3_3

1UF,25V,0603

C512

C34

2

100PF,6.3V,0402

2

D1

3 1

2

1

L4

F1

0.33UH

5AMPS

1

2

LOAD=NO

PHASE_VCCP_1_2

1

C52

2

100PF,6.3V,0402

1

1

1

C54

C119

2

100PF,6.3V,0402

100NF,6.3V,0402,X5R

C360

2

2

100NF,6.3V,0402,X5R

100PF,6.3V,0402

LOAD=NO

LOAD=NO

LOAD=NO

LOAD=NO

LOAD=NO

1

1

C506

C362

2

2

100PF,6.3V,0402

IND_VCCP_1_2

IND_VCCP_1_2

1

BOOT_VCCP_1_2

OCSETPVCC

BOOT

UGATE

PHASE

LGATE

COMP

GND

PGND

1

C37

2

27NF,16V,0603

0.01UF,16V,0603

2

2

10

1

9

8

1

12

4

7

11

1

1

C31

R204

680

2

1

2

0

R47

2

0

R45

2

ISL6522

10K

1

2

B B

1

1M

R43

1

2

220NF,10V,0402

U11

14

R187

C32

VCC

13

6

EN

3

SS

1

RT

5

FB

1.2NF,16V,0603

2

C35

8.25K,1%

2

1

R202

A A

0.1UF,25V

4

1

0.1UF,25V

C40

2

UGATE_VCCP_1_2

PHASE_VCCP_1_2

LGATE_VCCP_1_2

5

Q3

1

2

C10

IRF7811

2

1

876

3

876

5

IRF7831

4

Q4

3

1

2

1.5UH

1

L2

876

5

IRF7811

4

Q9

3

1

2

2

33NF,16V,0603

R207

4.99K,1%

1

56UF,25V,MM

2

2.7K,1%

2

2

1

C41

1

C42

2

680UF,2.5V,MM

R209

C45

2

56UF,25V,MM

1

1

1

1

1

1

C51

C50

C49

C47

C46

C43

2

2

680UF,2.5V,MM

1

49.9,1%

2

R210

2

2

680UF,2.5V,MM

680UF,2.5V,MM

1

2

2

680UF,2.5V,MM

680UF,2.5V,MM

VCCP_1_2

D

1.2V GENERATION

AGEIA_ARD

ENGINEER:

8

7

6

45

3

2

DATE:TITLE:

PAGE:

28-12-2004

17

1

Page 18

CR-18 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE18

LOAD=NO

1

C374

2

IND_VCCP_1_8

1

8

D

7

IDE POWER CONNECTOR

IDE_VCCP_12_0

IDE_VCCP_5_0

56

VRM_2V5_ENABLE

4

REG_VCCP_3_3

LP3982

U17

2

IN

7

SHDN_N

1

MX53109

J3

5V0

1

12V0

2

1

6 5

R81

LOAD=NO LOAD=NO

BODY:IDE_POWER_CONN

0

MECH2 MECH1

24

GND1

3

GND2

2

1

0

R82

C18

2

2.2UF,10V,0603

C C

PCI_VCCP_12_0

1

C24

0.1UF,25V

2

B B

VRM_1V8_ENABLE

2

R44

1M

1

1

2

220NF,10V,0402

A A

14

13

6

3

1

5

6.81K,1%

C23

1

2

2.05K,1%,0603

R203

1

1UF,25V,0603

ISL6522

U25

VCC

EN

SS

RT

FB

R179

1

2

C26

1.2NF,16V,0603

2

2

2

LOAD=NO

1

C513

2

OCSETPVCC

BOOT

UGATE

PHASE

LGATE

COMP

PGND

1

C28

2

C27

33NF,16V,0603

C29

100PF,6.3V,0402

GND

1

33NF,16V,0603

1

1

0.01UF,16V,0603

2

C55

2

1

10

1

9

8

R62

0

1

12

R61

4

7

11

2.7K,1%

R205

1

R206

R208

910

0

2

2

49.9,1%

1

0.1UF,25V

2

2

UGATE_VCCP_1_8

PHASE_VCCP_1_8

LGATE_VCCP_1_8

2

1

C12

2

BODY:LIN_REG

IDE_VCCP_12_0

2

1

2

D3

3

F3

0.33UH

L5

1

IND_VCCP_1_8

876

5

BOOT_VCCP_1_8

4

1

C30

2

IRF7805

Q5

3

1

2

876

5

0.1UF,25V

4

IRF7805

Q7

1

2

3

1

OUT1

4

OUT2

5

SET

8

FAULT_N

6

CC

3

GND

2

1

2.5AMPS

PHASE_VCCP_1_8

LOAD=NO

1

C56

2

56UF,25V,MM

3.3UH

2

1

L1

3

1

C22

2

33NF,16V,0603

1

C151

56UF,25V,MM

2

1

1

C38

2

2

680UF,2.5V,MM

680UF,2.5V,MM

2

VCCP_2_5

2

1

100K

R201

1

C25

2

2.2UF,10V,0603

LOAD=NO

LOAD=NO

LOAD=NO

1

1

C364

2

100PF,6.3V,0402

VCCP_1_8

1

C366

2

100PF,6.3V,0402

C368

2

100NF,6.3V,0402,X5R

100NF,6.3V,0402,X5R

1

C503

C48

2

680UF,2.5V,MM

D

28-12-2004

IDE CONNECTOR, 1.8 V AND 2.5V GENERATION

AGEIA_ARD

ENGINEER:

8

7

6

45

3

2

DATE:TITLE:

PAGE:

18

1

Page 19

CR-19 : @PCI_UNIV_8LR_LIB.PCI_UNIV_8LR(SCH_1):PAGE19

8

7

56

4

3

2

1

D

REG_VCCP_3_3

1

C11

2

100NF,6.3V,0402,X5R

2

2

1.3K

620,1%

2.8K,1%

R86

R128

1

1

VCCP_3_3

VCCP_2_5

2

VCCP_1_8

2

1K

1

R90

2

1K

1

R91

2

2

274,1%

R88

R130

1

1

1K

1

R92

C C

2

2

2

2

1K

1K

1K

R129

1

EVQPAE04M

LOAD=NO

SW1

1

A1

4

A2

B B

2

3

B1

B2

BODY:PUSH_SWITCH

1K

R89

R85

R87

1

1

1

1

1

C357

C17

2

2

0.1UF,16V,0603

0.1UF,16V,0603

2

1K

1

1UF,25V,0603

VCCP_1_2

R93

1

2

C273

PCI_VCCP_12_0

1

2

3

6

7

4

5

8

9

10

11

12

1

C358

2

0.01UF,16V,0603

C500

0.1UF,16V,0603

U12

VCC

1IN-

1IN+

2IN-

2IN+

3IN-

3IN+

4IN-

4IN+

GND

LM2901

BODY:LM2901

1

LOAD=NO

1OUT

2OUT

3OUT

4OUT

33K

2

R96

33K

2

1

R97

100K

1

R95

PCI_VCCP_12_0

2

1K

1K

R94

1

1

2

14

13

2

33K

2

1

R98

REG_VCCP_3_3

2

2

R99

1

2

1K

R100

1

1K

R101

1

VRM_1V8_ENABLE

VRM_2V5_ENABLE

C_RESET_N

OUT

OUT

OUT

REG_VCCP_3_3

6

5

2