Page 1

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

ASSEMBLYNVPNVARIANT

B

1

2

SKU

3

4

5

6

12

13

14

7

8

9

10

11

15

E266 - MXM PCI-E Desktop adapter card (Interposer)

Revision History:

A00: INITIAL VERSION - 600-10266-0000-000

2/19/04 - Adding in the Power Supplies and Cleaning up the look.

2/25/04 - Need to change back to P266 from E266

Table of Contents:

3/01/04 - Major Schematic Changes: All Power Supplies and I/O

3/04/04 - Cleaning up some Power Net errors + other stuff

3/10/04 - Updating changes from design review

3/12/04 - Change names back to E266, Pullups on DDCB_S* and swap Drain/

1. Title Page - This Page

2. PCI-E / MXM Connectors and Zero Buffer Delay

3. MXM I/O Connector, Power Good, DVI Connectors, Hotplug

4. VGA and TV Filters and Connecors

5. Panel Power and SPWG Panel I/O; 60 Pin Board to Board Con

3/16/04 - Added New Docking Station Connector Page 9.

3/17/04 - Added Mechanical HW page 8: Bracket and screws

3/19/04 - Added gnd to bracket, added net rules to TV and Dock TMDS nets

6. Power Supply I: VBAT, 5VRUN, 1V8RUN, External In

7. Power Supply II: 2V5RUN, 3V3RUN, 1V2_INT

8. Mechanical, Fan Control, DDC-C Config ROM

9. Docking Station Connector

10.LVDS - SPWG Panel Daughter Board

3/24/04 - Board has been REFDES re-sequenced, added 3 reserved signals

src on Q16 and Q17. Fixed 5V_DDC net. Added Pullups on I2C

nets and changed to the correct voltage.

U1 now power to 3V3_PEX was 3VRUN. deleted r155,157,159 tv.

Extin CKT: D4 changed pkg from sot23 to SMA. Moved D2 to Q1.

Q1 - changed part number same package, flipped Drain & SRC.

1V3_INT CKT: Use RUN_PWR_OK to EN.

Docking Connector TV signal pins changed, DDC SDATA/CLK pins

Changed.

2V5RUN: EN added 2 resistors from 5VRUN.

Fixed PWM controller: Had some wrong pins.

from MXM CN1 to docking connector.

A00: 600-10266-0000-100

4/06/04 - Fixed J2 4-pin power panel net from VBATT to VBAT.

A02: 600-10266-0000-200

BASE

0000BRINGUP

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

600-10266-base-sch

600-10266-0000-200

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

E266-A02 MXM Adapter Board

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

Table of Contents

6/01/04 - Fixed VBAT FET swapped Drain and Source

6/07/04 - Added R117 1210 1/4W pull-down to sink diode

6/09/04 - Fixed DAC/TV Impedance rule 50+/-2. This changes 75 to 150.

A03: 600-10266-0000-300

9/16/04 - Add New MXM Connector for P311.

10/18/04 - C14 package change to 1206 from 1210.

Added N-chn fet for the 1V8 Power supply LED to 5V. Was not

bright enough before.

Changed value of R502 on 2V5RUN linear to 8.2K. Voltage on

enable pin was too low before.

5VRUN, 1V8RUN, and 3V3RUN ISL6224 switcher EN pin 3 was

getting too high with VBAT >19V or 7V EN. This caused the

switcher not to work. Added Comparator to EN 5VRUN, and used

5VRUN for 1V8RUN and 3V3RUN.

External/12V_PEX input sense circuit did not work on A00.

Added 2 more FETS to set the external VBAT switcher voltage.

CN1 mxm connector changed 4 pin nets. 1V8RUN, 5VRUN, RUNPWROK.

Added MXM_CUTOUT symbol to ground the mxm mounting holes.

Added LVDS ZIF connector for Panel Power

leakage current at high temp.

Change Board outline in Lower right corner to fit into Alviso.

Added Page 10. LVDS brd to Brd Daughter board interface.

New 2x30 brd tio brd connector for LVDS qualification.

Power Supply fets changed to 12V_PEX from VBAT.

Added AC_BATT* circuit.

600-10266-0000-300

e266_a03

e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03

pmelucci

pmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmelucci

1 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 101 OF 10

9-JUN-2004

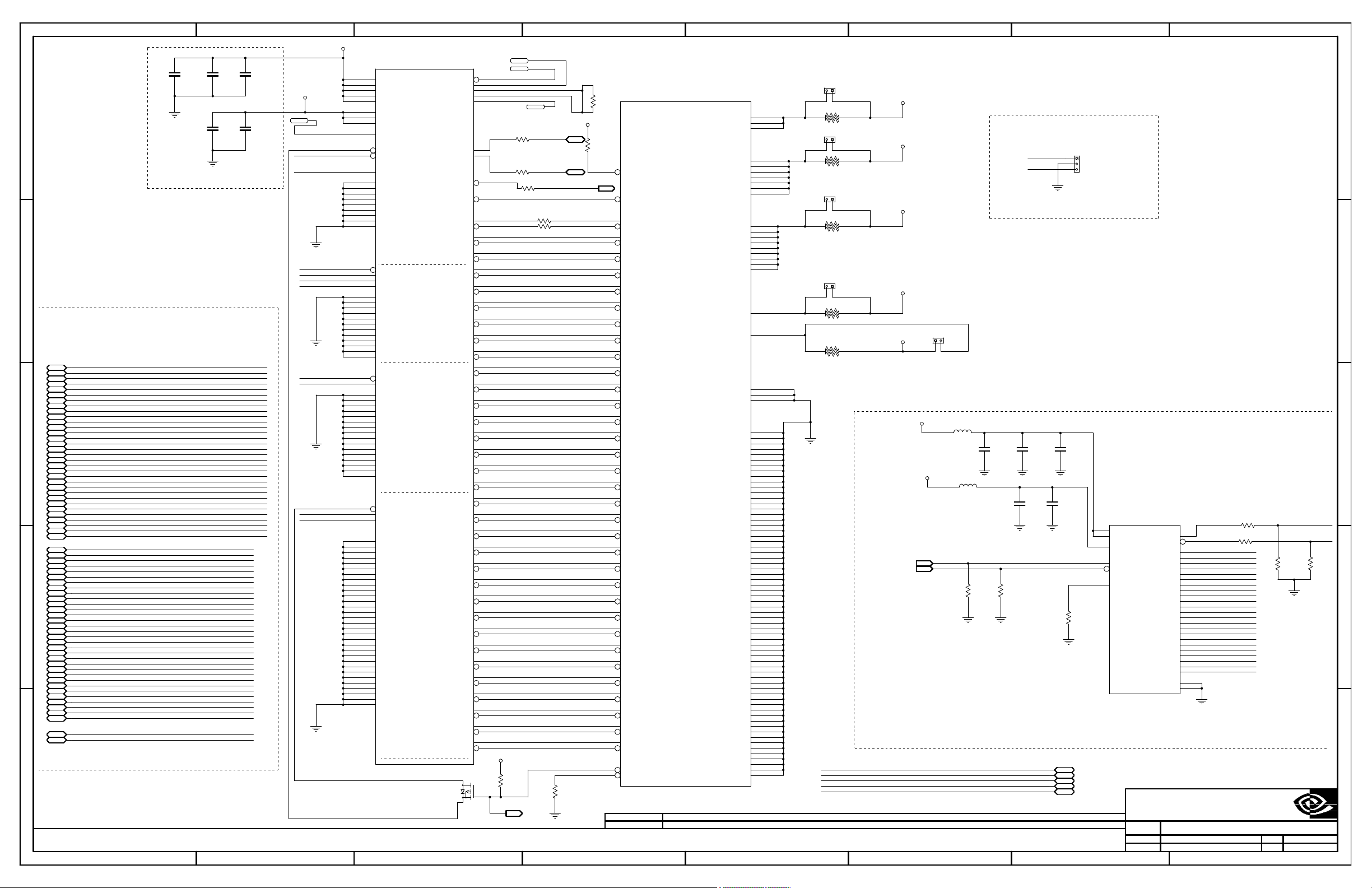

Page 2

TP_3V3AUX_PEX

IN

IN

NC0

NC1

NC4

NC3

NC5

NC6

NC2

NC7

NC12

NC15

NC9

NC8

NC10

NC14

NC13

NC11

NC16

NC17

NC18

NC19

NC20

NC21

NC22

GND

CLK_OUT*

CLK_OUT

PAD_GND

VDD0

VDD1

CLK_IN

CLK_IN*

IREF

VDDA

BIBIBIBIBI

BIBIOUT

1/2 PCI-Express, Power

PEX_RST

CLK_REQ

PEX_REFCLK

PEX_RX0

PEX_RX0

PEX_TX0

PEX_TX0

PEX_RX1

PEX_TX1

PEX_TX2

PEX_RX2

PEX_REFCLK

PEX_RX1

PEX_TX1

PEX_RX2

PEX_TX2

PEX_RX3

PEX_TX3

PEX_RX4

PEX_RX5

PEX_TX4

PEX_RX6

PEX_TX5

PEX_RX3

PEX_TX3

PEX_RX4

PEX_TX4

PEX_RX5

PEX_TX5

PEX_RX6

PEX_TX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX9

PEX_RX7

PEX_TX6

PEX_TX6

PEX_RX7

PEX_TX7

PEX_RX8

PEX_RX10

PEX_RX10

PEX_TX10

PEX_TX10

PEX_RX11

PEX_RX11

PEX_TX11

PEX_TX11

PEX_RX12

PEX_RX12

PEX_RX13

PEX_RX12

PEX_TX12

PEX_RX13

PEX_TX13

PEX_TX13

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX14

PEX_RX15

PEX_RX15

PEX_TX15

PEX_TX15

PRSNT1

PRSNT2

3V3RUN

3V3RUN

1V8RUN

1V8RUN

1V8RUN

1V8RUN

1V8RUN

1V8RUN

1V8RUN

3V3RUN

PWR_SRC

PWR_SRC

2V5RUN

PWR_SRC

PWR_SRC

PWR_SRC

PWR_SRC

PWR_SRC

PWR_SRC

PWR_SRC

GND

GND

5VRUN

PAD

PAD

PAD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

OUT

D

S

G

BIBIBIBIBIBIBI

END OF X4

END OF X1

END OF X16

END OF X8

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

WAKE

SMDAT

SMCLK

PERST

REFCLK

PERP0

PERN0

REFCLK

PETP0

PERN1

PERP1

PETN0

PERP2

PETN1

PETP1

PETP2

PETN3

PETP3

PERN3

PETN2

PERN2

PERP3

PETP4

PERP5

PETN4

PERN4

PERP4

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PETP8

PETN8

PERN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN12

PERP12

PETN11

PETP11

PERN11

PETN13

PETP12

PETN12

PERN13

PETP13

PERP13

PERP14

PETN15

PETP15

PERN15

PERP15

PERN14

PETN14

PETP14

TRST* JTAG1+12V

+12V/RSVD

+3V3AUX

+12V

+12V

+12V

+3V3

+3V3

+3V3

PRSNT2

PRSNT1

GND

GND

RSVD

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

RSVD

GND

GND

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

GND

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

BIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBI

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

NO STUFF

PCIE_PRSNT1*

12V_PEX

C69

4.7UF

25V

10%

X5R

1206

COMMON

GND

C534

4.7UF

25V

10%

X5R

1206

COMMON

C533

4.7UF

25V

10%

X5R

1206

COMMON

GND

C70

0.1UF

16V

10%

X5R

0402

COMMON

C71

0.1UF

16V

10%

X5R

0402

COMMON

3V3_PEX

TP2

SNN_PEX_PRSNT2_A

Place caps near connector!

3GIO NET RULES

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

PEX_RX0

PEX_RX0*

PEX_RX1

PEX_RX1*

PEX_RX2

PEX_RX2*

PEX_RX3

PEX_RX3*

PEX_RX4

PEX_RX4*

PEX_RX5

PEX_RX5*

PEX_RX6

PEX_RX6*

PEX_RX7

PEX_RX7* PEX_RX7

PEX_RX8

PEX_RX8*

PEX_RX9

PEX_RX9*

PEX_RX10

PEX_RX10*

PEX_RX11

PEX_RX11*

PEX_RX12

PEX_RX12*

PEX_RX13

PEX_RX13*

PEX_RX14

PEX_RX14*

PEX_RX15

PEX_RX15*

PEX_REFCLK

PEX_REFCLK*

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

4MILS

DIFFPAIRMIN_LINE_WIDTHNET

PEX_TX0

PEX_TX0

PEX_TX1

PEX_TX1

PEX_TX2

PEX_TX2

PEX_TX3

PEX_TX3

PEX_TX4

PEX_TX4

PEX_TX5

PEX_TX5

PEX_TX6

PEX_TX6

PEX_TX7

PEX_TX7

PEX_TX8

PEX_TX8

PEX_TX9

PEX_TX9

PEX_TX10

PEX_TX10

PEX_TX11

PEX_TX11

PEX_TX12

PEX_TX12

PEX_TX13

PEX_TX13

PEX_TX14

PEX_TX14

PEX_TX15

PEX_TX15

PEX_RX0

PEX_RX0

PEX_RX1

PEX_RX1

PEX_RX2

PEX_RX2

PEX_RX3

PEX_RX3

PEX_RX4

PEX_RX4

PEX_RX5

PEX_RX5

PEX_RX6

PEX_RX6

PEX_RX7

PEX_RX8

PEX_RX8

PEX_RX9

PEX_RX9

PEX_RX10

PEX_RX10

PEX_RX11

PEX_RX11

PEX_RX12

PEX_RX12

PEX_RX13

PEX_RX13

PEX_RX14

PEX_RX14

PEX_RX15

PEX_RX15

PEX_REFCLK

PEX_REFCLK

NET_SPACING_RULE

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

Silkscreen Text by TestPoint!

MXM PRESENT

GND

SNN_PEX_PRSNT2_B

SNN_PEX_RSVD2

SNN_PEX_RSVD3

SNN_PEX_RSVD4

GND

SNN_PEX_PRSNT2_C

SNN_PEX_RSVD5

GND

PCIE_PRSNT2*

SNN_PEX_RSVD6

SNN_PEX_RSVD7

GND

CN2

CON_X16NONPHY-X16

CON_PCIEXP_X16_EDGE

COMMON

B1

B2

A2

A3

B3

B8

A9

A10

B10

A1

B17

B12SNN_PEX_RSVD1

B4

A4

B7

A12

B13

A15

B16

B18

A18

B31

A19

B30

A32

A20

B21

B22

A23

A24

B25

B26

A27

A28

B29

A31

B32

B48

A33

A34

B35

B36

A37

A38

B39

B40

A41

A42

B43

B44

A45

A46

B47

B49

A49

B81

A50

B82

A51

B52

B53

A54

A55

B56

B57

A58

A59

B60

B61

A62

A63

B64

B65

A66

A67

B68

B69

A70

A71

B72

B73

A74

A75

B76

B77

A78

A79

B80

A82

TP0610T

SOT23_1G1D1S

MAX_VOLTAGE=60V

CONTINUOUS_CURRENT=0.12A@25C

R_DS_ON=10R

MAX_CURRENT=0.4A

MAX_WATTAGE=0.36W@25C

V_BE_GS=-2.4V

COMMON

3

Q9

2

TP3

TP4

TP_PEX_JTAG_TRST*

B9

TP_PEX_JTAG_TCLK

A5

PEX_JTAG_TDI_TDO

A6

A7

TP_PEX_JTAG_TMS

A8

Make these Test points

available for JTAG use

R549

0

PCIE_SMB_CLK

B5

B6

PCIE_SMB_DATA

B11

A11

A13

A14

A16

A17

B14

B15

A21

A22

B19

B20

A25

A26

B23

B24

A29

A30

B27

B28

A35

A36

B33

B34

A39

A40

B37

B38

A43

A44

B41

B42

A47

A48

B45

B46

A52

A53

B50

A56

A57

B54

B55

A60

A61

B58

B59

A64

A65

B62

B63

A68

A69

B66

B67

A72

A73

B70

B71

A76

A77

B74

B75

A80

A81

B79

COMMON

R548

0

COMMON

WAKE*

PERST*

Zero Delay Buffer Bypass

PEX_REFCLK

PEX_REFCLK*

PEX_TX0

PEX_TX0*

PEX_RX0

PEX_RX0*

PEX_TX1

PEX_TX1*

PEX_RX1

PEX_RX1*

PEX_TX2

PEX_TX2*

PEX_RX2

PEX_RX2*

PEX_TX3

PEX_TX3*

PEX_RX3

PEX_RX3*

PEX_TX4

PEX_TX4*

PEX_RX4

PEX_RX4*

PEX_TX5

PEX_TX5*

PEX_RX5

PEX_RX5*

PEX_TX6

PEX_TX6*

PEX_RX6

PEX_RX6*

PEX_TX7

PEX_TX7*

PEX_RX7

PEX_RX7*

PEX_TX8

PEX_TX8*

PEX_RX8

PEX_RX8*B51

PEX_TX9

PEX_TX9*

PEX_RX9

PEX_RX9*

PEX_TX10

PEX_TX10*

PEX_RX10

PEX_RX10*

PEX_TX11

PEX_TX11*

PEX_RX11

PEX_RX11*

PEX_TX12

PEX_TX12*

PEX_RX12

PEX_RX12*

PEX_TX13

PEX_TX13*

PEX_RX13

PEX_RX13*

PEX_TX14

PEX_TX14*

PEX_RX14

PEX_RX14*

PEX_TX15

PEX_TX15*

PEX_RX15B78

PEX_RX15*

3V3_PEX

R63

10K

1G1D1S

5%

0402

COMMON

1

NO STUFF

NO STUFF

5%

5%

R550

0

NO STUFF

5.1D<

5.3F<

TP5

NO STUFF

0402

SMB_CLK

0402

SMB_DATA

5%

0402

MXM_THREM_ALERT*

R545

5%

0

COMMON

COMMON

0

R546

0402

MXM_REFCLK

MXM_REFCLK*

5%

MXM_PRSNT1*

MXM_PRSNT2*

R62

10K

5%

0402

COMMON

GND

3V3RUN

MXM_CLK_REQ*

0402

R551

0

5%

0402

NO STUFF

R522

10K

5%

0402

COMMON

137

139

135

133

129

127

132

130

123

121

126

124

117

115

120

118

111

109

114

112

105

103

108

106

99

97

102

100

93

91

96

94

87

85

90

88

81

79

84

82

75

73

78

76

69

67

72

70

63

61

66

64

57

55

60

58

51

49

54

52

45

43

48

46

39

37

42

40

134

38

2. PCI-E / MXM Connectors

CON_MXM_ULTRA_PCIE_X16_MB

8.5A<

5.3D<> 3.3A<>

8.5A<>

5.3D<> 3.3A<>

3.3A<

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PCI-E / MXM Connectors

CN1

ULTRA-PHY-X16

ULTRA-PHY

COMMON

240

242

238

4

6

8

10

12

14

2

3

5

7

9

11

13

15

1

E1

234

18

243

244

245

19

21

22

23

24

17

20

41

44

47

50

53

56

59

62

65

68

71

74

77

80

83

86

89

92

95

98

101

104

107

110

113

116

119

122

125

128

131

138

142

146

150

154

158

164

170

176

182

187

188

194

199

200

205

206

211

212

218

223

229

235

236

241

E2

MXM_3V3RUN

MXM_1V8RUN

MXM_2V5RUN

MXM_5VRUN

MXM_VBAT

2.54MM

COMMON

RL7520

2.54MM

COMMON

RL7520

2.54MM

COMMON

RL7520

2.54MM

COMMON

RL7520

RL7520

GND

NORM

RS4

NORM

RS1

RS3

NORM

RS5

RS2

J19

Silkscreen Text by Header!

HDR_1M2

MALE

0

1

2

0.01

J16

HDR_1M2

MALE

0

1

2

0.01

J18

HDR_1M2

MALENORM

0

1

2

0.01

COMMON

J20

HDR_1M2

MALE

0

1

2

0.01

0.01

NET

MXM_VBAT

MXM_2V5RUN

MXM_1V8RUN

MXM_3V3RUN

MXM_5VRUN

CUR_3V3RUN

3V3RUN

1%COMMON

1V8RUN

1%COMMON

VBAT

1%

2V5RUN

1%COMMON

J17

HDR_1M2

5VRUN

1%COMMON

MALE

NORM

2.54MM

0

COMMON

1

2

3V3RUN

LB3

NO STUFF

BEAD_0603

3V3RUN

LB5

NO STUFF

BEAD_0603

Pleace one 0.047uF cap per pin

2.5A<>

2.5A<>

Pleace Termination Resistors as Close

as Possible to ICS9DB

GND

MIN_LINE_WIDTH

50 MIL

12 MIL

50 MIL

12 MIL

12 MIL

15.0

6.0

External PRG CON

SMB_CLK

1

J26

HDR_1M3

2

SMB_DATA

MALE

3

2.54MM

0

NORM

COMMON

GND

Pleace one 0.01uF cap per pin

GND

GND

C54

.047UF

16V

10%

X7R

0402

NO STUFF

C68

10UF

6.3V

20%

X5R

NO STUFF

ICS9DB202_VDD

C64

.047UF

16V

10%

X7R

0402

NO STUFF

GND

ICS9DB202_VDDA

C67

.047UF

16V

10%

X7R

04020805

NO STUFF

GND

U9

ICS9DB202-01

MLF32

MLF32

NO STUFF

13

20

150-220R@100MHz

C61

10UF

6.3V

20%

X5R

0805

NO STUFF

GND

150-220R@100MHz

3

R84

475

1%

0402

NO STUFF

4

5

1IREF

R85

49.9

1%

0402

NO STUFF

GND

PEX_REFCLK

PEX_REFCLK*

R86

49.9

1%

0402

NO STUFF

GND

Zero Delay Buffer

For High Jitter Motherboard PEX_REFCLKs

VOLTAGE

12V

2.5V

1.8V

3.3V

5V

600-10266-0000-300

e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03

e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03

pmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmelucci

pmelucci

Place resistors near ICS9DB202

CLk_OUT

9

CLK_OUT*10

SNN_ICS9DB202_NC0

2

SNN_ICS9DB202_NC1

6

SNN_ICS9DB202_NC2

7

SNN_ICS9DB202_NC3

8

SNN_ICS9DB202_NC4

11

SNN_ICS9DB202_NC5

12

SNN_ICS9DB202_NC6

14

SNN_ICS9DB202_NC7

15

SNN_ICS9DB202_NC8

16

SNN_ICS9DB202_NC9

17

SNN_ICS9DB202_NC10

18

SNN_ICS9DB202_NC11

19

SNN_ICS9DB202_NC12

21

SNN_ICS9DB202_NC13

22

SNN_ICS9DB202_NC14

23

SNN_ICS9DB202_NC15

24

SNN_ICS9DB202_NC16

25

SNN_ICS9DB202_NC17

26

SNN_ICS9DB202_NC18

28

SNN_ICS9DB202_NC19

29

SNN_ICS9DB202_NC20

30

SNN_ICS9DB202_NC21

31

SNN_ICS9DB202_NC22

32

27

33

R83

0402

R82

0402

5%

5%

33

NO STUFF

33

NO STUFF

GND

MXM_REFCLK

MXM_REFCLK*

R88

49.9

1%

0402

NO STUFF

2 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 102 OF 10

9-JUN-2004

GND

R89

49.9

1%

0402

NO STUFF

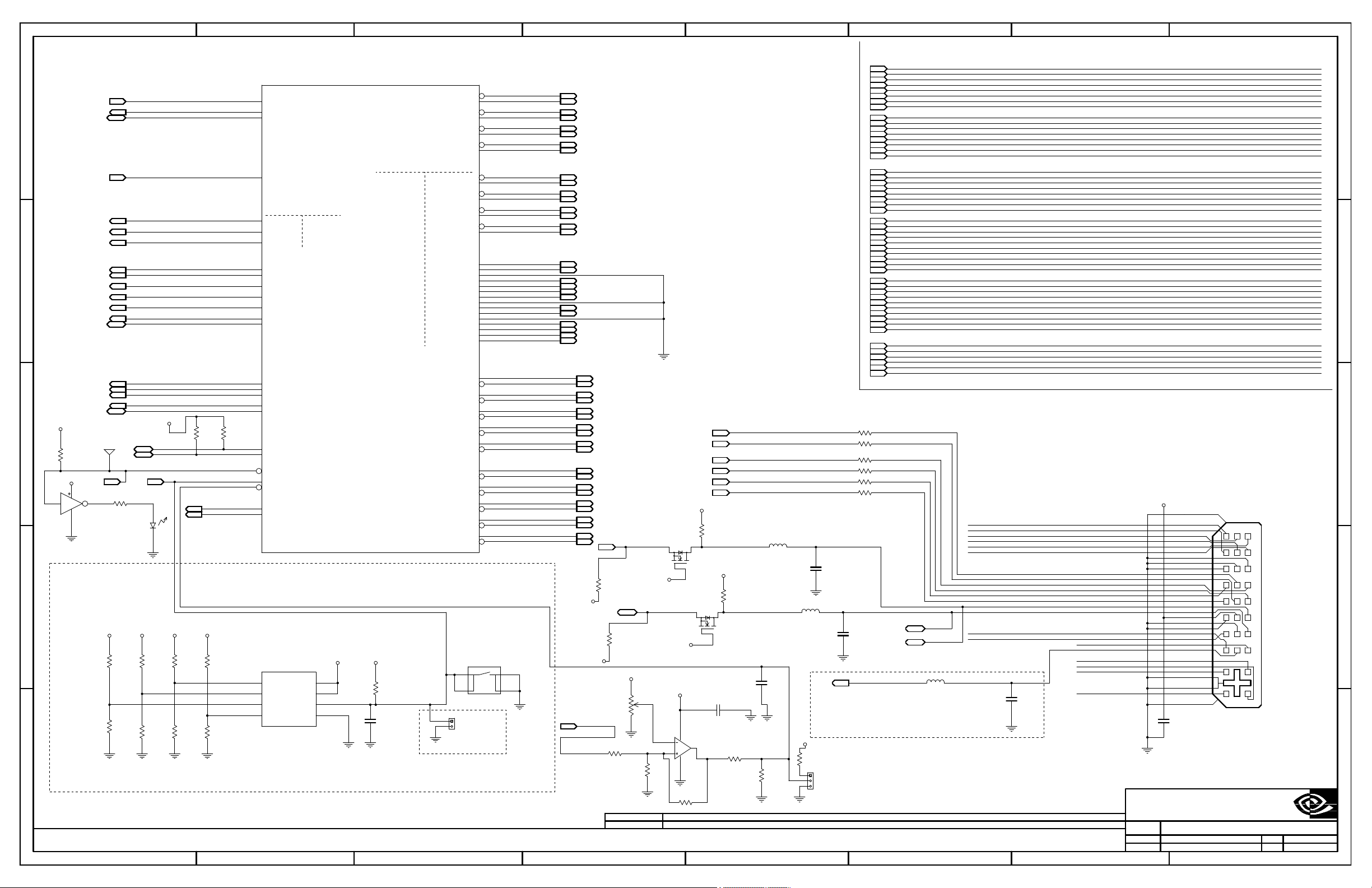

Page 3

1917

81624

C1

C5A

C2

C3

C5

C4

SHIELD2

SHIELD1

SHLD05

SHLD13

SHLD24

TX0-

TX1-

TX2-

TX1+

TX0+

TX2+

TX3TX3+

TX4-

DDCC

TX4+

TX5TX5+

GND

VDDC

DDCD

TXC-

SHLDC

TXC+

HPD

R

VSYNC

G

AGND2

AGND1

B

HSYNC

BIBIINININININININININININININININININININININININININININININININININININININININININININININININININ

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

ININININININOUT

S

D

G

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

S

D

G

BI

IN

OUT

OUT

OUT

OUT

IN

V+

V-

ININBI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTBIOUT

OUT

OUT

MXM DVI-BIGP

2/2 IO - LVDS,DVI,VGA,TV

HDTVSDTV

DVI_A_CLK

DVI_A_TX0

DVI_A_TX0

DVI_A_TX1

DVI_A_TX1

DVI_A_TX2

DVI_A_CLK

DVI_A_TX2

DVI_B_CLK

DVI_B_CLK

DVI_B_TX2

DVI_B_TX2IGP_LTX2

IGP_LTX2

IGP_LCLK

IGP_LCLK

DVI_B_TX1

DVI_B_TX0

DVI_B_TX0

DVI_B_TX1

IGP_LTX0

IGP_LTX0

IGP_RSVD

IGP_RSVD

IGP_RSVD

IGP_RSVD

IGP_RSVD

IGP_RSVD

IGP_RSVD

IGP_RSVD

IGP_RSVD

IGP_RSVD

IGP_LTX1

IGP_LTX1

IGP_RSVD

LVDS_UTX1

LVDS_UTX2

LVDS_UTX2

LVDS_UTX3

LVDS_UTX0

LVDS_UTX0

LVDS_UTX1

IGP_RSVD

IGP_RSVD

IGP_RSVD

IGP_RSVD

LVDS_UTX3

LVDS_UCLK

LVDS_LTX0

LVDS_LTX0

LVDS_UCLK

LVDS_LTX1

LVDS_LTX3

LVDS_LCLK

LVDS_LTX2

LVDS_LTX3

LVDS_LTX2

LVDS_LTX1

LVDS_LCLK

DDCB_SDATA

DDCB_SCLK

DVI_A_HPD

DVI_B_HPD

HDTV_Pr

HDTV_Y

HDTV_PbTV_CVBS

TV_Y

TV_C

VSYNC

HSYNC

VGA_RED

VGA_BLU

VGA_GRN

DDCA_SCLK

DDCA_SDATA

DDCC_SDATA

LVDS_PPEN

LVDS_BLEN

DDCC_SCLK

LVDS_BL_BRGHT

RSVD

RSVD

AC/BATT*

RUNPWROK

SMB_CLK

SMB_DAT

THERM

EN

VCC

GND

PGOOD

UVLO_D

UVLO_B

UVLO_C

UVLO_A

OUT

OUTBIBIINOUTBIIN

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

CN1

CON_MXM_ULTRA_PCIE_X16_MB

(ULTRA-(N))(NON)PHY(-X16)

ULTRA-PHY

COMMON

217

232

230

219

221

237

239

231

233

225

227

DVI_A_CLK*

DVI_A_CLK

DVI_A_TX0*

DVI_A_TX0

DVI_A_TX1*

DVI_A_TX1

DVI_A_TX2*

DVI_A_TX2

3.1F<

3.1F<

3.1F<

C-Link

3.1F<

3.1F<

3.1F<

3.1F<

3.1F<

3.4E>

3.4D<

3.4D<>

MXM_DVI_A_HPD

MXM_DDCB_SCLK

MXM_DDCB_SDATA

3. MXM I/O & DVI Connectors & Power Good

goes to dvi-a and docking thru r's

Goes to docking station

IGPL_DVIB_CLK*

S6

SW_KT11P2SM

SMD_4

COMMON

2

3

J3

HDR_JMPR_1M2

MALE

2.54MM

0

NORM

COMMON

189

IGPL_DVIB_CLK

191

IGPL_DVIB_TX2*

201

IGPL_DVIB_TX2

203

IGPL_DVIB_TX1*

207

IGPL_DVIB_TX1

209

IGPL_DVIB_TX0*

213

IGPL_DVIB_TX0

215

IGP_UCLK*

159

IGP_UCLK

161

163

IGP_UTX3*

165

IGP_UTX3

167

IGP_UTX2*

171

173 IGP_UTX2

175

IGP_UTX1*

177

IGP_UTX1

179

181

IGP_UTX0*

183

IGP_UTX0

185

IGP_LTX3*

195

IGP_LTX3

197

LVDS_UTX0

186

LVDS_UTX0*

184

LVDS_UTX1

180

LVDS_UTX1*

178

LVDS_UTX2

174

LVDS_UTX2*

172

LVDS_UTX3

168

LVDS_UTX3*

166

LVDS_UCLK

162

LVDS_UCLK*

160

LVDS_LTX0

216

LVDS_LTX0*

214

LVDS_LTX1

210

LVDS_LTX1*

208

LVDS_LTX2

204

LVDS_LTX2*

202

198 LVDS_LTX3

LVDS_LTX3*

196

LVDS_LCLK

192

LVDS_LCLK*

190

AC_BATT*

1

4

GND

6.5C<>

3.1F<

3.1F<

3.1F<

3.1F<

3.1F<

3.1F<

3.1F<

3.1F<

3.1F<

5.5H<

5.5F<

3.2F<

3.2F< 5.2E> 5.4F<

3.2F<

3.1F<

3.1F<

3.1F<

5.4H<

5.4F<

3.1A>

3V3RUN

VBAT_EXTERNAL_IN

5.2E>

5.2E>

3.3E<

3.3E<

3.3E<

3.3E<

D-Link

3.3E<

5.2E>

5.3E>

5.2E>

5.2E>

5.2E>

5.2E>

5.2E>

3.2F<

3.2F<

3.2F<

3.2F<

3.2F<

B-Link

4-7

3.2F<

3.2F<

3.2F<

3.2F<

3.2F<

3.2F<

A-Link

0-3

3.2F<

3.2F<

3.2F<

R511

4.7K

5%

0402

NO STUFF

3.1A<>

3V3RUN

R126

0-500K

10%

SMD_3

COMMON

R122

0402

9.2D<

9.2D<

5.2E> 9.2D<

5.2E> 9.2D<

5.2E> 9.2D<

5.2E> 9.2D<

3.1F<

5.2E> 9.2D<

5.5H<

5.5F<

5.4H<

5.4H<

5.4F<

5.4H<

5.4F<

5.3B<

5.3B<

5.3B<

5.3B<

5.3B<

9.2D<

5.3B<

5.3B<

9.2D<

9.2D<

5.4B<

5.4B<

9.2D<

5.4B<

9.2D<

5.4B<

3.2F< 5.3B<

5.3B<

5.3B<

5.3B<

MXM_DDCB_SCLK

MAX_WATTAGE=0.36W@25C

MAX_CURRENT=0.88A

CONTINUOUS_CURRENT=0.22A@31C

SOT23_1G1D1S

R517

4.7K

5%

0402

NO STUFF

12V_PEX

1

AC_BATT_THRES

3

GND

AC_BATT_EX_IN

10K

COMMON

5%

5.2E> 9.2D< 3.3E<

GND

5.3B<

3.2F<

5.3B< 3.2F<

5.3B< 3.2F<

5.2E>

5.2E>

5.2E>

5.2E>

5.2E>

3.2F<

5.3B<

V_BE_GS=+/-20V

MAX_VOLTAGE=50V

R_DS_ON=3.5R

3V3RUN

MXM_DDCB_SDATA

MAX_WATTAGE=0.36W@25C

CONTINUOUS_CURRENT=0.22A@31C

3.2D>

9.2D<

3.2D>

3.2D>

3.2D>

3.1F<

3.2D>

2

1

V_BE_GS=+/-20V

MAX_CURRENT=0.88A

MAX_VOLTAGE=50V

R_DS_ON=3.5R

SOT23_1G1D1S

3V3RUN

AC_BATT*

3.1F<

5.2E>

3.1F<

3.1F<

3.1F<

3.1D>

3.1F<

5V_DDC

3

Q503

BSS138

1G1D1S

COMMON

2

1

R509

2.2K

5%

0402

COMMON

FET_DDCB_SCLK

5V_DDC

3

Q504

BSS138

1G1D1S

COMMON

R515

2.2K

5%

0402

COMMON

FET_DDCB_SDATA

LB503

BEAD_0603

12V_PEX

2

2

4

3

R123

5

10K

5%

0402

COMMON

GND

R124

GND

0603

5%

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

MXM I/O & DVI Connectors

C72

0402

U11

SOT23_5

LMC7211

COMMON

AC_BATT_COMP_OUT

1

10M

COMMON

R127

0402

.1UF

16V

10%

X5R

COMMON

GNDGND

3.09K

COMMON

1%

GND

MXM_DVI_B_HPD

DACB_GREEN

TVY

DACB_RED

TVC

DACB_BLUE

TVCVBS

DACA_VSYNC

DACA_HSYNC

DACA_RED

DACA_GREEN

DACA_BLUE

MXM_DDCA_SCLK

MXM_DDCA_SDATA

LVDS_PPEN

LVDS_BLEN

LVDS_BL_BRGHT

DDCC_SCLK

DDCC_SDATA

3V3RUN

SMB_DATA

SMB_CLK

Pull-ups incase MB leaves floating

7.1F<

THREM_LED

1K

COMMON

5%

LED_TH_3MM

DS6

15MA

2.2V

RED

2.1D>

TH

COMMON

9.3F<

2

9.3F<

1

GND

MXM_THREM_ALERT*

R524

47K

5%

0402

COMMON

RUN_PWR_OK

AC_BATT*

MXM_RSVD_1

MXM_RSVD_2

4.3E<

4.4E< 4.1F>

8.5A<>

2.1D<>

5.3D<>

Output drive 2ma. Good enough.

8.2A<>

8.2A<

3V3RUN

2

5.4D<>

3V3RUN

R48

47K

5%

0402

COMMON

GND

4.5A<

5

3

4.1A<>

5.1E<>

9.4C<>

8.5A<

2.1D<>

5.3D<>

U6

SINGLE

SC70

COMMON

9.3F>

4.1F>

4.1F> 4.3E<

4.2A<

4.3A<

4.1F> 4.3A<

4.1F> 4.4A<

4.1F>

4.1A<

5.4D<

5.4D<

5.4D<

9.4C<

5.1E> 5.4D<

TP1

TESTPOINT2

SCHMOO

NO STUFF

1

THREM_BUF_OUT*

4

R49

0402

Check to make sure threshold includes 5% tol.!

VBAT

R15

7.15K

1%

0402

COMMON

5VRUN

R12

10K

5%

0402

COMMON

2V5RUN

R11

10K

5%

0402

COMMON

1V8RUN

R14

1K

R13

5%

2.7K

0402

5%

COMMON

0402

Approx. 1V Threshold for nominal rail voltages

Approx. ~.8V Threshold for NV_12V

R10

6.8K

5%

0402

COMMONCOMMON

GNDGNDGNDGND

193

140

136

144

153

151

148

152

156

155

157

224

228

226

222

220

R523

47K

5%

0402

COMMON

145

147

149

16

169

141

143

Power Good

R16

10K

5%

0402

COMMON

2V5_GOOD

5V_GOOD

VBAT_GOOD

1V8_GOOD

R17

12.4K

1%

0402

COMMON

U3

ISL6536

S08

COMMON

8

7

6

5

Vref = 0.62V

Hys = <40uS

Delay= 5uS(typical)

3V3_PEX

1

3

2

4

3V3_PEX

GNDGND

R20

10K

5%

0402

COMMON

C3

.47UF

10V

10%

X7R

0603

COMMON

1

2

GND

JUMPER to Force Power good to not ready.

Please Indicate State on Silk Screen

9.2D< 5.2E>

9.2D< 5.2E>

9.2D< 5.2E>

9.2D< 5.2E>

9.2D< 5.2E>

9.2D< 5.2E>

D-Link

IGPL_DVIB_TX0*

IGPL_DVIB_TX0

IGPL_DVIB_TX1*

IGPL_DVIB_TX1

IGPL_DVIB_TX2*

IGPL_DVIB_TX2

150-220R@100MHz

COMMON

LB504

BEAD_0603

C78

.22UF

16V

20%

X7R

0603

COMMON

AC_BATT*

R128

1K

5%

0402

COMMON

9.2D<

5.5F<

5.5H<

5.4F<

5.4H<

5.4F<

5.4H<

5.4F<

5.4H<

9.3F<>

9.3F<

3V3RUN

R125

0

5%

0402

COMMON

1

2

3

GND

5.2E> 9.2D<

5.2E>

3.3E<

3.3E<

3.3E<

3.3E<

3.3E<

3.3E<

5.3E>

5.2E>

5.2E>

5.2E>

5.2E>

5.2E>

5.2E>

5.2E>

5.3B<

5.3B<

5.3B<

5.3B<

5.3B<

5.3B<

5.3B<

5.3B<

5.3B<

5.3B<

5.4B<

5.4B<

5.4B<

5.3B<

5.3B<

5.3B<

5.3B<

5.3B<

5.3B<

C511

220PF

50V

5%

COG

0402

COMMON

GND

150-220R@100MHz

COMMON

3.4F<>

3.4F<>

GND

3.1A<

AC_BATT_PULLUP

J23

HDR_1M3

MALE

2.54MM

0

NORM

COMMON

9.3F<

0

COMMON

0

COMMON

0

0

COMMON

0

COMMON

0

COMMON

DVI_A_CLK

DVI_A_CLK*

DVI_A_TX0

DVI_A_TX0*

DVI_A_TX1

DVI_A_TX1*

DVI_A_TX2

DVI_A_TX2*

IGPL_DVIB_CLK

IGPL_DVIB_CLK*

IGPL_DVIB_TX0

IGPL_DVIB_TX0*

IGPL_DVIB_TX1

IGPL_DVIB_TX1*

IGPL_DVIB_TX2

IGPL_DVIB_TX2*

IGP_UCLK

IGP_UCLK*

IGP_UTX0

IGP_UTX0*

IGP_UTX1

IGP_UTX1*

IGP_UTX2

IGP_UTX2*

LVDS_UTX0

LVDS_UTX0*

LVDS_UTX1

LVDS_UTX1*

LVDS_UTX2

LVDS_UTX2*

LVDS_UTX3

LVDS_UTX3*

LVDS_UCLK

LVDS_UCLK*

LVDS_LTX0

LVDS_LTX0*

LVDS_LTX1

LVDS_LTX1*

LVDS_LTX2

LVDS_LTX2*

LVDS_LTX3

LVDS_LTX3*

LVDS_LCLK

LVDS_LCLK*

DVI_IGPL_DVIB_TX0

DVI_IGPL_DVIB_TX0*

DVI_IGPL_DVIB_TX1

DVI_IGPL_DVIB_TX1*

DVI_IGPL_DVIB_TX2

DVI_IGPL_DVIB_TX2*

DVI_DDCB_SDATA

3.4F<>

9.3F<>

3.4F<>

DVI_DDCB_SCLK

LB505

BEAD_0603

3.1D>

3.1D>

3.1D>

3.1D>

3.1D>

3.1D>

3.1D>

3.1D>

3.1D>

3.1D>

3.2D>

3.2D>

3.2D>

3.2D>

3.2D>

3.1D>

3.2D>

3.2D>

3.2D>

3.2D>

3.2D>

3.2D>

3.2D>

3.2D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D> 5.4B<

3.3D>

3.3D>

3.3D>

3.4D>

3.4D>

3.4D>

R28

0402

R32

0402

R34

0402 COMMON

R37

0402

R39

0402

R41

0402

DVI_DDCB_SCLK

C512

220PF

50V

5%

COG

0402

COMMON

MXM_DVI_A_HPD

5%

5%

5%

5%

5%

5%

Hotplug Detection

150-220R@100MHz

COMMON

DVI_A_TX0*

DVI_A_TX0

DVI_A_TX1*

DVI_A_TX1

DVI_A_TX2*

DVI_A_TX2

DVI_IGPL_DVIB_TX0*

DVI_IGPL_DVIB_TX0

DVI_IGPL_DVIB_TX1*

DVI_IGPL_DVIB_TX1

DVI_IGPL_DVIB_TX2*

DVI_IGPL_DVIB_TX2

DVI_DDCB_SDATA

DVI_A_CLK*

DVI_A_CLK

GND

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

C513

220PF

50V

5%

COG

0402

COMMON

DVI_A_CLK

DVI_A_CLK

DVI_A_TX0

DVI_A_TX0

DVI_A_TX1

DVI_A_TX1

DVI_A_TX2

DVI_A_TX2

IGPL_DVIB_CLK

IGPL_DVIB_CLK

IGPL_DVIB_TX0

IGPL_DVIB_TX0

IGPL_DVIB_TX1

IGPL_DVIB_TX1

IGPL_DVIB_TX2

IGPL_DVIB_TX2

IGP_UCLK

IGP_UCLK

IGP_UTX0

IGP_UTX0

IGP_UTX1

IGP_UTX1

IGP_UTX2

IGP_UTX2

LVDS_UTX0

LVDS_UTX0

LVDS_UTX1

LVDS_UTX1

LVDS_UTX2

LVDS_UTX2

LVDS_UTX3

LVDS_UTX3

LVDS_UCLK

LVDS_UCLK

LVDS_LTX0

LVDS_LTX0

LVDS_LTX1

LVDS_LTX1

LVDS_LTX2

LVDS_LTX2

LVDS_LTX3

LVDS_LTX3

LVDS_LCLK

LVDS_LCLK

DVI_IGPL_DVIB_TX0

DVI_IGPL_DVIB_TX0

DVI_IGPL_DVIB_TX1

DVI_IGPL_DVIB_TX1

DVI_IGPL_DVIB_TX2

DVI_IGPL_DVIB_TX2

5V_DDC

25

17

18

10

11

19

12

13

20

21

14

15

22

24

C5A

23

16

C1

C2

C3

C5

C4

SNN_DVI_VSYNC

HPD

SNN_DVI_R

SNN_DVI_G

SNN_DVI_B

SNN_DVI_HSYNC

26

C508

4700PF

25V

10%

X7R

0402

COMMON

GND

600-10266-0000-300

e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03

pmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmelucci

pmelucci

NET_SPACING_RULEDiffpairMIN_LINE_WIDTHNet Name

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

DVI-D without RGB

9

1

2

3

4

5

6

7

8

J8

DVI-I

DVI_I

COMMON

N/A

065-00030-0002-000

3 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 103 OF 10

9-JUN-2004

Page 4

BI

BI

POLYSWITCH

out

in

out

out

in

SDA

Y/CVBS

GND

C

SCL

Pb out

C/Pr

Y/CVBS

GND

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTINOUT

OUT

S

D

G

S

D

G

S

D

G

OUT

OUTININ

S

D

G

INBIIN

11

15

6

10

1

5

ID2

ID0

SCL

SDA

HSYNC

VSYNC

SHIELD

G

R

SHIELD

5V

B

GND

GND-R

GND-G

GND_B

GND

INININ

IN

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

4. VGA / TV

3.2A>

3.2A<>

3.2A>

3.2A>

3.2A>

4.1F>

MXM_DDCA_SCLK

MXM_DDCA_SDATA

DACA_VSYNC

DACA_HSYNC

DACA_RED

5VRUN

U502

74ACT08

DACA_VSYNC_B

3

74ACT_SO

COMMON

GND

14

1

2

7

GND

R531

0402

5%

5VRUN

14

U502

4

74ACT08

DACA_HSYNC_B

5

6

74ACT_SO

COMMON

7

GND

R533

0402

5%

Which inductor should I use?

DACA_VSYNC_R

3V3RUN

2

D14

BAV99

3

SOT23

100V

100mA

COMMON

1

GND

3V3RUN

2

D17

BAV99

3

SOT23

100V

100mA

COMMON

1

GND

DACA_VSYNC_CLAMP

2

D15

BAV99

3

SOT23

100V

100mA

COMMON

1

GND

C522

0.1UF

16V

10%

X5R

0402

COMMON

33

NO STUFF

R532

0402

3V3RUN

5%

33

COMMON

R70

2.2K

5%

0402

NO STUFF

R87

2.2K

5%

0402

NO STUFF

Stuffing Clamping Voltage Option.

DACA_HSYNC_R

33

R534

COMMON

0402

5%

2

D16

BAV99

3

SOT23

33

NO STUFF

L503

::50.0:2.0

47nH

COMMON0603

DACA_RED_C

100V

100mA

COMMON

1

GND

150-220R@100MHz

LB2

COMMONBEAD_0603

150-220R@100MHz

LB4

COMMONBEAD_0603

12V_PEX

DACA_VSYNC_F

22nH

L9

COMMON

0603

NO STUFF

0

5%

0402

R77

12 MIL

5VRUN

COMMON

0

5%

0402

R76

L10

COMMON0603

22nH

C53

15PF

50V

5%

NPO

0603

COMMON

GND

12V_PEX

DACA_HSYNC_F

3V3RUN

GND

Stuffing Clamping Voltage Option.

COMMON

COMMON

C57

15PF

50V

5%

NPO

0603

COMMON

22PF

0603

22PF

0603

I2CA_SDA_C

I2CA_SCL_C

5V_DDC

R81

2.2K

5%

0603

COMMON

1

1G1D1S

1

3

Q10

BSS138

SOT23_1G1D1S

COMMON

2

MAX_VOLTAGE=50V

CONTINUOUS_CURRENT=0.22A@31C

R_DS_ON=3.5R

MAX_CURRENT=0.88A

MAX_WATTAGE=0.36W@25C

V_BE_GS=+/-20V

3

Q13

BSS138

SOT23_1G1D1S

COMMON

2

MAX_VOLTAGE=50V

CONTINUOUS_CURRENT=0.22A@31C

R_DS_ON=3.5R

MAX_CURRENT=0.88A

MAX_WATTAGE=0.36W@25C

V_BE_GS=+/-20V

1G1D1S

5VRUN

I2CA_SCL_F

C50

50V

5%

NPO

GND

5VRUN

I2CA_SDA_F

C65

50V

5%

NPO

GND

1G1D1S

1G1D1S

3

Q11

BSS138

SOT23_1G1D1S

1

COMMON

2

MAX_VOLTAGE=50V

CONTINUOUS_CURRENT=0.22A@31C

R_DS_ON=3.5R

MAX_CURRENT=0.88A

MAX_WATTAGE=0.36W@25C

V_BE_GS=+/-20V

3

Q12

BSS138

SOT23_1G1D1S

1

COMMON

2

MAX_VOLTAGE=50V

CONTINUOUS_CURRENT=0.22A@31C

R_DS_ON=3.5R

MAX_CURRENT=0.88A

MAX_WATTAGE=0.36W@25C

V_BE_GS=+/-20V

DACA_VSYNC_C

DACA_HSYNC_C

5V_DDC

9.3F<>

R73

2.2K

5%

0603

COMMON

UNUSED Gates

9.3F<

14

13

12

7

GND

14

10

9

7

GND

3.2A> 4.1F>

3.2A> 4.1F>

TVY

3V3RUN

COMMON0603

47nH

47nH

GND

GND

GND

C530

3.9PF

50V

+/-.25PF

COG

0603

COMMON

C528

3.9PF

50V

+/-.25PF

COG

0603

COMMON

C526

3.9PF

50V

+/-.25PF

COG

0603

COMMON

::50.0:2.0

DACA_GREEN_C

::50.0:2.0

DACA_BLUE_C

5V_DDC

5V_DDC

GND

J21

CON_DSUB15HD

VGA

16

1

COMMON

4

SNN_VGA_ID2

SNN_VGA_ID011

4.1F> 3.2A>

2

3

13

14

9

17

5

10

8

7

6

15

12

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

VGA & TV

Place in line with inductor!

Route Inner Layer as much as possible

GND

GND

GND

C529

3.9PF

50V

+/-.25PF

COG

0603

COMMON

C527

3.9PF

50V

+/-.25PF

COG

0603

COMMON

C525

3.9PF

50V

+/-.25PF

COG

0603

COMMON

L502

COMMON0603

L501

R547

D502

BAV99

SOT23

100V

100MA

COMMON

D501

BAV99

SOT23

100V

100MA

COMMON

150

1%

0603

COMMON

GND

R544

150

1%

0603

COMMON

GND

R543

150

1%

0603

COMMON

GND

Can't find 3.3pF caps in the library

2

D503

BAV99

3

SOT23

100V

100MA

COMMON

1

GND

3.2A>

4.1F>

DACA_GREEN

3V3RUN

2

3

1

GND

DACA_BLUE

3V3RUN

2

3

1

GND

3.2A>

4.1F>

5VRUN

5VRUN

TVCVBS

U502

74ACT08

11

74ACT_SO

COMMON

U502

74ACT08

8

74ACT_SO

COMMON

TVC

4.3A<

4.4A<

4.5A<

SNN_AND_G1

4.3E<

4.4E<

9.4F<

9.4F<

9.4F<

SNN_AND_G2

R56

0402

R51

0402

R54

5%

3.2A>

3.2A>

3.2A>

3.2A>

3.2A>

4.3F>

4.3F>

4.4F>

0

NO STUFF

5%

5%

0

NO STUFF

0

NO STUFF0402

To Docking Connector

TVY_DOCK

To Docking Connector

TVCVBS_DOCK

To Docking Connector

TVC_DOCK

NET SPACING RULE

NET

DACA_RED

DACA_GREEN

DACA_BLUE

TVY

TVCVBS

TVC

TVY_DOCK

TVCVBS_DOCK

TVC_DOCK

9.4F< 4.1F>

3

9.4F<

4.1F>

3

9.4F<

4.1F>

3

5V_DDC

3V3RUN

2

1

3V3RUN

2

1

GND

3V3RUN

2

1

D7

BAV99

SOT23

100V

100mA

COMMON

D4

BAV99

SOT23

100V

100mA

COMMON

D5

BAV99

SOT23

100V

100mA

COMMON

5VRUN

GND

NET

GNDGND

GND

GNDGND

C43

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

5V_Fused

5V_DDC

5V_DDC_diode

R55

150

1%

0603

COMMON

R52

150

1%

0603

COMMON

R53

150

1%

0603

COMMON

5V DDC Supply

F2

1A

1812

COMMON

5V_Fused2 D11

MIN_LINE_WIDTH

12 MIL

12 MIL

12 MIL

L5

C30

82PF

50V

5%

NPO

0603

COMMON

C21

0603

L3

C22

82PF

50V

5%

NPO

0603

COMMON

L4

C26

82PF

50V

5%

NPO

0603

COMMON

C38

.100UF

25V

10%

X7R

0603

COMMON

1

GND

GND

GND

IMPEDANCE_RULE

::50.0:2.0

::50.0:2.0

::50.0:2.0

::50.0:2.0

::50.0:2.0

::50.0:2.0

::50.0:2.0

::50.0:2.0

::50.0:2.0

Backdrive Diode

8.2PF

C29

+/-0.5PF

50V

0603

NPO

COMMON

0.56uH

COMMON

0603

8.2PF

+/-0.5PF

50V

NPO

COMMON

0.56uH

COMMON

0603

8.2PF

C25

+/-0.5PF

50V

0603

NPO

COMMON

0.56uH

COMMON

0603

1

2

SMA

40V

2.1A

COMMON

GND

GND

GND

NET_SPACING_TYPE

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

5V_DDC_diodeIR10MQ040N

L7

120R@100MHz

BEAD_1206

COMMON

VOLTAGE

5V

5V

5V

::50.0

TVY_C

C28

82PF

50V

5%

NPO

0603

COMMON

::50.0

TVCVBS_C

C20

82PF

50V

5%

NPO

0603

COMMON

::50.0

TVC_C

SNN_TV1

J13

CON_MINIDIN_9

AV_POD

COMMON

7

9

8

5

1SNN_TV4

C24

82PF

50V

5%

NPO

0603

COMMON

GND

GND

600-10266-0000-300

e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03

e266_a03

pmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmelucci

pmeluccipmeluccipmeluccipmeluccipmelucci

5V_DDC

GND

4

6

3

GND

5V_DDC

C44

.1UF

16V

10%

X7R

0603

COMMON

SNN_TV2

SNN_TV32

4 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 104 OF 10

9-JUN-2004

Page 5

SPWG CONNECTOR

VDD2

VDD1

DDC_3V3

VSS7

VSS8

VSS6

VSS5

VSS4

VSS2

VSS3

VSS1

FGND1

FGND2

SH_GND1

SH_GND2

NC

EVEN_CLKINEVEN_CLKIN+

DDC_DATA

DDC_CLK

ODD_RIN0ODD_RIN0+

ODD_RIN2+

ODD_RIN1+

ODD_CLKIN-

ODD_RIN2-

ODD_RIN1-

ODD_CLKIN+

EVEN_RIN0-

EVEN_RIN1+

EVEN_RIN0+

EVEN_RIN1-

EVEN_RIN2+

EVEN_RIN2-

INININININININININ

IN

S

D

G

IN

INININININININININ

IN

ININININININININOUTBIOUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

S

DGS

D

G

IN

BIBIINININBIINININ

BOARD to BOARD CONNECTOR

2

4

6

8

10

12

14

20

18

16

22

26

30

28

24

32

38

36

34

40

42

46

44

50

48

52

54

56

58

60

1

3

5

9

7

11

13

15

19

17

21

25

29

27

23

31

33

35

39

37

41

47

43

45

49

51

53

55

59

57

INININININININININININININININININ

IN

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

B C

2

A

1

3

4

5

E GD F HCA B

5. Panel Power and SPWG Panel I/O

DDCC_SCLK

2

3

Q501

BSS138

SOT23_1G1D1S

2.5D> 5.3F<

MXM_PRSNT1*

COMMON

BSS138

SOT23_1G1D1S

COMMON

Q502

J24

COMMON

F

3.2F< 3.3D>

3.2F< 3.3D>

3.2F<

3.3D>

3.2F<

3.3D>

3.2F<

3.3D>

3.2F<

3.3D>

3.2F<

3.3D>

3.2F<

3.3D>

3.2F<

3.3D>

3.2F<

3.3D>

3.4D>

3.4D>

3.3D>

3.4D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.3D>

3.2F<

3.2F<

3.2F<

3.2F<

3.2F<

3.2F<

3.2F<

3.2F<

3.2F<

3.2F<

LVDS_UCLK

LVDS_UCLK*

LVDS_UTX3

LVDS_UTX3*

LVDS_UTX2

LVDS_UTX2*

LVDS_UTX1

LVDS_UTX1*

LVDS_UTX0

LVDS_UTX0*

LVDS_LCLK

LVDS_LCLK*

LVDS_LTX3

LVDS_LTX3*

LVDS_LTX2

LVDS_LTX2*

LVDS_LTX1

LVDS_LTX1*

LVDS_LTX0

LVDS_LTX0*

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

CON_SMT_2X30_P050

BRD_TO_BRD_CONNECTOR

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

SNN_LVDS_USER3

SNN_LVDS_USER2

SNN_LVDS_USER1

SMB_DATA

SMB_CLK

SNN_LVDS_USER0

LVDS_PPEN

DDCC_SCLK

DDCC_SDATA

LVDS_BLEN

LVDS_BL_BRGHT

3.3A>

3.3A>

3.3A>

3.3A>

3V3RUN

5VRUN

VBAT

2.1D<>

2.1D<>

3.3A<>

8.2A< 5.1E>

3.3A<>

3.3A<>

5.1E<>

9.4C<

8.5A<>

8.5A<

9.4C<> 8.2A<>

1G1D1S

MAX_VOLTAGE=50V

CONTINUOUS_CURRENT=0.22A@31C

R_DS_ON=3.5R

MAX_CURRENT=0.88A

MAX_WATTAGE=0.36W@25C

V_BE_GS=+/-20V

1

DDCC_SDATA

2

3

1G1D1S

MAX_VOLTAGE=50V

CONTINUOUS_CURRENT=0.22A@31C

R_DS_ON=3.5R

MAX_CURRENT=0.88A

MAX_WATTAGE=0.36W@25C

V_BE_GS=+/-20V

1

3.2D>

3.3E<

9.2D<

9.2D<

9.2D<

9.2D<

9.2D<

9.2D<

3.3E<

3.3E<

3.3E<

3.3E<

3.3E<

9.2D<

9.2D<

5.4H<

5.4F<

5.4H<

5.4F<

5.4H<

5.4F<

5.5H<

5.5F<

3.2D>

3.2D>

3.2D>

3.1F<

3.2D>

3.1F<

3.1F<

3.2D>

3.2D>

3.2F<

3.2D>

3.2F<

3.2F<

3.2D>

3.2D>

3.3A>

8.2A<

3.1F<

3.1F<

3.1F<

3.1F<

3.1D>

3.1F<

3.1D>

3.1D>

3.1F<

3.1F<

3.2D>

3.1F<

3.2D>

3.2D>

3.1F<

3.1F<

8.2A<>

3.3A<>

5.4D<>

9.4C<>

5.4D<

9.4C<

5.4F<

5.4H<

5.4F<

5.4H<

5.4F<

5.4H<

5.4F<

5.4H<

Net Name

SPWG_IN_IGP_LTX0

SPWG_IN_IGP_LTX0*

SPWG_IN_IGP_LTX1

SPWG_IN_IGP_LTX1*

SPWG_IN_IGP_LTX2

SPWG_IN_IGP_LTX2*

SPWG_IN_IGP_LCLK

SPWG_IN_IGP_LCLK*

MIN_LINE_WIDTH

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

3.5MIL

SPWG Input Connector

SPWG_IN_DDCC_SCLK

SPWG_IN_DDCC_SDATA

IGPL_DVIB_TX0*

IGPL_DVIB_TX0

IGPL_DVIB_TX1*

IGPL_DVIB_TX1

IGPL_DVIB_TX2*

IGPL_DVIB_TX2

IGPL_DVIB_CLK*

IGPL_DVIB_CLK

IGP_UTX0*

IGP_UTX0

IGP_UTX1*

IGP_UTX1

IGP_UTX2*

IGP_UTX2

IGP_UCLK*

IGP_UCLK

R503

0402

R507

0402

R508

0402

R510

0402

R512

0402

R513

0402

R514

0402

R516

0402

Place Above MXM MB Conn./Place on Solder Side

Integrated Graphics LoopBack Testing

2.5D>

5.1D<

5%

5%

5%

5%

5%

5%

5%

5%

SPWG_IN_IGP_LTX0*

0

NO STUFF

SPWG_IN_IGP_LTX0

0

NO STUFF

SPWG_IN_IGP_LTX1*

0

NO STUFF

SPWG_IN_IGP_LTX1

0

NO STUFF

SPWG_IN_IGP_LTX2*

0

NO STUFF

SPWG_IN_IGP_LTX2

0

NO STUFF

SPWG_IN_IGP_LCLK*

0

NO STUFF

SPWG_IN_IGP_LCLK

0

NO STUFF

2MXM_PRSNT1*

3V3RUN

5

3

GND

7

8

9

10

12

13

15

16

18

19

21

22

24

25

27

28

30

31

IGP_PPEN

4

U2

SINGLE

SC70

COMMON

J502

SPWG

SMD_34

COMMON

SNN_SPWG_11

SPWG_IN_IGP_LTX0

SPWG_IN_IGP_LTX0

SPWG_IN_IGP_LTX1

SPWG_IN_IGP_LTX1

SPWG_IN_IGP_LTX2

SPWG_IN_IGP_LTX2

SPWG_IN_IGP_LCLK

SPWG_IN_IGP_LCLK

6

4

1G4D3S

3V3RUN

NET_SPACING_RULEDiffpair

3

4

2

11

14

17

20

23

26

29

1

32

33

34

3

2

1

COMMON

SO8_1G4D3S

IRF7410

Q2

V_BE_GS=+/-8V

5

MAX_WATTAGE=2.5W@25C, 1.6W@70C

MAX_CURRENT=65A

6

R_DS_ON=7mohm@4.5V, 13mohm@1.8V (max)

CONTINUOUS_CURRENT=16A@25C, 13A@70C

7

MAX_VOLTAGE=20V

8

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

20MIL_G2G_30MIL

SPWG_IN_DDC_3V35

IGP_VCC

GND

GND

GND

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

LVDS Panel Interface

5.2E> 3.2D>

5.2E> 3.2D>

3.1F<

3.1F<

5.1E<

5.1E<

5.1E<

3.2D>

5.1E<

5.2E>

3.2F<

3.2D>

3.2D>

3.1F<

3.2D>

5.3E>

GND

0

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

IGP_VCC

SPWG_IN_DDC_3V3

SPWG_IN_DDCC_SDATA

SPWG_IN_IGP_LTX0*

SPWG_IN_IGP_LTX1*

SPWG_IN_IGP_LTX2*

IGP_LTX3*

SPWG_IN_IGP_LCLK*

IGP_UTX0*

IGP_UTX1*

IGP_UTX2*

IGP_UTX3*

IGP_UCLK*

SPWG_IN_DDCC_SCLK

SPWG_IN_IGP_LTX0

SPWG_IN_IGP_LTX1

SPWG_IN_IGP_LTX2

IGP_LTX3

SPWG_IN_IGP_LCLK

IGP_UTX0

IGP_UTX1

IGP_UTX2

IGP_UTX3

IGP_VCC

10

12

14

16

18

20

22

24

26

28

30IGP_UCLK

HDR_2M15

2

4

6

8

MALE

2.54MM

NORM

COMMON

J6

IGP 24 BIT Panel Connector

600-10266-0000-300

e266_a03

e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03

e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03e266_a03

pmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmeluccipmelucci

pmelucci

GND

5.1E<

5.1E<

5.1E<

3.2D>

5.1E<

3.1F<

5.2E>

3.2D>

3.2D>

3.1F<

5.2E>

3.2D>

3.2D>

3.2F<

5.2E>

3.2D>

3.2F<

5 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 105 OF 10

9-JUN-2004

5.2E>

Page 6

BI

OUT

TAB

GND/ADJ

IN

S

D

G

BIBIBIBIBIBIBIBIBI

S

D

G

S

D

G

BIBIBIBIBIBIBIBIBI

VIN

PHASE

UGATE

BOOT

VOUT

LGATE

ISEN

VSEN

VCC

FCCM

EN

PGOOD

SOFT

OCSET

GND

PGND

S

D

G

S

D

G

V+

V-

VIN

PHASE

UGATE

BOOT

VOUT

LGATE

ISEN

VSEN

VCC

FCCM

EN

PGOOD

SOFT

OCSET

GND

PGND

S

D

G

S

D

G

BI

BI

D

S

G

1

5

4

3

2

F G H

PAGE

DATE

SANTA CLARA, CA 95050, USA

2701 SAN TOMAS EXPRESSWAY

NVIDIA CORPORATION

NV_PN

ID

NAME

ED

ASSEMBLY

PAGE DETAIL

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY