Page 1

8

<Variant Name>

Title

7

6

5

4

Schematic No.

3

2

1

Date:

Maverick T510 PCIe Plug-in Card with 16 MiB DDR

REVISION HISTORY

D D

Sch

PCB

Rev

Rev

00A

0

C C

Date

05/11/04

05/19/04 KB - Removed SMT test points on REFCLK+/- and PERp/n0 in PCIe section and added note to use via testpoints instead. Added terminating resistors for REFCLK+/-. Removed tantalum cap from 3.3V rail and added bulk

KB - Initial revision of the schematic based on A346 -Iceman

cap to 12V rail (C103). Added R114 & R115 between GND_PCIE and GND. Renumbered various R's & C's in PCIe section to remove large gaps in numbering sequence. Removed GND_PCIE and connected directly to

GND. Removed R144 & R115. Swapped Rio PCIe receive signal polarities for routing. Added alternate PVCC supply circuit to 6.5V SMPS circuit. Changed part reference L1 to L701. Changed alternate PVCC

supply and added schottky diode D702 on SMPS output. Renumbered C857 on page 7 to C715. Renumbered C758 to C714. Changed L1 to 68 uH and renumbered to L701. Changed Added net short requirement for

HSEL1 and HSEL2&3 nets.

REVISION DESCRIPTION

105-A34700-00A

Thursday, August 26, 2004

Rev

0

B B

A A

Merlin (ATSB/DVB & Analog PCI) = A345

Maverick (PCIe) = A347

Iceman (PCI) = A346

Goose (Dual Rio PCI) = A365/371

Cougar (Dual Rio PCIe) = A447

8

7

6

5

4

3

2

1

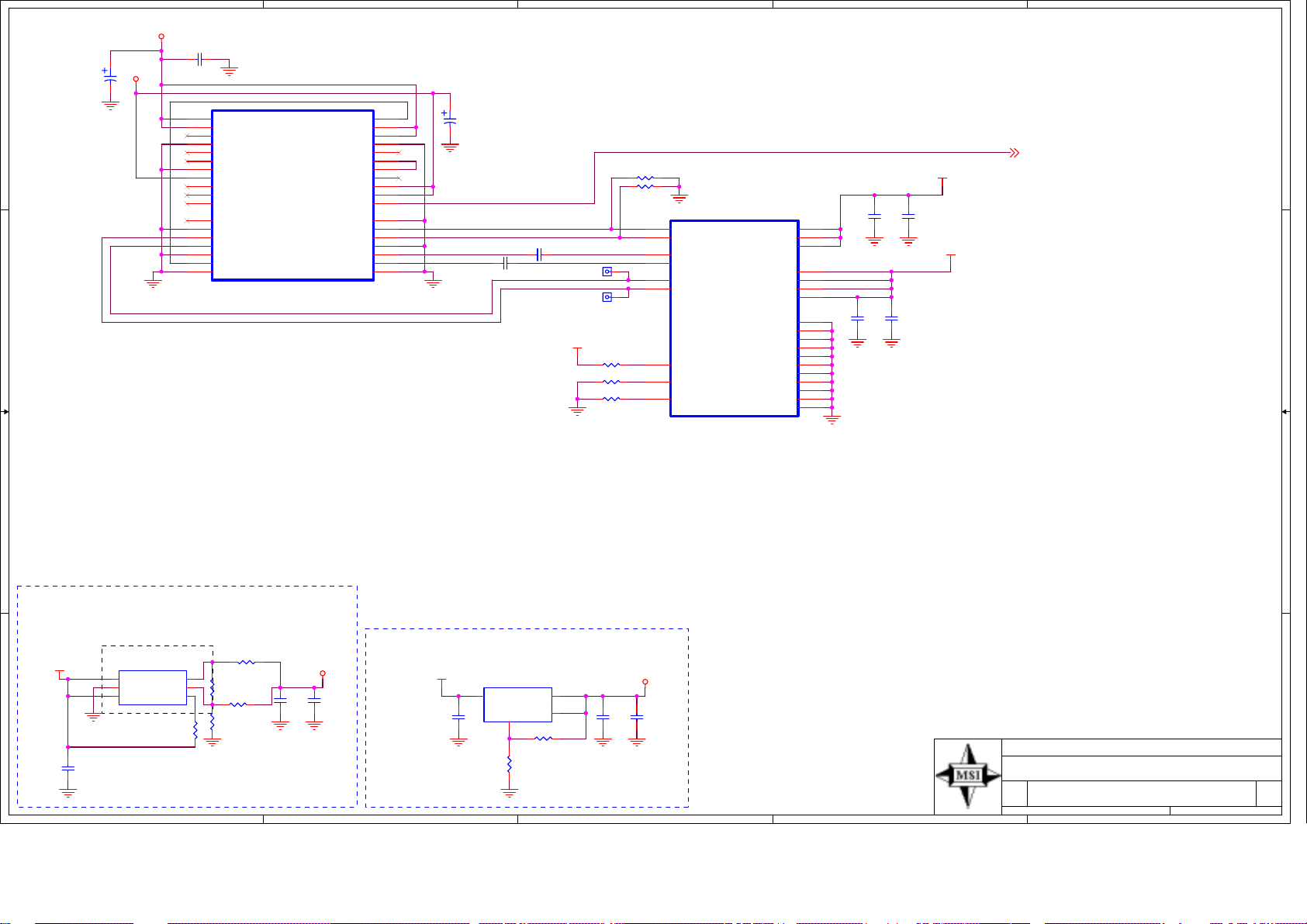

Page 2

5

+12V_BUS

C101

4

3

2

1

C103

100uF_16V

DNI

D D

C C

B B

+3.3V_BUS

RIO_PERp0

RIO_PERn0

Note: n0 and p0 signals are swapped between RIO and connector. This is allowed by PCIe spec.

100nF

MPCIE101

B1

+12V#B1

B2

+12V#B2

B3

RSVD#B3

B4

GND#B4

B5

SMCLK

B6

SMDAT

B7

GND#B7

B8

B10

B11

B12

B13

B14

B15

B16

B17

B18

B9

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

x1 PCIe

+3.3V#A10

Mechanical Key

TRST#

Note: PCIE connector is labelled from system board perspective.

(i.e. you must cross connect receive & transmit signals)

PRSNT1#

+12V#A2

+12V#A3

GND#A4

JTAG2

JATG3

JATG4

JATG5

+3.3V#A9

PERST#

GND#A12

REFCLK+

REFCLK-

GND#A15

PERp0

PERn0

GND#A18

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

TCK

TDI

TDO

TMS

PERp0

PERn0

C102

100uF_16V

DNI

C107 100nF

REFCLK+

REFCLK-

C106 100nF

R104 100R

R105 100R

RIO_PETp0

RIO_PETn0

TP101

TP102

Locate TP's near U101.

VDDA12

R101 100R

R102 150R

R103 10K

Y20

Y21

AB17

AB18

AB21

AB20

Y18

Y17

W18

DNI

DNI

U101B

REFCLK+

REFCLK-

PCIE_TXp0

PCIE_TXn0

PCIE_RXp0

PCIE_RXn0

PCIE_CALRN

PCIE_CALRP

PCIE_TXISET

RIO510

VDDA18_RIO

C104

4.7uF

VSSA_1

VSSA_2

VSSA_3

VSSA_4

VSSA_5

VSSA_6

VSSA_7

VSSA_8

VSSA_9

VSSA_10

VSSA_11

AA20

AA21

AA22

W21

W22

W19

W20

W16

W17

Y16

Y19

Y22

AA16

AA17

AA18

AA19

AB16

AB19

DNI

VDDA12_RIO

C108

4.7uF

DNI

VDDA18_1

VDDA18_2

VDDA18_3

VDDA12_1

VDDA12_2

VDDA12_3

VDDA12_4

PCI Express (2/9)

C105

100nF

C109

100nF

PCI_RESET# (9)

VDDA18

VDDA12

+1.2V Regulator for RIO Digital PCIe Core

Replace with FAN2558

+3.3V_BUS

A A

C110

4.7uF

REG101

TK11819M

1

Vin

2

OSC

3

GND

DK

Vout

R108

47K

I(load) = 138 mA max.

Est. Regulator Power = 0.29W

5

R106 0R

DNI

R179

6

T1

0R

5

DNI

4

R107

0R

R181

0R

DNI

C111

100nF

VDDA12

C112

4.7uF

+1.8V Regulator for Analog PCIe

+3.3V_BUS

C113

4.7uF

I(load) = 35 mA max.

Est. Regulator Power = 0.057W

4

REG102

3 2

IN OUT

CASE

ADJ

LT1117CST

1

R112 681R

R113

1.50K

1%

Place test point via's on REFCLK+, REFCLK-, RIO_PETp0 and RIO_PETn0 where trace transitions from bottom to top layer near U101.

VDDA18

4

1%

C114

100nF

C115

4.7uF

Micro-Star International Co., LTD.

Maverick PCIe Rio Interface

Size Document Number Rev

B

8622-100 ATI PCI-E TV CARD

3

2

Date:

Friday, August 27, 2004

1

111

Sheet of

100

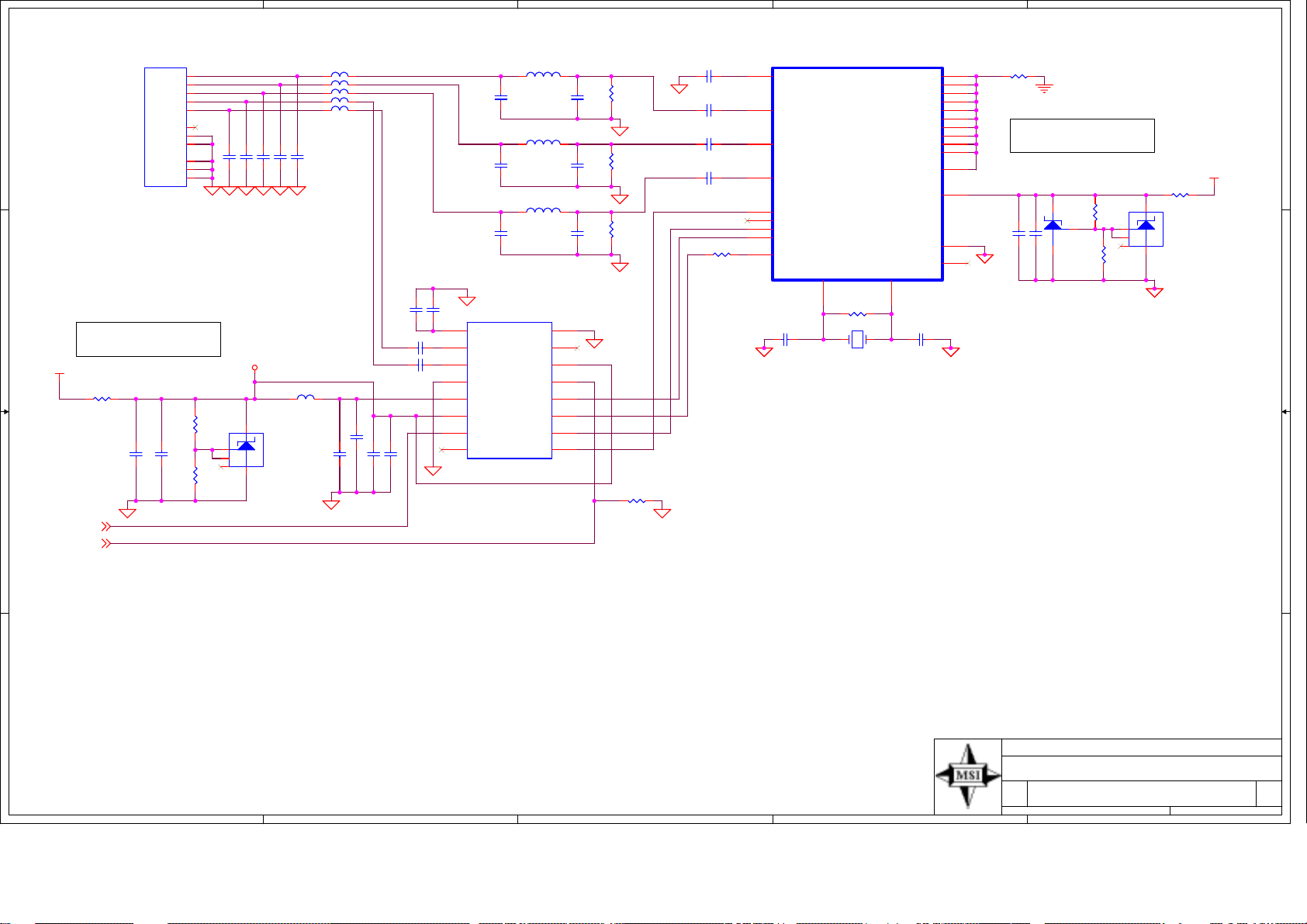

Page 3

5

4

3

2

1

J201

D D

C C

B B

Shunt regulator for +V_AUD

Vout = 3V

Iout = 10 mA max. (100R)

+5V_RF

R211 200R

AUD_LVL_SEL(5)

I2S_RESET#(5)

C225 100nF

AUD

VIDEO

GND

GND#3

GND#5

CASE

CASE#10

CASE#11

R212

DNI

301R

1%

R213

1.5K

C226 4.7uF

1%

1

6

Y

8

C

7

AL

4

AR

2

3

5

9

10

11

C207 33pF

C206 33pF

c c c c c c

+V_AUD

4

NC

1

NC

2

5 3

C210 33pF

C208 33pF

C209 33pF

B209 120R

REG202

TL431CDBVR

B201 120R

B202 120R

B203 120R

B204 120R

B205 120R

DNI

C227 10uF

AUD

C228 100nF

C218

2.2uF

C222 4.7uF

C223 4.7uF

DNI

C229 10uF

C230 100nF

L201 1.2uH

C202

120pF

L202 1.2uH

C211

120pF

L203 1.2uH

C214

120pF

AUD

C219

100nF

U201

1

VCOM

2

RIN

3

LIN

4

VSS

5

VA

6

VD

7

SEL

8 9

NC#8 SDTO

AK5355VT

AUD

TST1

NC#15

PDN

BCLK

MCLK

LRCK

C201 100nF

R202

C203

75.0R

120pF

AVSS

R203

C212

75.0R

120pF

AVSS

R205

C215

75.0R

120pF

AVSS

16

AUD

15

14

DIF

13

12

11

10

R214 10K

AVSS

C204 100nF

C205 100nF

C213 100nF

R206 33R

AUD

U101G

P4

CVBS_IN0

P2

CVBS_IN1

M2

LUMA_IN

R1

CHROMA_IN

RIO510

B4

GPIOd_C3/I2S_DI

B5

GPIOd_C2/I2S_DO

C5

GPIOd_C4/I2S_WS

A4

GPIOd_C1/I2S_SCLK

A5

GPIOd_C0/MCLK

C220 22pF

GPIO_D0/PDATA0

GPIO_D1/PDATA1

GPIO_D2/PDATA2

GPIO_D3/PDATA3

GPIO_D4/PDATA4

GPIO_D5/PDATA5

GPIO_D6/PDATA6

GPIO_D7/PDATA7

GPIO_D8/PDATA8

GPIO_D9/PDATA9

GPIOd_D10/PCLK

A/V I/O &

Oscillator

(7/9)

XTAL_OUTXTAL_IN

L4K4

R208 1.0M

Y201

21

27.05MHz

OSC_AVDD

OSC_AVSS

OSC_OUT

C221 22pF

C6

B6

C7

B7

A7

B8

A8

C9

B9

A9

C8

K3

J3

J4

OSCOSC

OSCOSC

R209 10K

Shunt regulator for +V_OSC

Vout = 1.8V

Iout = 15 mA max. (82R)

+V_OSC

MREG201

AS432S

OSCOSC

C216 100nF

C217 4.7uF

3 2

+3.3V_BUS

R201 82R

R204

681R

1%

1

4

1

2

R207

1.5K

1%

NC

NC

5 3

OSC

OSC

REG201

SC431LC5SK-1

DNI

Pad sharing:

REG201/MREG201

REG202/MREG202

A A

Micro-Star International Co., LTD.

Maverick A/V Input & Rio Oscillator

Size Document Number Rev

B

8622-100 ATI PCI-E TV CARD

5

4

3

2

Date:

Friday, August 27, 2004

1

211

Sheet of

100

Page 4

5

J301

1

234

5

c

J302

D D

234

5

c

Install as

required for EMI

R340 0R

R341 0R

R342 0R

R343 0R

R355 0R

R356 0R

c

C C

B B

RF_AGC_LPF(4)

C304 10nF

C308 10nF

1

+5V_RF

C333

100nF

ANT/FM _RF

CABLE_RF

C334

10nF

R315

RF

0R

R327 12K

RF

R334 2K7

RF

R319

12K

1

U302

3

RF IN 1

13

RF IN 2

17

V1

19

V1#19

18

V2

1

GND

2

GND#2

4

GND#4

7

GND#7

9

GND#9

12

GND#12

14

GND#14

15

GND#15

RF

PE4256

Q301

BFS17

2 3

R332

75R

C343 10nF

R317

392K

RF GND#10

RF GND#11

RF GND#16

RF GND#20

R320

4.7K

1

RF OUT

RF GND

RF GND#6

RF

2 3

R304 0R

C329 100nF

C335 10nF

Q302

BFS17

R333

1K

RF

DNI

R344 0R

8

B303 120R

5

6

C321 10nF

10

11

16

20

RF

R328

4.7K

1

4

RF_SW_OUT

RF

R312 10K

R313 10K

ANT/FM_SEL

CABLE_SEL

R322

20K

R330 75K

R329

12K

Q303

BFS17

2 3

RF

+V_AUD

C344 10uf

RF

C318 100nF

RF

R323 0R

R331 0R

C336

100nF

C301 39pF

C305

180pF

L302

220NH

RF

C337

100nF

should be 680R

3150068100

CB Trap

C302 27pF

DNI

R321

560R

C306

82pF

RF RF

C323

10nF

C328 100nF

RF

C338

3.3NF

C303 56pF

L303

330nH

RF

C339

1uF

RF

3

R314

330R

RF-

C340

22pF

T301

2

+5V_RF

LO Leakage

Filter

L301

12NH

64

Transformer

RF+

13

L305

82nH

U301

1

2

3

4

5

6

7

8

9

10

11

12

RF

C307

2.0pF

RF

MT2050_RF_IN

LNAIn_n

VCC_LNA1

AGC_In

AVCC_Io1

LO1_tk1

LO1_tk2

LO1_Reg

DVCC_Io1

LO1_lpf

GPO0

DNC_1

SERca

B302

1.8NH

48

LNAIn_p

VCC_LNA2

SAW301 CB00058

1

2

GPO2

DNC_6

MIX1_op

MIX1_on

VCC_mx1

4

MIX2_ip

MIX2_in

VCC_mx2

837

VCC_tga

Pad sharing:

R335/R336

R325/R345

R326/R346

R323/R331

5

6

RF

3738394041424344454647

DNC_5

FGAop

FGAon

AVCC_lo2

LO2_tk

LO2_Reg

LO2_lpf

DNC_4

DVCClo2

GPO1

DNC_3

VGAip

VGAin

GND_PAD

L304

7.5NH

36

35

34

33

32

31

30

29

28

27

26

25

49

2

C324

1uF

RF

+5V_RF

RF

C325

1uF

IFOutP

IFOutN

C330

6.8nF

R318 560R

C326

1uF

C331

100nF

C327

22pF

RF

C332

100nF

R325 0R

R326 0R

L306

1uH

RF

C341

10nF

2

534

1

SAW302 44.0MHZ

R345 0R

R346 0R

1

SAW2_OUTp (4)

SAW2_OUTn (4)

LM324M

12

+

PDET_VCMP_PWM(5)

PDET_CMP(5)

AUX_VREF_PWM(5)

A A

SCL_3V3(5)

SDA_3V3(5)

IF_AGC_LPF(4)

R316 1K

C354 100nF

R347 1K

C355 100nF

5

13

14

-

U303D

DNI

R376

10K

R375

0R

+5V_RF

C347

1uF

Place inside metal shield

R337 100R

R338 100R

4

3

MT2050TR

C348

22pF

RF

C351 33pF

I2C_en

SCL

SDA

DNC_2

VCC

SROn

SROp

GPADin

VGAop

VGAon

1314151617181920212223

C350 18pF

Y301 4.000_Mhz

2 1

RFRF

C352 33pF

R339 1K

VCCvga

VGActrl

24

R335 0R

R336 0R

C349 100nF

R324 560R

RF

DNI

RF

2

C346 1uF

RF

RF

MT2050_VGA_OUTn (4)

MT2050_VGA_OUTp (4)

Micro-Star International Co., LTD.

Maverick RF Switch & MT2050 Tuner

Size Document Number Rev

B

8622-100 ATI PCI-E TV CARD

Date:

Friday, August 27, 2004

Sheet of

1

100

311

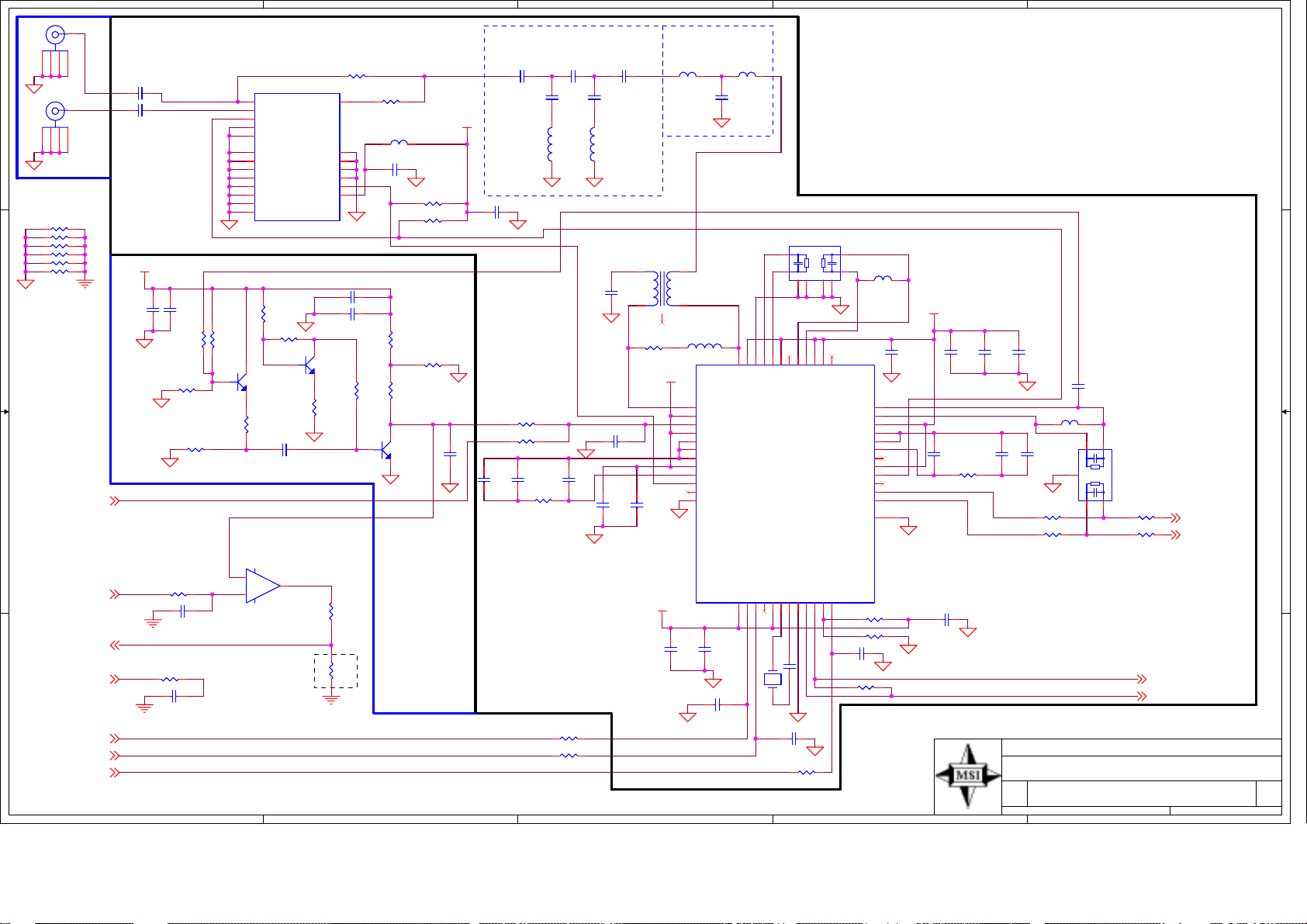

Page 5

5

+5V_RF

B401

200R

D D

SAW2_OUTp(3)

SAW2_OUTn(3)

C C

Optionally place

C412 100nF

C415 100nF

C402

0.1uF

U401

1

VCC

GND

2

IN1

OUT2

3 7

IN2 OUT1

4

VAGC

GND#8

UPC3221GV

4

R402 0R

C403

1uF

RF

5

RF

6

8

RF

R414 0R

R403

200R

R412

200R

C405

15PF

C416

15PF

DNI

DNI

C413

39pF

B402

820nH

B403

820nH

L402

330nH

C406

39pF

L401

560nH

L404

560nH

C417

39pF

3

Pad sharing:

C437

C438

27pF

L406

270nH

C414

22pF

L407

270nH

27pF

C407

100nF

DNI

L403

560nH

C418

100nF

DNI

R402/R403

R412/R414

R432/R427

R437/R426

REG402/MREG402

2

1

+1.8V Regulator for analog FE power supplies

+3.3V_BUS

3 2

C408

4.7uF

I(load) = 400 mA max.

Est. Regulator Power = 0.6W

REG401

IN OUT

CASE

ADJ

LT1117CST

1

R410

1.50K

1%

AVSS

681R

4

R405

1%

+AVDD18

C409

C411

4.7uF

100nF

AVSS AVSS

inside metal shield

R417 0R

C419 100nF

R418 2K

R419 2K

IF_AGC_PWM

RF_AGC_PWM

B B

R427 0R

MT2050_VGA_OUTp(3)

MT2050_VGA_OUTn(3)

A A

R432 47R

R437 47R

5

R426 0R

C423 100nF

DNI

Replace with 402 ohm

0402 pkg when avail.

C427 100nF

DNI

R436

432R

C429 10uf

C430 100nF

C435 10uf

C436 100nF

AVSS

U101F

L1 G2

IF_IN+ IF_AGC

RF_AGC

AVDD33

AVDD1_1

AVDD1_2

AVDD1_3

AVDD1_4

AVDD1_5

AVDD1_6

FE Power

(6/9)

AVSS1_1

AVSS1_2

AVSS1_3

AVSS1_4

AVSS1_5

AVSS1_6

AVSS

C428

100nF

H2

K1

R3

R2

N1

J2

GUARD

IF_INREFP

REFM

BYPASS0

BYPASS1

RIO510

IF Input &

4

H3

H4

K2

L2

M1

N2

N3

P1

L3

M3

M4

N4

P3

R4

Shunt regulator for +AVDD33

Vout = 3.3V

Iout = 20 mA max. (340R)

+AVDD33

C425 100nF

C426 4.7uF

C431

C432

100nF

100nF

AVSS

AVSS AVSS

AVSS

+AVDD33

C434

100nF

3

R422 2K

R423 2K

C420 100nF

R434

475R

1%

4

NC

1

NC

2

R438

1.5K

1%

+5V_RF

5 3

R440

56R

DNI

REG402

TL431CDBVR

AVSS

U303C

-

9

+

10

LM324M

R424 0R

+6.5V_SMPS

R429 150R

+AVDD18

8

DNI

R420 0R

R428 2K

R433 2K

R435 2K

C424 100nF

R421 0R

R457

DNI

10K

RF

C421 100nF

R425 2K

U303A

2

3

C422 0.1uF

RF

2

DNI

RF

-

1

+

LM324M

4 11

R439 0R

IF_AGC_LPF (3)

R441

0R

+5V_RF

R431 0R

R458

10K

DNI

RF

B404 120R

DNI

RF_AGC_LPF (3)

+12V_BUS

C439 0.1uF

DNI

R430 0R

DNI

Micro-Star International Co., LTD.

Maverick IF BPF & Rio Front End

Size Document Number Rev

B

Date:

8622-100 ATI PCI-E TV CARD

Friday, August 27, 2004

1

411

Sheet of

RF

100

Page 6

5

4

3

2

1

D D

AUD_LVL_SEL(2)

C C

B B

+MVDDQ

+3.3V_BUS

R501 5.1K

R502 5.1K

R503 10K

R504 10K

R505 10K

DNI

DNI

DNI

R511 10K

R512 10K

DNI

DNI

Host Mode

select = PCIe 32 bit address space

HSEL0

HSEL1

HSEL2&3

R515 5.1K

R514 5.1K

R513 10K

U101E

G1

GPIO0d/HSEL0

F1

GPIO1d/HSEL1

F2

GPIO2d/HSEL2

F3

GPIO3d/HSEL3

E1

GPIO4u/EJ_DINT

D1

GPIO5d/EJ_TDO

E2

GPIO6d/EJ_TDI/LOR2

C1

GPIO7d/EJ_TCK/LOR3

C20

TEST_YCLK/LOR0

A20

TEST_MCLK/LOR1

G3

TEST_ENd

RIO510

JU502

Header_2_Pin_1X2

1

2

DNI

GPIO8d/EJ_TMS

GPIO9d/EJ_TRST#

GPIO10d/UART_Rx

GPIO11d/UART_Tx

GPIO12d/IRTxD

GPIO13u/IRRxD

GPIO14u/M_SCL

GPIO15u/M_SDA

GPIO & Test

& LOR (5/9)

ATBP/NC

ATBM/NC

C503 100nF

U501

1

E0

2

E1

M/WC

3

E2

4 5

VSS SDA

AT24C01A-10SC2.7

Can also use

2280240200

R517 10K

VCC

SCL

D2

E3

B1

D3

C2

C4

B3

A3

T1

T2

+3.3V_BUS

8

7

6

R516 10K

JU501

Header_2_Pin_1X2

2

1

DNI

R506 4.7K

R507 4.7K

+3.3V_BUS

I2S_RESET# (2)

PDET_CMP (3)

AUX_VREF_PWM (3)

PDET_VCMP_PWM (3)

SCL_3V3 (3)

SDA_3V3 (3)

HOST MODE SELECTION ST RAPPING

HSEL[3:0]

A A

PCI - relocatable in 32 bit address space - no I2C EEPROM

0

1

PCI - relocatable in 32 bit address space - with I2C EEPROM

PCI Express - relocatable in 32 bit address space

2

3

PCI Express - relocatable in 64 bit address space

4

VIP Host with Device ID = 0

5

VIP Host with Device ID = 1

VIP Host with Device ID = 2

6

VIP Host with Device ID = 3

7

8

I2C with 7 bit address = 0x40

I2C with 7 bit address = 0x42

9

A

I2C with 7 bit address = 0x88

B

I2C with 7 bit address = 0x8A

I2C with 10 bit address = 0x40

C

I2C with 10 bit address = 0x42

D

E

I2C with 10 bit address = 0x88

F

I2C with 10 bit address = 0x8A

MODE

5

Use net short to connect HSEL2&3 to GND.

1

Use net short to connect HSEL1 to +3.3V_BUS.

2

Possible pad sharing:

3

No keep-out area needed for JU501 & JU502.

4

4

NOTES:

R501/R515

R502/R514

R503/R513

R504/R512

R505/R511

Micro-Star International Co., LTD.

Maverick GPIO and LoR

Size Document Number Rev

B

8622-100 ATI PCI-E TV CARD

3

2

Date:

Friday, August 27, 2004

1

511

Sheet of

100

Page 7

5

D D

Locate near U102

Trace impedance = 65 ohms.

MA0

MA1

MA2

MA3

MA4 MA1

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

C C

+MVDDQ

C602 100nF

R607 499R

C603 100nF

R610 499R

+MVDDQ

RP610A 22R

RP610B 22R

RP610C 22R

C604 100nF

R616 499R

R670 22R

R672 22R

R674 22R

R676 22R

R679 22R

R688 22R

R694 22R

R697 22R

R6100 22R

R6103 22R

R6106 22R

R6109 22R

C605 100nF

R618 499R

81

72

63

R608 5.1K

R611 5.1K

R613 5.1K

R614 5.1K

RIO_MA0

RIO_MA1

RIO_MA2

RIO_MA3

RIO_MA4

RIO_MA5

RIO_MA6

RIO_MA7

RIO_MA8

RIO_MA9

RIO_MA10

RIO_MA11

RIO_MA12

RIO_MA13

RIO_MA14

DNI

DNI

G22

E22

E21

G20

H22

H20

E20

D22

D21

G21

H21

B20

A21

C21

D20

B21

R617

45.3R

F22

F21

F20

J20

U101C

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10/AP

MEM_A11

MEM_A12

MEM_A13/BA1

MEM_A14/BA0

MEM_VREFD

MEM_VREFS

MEM_VMODE_0

MEM_VMODE_1

MEM_TEST

RIO510

+2.5V Regulator for MVDDC

B B

+12V_BUS

+3.3V_BUS

R6137 560R

C636

1uF

I(load) = 170 mA max.

Est. Regulator Power = 0.14W @ 2.5V

Est. Regulator Power = 0.26W @ 1.8V

Q903

ZXM61N03FTA

3 2

1

REG601

DNI

4

NC

1

NC

2

TL431CDBVR

5 3

+MVDDC

0R

R6138

C654

1nF

R6139 1.0K

C608

10uf

+3.3V_BUS

C628

470uF_10V

+MVDDQ

+2.5V Regulator for MVDDQ

+12V_BUS

A A

Est. Regulator Power = 0.95W

I(load) = 450 mA peak parallel termination.

I(load) = 120 mA max. serial termination.

+3.3V_BUS

R6140 560R

C637

1uF

Q904

ZXM61N03FTA

3 2

1

REG602

DNI

4

NC

1

NC

2

TL431CDBVR

5 3

5

+MVDDQ

0R

R6141

C655

1nF

R6142 1.0K

C607

10uf

+MVDDC +MVDDQ

C615 100nF

C614 100nF

Place near U601

pins 1, 18 and 33

4

RIO_MDQ0

V20

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQM0

MEM_DQM1

MEM_RAS#

MEM_CAS#

MEM_WE#

MEM_CS#

MEM_QS0

Memory Interface (3/9)

MEM_QS1

MEM_CLK

MEM_CLK#

MEM_CKE

V22

V21

U20

T20

T21

T22

R20

M21

M22

M20

N22

N20

P21

P20

R21

R22

L22

K21

K22

L21

J21

U21

N21

K20

L20

J22

RIO_MDQ1

RIO_MDQ2

RIO_MDQ3

RIO_MDQ4

RIO_MDQ5

RIO_MDQ6

RIO_MDQ7

RIO_MDQ8

RIO_MDQ9

RIO_MDQ10

RIO_MDQ11

RIO_MDQ12

RIO_MDQ13

RIO_MDQ14

RIO_MDQ15

RIO_RAS#

RIO_CAS#

RIO_WE#

RIO_CS#

CLK

CLK#

RIO_CKE

+1.25V Regulator for MVTT

3

REG603

1 5

R606 100K

R609 100K

C609 1uF

C616 100nF

4

IN VOUT

4 2

I(load) = +/- 450 mA peak

Est. Regulator Power = 0.75W

Place near U601

pins 3, 9, 15, 55 and 61

VCNTL

REFEN GND

RT9173ACL5

C619 100nF

C617 100nF

C618 100nF

MA[14..0]

RP604B 22R

RP604C 22R

RP604D 22R

RP604A 22R

6

TAB

C621 100nF

C620 100nF

3

RIO_MDQ0

RIO_MDQ1

RIO_MDQ2

RIO_MDQ3

RIO_MDQ4

RIO_MDQ5

RIO_MDQ6

RIO_MDQ7

RIO_MDQ8

RIO_MDQ9

RIO_MDQ10

RIO_MDQ11

RIO_MDQ12

RIO_MDQ13

RIO_MDQ14

RIO_MDQ[15..0]

RIO_MDQ15

72

63

54

81

RIO_QS0

RIO_QS1

R6125 56R

Locate near U102

Trace impedance

= 65 ohms.

C610

10uf

Locate near U601

Trace impedance

= 65 ohms.

RP606A 47R

RP606B 47R

RP606C 47R

RP606D 47R

RP607A 47R

RP607B 47R

RP607C 47R

RP607D 47R

RP608D 47R

RP608C 47R

RP608B 47R

RP608A 47R

RP609D 47R

RP609C 47R

RP609B 47R

RP609A 47R

Locate near U601

Trace impedance = 65 ohms.

RP601D 22R

RP601C 22R

RP601B 22R

RP601A 22R

RP602D 22R

RP602C 22R

RP602B 22R

RP602A 22R

RP605A 22R

RP605B 22R

RP605C 22R

RP605D 22R

RP603A 22R

RP603B 22R

RP603C 22R

RP603D 22R

RIO_DQM0

RIO_DQM1

RAS#

CAS#

WE#

CS#

CKE

+MVTT

C629

330uF_2.5V

RP610D 22R

RP612A 47R

RP615A 47R

+MVTT

81

C622 100nF

72

63

C623 100nF

54

81

C624 100nF

72

63

54

54

63

72

81

54

63

72

81

MDQ0

54

MDQ1

63

MDQ2

72

MDQ3

81

MDQ4

54

MDQ5

63

MDQ6

72

MDQ7

81

MDQ8

81

MDQ9

72

MDQ10

63

MDQ11

54

MDQ12

81

MDQ13

72

MDQ14

63

MDQ15

54

+MVTT

C631 100nF

C630 100nF

Signal integrity capacitors for

middle layer address lines.

54

81

81

MVDDQ & MVDDC Regulator Sharing

B601 600R

3

+MVDDC+MVDDQ

DNI

C632 100nF

MDQ3

MDQ2

MDQ1

MDQ0

MDQ4

MDQ5

MDQ6

MDQ7

MDQ8

MDQ9

MDQ[15..0]

MDQ10

MDQ11

MDQ15

MDQ14

MDQ13

MDQ12

MA12

+MVDDC+VDDC_18

+MVDDQ

C634 100nF

C633 100nF

U601

2

DQ0

4

DQ1

5

DQ2

7

DQ3

8

DQ4

10

DQ5

11

DQ6

13

DQ7

54

DQ8

56

DQ9

57

DQ10

59

DQ11

60

DQ12

62

DQ13

63

DQ14

65

DQ15

14

NC

17

NC#17

19

NC#19

25

NC#25

42

NC#42

43

NC#43

50

NC#50

53

NC#53

1

VDD

18

VDD#18

33

VDD#33

3

VDDQ

9

VDDQ#9

15

VDDQ#15

55

VDDQ#55

61

VDDQ#61

34

VSS

48

VSS#48

66

VSS#66

6

VSSQ#6

12

VSSQ#12

52

VSSQ

58

VSSQ#58

64

VSSQ#64

23542742F04

23522742P04

+MVTT

VREF

A10/AP

LDQS

UDQS

4MX16X4

COMMON

2

R604 0R

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

CK

CK

CKE

CS

RAS

CAS

WE

LDM

UDM

BA0

BA1

2

49

29

30

31

32

35

36

37

38

39

40

28

41

45

46

44

24

23

22

21

16

51

20

47

26

27

R601 5.1K

R602 5.1K

C606 100nF

R603 56R

R605 56R

CKE

CS#

RAS#

CAS#

WE#

QS0

QS1

DQM0

DQM1

+MVTT

Locate near U601

CLK

CLK#

1

+MVDDQ

Locate near U601

Trace impedance

= 65 ohms.

C601 10nF

CKE

R6116 47R

CS#

RP613A 47R

RAS#

RP613B 47R

CAS#

RP613C 47R

WE#

RP613D 47R

Locate near U601

R6120 56R

R6122 56R

R6112 56R

R6113 56R

Locate near U601

Trace impedance

= 65 ohms.

R6126 47R

R6127 47R

R6128 47R

R6129 47R

RIO_QS0

RIO_QS1

RIO_DQM0

RIO_DQM1

MA14

MA13

RIO_QS0

RIO_QS1

RIO_DQM0

RIO_DQM1

MA0

MA2

MA3

MA4

MA5

MA6

MA7

MA9

MA10

MA11

81

72

63

54

+MVTT

MA0

RP611A 47R

MA1

RP612D 47R

RP612C 47R

MA2

RP612B 47R

MA3

RP614D 47R

MA4

MA5

RP614C 47R

RP614B 47R

MA6

RP614A 47R

MA7

MA8MA8

RP615D 47R

MA9

RP615C 47R

RP611B 47R

MA10

MA11

RP615B 47R

MA14

RP611D 47R

RP611C 47R

MA13

MA12

R6136 47R

Pad sharing:

R608/R611

R613/R614

R604/R601

Micro-Star International Co., LTD.

Maverick GPIO and LoR

Size Document Number Rev

B

8622-100 ATI PCI-E TV CARD

Friday, August 27, 2004

Date:

Sheet of

1

+MVTT

81

54

63

72

54

63

72

81

54

63

72

72

C626 100nF

C627 100nF

Locate near U601

+MVTT

54

63

611

100

Page 8

5

4

3

2

1

D D

C701 1uF

+3.3V_BUS

R703

C C

C705

Unassigned

C703 33pF

C708

10nF

10K

2

3

4

5

6

7

R706

12K

R707

47K

+12V_BUS

R701

2.2R

C713 1nF

R702 33K

U701

OCSET

SS

COMP

FB

EN

GND

ISL6522CB

DNI

LGATE

UGATE

PHASE

VCCRT

PVCC

PGND

BOOT

D701

BAV99

141

13

12

11

10

9

8

3

R712 0R

2 1

C712 100nF

C704 100nF

C709 10nF

R704 10K

4

2

71

53

6

Q701B

FDS6898A

8

Q701A

FDS6898A

R713 0R

L701 68uH

B701 60R

C702

10uF

DNI

1 2

D702

SK14

0.8V

DNI

2 1

+12V_BUS

R705

5.11K

R708

715R

6.5V

C706

100uF_16V

C707

33uF_16V

+6.5V_SMPS

C710

4.7uF

+6.5V SMPS

B B

+6.5V_SMPS

+12V_BUS

C711 100nF

RF

A A

REG701

TL431CDBVR

C856

4.7uF

R709

680R

NC

NC

5 3

RF

5

Q702

RF

C714

1nF

R710 1.50K

4

1

R711 1.50K

2

4

1

32

BCP68

RF

+5V_RF

C715

4.7uF

RF

4

Micro-Star International Co., LTD.

Maverick Tuner SMPS & +5V_RF Regulator

Size Document Number Rev

A

3

Date:

8622-100 ATI PCI-E TV CARD

Friday, August 27, 2004

2

Sheet of

1

711

100

Page 9

5

4

3

2

1

Shunt regulator for +MPVDD

Vout = 1.8V

Iout = 20 mA max. (75R)

+3.3V_BUS

C809

1uF

Possible

Pad sharing:

REG802/MREG802

REG804/MREG804

+3.3V_BUS

+3.3V_BUS

B801 60R

C853

4.7uF

C850

10uF

R804 30.1K

R805 30.1K

I(load) = 1200 mA max.

Est. Regulator Power = 0.25W

+1.2V Regulator for VDDC

+3.3V_BUS

10

11

12

DNI

D D

REG802

U101I

A2

VSS_1

A6

VSS_2

A19

VSS_3

B2

VSS_4

B19

VSS_5

C3

VSS_6

C19

VSS_7

D4

VSS_8

D8

VSS_9

D9

VSS_10

D10

VSS_11

D14

VSS_12

D15

VSS_13

D19

VSS_14

E4

VSS_15

E19

VSS_16

F4

VSS_17

H9

VSS_18

H10

C C

B B

A A

H11

H12

H13

H14

J10

J11

J12

J13

J14

J15

K10

K11

K12

K13

K14

K15

K19

L10

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

J8

VSS_24

J9

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

K8

VSS_32

K9

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

L8

VSS_41

L9

VSS_42

VSS_43

RIO510

Digital Core & I/O Ground (9/9)

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

L11

L12

L13

L14

L15

L19

M8

M9

M10

M11

M12

M13

M14

M15

M19

N8

N9

N10

N11

N12

N13

N14

N15

N19

P8

P9

P10

P11

P12

P13

P14

P15

R9

R10

R11

R12

R13

R14

V4

W4

W9

W10

W11

+3.3V_BUS

+3.3V_BUS

+MVDDQ

+VDDC_18

+MVDDQ +VDDC+3.3V_BUS +VDDC_18

K18

P18

V18

W13

W14

W15

D11

D12

D13

D16

D17

D18

F19

G19

H19

J19

P19

R19

T19

U19

V19

F17

U17

W5

W6

W7

W8

D5

D6

D7

G4

F6

U6

U101H

PESD_1

PESD_2

PESD_3

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

VDDP_6

VDDP_7

VDDR4_1

VDDR4_2

VDDR4_3

VDDR4_4

VDDR4_5

VDDR4_6

VDDR4_7

VDDR4_8

VDDR4_9

VDDR4_10

RIO510

VDDR1_1

VDDR1_2

VDDR1_3

VDDR1_4

VDDR1_5

VDDR1_6

VDDR1_7

VDDR1_8

VDDR1_9

VDDC18_1

VDDC18_2

VDDC18_3

VDDC18_4

PCI

ESD

MEM

PLL

Core

PLL

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

Core

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

Digital Core & I/O Power (8/9)

VDDC_17

VDDC_18

VDDC_19

VDDC_20

Mem Mem I/O Digital I/O PCI I/O

VDDC_21

VDDC_22

MPVDD

MPVSS

VPVDD

VPVSS

C22

B22

H1

J1

G7

G8

G9

G15

G16

H7

H16

J16

P7

R7

R16

T3

T4

T7

T8

T14

T15

T16

U1

U2

U3

U4

+VPVDD

VPVSS

+VDDC

C805

100nF

AS432S

3 2

C806

4.7uF

C808 4.7uF

C807 100nF

VPVSS

Linear regulator for +PVDD

Vout = 1.8V

Iout = 130 mA max.

Pdiss= 0.2W max.

+MPVDD

R802

681R

1%

1

R803

1.5K

1%

REG803 1.8V

4

NC/FB

5

OUT

2

4

NC

1

NC

2

EN

GND

TPS76318

VPVSS

R801 75R

5 3

MPVSS

1

IN

3

MREG802

SC431LC5SK-1

DNI

+1.8V Regulator for VDDC18

+3.3V_BUS

1

C803

1uF

U801

7

8

9

4

MVPG30E-A2-NAE-C000-T

PVIN

SVIN

N/C

SHDN

VSET

PSET

SGND

ILIM

LDR

LFB

SFB

SWPGND

D801

B330B

DNI

R6143 75R

MREG804

3 2

2

3

1

5

6PAD

IN

3

EN

DNI

DNI

I(load) = 10 mA max.

Est. Regulator Power = 0.1W

R806

681R

1%

1

AS432S

L801

12

2.0uH

R807

1.5K

1%

4

1

2

REG8011.8V

NC/FB

OUT

GND

TPS76318

2

NC

NC

5 3

C851

10uF

+VDDC_18

4

5

REG804

SC431LC5SK-1

DNI

+VDDC

C852

10uF

C804

4.7uF

C810 2.2uF

C811 100nF

C812 100nF

C813 100nF

C814 100nF

5

C815 100nF

C816 100nF

C817 100nF

C818 100nF

C819 100nF

C820 100nF

C887 2.2uF

C821 2.2uF

C822 100nF

C823 100nF

C824 100nF

C825 100nF

C826 100nF

C827 100nF

4

C829 100nF

C830 2.2uF

C831 100nF

C832 100nF

C833 2.2uF

C834 100nF

C835 100nF

C836 100nF

C837 100nF

C838 100nF

C839 100nF

3

C840 100nF

C841 100nF

C842 2.2uF

C843 100nF

C844 100nF

C845 100nF

C846 100nF

C847 100nF

C848 100nF

C849 100nF

Micro-Star International Co., LTD.

Maverick Rio Power

Size Document Number Rev

B

8622-100 ATI PCI-E TV CARD

2

Date:

Friday, August 27, 2004

1

811

Sheet of

100

Page 10

5

U101D

C15

GPIOd_A0/TI_DATA0/TI_SDATA1

A16

GPIOd_A1/TI_DATA1/TI_CLK2

B16

GPIOd_A2/TI_DATA2/TI_SDATA2

C16

GPIOd_A3/TI_DATA3/TI_STRT2

C17

GPIOd_A4/TI_DATA4/TI_VALID2

A18

GPIOd_A5/TI_DATA5/TI_ERR2

B18

D D

C C

B B

+3.3V_BUS

A A

PCI_RESET#(1)

GPIOd_A6/TI_DATA6/LOR2

C18

GPIOd_A7/TI_DATA7/LOR3

B15

GPIOd_A9/TI_START1

A15

GPIOd_A10/TI_VALID1

B17

GPIOd_A8/TI_CLK1

B14

GPIOd_A11/TI_ERR1

RIO510

R902 10K

R903 10K

DNI

R904 10K

5

U101A

AB15

AD0/GPIO_E0/TO_ERR1

AA15

AD1/GPIO_E1/TO_VALID1

Y15

AD2/GPIO_E2/TO_START1

AB14

AD3/GPIO_E3/TO_SDATA1

AA14

AD4/GPIO_E4/TO_CLK1

Y14

AD5/GPIO_E5

AB13

AD6/GPIO_E6

Y13

AD7/GPIO_E7

AB12

AD8/GPIO_E8

AA12

AD9/GPIO_E9

Y12

AD10/GPIO_E10

AB11

AD11/GPIO_E11

AA11

AD12/GPIO_E12

Y11

AD13/GPIO_E13

AB10

AD14/GPIO_E14

AA10

AD15/GPIO_E15

Y7

AD16/GPIO_E16

AB6

AD17/GPIO_E17

AA6

AD18/GPIO_E18

Y6

AD19/GPIO_E19

AB5

AD20/GPIO_E20

AA5

AD21/GPIO_E21

Y5

AD22/GPIO_E22

AB4

AD23/GPIO_E23

AB3

AD24/GPIO_E24

AA3

AD25/GPIO_E25

Y3

AD26/GPIO_E26

AB2

AD27/GPIO_E27

AA2

AD28/GPIO_E28

Y2

AD29/GPIO_E29

AA1

AD30/GPIO_E30

Y1

AD31/GPIO_E31

AA13

C/BE0#/GPIO_E32

Y10

C/BE1#/GPIO_E33

AA7

C/BE2#/GPIO_E34

Y4

C/BE3#/GPIO_E35

AB9

PAR/GPIOd_E41

Y8

FRAME#/GPIOu_E36

W3

STOP#/GPIOu_E40

AB7

IRDY#/GPIOu_E37

AA8

TRDY#/GPIOu_E38

AA9

DEVSEL#/GPIOu_E39

V1

PERR#/VIP_HAD1/GPIOu_E43

W1

SERR#/VIP_HAD0/S_SCL/GPIOu_E44

AB8

REQ#/GPIOu_E42

V2

GNT#/VIP_HCTL/S_SDA/GPIOu_E45

AA4

IDSEL

W12

INTA#/INT#

Y9

PCI_CLK/VIP_CLK

W2

RST#/PERST#/VRST#

RIO510

GPIOd_B0/TO_DATA0/PDATA2

GPIOd_B1/TO_DATA1/PDATA3

GPIOd_B2/TO_DATA2/PDATA4

GPIOd_B3/TO_DATA3//PDATA5

GPIOd_B4/TO_DATA4/PDATA6

GPIOd_B5/TO_DATA5/PDATA7

GPIOd_B6/TO_DATA6/PDATA8

GPIOd_B7/TO_DATA7/PDATA9

GPIOd_B9/TO_START1

Transport

GPIOd_B10/TO_VALID1

Interface

(4/9)

GPIOd_B8/TO_CLK1/PCLK

GPIOd_B11/TO_ERR1

PCI_VREF

PCI (VIP) Interface (1/9)

4

C11

B11

C12

B12

C13

B13

A13

C14

A10

B10

A12

C10

R901 100K

V3

4

3

+VDDC_18

2

1

Micro-Star International Co., LTD.

U303B

-

6

5

RF

+

LM324M

7

3

2

Maverick Spare & Unused Devices

Size Document Number Rev

B

Date:

8622-100 ATI PCI-E TV CARD

Friday, August 27, 2004

1

911

Sheet of

100

Page 11

5

4

3

2

1

BRACKET MOUNTING PARTS

MISC. BOARD PARTS

ASSY1001

SCREW

PAN_HEAD

D D

ASSY1002

SCREW

PAN_HEAD

ASSY1003

BLANK

LABEL

1.50W_X_0.50H

REF1001

PCB

ASSY

109-A34700-00A

Place bracket here when

part/symbol available

- ASSY1003.

ASSY1005

ANTISTATIC

BAG

6_X_11

REF1002

ATI LOGO

LABEL

ATI_LOGO_LABEL

ASSY

MT1001

MT_Hole_0.136_in.

C C

MT1002

MT_Hole_0.136_in.

c c

ASSY906

Need tuner can when ready.

Mounting holes: TP203X127

TP1001

HOLE

B B

TP1002

HOLE

TP1003

HOLE

TP1004

HOLE

RF

A A

Micro-Star International Co., LTD.

Maverick Mechanical & Miscellaneous H/W for BOM

Size Document Number Rev

A

5

4

3

Date:

8622-100 ATI PCI-E TV CARD

Friday, August 27, 2004

2

Sheet of

1

10 11

100

Page 12

5

D D

C C

4

3

2

1

B B

A A

These nets are to be shorted manually

c

GND_RF

GND

5

4

VPVSS MPVSS

GND_VPVSS

GND_MPVSS

AUD AVSSOSCRF

GND_AUDIO

GND_CGND_OSC_AVSS

3

GND_AVSS

2

Micro-Star International Co., LTD.

Maverick Block Diagram

Size Document Number Rev

B

Date:

8622-100 ATI PCI-E TV CARD

Friday, August 27, 2004

1

11 11

Sheet of

100

Loading...

Loading...