Page 1

5

smd.db-x7.ru

4

3

2

1

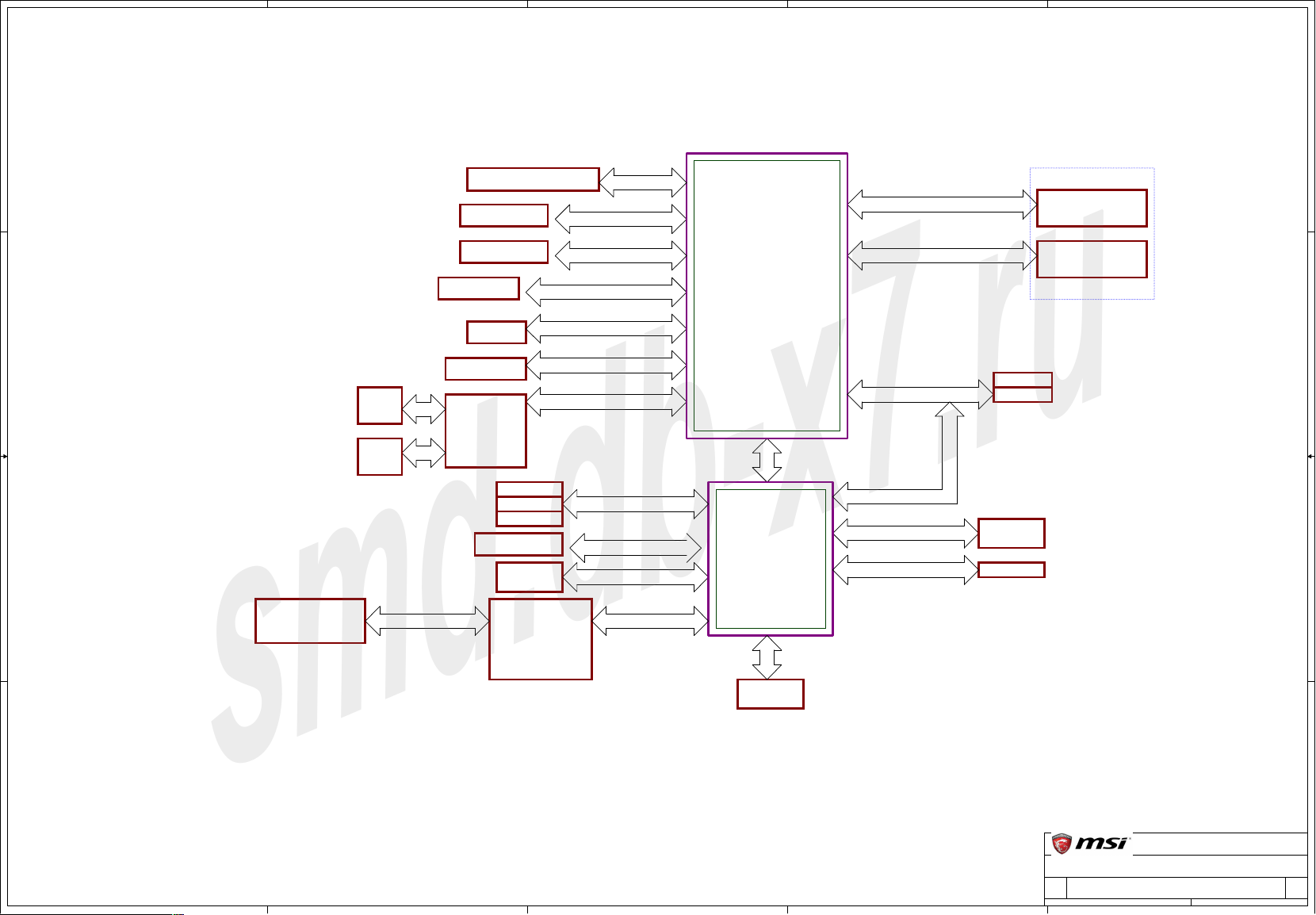

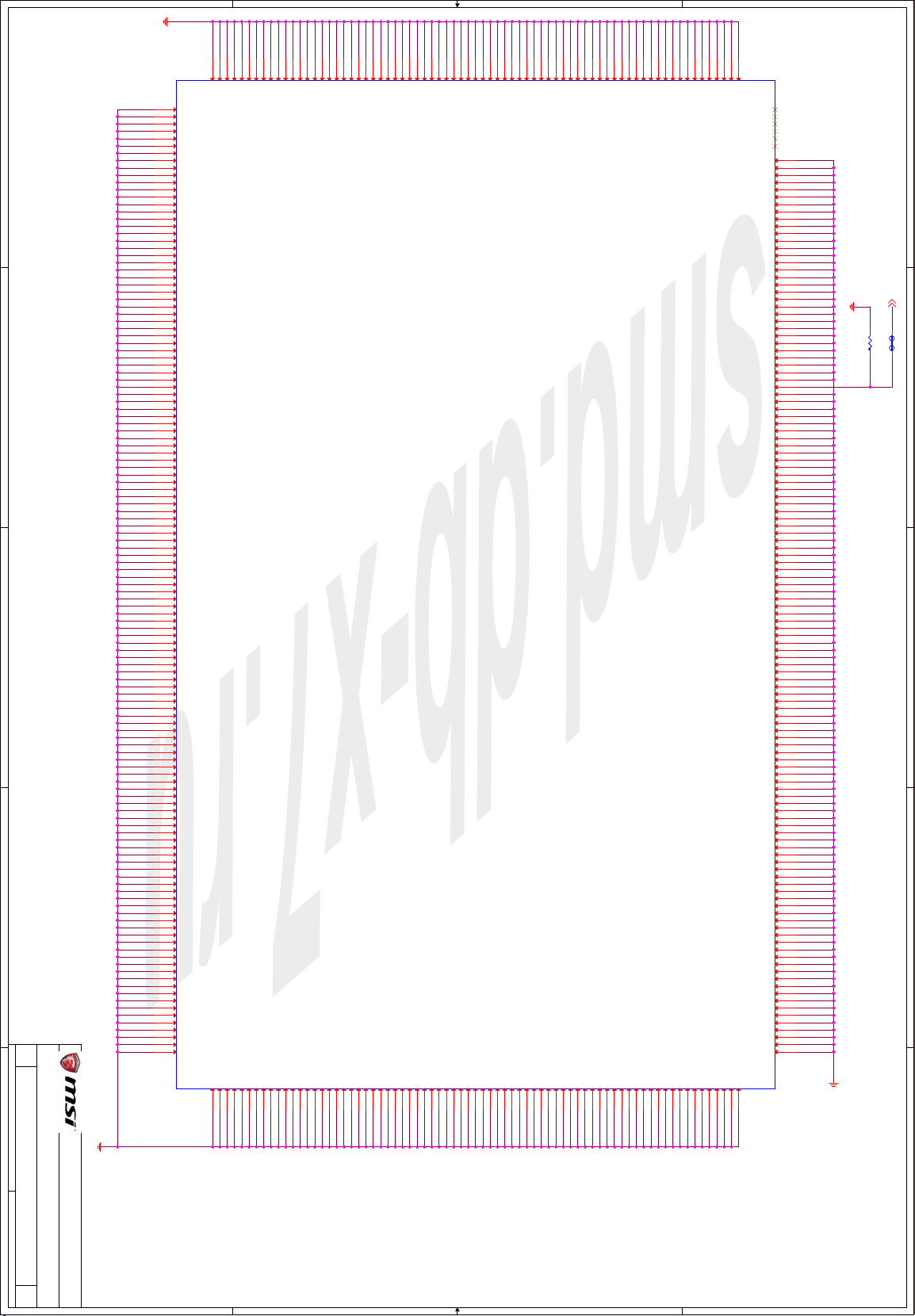

MS-7C58 Ver:10

CPU:

AMD AM4

D D

System Chipset:

Promontory A320 / B450

(Value DIY or System Builder)

Main Memory:

DDR IV * 2 MAX:64 GB

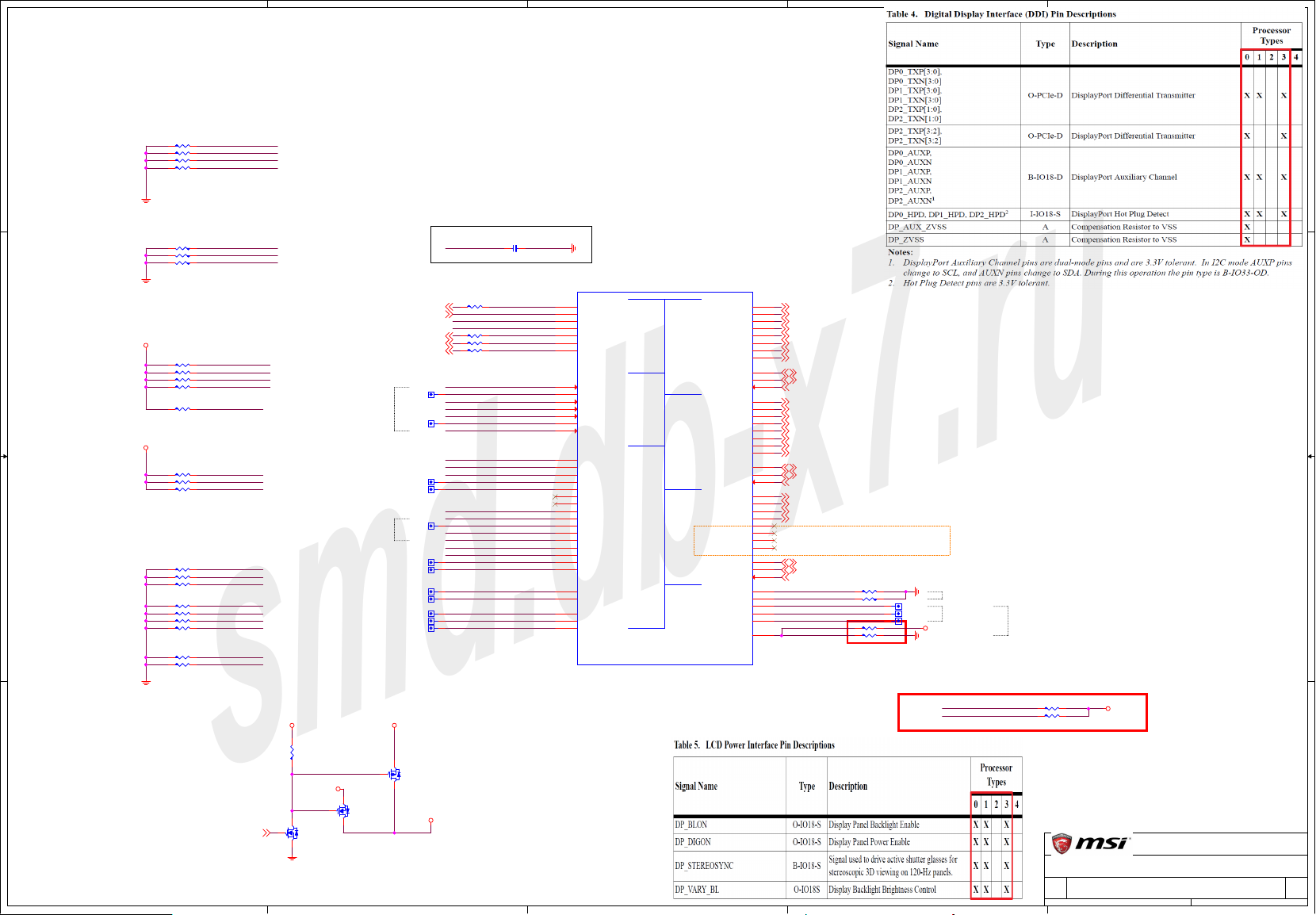

FUSION BLOCK DIAGRAM

DP to VGA & DVI CON & HDMI

PCIE x16 GEN3

DP0~1

PCIEx16

AM4

DDRIV 2400

CHA

UNBUFFERED

DDRIV DIMM1

00

VRM

RT8894 3+2

On Board Chipset:

LPC Super I/O --NCT6797D

C C

LAN RTL8111H

Azalia CODEC - Realtek ALC892

Expansion Slots:

KBD

MOUSE

From CPU

PCI Express X16 Slot * 1

PCI Express X1 Slot * 2

COM*2

LPT*1

PCI Slot * 1

M.2 Slot * 1

OCP IC:

UP6273

B B

PCI x1 Slot

PCI1

PCI

M.2 *x4 GEN3

REAR USB *4

ALC892

SPI ROM 16M/32M

NCT6797D

PCIE x1 *2 GEN3

PCIe To PCI

JUSB1

JUSB2

PS2+USB

JUSB3

Bridge

GPP_PCIE

USB2.0 & USB3.1 GEN1

AUDIO

SPI Bus

LPC

USB2.0

GPP_PCIE

USB3.1 GEN1

PCIe GEN2 x1

GPP[7]

Bristol Ridge

&

Summit Ridge

CLOCK

HUB *4

Promontory

PROM1

Chipset

A320/B450

GEN3

DDRIV 2400

PCIE SLOT & PROM

CLOCK 100MHz

USB 3.0

GPP_PCIE GEN2

CHB

PCIE_E1

USB X6

RTL8111H

UNBUFFERED

DDRIV DIMM2

01

Asmedia

ASM1083

SATA [4:1]

A A

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-7C58

MS-7C58

MS-7C58

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

10

10

1 55Monday, November 11, 2019

1 55Monday, November 11, 2019

1

1 55Monday, November 11, 2019

10

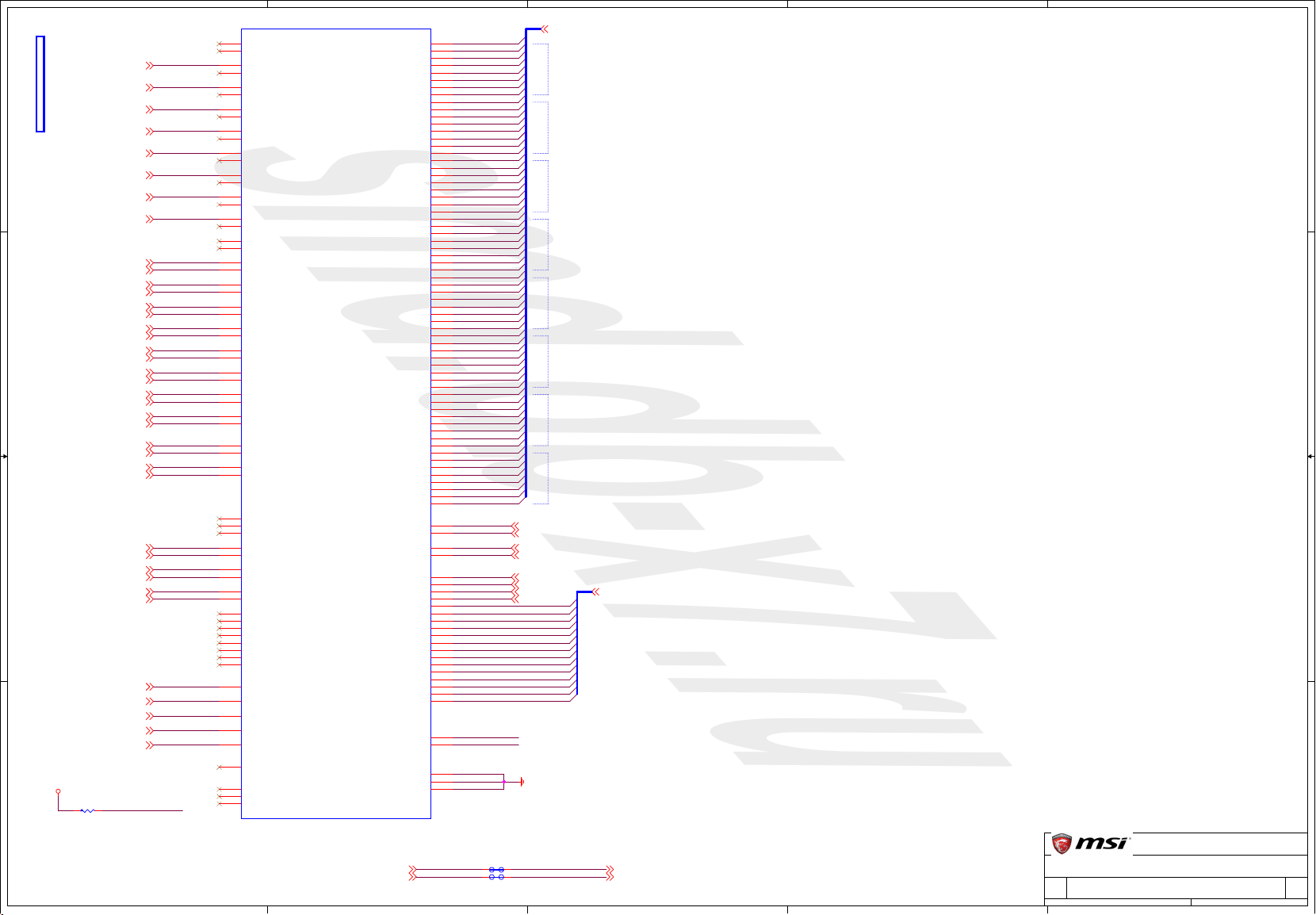

Page 2

1

smd.db-x7.ru

AMD

AM

A A

4

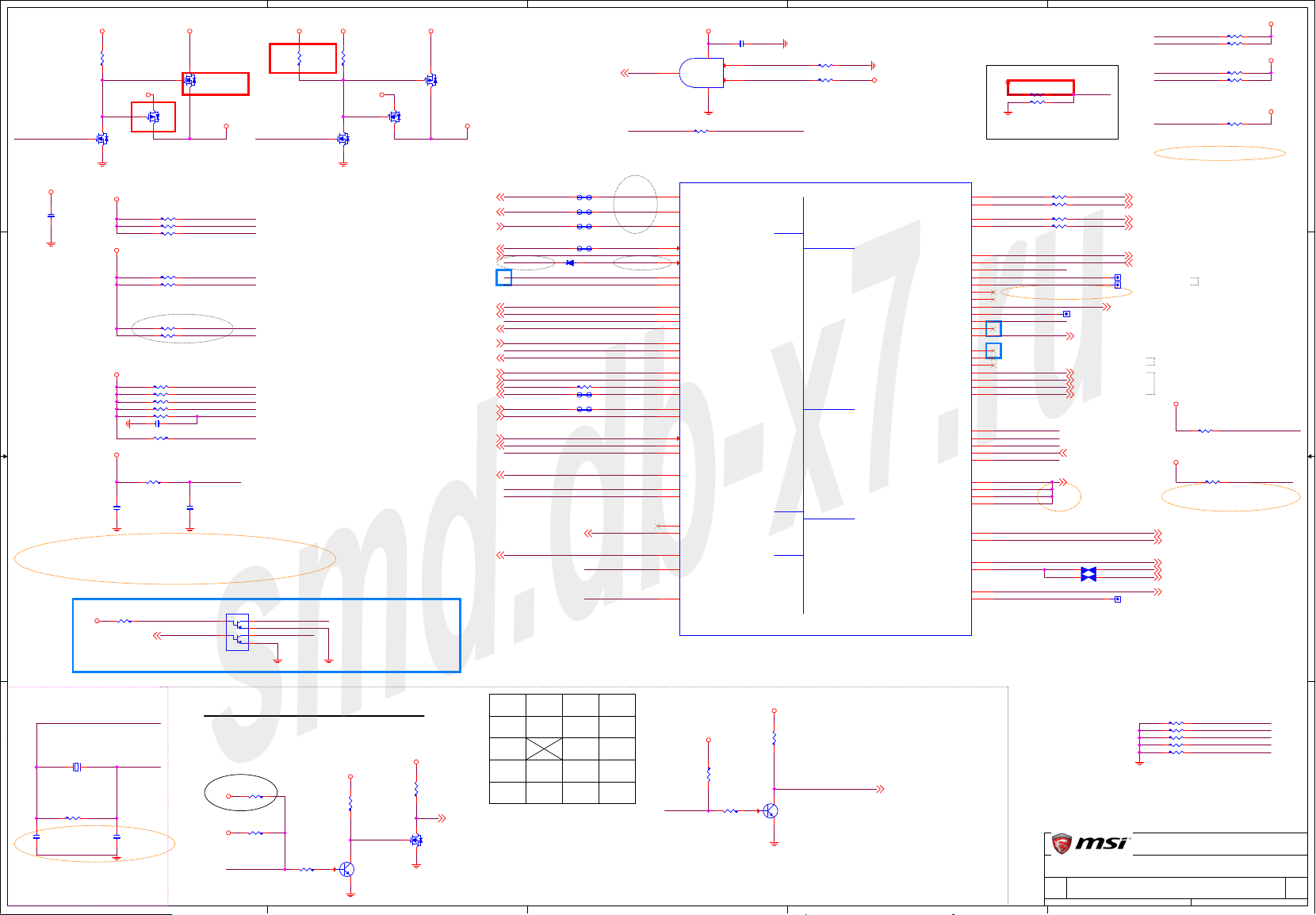

01 Block Diagram

02 Cover Sheet

03 FM4 DDR4 I/F

04 AM4 PCIE/SATAE

05 AM4 Display/Audio

06 AM4 SVI/ACPI/GPIO

07 AM4 LPC/SPI/USB/CLK/STRAP

08 AM4 Power/RTC Power/ 09 AM4 GND

10,11 DDR4-DIMM CH-A/B

12,13 DDR4-POWER/GND

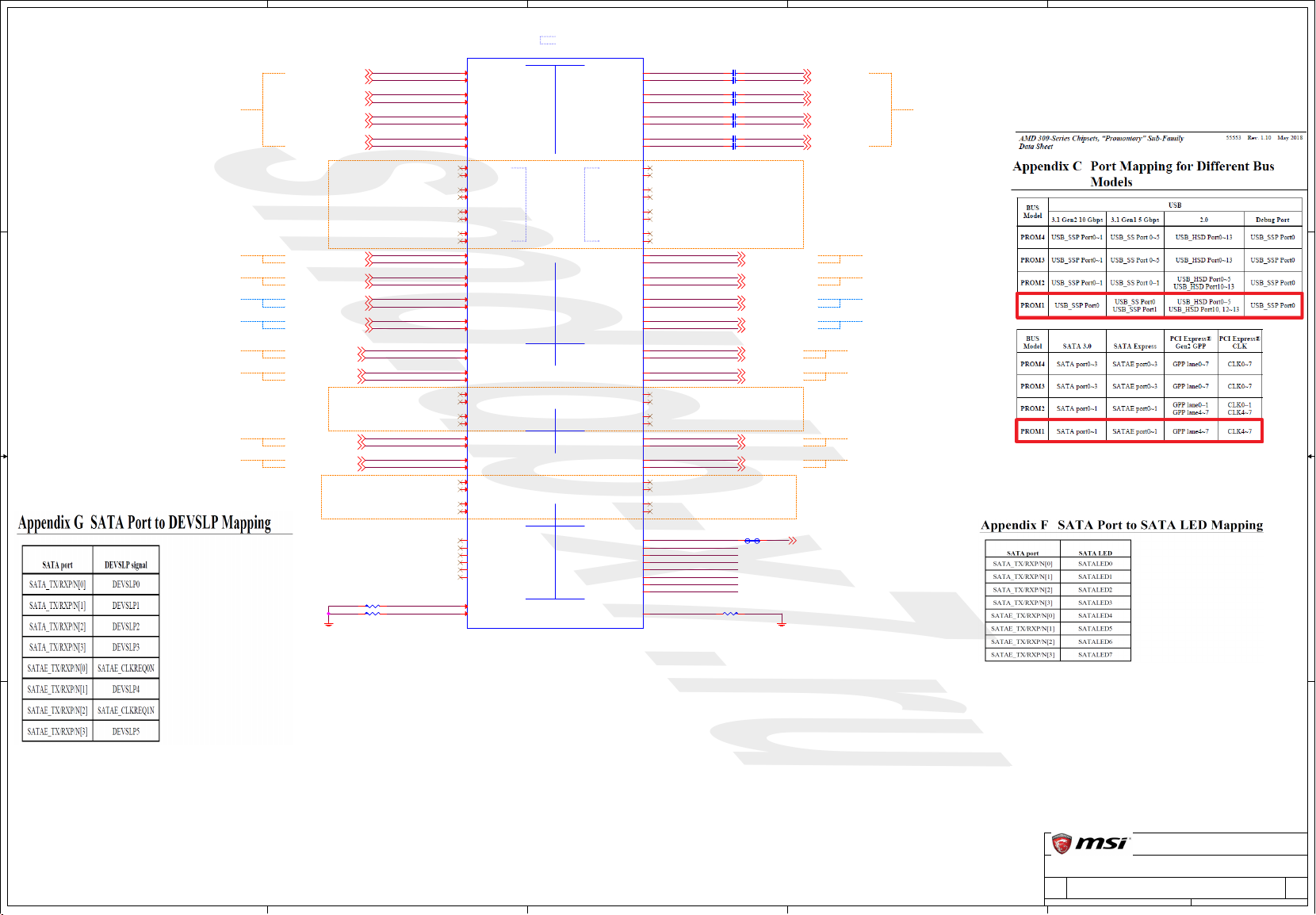

14 Promontory-PCIE/SATA/SATAE

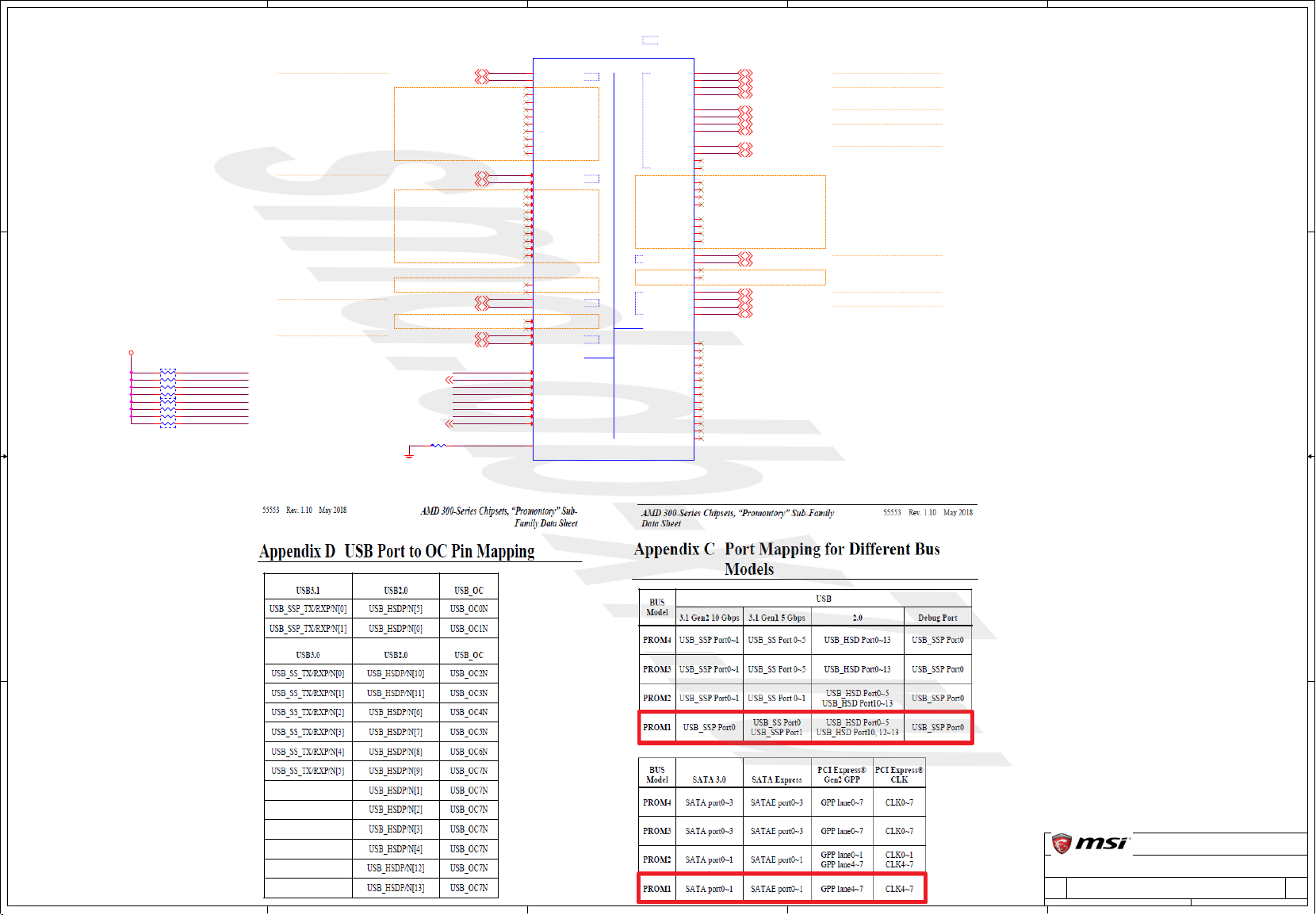

15 Promontory-USB/OC

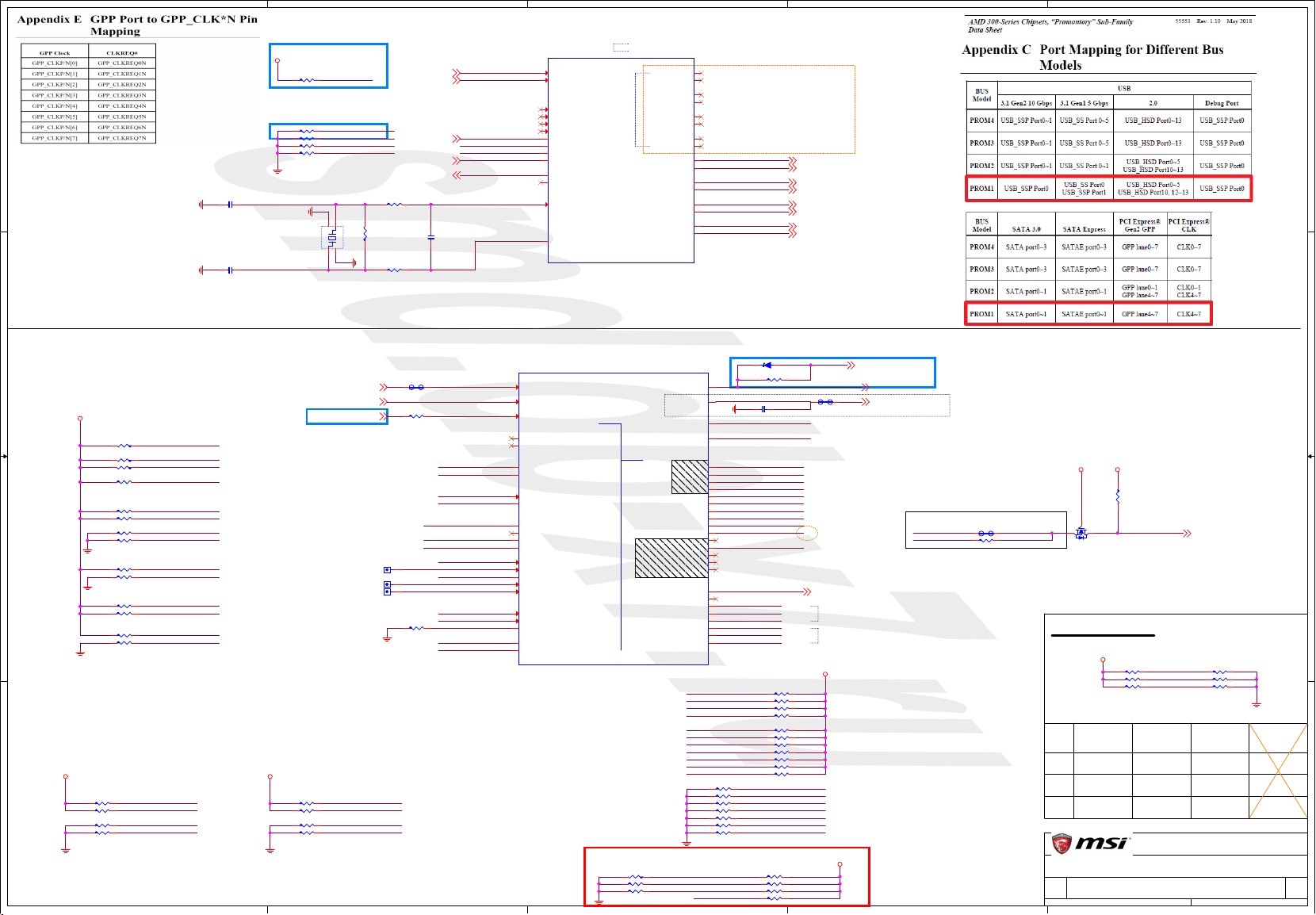

16 Promontory-CLK/ACPI/GPIO

17 Promontory-Power / 18 Promontory-GND

19 PCIE X16/X1 SLOT

20 ASM1083 PCI Bri.

37 DDR Power-RT8231AGQW

38 CPU Power 1P8_S0/S5

39 CPU Power VDDP

40 PWRGD

41 CPU Power RT8894 3+2 Phase

42 CPU Power Phase 1-3

43 CPU Power NB Phase 1-2

44 CPU Power NB Switch/NCT3933

45 CPU_PWR_CONN

46 ATX/Front Panel

47 ALL LED Control

48 RTC Circuit / Moat Cap

49 HDMI Connector

50 M2

51 BOM Option

52 History

21 PCI Slot/PCIE X1 Slot

22,23 SIO NCT6797D COM/LPT/HWM

24 CPU/SYS FAN + PS2

25 LAN-RTL8111H

26,27 Audio ALC892

28 Rear USB2.0 + USB Power

29 Rear USB 3.1 GEN1

30 Front USB2.0 + 3.1 GEN1

31 SATA Connector

32 DVI Connector

33 DP to VGA ITE6516

34 ACPI uPI-5VDIMM&3VSB

35 PM-1.05V/GS7133-2.5V

36 DDR PWR VPP25

53 Power Sequence

54 Power Delivery

55 GPIO MAP

1

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

COVER SHEET

COVER SHEET

COVER SHEET

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-7C58

MS-7C58

MS-7C58

Date: Sheet of

Date: Sheet of

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

2 55Monday, November 11, 2019

2 55Monday, November 11, 2019

2 55Monday, November 11, 2019

10

10

10

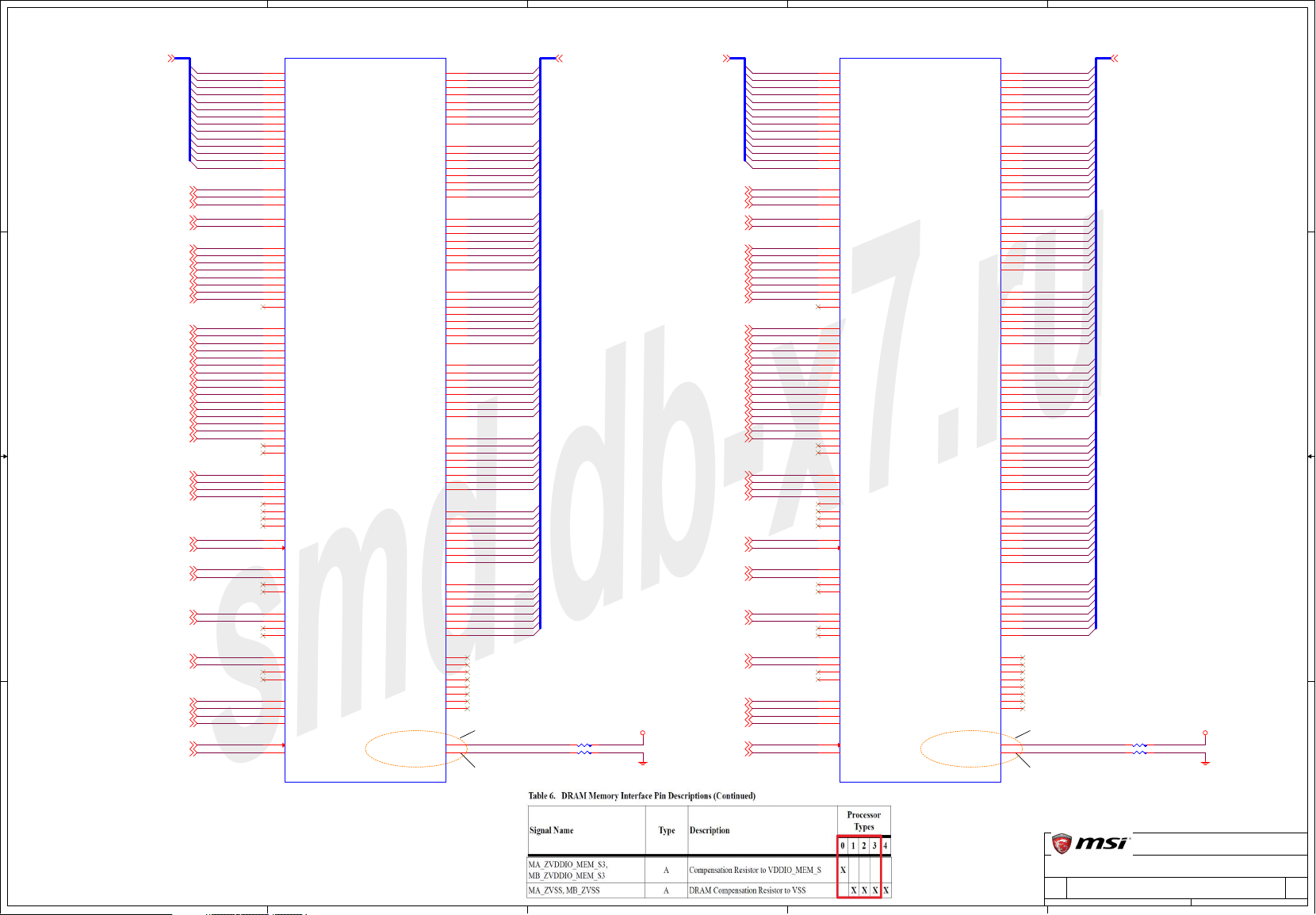

Page 3

5

smd.db-x7.ru

4

3

2

1

MA_ADD[13..0]10

D D

MA_ACT_L10

MA_BG010

MA_BG110

MA_BANK010

MA_BANK110

MA_DM010

MA_DM110

MA_DM210

MA_DM310

MA_DM410

MA_DM510

MA_DM610

MA_DM710

MA_DQS_H010

MA_DQS_L010

C C

B B

MA_DQS_H110

MA_DQS_L110

MA_DQS_H210

MA_DQS_L210

MA_DQS_H310

MA_DQS_L310

MA_DQS_H410

MA_DQS_L410

MA_DQS_H510

MA_DQS_L510

MA_DQS_H610

MA_DQS_L610

MA_DQS_H710

MA_DQS_L710

MA_CLK_H010

MA_CLK_L010

MA_CLK_H110

MA_CLK_L110

MA_RESET_L10

MA_EVENT_L10

MA0_CKE010

MA0_CKE110

MA0_ODT010

MA0_ODT110

MA0_CS_L010

MA0_CS_L110

MA_ADD_1710

MA_RAS_L10

MA_CAS_L10

MA_WE_L10

MA_ALERT_L10

MA_PAROUT10

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ACT_L

MA_BG0

MA_BG1

MA_BANK0

MA_BANK1

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_RESET_L

MA_EVENT_L

MA0_CKE0

MA0_CKE1

MA0_ODT0

MA0_ODT1

MA0_CS_L0

MA0_CS_L1

MA_ADD_17

MA_RAS_L

MA_CAS_L

MA_WE_L

MA_ALERT_L

MA_PAROUT

A A

AA32

AA36

AE32

M35

N31

N32

AA35

AA33

G26

H30

AJ31

AM31

AL29

AL26

G34

H19

G19

G23

AJ33

AJ34

AN32

AN33

AP29

AN29

AP26

AN26

H34

H33

U34

U33

W32

W35

M32

M30

M33

AD35

AF31

AD33

AF34

AC33

AE35

AC34

AE34

AF33

AB34

AD32

AB35

N34

CPU1A

T32

T35

T31

R30

R33

R32

P34

P30

P31

P33

N35

K19

J23

F23

F27

F26

F30

E30

T34

V33

V35

V36

V32

L33

L34

Y33

MA_ADD[0]

MA_ADD[1]

MA_ADD[2]

MA_ADD[3]

MA_ADD[4]

MA_ADD[5]

MA_ADD[6]

MA_ADD[7]

MA_ADD[8]

MA_ADD[9]

MA_ADD[10]

MA_ADD[11]

MA_ADD[12]

MA_ADD[13]

MA_ACT_L

MA_BG[0]

MA_BG[1]

MA_BANK[0]

MA_BANK[1]

MA_DM[0]

MA_DM[1]

MA_DM[2]

MA_DM[3]

MA_DM[4]

MA_DM[5]

MA_DM[6]

MA_DM[7]

MA_DM[8]

MA_DQS_H[0]

MA_DQS_L[0]

MA_DQS_H[1]

MA_DQS_L[1]

MA_DQS_H[2]

MA_DQS_L[2]

MA_DQS_H[3]

MA_DQS_L[3]

MA_DQS_H[4]

MA_DQS_L[4]

MA_DQS_H[5]

MA_DQS_L[5]

MA_DQS_H[6]

MA_DQS_L[6]

MA_DQS_H[7]

MA_DQS_L[7]

MA_DQS_H[8]

MA_DQS_L[8]

MA_CLK_H[0]

MA_CLK_L[0]

MA_CLK_H[1]

MA_CLK_L[1]

MA_CLK_H[2]

MA_CLK_L[2]

MA_CLK_H[3]

MA_CLK_L[3]

MA_RESET_L

MA_EVENT_L

MA0_CKE[0]

MA0_CKE[1]

MA1_CKE[0]

MA1_CKE[1]

MA0_ODT[0]

MA0_ODT[1]

MA1_ODT[0]

MA1_ODT[1]

MA0_CS_L[0]

MA0_CS_L[1]

MA1_CS_L[0]

MA1_CS_L[1]

MA_ADD_17

MA_RAS_L_ADD[16]

MA_CAS_L_ADD[15]

MA_WE_ L_ADD[14]

MA_ALERT_L

MA_PAROUT

PART 1 OF 9

MAMORY-A

AM4

MA_DATA[0]

MA_DATA[1]

MA_DATA[2]

MA_DATA[3]

MA_DATA[4]

MA_DATA[5]

MA_DATA[6]

MA_DATA[7]

MA_DATA[8]

MA_DATA[9]

MA_DATA[10]

MA_DATA[11]

MA_DATA[12]

MA_DATA[13]

MA_DATA[14]

MA_DATA[15]

MA_DATA[16]

MA_DATA[17]

MA_DATA[18]

MA_DATA[19]

MA_DATA[20]

MA_DATA[21]

MA_DATA[22]

MA_DATA[23]

MA_DATA[24]

MA_DATA[25]

MA_DATA[26]

MA_DATA[27]

MA_DATA[28]

MA_DATA[29]

MA_DATA[30]

MA_DATA[31]

MA_DATA[32]

MA_DATA[33]

MA_DATA[34]

MA_DATA[35]

MA_DATA[36]

MA_DATA[37]

MA_DATA[38]

MA_DATA[39]

MA_DATA[40]

MA_DATA[41]

MA_DATA[42]

MA_DATA[43]

MA_DATA[44]

MA_DATA[45]

MA_DATA[46]

MA_DATA[47]

MA_DATA[48]

MA_DATA[49]

MA_DATA[50]

MA_DATA[51]

MA_DATA[52]

MA_DATA[53]

MA_DATA[54]

MA_DATA[55]

MA_DATA[56]

MA_DATA[57]

MA_DATA[58]

MA_DATA[59]

MA_DATA[60]

MA_DATA[61]

MA_DATA[62]

MA_DATA[63]

MA_CHECK[0]

MA_CHECK[1]

MA_CHECK[2]

MA_CHECK[3]

MA_CHECK[4]

MA_CHECK[5]

MA_CHECK[6]

MA_CHECK[7]

MA_ZVDDIO_MEM_S3

MA_ZVSS

ZIF-SOCKET1331

E18

J18

J20

H21

H18

F18

G20

F20

H22

G22

E24

J24

F21

J21

H24

F24

J26

J27

G28

H28

H25

G25

E28

H27

F29

J30

H31

F32

J29

G29

E31

G31

AH34

AJ30

AK30

AL34

AH31

AH32

AK33

AK32

AM34

AM33

AP31

AR33

AL32

AL31

AP34

AP32

AR31

AK29

AM28

AL28

AM30

AN30

AP28

AR28

AK27

AK26

AP25

AR25

AN27

AM27

AL25

AM25

F33

G32

K31

K32

E33

E34

J32

J33

Type0 Only

MA_ZVDDIO_MEM_S3

Y34

MA_ZVSS

AJ37

Type2/3 Only

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DATA[63..0] 10

VCC_DDR VCC_DDR

R269 X_40.2R1%/4 R271 X_40.2R1%/4

MB_ADD[13..0]11

MB_ACT_L11

MB_BG011

MB_BG111

MB_BANK011

MB_BANK111

MB_DM011

MB_DM111

MB_DM211

MB_DM311

MB_DM411

MB_DM511

MB_DM611

MB_DM711

MB_DQS_H011

MB_DQS_L011

MB_DQS_H111

MB_DQS_L111

MB_DQS_H211

MB_DQS_L211

MB_DQS_H311

MB_DQS_L311

MB_DQS_H411

MB_DQS_L411

MB_DQS_H511

MB_DQS_L511

MB_DQS_H611

MB_DQS_L611

MB_DQS_H711

MB_DQS_L711

MB_CLK_H011

MB_CLK_L011

MB_CLK_H111

MB_CLK_L111

MB_RESET_L11

MB_EVENT_L11

MB0_CKE011

MB0_CKE111

MB0_ODT011

MB0_ODT111

MB0_CS_L011

MB0_CS_L111

MB_ADD_1711

MB_RAS_L11

MB_CAS_L11

MB_WE_L11

MB_ALERT_L11

MB_PAROUT11

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ACT_L

MB_BG0

MB_BG1

MB_BANK0

MB_BANK1

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_RESET_L

MB_EVENT_L

MB0_CKE0

MB0_CKE1

MB0_ODT0

MB0_ODT1

MB0_CS_L0

MB0_CS_L1

MB_ADD_17

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_ALERT_L

MB_PAROUT

AC36

AC39

AG38

AD38

AC37

AL38

AR39

AT35

AW29

AM37

AM36

AT38

AT39

AU34

AV34

AU28

AU29

W38

W37

AA39

AA38

AF39

AH36

AF37

AH38

AE37

AG39

AE38

AG36

AH37

AD36

AF36

AD39

AB38

U36

U37

T38

T37

R39

R36

P39

R38

P36

P37

N38

M38

M36

M39

C21

D26

A32

D37

F39

B22

A22

C27

B27

C33

C32

B37

A37

G38

G37

U39

V39

V38

Y37

Y39

K35

K37

N37

L37

L39

L36

CPU1B

MB_ADD[0]

MB_ADD[1]

MB_ADD[2]

MB_ADD[3]

MB_ADD[4]

MB_ADD[5]

MB_ADD[6]

MB_ADD[7]

MB_ADD[8]

MB_ADD[9]

MB_ADD[10]

MB_ADD[11]

MB_ADD[12]

MB_ADD[13]

MB_ACT_L

MB_BG[0]

MB_BG[1]

MB_BANK[0]

MB_BANK[1]

MB_DM[0]

MB_DM[1]

MB_DM[2]

MB_DM[3]

MB_DM[4]

MB_DM[5]

MB_DM[6]

MB_DM[7]

MB_DM[8]

MB_DQS_H[0]

MB_DQS_L[0]

MB_DQS_H1]

MB_DQS_L[1]

MB_DQS_H[2]

MB_DQS_L[2]

MB_DQS_H[3]

MB_DQS_L[3]

MB_DQS_H[4]

MB_DQS_L[4]

MB_DQS_H[5]

MB_DQS_L[5]

MB_DQS_H[6]

MB_DQS_L[6]

MB_DQS_H[7]

MB_DQS_L[7]

MB_DQS_H[8]

MB_DQS_L[8]

MB_CLK_H[0]

MB_CLK_L[0]

MB_CLK_H[1]

MB_CLK_L[1]

MB_CLK_H[2]

MB_CLK_L[2]

MB_CLK_H[3]

MB_CLK_L[3]

MB_RESET_L

MB_EVENT_L

MB0_CKE[0]

MB0_CKE[1]

MB1_CKE[0]

MB1_CKE[1]

MB0_ODT[0]

MB0_ODT[1]

MB1_ODT[0]

MB1_ODT[1]

MB0_CS_L[0]

MB0_CS_L[1]

MB1_CS_L[0]

MB1_CS_L[1]

MB_ADD_17

MB_RAS_L_ADD[16]

MB_CAS_L_ADD[15]

MB_WE_ L_ADD[14]

MB_ALERT_L

MB_PAROUT

PART 2 OF 9

MEMORY-B

AM4

MB_DATA[0]

MB_DATA[1]

MB_DATA[2]

MB_DATA[3]

MB_DATA[4]

MB_DATA[5]

MB_DATA[6]

MB_DATA[7]

MB_DATA[8]

MB_DATA[9]

MB_DATA[10]

MB_DATA[11]

MB_DATA[12]

MB_DATA[13]

MB_DATA[14]

MB_DATA[15]

MB_DATA[16]

MB_DATA[17]

MB_DATA[18]

MB_DATA[19]

MB_DATA[20]

MB_DATA[21]

MB_DATA[22]

MB_DATA[23]

MB_DATA[24]

MB_DATA[25]

MB_DATA[26]

MB_DATA[27]

MB_DATA[28]

MB_DATA[29]

MB_DATA[30]

MB_DATA[31]

MB_DATA[32]

MB_DATA[33]

MB_DATA[34]

MB_DATA[35]

MB_DATA[36]

MB_DATA[37]

MB_DATA[38]

MB_DATA[39]

MB_DATA[40]

MB_DATA[41]

MB_DATA[42]

MB_DATA[43]

MB_DATA[44]

MB_DATA[45]

MB_DATA[46]

MB_DATA[47]

MB_DATA[48]

MB_DATA[49]

MB_DATA[50]

MB_DATA[51]

MB_DATA[52]

MB_DATA[53]

MB_DATA[54]

MB_DATA[55]

MB_DATA[56]

MB_DATA[57]

MB_DATA[58]

MB_DATA[59]

MB_DATA[60]

MB_DATA[61]

MB_DATA[62]

MB_DATA[63]

MB_CHECK[0]

MB_CHECK[1]

MB_CHECK[2]

MB_CHECK[3]

MB_CHECK[4]

MB_CHECK[5]

MB_CHECK[6]

MB_CHECK[7]

MB_ZVDDIO_MEM_S3

MB_ZVSS

ZIF-SOCKET1331

D20

B21

B24

C24

A20

C20

A23

C23

A26

C26

A29

C29

A25

B25

A28

B28

A31

B31

B34

C35

B30

C30

B33

A34

B36

E36

C39

D38

A35

C36

B38

C38

AK39

AL37

AN36

AN39

AK38

AK36

AM39

AN38

AR36

AR37

AU37

AV37

AP37

AP38

AT36

AU38

AW35

AU35

AW32

AU32

AV36

AW36

AW33

AV33

AW30

AV30

AW27

AW26

AV31

AU31

AV28

AV27

F38

F36

H39

J39

E37

E39

H36

H37

Type0 Only

MB_ZVDDIO_MEM_S3

Y36

MB_ZVSS

AJ39

Type2/3 Only

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DATA[63..0] 11

R257 39.2R1%/4R256 39.2R1%/4

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

AM4 DDR4 I/F

AM4 DDR4 I/F

AM4 DDR4 I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-7C58

MS-7C58

MS-7C58

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

10

10

3 55Monday, November 11, 2019FL7

3 55Monday, November 11, 2019

1

3 55Monday, November 11, 2019

10

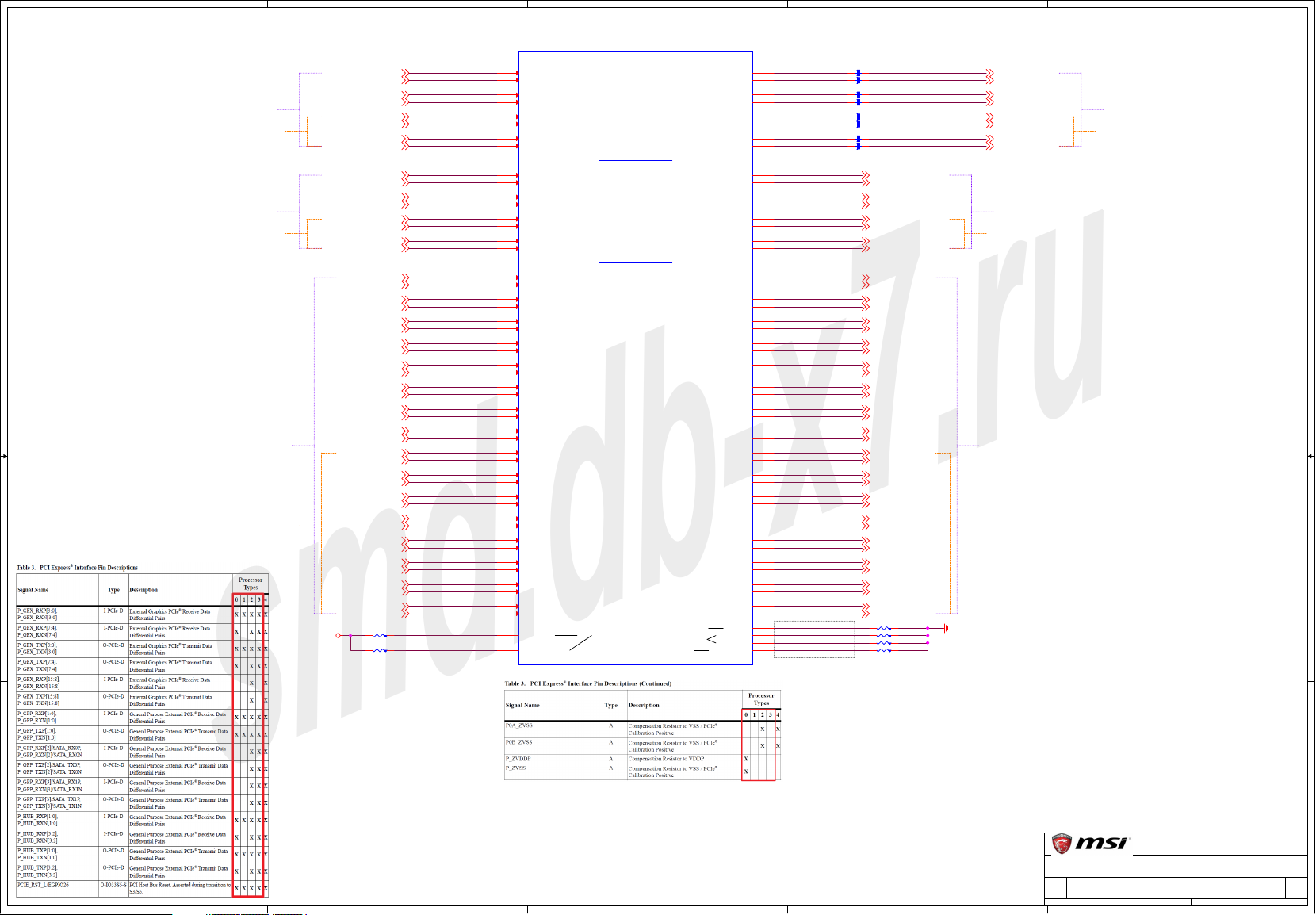

Page 4

5

smd.db-x7.ru

4

3

2

1

CPU1C

APU_RXP014

APU_RXN014

APU_RXP114

CPU_VDDP

APU_RXN114

APU_RXP214

APU_RXN214

APU_RXP314

APU_RXN314

APU_GPP_RXP050

APU_GPP_RXN050

APU_GPP_RXP150

APU_GPP_RXN150

APU_GPP_RXP250

APU_GPP_RXN250

APU_GPP_RXP350

APU_GPP_RXN350

GFX_RXP019

GFX_RXN019

GFX_RXP119

GFX_RXN119

GFX_RXP219

GFX_RXN219

GFX_RXP319

GFX_RXN319

GFX_RXP419

GFX_RXN419

GFX_RXP519

GFX_RXN519

GFX_RXP619

GFX_RXN619

GFX_RXP719

GFX_RXN719

GFX_RXP819

GFX_RXN819

GFX_RXP919

GFX_RXN919

GFX_RXP1019

GFX_RXN1019

GFX_RXP1119

GFX_RXN1119

GFX_RXP1219

GFX_RXN1219

GFX_RXP1319

GFX_RXN1319

GFX_RXP1419

GFX_RXN1419

GFX_RXP1519

GFX_RXN1519

R258 196R1%/4

R304 1K1%/4

D D

No fuction for Type1 No fuction for Type1

From M2_1 To M2_1

No fuction for Type0/1 No fuction for Type0/1

From FCH T

C C

From PCI_E2 To PCI_E2

No fuction for Type0/1/3 No fuction for Type0/1/3

B B

APU_RXP0

APU_RXN0

APU_RXP1

APU_RXN1

APU_RXP2

APU_RXN2

APU_RXP3

APU_RXN3

APU_GPP_RXP0

APU_GPP_RXN0

APU_GPP_RXP1

APU_GPP_RXN1

GFX_RXP0

GFX_RXN0

GFX_RXP1

GFX_RXN1

GFX_RXP2

GFX_RXN2

GFX_RXP3

GFX_RXN3

GFX_RXP4

GFX_RXN4

GFX_RXP5

GFX_RXN5

GFX_RXP6

GFX_RXN6

GFX_RXP7

GFX_RXN7

GFX_RXP8

GFX_RXN8

GFX_RXP9

GFX_RXN9

GFX_RXP10

GFX_RXN10

GFX_RXP11

GFX_RXN11

GFX_RXP12 GFX_TXP12

GFX_RXN12 GFX_TXN12

GFX_RXP13

GFX_RXN13

GFX_RXP14

GFX_RXN14

GFX_RXP15

GFX_RXN15

APU_P_ZVDDP

Within 1500 mils from APU

APU_SATA_ZVDDP

Within 1000 mils from APU

AE8

P_HUB_RXP[0]

AD8

P_HUB_RXN[0]

AB8

P_HUB_RXP[1]

AA8

P_HUB_RXN[1]

Y6

P_HUB_RXP[2]

Y7

P_HUB_RXN[2]

W4

P_HUB_RXP[3]

W5

P_HUB_RXN[3]

AR9

P_GPP_RXP[0]

AT9

P_GPP_RXN[0]

AM9

P_GPP_RXP[1]

AM10

P_GPP_RXN[1]

AR10

P_GPP_RXP[2]/SAT A_RX0P

AP10

P_GPP_RXN[2]/SA TA_RX0N

AP11

P_GPP_RXP[3]/SAT A_RX1P

AN11

P_GPP_RXN[3]/SA TA_RX1N

F6

P_GFX_RXP[0]

F5

P_GFX_RXN[0]

G5

P_GFX_RXP[1]

G4

P_GFX_RXN[1]

H7

P_GFX_RXP[2]

H6

P_GFX_RXN[2]

J6

P_GFX_RXP[3]

J5

P_GFX_RXN[3]

K8

P_GFX_RXP[4]

K7

P_GFX_RXN[4]

K5

P_GFX_RXP[5]

K4

P_GFX_RXN[5]

L7

P_GFX_RXP[6]

L6

P_GFX_RXN[6]

M6

P_GFX_RXP[7]

M5

P_GFX_RXN[7]

N8

P_GFX_RXP[8]

N7

P_GFX_RXN[8]

N5

P_GFX_RXP[9]

N4

P_GFX_RXN[9]

P7

P_GFX_RXP[10]

P6

P_GFX_RXN[10]

R6

P_GFX_RXP[11]

R5

P_GFX_RXN[11]

T8

P_GFX_RXP[12]

T7

P_GFX_RXN[12]

T4

P_GFX_RXP[13]

T5

P_GFX_RXN[13]

U7

P_GFX_RXP[14]

U6

P_GFX_RXN[14]

V6

P_GFX_RXP[15]

V5

P_GFX_RXN[15]

W8

P_ZVDDP

AV7

SATA_ZVDDP

Type0 Only

PCIE

SATA

Express

AM4

Type0 Only

PART 3 OF 9

P_HUB_TXP[0]

P_HUB_TXN[0]

P_HUB_TXP[1]

P_HUB_TXN[1]

P_HUB_TXP[2]

P_HUB_TXN[2]

P_HUB_TXP[3]

P_HUB_TXN[3]

P_GPP_TXP[0]

P_GPP_TXN[0]

P_GPP_TXP[1]

P_GPP_TXN[1]

P_GPP_TXP[2]/SATA _TX0P

P_GPP_TXN[2]/SAT A_TX0N

P_GPP_TXP[3]/SATA _TX1P

P_GPP_TXN[3]/SAT A_TX1N

P_GFX_TXP[0]

P_GFX_TXN[0]

P_GFX_TXP[1]

P_GFX_TXN[1]

P_GFX_TXP[2]

P_GFX_TXN[2]

P_GFX_TXP[3]

P_GFX_TXN[3]

P_GFX_TXP[4]

P_GFX_TXN[4]

P_GFX_TXP[5]

P_GFX_TXN[5]

P_GFX_TXP[6]

P_GFX_TXN[6]

P_GFX_TXP[7]

P_GFX_TXN[7]

P_GFX_TXP[8]

P_GFX_TXN[8]

P_GFX_TXP[9]

P_GFX_TXN[9]

P_GFX_TXP[10]

P_GFX_TXN[10]

P_GFX_TXP[11]

P_GFX_TXN[11]

P_GFX_TXP[12]

P_GFX_TXN[12]

P_GFX_TXP[13]

P_GFX_TXN[13]

P_GFX_TXP[14]

P_GFX_TXN[14]

P_GFX_TXP[15]

P_GFX_TXN[15]

Type0 Only

Type2 Only

P_ZVSS

P0A_ZVSS

P0B_ZVSS

SATA_ZVSS

ZIF-SOCKET1331

AE4

APUTXP0

AE5

APUTXN0

AA5

APUTXP1

AB5

APUTXN1

AC6

APUTXP2

AC7

APUTXN2

AD5

APUTXP3

AD6

APUTXN3

APU_GPP_TXP0

AT12

APU_GPP_TXN0

AR12

APU_GPP_TXP1

AP13

APU_GPP_TXN1

AR13

AL13

AM13

AN14

AP14

GFX_TXP0

D1

GFX_TXN0

E1

GFX_TXP1

E3

GFX_TXN1

F3

GFX_TXP2

F2

GFX_TXN2

G2

GFX_TXP3

G1

GFX_TXN3

H1

GFX_TXP4

H3

GFX_TXN4

J3

GFX_TXP5

J2

GFX_TXN5

K2

GFX_TXP6

K1

GFX_TXN6

L1

GFX_TXP7

L3

GFX_TXN7

M3

GFX_TXP8

M2

GFX_TXN8

N2

GFX_TXP9

N1

GFX_TXN9

P1

GFX_TXP10

P3

GFX_TXN10

R3

GFX_TXP11

R2

GFX_TXN11

T2

T1

U1

GFX_TXP13

U3

GFX_TXN13

V3

GFX_TXP14

V2

GFX_TXN14

W2

GFX_TXP15

W1

GFX_TXN15

Y1

APU_P_ZVSS

W7

APU_P0A_ZVSS

V8

APU_P0B_ZVSS

AT8

APU_SATA_ZVSS

AV6

Within 1500 mils from APU

C906 C0.22u16X5/4

C905 C0.22u16X5/4

C912 C0.22u16X5/4

C911 C0.22u16X5/4

C909 C0.22u16X5/4

C910 C0.22u16X5/4

C907 C0.22u16X5/4

C908 C0.22u16X5/4

APU_GPP_TXP0 50

APU_GPP_TXN0 50

APU_GPP_TXP1 50

APU_GPP_TXN1 50

APU_GPP_TXP2 50

APU_GPP_TXN2 50

APU_GPP_TXP3 50

APU_GPP_TXN3 50

GFX_TXP0 19

GFX_TXN0 19

GFX_TXP1 19

GFX_TXN1 19

GFX_TXP2 19

GFX_TXN2 19

GFX_TXP3 19

GFX_TXN3 19

GFX_TXP4 19

GFX_TXN4 19

GFX_TXP5 19

GFX_TXN5 19

GFX_TXP6 19

GFX_TXN6 19

GFX_TXP7 19

GFX_TXN7 19

GFX_TXP8 19

GFX_TXN8 19

GFX_TXP9 19

GFX_TXN9 19

GFX_TXP10 19

GFX_TXN10 19

GFX_TXP11 19

GFX_TXN11 19

GFX_TXP12 19

GFX_TXN12 19

GFX_TXP13 19

GFX_TXN13 19

GFX_TXP14 19

GFX_TXN14 19

GFX_TXP15 19

GFX_TXN15 19

R222 196R1%/4

R253 X_200R/4

R325 X_200R/4

R309 1K1%/4

APU_TXP0

APU_TXN0

APU_TXP1

APU_TXN1

APU_TXP2

APU_TXN2

APU_TXP3

APU_TXN3

APU_TXP0 14

APU_TXN0 14

APU_TXP1 14

APU_TXN1 14

APU_TXP2 14

APU_TXN2 14

APU_TXP3 14

APU_TXN3 14

o FCH

A A

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

AM4 PCIE/SATAE

AM4 PCIE/SATAE

AM4 PCIE/SATAE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-7C58

MS-7C58

MS-7C58

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

10

10

4 55Monday, November 11, 2019

4 55Monday, November 11, 2019

1

4 55Monday, November 11, 2019

10

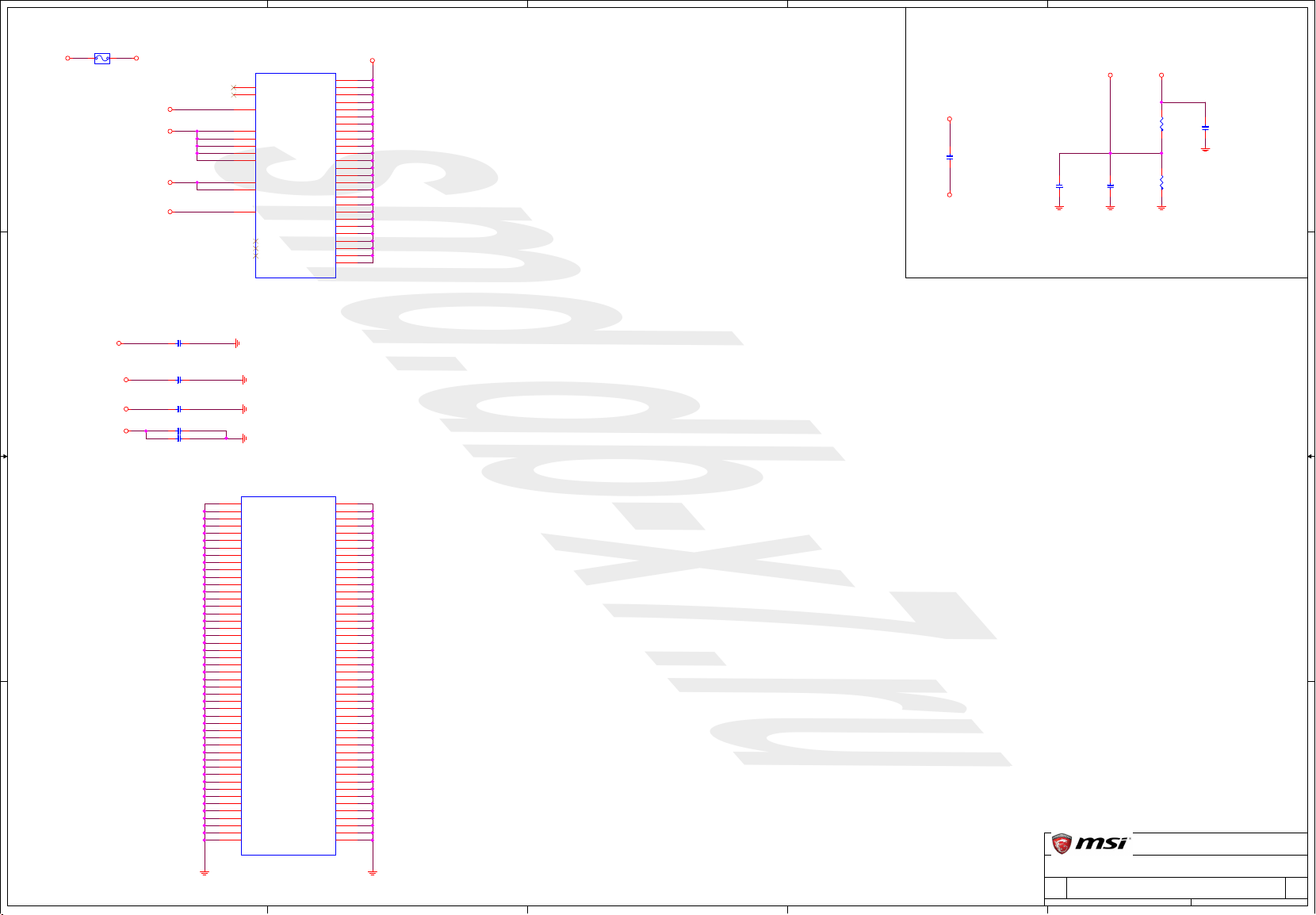

Page 5

5

smd.db-x7.ru

D D

R313 1K/4

R311 1K/4

R316 1K/4

R312 1K/4

AZ_BITCLK_R

AZ_RST_R

AZ_SYNC_R

AZ_SDOUT_R

4

3

2

1

R345 X_10K/4

R329 10K/4

R308 10K/4

C C

B B

PWR_1P8_SW

R188 1K/4

R187 1K/4

R186 1K/4

R185 1K/4

R176 1K/4

3VSB

R355 X_1K/4

R346 X_2.2K/4

R323 X_2.2K/4

R344 15K1%/4

R353 15K1%/4

R324 15K1%/4

R183 X_1K/4

R182 X_1K/4

R206 X_1K/4

R205 X_1K/4

R156 1K/4

R155 1K/4

AZ_SDIN0 AZ_BITCLK_R

AZ_SDIN1

AZ_SDIN2

APU_TCK

APU_TMS

APU_TDI

APU_TRST#

APU_DBREQ#

APU_TEST1

APU_TEST0

APU_TEST0

APU_TEST1

APU_TEST2

APU_TEST11

APU_TEST14

APU_TEST17

APU_TEST16

APU_TEST18

APU_TEST19

For Debug1

For Debug2

EMI

TP11

TP5

TP1

TP2

TP10

TP14

TP4

TP12

TP13

TP3

TP16

TP9

R321 33R/4

R303 33R/4

R319 33R/4

R318 33R/4

AZ_BITCLK26

AZ_SDIN026

AZ_RST#26

AZ_SYNC26

AZ_SDOUT26

AZ_BITCLK_R

AZ_SDIN0

AZ_SDIN1

AZ_SDIN2

AZ_RST_R

AZ_SYNC_R

AZ_SDOUT_R

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

APU_TEST0

APU_TEST1

APU_TEST2

APU_TEST4

APU_TEST5APU_TEST2

APU_TEST11

APU_TEST14

APU_TEST15

APU_TEST16

APU_TEST17

APU_TEST18

APU_TEST19

APU_TEST46

APU_TEST47

APU_TEST28_H

APU_TEST28_L

APU_TEST31

APU_TEST40

APU_TEST41

C303

X_C0.1u16X/4

AW3

AM6

AM7

M22

AA30

W30

AV3

AU5

AV4

AU1

AU2

AU4

A14

C14

C15

B15

B13

E13

D14

AT3

D13

AB4

A13

C12

B12

C11

D11

G16

H16

AL4

P28

A16

L23

E6

E7

CPU1D

AZ_BITCLK

AZ_SDIN0

AZ_SDIN1

AZ_SDIN2

AZ_RST_L

AZ_SYNC

AZ_SDOUT

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

TEST0

TEST1/TMS

TEST2

TEST4

TEST5

TEST6

TEST10

TEST11

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST46[13]

TEST47

TEST28_H

TEST28_L

TEST31

TEST40

TEST41

AUDIO

TEST

AM4

PART 4 OF 9

DP0_TXP[0]

DP0_TXN[0]

DP0_TXP[1]

DP0_TXN[1]

DP0_TXP[2]

DP0_TXN[2]

DP0_TXP[3]

DP0_TXN[3]

DP0_AUXP

DP0_AUXN

DISPLAY-0

DP0_HPD

DP1_TXP[0]

DP1_TXN[0]

DP1_TXP[1]

DP1_TXN[1]

DP1_TXP[2]

DP1_TXN[2]

DP1_TXP[3]

DP1_TXN[3]

DP1_AUXP

DP1_AUXN

DISPLAY-1

DP1_HPD

DP2_TXP[0]

DP2_TXN[0]

DP2_TXP[1]

DP2_TXN[1]

DP2_TXP[2]

DP2_TXN[2]

DP2_TXP[3]

DP2_TXN[3]

DP2_AUXP

DP2_AUXN

DISPLAY-2

DP2_HPD

DP_ZVSS

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP_STEREOSYNC

ZIF-SOCKET1331

D2

DP0_TX2P_APU 49

C2

DP0_TX2N_APU 49

C3

DP0_TX1P_APU 49

B3

DP0_TX1N_APU 49

B4

DP0_TX0P_APU 49

A4

DP0_TX0N_APU 49

C5

DP0_CLKP_APU 49

C6

DP0_CLKN_APU 49

G10

DP0_AUXP 49

H10

DP0_AUXN 49

H9

DP0_HDMI_HPD 49

D4

DP1_TX2P_APU 32

D5

DP1_TX2N_APU 32

D7

DP1_TX1P_APU 32

D8

DP1_TX1N_APU 32

F8

DP1_TX0P_APU 32

G8

DP1_TX0N_APU 32

E9

DP1_CLKP_APU 32

F9

DP1_CLKN_APU 32

F11

DP1_AUXP 32

G11

DP1_AUXN 32

D10

DP1_DP_HPD 32

B6

DP2_TX0P_APU 33

B7

DP2_TX0N_APU 33

A7

DP2_TX1P_APU 33

A8

DP2_TX1N_APU 33

C8

C9

B9

No fuction for Type1

B10

A10

DP2_AUXP 33

A11

DP2_AUXN 33

E10

DP2_DP_HPD 33

DP_ZVSS

F12

E12

G13

H13

H12

K14

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP_STEREOSYNC

R170 2K1%/4

R159 150R1%/4

R147 1K/4

R148 X_1K/4

K14 PIN: HDMI SPEC

For HDMI

For DVI

For DP to VGA

TP8

TP7

TP6

CPU_1P8

Pull-up ENBLE

Type0 Only

For Debug2

2019/4/10

DDI rounting passed to follo w up PM spec

Not support Type2

DP1_AUXP

ATX_5VSB CPU_1P8_S5

R2408

A A

TYPE1_CPU_SEL:

1:1.8V_S5(Type2, 3)

0:1.8V(Type0)

TYPE1_CPU_SEL6,28,39,40,44

2019/7/19 (1.1 o nly)

R2408, Q157, Q160, Q161 are added by Ryan's comment(2019/6/1 3)

5

47K/4

CPU_1P8

D

G

Q157

S

N-2N7002ET1G

S

Q160

G

D

N-PM514BA

PN514 Vgs

=0.45V~1.2V

G

Q161

P-PA002FMG

D S

PWR_1P8_SW

4

3

DP1_AUXN

2

R173 2.2K/4

R175 2.2K/4

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCC3

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

AM4 Display/Audio

AM4 Display/Audio

AM4 Display/Audio

MS-7C58

MS-7C58

MS-7C58

1

5 55Monday, November 11, 2019

5 55Monday, November 11, 2019

5 55Monday, November 11, 2019

10

10

10

Page 6

5

smd.db-x7.ru

ATX_5VSB 3VSB

R455

47K/4

TYPE1_CPU_SEL:

1

:NC (Type2,3)

0:3.3V(Type0)

D D

TYPE1_CPU_SEL

PWR_SW

C C

B B

CPU_1P8_S5

G

Q62

D

G

S

N-2N7002ET1G

PWR_SW

C445

C0.1u16X/4

2019/5/8

Q27, R146 are deleted by Rya n's comment

VCC3

Ib=(3.3-0.95)/4. 7k=0.5mA

Ic=(3.3-0.2)/4.7 k=0.66mA

R179 1K/4

R141 1K/4

R152 1K/4

CPU_1P8

R144 1K/4

R145 1K/4

R189 300R/4

R172 300R/4

2019/4/17

3VSB

R393 is unstu ffed by Ryan's comment

R386 10K/4

R393 X_10K/4

R363 10K/4

R397 10K/4

R396 10K/4

C358 X_C100p50N/4

R518 10K/4

CPU_1P8_S5

R377 22K/4

C349

X_10u6.3X/6

R85 4.7K/4

PROCHOT#22,41

G

DS

Q85

X_P-PA002FMG

Follow CRB

PN514 Vgs

=0.5V~1.0V

D

Q90

N-PM514BA

S

PWR_SB_SW

APU_ALERT#

APU_PROCHOT#

APU_THERMTRIP#

APU_SIC

APU_SID

PWROK

RESET_L

PWRBTN#

APU_AM4R1

BLINK

WAKE_L

PCIE_RST

S5_MUX_CTRL

RSMRST#

C346

1u6.3X/4

2

5

Q18

NN-CMKT3904

ATX_5VSB

TYPE1_CPU_SEL:

1:3.3V(Type2,3)

0:1.8V(Type0)

TYPE1_CPU_SEL

APU_PROCHOT#PROCHOT#_LS

6

1

PROCHOT#_LS

3

4

VCC5 3VSB

R496

47K/4

D

G

S

Ib=(3.3-0.95)/4. 7k=0.5mA

Ic=(3.3-0.2)/1k= 3.1mA

Ic=(1.8-0.2)/1k= 1.6mA

R495

X_47K/4

CPU_1P8

Q63

N-2N7002ET1G

4

VCC3

G

S

Q91

G

D

N-PM514BA

PN514 Vgs

=

0.45V~1.2V

Q94

P-PA002FMG

D S

APU_PWROK41

ALL_PWR_PW RGD40

SLP_S5#22,34,36,37,48

S5_MUX_CTRL44

PWRBTN#22,48

SPKR46

RSMRST#22,40

SYSREST#7,35,40,46

PCIE_REST#19

KBRST#22

APU_WAKE#16,19,21,50

APU_LPC_PME#16,20,21,22

APU_SIC22

APU_SID22

PWR_SW

APU_SVC41

APU_SVD41

APU_SVT41

APU_AM4R134,37,38,39,40

RTCCLK7

APU_SVC

R198 X_R/2

APU_SVD

R197 X_R/2

APU_SVT

R196 X_R/2

APU_PWROK

R190 X_R/2

ALL_PWR_PW RGD

KBRST#

D14 X_S-LRB520S -40T1G

3.3V

APU_PROCHOT#

APU_THERMTRIP#

APU_SLP_S3#

SLP_S5#

APU_S0A3_GPIO

S5_MUX_CTRL

PWRBTN#

BLINK

SPKR

RSMRST#

SYSREST#

PCIE_REST#

KBRST#

APU_SIC

APU_SID

APU_ALERT#

APU_AM4R1

CORETYPE0

CORETYPE1

ITE6516_URDBG33

RTCCLK

SLP_S3#22,34,35,37,38,40

R398 33R/4

R384 X_R/2

R399 X_R/2

ITE6516_URDBG

APU_32K_X1

APU_32K_X2

3

C431 C0.1u16X/4

53

U44

VCC

1

Y

GND

NC7SZ08M5X

R483 X_0R/4

A

2

B

4

SLP_S3# APU_SLP_S3#

Within 500mils

CPU1E

D17

SVC

SVD

SVT

PWROK

RESET_L

PCIE_RST

KBRST_L

WAKE_L

SVC

C17

SVD

A17

SVT

E16

PWROK

AM3

PWR_G OOD

B16

RESET_L

1.8V

H15

PROCHOT_L

A19

THERMTRIP_L

AT2

SLP_S3_L

AP2

SLP_S5_L

AR3

S0A3_GPIO/AGPIO10/SG PIO0_CLK

AP4

S5_MUX_CTRL/EGPIO4 2

AN5

PWR_BT N_L/AGPIO0

AT5

BLINK/AGPIO11

AW23

SPKR/AGPIO91

AP5

RSMRST_L

AM4

SYS_RESET_L/AGPIO1

AL7

PCIE_RST_L/EGPIO26

AN24

ESPI_RESET_L/KBRST_L

AL5

WAKE_L/ AGPIO2

AL2

LPC_PME_L/AGPIO22

B18

SIC

C18

SID

D16

ALERT_L

AL8

AM4R1

AM24

CORETYPE[0]

AN9

CORETYPE[1]

AN23

FANIN0/AGPIO84

AP23

FANOUT0/AGPIO85

AP8

RTCCLK

AW5

X32K_X1

AW6

X32K_X2

APU_SLP_S3#

APU_S0A3_GPIO

MISCACPI

FANSVI

RTC

R337 100K/4

R301 2.2K/4

3VSB

2018/5/10

R287, R365 ar e deleted by Ry an's comment

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO11 4

SCL1/I2C3_SCL/AGPIO19

SDA1/I2C3_SDA/AGPIO20

SMBus

AGPIO9/SGPIO0_DATAO UT

AGPIO23/SGPIO0_LOAD

AGPIO40/SGPIO0_DATAIN

GENINT1_L/AGPIO89

GENINT2_L/AGPIO90

SATA_ACT_L/AGPIO130

GPIO

CLK_REQ0_L/SATA_IS0_L/S ATA_ZP0_L/AGPIO92

CLK_REQ3_L/SATA_IS1_L/S ATA_ZP1_L/EGPIO131

OC

SENSE

AM4

PART 5 OF 9

CLK_REQ1_L/AGPIO115

CLK_REQ2_L/AGPIO116

CLK_REQG_L/OSCIN/ EGPIO132

USB_OC0_L/AGPIO16

USB_OC1_L/TDI/AGPIO1 7

USB_OC2_L/TCK/AG PIO18

USB_OC3_L/TDO/AG PIO24

VDDCR_CPU_SENSE

VDDCR_SOC_SENSE

VDDIO_MEM_S3_SENSE

ZIF-SOCKET1331

2

AGPIO3

AGPIO4

AGPIO5/DEVSLP0

AGPIO6

AGPIO8

AGPIO86

EGPIO70

EGPIO95

EGPIO96

EGPIO97

EGPIO98

EGPIO99

EGPIO100

VSS_SENSE_A

VDDP_SENSE

VSS__SENSE_B

VCC3

R364 8.2K/4

R354 X_10K/4

AMD Hardware Validated Boot

(HVB)

0:Enable

1 or NC:Disable

AU25

SCL0

AV25

SDA0

AK3

SCL1

AK2

SDA1

AT6

AGPIO3

AR6

AGPIO5_DEVSLP0

AP22

CPUFAN1_MODE

AN8

SYSFAN1_MODE

AP7

AN2

AN3

iGPU_LED

AR4

AW17

AGPIO86

GENINT1_L

AV22

AU23

SATA_LED#

AM22

AT18

AW11

AV12

GPIO97_CPU

AW12

GPIO98_DRAM

AU13

GPIO99_VGA

AV13

GPIO100_DEVICE

AT14

CLK_REQ0

AT23

CLK_REQ1

AV24

CLK_REQ2

AT24

CLK_REQ3

AL23

CLK_REQG

AR22

APU_OC0#

AL1

AM1

AR1

AP1

VDDCR_CPU_SENSE +

F14

VDDCR_SOC_SENSE+

E15

VDDIO_MEM_S3_SENSE+

G14

VSS_SENSE_A

F15

CPU_VDDP_SENSE

AL22

VSS_SENSE_B

AM23

GENINT1_L

R416 100R1%/4

R413 100R1%/4

R281 X_0R/4

R280 X_0R/4

TP22

SATA_LED# 46

GPIO97_CPU 47

GPIO98_DRAM 47

GPIO99_VGA 47

GPIO100_DEVICE 47

CLK_REQ3 50

APU_OC0# 28,29

CP3 X_COPPER

CP5 X_COPPER

1

SCL0

SDA0

SCL1

SDA1

AGPIO5_DEVSLP0

R424 2.2K/4

R415 2.2K/4

R282 2.2K/4

R279 2.2K/4

R417 10K/4

by check list

SCLK0 10,41,44,48

SDATA0 10,41,44,48

SCLK_PCIE 19,21

SDATA_PCIE 19,21

AGPIO3 7

M2_DET 50

TP23

TP24

iGPU_LED 47APU_SLP_S3#48

For K TYPE FAN

PCIE X16/X8 LED Control

GPIO97~100 for Debug LED

VCC3

R375 560R/4

3VSB

2019/4/17

R292, R302, R 299 are deleted

by Ryan's com ment

TP21

R285 200K/4

VDDCR_CPU_SENSE + 41

VDDCR_SOC_SENSE+ 41

VDDIO_MEM_S3_SENSE+ 37

VDDCR_CPU_SENSE - 41

VDDCR_SOC_SENSE- 41

CPU_VDDP_SENSE 39

SATA_LED#

VCC3

3VSB

VCC3

APU_OC0#

Layout:Place x'tal within 1.5 inch of APU

APU_32K_X2

2019/7/2

C295, C296 ar e changed from 15pF to 12pF by RTC fail from DQ A

Y2

APU_32K_X1

A A

PLACE THESE COMPONENTS CLOSE TO

U600, AND USE GROUND GUARD FOR

32K_X1 AND 32K_X2

12

32.768KHZ12.5p

R317 20M/6

C296

C12p50N

Keep on 0603 typ e

C295

C12p50N

5

AM4 CPU TYPE Circuit

Change by CRB rev. E

3VSB

CPU_1P8_S5

R402

1K/4

R405

X_1K/4

CORETYPE1

R401

10K/4

ATX_5VSB

B

ATX_5VSB

R383

4

47K/4

D

Q69

G

N-2N7002ET1G

S

R400

47K/4

TYPE1_SEL

CE

Q78

N-SST3904

Ib=(3.3-0.95)/11 k=0.214mA

Ic=(5-0.2)/47k=0 .102mA

CPU

BR

SR

RV/ZP

TYPE1_CPU_SEL 5,28,39,40,44

TYPE1_CPU_SEL

0:BR/NA

1:ST/RV/ZP

TYPE

0

2

3

CORETYPE

0 0

0NA

1

1 1

TYPE1_CPU_SEL

R443

1K/4

R444

4.7K/4

ATX_5VSB

0:BR/NA

1:ST/RV/ZP

R474

47K/4

TYPE0_CPU_SEL

CE

B

Q87

N-SST3904

Ib=(1.8-0.95)/5. 7k=0.149mA

Ic=(5-0.2)/47k=0 .102mA

TYPE0_CPU_SEL 39,40

2

R342 10K/4

R412 10K/4

R336 10K/4

R335 10K/4

R2403 10K/4

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

AM4 SVI/ACPI/GPIO

AM4 SVI/ACPI/GPIO

AM4 SVI/ACPI/GPIO

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-7C58

MS-7C58

MS-7C58

Date: Sheet of

Date: Sheet of

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

CLK_REQ0

CLK_REQ1

CLK_REQ2

CLK_REQ3

CLK_REQG

6 55Monday, November 11, 2019

6 55Monday, November 11, 2019

1

6 55Monday, November 11, 2019

10

10

10

01

1

CPU_1P8_S5

0

CORETYPE0

CORETYPE0

0:BR/SR

1:RV/ZP

3

Page 7

5

smd.db-x7.ru

4

3

2

1

EMI

LPCCLK1

C313 X_C0.1u16X/4

20

19/5/2

R2387 is adde d by Ryan's com ment

TPM_LPCCLK046

VCC3

D D

R2387

10K/4

LPC_LDRQ0#

VCC3

R2409

2019/8/15

10K/4

R2409 is added b y 7B86

LPC_SERIRQ

EMI

SPI_CLK

C314 X_C0.1u16X/4

SIO_LPCCLK122

LPC_AD022,46

LPC_AD122,46

LPC_AD222,46

LPC_AD322,46

LPC_LFRAME#22,46

LPC_LDRQ0#22

LPC_SERIRQ22,46

LPC_RST#22,46

R330 22R/4

R352 0R/4

R314 2K1%/4

R28 33R/4

R338 10R1%/4

To PCI_E2

C C

To FCH

To M2_1

B B

LPCCLK0

LPCCLK1

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_LFRAME#

LPC_LDRQ0#

LPC_SERIRQ

LPC_CLKRUN

LPC_RST_L

C59 X_C150p50N/4

SPI_CLK_RSPI_CLK

SPI_CS#

SPI_DATAIN

SPI_DATAOUT

SPI_WP#_R

SPI_HOLD#_R

PE1_GFX_CLKP19

PE1_GFX_CLKN19

APU_CLKP16

APU_CLKN16

CLK_M2_DP50

CLK_M2_DN50

APU_48M_X1

APU_48M_X2

SPI ROM(1.8V)

Layout:Place x'tal within 1.5 inch of APU

R261 1M/6

Y1

3 4

GND

12

GND

A A

48MHZ12p_S-RH

C243

10p50N/4

PLACE THESE COMPONENTS CLOSE TO U600, AND USE

GROUND GUARD FOR48M_X1 AND 48M_X2

R262

49.9R1%/4

C251

10p50N/4

5

APU_48M_X2

APU_48M_X1

2019/5/8

R492, R525 ar e changed to 0o hm to short copp er

by cost reduc tion.

SPI_CS#

SPI_WP#_R

SPI CS# < 20pF

D0G-0402510-SI0

CPU1F

AU20

LPCCLK0/EGPIO74

AU19

LPCCLK1/EGPIO75

AW20

LAD0/EGPIO104

AV21

LAD1/EGPIO105

AT21

LAD2/EGPIO106

AT20

LAD3/EGPIO107

AW18

LFRAME_L/EGPIO109

AT15

ESPI_ALERT_L/LDRQ0_L/ EGPIO108

AW21

SERIRQ/AGPIO87

AV19

LPC_CLKRUN_L/AGPIO 88

AV18

LPC_PD_L/AGPIO21

AU22

LPC_RST_L

AW14

SPI_CLK/ESPI_CLK/EGPIO1 17

AT17

SPI_CS1_L/EGPIO118

AW15

SPI_CS2_L/ESPI_CS_L/EGP IO119

AU14

SPI_DI/ESPI_DAT1/EGPIO120

AU16

SPI_DO/ESPI_DAT0/EGP IO121

AV16

SPI_WP_L/E SPI_DAT2/EGPIO122

AV15

SPI_HOLD_L/ESPI_DAT3/E GPIO133

AU17

SPI_TPM_CS_L/AGPIO76

AF6

GFX_CLKP

AF7

GFX_CLKN

AG5

GPP_CLK0P

AG6

GPP_CLK0N

AH4

GPP_CLK1P

AH5

GPP_CLK1N

AH7

GPP_CLK2P

AH8

GPP_CLK2N

AJ6

GPP_CLK3P

AJ7

GPP_CLK3N

AJ1

X48M_X1

AH1

X48M_X2

R517 X_R/2

R492 X_R/2

R504 X_R/2

P.S Close to JSP I1

CS#

DATAIN

SPI_WP#

D29

12

12

X_ESD-SFI0402-050E100NP

4

LPC/SPI/USB/CLOCK

48M_OSC

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB2.0

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

USB_SS_1RXP

USB_SS_1RXN

USB_SS_2TXP

USB3.0

USB_SS_2TXN

USB_SS_2RXP

USB_SS_2RXN

USB_SS_3TXP

ZIF-SOCKET1331

VCC

HOLD(IO3)

CLK

DI(IO0)

JSPI1

1 2

3 4

5

7 8

9

H2X6[10]M-2PITCH

USB_SS_3TXN

USB_SS_3RXP

USB_SS_3RXN

USB_SS_ZVSS

USB_SS_ZVDDP

USB_ZVSS

USB0_ZVSS

USB1_ZVSS

USB2_ZVSS

USB3_ZVSS

CPU_1P8

8

7

6

5

SPI_DATAOUT

SPI_CLK

6

SPI_HOLD#_R

1211

CLOCKLPC SPI

AM4

PART 6 OF 9

SPI1

1

CS

2

DO(IO1)

3

WP(IO2)

4

GND

W25Q128FWSIQ-RH

M31-2567300-M24

AVL:M31-2525620- W03

CPU_1P8 CPU_1P8

SPI_DATAIN

SPI_CS#

SPI_SW_SEL

SPI_WP#_R

D30

X_ESD-MLVS0402L04

SPI_HOLD#

SPI_CLK

DATAOUT

ALL_PWR_MUX40

APU_48M_OSC

AR7

AU7

AU8

AW8

AW9

AU10

AU11

AV9

AV10

AF3

AF4

Y3

Y4

AB1

AC1

AA2

AA3

AC3

AC4

AD2

AE2

AG2

AG3

AE1

AF1

Only Support Type0

USB_SS_ZVSS

AJ4

USB_SS_ZVDDP

AK8

USB_ZVSS

AT11

USB0_ZVSS

AJ3

USB1_ZVSS

AN6

USB2_ZVSS

AK6

USB3_ZVSS

AK5

Within 1000 mils from APU

Only Support

Type2/3

C449 10u6.3X/6

C452 C0.1u16X/4

R527 X_R/2

R525 X_R/2

TP20

APU_USB0+ 29

APU_USB0- 29

APU_USB1+ 29

APU_USB1- 29

APU_USB2+ 29

APU_USB2- 29

APU_USB3+ 29

APU_USB3- 29

APU_USB_SSTX0+ 29

APU_USB_SSTX0- 29

APU_USB_SSRX0+ 29

APU_USB_SSRX0- 29

APU_USB_SSTX1+ 29

APU_USB_SSTX1- 29

APU_USB_SSRX1+ 29

APU_USB_SSRX1- 29

APU_USB_SSTX2+ 29

APU_USB_SSTX2- 29

APU_USB_SSRX2+ 29

APU_USB_SSRX2- 29

APU_USB_SSTX3+ 29

APU_USB_SSTX3- 29

APU_USB_SSRX3+ 29

APU_USB_SSRX3- 29

R275 1K1%/4 R297

R273 1K1%/4

R305 11.8K1%/4

R268 X_200R1%/4

R274 X_200R1%/4

R270 X_200R1%/4

R272 X_200R1%/4

CPU_1P8

SPI_HOLD#_RSPI_DATAIN

SPI_DATAOUT

2019/4/11

The footprint of SPI1 is

chnaged to SI C8_SST_S2A_COLA Y_T

by 16M/32M co lay by PM spec

R539 X_R/2

3

R526 10K/4

R505 10K/4

R524 10K/4

SPI_SW_SEL

USB1

USB2

USB1

USB2

CPU_VDDP_S5

VDDP_S5

(S5 Wake

Implemented)

or

VDDP

(S5 Wake Not

Implemented)

SPI_HOLD#

SPI_WP#

SPI_CS#

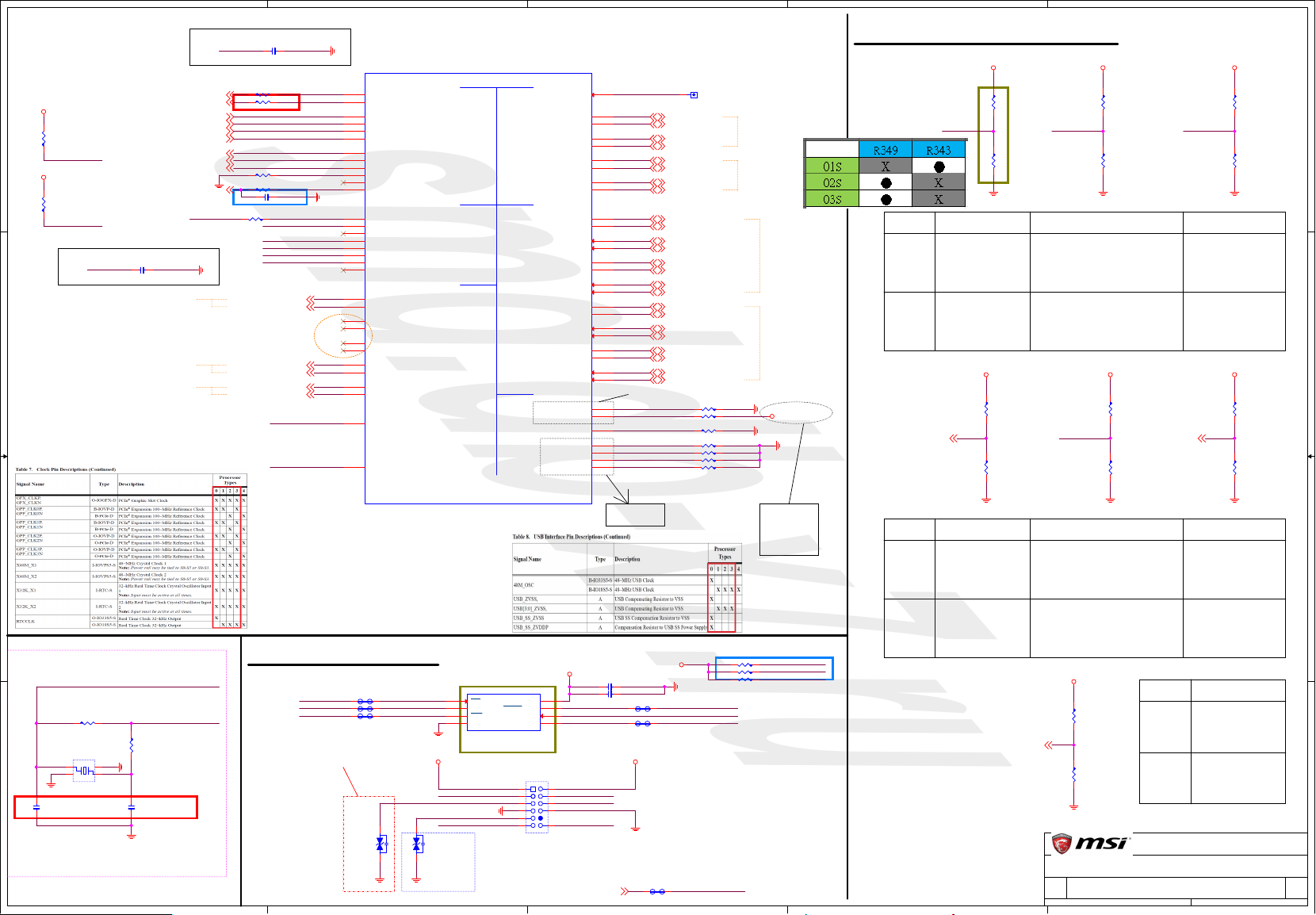

Strapping Options

2019/5/14

R349 & R343 p assed to follow

up PM's spec

PULL

HIGH

PULL

LOW

AGPIO36

PULL

HIGH

PULL

LOW

2

VCC3

R349

10K/4

32M

R343

X_2K1%/4

LPCCLK1

LPCCLK0

16M

LPCCLK0 LPCCLK1

LPC device

Boot Fail Timer

Enabled

LPC device

Boot Fail Timer

Disabled

(Default)

3VSB

R367

10K/4

R366

X_2K1%/4

Configured for

Internal clock g enerator

Configured for

External clock g enerator

?????

AGPIO3

Enhanced

Reset logic

(Default)

Traditional

Reset logic

Use 48Mhz crysta l clock

and generate bot h internal

and external clo cks

Use 100Mhz PCIE clock as

reference clock and generate

internal clocks only

RTCCLK6

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCC3 VCC3

R360

10K/4

LPC_LFRAME#

R340

X_2K1%/4

SIO_LFRAME

SPI ROM

(Default)

R315

10K/4

SPI_CLK_R

R306

X_2K1%/4

SYSREST#6,35,40,46

SPI_CLK

(Default)

PWR_SB_SW

R378

10K/4

R373

X_2K1%/4

AM4 LPC/SPI/USB/CLK/STRAP

AM4 LPC/SPI/USB/CLK/STRAP

AM4 LPC/SPI/USB/CLK/STRAP

MS-7C58

MS-7C58

MS-7C58

PULL

HIGH

PULL

LOW

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

(Default)

LPC ROM

3VSBCPU_1P8

SYSREST#

Normal reset

mode

(Default)

short reset

mode

RTCCLK

RTC Coin Battery

is on board

(Default)

RTC Coin Battery

is not on board

7 55Friday, November 22, 2019

7 55Friday, November 22, 2019

1

7 55Friday, November 22, 2019

R320

10K/4

R307

X_2K1%/4

10K/4

R298

X_2K1%/4

10

10

10

Page 8

5

smd.db-x7.ru

VCORE

D D

C C

B B

A A

W10

W12

AA7

AA10

AA12

AB3

AB6

AB9

AB11

AB13

AC2

AC10

AC12

AD7

AD9

AD11

AD13

AE3

AE6

AE10

AE12

AF11

AF13

AG7

AG10

AG12

AG14

AG16

AG18

AG20

AG22

AG24

AG26

AH3

AH6

AH9

AH11

AH13

AH15

AH17

AH19

AH21

AH23

AH25

AH27

AJ10

AJ12

AJ14

AJ22

AJ24

AK7

AK9

AK11

AK13

AL10

AL12

AL14

AM2

AM8

AN7

AN10

AN13

AP3

AP9

AP12

AR2

AU3

AU6

AU9

AU12

AU15

AV5

AV8

AV11

AV14

M7

N3

N6

P2

R7

T3

T6

T9

U2

U10

V9

V11

W3

W6

Y2

Y9

Y11

Y13

AF2

AF9

AJ2

AL3

AL6

AT4

CPU1H

VDDCR_CPU_0

VDDCR_CPU_1

VDDCR_CPU_2

VDDCR_CPU_3

VDDCR_CPU_4

VDDCR_CPU_5

VDDCR_CPU_6

VDDCR_CPU_7

VDDCR_CPU_8

VDDCR_CPU_9

VDDCR_CPU_10

VDDCR_CPU_11

VDDCR_CPU_12

VDDCR_CPU_13

VDDCR_CPU_14

VDDCR_CPU_15

VDDCR_CPU_16

VDDCR_CPU_17

VDDCR_CPU_18

VDDCR_CPU_19

VDDCR_CPU_20

VDDCR_CPU_21

VDDCR_CPU_22

VDDCR_CPU_23

VDDCR_CPU_24

VDDCR_CPU_25

VDDCR_CPU_26

VDDCR_CPU_27

VDDCR_CPU_28

VDDCR_CPU_29

VDDCR_CPU_30

VDDCR_CPU_31

VDDCR_CPU_32

VDDCR_CPU_33

VDDCR_CPU_34

VDDCR_CPU_35

VDDCR_CPU_36

VDDCR_CPU_37

VDDCR_CPU_38

VDDCR_CPU_39

VDDCR_CPU_40

VDDCR_CPU_41

VDDCR_CPU_42

VDDCR_CPU_43

VDDCR_CPU_44

VDDCR_CPU_45

VDDCR_CPU_46

VDDCR_CPU_47

VDDCR_CPU_48

VDDCR_CPU_49

VDDCR_CPU_50

VDDCR_CPU_51

VDDCR_CPU_52

VDDCR_CPU_53

VDDCR_CPU_54

VDDCR_CPU_55

VDDCR_CPU_56

VDDCR_CPU_57

VDDCR_CPU_58

VDDCR_CPU_59

VDDCR_CPU_60

VDDCR_CPU_61

VDDCR_CPU_62

VDDCR_CPU_63

VDDCR_CPU_64

VDDCR_CPU_65

VDDCR_CPU_66

VDDCR_CPU_67

VDDCR_CPU_68

VDDCR_CPU_69

VDDCR_CPU_70

VDDCR_CPU_71

VDDCR_CPU_72

VDDCR_CPU_73

VDDCR_CPU_74

VDDCR_CPU_75

VDDCR_CPU_76

VDDCR_CPU_77

VDDCR_CPU_78

VDDCR_CPU_79

VDDCR_CPU_80

VDDCR_CPU_81

VDDCR_CPU_82

VDDCR_CPU_83

VDDCR_CPU_84

VDDCR_CPU_85

VDDCR_CPU_86

VDDCR_CPU_87

VDDCR_CPU_88

VDDCR_CPU_89

VDDCR_CPU_90

VDDCR_CPU_91

VDDCR_CPU_92

VDDCR_CPU_93

VDDCR_CPU_94

VDDCR_CPU_95

VDDCR_CPU_96

VDDCR_CPU_97

VDDCR_CPU_98

POWER

AM4

PART 8 OF 9

5

VDDCR_SOC_0

VDDCR_SOC_1

VDDCR_SOC_2

VDDCR_SOC_3

VDDCR_SOC_4

VDDCR_SOC_5

VDDCR_SOC_6

VDDCR_SOC_7

VDDCR_SOC_8

VDDCR_SOC_9

VDDCR_SOC_10

VDDCR_SOC_11

VDDCR_SOC_12

VDDCR_SOC_13

VDDCR_SOC_14

VDDCR_SOC_15

VDDCR_SOC_16

VDDCR_SOC_17

VDDCR_SOC_18

VDDCR_SOC_19

VDDCR_SOC_20

VDDCR_SOC_21

VDDCR_SOC_22

VDDCR_SOC_23

VDDCR_SOC_24

VDDCR_SOC_25

VDDCR_SOC_26

VDDCR_SOC_27

VDDCR_SOC_28

VDDCR_SOC_29

VDDCR_SOC_30

VDDCR_SOC_31

VDDCR_SOC_32

VDDCR_SOC_33

VDDCR_SOC_34

VDDCR_SOC_35

VDDCR_SOC_36

VDDCR_SOC_37

VDDCR_SOC_38

VDDCR_SOC_39

VDDCR_SOC_40

VDDCR_SOC_41

VDDCR_SOC_42

VDDCR_SOC_43

VDDCR_SOC_44

VDDCR_SOC_45

VDDCR_SOC_46

VDDCR_SOC_47

VDDCR_SOC_48

VDDCR_SOC_49

VDDCR_SOC_50

VDDCR_SOC_51

VDDCR_SOC_52

VDDCR_SOC_53

VDDCR_SOC_54

VDDCR_SOC_55

VDDCR_SOC_56

VDDCR_SOC_57

VDDCR_SOC_58

VDDCR_SOC_59

VDDCR_SOC_60

VDDCR_SOC_61

VDDCR_SOC_62

VDDCR_SOC_63

VDDCR_SOC_64

VDDCR_SOC_65

VDDCR_SOC_66

VDDCR_SOC_67

VDDCR_SOC_68

VDDCR_SOC_69

VDDCR_SOC_70

VDDCR_SOC_71

VDDCR_SOC_72

VDDCR_SOC_S5_0

VDDCR_SOC_S5_1

ZIF-SOCKET1331

B5

B8

B11

B14

B17

B20

C4

C7

C10

C13

C16

C19

D3

E2

F7

F10

F13

F16

G3

G6

G9

G12

G15

G18

H2

J7

J10

J12

J14

J16

K3

K6

K9

K11

K13

K15

L2

L10

L12

L14

L16

L18

L20

L22

L24

L26

M9

M11

M13

M15

M17

M19

M21

M23

M25

N10

N12

N14

N16

N18

N20

N22

N24

N26

P9

P11

P13

R10

R12

T11

T13

U12

V13

AJ18

AK18

VCCP_NB

VCCP_NB_S5

0.9A

4

3

VDDIO_AUDIO Circuit

2019/4/11

R537, C397, C4 59, U49, R529, C456, C464, R536 , R535, C453 are deleted by Ryan 's comment

1.5V

0.25A

TOP CAVITY

CPU1G

K36

VDDIO_MEM_S3_0

K39

VDDIO_MEM_S3_1

L32

VDDIO_MEM_S3_2

L35

VDDIO_MEM_S3_3

L38

VDDIO_MEM_S3_4

M29

VDDIO_MEM_S3_5

M31

VDDIO_MEM_S3_6

M34

VDDIO_MEM_S3_7

M37

VDDIO_MEM_S3_8

N28

VDDIO_MEM_S3_9

N30

VDDIO_MEM_S3_10

N33

VDDIO_MEM_S3_11

N36

VDDIO_MEM_S3_12

N39

VDDIO_MEM_S3_13

P27

VDDIO_MEM_S3_14

P29

VDDIO_MEM_S3_15

P32

VDDIO_MEM_S3_16

P35

VDDIO_MEM_S3_17

P38

VDDIO_MEM_S3_18

R28

VDDIO_MEM_S3_19

R31

VDDIO_MEM_S3_20

R34

VDDIO_MEM_S3_21

R37

VDDIO_MEM_S3_22

T27

VDDIO_MEM_S3_23

T29

VDDIO_MEM_S3_24

T33

VDDIO_MEM_S3_25

T36

VDDIO_MEM_S3_26

T39

VDDIO_MEM_S3_27

U28

VDDIO_MEM_S3_28

U30

VDDIO_MEM_S3_29

U32

VDDIO_MEM_S3_30

U35

VDDIO_MEM_S3_31

U38

VDDIO_MEM_S3_32

V27

VDDIO_MEM_S3_33

V29

VDDIO_MEM_S3_34

V31

VDDIO_MEM_S3_35

V34

VDDIO_MEM_S3_36

V37

VDDIO_MEM_S3_37

W28

VDDIO_MEM_S3_38

W33

VDDIO_MEM_S3_39

W34

VDDIO_MEM_S3_40

W36

VDDIO_MEM_S3_41

W39

VDDIO_MEM_S3_42

Y27

VDDIO_MEM_S3_43

Y29

VDDIO_MEM_S3_44

Y31

VDDIO_MEM_S3_45

Y32

VDDIO_MEM_S3_46

Y35

VDDIO_MEM_S3_47

Y38

VDDIO_MEM_S3_48

AA28

VDDIO_MEM_S3_49

AA34

VDDIO_MEM_S3_50

AA37

VDDIO_MEM_S3_51

AB27

VDDIO_MEM_S3_52

AB29

VDDIO_MEM_S3_53

AB31

VDDIO_MEM_S3_54

AB32

VDDIO_MEM_S3_55

AB33

VDDIO_MEM_S3_56

AB36

VDDIO_MEM_S3_57

AB39

VDDIO_MEM_S3_58

AC28

VDDIO_MEM_S3_59

AC30

VDDIO_MEM_S3_60

AC32

VDDIO_MEM_S3_61

AC35

VDDIO_MEM_S3_62

AC38

VDDIO_MEM_S3_63

AD27

VDDIO_MEM_S3_64

AD29

VDDIO_MEM_S3_65

AD31

VDDIO_MEM_S3_66

AD34

VDDIO_MEM_S3_67

AD37

VDDIO_MEM_S3_68

AE28

VDDIO_MEM_S3_69

AE30

VDDIO_MEM_S3_70

AE33

VDDIO_MEM_S3_71

AE36

VDDIO_MEM_S3_72

AE39

VDDIO_MEM_S3_73

AF27

VDDIO_MEM_S3_74

AF29

VDDIO_MEM_S3_75

AF32

VDDIO_MEM_S3_76

AF35

VDDIO_MEM_S3_77

AF38

VDDIO_MEM_S3_78

AG33

VDDIO_MEM_S3_79

AG34

VDDIO_MEM_S3_80

AG35

VDDIO_MEM_S3_81

AG37

VDDIO_MEM_S3_82

AH39

VDDIO_MEM_S3_83

4

POWER

AM4

PART 7 OF 9

ZIF-SOCKET1331

VDDP_0

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

VDDP_6

VDDP_7

VDDP_8

VDDIO_AUDIO

VDD_18_0

VDD_18_1

VDD_33_0

VDD_33_1

VDDP_S5_0

VDDP_S5_1

VDD_18_S5_0

VDD_18_S5_1

VDD_33_S5_0

VDD_33_S5_1

VDDBT_RTC_G

RSVD_0

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

RSVD_16

RSVD_17

RSVD_18

RSVD_19

RSVD_20

RSVD_21

RSVD_22

RSVD_23

RSVD_24

RSVD_25

RSVD_26

RSVD_27

RSVD_28

RSVD_29

RSVD_30

RSVD_31

RSVD_32

RSVD_33

RSVD_34

RSVD_35

RSVD_36

RSVD_37

RSVD_38

RSVD_39

RSVD_40

RSVD_41

RSVD_42

RSVD_43

RSVD_44

RSVD_45

RSVD_46

CPU_VDDPVCC_DDR

AM18

AM19

AM20

AN18

AN19

AN20

AP18

AP19

AP20

AM15

AJ20

AK20

AJ21

AK21

AJ16

AJ17

AJ15

AK15

AJ19

AK19

AL15

C722 1u6.3X/4

C719 C0.22u16X5/4

AM12

AT25

AR15

AP15

AN12

AN15

AT30

AW24

AR24

A5

AD3

AB2

AH2

AL16

AL17

AL18

AL19

AL20

AL21

AM16

AM17

AM21

AN16

AN17

AN21

AP16

AP17

AP21

AR16

AR18

AR19

AR20

AR21

AT19

D28

E19

E22

E25

G17

J36

J38

K34

K38

R35

AB37

AH35

AK34

8.5A

C317 C0.22u16X5/4

C320 10u6.3X/6

CPU_1P8

VCC3

CPU_VDDP_S5

CPU_1P8_S5

3VSB

3

CPU_1P8_S5

2.00A

0.25A

0.25A

VDDBT_RTC_G

C903

C22u6.3X/6

1.00A

0.5A

CPU_VDDP

0.25A

C294

C22u6.3X/6

VCORE VCCP_NB VCC_DDR

C880 C22u6.3X/6

C217 C22u6.3X/6

C865 C22u6.3X/6

C863 C22u6.3X/6

C228 C22u6.3X/6

C218 C22u6.3X/6

C876 C22u6.3X/6

C884 C22u6.3X/6

C232 C22u6.3X/6

C229 C22u6.3X/6

C230 C22u6.3X/6

C867 C22u6.3X/6

BOTTOM CAVITY

VCORE VCCP_NB VCC_DDR

C122 C22u6.3X/6

C845 C22u6.3X/6

C118 C22u6.3X/6

C848 C22u6.3X/6

C212 C22u6.3X/6

C213 C22u6.3X/6

C877 C22u6.3X/6

C172 C22u6.3X/6

C844 C22u6.3X/6

4.5uA

C231 C22u6.3X/6

C883 C22u6.3X/6

C882 C22u6.3X/6

C856 C180p50N/4

C843 C22u6.3X/6

C849 C22u6.3X/6

C868 X_C22u6.3X/6

C878 X_C22u6.3X/6

C112 X_C22u6.3X/6

C125 X_C22u6.3X/6

C846 X_C22u6.3X/6

C137 X_C22u6.3X/6

C847 X_C22u6.3X/6

C837 X_C2.2u6.3X/4

C929 X_C2.2u6.3X/4

C928 X_C2.2u6.3X/4

C927 X_C2.2u6.3X/4

C926 X_C2.2u6.3X/4

C925 X_C2.2u6.3X/4

C924 X_C2.2u6.3X/4

C923 X_C2.2u6.3X/4

C922 X_C2.2u6.3X/4

C921 X_C2.2u6.3X/4

C972 X_C2.2u6.3X/4

C891 X_C2.2u6.3X/4

C895 X_C0.22u16X5/4

C897 X_C0.22u16X5/4

C850 X_C0.22u16X5/4

C874 X_C0.22u16X5/4

C920 X_C0.22u16X5/4

C879 X_C0.22u16X5/4

C904 X_C0.22u16X5/4

C896 X_C180p50N/4

C869 X_C180p50N/4

C873 X_C1000p50X4

2

C835 C22u6.3X/6

C823 C22u6.3X/6

C80 C22u6.3X/6

C825 C22u6.3X/6

C81 C22u6.3X/6

C824 C22u6.3X/6

C82 C22u6 .3X/6

C200 C22u6.3X/6

C815 C22u6.3X/6

C679 C22u6.3X/6

C821 C22u6.3X/6

C201 C22u6.3X/6

C86 C22u6 .3X/6

C202 C22u6.3X/6

C85 C22u6 .3X/6

C807 C180p50N/4

C818 X_C2.2u6.3X/4

C793 X_C2.2u6.3X/4

C792 X_C2.2u6.3X/4

C809 X_C2.2u6.3X/4

C794 X_C2.2u6.3X/4

C804 X_C2.2u6.3X/4

C832 X_C2.2u6.3X/4

C811 X_C2.2u6.3X/4

C796 X_C2.2u6.3X/4

C808 X_C2.2u6.3X/4

C814 X_C2.2u6.3X/4

C805 X_C2.2u6.3X/4

C806 X_C2.2u6.3X/4

C802 X_C0.22u16X5/4

C795 X_C0.22u16X5/4

C800 X_C0.22u16X5/4

C789 X_C0.22u16X5/4

C798 X_C0.22u16X5/4

C788 X_C0.22u16X5/4

C813 X_C0.22u16X5/4

C820 X_C0.22u16X5/4

C803 X_C0.22u16X5/4

C791 X_C0.22u16X5/4

C797 X_C180p50N/4

C801 X_C180p50N/4

2

TOP SIDE

VCORE VCCP_NB

C233 X_C22u6.3X/6

C862 X_C22u6.3X/6

C881 X_C22u6.3X/6

C215 X_C22u6.3X/6

C894 X_C2.2u6.3X/4

C885 X_C2.2u6.3X/4

C872 X_C2.2u6.3X/4

C889 X_C2.2u6.3X/4

CPU_1P8

C852 C22u6.3X/6

C236 C22u6.3X/6

C222 C22u6.3X/6

C210 C22u6.3X/6

C205 X_C22u6.3X/6

C219 X_C22u6.3X/6

C859 X_C22u6.3X/6

C810 C0.22u16X5/4

C190 C180p50N/4

C860 X_C22u6.3X/6

C235 X_C22u6.3X/6

C197 X_C22u6.3X/6

C870 X_C2.2u6.3X/4

C858 X_C2.2u6.3X/4

C241 X_C2.2u6.3X/4

C240 X_C2.2u6.3X/4

C831 X_C2.2u6.3X/4

C816 X_C2.2u6.3X/4

C871 X_C2.2u6.3X/4

C875 X_C2.2u6.3X/4

C799 X_C0.22u16X5/4

C817 X_C0.22u16X5/4

C888 X_C180p50N/4

C886 X_C180p50N/4

C221 X_C1u16X/6

C272 X_C0.1u16X/4

C259 X_C0.1u16X/4

C207 X_C0.1u16X/4

C186 X_C0.1u16X/4

C182 X_C0.1u16X/4

C195 X_C0.1u16X/4

C209 X_C0.1u16X/4

C192 X_C0.1u16X/4

Title

Title

Title

AM4 Power/RTC Power

AM4 Power/RTC Power

AM4 Power/RTC Power

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-7C58

MS-7C58

MS-7C58

Date: Sheet of

Date: Sheet of

Date: Sheet of

BOTTOM SIDE

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

1

C830 X_C22u6.3X/6

C199 X_C22u6.3X/6

C826 X_C22u6.3X/6

C203 X_C22u6.3X/6

C828 X_C22u6.3X/6

C827 X_C22u6.3X/6

C84 X_C22u6.3X/6

VCC3

C900 C0.22u16X5/4

C335 C22u6.3X/6

C331 C0.22u16X5/4

C330 C0.22u16X5/4

C329 C0.1u16X/4

CPU_1P8_S5

C901 10u6.3X/6

C892 C0.22u16X5/4

VCCP_NB_S5

C220 C22u6.3X/6

C299 C0.22u16X5/4

CPU_VDDP_S5

C333 10u6.3X/6

C321 C0.22u16X5/4

CPU_1P8

C893 C0.22u16X5/4

3VSB

C315 C0.22u16X5/4

1

10

10

8 55Monday, November 11, 2019

8 55Monday, November 11, 2019

8 55Monday, November 11, 2019

10

Page 9

A A

smd.db-x7.ru

B B

C C

D D

5

4

3

2

Date: Sheet of

Date: Sheet of

Date: Sheet of

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-7C5810AM4 GND

MS-7C5810AM4 GND

MS-7C5810AM4 GND

D39

E11

E14

E17

E20

E21

E23

E26

E27

E29

E32

E35

E38

F17

F19

F22

F25

F28

F31

F34

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28D6VSS_29D9VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49E4VSS_50E5VSS_51E8VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64F1VSS_65F4VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

F35

VSS_73

F37

VSS_74

G7

VSS_75

G21

VSS_76

G24

VSS_77

G27

VSS_78

G30

VSS_79

G33

VSS_80

G35

VSS_81

G36

VSS_82

G39

VSS_83

H4

VSS_84

H5

VSS_85

H8

VSS_86

H11

VSS_87

H14

VSS_88

H17

VSS_89

H20

VSS_90

H23

VSS_91

H26

VSS_92

H29

VSS_93

H32

VSS_94

H35

VSS_95

H38

VSS_96

J1

VSS_97

J4

VSS_98

J8

VSS_99

J9

VSS_100

J11

VSS_101

J13

VSS_102

J17

VSS_103

J19

VSS_104

J22

VSS_105

J25

VSS_106

J28

VSS_107

J31

VSS_108

J34

VSS_109

J35

VSS_110

J37

VSS_111

K10

VSS_112

K12

VSS_113

K18

VSS_114

K20

VSS_115

K21

VSS_116

K22

VSS_117

K23

VSS_118

K26

VSS_119

K27

VSS_120

K28

VSS_121

K29

VSS_122

K30

VSS_123

K33

VSS_124

L4

VSS_125

L5

VSS_126

L8

VSS_127

L9

VSS_128

L11

VSS_129

L13

VSS_130

L15

VSS_131

L17

VSS_132

L19

VSS_133

L21

VSS_134

L25

VSS_135

L27

VSS_136

L28

VSS_137

L30

VSS_138

L31

VSS_139

M1

VSS_140

M4

VSS_141

M8

VSS_142

M10

VSS_143

M12

VSS_144

M14

VSS_145

M16

VSS_146

M18

VSS_147

M20

VSS_148

M24

VSS_149

M26

VSS_150

M27

VSS_151

M28

VSS_152

N9

VSS_153

N11

VSS_154

N13

VSS_155

N15

VSS_156

N17

VSS_157

N19

VSS_158

N21

VSS_159

N23

VSS_160

N25

VSS_161

N27

VSS_162

N29

VSS_163

P4

VSS_164

P5

VSS_165

P8

VSS_166

P10

VSS_167

P12

VSS_168

R1

VSS_169

R4

VSS_170

R8

VSS_171

R9

VSS_172

R11

VSS_173

R13

VSS_174

R27

VSS_175

R29

VSS_176

T10

VSS_177

T12

VSS_178

T28

VSS_179

T30

VSS_180

U4

VSS_181

U5

VSS_182

U8

VSS_183

U9

VSS_184

U11

VSS_185

U13

VSS_186

U27

VSS_187

U29

VSS_188

U31

VSS_189

V1

VSS_190

V4

VSS_191

V7

VSS_192

V10

VSS_193

V12

VSS_194

V28

VSS_195

V30

VSS_196

W9

VSS_197

W11

VSS_198

W13

VSS_199

W27

VSS_200

Title

Title

Title

W29

W31

ZIF-SOCKET1331

VSS_201

VSS_202

VSS_218

VSS_217

VSS_216

VSS_215

VSS_214

VSS_213

VSS_212

VSS_211

VSS_210

VSS_209

VSS_208

VSS_207

VSS_206

VSS_205

VSS_204Y8VSS_203

AB7

AA31

AA29

AA27

AA13

AA11

AA9

AA6

AA4

AA1

Y30

Y28

Y12

Y10

Y5

PART 9 OF 9

AM4

VSS_239

VSS_238

VSS_237

VSS_236

VSS_235

VSS_234

VSS_233

VSS_232

VSS_231

VSS_230

VSS_229

VSS_228

VSS_227

VSS_226

VSS_225

VSS_224

VSS_223

VSS_222

VSS_221

VSS_220

VSS_219

AE11

AE9

AE7

AD30

AD28

AD12

AD10

AD4

AD1

AC31

AC29

AC27

AC13

AC11

AC9

AC8

AC5

AB30

AB28

AB12

AB10

GND

VSS_253

VSS_252

VSS_251

VSS_250

VSS_249

VSS_248

VSS_247

VSS_246

VSS_245

VSS_244

VSS_243

VSS_242

VSS_241

VSS_240

AM26

AM29

AM32

AM35

AM38

AF12

AF10

AF8

AF5

AE31

AE29

AE27

AE13

B23

B26

B29

B32

B35

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21C1VSS_22

VSS_260

VSS_259

VSS_258

VSS_257

VSS_256

VSS_255

VSS_254

AL33

AL35

AL36

AL39

AM5

AM11

AM14

A21

A24

A27

A30

A33

A36

B19

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_267

VSS_266

VSS_265

VSS_264

VSS_263

VSS_262

VSS_261

AK35

AK37

AL9

AL11

AL24

AL27

AL30

C22

C25

C28

C31

C34

C37

D12

D15

D18

D19

D21

D22

D23

D24

D25

D27

D29

D30

D31

D32

D33

D34

D35

D36

AJ11

A12

A15

A18

VSS_7

VSS_268

AK31

L29

J15

CPU1I

VSS_0

VSS_1

VSS_2

VSS_3A3VSS_4A6VSS_5A9VSS_6

MEC6

MEC6

MEC5

MEC5

MEC4

MEC4

MEC3

MEC3

MEC2

MEC2

MEC1

MEC1

AN1

VSS_398

AN4

VSS_397

AN22

VSS_396

AN25

VSS_395

AN28

VSS_394

AN31

VSS_393

AN34

VSS_392

AN35

VSS_391

AN37

VSS_390

AP6

VSS_389

AP24

VSS_388

AP27

VSS_387

AP30

VSS_386

AP33

VSS_385

AP35

VSS_384

AP36

VSS_383

AP39

VSS_382

AR5

VSS_381

AR8

VSS_380

AR11

VSS_379

AR14

VSS_378

AR17

VSS_377

AR23

VSS_376

AR26

VSS_375

AR27

VSS_374

AR29

VSS_373

AR30

VSS_372

AR32

VSS_371

AR34

VSS_370

AR35

VSS_369

AR38

VSS_368

AT1

VSS_367

AT7

VSS_366

AT10

VSS_365

AT13

VSS_364

AT16

VSS_363

AT22

VSS_362

AT26

VSS_361

AT27

VSS_360

AT28

VSS_359

AT29

VSS_358

AT31

VSS_357

AT32

VSS_356

AT33

VSS_355

AT34

VSS_354

AT37

VSS_353

AU18

VSS_352

AU21

VSS_351

AU24

VSS_350

AU26

VSS_349

AU27

VSS_348

AU30

VSS_347

AU33

VSS_346

AU36

VSS_345

AU39

VSS_344

AV2

VSS_343

AV17

VSS_342

AV20

VSS_341

AV23

VSS_340

AV26

VSS_339

AV29

VSS_338

AV32

VSS_337

AV35

VSS_336

AV38

VSS_335

AW4

VSS_334

AW7

VSS_333

AW10

VSS_332

AW13

VSS_331

AW16

VSS_330

AW19

VSS_329

AW22

VSS_328

AW25

VSS_327

AW28

VSS_326

AW31

VSS_325

AW34

VSS_324

AW37

VSS_323

AF28

VSS_322

AF30

VSS_321

AG1

VSS_320

AG4

VSS_319

AG8

VSS_318

AG9

VSS_317

AG11

VSS_316

AG13

VSS_315

AG15

VSS_314

AG17

VSS_313

AG19

VSS_312

AG21

VSS_311

AG23

VSS_310

AG25

VSS_309

AG27

VSS_308

AG28

VSS_307

AG29

VSS_306

AG30

VSS_305

AG31

VSS_304

AG32

VSS_303

AH10

VSS_302

AH12

VSS_301

AH14

VSS_300

AH16

VSS_299

AH18

VSS_298

AH20

VSS_297

AH22

VSS_296

AH24

VSS_295

AH26

VSS_294

AH28

VSS_293

AH29

VSS_292

AH30

VSS_291

AH33

VSS_290

AJ5

VSS_289

AJ8

VSS_288

AJ9

VSS_287

AJ13

VSS_286

AJ23

VSS_285

AJ25

VSS_284

AJ26

VSS_283

AJ27

VSS_282

AJ28

VSS_281

AJ29

VSS_280

AJ32

VSS_279

AJ35

VSS_278

AJ36

VSS_277

AJ38

VSS_269

AK28

VSS_276

VSS_275

VSS_274

VSS_273

VSS_272

VSS_271

VSS_270

AK25

AK1

AK4

AK10

AK12

AK14

AK22

5

CPU_IN#48

R1392 X_0R/4

R1391 X_R /2

4

3

2

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

1

9 55Monday, November 11, 2019

9 55Monday, November 11, 2019

9 55Monday, November 11, 2019

1

Page 10

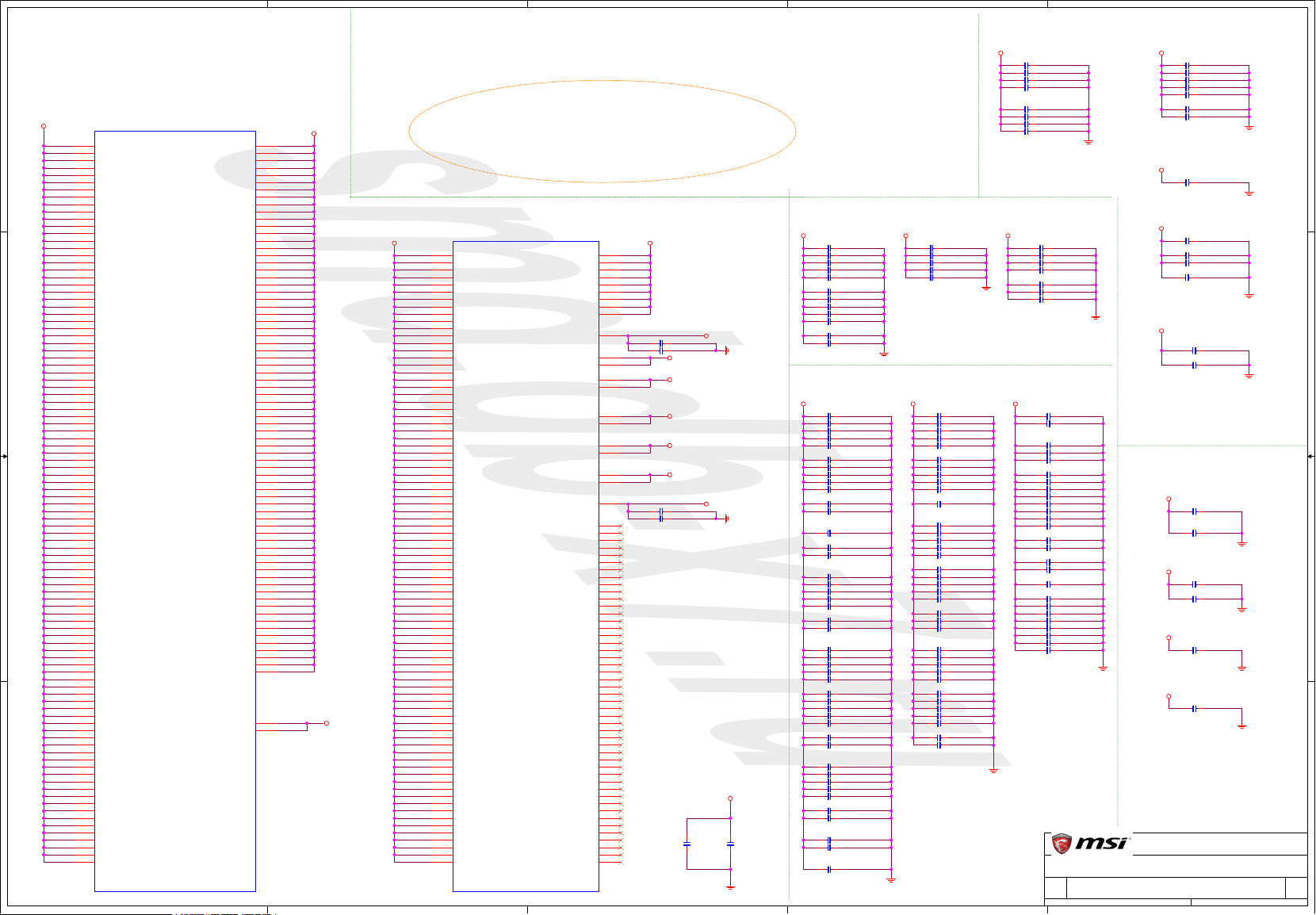

5

smd.db-x7.ru

A1

MA_DM73

MA_DM63

D D

C C

B B

VCC_DDR

A A

MA_DM53

MA_DM43

MA_DM33

MA_DM23

MA_DM13

MA_DM03

MA_DQS_H73

MA_DQS_L73

MA_DQS_H63

MA_DQS_L63

MA_DQS_H53

MA_DQS_L53

MA_DQS_H43

MA_DQS_L43