Page 1

5

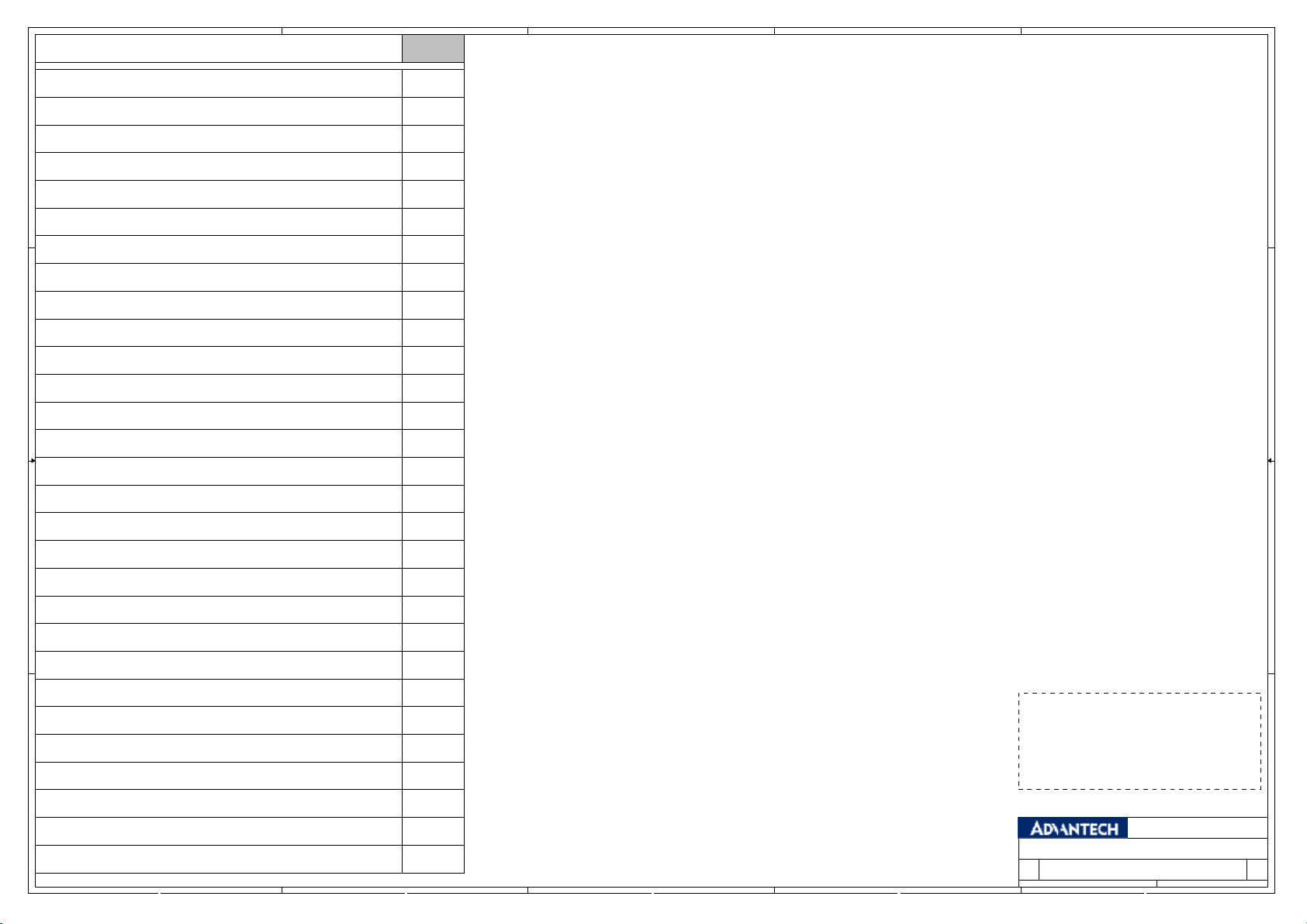

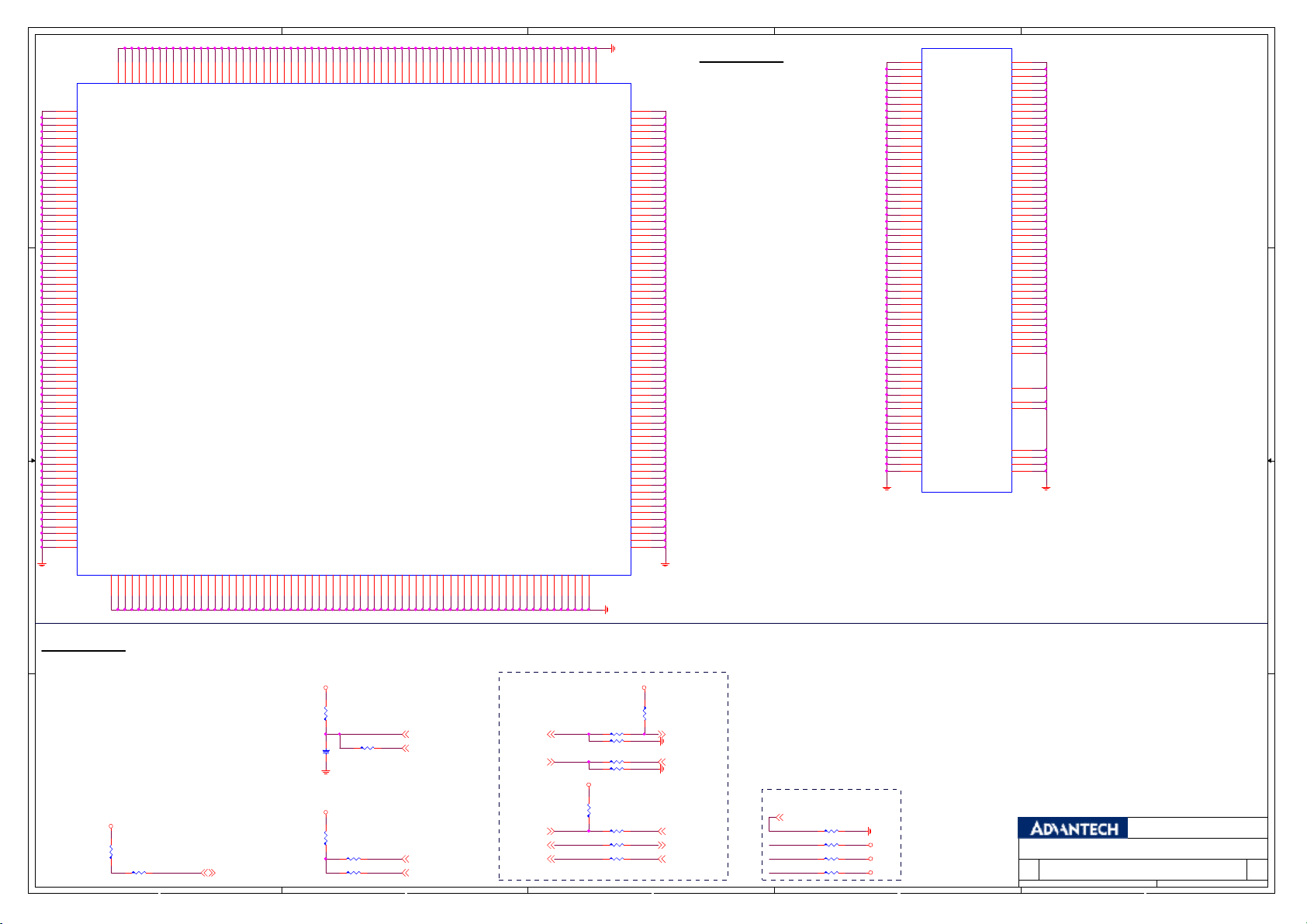

CONTENT SHEET

Cover Sheet & Block Diagram

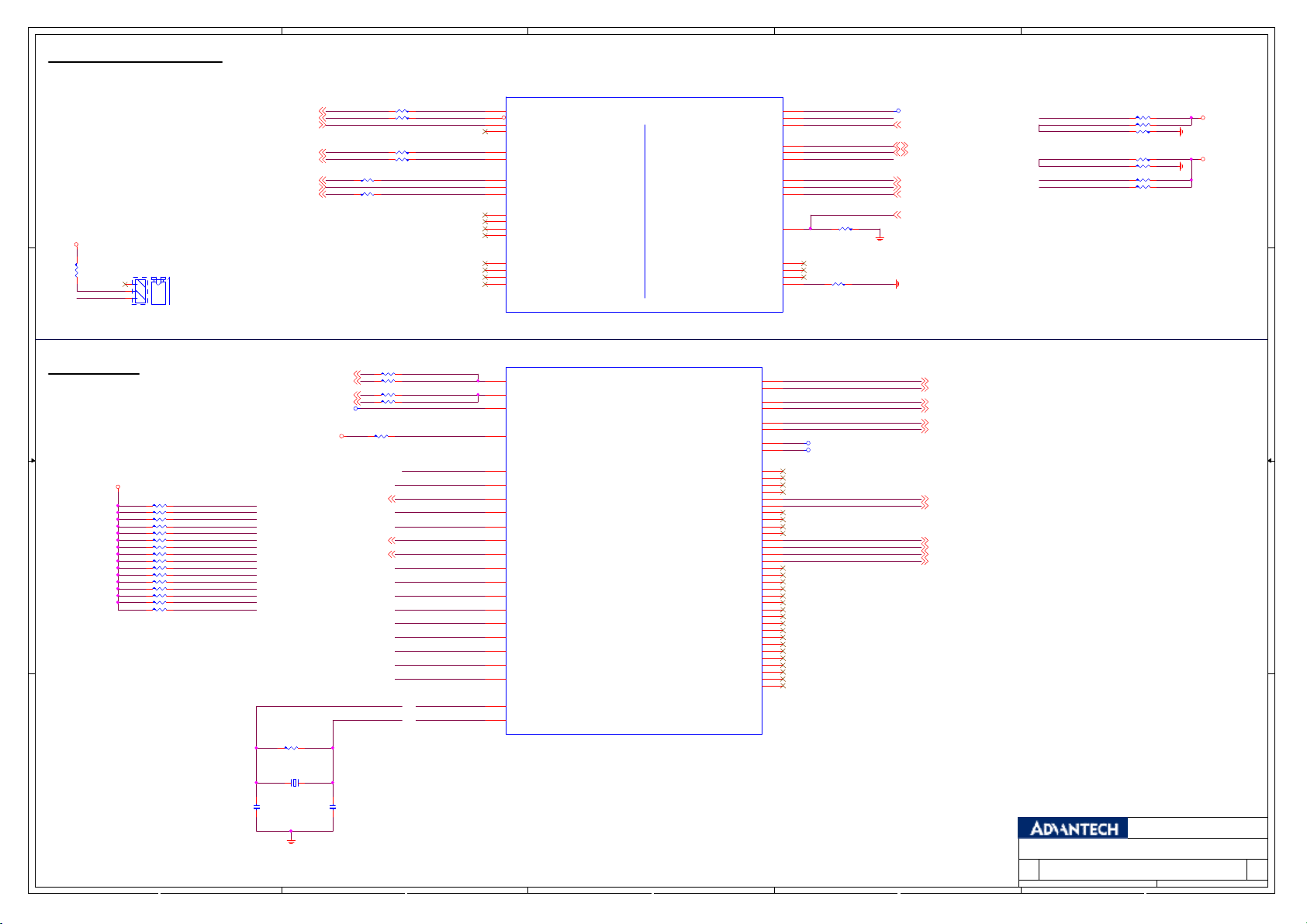

CPU-CLK/CTL/MISC/DMI/AUDIO/DSP/MEM

4

1-2

3-4

DMS-SA30

Intel Skylake-S

3

2

1

Rev.10

CPU-Power/GND/XDP

D D

DDRIV-DIMMA1/DIMMB1

PCH-USB/PCIE/DMI/SATA

PCH-Audio/Display/Clock

PCH-GPIO/USBOC#/SATAGP

PCH-LPC/SPI/SMBUS/MISC

PCH-POWER/GND/Strap/SPKR

HDMI to LVDS (TSUMU58BDC2-1)

C C

LVDS Output & EDID Switch & USB2.0*2

OSD & LED & SPK & GL850G - USB2.0 HUB

VGA(CH7517A) & DP Connector

LAN I219 (LM/V) & USB3.0

Audio Codec ALC898 & Amplifier TPA2008D2

M_PCI-E & LPC-TPM & JTPM/JLPC & USB2.0*1

SIO-NCT6106D

COM & USB3.0 & Exp BD

B B

+24V Boost & +5VSB & Power USB(USB2.0*1)

Cash Drawer

+19VA / +12VSB / +12V / +3VA

System Power +5VSUS/+3VSUS/+5V/+3V

IMVP8-ISL95855(VCCP/VGT/VSA)

VCCP & VCCGT

VCCSA & VCCIO

DDR4 Power

A A

PCH Power - PCH_1VSB

Manual Parts

PWR Map & Design change list

5

5-6

7-8

9

10

11

12

13-14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34-35

4

CPU:

Intel SKL-S CPU (LGA1151)

Max. TDP: 35W

System Chipset:

Intel 100 series

Q170/H110

Main Memory:

DDR4-1866/2133 SO-DIMM x2 (1DPC, Max:32GB)

On Board Chip:

HDMI to LVDS - TSUMU58DC2-1

eDP to VGA - CH7517A

Super I/O - NCT6106D

Audio - Realtek HD Audio Codec ALC898 + Amplifier TPA2008D2

LAN - Intel Jacksonville i219LM(Q170) / V(H110)

BIOS - SPI Flash ROM 128MB(Q170) / 64MB(H110)

TPM 2.0/1.2 - SLB9665/9660 (For Q170 SKU)

GL850G - USB2.0 HUB (For H110 SKU)

VRM Controller:

IMVP8-ISL95855(VCCP/VCCGT/VCCSA)

ISL8016(VCCIO)

NCP1589L(VCC_DDR) + UP1727(VPP_DDR)

NCP1589L(PCH_1VSB)

NCP1589A(+12VSB)

TPS40210DGQ(+24VSB)

TPS51125RGER(SYS_PWR)

Expansion Slots:

SATA Riser Connector (2* SATA ports)

Mini-PCIE *2

Expension Board (RS232*2, USB*1 ...)

Others :

Cash Drawer

Power USB

3

How to distinguish different Sku

BLUE Color for all models

一

一

Orange Color for Q170 SKU

Purple Color for H110 SKU

一

Title

Title

Title

Cover page

Cover page

Cover page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

DMS-SA30

DMS-SA30

DMS-SA30

10

10

1 35Friday, March 31, 2017

1 35Friday, March 31, 2017

1

1 35Friday, March 31, 2017

10

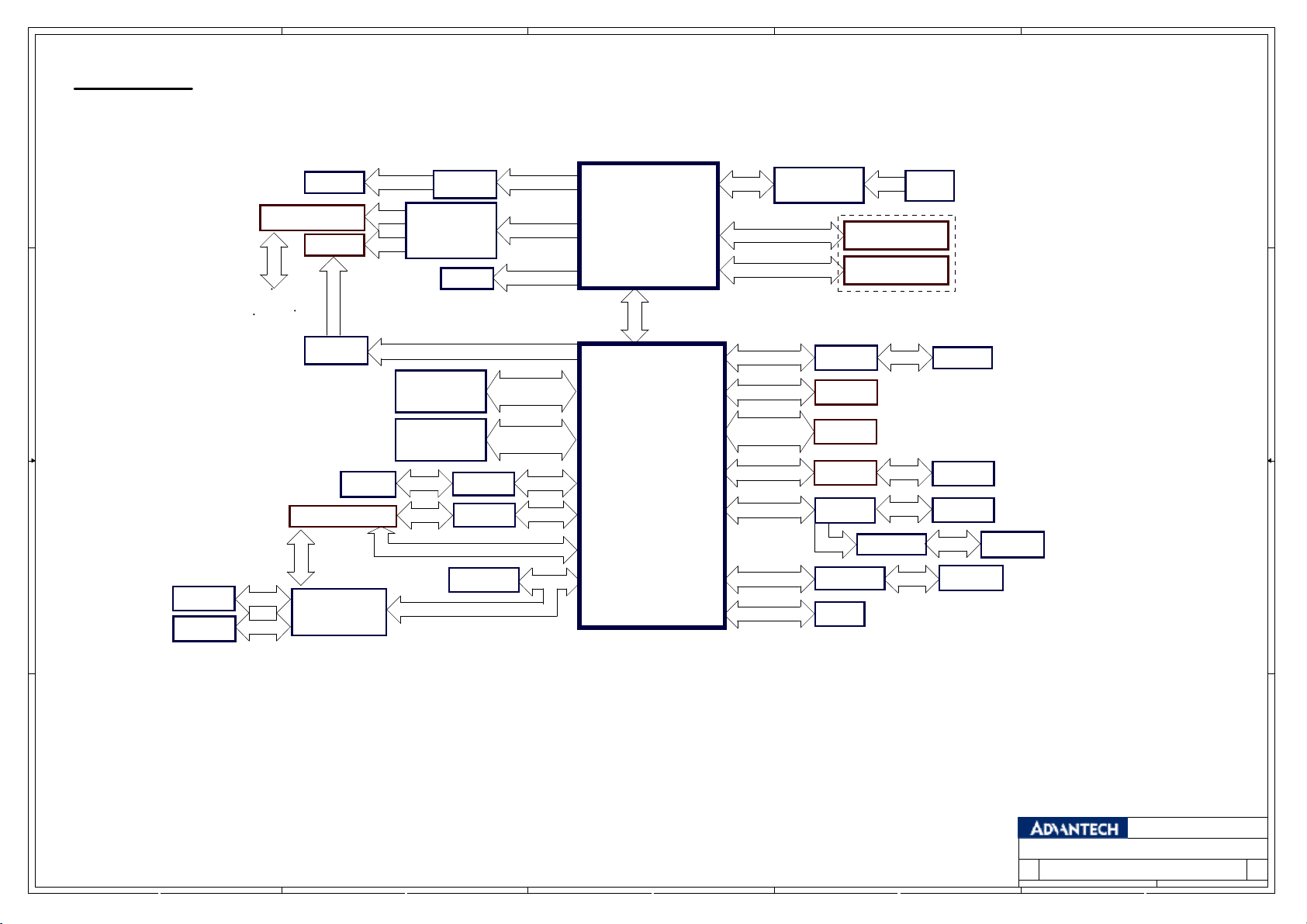

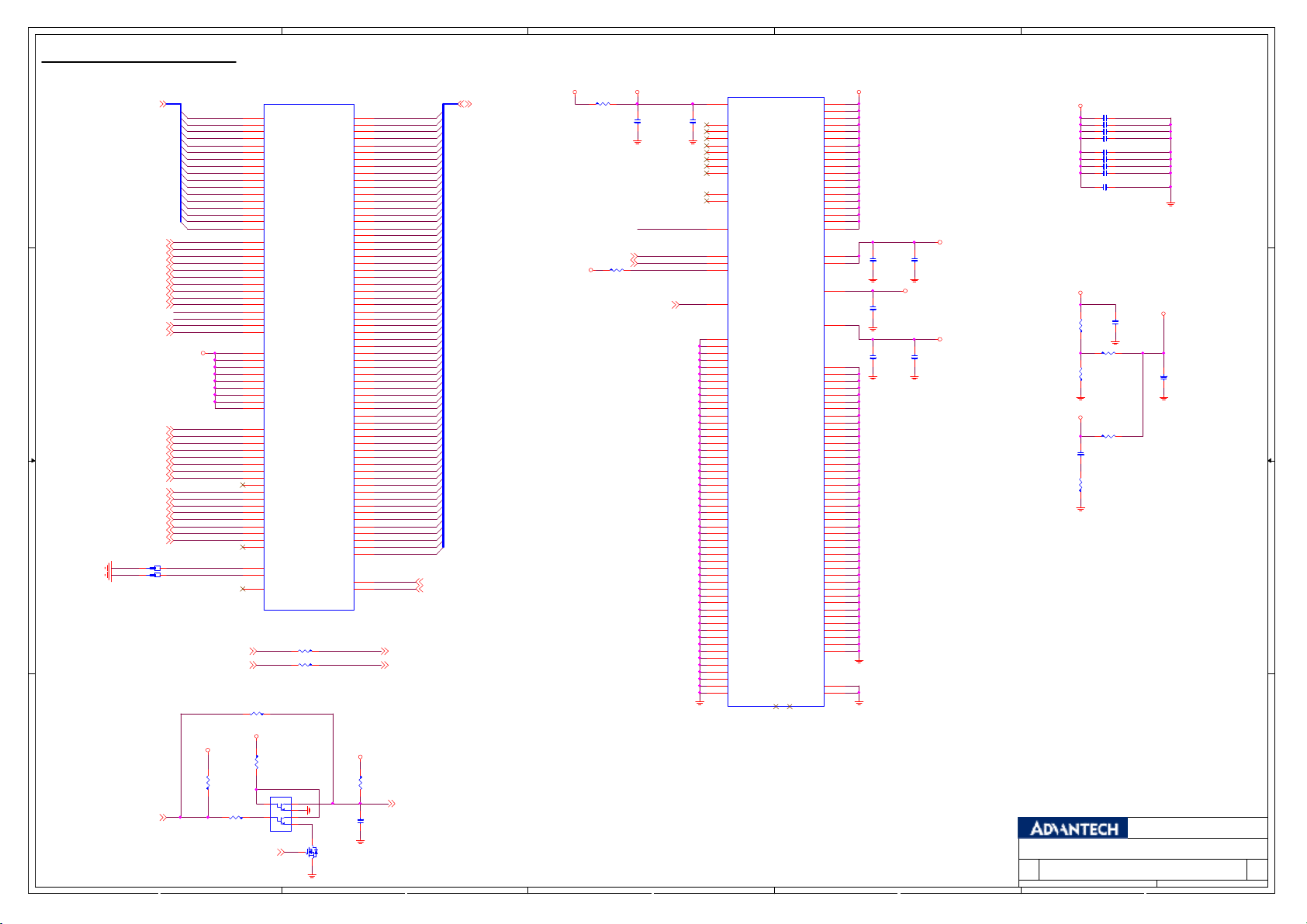

Page 2

5

4

3

2

1

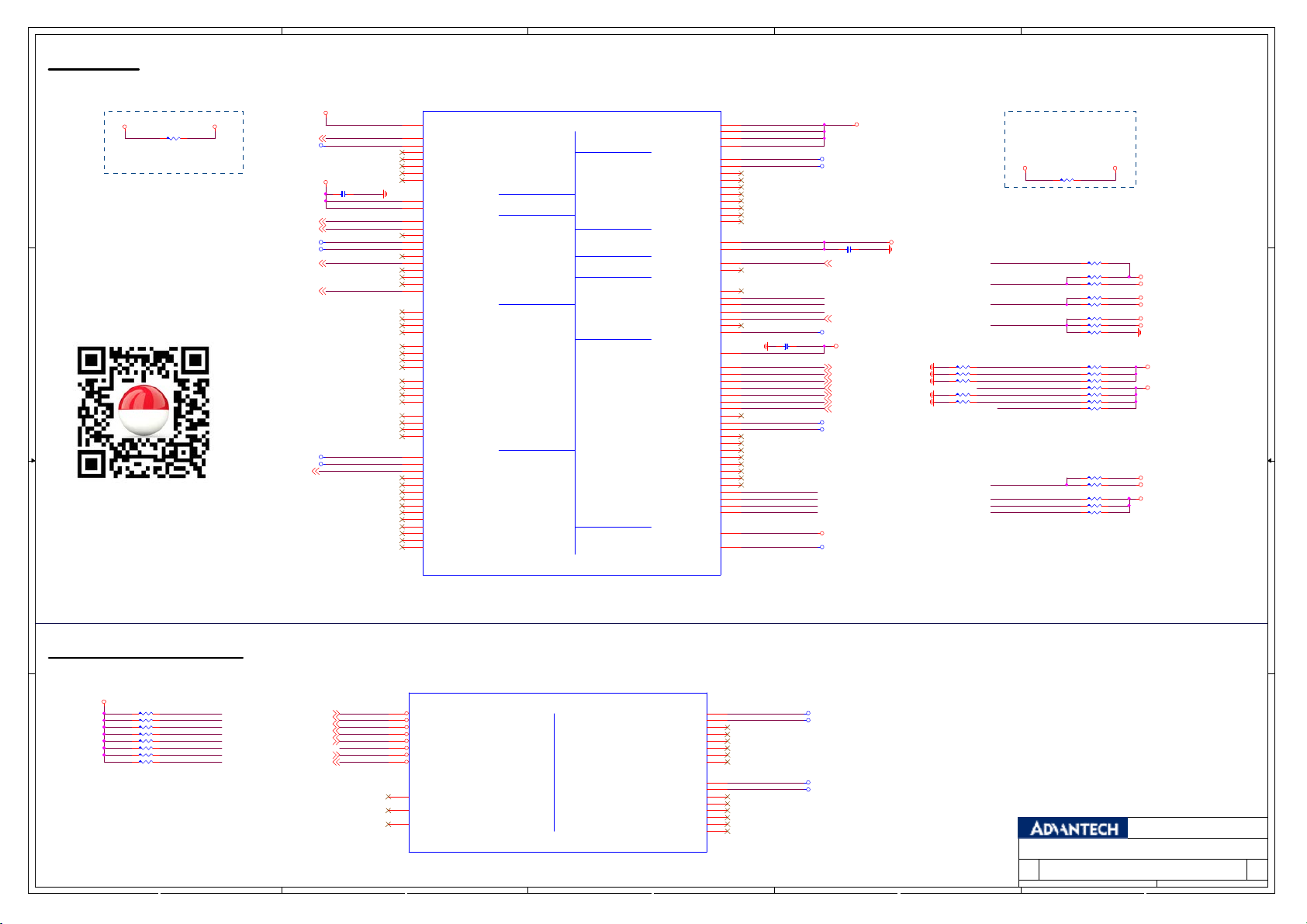

Block Diagram

D D

VGA Conn.

LVDS Conn.

LVDS/BKL/USB2.0*2

USB2.0

#5 & #6

PCH

USB2.0

C C

OSD Conn.

USB2.0 HUB

GL850G

DP to VGA

CH7517A

HDMI to LVDS

TSUMU58BDC2

DP Conn.

USB2.0 #10

RJ45-LAN with

USB3.0 #1#2

USB2.0 #1#2

DP (DDPB)

TMDS (DDPC)

DP (DDPD)

Rear

USB3.0&2.0

INTEL

SKL-S LGA1151

35W

DMI [X4]

INTEL

RJ45-RS232 with

USB3.0 #3#4

USB2.0 #3#4

PWR_USB

EXP Conn.

GPIO

COM3

B B

DSUB Conn.

RJ45 Conn.

COM1

COM2

COM4

SIO

NCT6106D

TPM 2.0/1.2

USB2.0 #7

USB2.0 #8

CDW_GPIO

Rear

USB3.0&2.0

USB2.0

USB2.0

LPC

100 Series

H110/Q170

IMVP8

ISL95855

VCCP+VCCGT+SA

DDR4_CHA - 2133

DDR4_CHA - 2133

PCI-E[X1] #4 RJ45 Conn.

PCI-E[X1] #5

PCI-E[X1] #6

USB2.0 #9

SATA # 0&1

HD Audio I/F

GPIO

SPI I/F

DDR4 SO-DIMM_A1

DDR4 SO-DIMM_B1

Intel LAN

I219LM/V

Mini PCIE1

Full Size

Mini PCIE2

Standard

PCI-E[X1]

Riser Conn.

Audio

ALC898/892

Amplifier

TPA2008D2

Cash Drawer

SPI ROM

DC19V

Adapter

SATA Port0

SATA Port1

Line Out

Mic In

RJ11 Conn.

Speaker R/L

2W

A A

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

DMS-SA30

DMS-SA30

DMS-SA30

10

10

2 35Friday, March 31, 2017

2 35Friday, March 31, 2017

1

2 35Friday, March 31, 2017

10

Page 3

5

Vinafix.com

CPU-CTL/MISC/CFG/Audio/DSP

VCCST

R537 X_100R1%4

R541 100R1%4

D D

C C

H_PROCHOT#

PDG: 500ohm

CRB Rev.11: 75ohm

R548 56.2R1%4

R533 75R1%4

R176 1K/4

R178 X_49.9K1%4

VCCIO

R817 1K/4

Pocessor Strapping

CFG[0] ITP will drive the net to GND.

CFG[2] Reserved. No connect

CFG[4] Display Port Presence strap

=1:Disabled - No Physical Display Port attached to

Embedded DisplayPort*.No connect for disable.

=0:Enabled - An external Display Port device is

connected to the Embedded Display Port.

CFG[5,6] (1, 1) PCIE 16X

CFG[19:5] Reserved configuration lands.

A test point be placed on the board for these lands.

CRB1.0 Note

PD CFG9 FOR HASWELL INTERPOSER

PD CFG12 FOR HASWELL INTERPOSER

PD CFG13 FOR LPT-H INTERPOSER

H_VIDSCLK

H_VIDSOUT

H_VIDALERT#

H_PROCHOT#

THERMTRIP_N

CATERR#

CPU_PM_DOWN_R < 200 mil

PROC_SELECT#

VCCST Power Good

VCCST_PWRGD(28)

R128 6.04K1%4

R142 2.8K1%4

PCH_CPU_NSSC_CLK_DP(10)

PCH_CPU_NSSC_CLK_DN(10)

SIO

R1 81 X_1K/4

R1 79 X_1K/4

R1 92 X_1K/4

R2 43 X_1K/4

R2 51 1K/4

R2 21 X_1K/4

R2 95 X_1K/4

R2 98 X_1K/4

R2 11 X_1K/4

R1 87 X_1K/4

R1 97 X_1K/4

R2 64 X_1K/4

R2 76 X_1K/4

R2 57 X_1K/4

R2 93 X_1K/4

R2 88 X_1K/4

VCCST_PWRGD_CPU

4

PCH_CPU_BCLK_DP(10 )

PCH_CPU_BCLK_DN(10)

PCH_CPU_PCIE_DP(10 )

PCH_CPU_PCIE_DN(10)

CPU_VIDCLK

CPU_VIDSOUT

CPU_VIDALERT#

CPU_P ROCHOT#

VCCST_PWRGD_CPU

CPU_PM_DOWN_R

THERMTRIP_N

DDR_VTT_CTRL

TP61

PROC_SELECT#

CATERR#

H_ CFG 0

H_CFG1

H_CFG2

H_CFG3

H_CFG4

H_CFG5

H_CFG6

H_CFG7

H_CFG8

H_ CFG 9

H_CFG10

H_CFG11

H_CFG12

H_CFG13

H_CFG14

H_CFG15

XDP_PCUSTB0P

TP27

XDP_PCUSTB0N

TP29

XDP_PCUSTB1P

TP32

XDP_PCUSTB1N

TP34

CFG_COMP

CFG_COMP 12/15mil

Place inside CPU cavity

H_PECI(22)

R536 0R/4

R540 0R/4

R547 220R1%4

R532 100R1%4

R407 X_0R/4

R227 20R1%4

R175 0R/4

H_ CFG 0(6)

R781 49.9R1%4

H_VIDSCLK(28 )

H_VIDSOUT(28 )

H_VIDALERT#(28)

H_PROCHOT#(28 )

CPU_PWRGD(12 )

CPURST#(6,12)

PCH_PECI(12)

CPU_PM_SYNC(12)

CPU_PM_DOWN(12)

H_THERMTRIP#(12)

PROC_SELECT#(30)

CPU_SKTOCC#(11)

H_ CFG 0

H_ CFG 1

H_CFG2

H_CFG3

H_CFG4

H_CFG5

H_CFG6

H_CFG7

H_CFG8

H_CFG9

H_CFG10

H_CFG11

H_CFG12

H_CFG13

H_ CFG 1 4

H_ CFG 1 5

E38

E40

E39

C39

D11

AC36

AB36

AB35

D13

H15

F15

F16

H16

F19

H18

G21

H20

G16

E16

F17

H17

G20

F20

F21

H19

F14

E14

F18

G18

M11

W5

W4

W1

W2

K9

J9

F8

U2

E7

G7

E8

D8

CPU1E

LGA1151

ZIF-SOCKET1151

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDSCK

VIDSOUT

VIDALERT#

PROCHOT#

PROCPWRGD

VCCST_PWRGD

RESET#

PECI

PM_SYNC

PM_DOWN

THERMT RIP #

DDR_VTT _CNTL

PROC_SELECT#

SKTO CC#

CATERR#

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

CFG_RCOMP

3

SKYLAKE-S

VCC_SENSE

VSS_SENSE

VCCGT_SENSE

VSSGT_SENSE

VCCGTX_SENSE

VSSGTX_SENSE

VCCSA_SENSE

VCCIO_SENSE

VSS_SAIO_SENSE

VCCOPC_SENSE

VCCEOPIO_SENSE

VSSOPC_EOPIO_SENSE

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROC_AUDIO_ CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

PROC_TRIGIN

PROC_TRIGOUT

ZVM#

2

VCORE_VCC_SEN

C38

VCORE_VSS_SEN

D38

VCCGT_VCC_SEN

F39

VCCGT_VSS_SEN

F38

VCCGTX_SENSE

F37

F36

VCCSA_SEN_P

AD5

VCCIO_SEN

AF4

VCCSA_SEN_N

AE4

VCCOPC_SEN

AK21

VCCEOPIO_SEN

AJ24

AK22

H13

G12

F13

F11

XDP_MBP0

D16

XDP_MBP1

D17

G14

H14

PCH_CPU_AUD_SCLK

V3

PCH_CPU_AUD_SDO

V2

PCH_CPU_AUD_SDI_R

U1

H_TRST# H_TRST#

F12

H_PREQ#

B9

H_PRDY#

B10

CPU_INPUT_TRIGGER

D1

CPU_OUTPUT_TRIGGER_R

B3

ZV M # _ R

AC38

VCORE_VCC_SEN (28)

VCORE_VSS_SEN (28)

VCCGT_VCC_SEN (28)

VCCGT_VSS_SEN (28 )

TP44

VCCSA_SEN_P (28)

VCCIO_SEN (30)

VCCSA_SEN_N (28)

TP35

TP36

H_ TD O (6)

H_ TD I (6)

H_TMS (6)

H_TCK (6)

TP30

TP31

R1 41 20R1%4

RVP8 Rev1.1stuff 20R

H_TRST# (6)

TP20

TP22

R2 38 20R1%4

TP48

PCH_CPU_AUD_SCLK (10)

PCH_CPU_AUD_SDO (10)

PCH_CPU_AUD_SDI (10)

CPU_INPUT_TRIGGER (12)

CPU_OUTPUT_TRIGGER (12)

VCORE_VCC_SEN

VCORE_VSS_SEN

VCCGT_VCC_SEN

VCCGT_VSS_SEN

VCCSA_SEN_P

VCCSA_SEN_N

H_PREQ#

R277 100R1%4

R286 100R1%4

R252 100R1%4

R246 100R1%4

R248 100R1%4

R752 100R1%4

R232 X_51R/4

R177 X_51R/4

1

VCCP

VCCGT

VCCSA

VCCST

CPU1C

PEG_RXP[0]

PEG_RXN[0]

PEG_RXP[1]

PEG_RXN[1]

PEG_RXP[2]

PEG_RXN[2]

PEG_RXP[3]

PEG_RXN[3]

PEG_RXP[4]

PEG_RXN[4]

PEG_RXP[5]

PEG_RXN[5]

PEG_RXP[6]

PEG_RXN[6]

PEG_RXP[7]

PEG_RXN[7]

PEG_RXP[8]

PEG_RXN[8]

PEG_RXP[9]

PEG_RXN[9]

PEG_RXP[10]

PEG_RXN[10]

PEG_RXP[11]

PEG_RXN[11]

PEG_RXP[12]

PEG_RXN[12]

PEG_RXP[13]

PEG_RXN[13]

PEG_RXP[14]

PEG_RXN[14]

PEG_RXP[15]

PEG_RXN[15]

DMI_RXP[0]

DMI_RXN[0]

DMI_RXP[1]

DMI_RXN[1]

DMI_RXP[2]

DMI_RXN[2]

DMI_RXP[3]

DMI_RXN[3]

PEG_RCOMP

LGA1151

ZIF-SOCKET1151

SKYLAKE-S

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

A5

A6

B4

B5

C3

C4

D2

D3

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

L1

L2

M2

M3

N1

N2

P2

P3

R2

R1

T2

T3

AC2

AC1

AD3

AD2

AE2

AE1

AF2

AF3

DMI_TXP0 (9)

DMI_TXN0 (9)

DMI_TXP1 (9)

DMI_TXN1 (9)

DMI_TXP2 (9)

DMI_TXN2 (9)

DMI_TXP3 (9)

DMI_TXN3 (9)

VCCIO

4

EDP_COMP

R782 24.9R1%4

EDP_COMP <600MIL

12/20/25mil

B8

B7

C7

C6

D6

D5

PEG_COMP

AA4

AA5

AB4

AB3

AC4

AC5

E5

E4

F6

F5

G5

G4

H6

H5

J5

J4

K6

K5

L5

L4

M6

M5

N5

N4

P6

P5

R5

R4

T6

T5

U5

U4

Y3

Y4

L7

5

B B

DMI_RXP0(9)

A A

DMI_RXN0( 9)

DMI_RXP1(9)

DMI_RXN1( 9)

DMI_RXP2(9)

DMI_RXN2( 9)

DMI_RXP3(9)

DMI_RXN3( 9)

VCCIO

R786 24.9R1%4

PEG_COMP <400mil

12/15/15mil

MEC1

MEC2

MEC3

MEC4

MEC5

MEC6

MEC7

E10

D10

G10

H10

D12

E12

D14

D9

C9

F9

G9

M9

CPU1D

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXP[2]

EDP_TXN[2]

EDP_TXP[3]

EDP_TXN[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOM P

MEC1

MEC2

MEC3

MEC4

MEC5

MEC6

MEC7

LGA1151

ZIF-SOCKET1151

SKYLAKE-S

DDI1_TXP[0]

DDI1_TXN[0]

DDI1_TXP[1]

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

DDI2_TXP[0]

DDI2_TXN[0]

DDI2_TXP[1]

DDI2_TXN[1]

DDI2_TXP[2]

DDI2_TXN[2]

DDI2_TXP[3]

DDI2_TXN[3]

DDI3_TXP[0]

DDI3_TXN[0]

DDI3_TXP[1]

DDI3_TXN[1]

DDI3_TXP[2]

DDI3_TXN[2]

DDI3_TXP[3]

DDI3_TXN[3]

3

DDI1_AUXP

DDI1_AUXN

DDI2_AUXP

DDI2_AUXN

DDI3_AUXP

DDI3_AUXN

Port B: DP to VGA

C21

VGA_DDPB_TXP0 (18)

D21

VGA_DDPB_TXN0 (18)

D22

VGA_DDPB_TXP1 (18)

E22

VGA_DDPB_TXN1 (18)

B23

A23

C23

D23

B13

C13

B18

A18

D18

E18

C19

D19

D20

E20

A12

B12

B14

A14

C15

B15

B16

A16

C17

B17

B11

C11

VGA_DDPB_AUXP (18)

VGA_DDPB_AUXN (18)

Port C: HDMI to Scalar

HDMI_DDPC_AUXP

HDMI_DDPC_AUXN

Port D: DP connector

HDMI_DDPC_TXP2 (15)

HDMI_DDPC_TXN2 ( 15)

HDMI_DDPC_TXP1 (15)

HDMI_DDPC_TXN1 ( 15)

HDMI_DDPC_TXP0 (15)

HDMI_DDPC_TXN0 ( 15)

HDMI_DDPC_CLKP (15)

HDMI_DDPC_CLKN (15)

DSP_DDPD_TXP0 (18)

DSP_DDPD_TXN0 (18)

DSP_DDPD_TXP1 (18)

DSP_DDPD_TXN1 (18)

DSP_DDPD_TXP2 (18)

DSP_DDPD_TXN2 (18)

DSP_DDPD_TXP3 (18)

DSP_DDPD_TXN3 (18)

DSP_DDPD_AUXP (18 )

DSP_DDPD_AUXN (18)

TP26

TP25

TP52

TP53

CPU_L12

CPU_K12

TP_CPU_AU39

TP_CPU_AU40

PCH_AB11(14)

PCH_AB10(14)

R785 X_0R/4

R787 X_0R/4

2

CPU1F

SKYLAKE-S

H8

VSS-372

K10

RSVD-2

L10

RSVD-3

J17

RSVD-4

B39

RSVD-5

J19

RSVD-6

C40

RSVD-7

L12

RSVD-8

K12

RSVD-9

AU39

RSVD-10

AU40

RSVD-11

J15

RSVD-12

J14

RSVD-13

AU9

RSVD-14

AU10

RSVD-15

J13

RSVD-16

K11

RSVD-17

D15

RSVD-18

J11

RSVD-19

LGA1151

ZIF-SOCKET1151

Ti t l e

Ti t l e

Ti t l e

CPU-CTL/MISC/CFG/Audio/DSP

CPU-CTL/MISC/CFG/Audio/DSP

CPU-CTL/MISC/CFG/Audio/DSP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

RSVD-20

VSS-373

VSS-374

RSVD-23

RSVD_TP-1

RSVD_TP-2

RSVD_TP-3

RSVD_TP-4

RSVD_TP-5

RSVD_TP-6

RSVD_TP-7

RSVD_TP-8

RSVD_TP-9

RSVD_TP-10

DMS-SA30

DMS-SA30

DMS-SA30

1

AC37

G8

AY3

K13

J8

J7

L8

K8

AV1

AW2

H11

H12

AW38

AV39

TP_CPU_K13

TP_CPU_J8

TP_CPU_J7

TP_CPU_L8

TP_CPU_K8

TP_CPU_AV1

TP_CPU_AW2

TP_CPU_H11

TP_CPU_H12

TP_CPU_AW38

TP_CPU_AV39

3 35Friday, March 31, 2017

3 35Friday, March 31, 2017

3 35Friday, March 31, 2017

R183

X_560R/4

CRB

TP21

TP18

TP24

TP19

TP17

TP16

TP23

TP28

TP46

TP51

10

10

10

Page 4

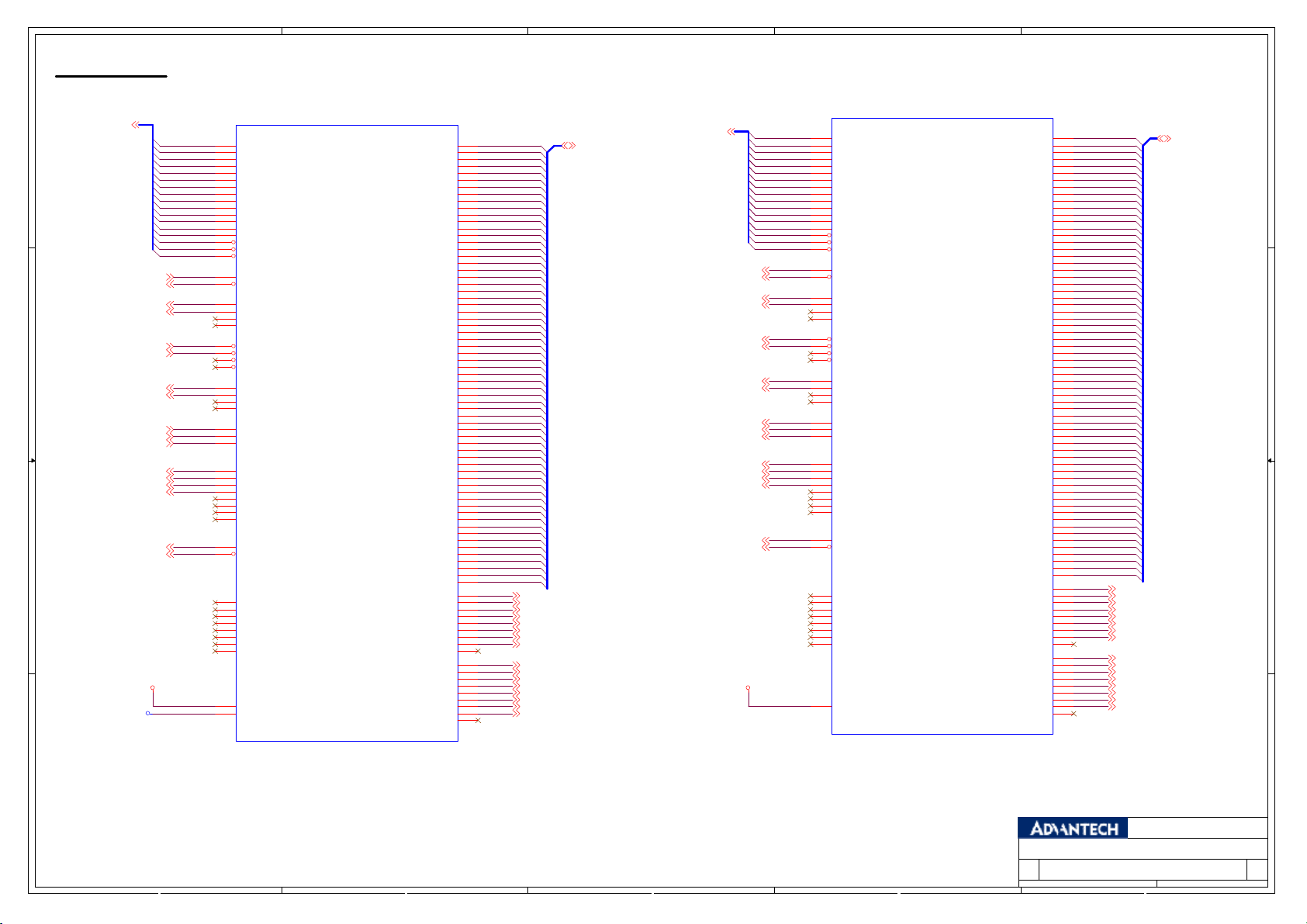

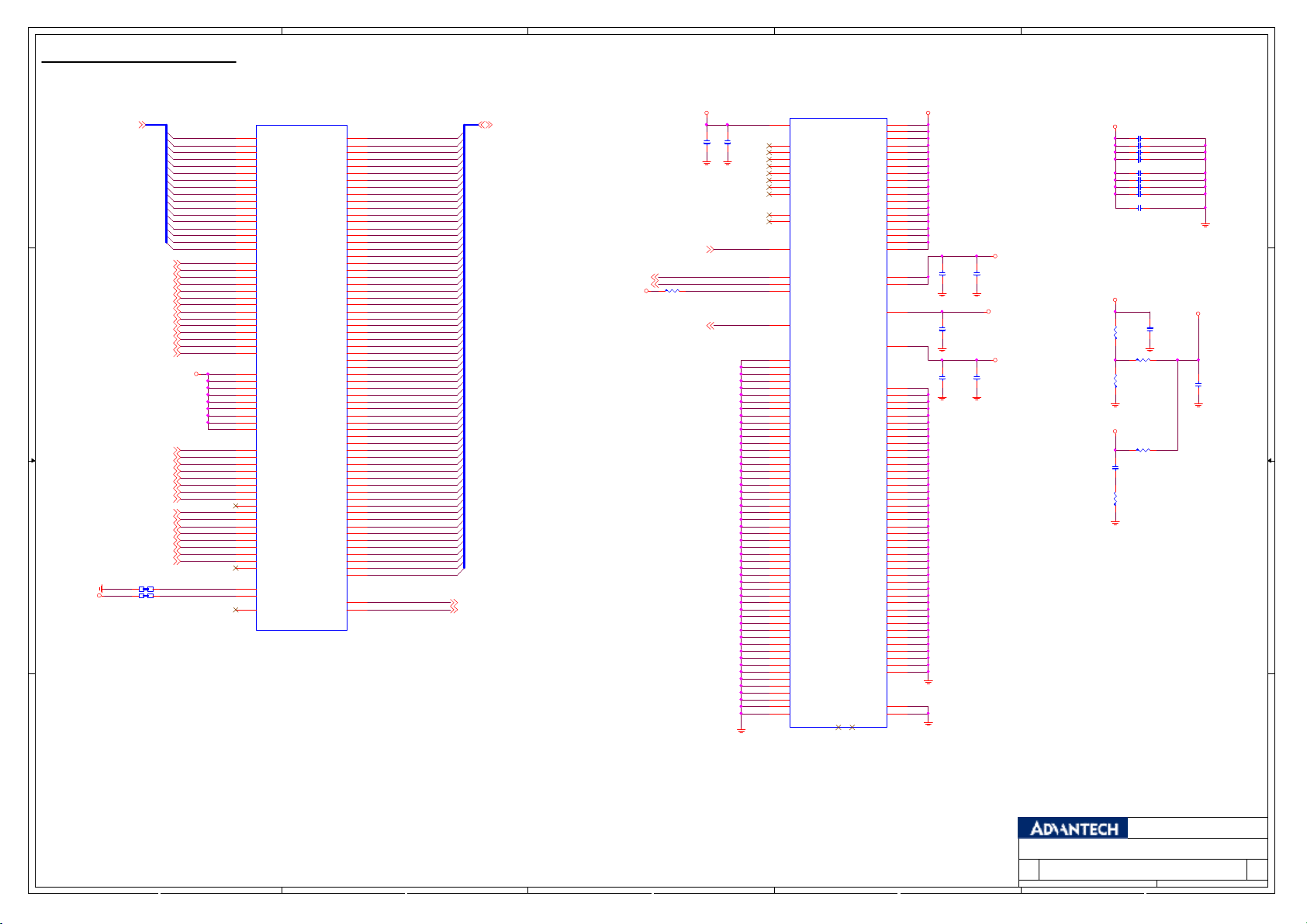

CPU-Memory

5

4

3

2

1

MEM_MA_ADD[16..0](7)

D D

MEM_MA_ACT#(7)

C C

MEM_MA_CLK_H0(7)

MEM_MA_CLK_L0(7)

MEM_MA_CLK_H1(7)

MEM_MA_CLK_L1(7)

B B

MEM_MA_ALERT#(7)

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_ADD16

MEM_MA_BG1(7)

MEM_MA_CKE0(7)

MEM_MA_CKE1(7)

MEM_MA_CS_L0(7)

MEM_MA_CS_L1(7)

MEM_MA_ODT0(7)

MEM_MA_ODT1(7)

MEM_MA_BA0(7)

MEM_MA_BA1(7)

MEM_MA_BG0(7)

MEM_MA_PAR(7)

CPU_CA_VREF_A CPU_DQ_VREF_B

CPU_VREF_DQ_A

TP59

CPU1A

AW15

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

AU18

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

AU17

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

AV19

DDR0_MA[3]

AT19

DDR0_MA[4]

AU20

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

AV20

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

AU21

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

AT20

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

AT22

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

AY14

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

AU22

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

AV22

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

AV12

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

AV14

DDR0_MA[14]/DDR0_CAB[2]/DDR0_WE#

AY11

DDR0_MA[15]/DDR0_CAB[1]/DDR0_CAS#

AW13

DDR0_MA[16]/DDR0_CAB[3]/DDR0_RAS#

AV23

DDR0_BG[1]/DDR0_CAA[9]/DDR0_MA[14]

AU24

DDR0_ACT#/DDR0_CAA[8]/DDR0_MA[15]

AY24

DDR0_CKE[0]

AW24

DDR0_CKE[1]

AV24

DDR0_CKE[2]

AV25

DDR0_CKE[3]

AW12

DDR0_CS#[0]

AU11

DDR0_CS#[1]

AV13

DDR0_CS#[2]

AV10

DDR0_CS#[3]

AW11

DDR0_ODT[0]

AU14

DDR0_ODT[1]

AU12

DDR0_ODT[2]

AY10

DDR0_ODT[3]

AY13

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

AV15

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

AW23

DDR0_BG[0]/DDR0_CAA[5]/DDR0_BA[2]

AW18

DDR0_CKP[0]

AV18

DDR0_CKN[0]

AW17

DDR0_CKP[1]

AY17

DDR0_CKN[1]

AW16

DDR0_CKP[2]

AV16

DDR0_CKN[2]

AT16

DDR0_CKP[3]

AU16

DDR0_CKN[3]

AY15

DDR0_PAR

AT23

DDR0_ALERT#

AU33

DDR0_ECC[0]

AT33

DDR0_ECC[1]

AW33

DDR0_ECC[2]

AV31

DDR0_ECC[3]

AU31

DDR0_ECC[4]

AV33

DDR0_ECC[5]

AW31

DDR0_ECC[6]

AY31

DDR0_ECC[7]

AB40

DDR_VREF_CA

AC40

DDR0_VREF_DQ

LGA1151

ZIF-SOCKET1151

SKYLAKE-S

CHANNEL A

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR0_DQ[32]/DDR0_DQ[16]

DDR0_DQ[33]/DDR0_DQ[17]

DDR0_DQ[34]/DDR0_DQ[18]

DDR0_DQ[35]/DDR0_DQ[19]

DDR0_DQ[36]/DDR0_DQ[20]

DDR0_DQ[37]/DDR0_DQ[21]

DDR0_DQ[38]/DDR0_DQ[22]

DDR0_DQ[39]/DDR0_DQ[23]

DDR0_DQ[40]/DDR0_DQ[24]

DDR0_DQ[41]/DDR0_DQ[25]

DDR0_DQ[42]/DDR0_DQ[26]

DDR0_DQ[43]/DDR0_DQ[27]

DDR0_DQ[44]/DDR0_DQ[28]

DDR0_DQ[45]/DDR0_DQ[29]

DDR0_DQ[46]/DDR0_DQ[30]

DDR0_DQ[47]/DDR0_DQ[31]

DDR1_DQ[0]/DDR0_DQ[32]

DDR1_DQ[1]/DDR0_DQ[33]

DDR1_DQ[2]/DDR0_DQ[34]

DDR1_DQ[3]/DDR0_DQ[35]

DDR1_DQ[4]/DDR0_DQ[36]

DDR1_DQ[5]/DDR0_DQ[37]

DDR1_DQ[6]/DDR0_DQ[38]

DDR1_DQ[7]/DDR0_DQ[39]

DDR1_DQ[8]/DDR0_DQ[40]

DDR1_DQ[9]/DDR0_DQ[41]

DDR1_DQ[10]/DDR0_DQ[42]

DDR1_DQ[11]/DDR0_DQ[43]

DDR1_DQ[12]/DDR0_DQ[44]

DDR1_DQ[13]/DDR0_DQ[45]

DDR1_DQ[14]/DDR0_DQ[46]

DDR1_DQ[15]/DDR0_DQ[47]

DDR1_DQ[32]/DDR0_DQ[48]

DDR1_DQ[33]/DDR0_DQ[49]

DDR1_DQ[34]/DDR0_DQ[50]

DDR1_DQ[35]/DDR0_DQ[51]

DDR1_DQ[36]/DDR0_DQ[52]

DDR1_DQ[37]/DDR0_DQ[53]

DDR1_DQ[38]/DDR0_DQ[54]

DDR1_DQ[39]/DDR0_DQ[55]

DDR1_DQ[40]/DDR0_DQ[56]

DDR1_DQ[41]/DDR0_DQ[57]

DDR1_DQ[42]/DDR0_DQ[58]

DDR1_DQ[43]/DDR0_DQ[59]

DDR1_DQ[44]/DDR0_DQ[60]

DDR1_DQ[45]/DDR0_DQ[61]

DDR1_DQ[46]/DDR0_DQ[62]

DDR1_DQ[47]/DDR0_DQ[63]

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSN[4]/DDR0_DQSN[2]

DDR0_DQSN[5]/DDR0_DQSN[3]

DDR1_DQSN[0]/DDR0_DQSN[4]

DDR1_DQSN[1]/DDR0_DQSN[5]

DDR1_DQSN[4]/DDR0_DQSN[6]

DDR1_DQSN[5]/DDR0_DQSN[7]

DDR0_DQSN[8]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[4]/DDR0_DQSP[2]

DDR0_DQSP[5]/DDR0_DQSP[3]

DDR1_DQSP[0]/DDR0_DQSP[4]

DDR1_DQSP[1]/DDR0_DQSP[5]

DDR1_DQSP[4]/DDR0_DQSP[6]

DDR1_DQSP[5]/DDR0_DQSP[7]

DDR0_DQSP[8]

MEM_MA_DATA0

AE38

MEM_MA_DATA1

AE37

MEM_MA_DATA2

AG38

MEM_MA_DATA3

AG37

MEM_MA_DATA4

AE39

MEM_MA_DATA5

AE40

MEM_MA_DATA6

AG39

MEM_MA_DATA7

AG40

MEM_MA_DATA8

AJ38

MEM_MA_DATA9

AJ37

MEM_MA_DATA10

AL38

MEM_MA_DATA11

AL37

MEM_MA_DATA12

AJ40

MEM_MA_DATA13

AJ39

MEM_MA_DATA14

AL39

MEM_MA_DATA15

AL40

MEM_MA_DATA16

AN38

MEM_MA_DATA17

AN40

MEM_MA_DATA18

AR38

MEM_MA_DATA19

AR37

MEM_MA_DATA20

AN39

MEM_MA_DATA21

AN37

MEM_MA_DATA22

AR39

MEM_MA_DATA23

AR40

MEM_MA_DATA24

AW37

MEM_MA_DATA25

AU38

MEM_MA_DATA26

AV35

MEM_MA_DATA27

AW35

MEM_MA_DATA28

AU37

MEM_MA_DATA29

AV37

MEM_MA_DATA30

AT35

MEM_MA_DATA31

AU35

MEM_MA_DATA32

AY8

MEM_MA_DATA33

AW8

MEM_MA_DATA34

AV6

MEM_MA_DATA35

AU6

MEM_MA_DATA36

AU8

MEM_MA_DATA37

AV8

MEM_MA_DATA38

AW6

MEM_MA_DATA39

AY6

MEM_MA_DATA40

AY4

MEM_MA_DATA41

AV4

MEM_MA_DATA42

AT1

MEM_MA_DATA43

AT2

MEM_MA_DATA44

AV3

MEM_MA_DATA45

AW4

MEM_MA_DATA46

AT4

MEM_MA_DATA47

AT3

MEM_MA_DATA48

AP2

MEM_MA_DATA49

AM4

MEM_MA_DATA50

AP3

MEM_MA_DATA51

AM3

MEM_MA_DATA52

AP4

MEM_MA_DATA53

AM2

MEM_MA_DATA54

AP1

MEM_MA_DATA55

AM1

MEM_MA_DATA56

AK3

MEM_MA_DATA57

AH1

MEM_MA_DATA58

AK4

MEM_MA_DATA59

AH2

MEM_MA_DATA60

AH4

MEM_MA_DATA61

AK2

MEM_MA_DATA62

AH3

MEM_MA_DATA63

AK1

AF39

AK39

AP39

AU36

AW7

AU3

AN3

AJ3

AU32

AF38

AK38

AP38

AV36

AV7

AU2

AN2

AJ2

AV32

MEM_MA_DQS_L0(7)

MEM_MA_DQS_L1(7)

MEM_MA_DQS_L2(7)

MEM_MA_DQS_L3(7)

MEM_MA_DQS_L4(7)

MEM_MA_DQS_L5(7)

MEM_MA_DQS_L6(7)

MEM_MA_DQS_L7(7)

MEM_MA_DQS_H0(7)

MEM_MA_DQS_H1(7)

MEM_MA_DQS_H2(7)

MEM_MA_DQS_H3(7)

MEM_MA_DQS_H4(7)

MEM_MA_DQS_H5(7)

MEM_MA_DQS_H6(7)

MEM_MA_DQS_H7(7)

MEM_MA_DATA[63..0](7)

MEM_MB_ADD[16..0](8)

MEM_MB_CLK_H0(8)

MEM_MB_CLK_L0(8)

MEM_MB_CLK_H1(8)

MEM_MB_CLK_L1(8)

MEM_MB_ALERT#(8)

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_ADD16

MEM_MB_BG1(8)

MEM_MB_ACT#(8)

MEM_MB_CKE0(8)

MEM_MB_CKE1(8)

MEM_MB_CS_L0(8)

MEM_MB_CS_L1(8)

MEM_MB_ODT0(8)

MEM_MB_ODT1(8)

MEM_MB_BA0(8)

MEM_MB_BA1(8)

MEM_MB_BG0(8)

MEM_MB_PAR(8)

CPU1B

AL19

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

AL22

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

AM22

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

AM23

DDR1_MA[3]

AP23

DDR1_MA[4]

AL23

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

AW26

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

AY26

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

AU26

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

AW27

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

AP18

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

AU27

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

AV27

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

AR15

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

AL17

DDR1_MA[14]/DDR1_CAB[2]/DDR1_WE#

AP16

DDR1_MA[15]/DDR1_CAB[1]/DDR1_CAS#

AN18

DDR1_MA[16]/DDR1_CAB[3]/DDR1_RAS#

AY28

DDR1_BG[1]/DDR1_CAA[9]/DDR1_MA[14]

AU28

DDR1_ACT#/DDR1_CAA[8]/DDR1_MA[15]

AY29

DDR1_CKE[0]

AV29

DDR1_CKE[1]

AW29

DDR1_CKE[2]

AU29

DDR1_CKE[3]

AP17

DDR1_CS#[0]

AN15

DDR1_CS#[1]

AN17

DDR1_CS#[2]

AM15

DDR1_CS#[3]

AM16

DDR1_ODT[0]

AL16

DDR1_ODT[1]

AP15

DDR1_ODT[2]

AL15

DDR1_ODT[3]

AL18

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

AM18

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

AW28

DDR1_BG[0]/DDR1_CAA[5]/DDR1_BA[2]

AM20

DDR1_CKP[0]

AM21

DDR1_CKN[0]

AP22

DDR1_CKP[1]

AP21

DDR1_CKN[1]

AN20

DDR1_CKP[2]

AN21

DDR1_CKN[2]

AP19

DDR1_CKP[3]

AP20

DDR1_CKN[3]

AL20

DDR1_PAR

AY25

DDR1_ALERT#

AR25

DDR1_ECC[0]

AR26

DDR1_ECC[1]

AM26

DDR1_ECC[2]

AM25

DDR1_ECC[3]

AP26

DDR1_ECC[4]

AP25

DDR1_ECC[5]

AL25

DDR1_ECC[6]

AL26

DDR1_ECC[7]

AC39

DDR1_VREF_DQ

LGA1151

ZIF-SOCKET1151

SKYLAKE-S

CHANNEL B

DDR0_DQ[16]/DDR1_DQ[0]

DDR0_DQ[17]/DDR1_DQ[1]

DDR0_DQ[18]/DDR1_DQ[2]

DDR0_DQ[19]/DDR1_DQ[3]

DDR0_DQ[20]/DDR1_DQ[4]

DDR0_DQ[21]/DDR1_DQ[5]

DDR0_DQ[22]/DDR1_DQ[6]

DDR0_DQ[23]/DDR1_DQ[7]

DDR0_DQ[24]/DDR1_DQ[8]

DDR0_DQ[25]/DDR1_DQ[9]

DDR0_DQ[26]/DDR1_DQ[10]

DDR0_DQ[27]/DDR1_DQ[11]

DDR0_DQ[28]/DDR1_DQ[12]

DDR0_DQ[29]/DDR1_DQ[13]

DDR0_DQ[30]/DDR1_DQ[14]

DDR0_DQ[31]/DDR1_DQ[15]

DDR0_DQ[48]/DDR1_DQ[16]

DDR0_DQ[49]/DDR1_DQ[17]

DDR0_DQ[50]/DDR1_DQ[18]

DDR0_DQ[51]/DDR1_DQ[19]

DDR0_DQ[52]/DDR1_DQ[20]

DDR0_DQ[53]/DDR1_DQ[21]

DDR0_DQ[54]/DDR1_DQ[22]

DDR0_DQ[55]/DDR1_DQ[23]

DDR0_DQ[56]/DDR1_DQ[24]

DDR0_DQ[57]/DDR1_DQ[25]

DDR0_DQ[58]/DDR1_DQ[26]

DDR0_DQ[59]/DDR1_DQ[27]

DDR0_DQ[60]/DDR1_DQ[28]

DDR0_DQ[61]/DDR1_DQ[29]

DDR0_DQ[62]/DDR1_DQ[30]

DDR0_DQ[63]/DDR1_DQ[31]

DDR1_DQ[16]/DDR1_DQ[32]

DDR1_DQ[17]/DDR1_DQ[33]

DDR1_DQ[18]/DDR1_DQ[34]

DDR1_DQ[19]/DDR1_DQ[35]

DDR1_DQ[20]/DDR1_DQ[36]

DDR1_DQ[21]/DDR1_DQ[37]

DDR1_DQ[22]/DDR1_DQ[38]

DDR1_DQ[23]/DDR1_DQ[39]

DDR1_DQ[24]/DDR1_DQ[40]

DDR1_DQ[25]/DDR1_DQ[41]

DDR1_DQ[26]/DDR1_DQ[42]

DDR1_DQ[27]/DDR1_DQ[43]

DDR1_DQ[28]/DDR1_DQ[44]

DDR1_DQ[29]/DDR1_DQ[45]

DDR1_DQ[30]/DDR1_DQ[46]

DDR1_DQ[31]/DDR1_DQ[47]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR0_DQSN[2]/DDR1_DQSN[0]

DDR0_DQSN[3]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[2]

DDR0_DQSN[7]/DDR1_DQSN[3]

DDR1_DQSN[2]/DDR1_DQSN[4]

DDR1_DQSN[3]/DDR1_DQSN[5]

DDR0_DQSP[2]/DDR1_DQSP[0]

DDR0_DQSP[3]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[2]

DDR0_DQSP[7]/DDR1_DQSP[3]

DDR1_DQSP[2]/DDR1_DQSP[4]

DDR1_DQSP[3]/DDR1_DQSP[5]

DDR1_DQ[63]

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSN[8]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

MEM_MB_DATA0

AD34

MEM_MB_DATA1

AD35

MEM_MB_DATA2

AG35

MEM_MB_DATA3

AH35

MEM_MB_DATA4

AE35

MEM_MB_DATA5

AE34

MEM_MB_DATA6

AG34

MEM_MB_DATA7

AH34

MEM_MB_DATA8

AK35

MEM_MB_DATA9

AL35

MEM_MB_DATA10

AK32

MEM_MB_DATA11

AL32

MEM_MB_DATA12

AK34

MEM_MB_DATA13

AL34

MEM_MB_DATA14

AK31

MEM_MB_DATA15

AL31

MEM_MB_DATA16

AP35

MEM_MB_DATA17

AN35

MEM_MB_DATA18

AN32

MEM_MB_DATA19

AP32

MEM_MB_DATA20

AN34

MEM_MB_DATA21

AP34

MEM_MB_DATA22

AN31

MEM_MB_DATA23

AP31

MEM_MB_DATA24

AL29

MEM_MB_DATA25

AM29

MEM_MB_DATA26

AP29

MEM_MB_DATA27

AR29

MEM_MB_DATA28

AM28

MEM_MB_DATA29

AL28

MEM_MB_DATA30

AR28

MEM_MB_DATA31

AP28

MEM_MB_DATA32

AR12

MEM_MB_DATA33

AP12

MEM_MB_DATA34

AM13

MEM_MB_DATA35

AL13

MEM_MB_DATA36

AR13

MEM_MB_DATA37

AP13

MEM_MB_DATA38

AM12

MEM_MB_DATA39

AL12

MEM_MB_DATA40

AP10

MEM_MB_DATA41

AR10

MEM_MB_DATA42

AR7

MEM_MB_DATA43

AP7

MEM_MB_DATA44

AR9

MEM_MB_DATA45

AP9

MEM_MB_DATA46

AR6

MEM_MB_DATA47

AP6

MEM_MB_DATA48

AM10

MEM_MB_DATA49

AL10

MEM_MB_DATA50

AM7

MEM_MB_DATA51

AL7

MEM_MB_DATA52

AM9

MEM_MB_DATA53

AL9

MEM_MB_DATA54

AM6

MEM_MB_DATA55

AL6

MEM_MB_DATA56

AJ6

MEM_MB_DATA57

AJ7

MEM_MB_DATA58

AE6

MEM_MB_DATA59

AF7

MEM_MB_DATA60

AH7

MEM_MB_DATA61

AH6

MEM_MB_DATA62

AE7

MEM_MB_DATA63

AF6

AF34

AK33

AN33

AN29

AN13

AR8

AM8

AG6

AN26

AF35

AL33

AP33

AN28

AN12

AP8

AL8

AG7

AN25

MEM_MB_DQS_L0(8)

MEM_MB_DQS_L1(8)

MEM_MB_DQS_L2(8)

MEM_MB_DQS_L3(8)

MEM_MB_DQS_L4(8)

MEM_MB_DQS_L5(8)

MEM_MB_DQS_L6(8)

MEM_MB_DQS_L7(8)

MEM_MB_DQS_H0(8)

MEM_MB_DQS_H1(8)

MEM_MB_DQS_H2(8)

MEM_MB_DQS_H3(8)

MEM_MB_DQS_H4(8)

MEM_MB_DQS_H5(8)

MEM_MB_DQS_H6(8)

MEM_MB_DQS_H7(8)

MEM_MB_DATA[63..0](8)

SOCKET PN N12-151A010-L06

A A

Title

Title

Title

CPU-Memory

CPU-Memory

CPU-Memory

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

DMS-SA30

DMS-SA30

DMS-SA30

10

10

4 35Friday, March 31, 2017

4 35Friday, March 31, 2017

1

4 35Friday, March 31, 2017

10

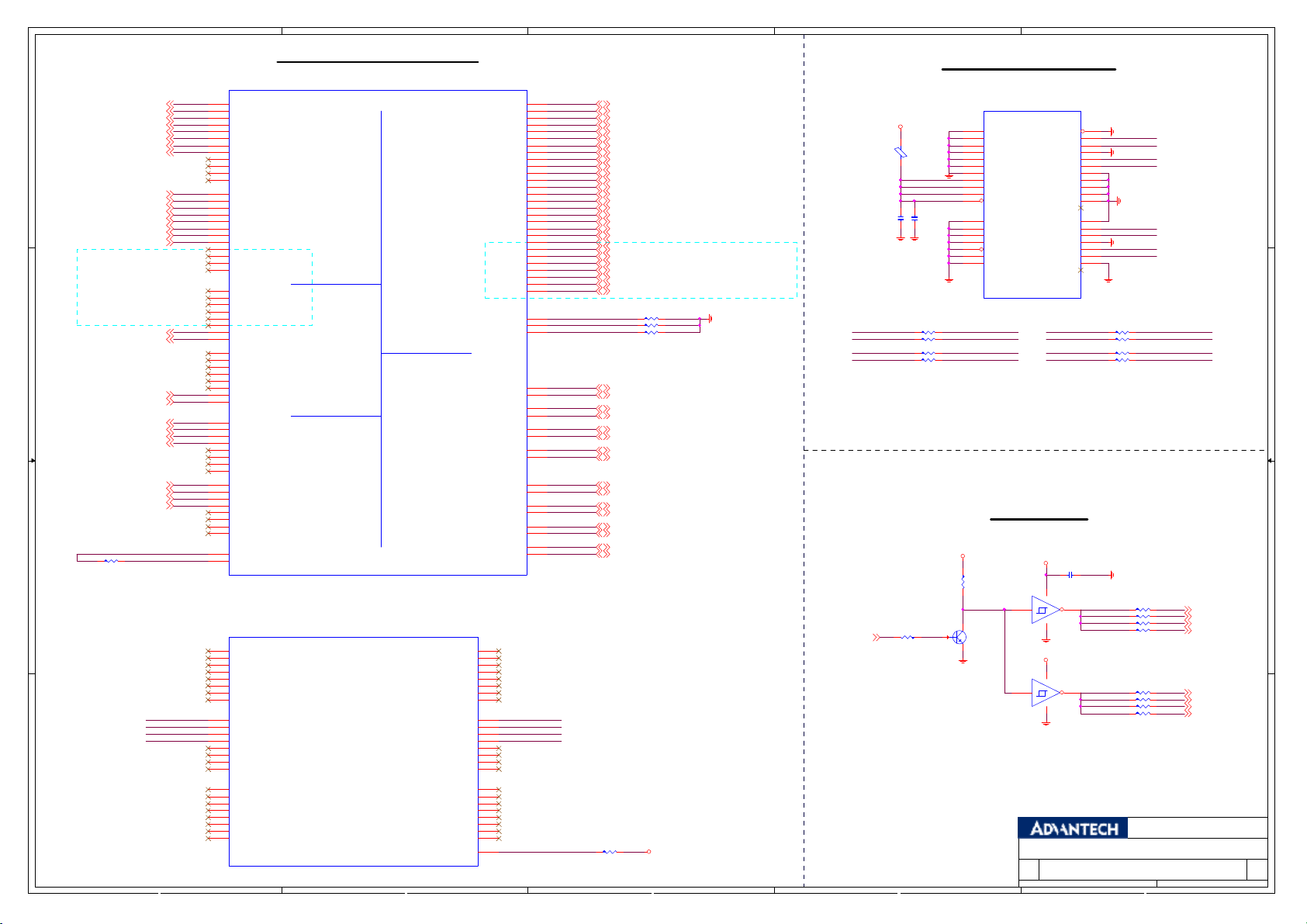

Page 5

CPU-Power

Vinafix.com

5

4

3

2

1

VCCP VCCP

CPU1G

SKYLAKE-S

D D

C C

B B

A25

A26

A27

A28

A29

A30

B25

B27

B29

B31

B32

B33

B34

B35

B36

B37

C25

C26

C27

C28

C29

C30

C32

C34

C36

D25

D27

D29

D31

D32

D33

D34

D35

D36

E24

E25

E26

E27

E28

E29

E30

E32

E34

E36

F23

F24

F25

F27

F29

F31

G30

G32

H22

H23

H25

H27

H29

H31

AJ11

AJ13

AJ15

AJ17

AJ19

AJ21

VCC-001

VCC-002

VCC-003

VCC-004

VCC-005

VCC-006

VCC-007

VCC-008

VCC-009

VCC-010

VCC-011

VCC-012

VCC-013

VCC-014

VCC-015

VCC-016

VCC-017

VCC-018

VCC-019

VCC-020

VCC-021

VCC-022

VCC-023

VCC-024

VCC-025

VCC-026

VCC-027

VCC-028

VCC-029

VCC-030

VCC-031

VCC-032

VCC-033

VCC-034

VCC-035

VCC-036

VCC-037

VCC-038

VCC-039

VCC-040

VCC-041

VCC-042

VCC-043

VCC-044

VCC-045

VCC-046

VCC-047

VCC-048

VCC-049

VCC-050

VCC-051

VCC-052

VCC-053

VCC-054

VCC-055

VCC-056

VCC-057

VCC-058

VCC-059

VCC-060

VCC-061

VCC-062

VCC-063

VCC-064

LGA1151

ZIF-SOCKET1151

VCC-128

VCC-127

VCC-126

VCC-125

VCC-124

VCC-123

VCC-122

VCC-121

VCC-120

VCC-119

VCC-118

VCC-117

VCC-116

VCC-115

VCC-114

VCC-113

VCC-112

VCC-111

VCC-110

VCC-109

VCC-108

VCC-107

VCC-106

VCC-105

VCC-104

VCC-103

VCC-102

VCC-101

VCC-100

VCC-099

VCC-098

VCC-097

VCC-096

VCC-095

VCC-094

VCC-093

VCC-092

VCC-091

VCC-090

VCC-089

VCC-088

VCC-087

VCC-086

VCC-085

VCC-084

VCC-083

VCC-082

VCC-081

VCC-080

VCC-079

VCC-078

VCC-077

VCC-076

VCC-075

VCC-074

VCC-073

VCC-072

VCC-071

VCC-070

VCC-069

VCC-068

VCC-067

VCC-066

VCC-065

H32

J21

F32

F33

F34

G23

G24

G25

G26

G27

G28

G29

J22

J23

J24

J25

J26

J27

J28

J29

J30

J31

K16

K18

K20

K21

K23

K25

K27

K29

K31

L14

L15

L16

L17

L18

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

M13

M14

M16

M18

M20

M22

M24

M26

M28

M30

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

VCCGT VCCGT VCCSA

CPU1H

VCCGT-01

VCCGT-02

VCCGT-03

VCCGT-04

VCCGT-05

VCCGT-06

VCCGT-07

G36

VCCGT-08

G37

VCCGT-09

G38

VCCGT-10

G39

VCCGT-11

G40

VCCGT-12

H36

VCCGT-13

H38

VCCGT-14

H40

VCCGT-15

J36

VCCGT-16

J37

VCCGT-17

J38

VCCGT-18

J39

VCCGT-19

J40

VCCGT-20

K36

VCCGT-21

K38

VCCGT-22

K40

VCCGT-23

L34

VCCGT-24

L35

VCCGT-25

L36

VCCGT-26

L37

VCCGT-27

L38

VCCGT-28

L39

VCCGT-29

L40

VCCGT-30

M33

VCCGT-31

M34

VCCGT-32

M36

VCCGT-33

M38

VCCGT-34

M40

VCCGT-35

N34

VCCGT-36

N35

VCCGT-37

N36

VCCGT-38

N40

VCCGT-39

P33

VCCGT-40

LGA1151

ZIF-SOCKET1151

SKYLAKE-S

SLP_S4_CTL(26)

N39

VCCGT-80

N38

VCCGT-79

N37

VCCGT-78

R34

VCCGT-77

P40

VCCGT-76

P38

VCCGT-75

P36

VCCGT-74

P34

VCCGT-73

R35

VCCGT-72

R36

VCCGT-71

R37

VCCGT-70

R38

VCCGT-69

R39

VCCGT-68

R40

VCCGT-67

T33

VCCGT-66

T34

VCCGT-65

T36

VCCGT-64

T38

VCCGT-63

T40

VCCGT-62

U34

VCCGT-61

U35

VCCGT-60

U36

VCCGT-59

U37

VCCGT-58

U38

VCCGT-57

U39

VCCGT-56

U40

VCCGT-55

V33

VCCGT-54

V34

VCCGT-53

V36

VCCGT-52

V38

VCCGT-51

V40

VCCGT-50

W34

VCCGT-49

W35

VCCGT-48

W36

VCCGT-47

W37

VCCGT-46

W38

VCCGT-45

Y33

VCCGT-44

Y34

VCCGT-43

Y36

VCCGT-42

Y38

VCCGT-41

+5V A +5V SU S

R716

10K/4

G2

D1

SLP_S4#(7,12,17,22,24,31)

G1

Q59

2N7002DW_SOT363

S1

VCCIO

For 4+4e

R8 06

X_0R/6

D2

S2

AA34

AA35

AA36

AA37

AA38

AB33

AB34

AA7

AB6

AB7

AB8

AC7

AC8

N7

P7

R7

T7

U7

Y6

Y7

Y8

W7

V7

AA6

AK11

AK14

AK24

AJ23

M8

P8

T8

U8

W8

F35

G34

G35

H33

H34

J33

J35

K32

K34

L31

L33

M32

R718

10K/4

VCCST_PLL_EN

CPU1I

VCCSA-01

VCCSA-02

VCCSA-03

1.05V/12.3A

VCCSA-04

VCCSA-05

VCCSA-06

VCCSA-07

VCCSA-08

VCCSA-09

VCCSA-10

VCCSA-11

VCCSA-12

VCCSA-13

VCCSA-14

VCCSA-15

VCCSA-16

VCCSA-17

VCCIO-01

0.95V/5.5A

VCCIO-02

VCCIO-03

VCCIO-04

VCCIO-05

VCCIO-06

VCCIO-07

VCCIO-08

VCCIO-09

VCCGTX-01

VCCGTX-02

VCCGTX-03

VCCGTX-04

VCCGTX-05

VCCGTX-06

VCCGTX-07

VCCGTX-08

VCCGTX-09

VCCGTX-10

VCCGTX-11

VCCGTX-12

LGA1151

ZIF-SOCKET1151

PCH_1VSB

SKYLAKE-S

1.2V/2.0A

1V/3A

1V/3.3A

VCC_OPC_1P8-01

1.8V/50mA

VCC_OPC_1P8-02

1V/120mA

R7 23 X_0R0805

D

G

Q60

S

N-P3203CMG_SOT23

VDDQ-01

VDDQ-02

VDDQ-03

VDDQ-04

VDDQ-05

VDDQ-06

VDDQ-07

VDDQ-08

VDDQ-09

VDDQ-10

VDDQ-11

VDDQ-12

VDDQ-13

VDDQ-14

VDDQ-15

VDDQ-16

VCCPLL_OC

VCCOPC-01

VCCOPC-02

VCCOPC-03

VCCOPC-04

VCCOPC-05

VCCEOPIO-01

VCCEOPIO-02

VCCST-01

VCCST-02

VCCPLL

1V/130mA

VCC_DDR

AT18

AT21

AU13

AU15

AU19

AU23

AV11

AV17

AV21

AW10

AW14

AW25

AY12

AY16

AY18

AY23

AJ9

AJ30

AJ27

AJ28

AJ29

AK27

For 4+4e

AJ25

AJ26

AB37

AB38

V5

V6

V4

C488

C22u6.3X8

TOP SIDE SOCKET CAVITY

VCCPLL_OC

VCCST

VCCSTG

VCCPLL

VCCST

VCC_DDR

R300 0R/4

VCCIO

C486 C22u6.3X6

C494 C22u6.3X6

C516 C22u6.3X6

C523 C22u6.3X6

TOP SIDE SOCKET CAVITY

VCC_DDR

TP4

R8 07

X_0R/6

R798

X_0R/6

VCCSTG VCCST

R818

X_0R/6

VCCPLL VCCST

R788 0R/6

C481 C1u6.3X4

TOP SIDE SOCKET CAVITY

R792 0R/6

C490 C1u6.3X4

TOP SIDE SOCKET CAVITY

PDG, Page447:

Figure 41-3.Primary Debug Port-XDP_PRESENT# Connectivity

NOTE1:

VCCST/VCCSTG Power Override Mechanism is for Merged XDP usage model.

WhenXDP is pluggedin, VCCST/VCCSTGwill be forced on. This is to support PCH Sx

debug. If onlyS0 debug is required, the override mechanism is not requiredunless C10

debug support is also needed.

NOTE 2:

XDP_PRESENT#/

XDP_PRESENT_PCH connection

to 2 p in header on some Intel

reference designis optional. It is

onlyuse d forIntel pow er- o n.

NOTE 3:

Use Existing Override

Logic. Don't have to

addnew logic, just

connect Override Logic

to the VccST-G/-U

po wer gat ing logic

alreadyin the board

Note 4… just a representation…

maybe be FETorIntegratedLoad Switch

Close to CPU

Pins.

C478

C0.1u6.3X4

C480

C0.1u6.3X4

A A

Ti t l e

Ti t l e

Ti t l e

CPU-Power

CPU-Power

CPU-Power

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

DMS-SA30

DMS-SA30

DMS-SA30

5 35Friday, March 31, 2017

5 35Friday, March 31, 2017

1

5 35Friday, March 31, 2017

10

10

10

Page 6

5

AR24

AR31

AR32

AR34

AR35

AR36

AR4

AR5

AR33

AR27

AR3

CPU1J

A7

VSS-001

A11

VSS-002

A13

VSS-003

A15

VSS-004

A17

VSS-005

A24

D D

C C

B B

AA33

AB39

AC33

AC34

AC35

AD33

AD36

AD37

AD38

AD39

AD40

AE33

AE36

AF33

AF36

AF37

AF40

AG33

AG36

AH33

AH36

AH37

AH38

AH39

AH40

AJ31

AJ32

AJ33

AJ34

AJ35

AG1

AG2

AG3

AG4

AG5

AG8

AH5

AH8

AA3

AA8

AB5

AC3

AC6

AD1

AD4

AD6

AD7

AD8

AE3

AE5

AE8

AF1

AF5

AF8

AJ1

AJ4

AJ5

AJ8

VSS-006

VSS-007

VSS-008

VSS-009

VSS-010

VSS-011

VSS-012

VSS-013

VSS-014

VSS-015

VSS-016

VSS-017

VSS-018

VSS-019

VSS-020

VSS-021

VSS-022

VSS-023

VSS-024

VSS-025

VSS-026

VSS-027

VSS-028

VSS-029

VSS-030

VSS-031

VSS-032

VSS-033

VSS-034

VSS-035

VSS-036

VSS-037

VSS-038

VSS-039

VSS-040

VSS-041

VSS-042

VSS-043

VSS-044

VSS-045

VSS-046

VSS-047

VSS-048

VSS-049

VSS-050

VSS-051

VSS-052

VSS-053

VSS-054

VSS-055

VSS-056

VSS-057

VSS-058

VSS-059

VSS-060

VSS-061

VSS-062

VSS-063

VSS-064

LGA1151

AR30

VSS-268

VSS-264

VSS-267

VSS-266

VSS-265

VSS-65

VSS-70

VSS-69

VSS-68

VSS-67

VSS-66

AK9

AK8

AK7

AK6

AK5

AJ36

AK10

AT9

AT8

AT7

AT6

AT5

AT40

AT39

AT38

AT37

AT36

AT34

AT32

AT31

AT30

AT29

AT28

AT27

AT26

AT25

AT24

AT17

AT14

AT13

VSS-263

VSS-261

VSS-260

VSS-259

VSS-258

VSS-257

VSS-262

VSS-256

VSS-255

VSS-254

VSS-253

VSS-252

VSS-251

VSS-250

VSS-249

VSS-248

VSS-247

VSS-246

VSS-245

VSS-244

VSS-243

VSS-242

VSS-241

VSS-240

VSS-239

VSS-238

VSS-237

VSS-236

VSS-235

VSS-234

SKYLAKE-S

GND

VSS-71

VSS-72

VSS-73

VSS-74

VSS-75

VSS-76

VSS-77

VSS-78

VSS-79

VSS-80

VSS-81

VSS-82

VSS-83

VSS-84

VSS-85

VSS-86

VSS-87

VSS-88B6VSS-89

VSS-90

VSS-91

VSS-92

VSS-93

VSS-94

VSS-95

VSS-96

VSS-97

VSS-98

VSS-99

VSS-100

J10

B24

B26

B28

B30

C12

C14

C16

C18

AK12

AK13

AK15

AK16

AK17

AK18

AK19

AK20

AK23

AK25

AK26

AK28

C20

J12

C22

C24

C31

C33

C35

4

AK29

AK30

AK36

AK37

AT12

AT11

AT10

AU7

AU5

AU4

AU34

AU30

AU25

AU1

AV9

AV5

AV38

AV34

AV30

AV28

AV26

AV2

AW32

AW30

AW3

AW34

AW36

AW5

AW9

AY27

AY30

AY5

VSS-233

VSS-232

VSS-231

VSS-230

VSS-229

VSS-228

VSS-227

VSS-226

VSS-225

VSS-224

VSS-223

VSS-222

VSS-221

VSS-220

VSS-219

VSS-218

VSS-217

VSS-216

VSS-215

VSS-214

VSS-213

VSS-212

VSS-211

VSS-210

VSS-209

VSS-208

VSS-207

VSS-108K1VSS-109

VSS-113

VSS-112

VSS-111

VSS-104J3VSS-105

J32

VSS-110

VSS-106

VSS-107

J6

J34

K14

K24

K22

K19

K17

K15

VSS-101

VSS-102

VSS-103

J16

J18

J20

VSS-120

VSS-119

VSS-118

VSS-117

VSS-116

VSS-115

VSS-114

K37

K35

K33

K30

K28

K26

AR21

VSS-127

VSS-126

VSS-125

VSS-124

VSS-123

VSS-122

VSS-121

AR2

AR14

AR16

AR17

AR18

AR19

AR20

AK40

AY7

AY9

VSS-203

VSS-202

VSS-201

VSS-200

VSS-206

VSS-128

VSS-199

VSS-205

VSS-204

VSS-198

VSS-197

VSS-196

VSS-195

VSS-194

VSS-193

VSS-192

VSS-191

VSS-190

VSS-189

VSS-188

VSS-187

VSS-186

VSS-185

VSS-184

VSS-183

VSS-182

VSS-181

VSS-180

VSS-179

VSS-178

VSS-177

VSS-176

VSS-175

VSS-174

VSS-173

VSS-172

VSS-171

VSS-170

VSS-169

VSS-168

VSS-167

VSS-166

VSS-165

VSS-164

VSS-163

VSS-162

VSS-161

VSS-160

VSS-159

VSS-158

VSS-157

VSS-156

VSS-155

VSS-154

VSS-153

VSS-152

VSS-151

VSS-150

VSS-149

VSS-148

VSS-147

VSS-146

VSS-145

VSS-144

VSS-143

VSS-142

VSS-141

VSS-140

VSS-139

VSS-138

VSS-137

VSS-136

VSS-135

VSS-130

VSS-129

VSS-134

VSS-133

VSS-132L9VSS-131

ZIF-SOCKET1151

L6

L13

L32

AR1

AR11

AL1

AL11

AL14

AL2

AL21

AL24

AL27

AL3

AL30

AL36

AL4

AL5

AM35

AM34

AM33

AM32

AM31

AM30

AM27

AM24

AM19

AM17

AM14

AM11

AM36

AM37

AM38

AM39

AM40

AM5

AN1

AN10

AN11

AN14

AN16

AN19

AN22

AN23

AN24

AN27

AN30

AN36

AN4

AN5

AN6

AN7

AN8

AN9

AP11

AP14

AP24

AP27

AP30

AP36

AP37

AP40

AP5

K39

K4

K7

L3

L11

M1

M4

3

CPU-GND

2

M7

M10

M12

M15

M17

M19

M21

M23

M25

M27

M29

M35

M37

M39

N3

N33

N6

N8

P1

P35

P37

P39

P4

R3

R33

R6

R8

T1

T35

T37

T39

T4

U3

U33

U6

V1

V35

V37

V39

V8

W3

W33

W6

Y35

Y37

Y5

C10

C8

C5

C37

D37

D30

D28

D26

D24

D4

D39

D7

E13

E11

CPU1K

SKYLAKE-S

VSS-269

VSS-270

VSS-271

VSS-272

VSS-273

VSS-274

VSS-275

VSS-276

VSS-277

VSS-278

VSS-279

VSS-280

VSS-281

VSS-282

VSS-283

VSS-284

VSS-285

VSS-286

VSS-287

VSS-288

VSS-289

VSS-290

VSS-291

VSS-292

VSS-293

VSS-294

VSS-295

VSS-296

GND

VSS-297

VSS-298

VSS-299

VSS-300

VSS-301

VSS-302

VSS-303

VSS-304

VSS-305

VSS-306

VSS-307

VSS-308

VSS-309

VSS-310

VSS-311

VSS-312

VSS-313

VSS-314

VSS-315

VSS-316

VSS-317

VSS-318

VSS-319

VSS-320

VSS-321

VSS-322

VSS-323

VSS-324

VSS-325

VSS-326

VSS-327

VSS-328

LGA1151

ZIF-SOCKET1151

VSS-329

VSS-330

VSS-331

VSS-332

VSS-333

VSS-334

VSS-335

VSS-336

VSS-337

VSS-338

VSS-339

VSS-340

VSS-341

VSS-342

VSS-343

VSS-344

VSS-345

VSS-346

VSS-347

VSS-348

VSS-349

VSS-350

VSS-351

VSS-352

VSS-353

VSS-354

VSS-355

VSS-356

VSS-357

VSS-358

VSS-359

VSS-360

VSS-361

VSS-362

VSS-363

VSS-364

VSS-365

VSS-366

VSS-367

VSS-368

VSS-369

VSS-370

VSS-371

VSS-AT15

VSS-AR23

VSS-AR22

VSS_NCTF-1

VSS_NCTF-2

VSS_NCTF-3

VSS_NCTF-4

E15

E17

E19

E21

E23

E3

E31

E33

E35

E37

E6

E9

F1

F10

F22

F26

F28

F30

F4

F40

F7

G11

G13

G15

G17

G19

G22

G3

G31

G33

G6

H1

H21

H24

H26

H28

H30

H35

H37

H39

H4

H7

H9

AT15

AR23

AR22

D40

C2

B38

A4

1

CPU-XDP

Defensive Design

R236 0R/4

R237 51R/4

R231 0R/4

R233 51R/4

R229

51R/4

R230 0R/4

R234 0R/4

R226 0R/4

VCCST

R235

X_1K/4

PCH_JTAGX(12)

H_TRST_R#(12)

PCH_TDO(12)

PCH_TDI(12)

PCH_TMS(12)

3

Place close to PCH

PCH_TCK(12)

PCH_TCK

PCH_TDO

PCH_TDI

PCH_TMS

R429 X_51R/4

R143 51R/4

R144 51R/4

R145 51R/4R406 X_1K/4

VCCST

VCCST

VCCST

Title

Title

Title

CPU-GND/XDP

CPU-GND/XDP

CPU-GND/XDP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

DMS-SA30

DMS-SA30

DMS-SA30

10

10

6 35Friday, March 31, 2017

6 35Friday, March 31, 2017

1

6 35Friday, March 31, 2017

10

+3VSUS

All Seial&PD resistor

H_TRST#(3)

H_TCK(3)

H_TDO(3)

H_TDI(3)

H_TMS(3)

Near CPU within 1.1"

H_TCK

H_TRST#

VCCST

H_TDO

H_TDI

H_TMS

R519

2.2K/4

R508 X_0R/4

C247

X_C0.1u6.3X4

A A

VCCIO

R161

150R1%4

R180 1K/4

H_CFG0

H_CFG0(3)

5

PCH_1VSB

R296

2.2K/4

R408 0R/4

From PCH_MOSI

XDP_HOOK3(12)

SYS_PWROK(12,22)

ITP_MODE(12)

CPURST#(3,12)

4

Page 7

5

Vinafix.com

4

3

2

1

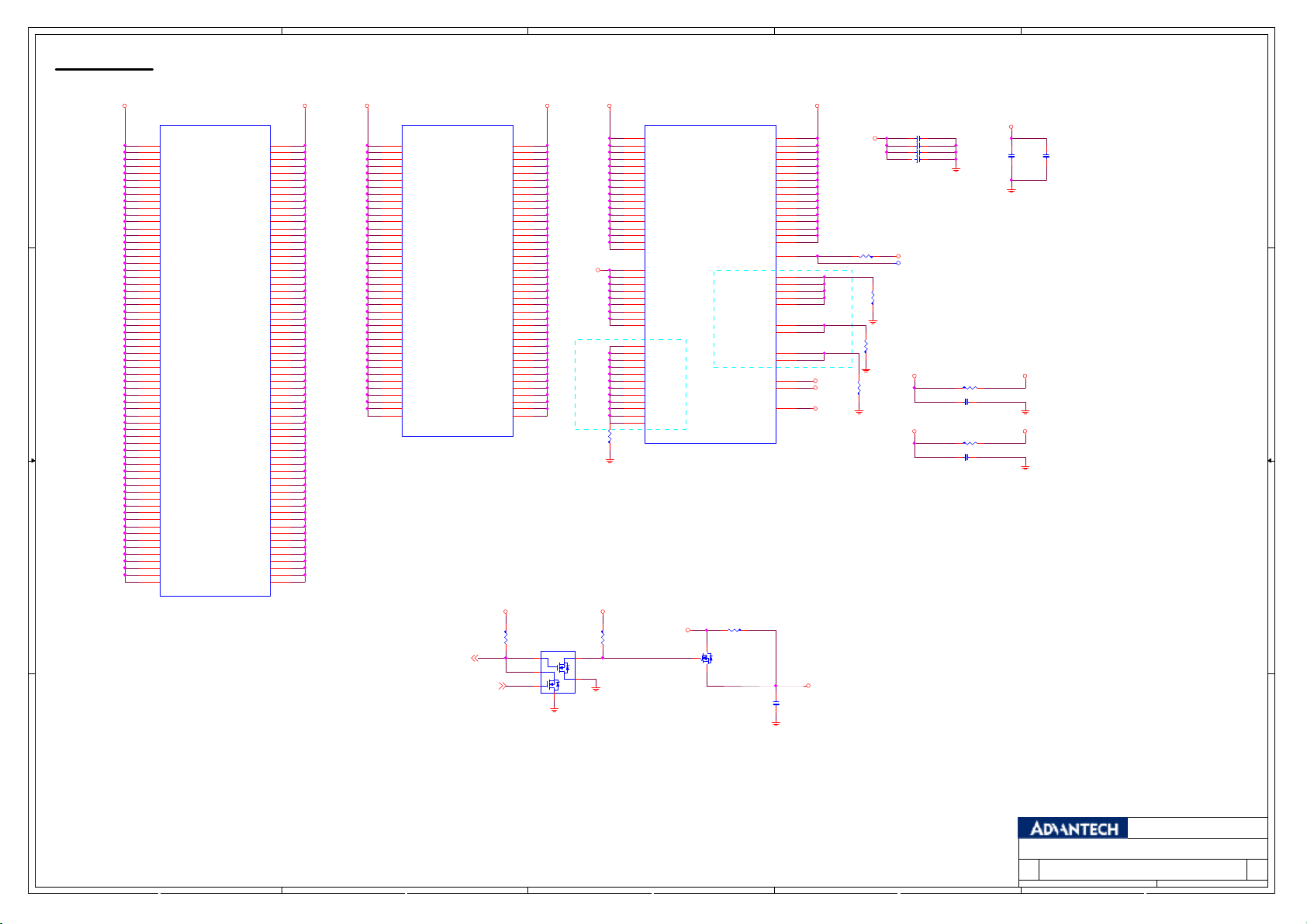

DDR4 SO-DIMM DIMM1

Channel A (W/O ECC)

MEM_MA_ADD[16..0](4) MEM_MA_DATA[63..0] ( 4)

D D

MEM_MA_BA0(4)

MEM_MA_BA1(4)

MEM_MA_CLK_H0(4)

MEM_MA_CLK_L0(4)

MEM_MA_CLK_H1(4)

MEM_MA_CLK_L1(4)

MEM_MA_CKE0(4)

MEM_MA_ODT0(4)

MEM_MA_ODT1(4)

C C

B B

A A

Tie DIMM connector DM[7:0] pins

directly to VDDQ

MEM_MA_DQS_H0(4)

MEM_MA_DQS_H1(4)

MEM_MA_DQS_H2(4)

MEM_MA_DQS_H3(4)

MEM_MA_DQS_H4(4)

MEM_MA_DQS_H5(4)

MEM_MA_DQS_H6(4)

MEM_MA_DQS_H7(4)

MEM_MA_DQS_L0(4)

MEM_MA_DQS_L1(4)

MEM_MA_DQS_L2(4)

MEM_MA_DQS_L3(4)

MEM_MA_DQS_L4(4)

MEM_MA_DQS_L5(4)

MEM_MA_DQS_L6(4)

MEM_MA_DQS_L7(4)

R2 00 X_0R/4

R1 99 X_0R/4

ADDRESS : A0

1010,0000

PCH_DRAM_RST#(12)

MEM_MA_ADD0 MEM_MA_DATA0

MEM_MA_ADD1 MEM_MA_DATA1

MEM_MA_ADD2 MEM_MA_DATA2

MEM_MA_ADD3 MEM_MA_DATA3

MEM_MA_ADD4 MEM_MA_DATA4

MEM_MA_ADD5 MEM_MA_DATA5

MEM_MA_ADD6 MEM_MA_DATA6

MEM_MA_ADD7 MEM_MA_DATA7

MEM_MA_ADD8 MEM_MA_DATA8

MEM_MA_ADD9 MEM_MA_DATA9

MEM_MA_ADD10 MEM_MA_DATA10

MEM_MA_ADD11 MEM_MA_DATA11

MEM_MA_ADD12 MEM_MA_DATA12

MEM_MA_ADD13 MEM_MA_DATA13

MEM_MA_ADD14 MEM_MA_DATA14

MEM_MA_ADD15 MEM_MA_DATA15

SMBCLK_DDR MEM_MA_DATA28

SMBDATA_DDR MEM_MA_DATA29

VCC_DDR

MEM_MA_SA0

MEM_MA_SA1

SMBCLK_VCC(12,21) SMBCLK_DDR (8)

SMBDATA_VCC(12,21) SMBDATA_DDR (8)

VCC_DDR

R791

X_1K/4

(1.2-0.85)/1K

=0.35mA

R789 X_1K/4

5

DIMM1A

144

A0

133

A1

132

A2

131

A3

128

A4

126

A5

127

A6

122

A7

125

A8

121

A9

146

A10/AP

120

A11

119

A12

158

A13

151

A14/WE#

156

A15/CAS#

152

A16/RAS#

150

BA0

145

BA1

149

CS0#

157

CS1#

137

CK0

139

CK0#

138

CK1

140

CK1#

109

CKE0

110

CKE1

253

SCL

254

SDA

155

ODT0

161

ODT1

12

DM0#/DBIO#

33

DM1#/DBI1#

54

DM2#/DBI2#

75

DM3#/DBI3#

178

DM4#/DBI4#

199

DM5#/DBI5#

220

DM6#/DBI6#

241

DM7#/DBI7#

96

DBI8#

13

DQS0

34

DQS1

55

DQS2

76

DQS3

179

DQS4

200

DQS5

221

DQS6

242

DQS7

97

DQS8

11

DQS0#

32

DQS1#

53

DQS2#

74

DQS3#

177

DQS4#

198

DQS5#

219

DQS6#

240

DQS7#

95

DQS8#

256

SA0

260

SA1

166

RFU

DDR4SODIMM-260PS_BLACK

R793 0R/4

+3VSUS

R790

X_4.7K/4

3.3/4.7K

(3.3-0.85)/4.7K

=0.7mA

=0.52mA

Q78

2

5

X_NN-CMKT3904

SLP_S4#(5,12,17,22,24,31)

R7 25 33R/4

R7 26 33R/4

6

1

3

4

D

G

S

8

DQ0

7

DQ1

20

DQ2

21

DQ3

4

DQ4

3

DQ5

16

DQ6

17

DQ7

28

DQ8

29

DQ9

41

DQ10

42

DQ11

24

DQ12

25

DQ13

38

DQ14

37

DQ15

50

DQ16

MEM_MA_DATA17

49

DQ17

MEM_MA_DATA18

62

DQ18

MEM_MA_DATA19

63

DQ19

MEM_MA_DATA20

46

DQ20

MEM_MA_DATA21

45

DQ21

58

DQ22

MEM_MA_DATA23

59

DQ23

MEM_MA_DATA24

70

DQ24

MEM_MA_DATA25

71

DQ25

MEM_MA_DATA26

83

DQ26

MEM_MA_DATA27

84

DQ27

66

DQ28

67

DQ29

MEM_MA_DATA30

79

DQ30

MEM_MA_DATA31

80

DQ31

MEM_MA_DATA32

174

DQ32

MEM_MA_DATA33

173

DQ33

MEM_MA_DATA34

187

DQ34

MEM_MA_DATA35

186

DQ35

MEM_MA_DATA36

170

DQ36

MEM_MA_DATA37

169

DQ37

MEM_MA_DATA38

183

DQ38

MEM_MA_DATA39

182

DQ39

MEM_MA_DATA40

195

DQ40

MEM_MA_DATA41

194

DQ41

MEM_MA_DATA42

207

DQ42

MEM_MA_DATA43

208

DQ43

MEM_MA_DATA44

191

DQ44

MEM_MA_DATA45

190

DQ45

MEM_MA_DATA46

203

DQ46

MEM_MA_DATA47

204

DQ47

MEM_MA_DATA48

216

DQ48

MEM_MA_DATA49

215

DQ49

MEM_MA_DATA50

228

DQ50

MEM_MA_DATA51

229

DQ51

MEM_MA_DATA52

211

DQ52

MEM_MA_DATA53

212

DQ53

MEM_MA_DATA54

224

DQ54

MEM_MA_DATA55

225

DQ55

MEM_MA_DATA56

237

DQ56

MEM_MA_DATA57

236

DQ57

MEM_MA_DATA58

249

DQ58

MEM_MA_DATA59

250

DQ59

MEM_MA_DATA60

232

DQ60

MEM_MA_DATA61

233

DQ61

MEM_MA_DATA62

245

DQ62

MEM_MA_DATA63

246

DQ63

115

BG0

113

BG1

VCC_DDR

R805

470R/4

1.2/470

=2.55mA

C529

X_C0.1u6.3X4

DDR_RESET# assertion to SLP_S4# assertion

Q75

(The negative minimum timingimplies that

X_2N7002

DDR_RESET# must eitherfallbefore SLP_S4#

orwithin100 nS after it). <Control by PCH>

MEM_MA_BG0 (4)

MEM_MA_BG1 (4)

DRAM_RESET# (8 )

15WW02:

It is recommended not to install any capacitor

on DDR Reset signal (DRAMRST).

4

+3V VDDSPD VCC_DDR

R729 0R/6

MEM_MA_ACT#(4)MEM_MA_CS_L0(4)

MEM_MA_ALERT#(4)MEM_MA_CS_L1(4)

VCC_DDR

C446

C2.2u6.3X4

R326 240R1%4

C449

C0.1u6.3X4

DRAM_RESET#MEM_MA_ADD16 MEM_MA_DATA16

MEM_MA_EVENT#MEM_MA_DATA22

MEM_MA_PAR(4)MEM_MA_CKE1(4)

3

255

92

91

101

105

88

87

100

104

162

165

108

114

116

134

143

1

2

5

6

9

10

14

15

18

19

22

23

26

27

30

31

35

36

39

40

43

44

47

48

51

52

56

57

60

61

64

65

68

69

72

73

77

78

81

82

85

86

89

90

93

94

98

99

102

103

106

107

DIMM1B

VDDSPD

CB0/NC4

CB1/NC3

CB2/NC6

CB3/NC8

CB4/NC2

CB5/NC1

CB6/NC5

CB7/NC7

C0/CS2#/NC9

C1/CS3#/NC10

RESET#

ACT#

ALERT#

EVENT#

Parity

VSS-1

VSS-2

VSS-3

VSS-4

VSS-5

VSS-6

VSS-7

VSS-8

VSS-9

VSS-10

VSS-11

VSS-12

VSS-13

VSS-14

VSS-15

VSS-16

VSS-17

VSS-18

VSS-19

VSS-20

VSS-21

VSS-22

VSS-23

VSS-24

VSS-25

VSS-26

VSS-27

VSS-28

VSS-29

VSS-30

VSS-31

VSS-32

VSS-33

VSS-34

VSS-35

VSS-36

VSS-37

VSS-38

VSS-39

VSS-40

VSS-41

VSS-42

VSS-43

VSS-44

VSS-45

VSS-46

VSS-47

VSS-48

VSS-49

VSS-50

VSS-51

VSS-52

111

VDD-1

112

VDD-2

117

VDD-3

118

VDD-4

123

VDD-5

124

VDD-6

129

VDD-7

130

VDD-8

135

VDD-9

136

VDD-10

141

VDD-11

142

VDD-12

147

VDD-13

148

VDD-14

153

VDD-15

154

VDD-16

159

VDD-17

160

VDD-18

163

VDD-19

257

VPP-1

259

VPP-2

164

VREF_CA

258

VTT

167

VSS-53

168

VSS-54

171

VSS-55

172

VSS-56

175

VSS-57

176

VSS-58

180

VSS-59

181

VSS-60

184

VSS-61

185

VSS-62

188

VSS-63

189

VSS-64

192

VSS-65

193

VSS-66

196

VSS-67

197

VSS-68

201

VSS-69

202

VSS-70

205

VSS-71

206

VSS-72

209

VSS-73

210

VSS-74

213

VSS-75

214

VSS-76

217

VSS-77

218

VSS-78

222

VSS-79

223

VSS-80

226

VSS-81

227

VSS-82

230

VSS-83

231

VSS-84

234

VSS-85

235

VSS-86

238

VSS-87

239

VSS-88

243

VSS-89

244

VSS-90

247

VSS-91

248

VSS-92

251

VSS-93

252

VSS-94

261

261

262

262

MEC1

MEC2

DDR4SODIMM-260PS_BLACK

MEC1

MEC2

C456

C0.1u6.3X4

C175

C0.1u6.3X4

C438

C0.1u6.3X4

C452

C2.2u6.3X4

DIMM_CA_VREF_A

C450

C4.7u6.3X6

2

VPP_DDR

VTT_DDR

VCC_DDR

C517 C0.1u6.3X4

C485 C0.1u6.3X4

C504 C0.1u6.3X4

C503 C0.1u6.3X4

C198 C1u16X4

C484 C1u16X4

C459 C1u16X4

C506 C1u16X4

C483 C10u6.3X6

VCC_DDR

C0.1u6.3X4

R312

1K1%4

DMS-SA30

DMS-SA30

DMS-SA30

DIMM_CA_VREF_A

C487

1

C191

C0.1u6.3X4

7 35Friday, March 31, 2017

7 35Friday, March 31, 2017

7 35Friday, March 31, 2017

R320

1K1%4

R325 0R/4

CPU_CA_VREF_A

R358 2R1%4

C216

C0.022u25X4

R369

24.9R1%4

Ti t l e

Ti t l e

Ti t l e

DDR4 SO-DIMM1 STD

DDR4 SO-DIMM1 STD

DDR4 SO-DIMM1 STD

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

10

10

10

Page 8

5

4

3

2

1

DDR4 SO-DIMM DIMM2

Channel B (W/O ECC)

VDDSPD from R729 (Page6)

MEM_MB_ADD[16..0](4) MEM_MB_DATA[63..0](4)

D D

MEM_MB_BA0(4)

MEM_MB_BA1(4)

MEM_MB_CS_L0(4) MEM_MB_ACT#(4)

MEM_MB_CS_L1(4) MEM_MB_ALERT#(4)

MEM_MB_CLK_H0(4)

MEM_MB_CLK_L0(4)

MEM_MB_CLK_H1(4)

MEM_MB_CLK_L1(4)

MEM_MB_CKE0(4)

MEM_MB_CKE1(4) MEM_MB_PAR(4)

SMBCLK_DDR(7)

SMBDATA_DDR(7)

MEM_MB_ODT0(4)

C C

B B

A A

MEM_MB_ODT1(4)

Tie DIMM connector DM[7:0] pins

directly to VDDQ

MEM_MB_DQS_H0(4)

MEM_MB_DQS_H1(4)

MEM_MB_DQS_H2(4)

MEM_MB_DQS_H3(4)

MEM_MB_DQS_H4(4)

MEM_MB_DQS_H5(4)

MEM_MB_DQS_H6(4)

MEM_MB_DQS_H7(4)

MEM_MB_DQS_L0(4)

MEM_MB_DQS_L1(4)

MEM_MB_DQS_L2(4)

MEM_MB_DQS_L3(4)

MEM_MB_DQS_L4(4)

MEM_MB_DQS_L5(4)

MEM_MB_DQS_L6(4)

MEM_MB_DQS_L7(4)

R210 X_0R/4

R196 X_0R/4

+3V

ADDRESS : A4

1010,0100

MEM_MB_ADD0 MEM_MB_DATA0

MEM_MB_ADD1 MEM_MB_DATA1

MEM_MB_ADD2 MEM_MB_DATA2

MEM_MB_ADD3 MEM_MB_DATA3

MEM_MB_ADD4 MEM_MB_DATA4

MEM_MB_ADD5 MEM_MB_DATA5

MEM_MB_ADD6 MEM_MB_DATA6

MEM_MB_ADD7 MEM_MB_DATA7

MEM_MB_ADD8 MEM_MB_DATA8

MEM_MB_ADD9 MEM_MB_DATA9

MEM_MB_ADD10 MEM_MB_DATA10

MEM_MB_ADD11 MEM_MB_DATA11

MEM_MB_ADD12 MEM_MB_DATA12

MEM_MB_ADD13 MEM_MB_DATA13

MEM_MB_ADD14 MEM_MB_DATA14

MEM_MB_ADD15 MEM_MB_DATA15

MEM_MB_ADD16 MEM_MB_DATA16

VCC_DDR

MEM_MB_SA0

MEM_MB_SA1

DIMM2A

144

A0

133

A1

132

A2

131

A3

128

A4

126

A5

127

A6

122

A7

125

A8

121

A9

146

A10/AP

120

A11

119

A12

158

A13

151

A14/WE#

156

A15/CAS#

152

A16/RAS#

150

BA0

145

BA1

149

CS0#

157

CS1#

137

CK0

139

CK0#

138

CK1

140

CK1#

109

CKE0

110

CKE1

253

SCL

254

SDA

155

ODT0

161

ODT1

12

DM0#/DBIO#

33

DM1#/DBI1#

54

DM2#/DBI2#

75

DM3#/DBI3#

178

DM4#/DBI4#

199

DM5#/DBI5#

220

DM6#/DBI6#

241

DM7#/DBI7#

96

DBI8#

13

DQS0

34

DQS1

55

DQS2

76

DQS3

179

DQS4

200

DQS5

221

DQS6

242

DQS7

97

DQS8

11

DQS0#

32

DQS1#

53

DQS2#

74

DQS3#

177

DQS4#

198

DQS5#

219

DQS6#

240

DQS7#

95

DQS8#

256

SA0

260

SA1

166

RFU

DDR4SODIMM-260PS_BLACK

N13-2600120-F02

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

BG0

BG1

8

7

20

21

4

3

16

17

28

29

41

42

24

25

38

37

50

MEM_MB_DATA17

49

MEM_MB_DATA18

62

MEM_MB_DATA19

63

MEM_MB_DATA20

46

MEM_MB_DATA21

45

MEM_MB_DATA22 MEM_MB_EVENT#

58

59

70

71

83

84

66

67

79

80

174

173

187

186

170

169

183

182

195

194

207

208

191

190

203

204

216

215

228

229

211

212

224

225

237

236

249

250

232

233

245

246

115

113

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_BG0(4)

MEM_MB_BG1(4)

VCC_DDR

VDDSPD VCC_DDR

DRAM_RESET#(7)

C432

C2.2u6.3X4

R328

240R1%4

C448

C0.1u6.3X4

DIMM2B

255

VDDSPD

92

CB0/NC4

91

CB1/NC3

101

CB2/NC6

105

CB3/NC8

88

CB4/NC2

87

CB5/NC1

100

CB6/NC5

104

CB7/NC7

162

C0/CS2#/NC9

165

C1/CS3#/NC10

108

RESET#

114

ACT#

116

ALERT#

134

EVENT#

143

Parity

1

VSS-1

2

VSS-2

5

VSS-3

6

VSS-4

9

VSS-5

10

VSS-6

14

VSS-7

15

VSS-8

18

VSS-9

19

VSS-10

22

VSS-11

23

VSS-12

26

VSS-13

27

VSS-14

30

VSS-15

31

VSS-16

35

VSS-17

36

VSS-18

39

VSS-19

40

VSS-20

43

VSS-21

44

VSS-22

47

VSS-23

48

VSS-24

51

VSS-25

52

VSS-26

56

VSS-27

57

VSS-28

60

VSS-29

61

VSS-30

64

VSS-31

65

VSS-32

68

VSS-33

69

VSS-34

72

VSS-35

73

VSS-36

77

VSS-37

78

VSS-38

81

VSS-39

82

VSS-40

85

VSS-41

86

VSS-42

89

VSS-43

90

VSS-44

93

VSS-45

94

VSS-46

98

VSS-47

99

VSS-48

102

VSS-49

103

VSS-50

106

VSS-51

107

VSS-52

DDR4SODIMM-260PS_BLACK

111

VDD-1

112

VDD-2

117

VDD-3

118

VDD-4

123

VDD-5

124

VDD-6

129

VDD-7

130

VDD-8

135

VDD-9

136

VDD-10

141

VDD-11

142

VDD-12

147

VDD-13

148

VDD-14

153

VDD-15

154

VDD-16

159

VDD-17

160

VDD-18

163

VDD-19

257

VPP-1

259

VPP-2

164

VREF_CA

258

VTT

167

VSS-53

168

VSS-54

171

VSS-55

172

VSS-56

175

VSS-57

176

VSS-58

180

VSS-59

181

VSS-60

184

VSS-61

185

VSS-62

188

VSS-63

189

VSS-64

192

VSS-65

193

VSS-66

196

VSS-67

197

VSS-68

201

VSS-69

202

VSS-70

205

VSS-71

206

VSS-72

209

VSS-73

210

VSS-74

213

VSS-75

214

VSS-76

217

VSS-77

218

VSS-78

222

VSS-79

223

VSS-80

226

VSS-81

227

VSS-82

230

VSS-83

231

VSS-84

234

VSS-85

235

VSS-86

238

VSS-87

239

VSS-88

243

VSS-89

244

VSS-90

247

VSS-91

248

VSS-92

251

VSS-93

252

VSS-94

261

261

262

262

MEC1

MEC2

MEC1

MEC2

C445

C0.1u6.3X4

C168

C0.1u6.3X4

C447

C0.1u6.3X4

VPP_DDR

C439

C2.2u6.3X4

DIMM_DQ_VREF_B

VTT_DDR

C430

C4.7u6.3X6

VCC_DDR

C551 C0.1u6.3X4

C515 C0.1u6.3X4

C244 C0.1u6.3X4

C561 C0.1u6.3X4

C505 C1u16X4

C460 C1u16X4

C489 C1u16X4

C518 C1u16X4

C534 C10u6.3X6

VCC_DDR

R297

1K1%4

R301 0R/4

R304

1K1%4

CPU_DQ_VREF_B

R306 2R1%4

C190

C0.022u25X4

R318

24.9R1%4

DIMM_DQ_VREF_B

C226

C0.1u6.3X4

C178

C0.1u6.3X4

Title

Title

Title

DDR4 SO-DIMM2 STD

DDR4 SO-DIMM2 STD

DDR4 SO-DIMM2 STD

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

DMS-SA30

DMS-SA30

DMS-SA30

10

10

8 35Friday, March 31, 2017

8 35Friday, March 31, 2017

1

8 35Friday, March 31, 2017

10

Page 9

5

PCH-USB/PCIE/DMI/SATA

USB1~2 for Rear USB3.0(LAN_USB1)

USB3~4 for Rear USB3.0(COM_USB1)

USB3_TX1P(19)

USB3_TX1N(19)

USB3_TX2P(19)

USB3_TX2N(19)

USB3_TX3P(23)

D D

The xHCI controller provides a

USB 3.0 debug port capability

on all SuperSpeed ports.

C C

B B

A A

USB3_TX3N(23)

USB3_TX4P(23)

USB3_TX4N(23)

USB3_RX1P(19)

USB3_RX1N(19)

USB3_RX2P(19)

USB3_RX2N(19)

USB3_RX3P(23)

USB3_RX3N(23)

USB3_RX4P(23)

USB3_RX4N(23)

USB5~9 & PCI-E1~3

No functtion for H110

PE4_LAN_TXP(19)

PE4_LAN_TXN(19)

PE4_LAN_RXP(19)

PE4_LAN_RXN(19)

PE5_PCIE_TXP(21)

PE5_PCIE_TXN(21)

PE6_PCIE_TXP(21)

PE6_PCIE_TXN(21)

PE5_PCIE_RXP(21)

PE5_PCIE_RXN(21)

PE6_PCIE_RXP(21)

PE6_PCIE_RXN(21)

R314 100R1%4

PCIE_RCOMP 12/15mil

RCOMPP&RCOMPN

Miss-match<1%

PCIECOMP_P

PCIECOMP_N

SATA0B_TXP

SATA0B_TXN

SATA1B_TXP

SATA1B_TXN

5

PCH1A

B11

USB3_1_TXP

C11

USB3_1_TXN

A12

USB3_2_TXP/SSIC_1_TXP

B12

USB3_2_TXN/SSIC_1_TXN

D13

USB3_3_TXP/SSIC_2_TXP

C13

USB3_3_TXN/SSIC_2_TXN

B13

USB3_4_TXP

A14

USB3_4_TXN

C14

USB3_5_TXP

B14

USB3_5_TXN

C15

USB3_6_TXP

B15

USB3_6_TXN

A7

USB3_1_RXP

B7

USB3_1_RXN

B8

USB3_2_RXP/SSIC_1_RXP

C8

USB3_2_RXN/SSIC_1_RXN

A9

USB3_3_RXP/SSIC_2_RXP

B10

USB3_3_RXN/SSIC_2_RXN

G11

USB3_4_RXP

E11

USB3_4_RXN

H13

USB3_5_RXP