5

smd.db-x7.ru

4

3

2

1

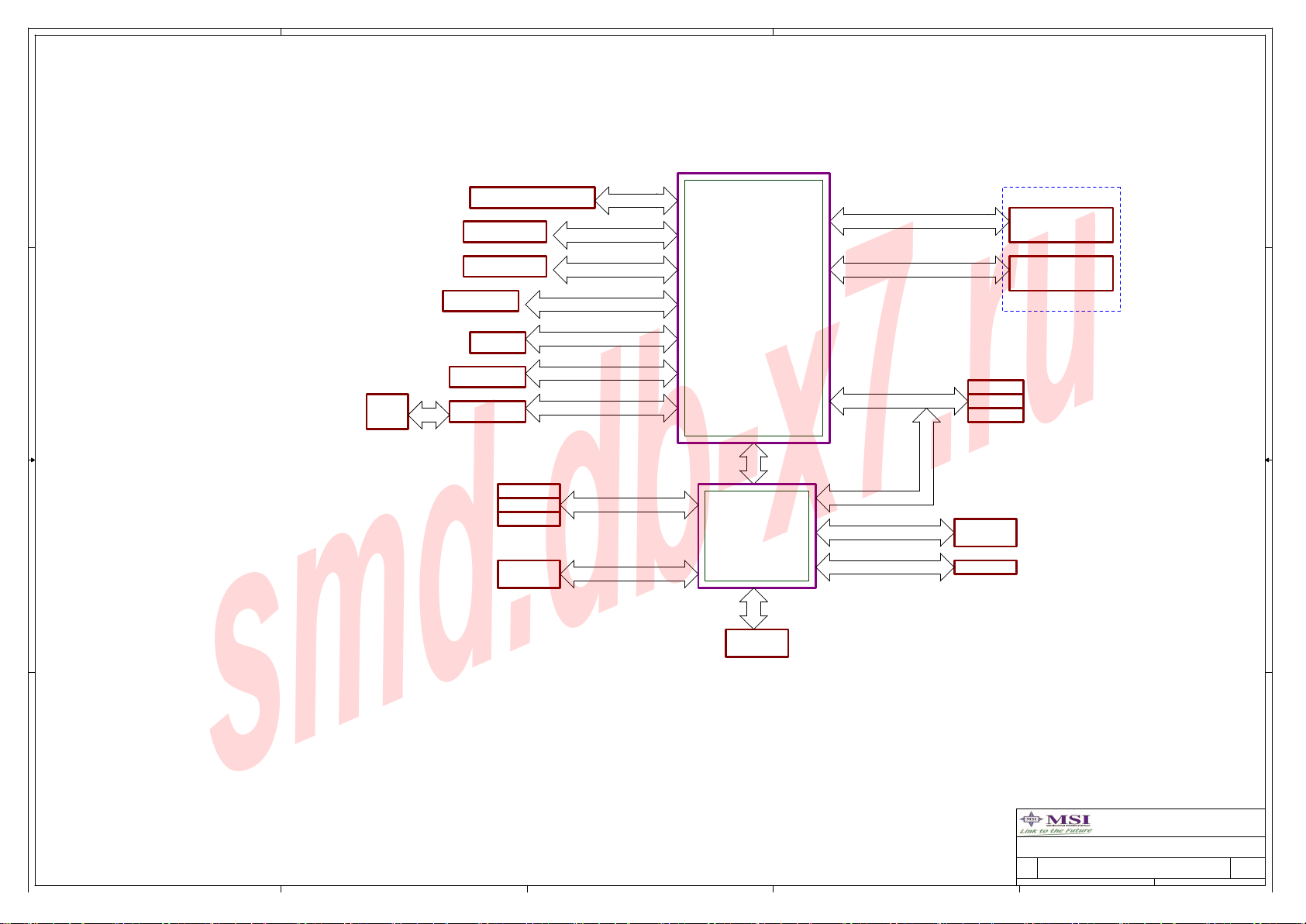

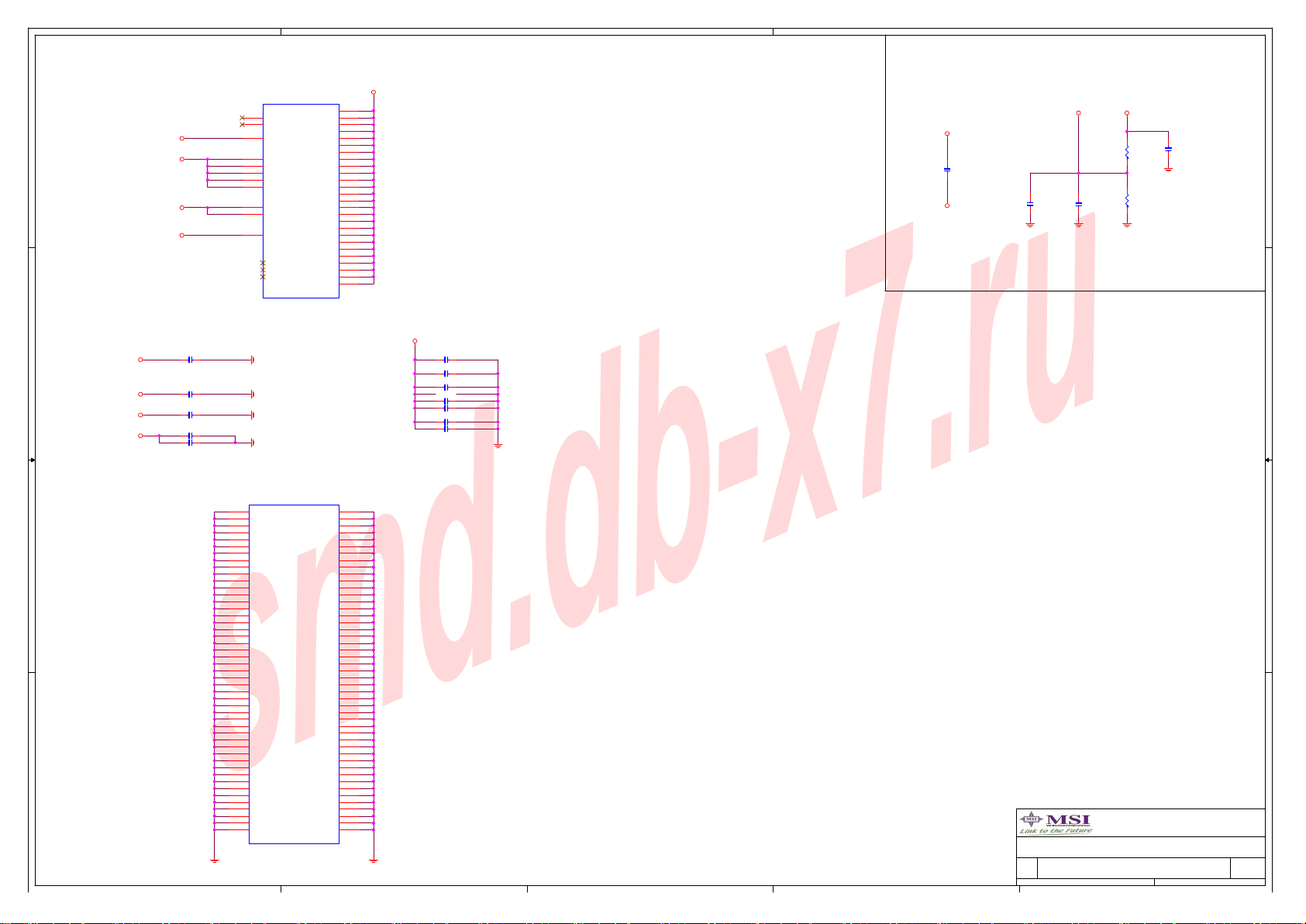

MS -7A36 Ver:3.0

CPU:

AMD AM4

D D

System Chipset:

Promontory A320

(Value DIY or S ystem Builder)

Main Memory:

DDR IV * 2 MAX :64 GB

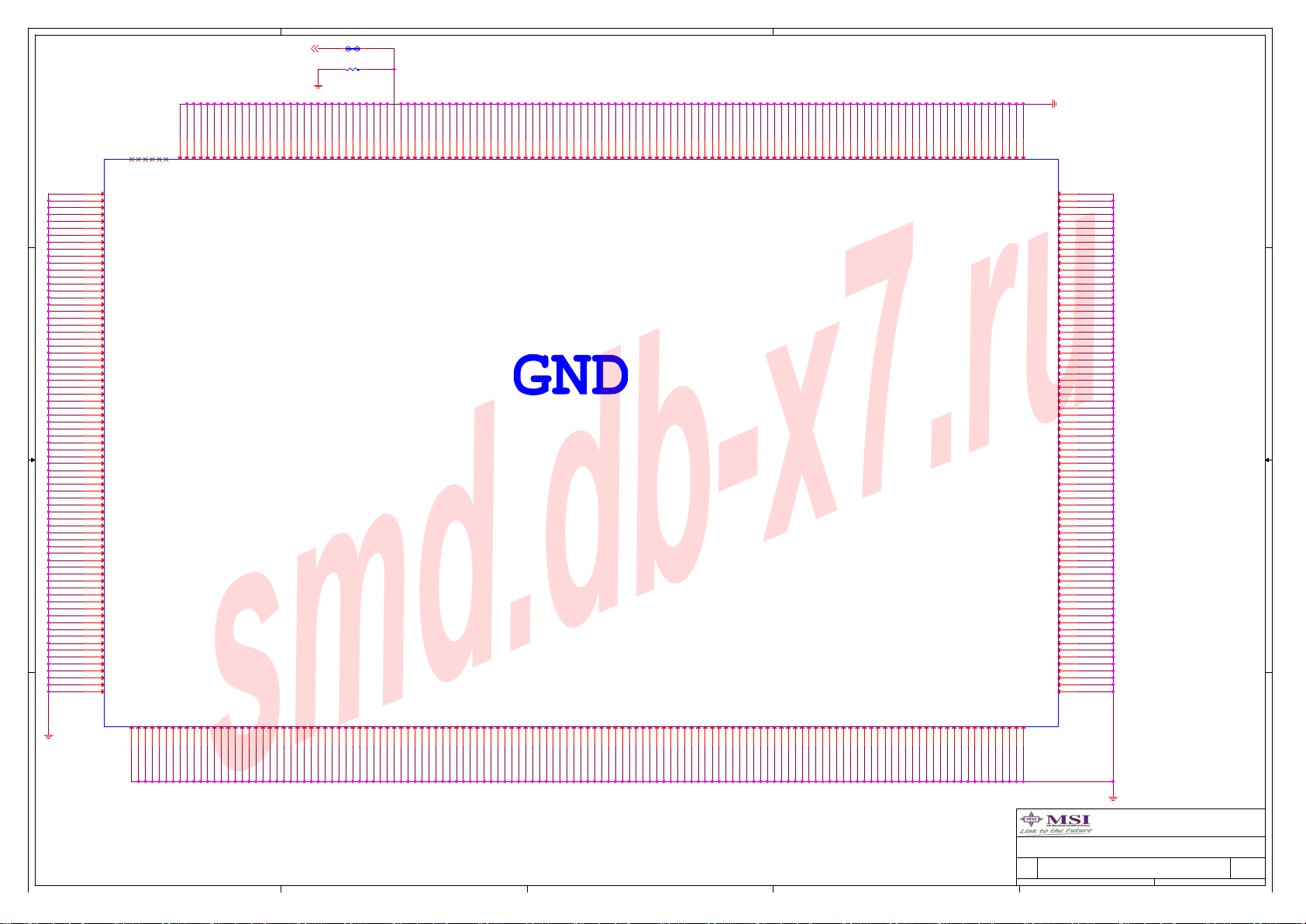

FUSION BL OC K DIAGRAM

DP to V GA & D VI CON

PC IE x1 6 GE N3

D P0 ~1

PC I E x 16

AM4

DD R IV 2 400

C HA

UNB UF FE R ED

DD RIV DIM M1

00

VR M

uP9505 3+2

On Board Chips et:

LPC S uper I/O --NCT5565

C C

LAN RTL8111H

Azalia CODEC - Realtek ALC887

Expansion S lots:

K BD

MO USE

PC IE x1 *2 GE N3

R EA R US B *4

AL C 887

SP I R OM 64 M

NC T5 56 5

GP P _P C IE

US B2 .0 & US B3 .1 GE N1

A UD IO

S PI Bu s

L PC

Bristol Ridg e

&

S ummit R idge

C L OC K

DD R IV 2 400

PC IE S LO T & PR OM

C HB

PC IE _E 1

PC IE _E 2

PC IE _E 3

UNB UF FE R ED

DD RIV DIM M2

01

From CPU

PCI E xpress X 16 S lot * 1

PCI E xpress X 1 S lot * 1

PCI E xpres s X1 Slot * 1

OC P IC:

J U SB 1

J U SB 2

PS 2+U SB

US B 2. 0

Promontory

UP6273

B B

J U SB 3

US B 3.1 G E N1

HUB *4

PROM1

Chipset

A320 Only

SA T A [4: 1]

GEN3

C LO C K 1 00 MH z

US B 3 .0

G PP_ PC IE G E N2

US B X 6

R TL 81 11 H

A A

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

Title

Title

Title

Bloc k Diagram

Bloc k Diagram

Bloc k Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICR O-S TAR T INT 'L C O.,LT D.

MS- 7A36. 30

MS- 7A36. 30

MS- 7A36. 30

1

of

of

of

1 50Monday, December 03, 2018

1 50Monday, December 03, 2018

1 50Monday, December 03, 2018

1

smd.db-x7.ru

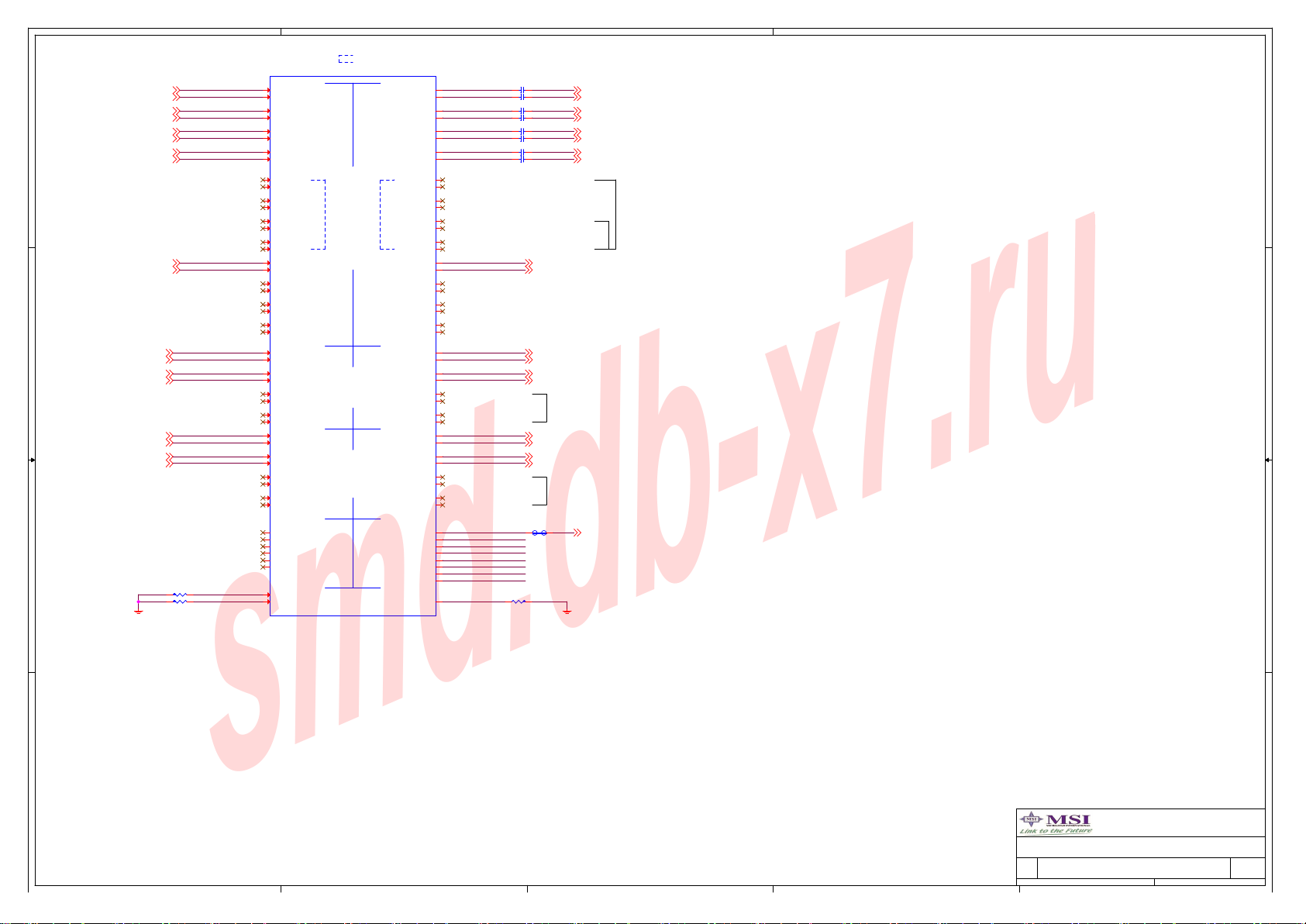

AMD

AM4

A A

01 Block Diagram

02 C over Sheet

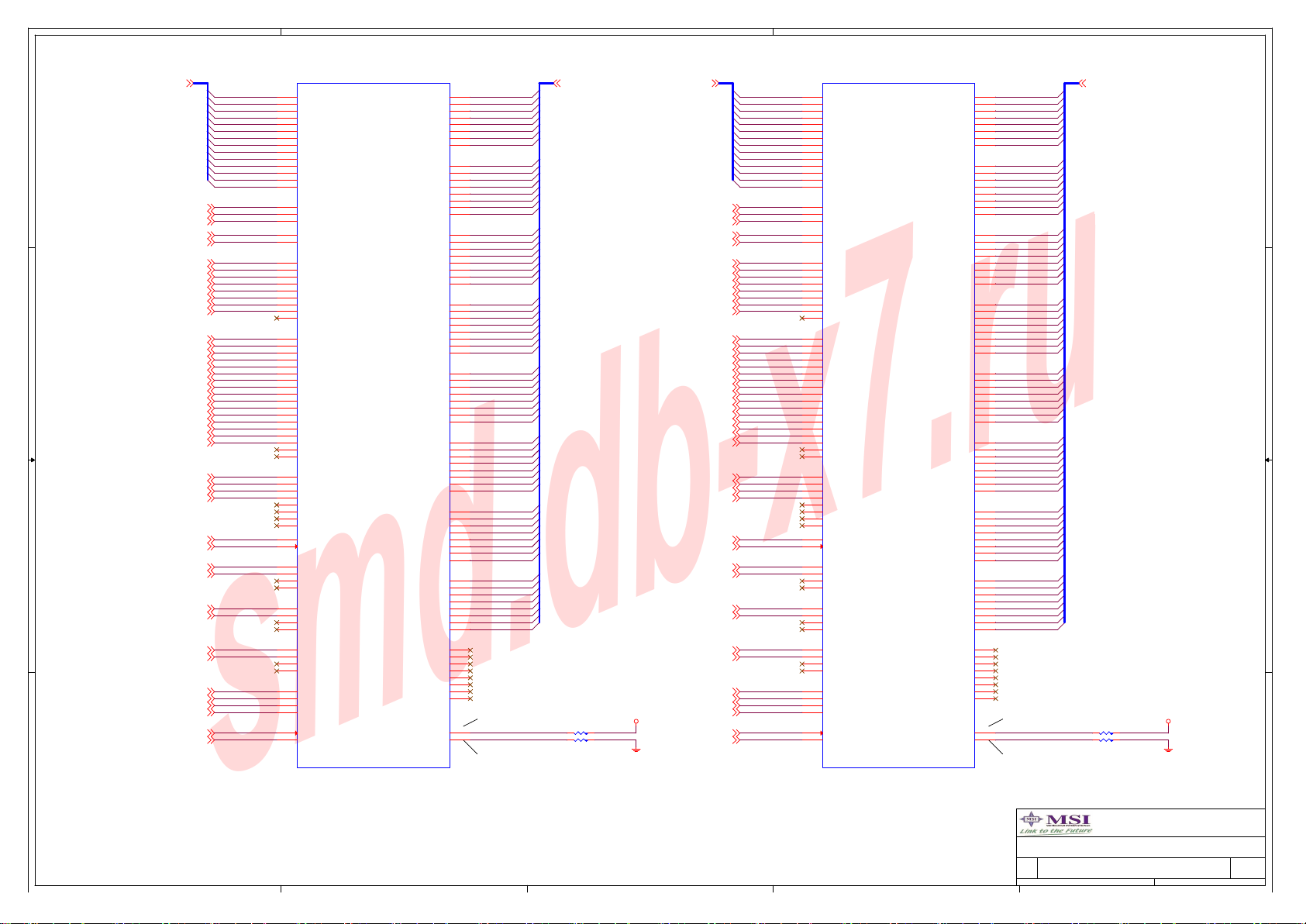

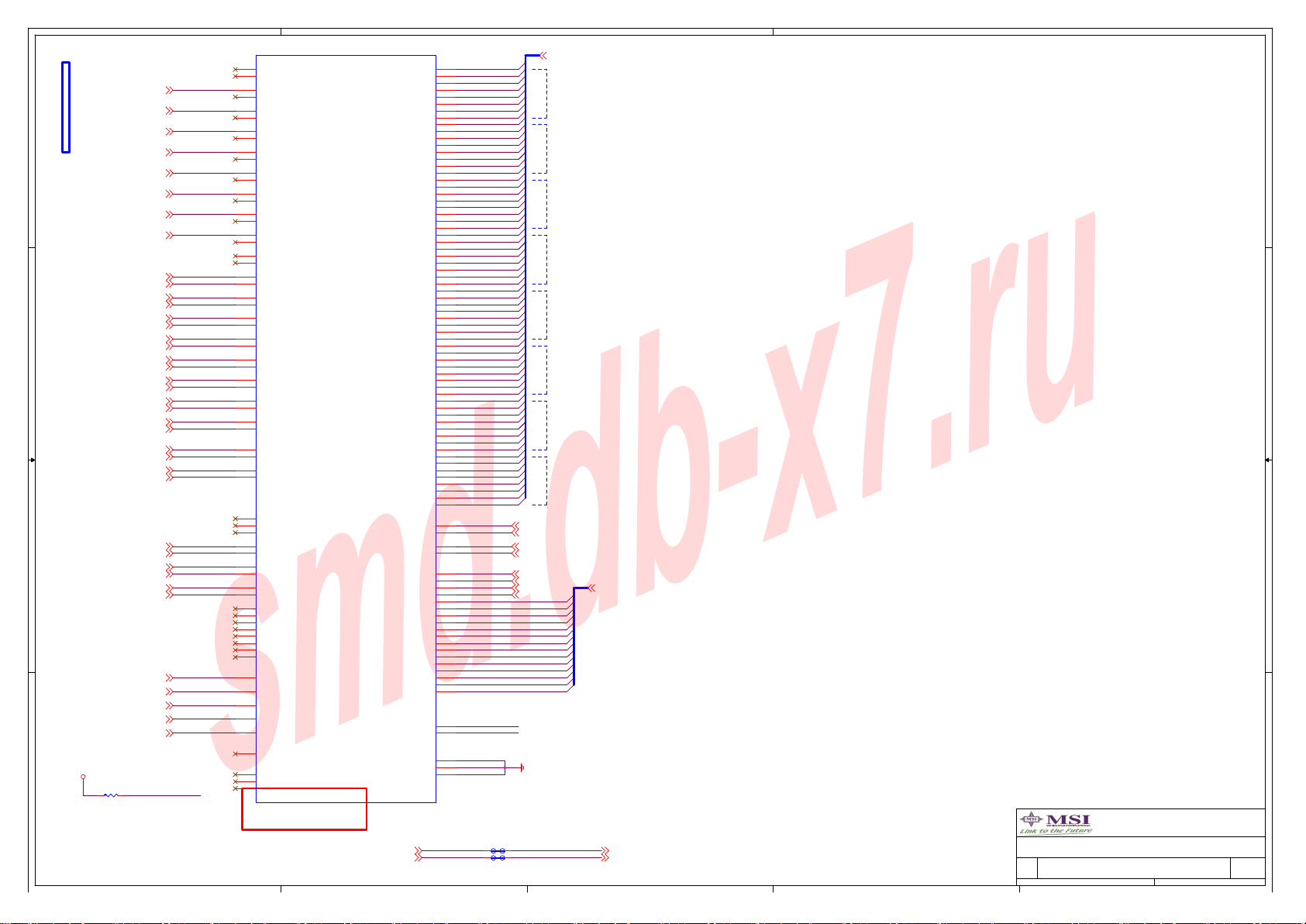

03 FM4 DDR 4 I/F

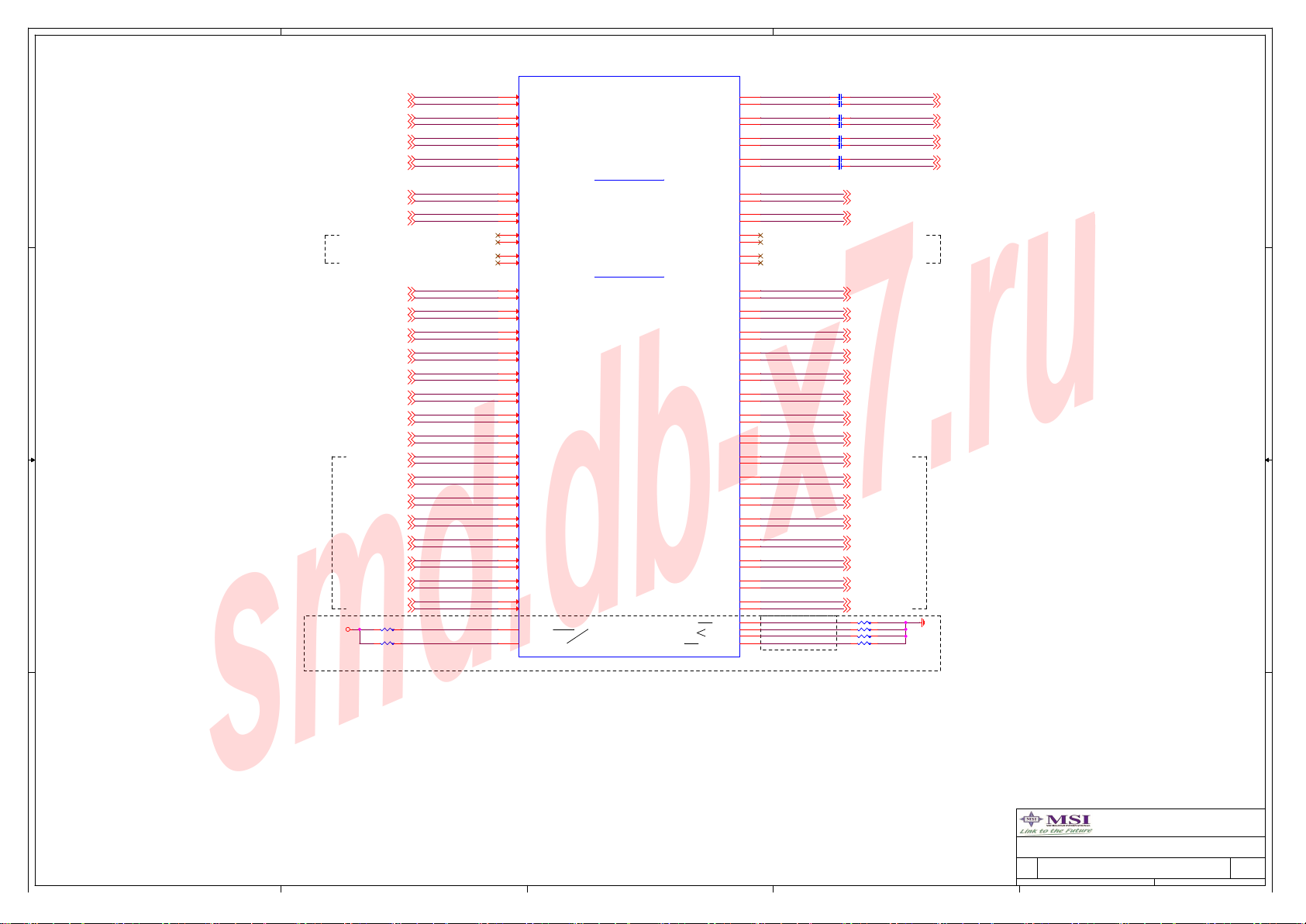

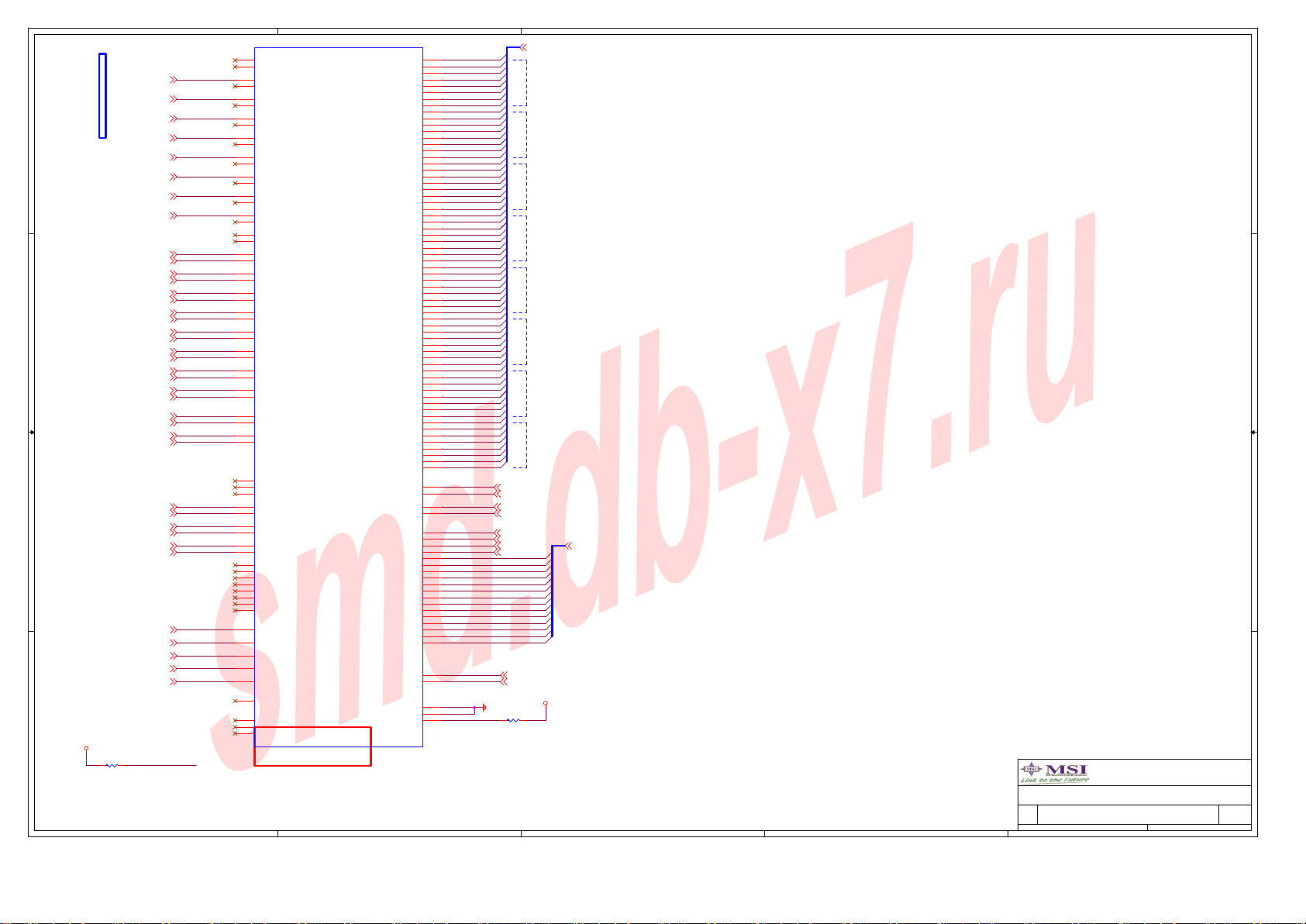

04 AM4 PC IE/SAT AE

05 AM4 Display/Audio

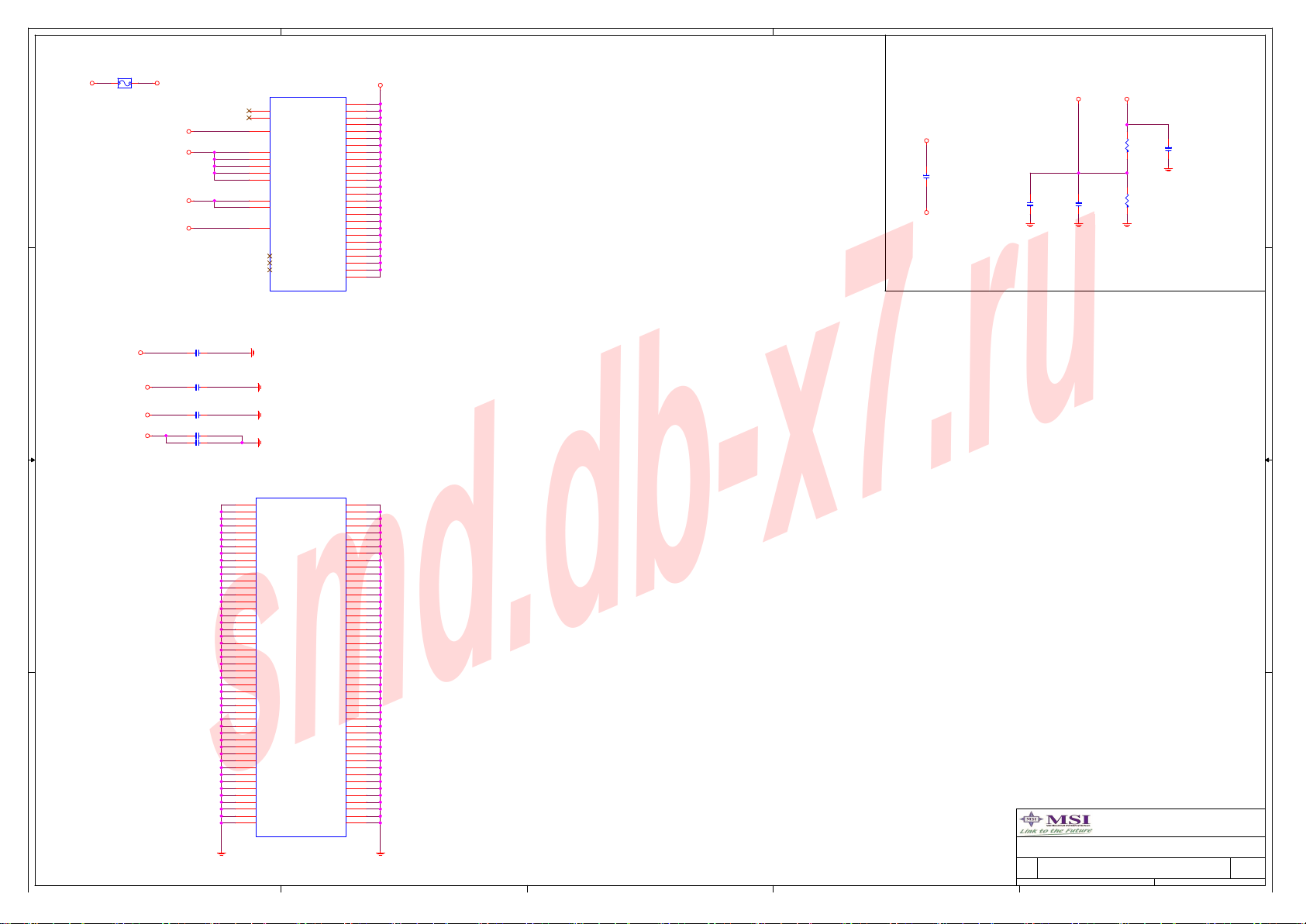

06 AM4 S V I/AC PI/G PIO

07 AM4 LPC/SPI/USB/C LK/S TR AP

08 AM4 Power/RTC Power/ 09 AM4 GND

10,11 DDR4-DIMM C H-A/B

12,13 DDR 4-POWER /GND

14 Promontory-PCIE/SATA/SATAE

15 Promontory-US B/OC

16 Promontory-CLK/ACPI/GPIO

17 Promontory-Power / 18 Promontory-G ND

19 PC IE X16(X1*2) S LOT

20 SIO NC T5565

21 CPU/SYS FAN Control TY PE K

36 C PU Power VDDP-RT8125E

37 C PU Power Connector/PWR GD

38 C PU Power uP9505 3+2 Phase

39 C PU Power Phase 1-3

40 C PU Power NB Phase 1-2

41 C PU Power NB S witch/NC T3933

42 UP6273 C URR ENT S E NSE

43 ATX/Front Panel

44 ALL LE D C ontrol

45 BOM Option

46 R TC Circuit/Moat C ap

47 History

48 Power Sequence

49 Power Delivery

50 GPIO MAP

22 LAN-RTL8111H

23 / 24 Audio ALC887

25 USB R ear PS2+US B2.0

26 USB Rear LAN+USB3.1 GE N1

27 USB Front Side

28 S ATA C onnector

29 DVI Connector

30 DP to VGA ITE6516

31 ACPI uPI-5VDIMM&3VS B

32 PM-NB681-1.05V/GS 7133-2.5V

33 DDR PWR VPP 25/V TT-MP2143

34 DDR Power-RT8231AGQW

35 C PU Power 1P8V-MP2147

Title

Title

Title

COV ER S HEE T

COV ER S HEE T

COV ER S HEE T

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

1

Date: Sheet

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

MS- 7A36. 30

MS- 7A36. 30

MS- 7A36. 30

of

of

of

2 50Monday, December 03, 2018

2 50Monday, December 03, 2018

2 50Monday, December 03, 2018

5

smd.db-x7.ru

4

3

2

1

MA_ADD [13..0][10]

D D

MA_AC T_ L[10]

MA_BG 0[10]

MA_BG 1[10]

MA_BA NK0[10]

MA_BA NK1[10]

MA_DM0[10]

MA_DM1[10]

MA_DM2[10]

MA_DM3[10]

MA_DM4[10]

MA_DM5[10]

MA_DM6[10]

MA_DM7[10]

MA_DQS _ H0[10]

MA_DQS _ L0[10]

C C

B B

A A

MA_DQS _ H1[10]

MA_DQS _ L1[10]

MA_DQS _ H2[10]

MA_DQS _ L2[10]

MA_DQS _ H3[10]

MA_DQS _ L3[10]

MA_DQS _ H4[10]

MA_DQS _ L4[10]

MA_DQS _ H5[10]

MA_DQS _ L5[10]

MA_DQS _ H6[10]

MA_DQS _ L6[10]

MA_DQS _ H7[10]

MA_DQS _ L7[10]

MA_C LK_ H0[10]

MA_C LK_ L0[10]

MA_C LK_ H1[10]

MA_C LK_ L1[10]

MA_R ES ET _L[10]

MA_E VENT _L[10]

MA0_C KE0[10]

MA0_C KE1[10]

MA0_ODT 0[10]

MA0_ODT 1[10]

MA0_C S_ L0[10]

MA0_C S_ L1[10]

MA_AD D_17[10]

MA_R AS_ L[10]

MA_C AS_ L[10]

MA_W E_ L[10]

MA_AL ERT _L[10]

MA_PA ROUT[10]

MA_ADD 0

MA_ADD 1

MA_ADD 2

MA_ADD 3

MA_ADD 4

MA_ADD 5

MA_ADD 6

MA_ADD 7

MA_ADD 8

MA_ADD 9

MA_ADD 10

MA_ADD 11

MA_ADD 12

MA_ADD 13

MA_AC T_ L

MA_BG 0

MA_BG 1

MA_BA NK0

MA_BA NK1

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS _ H0

MA_DQS _ L0

MA_DQS _ H1

MA_DQS _ L1

MA_DQS _ H2

MA_DQS _ L2

MA_DQS _ H3

MA_DQS _ L3

MA_DQS _ H4

MA_DQS _ L4

MA_DQS _ H5

MA_DQS _ L5

MA_DQS _ H6

MA_DQS _ L6

MA_DQS _ H7

MA_DQS _ L7

MA_C LK_ H0

MA_C LK_ L0

MA_C LK_ H1

MA_C LK_ L1

MA_R ES ET _L

MA_E VENT _L

MA0_C KE0

MA0_C KE1

MA0_ODT 0

MA0_ODT 1

MA0_C S_ L0

MA0_C S_ L1

MA_AD D_17

MA_R AS_ L

MA_C AS_ L

MA_W E_ L

MA_AL ERT _L

MA_PA ROUT

AA32

AA36

AE 32

AA35

AA33

AJ 31

AM31

AL29

AL26

AJ 33

AJ 34

AN32

AN33

AP29

AN29

AP26

AN26

AD35

AF 31

AD33

AF 34

AC 33

AE 35

AC 34

AE 34

AF 33

AB34

AD32

AB35

M35

N31

N32

K19

G26

H30

G34

H19

G19

G23

E30

H34

H33

U34

U33

V33

V35

V36

V32

W32

W35

M32

M30

M33

N34

Y33

CP U1A

T32

T35

T31

R30

R33

R32

P34

P30

P31

P33

N35

J 23

F23

F27

F26

F30

T34

L33

L34

MA_ ADD[0]

MA_ ADD[1]

MA_ ADD[2]

MA_ ADD[3]

MA_ ADD[4]

MA_ ADD[5]

MA_ ADD[6]

MA_ ADD[7]

MA_ ADD[8]

MA_ ADD[9]

MA_ ADD[10]

MA_ ADD[11]

MA_ ADD[12]

MA_ ADD[13]

MA_ ACT_ L

MA_ BG[0]

MA_ BG[1]

MA_ BANK[0]

MA_ BANK[1]

MA_ DM[0]

MA_ DM[1]

MA_ DM[2]

MA_ DM[3]

MA_ DM[4]

MA_ DM[5]

MA_ DM[6]

MA_ DM[7]

MA_ DM[8]

MA_ DQS_ H[0]

MA_ DQS_ L[0]

MA_ DQS_ H[1]

MA_ DQS_ L[1]

MA_ DQS_ H[2]

MA_ DQS_ L[2]

MA_ DQS_ H[3]

MA_ DQS_ L[3]

MA_ DQS_ H[4]

MA_ DQS_ L[4]

MA_ DQS_ H[5]

MA_ DQS_ L[5]

MA_ DQS_ H[6]

MA_ DQS_ L[6]

MA_ DQS_ H[7]

MA_ DQS_ L[7]

MA_ DQS_ H[8]

MA_ DQS_ L[8]

MA_ CLK_ H[0]

MA_ CLK_ L[0]

MA_ CLK_ H[1]

MA_ CLK_ L[1]

MA_ CLK_ H[2]

MA_ CLK_ L[2]

MA_ CLK_ H[3]

MA_ CLK_ L[3]

MA_ RES ET _ L

MA_ EVE NT_ L

MA0_ CKE [0]

MA0_ CKE [1]

MA1_ CKE [0]

MA1_ CKE [1]

MA0_ ODT[0]

MA0_ ODT[1]

MA1_ ODT[0]

MA1_ ODT[1]

MA0_ CS_ L[0]

MA0_ CS_ L[1]

MA1_ CS_ L[0]

MA1_ CS_ L[1]

MA_ ADD_ 17

MA_ RAS _L _ADD [16]

MA_ CAS _L_ ADD[15]

MA_W E_ L_ ADD[14]

MA_ ALER T_ L

MA_ PARO UT

PART 1 OF 9

MAMORY- A

AM4

MA_ DATA[0]

MA_ DATA[1]

MA_ DATA[2]

MA_ DATA[3]

MA_ DATA[4]

MA_ DATA[5]

MA_ DATA[6]

MA_ DATA[7]

MA_ DATA[8]

MA_ DATA[9]

MA_ DATA[10]

MA_ DATA[11]

MA_ DATA[12]

MA_ DATA[13]

MA_ DATA[14]

MA_ DATA[15]

MA_ DATA[16]

MA_ DATA[17]

MA_ DATA[18]

MA_ DATA[19]

MA_ DATA[20]

MA_ DATA[21]

MA_ DATA[22]

MA_ DATA[23]

MA_ DATA[24]

MA_ DATA[25]

MA_ DATA[26]

MA_ DATA[27]

MA_ DATA[28]

MA_ DATA[29]

MA_ DATA[30]

MA_ DATA[31]

MA_ DATA[32]

MA_ DATA[33]

MA_ DATA[34]

MA_ DATA[35]

MA_ DATA[36]

MA_ DATA[37]

MA_ DATA[38]

MA_ DATA[39]

MA_ DATA[40]

MA_ DATA[41]

MA_ DATA[42]

MA_ DATA[43]

MA_ DATA[44]

MA_ DATA[45]

MA_ DATA[46]

MA_ DATA[47]

MA_ DATA[48]

MA_ DATA[49]

MA_ DATA[50]

MA_ DATA[51]

MA_ DATA[52]

MA_ DATA[53]

MA_ DATA[54]

MA_ DATA[55]

MA_ DATA[56]

MA_ DATA[57]

MA_ DATA[58]

MA_ DATA[59]

MA_ DATA[60]

MA_ DATA[61]

MA_ DATA[62]

MA_ DATA[63]

MA_ CHEC K[0]

MA_ CHEC K[1]

MA_ CHEC K[2]

MA_ CHEC K[3]

MA_ CHEC K[4]

MA_ CHEC K[5]

MA_ CHEC K[6]

MA_ CHEC K[7]

MA_ ZVDDIO_ MEM_ S3

MA_ ZVS S

ZIF-S OCKE T1331

E18

J 18

J 20

H21

H18

F18

G20

F20

H22

G22

E24

J 24

F21

J 21

H24

F24

J 26

J 27

G28

H28

H25

G25

E28

H27

F29

J 30

H31

F32

J 29

G29

E31

G31

AH34

AJ 30

AK30

AL34

AH31

AH32

AK33

AK32

AM34

AM33

AP31

AR 33

AL32

AL31

AP34

AP32

AR 31

AK29

AM28

AL28

AM30

AN30

AP28

AR 28

AK27

AK26

AP25

AR 25

AN27

AM27

AL25

AM25

F33

G32

K31

K32

E33

E34

J 32

J 33

Ty pe0 Onl y

MA_ZV DDIO_ME M_S3

Y34

MA_ZV SS

AJ 37

Ty pe2/ 3 Onl y

MA_DAT A0

MA_DAT A1

MA_DAT A2

MA_DAT A3

MA_DAT A4

MA_DAT A5

MA_DAT A6

MA_DAT A7

MA_DAT A8

MA_DAT A9

MA_DAT A10

MA_DAT A11

MA_DAT A12

MA_DAT A13

MA_DAT A14

MA_DAT A15

MA_DAT A16

MA_DAT A17

MA_DAT A18

MA_DAT A19

MA_DAT A20

MA_DAT A21

MA_DAT A22

MA_DAT A23

MA_DAT A24

MA_DAT A25

MA_DAT A26

MA_DAT A27

MA_DAT A28

MA_DAT A29

MA_DAT A30

MA_DAT A31

MA_DAT A32

MA_DAT A33

MA_DAT A34

MA_DAT A35

MA_DAT A36

MA_DAT A37

MA_DAT A38

MA_DAT A39

MA_DAT A40

MA_DAT A41

MA_DAT A42

MA_DAT A43

MA_DAT A44

MA_DAT A45

MA_DAT A46

MA_DAT A47

MA_DAT A48

MA_DAT A49

MA_DAT A50

MA_DAT A51

MA_DAT A52

MA_DAT A53

MA_DAT A54

MA_DAT A55

MA_DAT A56

MA_DAT A57

MA_DAT A58

MA_DAT A59

MA_DAT A60

MA_DAT A61

MA_DAT A62

MA_DAT A63

MA_DAT A[63..0] [10]

R269 X_ 40.2R1%/4 R271 X_ 40.2R1%/4

MB_ADD [13..0][11]

MB_AC T_ L[11]

MB_BG 0[11]

MB_BG 1[11]

MB_BANK 0[11]

MB_BANK 1[11]

MB_DM0[11]

MB_DM1[11]

MB_DM2[11]

MB_DM3[11]

MB_DM4[11]

MB_DM5[11]

MB_DM6[11]

MB_DM7[11]

MB_DQS _H0[11]

MB_DQS _L 0[11]

MB_DQS _H1[11]

MB_DQS _L 1[11]

MB_DQS _H2[11]

MB_DQS _L 2[11]

MB_DQS _H3[11]

MB_DQS _L 3[11]

MB_DQS _H4[11]

MB_DQS _L 4[11]

MB_DQS _H5[11]

MB_DQS _L 5[11]

MB_DQS _H6[11]

MB_DQS _L 6[11]

MB_DQS _H7[11]

MB_DQS _L 7[11]

MB_C LK_ H0[11]

MB_C LK_ L0[11]

MB_C LK_ H1[11]

MB_C LK_ L1[11]

MB_R ES ET _L[11]

MB_E VENT _L[11]

MB0_C KE0[11]

MB0_C KE1[11]

MB0_ODT 0[11]

MB0_ODT 1[11]

MB0_C S_ L0[11]

MB0_C S_ L1[11]

MB_AD D_17[11]

MB_R AS_ L[11]

MB_C AS_ L[11]

VC C_ DDR VC C_ DDR

MB_W E_ L[11]

MB_AL ERT _L[11]

MB_PA ROUT[11]

MB_ADD 0

MB_ADD 1

MB_ADD 2

MB_ADD 3

MB_ADD 4

MB_ADD 5

MB_ADD 6

MB_ADD 7

MB_ADD 8

MB_ADD 9

MB_ADD 10

MB_ADD 11

MB_ADD 12

MB_ADD 13

MB_AC T_ L

MB_BG 0

MB_BG 1

MB_BANK 0

MB_BANK 1

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS _H0

MB_DQS _L 0

MB_DQS _H1

MB_DQS _L 1

MB_DQS _H2

MB_DQS _L 2

MB_DQS _H3

MB_DQS _L 3

MB_DQS _H4

MB_DQS _L 4

MB_DQS _H5

MB_DQS _L 5

MB_DQS _H6

MB_DQS _L 6

MB_DQS _H7

MB_DQS _L 7

MB_C LK_ H0

MB_C LK_ L0

MB_C LK_ H1

MB_C LK_ L1

MB_R ES ET _L

MB_E VENT _L

MB0_C KE0

MB0_C KE1

MB0_ODT 0

MB0_ODT 1

MB0_C S_ L0

MB0_C S_ L1

MB_AD D_17

MB_R AS_ L

MB_C AS_ L

MB_W E_ L

MB_AL ERT _L

MB_PA ROUT

AC 36

AC 39

AG38

AD38

AC 37

AL38

AR 39

AT3 5

AW29

AM37

AM36

AT3 8

AT3 9

AU34

AV34

AU28

AU29

W38

W37

AA39

AA38

AF 39

AH36

AF 37

AH38

AE 37

AG39

AE 38

AG36

AH37

AD36

AF 36

AD39

AB38

CP U1B

U36

U37

T38

T37

R39

R36

P39

R38

P36

P37

N38

M38

M36

M39

C21

D26

A32

D37

F39

B22

A22

C27

B27

C33

C32

B37

A37

G38

G37

U39

V39

V38

Y37

Y39

K35

L37

K37

L39

L36

N37

MB_A DD[0]

MB_A DD[1]

MB_A DD[2]

MB_A DD[3]

MB_A DD[4]

MB_A DD[5]

MB_A DD[6]

MB_A DD[7]

MB_A DD[8]

MB_A DD[9]

MB_A DD[10]

MB_A DD[11]

MB_A DD[12]

MB_A DD[13]

MB_A CT_ L

MB_B G[0]

MB_B G[1]

MB_B ANK[0]

MB_B ANK[1]

MB_D M[0]

MB_D M[1]

MB_D M[2]

MB_D M[3]

MB_D M[4]

MB_D M[5]

MB_D M[6]

MB_D M[7]

MB_D M[8]

MB_D QS_ H[0]

MB_D QS_ L[0]

MB_D QS_ H1]

MB_D QS_ L[1]

MB_D QS_ H[2]

MB_D QS_ L[2]

MB_D QS_ H[3]

MB_D QS_ L[3]

MB_D QS_ H[4]

MB_D QS_ L[4]

MB_D QS_ H[5]

MB_D QS_ L[5]

MB_D QS_ H[6]

MB_D QS_ L[6]

MB_D QS_ H[7]

MB_D QS_ L[7]

MB_D QS_ H[8]

MB_D QS_ L[8]

MB_C LK_ H[0]

MB_C LK_ L[0]

MB_C LK_ H[1]

MB_C LK_ L[1]

MB_C LK_ H[2]

MB_C LK_ L[2]

MB_C LK_ H[3]

MB_C LK_ L[3]

MB_R ES ET _L

MB_E VE NT_ L

MB0_C KE [0]

MB0_C KE [1]

MB1_C KE [0]

MB1_C KE [1]

MB0_O DT[0]

MB0_O DT[1]

MB1_O DT[0]

MB1_O DT[1]

MB0_C S_ L[0]

MB0_C S_ L[1]

MB1_C S_ L[0]

MB1_C S_ L[1]

MB_A DD_1 7

MB_R AS _L_ ADD[16]

MB_C AS_ L_ ADD[15]

MB_W E_ L_ ADD[14]

MB_A LER T_ L

MB_P ARO UT

PART 2 OF 9

MEMORY- B

AM4

MB_D ATA[0]

MB_D ATA[1]

MB_D ATA[2]

MB_D ATA[3]

MB_D ATA[4]

MB_D ATA[5]

MB_D ATA[6]

MB_D ATA[7]

MB_D ATA[8]

MB_D ATA[9]

MB_D ATA[10]

MB_D ATA[11]

MB_D ATA[12]

MB_D ATA[13]

MB_D ATA[14]

MB_D ATA[15]

MB_D ATA[16]

MB_D ATA[17]

MB_D ATA[18]

MB_D ATA[19]

MB_D ATA[20]

MB_D ATA[21]

MB_D ATA[22]

MB_D ATA[23]

MB_D ATA[24]

MB_D ATA[25]

MB_D ATA[26]

MB_D ATA[27]

MB_D ATA[28]

MB_D ATA[29]

MB_D ATA[30]

MB_D ATA[31]

MB_D ATA[32]

MB_D ATA[33]

MB_D ATA[34]

MB_D ATA[35]

MB_D ATA[36]

MB_D ATA[37]

MB_D ATA[38]

MB_D ATA[39]

MB_D ATA[40]

MB_D ATA[41]

MB_D ATA[42]

MB_D ATA[43]

MB_D ATA[44]

MB_D ATA[45]

MB_D ATA[46]

MB_D ATA[47]

MB_D ATA[48]

MB_D ATA[49]

MB_D ATA[50]

MB_D ATA[51]

MB_D ATA[52]

MB_D ATA[53]

MB_D ATA[54]

MB_D ATA[55]

MB_D ATA[56]

MB_D ATA[57]

MB_D ATA[58]

MB_D ATA[59]

MB_D ATA[60]

MB_D ATA[61]

MB_D ATA[62]

MB_D ATA[63]

MB_C HEC K[0]

MB_C HEC K[1]

MB_C HEC K[2]

MB_C HEC K[3]

MB_C HEC K[4]

MB_C HEC K[5]

MB_C HEC K[6]

MB_C HEC K[7]

MB_Z VDDIO_ MEM_ S3

MB_Z VS S

ZIF-S OCKE T1331

D20

B21

B24

C24

A20

C20

A23

C23

A26

C26

A29

C29

A25

B25

A28

B28

A31

B31

B34

C35

B30

C30

B33

A34

B36

E36

C39

D38

A35

C36

B38

C38

AK39

AL37

AN36

AN39

AK38

AK36

AM39

AN38

AR 36

AR 37

AU37

AV37

AP37

AP38

AT3 6

AU38

AW35

AU35

AW32

AU32

AV36

AW36

AW33

AV33

AW30

AV30

AW27

AW26

AV31

AU31

AV28

AV27

F38

F36

H39

J 39

E37

E39

H36

H37

Ty pe0 Onl y

MB_ZV DDIO_ME M_S3

Y36

MB_ZV SS

AJ 39

Ty pe2/ 3 Onl y

MB_DAT A0

MB_DAT A1

MB_DAT A2

MB_DAT A3

MB_DAT A4

MB_DAT A5

MB_DAT A6

MB_DAT A7

MB_DAT A8

MB_DAT A9

MB_DAT A10

MB_DAT A11

MB_DAT A12

MB_DAT A13

MB_DAT A14

MB_DAT A15

MB_DAT A16

MB_DAT A17

MB_DAT A18

MB_DAT A19

MB_DAT A20

MB_DAT A21

MB_DAT A22

MB_DAT A23

MB_DAT A24

MB_DAT A25

MB_DAT A26

MB_DAT A27

MB_DAT A28

MB_DAT A29

MB_DAT A30

MB_DAT A31

MB_DAT A32

MB_DAT A33

MB_DAT A34

MB_DAT A35

MB_DAT A36

MB_DAT A37

MB_DAT A38

MB_DAT A39

MB_DAT A40

MB_DAT A41

MB_DAT A42

MB_DAT A43

MB_DAT A44

MB_DAT A45

MB_DAT A46

MB_DAT A47

MB_DAT A48

MB_DAT A49

MB_DAT A50

MB_DAT A51

MB_DAT A52

MB_DAT A53

MB_DAT A54

MB_DAT A55

MB_DAT A56

MB_DAT A57

MB_DAT A58

MB_DAT A59

MB_DAT A60

MB_DAT A61

MB_DAT A62

MB_DAT A63

MB_DAT A[63..0] [11]

R257 39.2R1%/4R256 39.2R1%/4

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

Title

Title

Title

AM4 DDR4 I/F

AM4 DDR4 I/F

AM4 DDR4 I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICR O-S TAR T INT 'L C O.,LT D.

MS- 7A36. 30

MS- 7A36. 30

MS- 7A36. 30

1

of

of

of

3 50Monday, December 03, 2018

3 50Monday, December 03, 2018

3 50Monday, December 03, 2018

5

smd.db-x7.ru

4

3

2

1

CP U1C

APU_ RX P0[14]

APU_ RX N0[14]

APU_ RX P1[14]

APU_ RX N1[14]

D D

APU_ RX P2[14]

APU_ RX N2[14]

APU_ RX P3[14]

APU_ RX N3[14]

APU_ GPP _R XP0[19]

APU_ GPP _R XN0[19]

APU_ GPP _R XP1[19]

APU_ GPP _R XN1[19]

APU_ RX P0

APU_ RX N0

APU_ RX P1

APU_ RX N1

APU_ RX P2

APU_ RX N2

APU_ RX P3

APU_ RX N3

APU_ GPP _R XP0

APU_ GPP _R XN0

APU_ GPP _R XP1

APU_ GPP _R XN1

Not supp ort e d PCI E on AMD Fa mi l y 15h Mode l s 6 0h- 6F h Not supp ort e d PCI E on AMD Fa mi l y 15h Mode l s 6 0h- 6F h

GFX _R XP 0[19]

GFX _R XN0[19]

GFX _R XP 1[19]

GFX _R XN1[19]

GFX _R XP 2[19]

GFX _R XN2[19]

C C

Onl y s uppor t ed on AMD F ami l y 17 h/Model s 00 h- 0Fh

B B

CP U_VD DP

GFX _R XP 3[19]

GFX _R XN3[19]

GFX _R XP 4[19]

GFX _R XN4[19]

GFX _R XP 5[19]

GFX _R XN5[19]

GFX _R XP 6[19]

GFX _R XN6[19]

GFX _R XP 7[19]

GFX _R XN7[19]

GFX _R XP 8[19]

GFX _R XN8[19]

GFX _R XP 9[19]

GFX _R XN9[19]

GFX _R XP 10[19]

GFX _R XN10[19]

GFX _R XP 11[19]

GFX _R XN11[19]

GFX _R XP 12[19]

GFX _R XN12[19]

GFX _R XP 13[19]

GFX _R XN13[19]

GFX _R XP 14[19]

GFX _R XN14[19]

GFX _R XP 15[19]

GFX _R XN15[19]

R258 196R1%/4

R304 1K1%/4

GFX _R XP 0

GFX _R XN0

GFX _R XP 1

GFX _R XN1

GFX _R XP 2

GFX _R XN2

GFX _R XP 3

GFX _R XN3

GFX _R XP 4

GFX _R XN4

GFX _R XP 5

GFX _R XN5

GFX _R XP 6

GFX _R XN6

GFX _R XP 7

GFX _R XN7

GFX _R XP 8

GFX _R XN8

GFX _R XP 9

GFX _R XN9

GFX _R XP 10

GFX _R XN10

GFX _R XP 11

GFX _R XN11

GFX _R XP 12 GFX _TX P12

GFX _R XN12 GFX _T XN12

GFX _R XP 13

GFX _R XN13

GFX _R XP 14

GFX _R XN14

GFX _R XP 15

GFX _R XN15

APU_ P_ ZVDDP

Wi t hi n 1500 mi l s f r om APU

APU_ SAT A_Z VDDP

Wi t hi n 1000 mi l s f r om APU

AE 8

P_ HUB_ RX P[0]

AD8

P_ HUB_ RX N[0]

AB8

P_ HUB_ RX P[1]

AA8

P_ HUB_ RX N[1]

Y6

P_ HUB_ RX P[2]

Y7

P_ HUB_ RX N[2]

W4

P_ HUB_ RX P[3]

W5

P_ HUB_ RX N[3]

AR 9

P_ GPP _R XP[0]

AT9

P_ GPP _R XN[0]

AM9

P_ GPP _R XP[1]

AM10

P_ GPP _R XN[1]

AR 10

P_ GPP _R XP[2]/SA TA_ RX 0P

AP10

P_ GPP _R XN[2]/SAT A_R X0N

AP11

P_ GPP _R XP[3]/SA TA_ RX 1P

AN11

P_ GPP _R XN[3]/SAT A_R X1N

F6

P_ GFX _ RXP [0]

F5

P_ GFX _ RXN[0]

G5

P_ GFX _ RXP [1]

G4

P_ GFX _ RXN[1]

H7

P_ GFX _ RXP [2]

H6

P_ GFX _ RXN[2]

J 6

P_ GFX _ RXP [3]

J 5

P_ GFX _ RXN[3]

K8

P_ GFX _ RXP [4]

K7

P_ GFX _ RXN[4]

K5

P_ GFX _ RXP [5]

K4

P_ GFX _ RXN[5]

L7

P_ GFX _ RXP [6]

L6

P_ GFX _ RXN[6]

M6

P_ GFX _ RXP [7]

M5

P_ GFX _ RXN[7]

N8

P_ GFX _ RXP [8]

N7

P_ GFX _ RXN[8]

N5

P_ GFX _ RXP [9]

N4

P_ GFX _ RXN[9]

P7

P_ GFX _ RXP [10]

P6

P_ GFX _ RXN[10]

R6

P_ GFX _ RXP [11]

R5

P_ GFX _ RXN[11]

T8

P_ GFX _ RXP [12]

T7

P_ GFX _ RXN[12]

T4

P_ GFX _ RXP [13]

T5

P_ GFX _ RXN[13]

U7

P_ GFX _ RXP [14]

U6

P_ GFX _ RXN[14]

V6

P_ GFX _ RXP [15]

V5

P_ GFX _ RXN[15]

W8

P_ ZVD DP

AV7

SA TA_ ZVD DP

Ty pe0 Onl y

PCI E

SAT A

Ex pre ss

AM4

Ty pe0 Onl y

PART 3 OF 9

P_ HUB_T XP [0]

P_ HUB_T XN[0]

P_ HUB_T XP [1]

P_ HUB_T XN[1]

P_ HUB_T XP [2]

P_ HUB_T XN[2]

P_ HUB_T XP [3]

P_ HUB_T XN[3]

P_ GPP _T XP[0]

P_ GPP _T XN[0]

P_ GPP _T XP[1]

P_ GPP _T XN[1]

P_ GPP _T XP[2]/SAT A_ TX0P

P_ GPP _T XN[2]/SATA _T X0N

P_ GPP _T XP[3]/SAT A_ TX1P

P_ GPP _T XN[3]/SATA _T X1N

P_ GFX _T XP [0]

P_ GFX _T XN[0]

P_ GFX _T XP [1]

P_ GFX _T XN[1]

P_ GFX _T XP [2]

P_ GFX _T XN[2]

P_ GFX _T XP [3]

P_ GFX _T XN[3]

P_ GFX _T XP [4]

P_ GFX _T XN[4]

P_ GFX _T XP [5]

P_ GFX _T XN[5]

P_ GFX _T XP [6]

P_ GFX _T XN[6]

P_ GFX _T XP [7]

P_ GFX _T XN[7]

P_ GFX _T XP [8]

P_ GFX _T XN[8]

P_ GFX _T XP [9]

P_ GFX _T XN[9]

P_ GFX _T XP [10]

P_ GFX _T XN[10]

P_ GFX _T XP [11]

P_ GFX _T XN[11]

P_ GFX _T XP [12]

P_ GFX _T XN[12]

P_ GFX _T XP [13]

P_ GFX _T XN[13]

P_ GFX _T XP [14]

P_ GFX _T XN[14]

P_ GFX _T XP [15]

P_ GFX _T XN[15]

Ty pe0 Onl y

Ty pe2 Onl y

P_ ZVS S

P0A_ ZV SS

P0B_ ZV SS

SA TA_ ZVS S

ZIF-S OCKE T1331

AE 4

APUT XP0

AE 5

APUT XN0

AA5

APUT XP1

AB5

APUT XN1

AC 6

APUT XP2

AC 7

APUT XN2

AD5

APUT XP3

AD6

APUT XN3

APU_ GPP _T XP0

AT1 2

APU_ GPP _T XN0

AR 12

APU_ GPP _T XP1

AP13

APU_ GPP _T XN1

AR 13

AL13

AM13

AN14

AP14

GFX _T XP 0

D1

GFX _T XN0

E1

GFX _T XP 1

E3

GFX _T XN1

F3

GFX _T XP 2

F2

GFX _T XN2

G2

GFX _T XP 3

G1

GFX _T XN3

H1

GFX _T XP 4

H3

GFX _T XN4

J 3

GFX _T XP 5

J 2

GFX _T XN5

K2

GFX _T XP 6

K1

GFX _T XN6

L1

GFX _T XP 7

L3

GFX _T XN7

M3

GFX _T XP 8

M2

GFX _T XN8

N2

GFX _T XP 9

N1

GFX _T XN9

P1

GFX _T XP 10

P3

GFX _T XN10

R3

GFX _T XP 11

R2

GFX _T XN11

T2

T1

U1

GFX _T XP 13

U3

GFX _T XN13

V3

GFX _T XP 14

V2

GFX _T XN14

W2

GFX _T XP 15

W1

GFX _T XN15

Y1

APU_ P_ ZVS S

W7

APU_ P0A_ ZVS S

V8

APU_ P0B_ ZVS S

AT8

APU_ SAT A_Z VS S

AV6

Wi t hi n 1500 mi l s f r om APU

C906 C 0.22u6.3X/4

C905 C 0.22u6.3X/4

C912 C 0.22u6.3X/4

C911 C 0.22u6.3X/4

C909 C 0.22u6.3X/4

C910 C 0.22u6.3X/4

C907 C 0.22u6.3X/4

C908 C 0.22u6.3X/4

APU_ GPP _T XP0 [19]

APU_ GPP _T XN0 [19]

APU_ GPP _T XP1 [19]

APU_ GPP _T XN1 [19]

GFX _T XP0 [19]

GFX _T XN0 [19]

GFX _T XP1 [19]

GFX _T XN1 [19]

GFX _T XP2 [19]

GFX _T XN2 [19]

GFX _T XP3 [19]

GFX _T XN3 [19]

GFX _T XP4 [19]

GFX _T XN4 [19]

GFX _T XP5 [19]

GFX _T XN5 [19]

GFX _T XP6 [19]

GFX _T XN6 [19]

GFX _T XP7 [19]

GFX _T XN7 [19]

GFX _T XP8 [19]

GFX _T XN8 [19]

GFX _T XP9 [19]

GFX _T XN9 [19]

GFX _T XP10 [19]

GFX _T XN10 [19]

GFX _T XP11 [19]

GFX _T XN11 [19]

GFX _T XP12 [19]

GFX _T XN12 [19]

GFX _T XP13 [19]

GFX _T XN13 [19]

GFX _T XP14 [19]

GFX _T XN14 [19]

GFX _T XP15 [19]

GFX _T XN15 [19]

R222 196R1%/4

R253 X_ 200R/4

R325 X_ 200R/4

R309 1K1%/4

APU_ TX P0

APU_ TX N0

APU_ TX P1

APU_ TX N1

APU_ TX P2

APU_ TX N2

APU_ TX P3

APU_ TX N3

APU_ TX P0 [14]

APU_ TX N0 [14]

APU_ TX P1 [14]

APU_ TX N1 [14]

APU_ TX P2 [14]

APU_ TX N2 [14]

APU_ TX P3 [14]

APU_ TX N3 [14]

Not supp ort e d on AMD Fami l y 15h Mod el s 60h- 6 Fh

A A

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

Title

Title

Title

AM4 PCIE /S AT AE

AM4 PCIE /S AT AE

AM4 PCIE /S AT AE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICR O-S TAR T INT 'L C O.,LT D.

MS- 7A36. 30

MS- 7A36. 30

MS- 7A36. 30

1

of

of

of

4 50Monday, December 03, 2018

4 50Monday, December 03, 2018

4 50Monday, December 03, 2018

5

smd.db-x7.ru

D D

R313 1K/4

R311 1K/4

R316 1K/4

R312 1K/4

AZ_ BITCLK _R

AZ_ RS T_ R

AZ_ SY NC_R

AZ_ SDOUT _R

4

3

2

1

R345 X_ 10K/4

R329 10K/4

R308 10K/4

C C

B B

CP U_1P8

3VS B

R188 1K/4

R187 1K/4

R186 1K/4

R185 1K/4

R176 1K/4

R355 X_ 1K/4

R346 X_ 2.2K/4

R323 X_ 2.2K/4

R344 15K1%/4

R353 15K1%/4

R324 15K1%/4

R183 X_ 1K/4

R182 X_ 1K/4

R206 X_ 1K/4

R205 X_ 1K/4

R156 1K/4

R155 1K/4

AZ_ SDIN0

AZ_ SDIN1

AZ_ SDIN2

APU_ TC K

APU_ TMS

APU_ TDI

APU_ TR ST #

APU _DB RE Q#

APU_ TE ST 1

APU_ TE ST 0

APU_ TE ST 0

APU_ TE ST 1

APU_ TE ST 2

APU_ TE ST 11

APU_ TE ST 14

APU_ TE ST 17

APU_ TE ST 16

APU_ TE ST 18

APU_ TE ST 19

For Debug1

For Debug2

EMI

AZ_ BITCLK _R

AZ_ BITCL K[23]

AZ_ SDIN0[23]

AZ_ RS T#[23]

AZ_ SY NC[23]

AZ_ SDOUT[23]

TP 11

TP 5

TP 1

TP 2

TP 10

TP 14

TP 4

TP 12

TP 13

TP 3

TP 16

TP 9

R321 33R/4

R303 33R/4

R319 33R/4

R318 33R/4

APU_ TDI

APU_ TDO

APU_ TC K

APU_ TMS

APU_ TR ST #

APU_ DBR DY

APU _DB RE Q#

APU_ TE ST 0

APU_ TE ST 1

APU_ TE ST 2

APU_ TE ST 4

APU_ TE ST 5APU_ TE ST 2

APU_ TE ST 11

APU_ TE ST 14

APU_ TE ST 15

APU_ TE ST 16

APU_ TE ST 17

APU_ TE ST 18

APU_ TE ST 19

APU_ TE ST 46

APU_ TE ST 47

APU_ TE ST 28_H

APU_ TE ST 28_L

APU_ TE ST 31

APU_ TE ST 40

APU_ TE ST 41

C303 X_ C0.1u16X/4

AZ_ BITCLK _R

AZ_ SDIN0

AZ_ SDIN1

AZ_ SDIN2

AZ_ RS T_ R

AZ_ SY NC_R

AZ_ SDOUT _R

AW3

AM6

AM7

AA30

W30

AV3

AU5

AV4

AU1

AU2

AU4

A14

C14

C15

B15

B13

E13

D14

AT3

M22

D13

AB4

A13

C12

B12

C11

D11

G16

H16

AL4

P28

A16

L23

E6

E7

CP U1D

AZ_ BITC LK

AZ_ SD IN0

AZ_ SD IN1

AZ_ SD IN2

AZ_ RS T_ L

AZ_ SY NC

AZ_ SD OUT

TDI

TDO

TC K

TMS

TR ST _L

DBR DY

DBR EQ_ L

TE ST 0

TE ST 1/TMS

TE ST 2

TE ST 4

TE ST 5

TE ST 6

TE ST 10

TE ST 11

TE ST 14

TE ST 15

TE ST 16

TE ST 17

TE ST 18

TE ST 19

TE ST 46[13]

TE ST 47

TE ST 28_H

TE ST 28_L

TE ST 31

TE ST 40

TE ST 41

AUDI O

TEST

AM4

PART 4 OF 9

DP0_ TX P[0]

DP0_ TX N[0]

DP0_ TX P[1]

DP0_ TX N[1]

DP0_ TX P[2]

DP0_ TX N[2]

DP0_ TX P[3]

DP0_ TX N[3]

DP0_ AUX P

DP0_ AUX N

DI SPLAY- 0

DP0_ HPD

DP1_ TX P[0]

DP1_ TX N[0]

DP1_ TX P[1]

DP1_ TX N[1]

DP1_ TX P[2]

DP1_ TX N[2]

DP1_ TX P[3]

DP1_ TX N[3]

DP1_ AUX P

DP1_ AUX N

DI SPLAY- 1

DP1_ HPD

DP2_ TX P[0]

DP2_ TX N[0]

DP2_ TX P[1]

DP2_ TX N[1]

DP2_ TX P[2]

DP2_ TX N[2]

DP2_ TX P[3]

DP2_ TX N[3]

DP2_ AUX P

DP2_ AUX N

DI SPLAY- 2

DP2_ HPD

DP_ ZV SS

DP_ AUX _Z VSS

DP_ BLON

DP_ DIGON

DP_ VAR Y_ BL

DP_ ST ER EOS YNC

ZIF-S OCKE T1331

D2

C2

C3

B3

B4

A4

C5

C6

G10

H10

H9

D4

D5

D7

D8

F8

G8

E9

F9

F11

G11

D10

B6

B7

A7

A8

C8

C9

B9

B10

A10

A11

E10

F12

E12

G13

H13

H12

K14

Unus ed s i g nal s ar e l e f t unc onn ec t ed.

DP_ ZVS S

DP_ AUX_ ZVS S

DP_ BLON

DP_ DIGON

DP_ VAR Y_ BL

DP_ ST ER EOS YNC

K14 PI N: 有HDMI SPE C

DVI_ DDPC_ TX P2 [29]

DVI_ DDPC_ TX N2 [29]

DVI_ DDPC_ TX P1 [29]

DVI_ DDPC_ TX N1 [29]

DVI_ DDPC_ TX P0 [29]

DVI_ DDPC_ TX N0 [29]

DVI_ DDPC_ CLK _P [29]

DVI_ DDPC_ CLK _N [29]

DVI_D DPC_ CT RLC LK [29]

DVI_D DPC_ CT RLDA TA [29]

DVI_ DDPC_ HPD [29]

DP1_ TX0P _AP U [30]

DP1_ TX0N_ APU [30]

DP1_ TX1P _AP U [30]

DP1_ TX1N_ APU [30]

DP1_ AUXP [30]

DP1_ AUXN [30]

DP1_ DP_ HPD [30]

R170 2K1%/4

R159 150R1%/4

R147 1K/4

R148 X_ 1K/4

TP 8

TP 7

TP 6

的話需

CP U_1P8

For DVI

For DP t o VGA

Ty pe0 Onl y

For Debug2

Pul l - up ENBLE

Not su ppor t ed on AMD Fa mi l y 17h /Model s 00 h- 0Fh

Not s uppor t T ype2

功能

DVI_D DPC_ CT RLC LK

DVI_D DPC_ CT RLDA TA

A A

5

4

3

2

R173 2.2K/4

R175 2.2K/4

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

VC C3

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

AM4 DISP LAY /AUDIO

AM4 DISP LAY /AUDIO

AM4 DISP LAY /AUDIO

MS- 7A36. 30

MS- 7A36. 30

MS- 7A36. 30

1

5 50Monday, December 03, 2018

5 50Monday, December 03, 2018

5 50Monday, December 03, 2018

of

of

of

5

smd.db-x7.ru

ATX _5V SB 3VS B

R455

47K/4

T YPE 1_ CPU_ S EL :

1: NC ( T ype 2, 3 )

0: 3 . 3 V( T yp e0)

D D

TY PE 1_CP U_S EL

PWR _S W

C445

C0.1u16X/4

CP U_1P8_ S5

Q62

D

G

S

N-2N7002ET1G

PWR _S W

CP U_1P8

G

R179 1K/4

R141 1K/4

R152 1K/4

R144 1K/4

R145 1K/4

R189 300R/4

R172 300R/4

DS

Q85

X_ P-PA0 02FMG

PN514 Vgs

=0 . 5 V~1 . 0V

D

Q90

G

N-PM514BA

S

PWR _S B_S W

APU_ ALE RT #

APU_ PRO CHOT #

APU_ THE RMTR IP#

APU_ SIC

APU_ SID

PWR OK

RE SE T_ L

ATX _5V SB

T YPE 1_ CPU_ S EL :

1: 3 . 3 V( T yp e2, 3)

0: 1 . 8 V( T yp e0)

TY PE 1_CP U_S EL

VC C5 3VS B

R496

47K/4

D

G

S

Fo l l ow CRB

C C

3VS B

R386 10K/4

R393 10K/4

R363 10K/4

R397 10K/4

R396 10K/4

C358 X_ C100p50N/4

R518 10K/4

CP U_1P8_ S5

B B

VC C3

R146 4.7K/4

PR OCHOT #[38]

2

5

R377 22K/4

C349

X_ 10u6.3X/6

Q27

6

1

3

4

NN-CMKT 3904

PWR BTN#

APU_ AM4R1

BLINK

WAK E_ L

PC IE_R ST

S5_ MUX_ CTR L

RS MRS T#

C346

1u6.3X/4

APU_ PRO CHOT #PR OCHOT #_LS

PR OCHOT #_LS

I B= ( V cc 3- V be) / 1 0k

( 3 . 3 - 0. 9 5) / 1 0k =0. 2 35 mA

I C= ( V CC2 - Vc e) / 1 0k

( 3 . 3 - 0. 2 ) / 1 0k =0 . 3 1mA

R495

X_ 47K/4

CP U_1P8

Q63

N-2N7002ET1G

4

VC C3

G

D S

S

Q91

G

D

N-PM514BA

PN514 Vgs

=0 . 4 5V~ 1. 2 V

Q94

P-P A002FMG

PWR _S W

APU_ SV C[38]

APU_ SV D[38]

APU_ SV T[38]

APU_ PWR OK[38]

ALL_ PWR _P WR GD[37]

APU_ SL P_S 3#[45]

SL P_S 5#[20,31,33,34,45]

S5_ MUX_ CTR L[41]

PWR BTN#[20,45]

SP KR[42]

RS MRS T#[20,37]

SY SR ES T#[7,32,37,42]

PC IE_R ES T#[19]

KBR ST #[20]

APU_ WAK E#[16,19,22]

APU_ LPC _P ME#[16]

APU_ SIC[20]

APU_ SID[20]

APU_ AM4R1[31,34,35,36,37]

RT CC LK[7]

APU_ SV C

R198 X_ R/2

APU_ SV D

R197 X_ R/2

APU_ SV T

R196 X_ R/2

APU_ PWR OK

R190 X_ R/2

ALL_ PWR _P WR GD

KBR ST #

D14 X _S -LRB520S -40T1G

3. 3 V

APU_ PRO CHOT #

APU_ THE RMTR IP#

APU_ SL P_S 3#

SL P_S 5#

APU_ S0A3_ GPIO

S5_ MUX_ CTR L

PWR BTN#

BLINK

SP KR

RS MRS T#

SY SR ES T#

PC IE_R ES T#

KBR ST #

APU_ SIC

APU_ SID

APU_ ALE RT #

APU_ AM4R1

COR ET YPE 0

COR ET YPE 1

ITE6516_ URDBG[30]

RT CC LK

SL P_S 3#[20,31,32,34,35,37]

R398 33R/4

R384 X_ R/2

R399 X_ R/2

ITE6516_ URDBG

APU_ 32K_ X1

APU_ 32K_ X2

3

C431 C0.1u16X/4

53

U44

VCC

1

A

4

Y

2

B

GND

NC7S Z08M5X

SL P_S 3# APU_ SL P_S 3#

R483 X_ 0R/4

Wi t hi n 5 00 mi l s

CP U1E

D17

SV C

SV D

SV T

PWR OK

RE SE T_ L

PC IE_R ST

KBR ST _L

WAK E_ L

SV C

C17

SV D

A17

SV T

E16

PWR OK

AM3

PWR _G OOD

B16

RE SE T_ L

1. 8 V

H15

PR OCHOT _L

A19

THE RMT RIP_ L

AT2

SL P_ S3_ L

AP2

SL P_ S5_ L

AR 3

S0A 3_G PIO/AGPIO10/SG PIO0_C LK

AP4

S5 _MUX_ CT RL /EG PIO42

AN5

PWR _B TN_ L/AGPIO0

AT5

BLINK/AGP IO11

AW23

SP KR /A GPIO91

AP5

RS MRS T_ L

AM4

SY S_ R ESE T_ L/AGP IO1

AL7

PC IE_R ST _L /EGP IO26

AN24

ES PI_ RES E T_ L/KBRS T_ L

AL5

WAK E_ L/AGPIO2

AL2

LP C_P ME_ L/AGPIO22

B18

SIC

C18

SID

D16

ALE RT _L

AL8

AM4R 1

AM24

COR ET YP E[0]

AN9

COR ET YP E[1]

AN23

FA NIN0 /AGPIO84

AP23

FA NOUT0/AGP IO85

AP8

RT CC LK

AW5

X32K _X 1

AW6

X32K _X 2

APU_ SL P_S 3#

APU_ S0A3_ GPIO

MI SCACPI

FANSVI

RTC

R337 100K/4

R301 2.2K/4

3VS B

SC L0/I2C2_ SC L/EGP IO113

SD A0/I2 C2_ SDA/E GPIO114

SC L1/I2C3_ SC L/AGPIO19

SD A1/I2 C3_ SDA/AG PIO20

SMBus

AGP IO5/DEVS LP 0

AGP IO9/SG PIO0_ DATAOU T

AGP IO23/SG PIO0_ LOAD

AGP IO40/S GPIO0_ DATAIN

GE NINT1_L /AGPIO89

GE NINT2_L /AGPIO90

SA TA_ ACT _L /AGPIO130

GPI O

CL K_R EQ 0_L/S ATA_ IS0_ L/SAT A_ ZP0_ L/AGPIO92

CL K_R EQ 3_L/S ATA_ IS1_ L/SAT A_ ZP1_ L/EGP IO131

OC

SENSE

AM4

PART 5 OF 9

CL K_R EQ 1_L /A GPIO115

CL K_R EQ 2_L /A GPIO116

CL K_R EQ G_ L/OSCIN/EG PIO132

USB _OC 0_L /AGPIO16

USB _OC 1_L /TDI/AGPIO17

USB _OC 2_L /TCK/AG PIO18

USB _OC 3_L /TDO/AGPIO24

VDDC R_ CP U_ SE NSE

VDDC R_ S OC_ SE NSE

VDDIO_ MEM_ S3_ SE NSE

ZIF-S OCKE T1331

2

AGP IO3

AGP IO4

AGP IO6

AGP IO8

AGP IO86

EG PIO70

EG PIO95

EG PIO96

EG PIO97

EG PIO98

EG PIO99

EG PIO100

VS S_ SE NS E_ A

VDDP _S ENS E

VS S_ _ SENS E_ B

VC C3

R364 8.2K/4

R354 X_ 10K/4

AMD Hardwar e Val i da t ed Boot

( HVB)

0: E nabl e

1 or NC: Di s abl e

AU25

SC L0

AV25

SDA 0

AK3

SC L1

AK2

SDA 1

AT6

AGP IO3

USB _MODE_ R

AR 6

AGP IO5_DEV SLP 0

AP22

AN8

AP7

AN2

AN3

iGPU_ LE D

AR 4

AW17

AGP IO86

GE NINT1_ L

AV22

CLR _C ASO PN_E VENT

AU23

SAT A_ LED#

AM22

CAS EOP EN_ EVE NT#

AT1 8

AW11

AV12

GPIO97_ CPU

AW12

GPIO98_ DRAM

AU13

GPIO99_ VGA

AV13

GPIO100_ DEVIC E

AT1 4

CLK _R EQ0

AT2 3

CLK _R EQ1

AV24

CLK _R EQ2

AT2 4

CLK _R EQ3

AL23

CLK _R EQG

AR 22

APU_ OC0#

AL1

APU_ OC1#

AM1

APU_ OC2#

AR 1

APU_ OC3#

AP1

VDDC R_ CPU _S ENSE +

F14

VDDC R_ SOC _S ENS E+

E15

VDDIO_ MEM_S 3_S ENS E+

G14

VS S_ SE NSE _A

F15

CP U_VD DP_S ENS E

AL22

VS S_ SE NSE _B

AM23

GE NINT1_ L

R416 100R1%/4

R413 100R1%/4

R281 X_ 0R/4

R280 X_ 0R/4

R287 X_ R/2

TP 22

CLR _C ASO PN_E VENT [45]

SAT A_ LED# [14,42]

CAS EOP EN_ EVE NT# [45]

GPIO97_ CPU [43]

GPIO98_ DRAM [43]

GPIO99_ VGA [43]

GPIO100_ DEVIC E [43]

APU_ OC0# [26]

APU_ OC1# [26]

CP 3 X_ COP PER

CP 5 X_ COP PER

1

SC L0

SDA 0

SC L1

SDA 1

AGP IO5_DEV SLP 0

R365 10K/4

R392 10K/4

SC LK0 [10,38,41,45]

SDA TA0 [10,38,41,45]

SC LK_ PCIE [19]

SDA TA_ PCIE [19]

AGP IO3 [7]

USB _MODE [31]

CP UFAN1_MODE [21]

SY SF AN1_MODE [21]

iGPU_ LE D [43]

PCI E X16 /X 8 L ED Cont r ol

GPI O97 ~100 f or Debug LE D

VC C3

R348 10K/4

R375 560R/4

3VS B

R285 200K/4

R292 200K/4

R302 200K/4

R299 200K/4

VDDC R_ CPU _S ENSE + [38]

VDDC R_ SOC _S ENS E+ [38]

VDDIO_ MEM_S 3_S ENS E+ [34]

VDDC R_ CPU_ SE NSE - [38]

VDDC R_ SOC _S ENS E- [38]

CP U_VD DP_S ENS E [36]

TP 21

R342 10K/4

R412 10K/4

R336 10K/4

R335 10K/4

R341 10K/4

R424 2.2K/4

R415 2.2K/4

R282 2.2K/4

R279 2.2K/4

R417 10K/4

VC C3

3VS B

VC C3

by c he ck l i s t

USB _MODE_ R

CLR _C ASO PN_E VENT

For K T YPE FAN

CAS EOP EN_ EVE NT#

SAT A_ LED#

APU_ OC0#

APU_ OC1#

APU_ OC2#

APU_ OC3#

CLK _R EQ0

CLK _R EQ1

CLK _R EQ2

CLK _R EQ3

CLK _R EQG

La yout : Pl ac e x' t al wi t hi n 1. 5 i nch of APU

APU_ 32K_ X2

Y2

APU_ 32K_ X1

12

A A

32.768KHZ12.5p

R317 20M/6

C296

C15p50N/6

PL ACE T HES E C OMPONE NTS CL OS E T O

U600, A ND USE G ROUND GUAR D F OR

32K_ X1 AND 32K _X 2

C295

C15p50N/6

5

AM4 CPU TYPE Ci r cui t

Change by CRB r ev. E

3VS B

CP U_1P8_ S5

R402

1K/4

R405

X_ 1K/4

COR ET YPE 1

R401

10K/4

ATX _5V SB

B

R400

47K/4

TY PE1_ SE L

CE

Q78

N-SS T3904

ATX _5V SB

G

4

R383

47K/4

D

Q69

N-2N7002ET1G

S

CPU

BR

SR

RV/ Z P

TY PE 1_CP U_S EL [36,37,41]

T YPE 1_ CP U_ S EL

0: BR / NA

1: S T/ R V/ ZP

T YPE

CORET YP E

01

0

0 0

1

0NA

0

1

2

1 1

3

COR ET YPE 0

CORE TYP E0

0: BR / SR

1: R V/ ZP

3

CP U_1P8_ S5

R443

1K/4

R444

4.7K/4

ATX _5V SB

B

T YPE 1_ CP U_ S EL

0: BR / NA

1: S T/ R V/ ZP

R474

47K/4

TY PE 0_CP U_S EL

CE

Q87

N-SS T3904

TY PE 0_CP U_S EL [36,37]

2

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

Title

Title

Title

AM4 SV I/AC PI/GPIO

AM4 SV I/AC PI/GPIO

AM4 SV I/AC PI/GPIO

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICR O-S TAR T INT 'L C O.,LT D.

MS- 7A36. 30

MS- 7A36. 30

MS- 7A36. 30

1

of

of

of

6 50Monday, December 03, 2018

6 50Monday, December 03, 2018

6 50Monday, December 03, 2018

5

smd.db-x7.ru

4

3

2

1

EMI

LPC CLK 1

C313 X_ C0.1u16X/4

CP U1F

LPC CLK 0

LPC CLK 1

LPC _AD 0

LPC _AD 1

LPC _AD 2

LPC _AD 3

LPC _LF RAME #

LPC _LDR Q0#

LPC _S ER IRQ

LPC _C LKR UN

C59 X_ C100p50N/4

SP I_CLK _RSP I_CLK

SP I_CS #

SP I_DATA IN

SP I_DATA OUT

SP I_WP #_R

SP I_HOLD#_R

PE 1_GF X_ CLKP[19]

PE 1_GF X_ CLKN[19]

PE 2_GP P_C LKP[19]

PE 2_GP P_C LKN[19]

PE 3_GP P_C LKP[19]

PE 3_GP P_C LKN[19]

APU_ CLK P[16]

APU_ CLK N[16]

APU_ 48M_X1

APU_ 48M_X2

LPC _AD 0[20,42]

LPC _AD 1[20,42]

LPC _AD 2[20,42]

LPC _AD 3[20,42]

R330 22R/4

R352 0R/4

R314 2K1%/4

R28 33R /4

R338 10R1%/4

TP M_LPC CLK 0[42]

SIO_ LPC CLK1[20]

D D

LPC _LF RAME #[20,42]

LPC _LDR Q0#[20]

LPC _S ER IRQ[20,42]

LPC _R ST #[20,42]

EMI

SP I_CLK

C314 X_ C0.1u16X/4

C C

B B

AU20

LP CCL K0/EGP IO74

AU19

LP CCL K1/EGP IO75

AW20

LAD0/E GPIO104

AV21

LAD1/E GPIO105

AT2 1

LAD2/E GPIO106

AT2 0

LAD3/E GPIO107

AW18

LF RAME _L/E GPIO109

AT1 5

ES PI_A LER T_ L/LDR Q0_L /EGPIO108

AW21

SE RIR Q/AGPIO87

AV19

LP C_C LKR UN_ L/AGPIO88

AV18

LP C_P D_L /AGPIO21

AU22

LPC _R ST _L

AW14

SP I_CL K/ES PI_C LK/EG PIO117

AT1 7

SP I_CS 1_ L/EGP IO118

AW15

SP I_CS 2_ L/ES PI_C S_ L/EGP IO119

AU14

SP I_DI/ES PI_DA T1/EGP IO120

AU16

SP I_DO/ES PI_ DAT0/EG PIO121

AV16

SP I_WP _L/E SPI_ DAT2/E GPIO122

AV15

SP I_HOLD _L/E SPI_ DAT3 /EG PIO133

AU17

SP I_TP M_C S_ L/AGPIO76

AF 6

GF X_ CLK P

AF 7

GF X_ CLK N

AG5

GPP _C LK0P

AG6

GPP _C LK0N

AH4

GPP _C LK1P

AH5

GPP _C LK1N

AH7

GPP _C LK2P

AH8

GPP _C LK2N

AJ 6

GPP _C LK3P

AJ 7

GPP _C LK3N

AJ 1

X48M_ X1

AH1

X48M_ X2

SPI ROM( 1. 8V)

La yout : Pl ac e x' t al wi t hi n 1. 5 i nch of APU

R261 1M/6

Y1

3 4

GND

12

GND

A A

48MHZ12p

C243

10p50N/6

PL ACE T HES E C OMPONE NTS CL OSE T O U600, A ND USE

GR OUND G UARD FOR 48M_X 1 A ND 48M_X 2

R262

49.9R1%/4

C251

10p50N/6

5

APU_ 48M_X2

APU_ 48M_X1

SP I_CS #

R517 X_ R/2

R492 0R/4

SP I_WP #_R

R504 X_ R/2

SPI CS # < 20p F

D0G- 0 40 251 0- S I 0

P. S Cl os e t o J S PI 1

D29

12

X_ ES D-SF I0402-050E100NP

LPC/ S PI /USB/ CLOCK

48M_O SC

USB _HS D0P

USB _HS D0N

USB _HS D1P

USB _HS D1N

USB _HS D2P

USB _HS D2N

USB _HS D3P

USB _HS D3N

USB2. 0

USB _S S_ 0TX P

USB _S S_ 0TX N

USB _S S_ 0RX P

USB _S S_ 0RX N

USB _S S_ 1TX P

USB _S S_ 1TX N

USB _S S_ 1RX P

USB _S S_ 1RX N

USB _S S_ 2TX P

USB3. 0

USB _S S_ 2TX N

USB _S S_ 2RX P

USB _S S_ 2RX N

USB _S S_ 3TX P

ZIF-S OCKE T1331

VC C

HOLD(IO3)

CL K

DI(IO0)

J SP I1

1 2

3 4

5

7 8

9

H2X6[10]M-2PITCH

USB _S S_ 3TX N

USB _S S_ 3RX P

USB _S S_ 3RX N

USB _S S_ ZV SS

USB _S S_ ZV DDP

USB _ZV SS

USB 0_Z VS S

USB 1_Z VS S

USB 2_Z VS S

USB 3_Z VS S

CP U_1P8

8

SP I_HOLD#

7

SP I_CLK

6

5

DATA OUT

SP I_DATA OUT

SP I_CLK

6

SP I_HOLD#_R

1211

ALL_ PW R_ MUX[37 ]

CLOCKLPC SPI

AM4

PART 6 OF 9

SP I1

CS #

DATA IN

SP I_WP #

4

1

CS

2

DO(IO1)

3

WP( IO2)

4

GND

MX25U12873FM2I

AVL : M3 1- 2 51 288 3- W03

CP U_1P8 CP U_1P8

SP I_DATA IN

SP I_CS #

SP I_SW _S EL

SP I_WP #_R

12

D30

X_ ES D-MLVS 0402L04

APU_ 48M_OS C

AR 7

AU7

AU8

AW8

AW9

AU10

AU11

AV9

AV10

AF 3

AF 4

Y3

Y4

AB1

AC 1

AA2

AA3

AC 3

AC 4

AD2

AE 2

AG2

AG3

AE 1

AF 1

Onl y Suppo rt Ty pe0

USB _S S_Z VS S

AJ 4

USB_ S S_Z VDDP

AK8

USB_ ZV SS

AT1 1

USB 0_ZV SS

AJ 3

USB 1_ZV SS

AN6

USB 2_ZV SS

AK6

USB 3_ZV SS

AK5

Wi t hi n 1000 mi l s f r om APU

Onl y Supp ort

Ty pe2/ 3

C449 10u6.3X/6

C452 C0.1u16X/4

R527 X_ R/2

R525 0R/4

R539 X_ R/2

APU_ USB 0+ [26]

APU_ USB 0- [26]

APU_ USB 1+ [26]

APU_ USB 1- [26]

APU_ USB 2+ [26]

APU_ USB 2- [26]

APU_ USB 3+ [26]

APU_ USB 3- [26]

APU_ USB_ SS TX 0+ [26]

APU_ USB_ SS TX 0- [26]

APU_ USB_ S SRX 0+ [26]

APU_ USB_ SS RX 0- [26]

APU_ USB_ SS TX 1+ [26]

APU_ USB_ SS TX 1- [26]

APU_ USB_ S SRX 1+ [26]

APU_ USB_ SS RX 1- [26]

APU_ USB_ SS TX 2+ [26]

APU_ USB_ SS TX 2- [26]

APU_ USB_ S SRX 2+ [26]

APU_ USB_ SS RX 2- [26]

APU_ USB_ SS TX 3+ [26]

APU_ USB_ SS TX 3- [26]

APU_ USB_ S SRX 3+ [26]

APU_ USB_ SS RX 3- [26]

R275 1K1%/4

R273 1K1%/4

R305 11.8K1%/4

R268 X_ 200R1%/4

R274 X_ 200R1%/4

R270 X_ 200R1%/4

R272 X_ 200R1%/4

CP U_1P8

SP I_HOLD#_RSP I_DATA IN

SP I_DATA OUT

3

TP 20

SP I_SW _S EL

REAR USB3. 0

LAN+USB3. 0

R526 X_ 10K/4

R505 X_ 10K/4

R524 10K/4

REAR USB3. 0

LAN+USB3. 0

CP U_VD DP_S 5

VDDP_S 5

( S5 Wake

I mpl eme nt ed)

or

VDDP

( S5 Wak e Not

I mpl eme nt ed)

SP I_HOLD#

SP I_WP #

SP I_CS #

St r appi ng Opt i ons

VC C3 VC C3

LPC CLK 1

( Def aul t )

SP I_CLK _R

SPI _ CLK

( Def aul t )

PWR _S B_S W

R378

10K/4

R373

X_ 2K1%/4

AM4 LPC/S PI/US B/CL K/S TR AP

AM4 LPC/S PI/US B/CL K/S TR AP

AM4 LPC/S PI/US B/CL K/S TR AP

Custom

Custom

Custom

PUL L

HI GH

PUL L

L OW

PUL L

HI GH

PUL L

L OW

VC C3

R349

X_ 10K/4

LPC CLK 0

R343

2K1%/4

LPCCL K0 LPCCL K1

LP C dev i c e

Boot F ai l T i mer

En abl ed

LP C dev i c e

Boot F ai l T i mer

Di s a bl e d

( Def aul t )

3VS B

R367

10K/4

AGP IO3[6]

R366

X_ 2K1%/4

AGPI O3

En han ce d

Res et l og i c

( Def aul t )

T ra di t i o nal

Res et l og i c

RT CC LK[6]

2

Conf i g ur ed f o r

I nt e rn al c l oc k g ene ra t or

Conf i g ur ed f o r

Ex t er na l c l oc k ge ner at or

? ? ? ??

Use 48Mhz c ry st a l c l oc k

and gene ra t e bo t h i nt e rn al

and ext e r nal c l oc ks

Use 1 00Mhz PCI E c l oc k as

r ef e re nce cl o ck and g ener a t e

i nt er na l c l oc ks onl y

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

R360

10K/4

R340

X_ 2K1%/4

LPC _LF RAME #

R320

10K/4

R307

X_ 2K1%/4

SI O_ LFRAME

SPI ROM

( Def aul t )

LP C ROM

3VS BCP U_1P8

R315

10K/4

R306

X_ 2K1%/4

SY SR ES T#[6,32,37,42]

R297

10K/4

R298

X_ 2K1%/4

SY SREST #

Nor ma l r es et

mod e

( Def aul t )

s hor t r es et

mod e

RTCCLK

RTC C oi n Bat t er y

PUL L

i s on boar d

HI GH

( Def aul t )

RTC C oi n Bat t er y

PUL L

L OW

i s not on b oar d

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

MS- 7A36. 30

MS- 7A36. 30

MS- 7A36. 30

1

of

of

of

7 50Monday, December 03, 2018

7 50Monday, December 03, 2018

7 50Monday, December 03, 2018

5

smd.db-x7.ru

VC ORE

D D

C C

B B

A A

W10

W12

AA10

AA12

AB11

AB13

AC 2

AC 10

AC 12

AD7

AD9

AD11

AD13

AE 10

AE 12

AF 11

AF 13

AG7

AG10

AG12

AG14

AG16

AG18

AG20

AG22

AG24

AG26

AH3

AH6

AH9

AH11

AH13

AH15

AH17

AH19

AH21

AH23

AH25

AH27

AJ 10

AJ 12

AJ 14

AJ 22

AJ 24

AK11

AK13

AL10

AL12

AL14

AM2

AM8

AN7

AN10

AN13

AP12

AR 2

AU3

AU6

AU9

AU12

AU15

AV11

AV14

M7

N3

N6

P2

R7

T3

T6

T9

U2

U10

V9

V11

W3

W6

Y2

Y9

Y11

Y13

AA7

AB3

AB6

AB9

AE 3

AE 6

AF 2

AF 9

AJ 2

AK7

AK9

AL3

AL6

AP3

AP9

AT4

AV5

AV8

CP U1H

VDDC R_ CP U_ 0

VDDC R_ CP U_ 1

VDDC R_ CP U_ 2

VDDC R_ CP U_ 3

VDDC R_ CP U_ 4

VDDC R_ CP U_ 5

VDDC R_ CP U_ 6

VDDC R_ CP U_ 7

VDDC R_ CP U_ 8

VDDC R_ CP U_ 9

VDDC R_ CP U_1 0

VDDC R_ CP U_1 1

VDDC R_ CP U_1 2

VDDC R_ CP U_1 3

VDDC R_ CP U_1 4

VDDC R_ CP U_1 5

VDDC R_ CP U_1 6

VDDC R_ CP U_1 7

VDDC R_ CP U_1 8

VDDC R_ CP U_1 9

VDDC R_ CP U_2 0

VDDC R_ CP U_2 1

VDDC R_ CP U_2 2

VDDC R_ CP U_2 3

VDDC R_ CP U_2 4

VDDC R_ CP U_2 5

VDDC R_ CP U_2 6

VDDC R_ CP U_2 7

VDDC R_ CP U_2 8

VDDC R_ CP U_2 9

VDDC R_ CP U_3 0

VDDC R_ CP U_3 1

VDDC R_ CP U_3 2

VDDC R_ CP U_3 3

VDDC R_ CP U_3 4

VDDC R_ CP U_3 5

VDDC R_ CP U_3 6

VDDC R_ CP U_3 7

VDDC R_ CP U_3 8

VDDC R_ CP U_3 9

VDDC R_ CP U_4 0

VDDC R_ CP U_4 1

VDDC R_ CP U_4 2

VDDC R_ CP U_4 3

VDDC R_ CP U_4 4

VDDC R_ CP U_4 5

VDDC R_ CP U_4 6

VDDC R_ CP U_4 7

VDDC R_ CP U_4 8

VDDC R_ CP U_4 9

VDDC R_ CP U_5 0

VDDC R_ CP U_5 1

VDDC R_ CP U_5 2

VDDC R_ CP U_5 3

VDDC R_ CP U_5 4

VDDC R_ CP U_5 5

VDDC R_ CP U_5 6

VDDC R_ CP U_5 7

VDDC R_ CP U_5 8

VDDC R_ CP U_5 9

VDDC R_ CP U_6 0

VDDC R_ CP U_6 1

VDDC R_ CP U_6 2

VDDC R_ CP U_6 3

VDDC R_ CP U_6 4

VDDC R_ CP U_6 5

VDDC R_ CP U_6 6

VDDC R_ CP U_6 7

VDDC R_ CP U_6 8

VDDC R_ CP U_6 9

VDDC R_ CP U_7 0

VDDC R_ CP U_7 1

VDDC R_ CP U_7 2

VDDC R_ CP U_7 3

VDDC R_ CP U_7 4

VDDC R_ CP U_7 5

VDDC R_ CP U_7 6

VDDC R_ CP U_7 7

VDDC R_ CP U_7 8

VDDC R_ CP U_7 9

VDDC R_ CP U_8 0

VDDC R_ CP U_8 1

VDDC R_ CP U_8 2

VDDC R_ CP U_8 3

VDDC R_ CP U_8 4

VDDC R_ CP U_8 5

VDDC R_ CP U_8 6

VDDC R_ CP U_8 7

VDDC R_ CP U_8 8

VDDC R_ CP U_8 9

VDDC R_ CP U_9 0

VDDC R_ CP U_9 1

VDDC R_ CP U_9 2

VDDC R_ CP U_9 3

VDDC R_ CP U_9 4

VDDC R_ CP U_9 5

VDDC R_ CP U_9 6

VDDC R_ CP U_9 7

VDDC R_ CP U_9 8

POWE R

AM4

PART 8 OF 9

5

VDDC R_ S OC_ 0

VDDC R_ S OC_ 1

VDDC R_ S OC_ 2

VDDC R_ S OC_ 3

VDDC R_ S OC_ 4

VDDC R_ S OC_ 5

VDDC R_ S OC_ 6

VDDC R_ S OC_ 7

VDDC R_ S OC_ 8

VDDC R_ S OC_ 9

VDDC R_ S OC_ 10

VDDC R_ S OC_ 11

VDDC R_ S OC_ 12

VDDC R_ S OC_ 13

VDDC R_ S OC_ 14

VDDC R_ S OC_ 15

VDDC R_ S OC_ 16

VDDC R_ S OC_ 17

VDDC R_ S OC_ 18

VDDC R_ S OC_ 19

VDDC R_ S OC_ 20

VDDC R_ S OC_ 21

VDDC R_ S OC_ 22

VDDC R_ S OC_ 23

VDDC R_ S OC_ 24

VDDC R_ S OC_ 25

VDDC R_ S OC_ 26

VDDC R_ S OC_ 27

VDDC R_ S OC_ 28

VDDC R_ S OC_ 29

VDDC R_ S OC_ 30

VDDC R_ S OC_ 31

VDDC R_ S OC_ 32

VDDC R_ S OC_ 33

VDDC R_ S OC_ 34

VDDC R_ S OC_ 35

VDDC R_ S OC_ 36

VDDC R_ S OC_ 37

VDDC R_ S OC_ 38

VDDC R_ S OC_ 39

VDDC R_ S OC_ 40

VDDC R_ S OC_ 41

VDDC R_ S OC_ 42

VDDC R_ S OC_ 43

VDDC R_ S OC_ 44

VDDC R_ S OC_ 45

VDDC R_ S OC_ 46

VDDC R_ S OC_ 47

VDDC R_ S OC_ 48

VDDC R_ S OC_ 49

VDDC R_ S OC_ 50

VDDC R_ S OC_ 51

VDDC R_ S OC_ 52

VDDC R_ S OC_ 53

VDDC R_ S OC_ 54

VDDC R_ S OC_ 55

VDDC R_ S OC_ 56

VDDC R_ S OC_ 57

VDDC R_ S OC_ 58

VDDC R_ S OC_ 59

VDDC R_ S OC_ 60

VDDC R_ S OC_ 61

VDDC R_ S OC_ 62

VDDC R_ S OC_ 63

VDDC R_ S OC_ 64

VDDC R_ S OC_ 65

VDDC R_ S OC_ 66

VDDC R_ S OC_ 67

VDDC R_ S OC_ 68

VDDC R_ S OC_ 69

VDDC R_ S OC_ 70

VDDC R_ S OC_ 71

VDDC R_ S OC_ 72

VDDC R_ SO C_ S5_ 0

VDDC R_ SO C_ S5_ 1

ZIF-S OCKE T1331

B5

B8

B11

B14

B17

B20

C4

C7

C10

C13

C16

C19

D3

E2

F7

F10

F13

F16

G3

G6

G9

G12

G15

G18

H2

J 7

J 10

J 12

J 14

J 16

K3

K6

K9

K11

K13

K15

L2

L10

L12

L14

L16

L18

L20

L22

L24

L26

M9

M11

M13

M15

M17

M19

M21

M23

M25

N10

N12

N14

N16

N18

N20

N22

N24

N26

P9

P11

P13

R10

R12

T11

T13

U12

V13

AJ 18

AK18

VC CP_ NB

VC CP_ NB_S 5

0. 9 A

4

3VS B

R537

10K1%/4

CP U_V_ AUDIO_ EN

C397

C0.1u16X/4

4

5VDUAL

R529 10R1%/4

3VS B

C459

10u6.3X/6

AVL : I 31 - 37 30S 02 - N62

CP U1G

K36

VDDIO_ MEM_ S3_ 0

K39

VDDIO_ MEM_ S3_ 1

L32

VDDIO_ MEM_ S3_ 2

L35

VDDIO_ MEM_ S3_ 3

L38

VDDIO_ MEM_ S3_ 4

M29

VDDIO_ MEM_ S3_ 5

M31

VDDIO_ MEM_ S3_ 6

M34

VDDIO_ MEM_ S3_ 7

M37

VDDIO_ MEM_ S3_ 8

N28

VDDIO_ MEM_ S3_ 9

N30

VDDIO_ MEM_ S3_ 10

N33

VDDIO_ MEM_ S3_ 11

N36

VDDIO_ MEM_ S3_ 12

N39

VDDIO_ MEM_ S3_ 13

P27

VDDIO_ MEM_ S3_ 14

P29

VDDIO_ MEM_ S3_ 15

P32

VDDIO_ MEM_ S3_ 16

P35

VDDIO_ MEM_ S3_ 17

P38

VDDIO_ MEM_ S3_ 18

R28

VDDIO_ MEM_ S3_ 19

R31

VDDIO_ MEM_ S3_ 20

R34

VDDIO_ MEM_ S3_ 21

R37

VDDIO_ MEM_ S3_ 22

T27

VDDIO_ MEM_ S3_ 23

T29

VDDIO_ MEM_ S3_ 24

T33

VDDIO_ MEM_ S3_ 25

T36

VDDIO_ MEM_ S3_ 26

T39

VDDIO_ MEM_ S3_ 27

U28

VDDIO_ MEM_ S3_ 28

U30

VDDIO_ MEM_ S3_ 29

U32

VDDIO_ MEM_ S3_ 30

U35

VDDIO_ MEM_ S3_ 31

U38

VDDIO_ MEM_ S3_ 32

V27

VDDIO_ MEM_ S3_ 33

V29

VDDIO_ MEM_ S3_ 34

V31

VDDIO_ MEM_ S3_ 35

V34

VDDIO_ MEM_ S3_ 36

V37

VDDIO_ MEM_ S3_ 37

W28

VDDIO_ MEM_ S3_ 38

W33

VDDIO_ MEM_ S3_ 39

W34

VDDIO_ MEM_ S3_ 40

W36

VDDIO_ MEM_ S3_ 41

W39

VDDIO_ MEM_ S3_ 42

Y27

VDDIO_ MEM_ S3_ 43

Y29

VDDIO_ MEM_ S3_ 44

Y31

VDDIO_ MEM_ S3_ 45

Y32

VDDIO_ MEM_ S3_ 46

Y35

VDDIO_ MEM_ S3_ 47

Y38

VDDIO_ MEM_ S3_ 48

AA28

VDDIO_ MEM_ S3_ 49

AA34

VDDIO_ MEM_ S3_ 50

AA37

VDDIO_ MEM_ S3_ 51

AB27

VDDIO_ MEM_ S3_ 52

AB29

VDDIO_ MEM_ S3_ 53

AB31

VDDIO_ MEM_ S3_ 54

AB32

VDDIO_ MEM_ S3_ 55

AB33

VDDIO_ MEM_ S3_ 56

AB36

VDDIO_ MEM_ S3_ 57

AB39

VDDIO_ MEM_ S3_ 58

AC 28

VDDIO_ MEM_ S3_ 59

AC 30

VDDIO_ MEM_ S3_ 60

AC 32

VDDIO_ MEM_ S3_ 61

AC 35

VDDIO_ MEM_ S3_ 62

AC 38

VDDIO_ MEM_ S3_ 63

AD27

VDDIO_ MEM_ S3_ 64

AD29

VDDIO_ MEM_ S3_ 65

AD31

VDDIO_ MEM_ S3_ 66

AD34

VDDIO_ MEM_ S3_ 67

AD37

VDDIO_ MEM_ S3_ 68

AE 28

VDDIO_ MEM_ S3_ 69

AE 30

VDDIO_ MEM_ S3_ 70

AE 33

VDDIO_ MEM_ S3_ 71

AE 36

VDDIO_ MEM_ S3_ 72

AE 39

VDDIO_ MEM_ S3_ 73

AF 27

VDDIO_ MEM_ S3_ 74

AF 29

VDDIO_ MEM_ S3_ 75

AF 32

VDDIO_ MEM_ S3_ 76

AF 35

VDDIO_ MEM_ S3_ 77

AF 38

VDDIO_ MEM_ S3_ 78

AG33

VDDIO_ MEM_ S3_ 79

AG34

VDDIO_ MEM_ S3_ 80

AG35

VDDIO_ MEM_ S3_ 81

AG37

VDDIO_ MEM_ S3_ 82

AH39

VDDIO_ MEM_ S3_ 83

VDDI O_ A UDI O Circuit

CP U_V_ AUDIO_C NTL

U49

1

POK

2

EN

3

VIN

5

NC

POWE R

AM4

PART 7 OF 9

ZIF-S OCKE T1331

4

VOUT

VDD

FB

GND8GND

GS 7133SO

9

VDDP _0

VDDP _1

VDDP _2

VDDP _3

VDDP _4

VDDP _5

VDDP _6

VDDP _7

VDDP _8

VDDIO_ AUDIO

VDD_ 18_ 0

VDD_ 18_ 1

VDD_ 33_ 0

VDD_ 33_ 1

VDDP _S 5_ 0

VDDP _S 5_ 1

VDD_ 18_ S5_ 0

VDD_ 18_ S5_ 1

VDD_ 33_ S5_ 0

VDD_ 33_ S5_ 1

VDDB T_ RTC _G

RS VD_ 0

RS VD_ 1

RS VD_ 2

RS VD_ 3

RS VD_ 4

RS VD_ 5

RS VD_ 6

RS VD_ 7

RS VD_ 8

RS VD_ 9

RS VD_ 10

RS VD_ 11

RS VD_ 12

RS VD_ 13

RS VD_ 14

RS VD_ 15

RS VD_ 16

RS VD_ 17

RS VD_ 18

RS VD_ 19

RS VD_ 20

RS VD_ 21

RS VD_ 22

RS VD_ 23

RS VD_ 24

RS VD_ 25

RS VD_ 26

RS VD_ 27

RS VD_ 28

RS VD_ 29

RS VD_ 30

RS VD_ 31

RS VD_ 32

RS VD_ 33

RS VD_ 34

RS VD_ 35

RS VD_ 36

RS VD_ 37

RS VD_ 38

RS VD_ 39

RS VD_ 40

RS VD_ 41

RS VD_ 42

RS VD_ 43

RS VD_ 44

RS VD_ 45

RS VD_ 46

C456 1u6.3X/4

6

7

VF B= 0. 8

CP U_V_ AUDIO_ FB

CP U_VD DPVCC_ DDR

AM18

AM19

AM20

AN18

AN19

AN20

AP18

AP19

AP20

AM15

AJ 20

AK20

AJ 21

AK21

AJ 16

AJ 17

AJ 15

AK15

AJ 19

AK19

AL15

AM12

AT2 5

AR 15

AP15

AN12

AN15

AT3 0

AW24

AR 24

A5

AD3

AB2

AH2

AL16

AL17

AL18

AL19

AL20

AL21

AM16

AM17

AM21

AN16

AN17

AN21

AP16

AP17

AP21

AR 16

AR 18

AR 19

AR 20

AR 21

AT1 9

D28

E19

E22

E25

G17

J 36

J 38

K34

K38

R35

AB37

AH35

AK34

C317 C0.22u6.3X/4

C320 10u6.3X/6

C722 1u6.3X/4

C719 C0.22u6.3X/4

3

C464

C560p50X/4

8. 5 A

CP U_1P8

VC C3

CP U_VD DP_S 5

CP U_1P8_ S5

3VS B

3

VDDIO_ AUDIO

2. 0 0A

0. 2 5A

0. 2 5A

VDDBT _R TC _G

C903

C22u6.3X/6

R536

10K1%/4

R535

11.3K1%/4

1. 0 0A

0. 5 A

CP U_VD DP

0. 2 5A

4. 5 uA

C294

C22u6.3X/6

2

1. 5V

0. 25A

VDDIO_ AUDIO

C453

C22u6.3X/6

T OP CA VI T Y

VC ORE VC CP_ NB VC C_ DDR

C880 C22u6.3X/6

C217 C22u6.3X/6

C865 C22u6.3X/6

C863 C22u6.3X/6

C228 C22u6.3X/6

C218 C22u6.3X/6

C876 C22u6.3X/6

C884 C22u6.3X/6

C232 C22u6.3X/6

C229 C22u6.3X/6

C230 C22u6.3X/6

C867 C22u6.3X/6

C835 C22u6.3X/6

C823 C22u6.3X/6

C80 C 22u6.3X/6

C825 C22u6.3X/6

C81 C 22u6.3X/6

BOT T OM CA VI T Y

VC ORE VC CP_ NB VC C_ DDR

C122 C22u6.3X/6

C845 C22u6.3X/6

C118 C22u6.3X/6

C848 C22u6.3X/6

C212 C22u6.3X/6

C213 C22u6.3X/6

C877 C22u6.3X/6

C172 C22u6.3X/6

C844 C22u6.3X/6

C231 C22u6.3X/6

C883 C22u6.3X/6

C882 C22u6.3X/6

C856 C180p50N/4

C843 C22u6.3X/6

C849 C22u6.3X/6

C868 X_ C22u6.3X/6

C878 X_ C22u6.3X/6

C112 X_ C22u6.3X/6

C846 X_ C22u6.3X/6

C137 X_ C22u6.3X/6

C847 X_ C22u6.3X/6

C837 X_ C2.2u6.3X/4

C929 X_ C2.2u6.3X/4

C928 X_ C2.2u6.3X/4

C927 X_ C2.2u6.3X/4

C926 X_ C2.2u6.3X/4

C925 X_ C2.2u6.3X/4

C924 X_ C2.2u6.3X/4

C923 X_ C2.2u6.3X/4

C922 X_ C2.2u6.3X/4

C921 X_ C2.2u6.3X/4

C972 X_ C2.2u6.3X/4

C891 X_ C2.2u6.3X/4

C895 X_ C0.22u6.3X/4

C897 X_ C0.22u6.3X/4

C850 X_ C0.22u6.3X/4

C874 X_ C0.22u6.3X/4

C920 X_ C0.22u6.3X/4

C879 X_ C0.22u6.3X/4

C904 X_ C0.22u6.3X/4

C896 X_ C180p50N/4

C869 X_ C180p50N/4

C873 X_ C1000p16X/4

C824 C22u6.3X/6

C82 C 22u6.3X/6

C200 C22u6.3X/6

C815 C22u6.3X/6

C679 C22u6.3X/6

C821 C22u6.3X/6

C201 C22u6.3X/6

C86 C 22u6.3X/6

C202 C22u6.3X/6

C85 C 22u6.3X/6

C807 C180p50N/4

C818 X_ C2.2u6.3X/4

C793 X_ C2.2u6.3X/4

C792 X_ C2.2u6.3X/4

C809 X_ C2.2u6.3X/4

C794 X_ C2.2u6.3X/4

C804 X_ C2.2u6.3X/4

C832 X_ C2.2u6.3X/4

C811 X_ C2.2u6.3X/4

C796 X_ C2.2u6.3X/4

C808 X_ C2.2u6.3X/4

C814 X_ C2.2u6.3X/4

C805 X_ C2.2u6.3X/4

C806 X_ C2.2u6.3X/4

C802 X _C0.22u6.3X/4

C795 X _C0.22u6.3X/4

C800 X _C0.22u6.3X/4

C789 X _C0.22u6.3X/4

C798 X _C0.22u6.3X/4

C788 X _C0.22u6.3X/4

C813 X _C0.22u6.3X/4

C820 X _C0.22u6.3X/4

C803 X _C0.22u6.3X/4

C791 X _C0.22u6.3X/4

C797 X _C180p50N/4

C801 X _C180p50N/4

2

T OP S IDE

VC ORE VC CP_ NB

C233 X_ C22u6.3X/6

C862 X_ C22u6.3X/6

C881 X_ C22u6.3X/6

C215 X_ C22u6.3X/6

C894 X_ C2.2u6.3X/4

C885 X_ C2.2u6.3X/4

C872 X_ C2.2u6.3X/4

C889 X_ C2.2u6.3X/4

CP U_1P8

C852 C22u6.3X/6

C236 C22u6.3X/6

C222 C22u6.3X/6

C210 C22u6.3X/6

C205 X_ C22u6.3X/6

C219 X_ C22u6.3X/6

C859 X_ C22u6.3X/6

C810 C0.22u6.3X/4

C190 C180p50N/4

C860 X_ C22u6.3X/6

C235 X_ C22u6.3X/6

C197 X_ C22u6.3X/6

C870 X_ C2.2u6.3X/4

C858 X_ C2.2u6.3X/4

C241 X_ C2.2u6.3X/4

C240 X_ C2.2u6.3X/4

C831 X_ C2.2u6.3X/4

C816 X_ C2.2u6.3X/4

C871 X_ C2.2u6.3X/4

C875 X_ C2.2u6.3X/4

C799 X_ C0.22u6.3X/4

C817 X_ C0.22u6.3X/4

C888 X_ C180p50N/4

C886 X_ C180p50N/4

C221 X_ C1u16X/6

C272 X_ C0.1u16X/4C125 X_ C22u6.3X/6

C259 X_ C0.1u16X/4

C207 X_ C0.1u16X/4

C186 X_ C0.1u16X/4

C182 X_ C0.1u16X/4

C195 X_ C0.1u16X/4

C209 X_ C0.1u16X/4

C192 X_ C0.1u16X/4

Title

Title

Title

AM4 Power/RTC Power

AM4 Power/RTC Power

AM4 Power/RTC Power

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

BOT T OM S I DE

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

MICR O-S TAR T INT 'L C O.,LT D.

MS- 7A36. 30

MS- 7A36. 30

MS- 7A36. 30

1

C830 X_ C22u6.3X/6

C199 X_ C22u6.3X/6

C826 X_ C22u6.3X/6

C203 X_ C22u6.3X/6

C828 X_ C22u6.3X/6

C827 X_ C22u6.3X/6

C84 X_ C22u6.3X/6

VC C3

C900 C0.22u6.3X/4

C335 C22u6.3X/6

C331 C0.22u6.3X/4

C330 C0.22u6.3X/4

C329 C0.1u16X/4

CP U_1P8_ S5

C901 10u6.3X/6

C892 C0.22u6.3X/4

VC CP_ NB_S 5

C220 C22u6.3X/6

C299 C0.22u6.3X/4

CP U_VD DP_S 5

C333 10u6.3X/6

C321 C0.22u6.3X/4

CP U_1P8

C893 C0.22u6.3X/4

3VS B

C315 C0.22u6.3X/4

1

of

of

of

8 50Monday, December 03, 2018

8 50Monday, December 03, 2018

8 50Monday, December 03, 2018

5

smd.db-x7.ru

CP U_IN#[45]

R1391 X _R /2

R1392 X_ 0R/4

4

3

2

1

D D

C C

B B

AJ 11

CP U1I

J 15

VS S_ 0

L29

VS S_ 1

VS S_ 2

A3

VS S_ 3

A6

VS S_ 4

A9

VS S_ 5

A12

VS S_ 6

A15

VS S_ 7

A18

VS S_ 8

A21

VS S_ 9

A24

VS S_ 10

A27

VS S_ 11

A30

VS S_ 12

A33

VS S_ 13

A36

VS S_ 14

B19

VS S_ 15

B23

VS S_ 16

B26

VS S_ 17

B29

VS S_ 18

B32

VS S_ 19

B35

VS S_ 20

C1

VS S_ 21

C22

VS S_ 22

C25

VS S_ 23

C28

VS S_ 24

C31

VS S_ 25

C34

VS S_ 26

C37

VS S_ 27

D6

VS S_ 28

D9

VS S_ 29

D12

VS S_ 30

D15

VS S_ 31

D18

VS S_ 32

D19

VS S_ 33

D21

VS S_ 34

D22

VS S_ 35

D23

VS S_ 36

D24

VS S_ 37

D25

VS S_ 38

D27

VS S_ 39

D29

VS S_ 40

D30

VS S_ 41

D31

VS S_ 42

D32

VS S_ 43

D33

VS S_ 44

D34

VS S_ 45

D35

VS S_ 46

D36

VS S_ 47

D39

VS S_ 48

E4

VS S_ 49

E5

VS S_ 50

E8

VS S_ 51

E11

VS S_ 52

E14

VS S_ 53

E17

VS S_ 54

E20

VS S_ 55

E21

VS S_ 56

E23

VS S_ 57

E26

VS S_ 58

E27

VS S_ 59

E29

VS S_ 60

E32

VS S_ 61

E35

VS S_ 62

E38

VS S_ 63

F1

VS S_ 64

F4

VS S_ 65

F17

VS S_ 66

F19

VS S_ 67

F22

VS S_ 68

F25

VS S_ 69

F28

VS S_ 70

F31

VS S_ 71

F34

VS S_ 72

MEC 1

MEC 2

MEC 3

MEC 4

MEC 5

MEC 6

AN1

AN4

AN22

AN25

AN28

AN31

AN34

AN35

AN37

AP6

AP24

AP27

AP30

AP33

AP35

AP36

AP39

AR 5

AR 8

AR 11

AR 14

AR 17

AR 23

AR 26

AR 27

AR 29

AR 30

AR 32

AR 34

AR 35

AR 38

AT1

AT7

AT10

AT13

AT16

AT22

AT26

AT27

AT28

AT29

AT31

AT32

AT33

AT34

AT37

AU18

AU21

AU24

AU26

AU27

AU30

AU33

AU36

AU39

AV2

AV17

AV20

AV23

AV26

AV29

AV32

AV35

AV38

AW4

AW7

AW10

AW13

AW16

AW19

AW22

AW25

AW28

AW31

AW34

AW37

AF 28

AF 30

AG1

AG4

AG8

AG9

AG11

AG13

AG15

AG17

AG19

AG21

AG23

AG25

AG27

AG28

AG29

AG30

AG31

AG32

AH10

AH12

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH29

AH30

AH33

AJ 5

AJ 8

AJ 9

AJ 13

AJ 23

AJ 25

AJ 26

AJ 27

AJ 28

AJ 29

AJ 32

AJ 35

AJ 36

AJ 38

MEC 1

MEC 2

MEC 3

MEC 4

MEC 5

MEC 6

VS S_ 398

VS S_ 397

VS S_ 396

VS S_ 395

VS S_ 394

VS S_ 393

VS S_ 392

VS S_ 391

VS S_ 390

VS S_ 389

VS S_ 388

VS S_ 387

VS S_ 386

VS S_ 385

VS S_ 384

VS S_ 383

VS S_ 382

VS S_ 381

VS S_ 380

VS S_ 379

VS S_ 378

VS S_ 377

VS S_ 376

VS S_ 375

VS S_ 374

VS S_ 373

VS S_ 372

VS S_ 371

VS S_ 370

VS S_ 369

VS S_ 368

VS S_ 367

VS S_ 366

VS S_ 365

VS S_ 364

VS S_ 363

VS S_ 362

VS S_ 361

VS S_ 360

VS S_ 359

VS S_ 358

VS S_ 357

VS S_ 356

VS S_ 355

VS S_ 354

VS S_ 353

VS S_ 352

VS S_ 351

VS S_ 350

VS S_ 349

VS S_ 348

VS S_ 347

VS S_ 346

VS S_ 345

VS S_ 344

VS S_ 343

VS S_ 342

VS S_ 341

VS S_ 340

VS S_ 339

VS S_ 338

VS S_ 337

VS S_ 336

VS S_ 335

VS S_ 334

VS S_ 333

VS S_ 332

VS S_ 331

VS S_ 330

VS S_ 329

VS S_ 328

VS S_ 327

VS S_ 326

VS S_ 325

VS S_ 324

VS S_ 323

VS S_ 322

VS S_ 321

VS S_ 320

VS S_ 319

VS S_ 318

VS S_ 317

VS S_ 316

VS S_ 315

VS S_ 314

VS S_ 313

VS S_ 312

VS S_ 311

VS S_ 310

VS S_ 309

VS S_ 308

VS S_ 307

VS S_ 306

VS S_ 305

VS S_ 304

VS S_ 303

VS S_ 302

VS S_ 301

VS S_ 300

VS S_ 299

VS S_ 298

VS S_ 297

VS S_ 296

VS S_ 295

VS S_ 294

VS S_ 293

VS S_ 292

VS S_ 291

VS S_ 290

VS S_ 289

VS S_ 288

VS S_ 287

VS S_ 286

VS S_ 285

VS S_ 284

VS S_ 283

VS S_ 282

VS S_ 281

VS S_ 280

VS S_ 279

VS S_ 278

VS S_ 277

VS S_ 276

AK1

VS S_ 275

AK4

VS S_ 274

AK10

VS S_ 273

AK12

VS S_ 272

AK14

VS S_ 271

AK22

VS S_ 270

AK25

VS S_ 269

AK28

VS S_ 268

AK31

VS S_ 267

AK35

VS S_ 266

AK37

VS S_ 265

AL9

VS S_ 264

AL11

VS S_ 263

AL24

VS S_ 262

AL27

VS S_ 261

AL30

VS S_ 260

AL33

VS S_ 259

AL35

VS S_ 258

AL36

VS S_ 257

AL39