Page 1

1

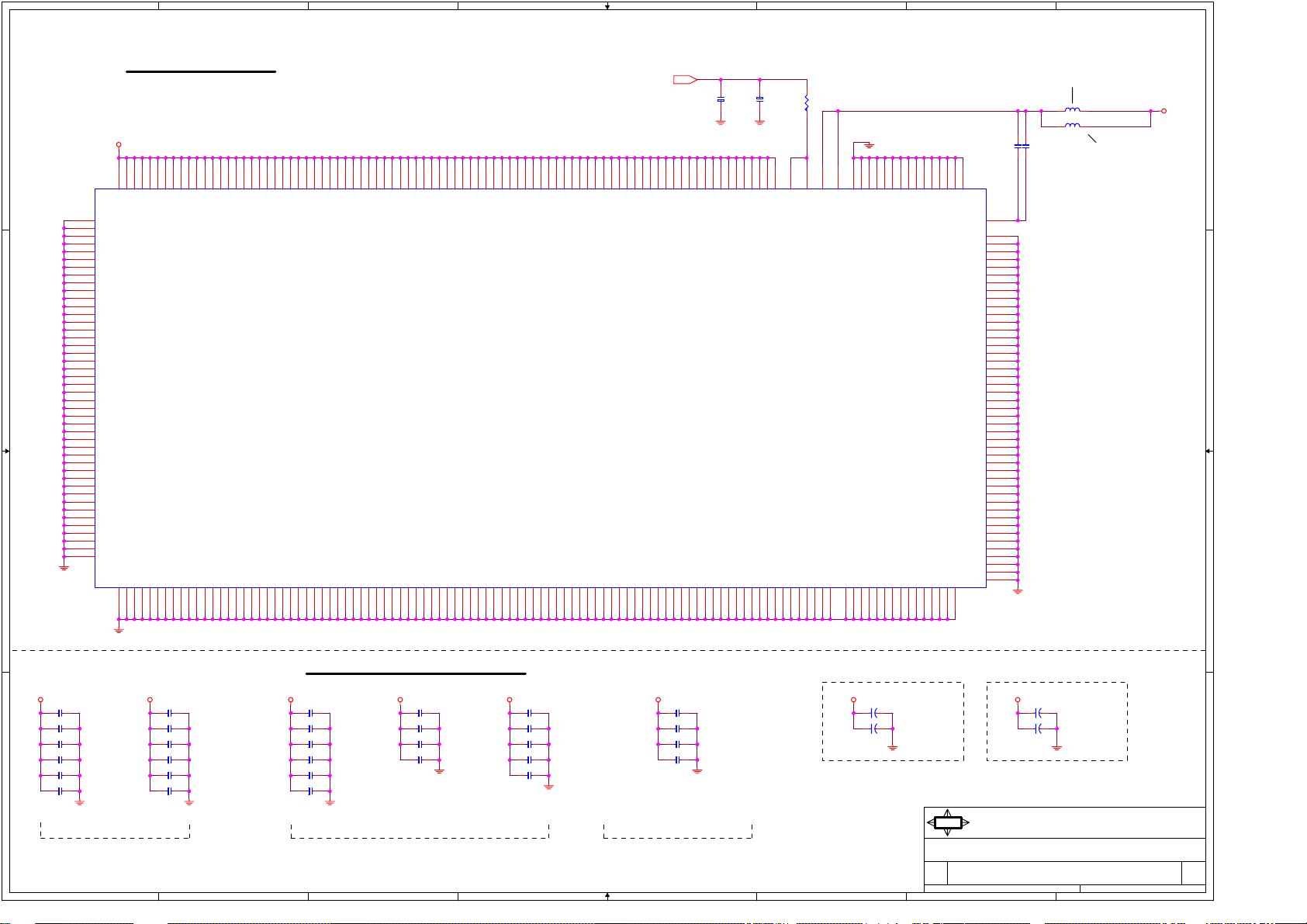

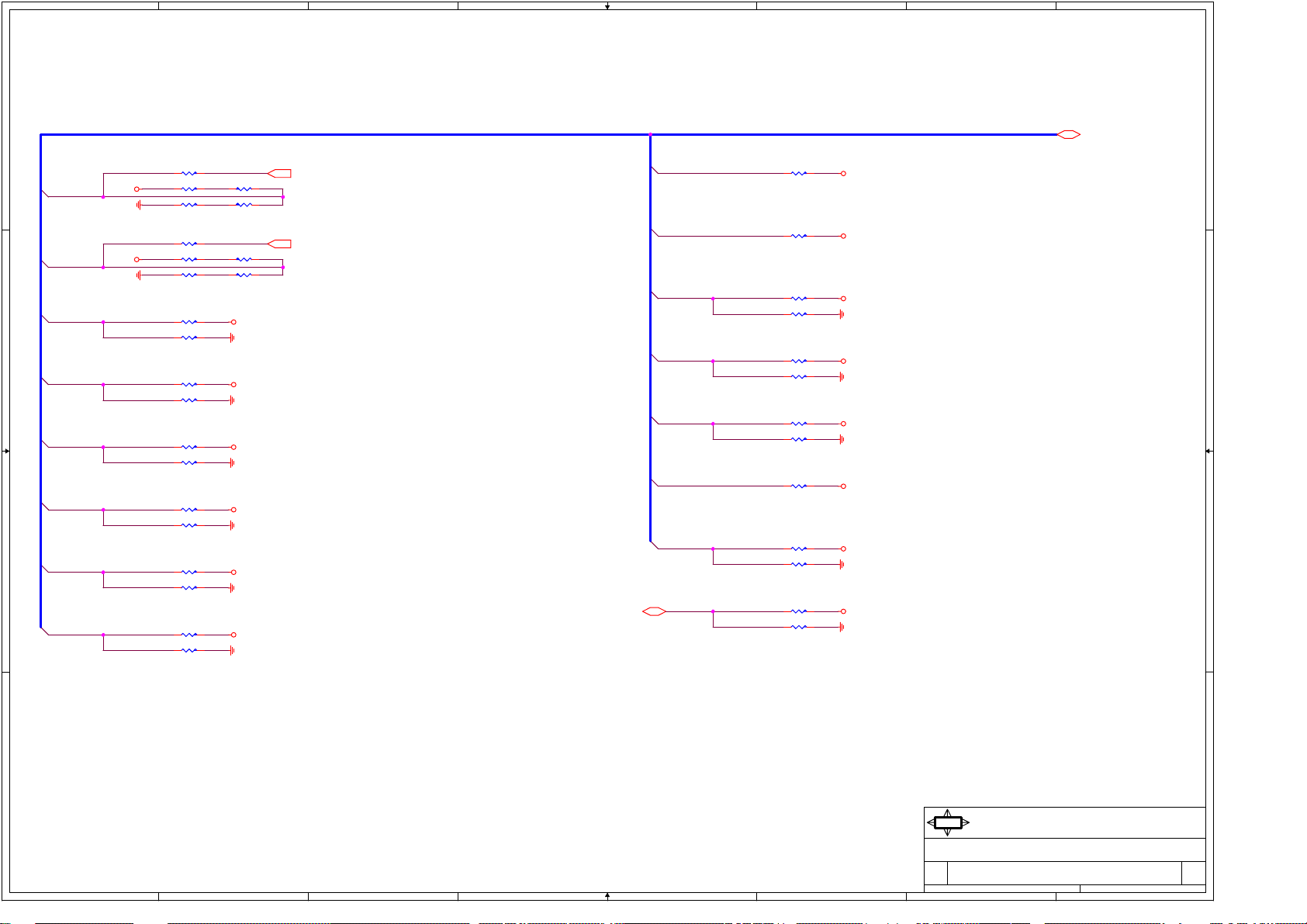

Cover Sheet, Block diagram

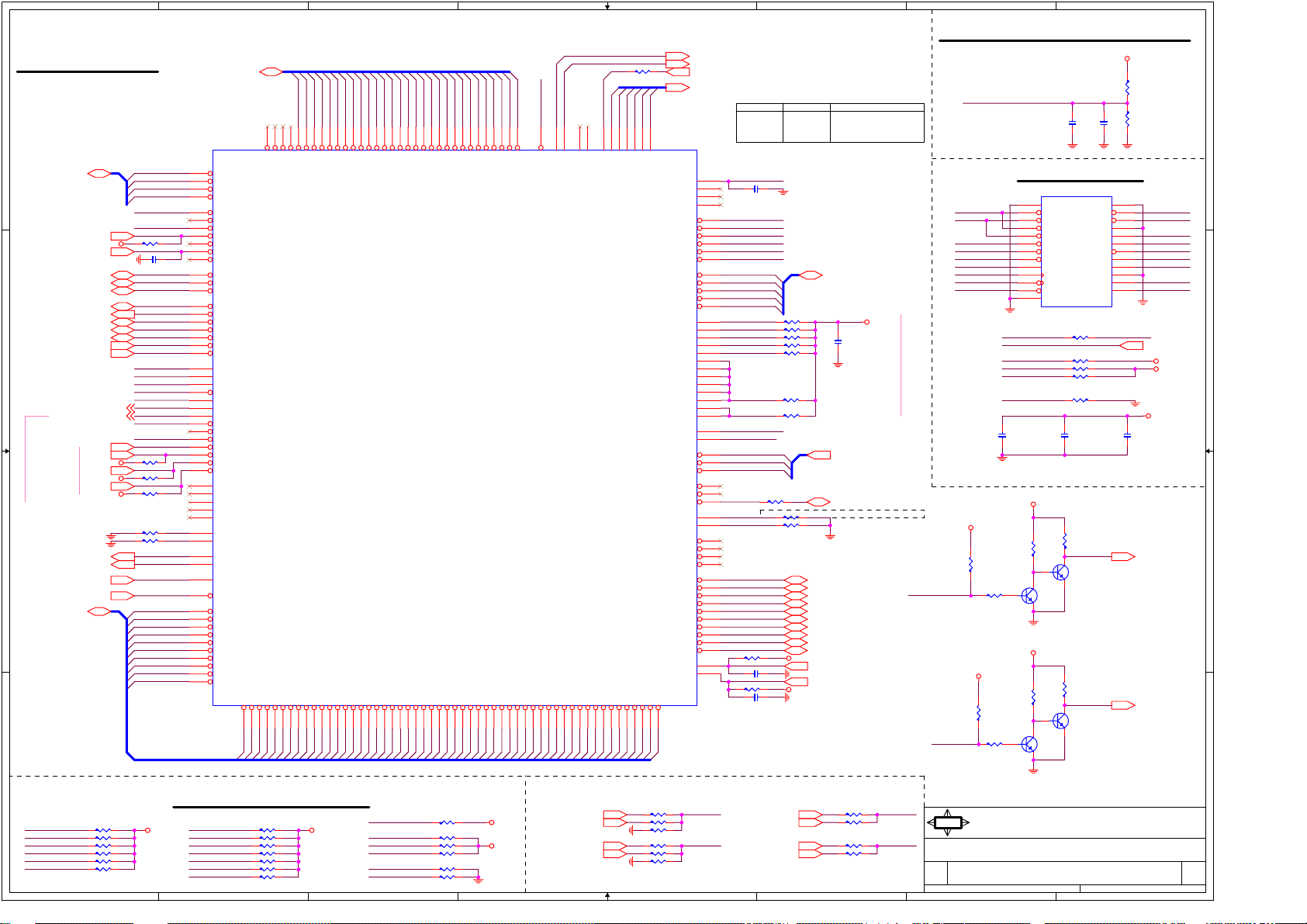

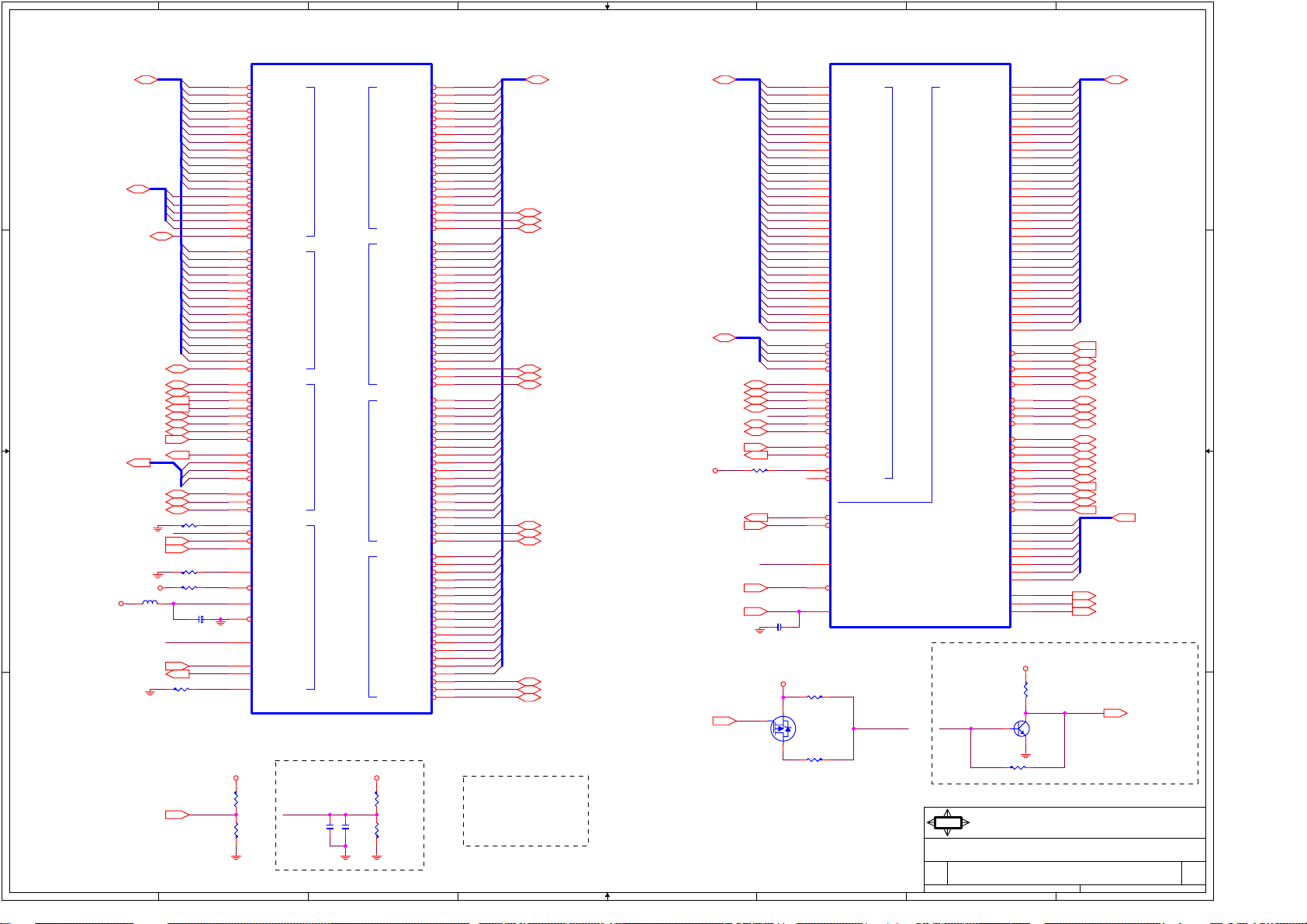

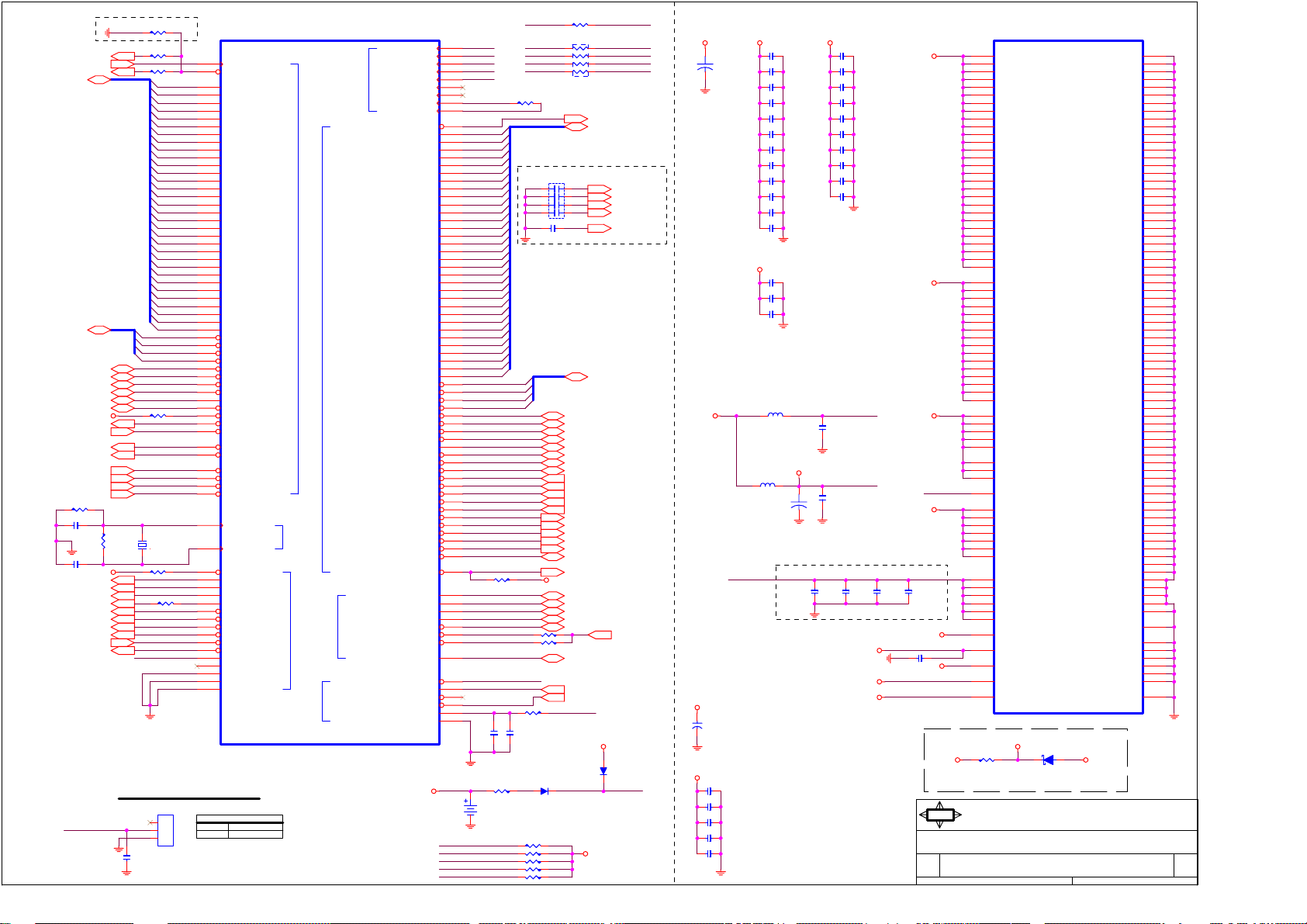

Intel µPGA478B CPU - Signals

Intel µPGA478B CPU - Power

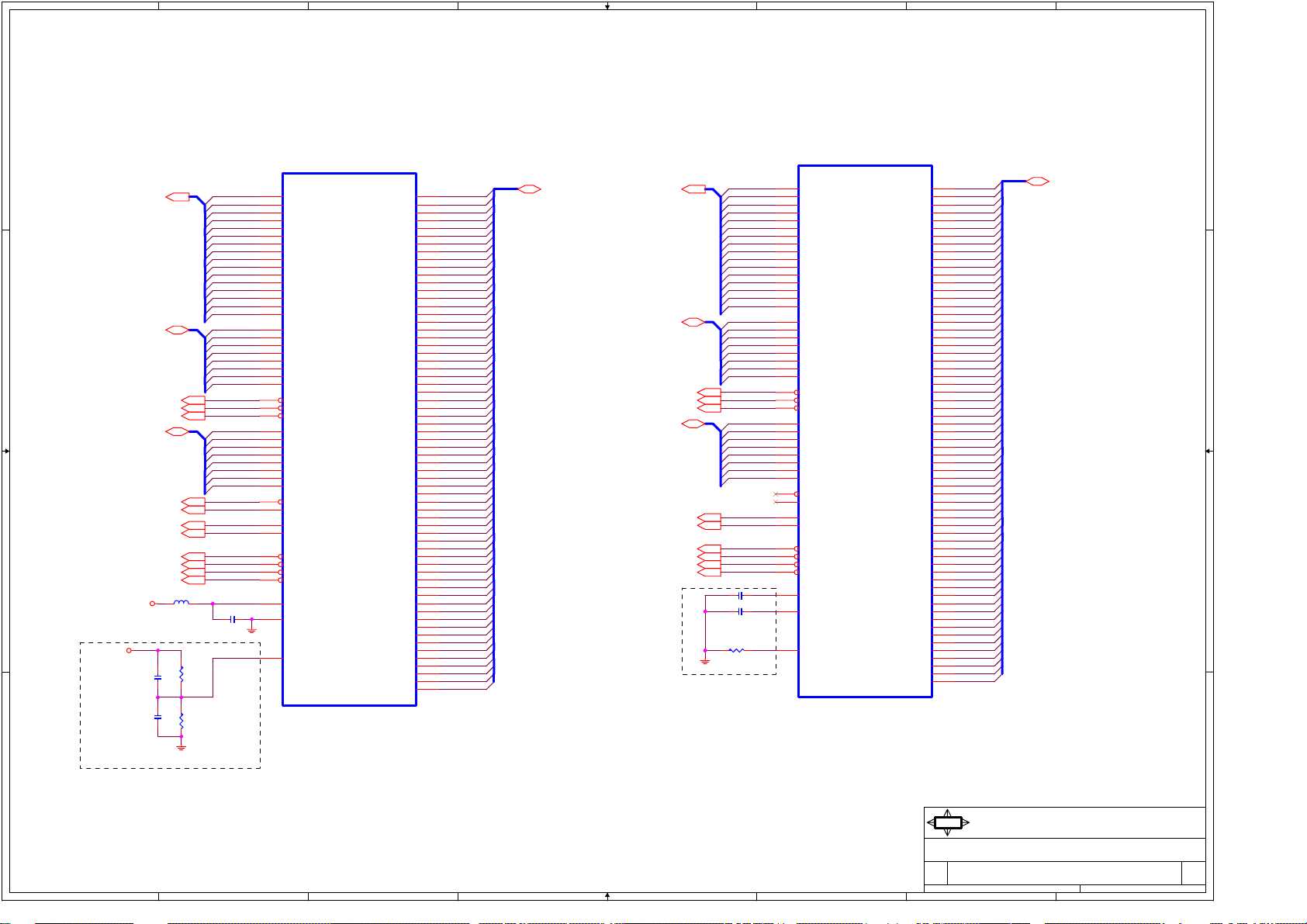

ATi RS300 - CPU & AGP & A-LINK

1-2

4

5

6

MS-6766

ATi RS300 (IGP) + SB250 (IXP) Chipset

Version 0A

Intel Northwood & Prescott mPGA478B Processor

ATi RS300 - MEMORY A & B signals

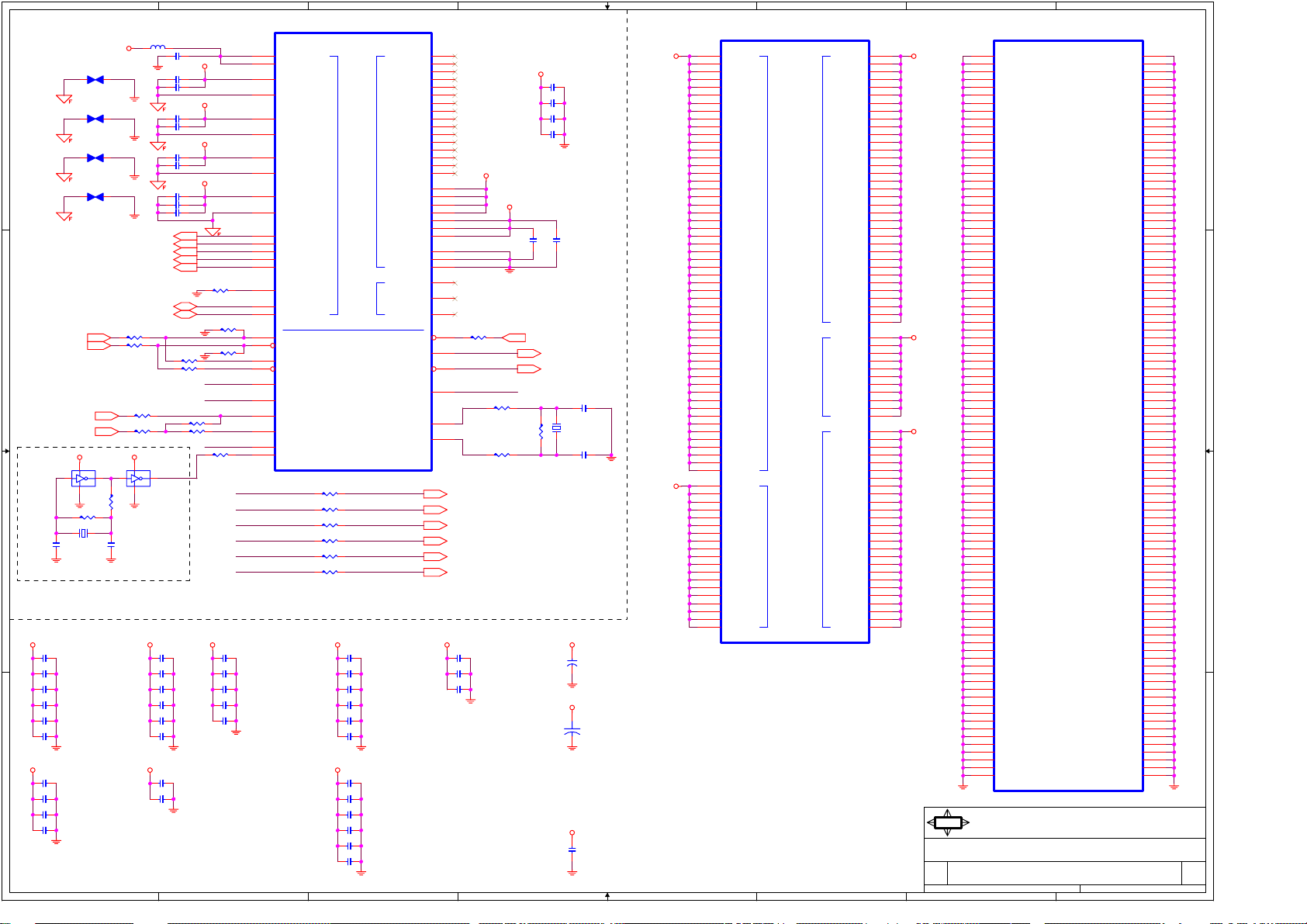

ATi RS300 - VIDEO & CLK & PWR & Straps

ATi SB200 - A-LINK & PCI & CPU & LPC & PWR

ATi SB200 - IDE & USB & MII & AC'97 & Straps

SIO-W83627HF & KB/MS

COM, LPT, FLOPPY & VGA

AC'97 & Audio

EXTERNAL CLOCK & DDR CLOCK BUFFER

DDR DIMM 1 & 2 17-18

7

8-9

10

11-12

13

14

15

16

CPU:

Intel Northwood/Prescott - 3.0G & Above

System Chipset:

ATi RS300 - RADEON IGP (North Bridge)

ATi SB250 - IXP250 (South Bridge)

On Board Chipset:

BIOS -- XBus EEPROM 4M

AC'97 Codec -- ALC650/F

LPC Super I/O -- W83627HF-AW

A A

DDR Terminational Resisitors

IDE Connectors

PCI Slot 1 & 2 & 3

19

20

21

LAN - Altima AC101L PHY

1394 -- NEC PD72874

DDR CLOCK BUFFER -- ICS ICS93750/93727

Main Memory:

AGP SLOT & FAN CONNECTORS

22

DDR * 4 (Max 4GB)

USB CONNECTORS

MII LAN - AC101L & Xbus Flash ROM

1394 - NEC PD72874

23

24

25

Expansion Slots:

PCI2.3 SLOT * 3

AGP4X/8X SLOT * 1

ATX,F_ PANEL,DDR&AGP POWER

VRM 10 - Intersil HIP 6556A + HIP 6602B

26

27ACPI Controller W83302D

28

Intersil PWM:

Controller: HIP6556A

Driver: HIP6602B * 2

RS300 & SB200 PWR GOOD

GPIO & JUMPER SETTING

29

30

Regulators

Manual Parts & Power Delivery

31

MSI

Title

Size Document Number Rev

1

Date: Sheet

MICRO-STAR INt'L CO., LTD.

COVER SHEET

(MS-6766)

131Wednesday, March 12, 2003

of

0A

Page 2

1

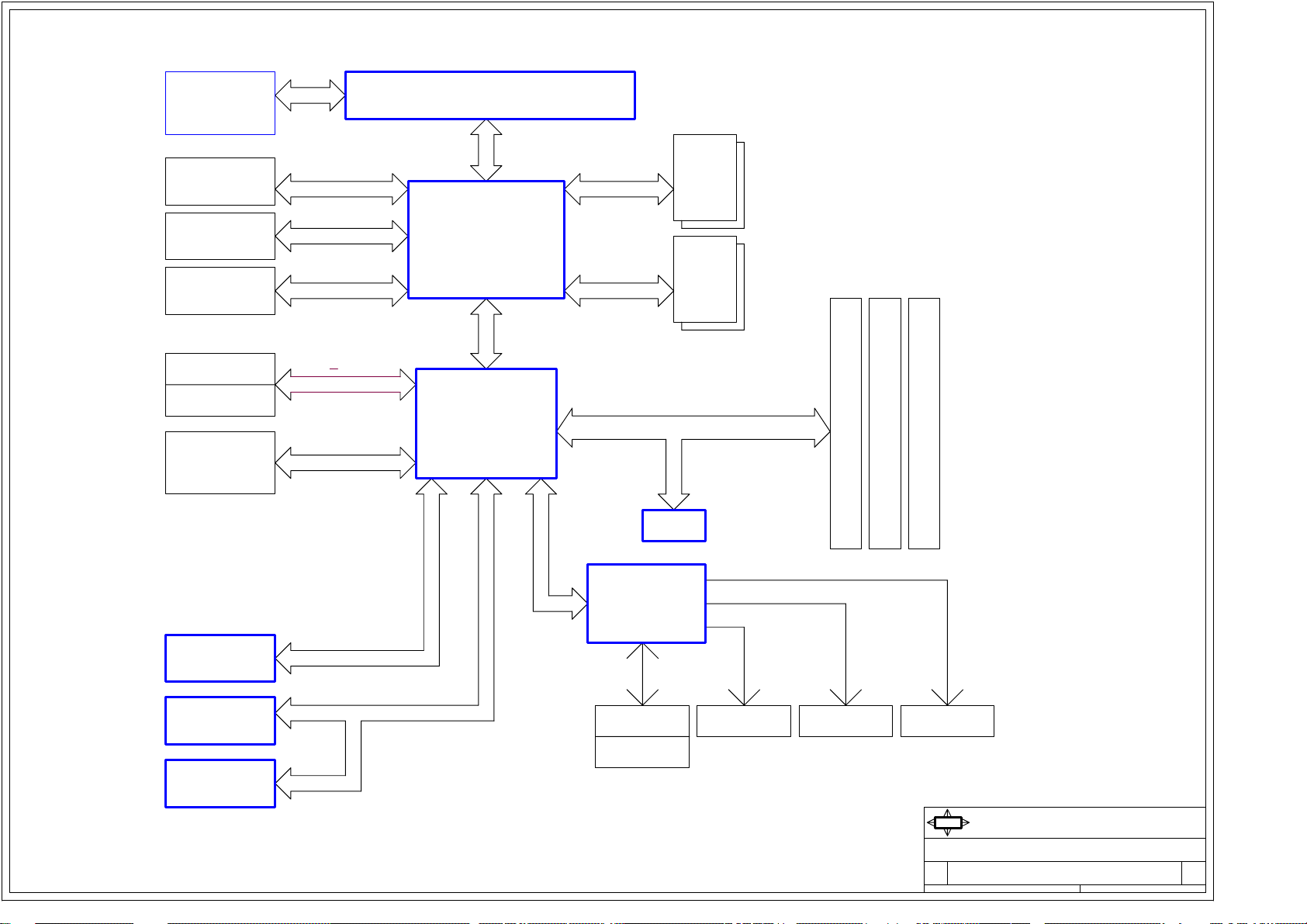

VRM 10

Intersil 6556

3-Phase PWM

P.28

Intel mPAG478B Processor

FSB

P.4~5

Block Diagram

2 DDR

AGP 1.5V

Connector

Analog

Video Out

TV-Out

IDE Primary

IDE Secondary

P.22

P.14

P.14

P.20

P.20

4X/8X w/Fast Wr i t e

UltraDMA

33/66/100

RS300 - IGP

HUB

Link

CHANNEL A

CHANNEL B

P.6~9

DIMM

Modules

2 DDR

DIMM

Modules

PCI

P.17

P.18

PCI Slot 1

PCI Slot 2

PCI Slot 3

SB250

P.23

USB

P.10~12

LPC Bus

Flash

P.24

P.21

P.21 P.21

A A

USB2.0

USB Port0~ 5

AC'97 Codec

ALC650 Ver:F

LAN

AC101L PHY

1394

NEC PD72874

P.15

P.24

P.25

AC'97 Link

PCI

LPC SIO

W83627HF

Keyboard

Mouse

1

P.13

P.13

P.13

Floopy Parallel Serial

P.14 P.14 P.14

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

BLOCK DIAGRAM

(MS-6766)

231Wednesday, March 12, 2003

of

0A

Page 3

5

4

3

2

1

Revision Initial ver: 0A on 01/20/2003

Schematic Initial on January 20.

Schematic modify with ATi suggestion on Feb.06'03(Review_02)

Schematic modify with ATi suggestion on Feb.10'03(Review_03)

D D

C C

B B

A A

MSI

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

MICRO-STAR INt'L CO., LTD.

REVISION HISTORY - 1

(MS-6766

331Wednesday, March 12, 2003

1

of

0A

Page 4

8

7

6

5

4

3

2

1

CPU GTL REFERNCE VOLTAG E BLO CK

3"

DBA#

DBR#

GND

TMS

TRST#

GND

CB282

0.1u

R29

1K_1%

Q1

2N3904S

R33

300

H_FERR#

Q3

2N3904S

TDI

VCCP

C2

0.1u

4

6

8

10

12

14

20

ITP_RST#CPURST#

/N

R1

200_1%

R2

169_1%

ITP_DBR# {26}

CB283

0.1u

PROCHOT# {11}

H_FERR# {10}

431Wednesday, March 12, 2003

of

1

ITP_DBA#

ITP_DBR#

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_FBI

ITP_VCC

ITP_TDO

VCC3

VCCP

VCCP

0A

VCC_SENSE {28}

CPU SIGNAL BLOCK

D D

VCCP

VCCP

VCCP

VCCP

HDBI#0

HDBI#1

HDBI#2

HDBI#3

IERR#

FERR#

R206 200_1%

5:5<17"

C440 100p

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

TRMTRIP#

H_PROCHOT#

R207 200_1%

R208 200_1%

R209 200_1%

R27 0

BOOT

R28 0

5:13<12"

CPU_GD

5:13<10"

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

VCCP VCCP

HDBI#[0..3]{6}

STPCLK#{10}

HINIT#{10}

HDBSY#{6}

HDRDY#{6}

HTRDY#{6}

HADS#{6}

HLOCK#{6}

HBNR#{6}

HIT#{6}

C C

5:7<17"

HBPRI#{6}

HDEFER#{6}

THERMDA_CPU{13}

THERMDC_CPU{6,13}

5:7<10"

IGNNE#{10}

H_SMI#{10}

HITM#{6}

A20M#{10}

SLP#{10}

10:10:10<8"

B B

A A

BPM#4

BPM#5

BPM#2

BPM#3

BPM#1

BPM#0

BSEL0{9}

BSEL1{9}

CPU_GD{10}

CPURST#{6}

HD#[0..63]{6}

R3 62

R4 62

R5 62

R6 62

R7 62

R8 62

8

HA#[3..31]{6}

HA#31

HA#26

HA#30

HA#27

HA#28

HA#25

CPU1A

E21

DBI0#

G25

DBI1#

P26

DBI2#

V21

DBI3#

AC3

IERR#

V6

MCERR#

B6

FERR#

Y4

STPCLK#

AA3

BINIT#

W5

INIT#

AB2

RSP#

H5

DBSY#

H2

DRDY#

J6

TRDY#

G1

ADS#

G4

LOCK#

G2

BNR#

F3

HIT#

E3

HITM#

D2

BPRI#

E2

DEFER#

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

D4

TCK

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

AF26

GND/SKTOCC#

C3

PROCHOT#

B2

IGNNE#

B5

SMI#

C6

A20M#

AB26

SLP#

A22

RESERVED0

A7

RESERVED1

AE21

RESERVED2

AF24

RESERVED3

AF25

RESERVED4

AD1

BOOTSELECT

AE26

OPTIMIZED/COMPAT#

AD6

BSEL0

AD5

BSEL1

AB23

PWRGOOD

AB25

RESET#

AA24

D63#

AA22

D62#

AA25

D61#

Y21

D60#

Y24

D59#

Y23

D58#

W25

D57#

Y26

D56#

W26

D55#

V24

D54#

CPU STRAPPING RESISTORS

ALL COMPONENTS CLOSE TO CPU

TRMTRIP#

CPU_GD

H_BR#0

CPURST#

IERR#

HINIT#

IGNNE#

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

V22

U21

V25

U23

U24

U26

T23

T22

T25

T26

R24

R25

P24

R21

HD#44 HA#29

<3"

<2"

HD#45

HD#43

HD#42

HD#40

HD#41

HD#51

HD#50

HD#52

HD#53

R16 62

R17 300

R18 62

R748 49.9

R210 62

R222 200_1%

R223 200_1%

7

HD#48

HD#49

HD#47

HD#46

HA#24

HA#23

A24#

D39#

N25

N26

HD#39

HD#38

HA#22

A23#

D38#

M26

HD#37

HA#21

A22#

D37#

HD#36

HA#18

HA#19

HA#20

A21#

A20#

A19#

D36#

D35#

D34#

N23

M24

P21

N22

HD#34

HD#35

HD#33

ITP_DBR#

ITP_TDI

ITP_TMS

ITP_TDO

ITP_TCK

ITP_TRST#

6

HA#17

HA#16

HA#15

A18#

A17#

A16#

D33#

D32#

D31#

M23

H25

K23

HD#30

HD#31

HD#32

R747 1K_1%

R9 150

R22 39

R23 75

R24 27

R12 680

HA#14

A15#

D30#

J24

HD#29

HA#13

A14#

D29#

L22

HD#28

HA#12

A13#

D28#

M21

HD#27

HA#11

A12#

D27#

H24

HD#26

HA#10

A11#

D26#

G26

HD#25

HA#9

A10#

D25#

L21

HD#24

HA#8

A9#

D24#

D26

HD#23

HA#7

A8#

D23#

F26

HD#22

HA#6

A7#

D22#

E25

HD#21

VCC3

VCCP

HA#5

A6#

D21#

F24

HD#20

HA#4

A5#

D20#

F23

HD#19

A4#

D19#

ITP_DBR#

HA#3

AE25A5A4

A3#

DBR#

D18#

D17#

D16#

D15#

D14#

G23

E24

H22

D25

J21

HD#15

HD#18

HD#14

HD#17

HD#16

Close to CPU

CPU_CLK_INT{8}

CPUCLK#_EXT{16}

CPU_CLK#_INT{8}

5

VCC_SENSE

D13#

D23

C26

HD#12

HD#13

CPUCLK_EXT{16}

VSS_SENSE

D12#

H21

HD#11

AD26

D11#

G22

HD#10

AC26

ITP_CLK1

D10#

B25

HD#9

ITP_CLK0

D9#

D8#

C24

HD#8

AD2

VIDPWRGD

D7#

C23

HD#7

R689 0

VID5HD#6

VID4

AE1

AD3

VID5#

VID4#

D6#

D5#

B24

D22

HD#5

VID1

VID2

VID3

AE2

AE3

AE4

VID3#

VID2#

D4#

D3#

C21

A25

A23

HD#2

HD#4

HD#3

R727 0

R728 X_0

R729 33

R724 0

R725 X_0

R726 33

VSS_SENSE {28}

VID_GD {27}

VID[0..5] {13,28}

RES. CONFIG.

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

H_BR#0

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI2

TESTHI0

CPU_CLK#

CPU_CLK

HRS#2

HRS#1

HRS#0

COMP1

COMP0

R225 200_1%

C439 100p

R224 200_1%

C438 100p

AD2

AF3

AD1

AE26 DNI

GTLREF

C3 220p

VID0

AE5

VID1#

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

D0#

NORTHWOOD/PRESCOTT

B22

B21

HD#1

HD#0

CPU_CLK ITP_CLK

CPU_CLK#

4

PRESCOTT NORTHWOOD/WILLAMETTE

INSTALL

INSTALL

DNI

PLACE CLOSE TO CPU

12:15<1.5"

R10 62

R11 62

R13 62

R14 62

R15 62

R20 62

R21 62

R226 X_0

ITP_CLK_EXT{16}

ITP_CLK_INT{8}

ITP_CLK#_EXT{16}

ITP_CLK#_INT{8}

5:7<8"

R25 51_1%

R26 51_1%

HADSTB#1 {6}

HADSTB#0 {6}

HDSTBP#3 {6}

HDSTBP#2 {6}

HDSTBP#1 {6}

HDSTBP#0 {6}

HDSTBN#3 {6}

HDSTBN#2 {6}

HDSTBN#1 {6}

HDSTBN#0 {6}

VCCP

H_NMI {10}

INTR {10}

VCCP

DNI

DNI

INSTALL

INSTALL

HREQ#[0..4] {6}

C4

0.1u

5:7<1"

HRS#[0..2] {6}

HBR#0 {6}

SOLDER SIDE

5:13<1.5"

R763 0

R764 X_0

R765 0

R766 X_0

3

VCCP

3"

10:7

GTLREF

0.63*VCC_AVG

CLOSE TO CPU

C1

220p

CPU ITP BLOCK

JTAG1

1 2

BPM#0

BPM#1

BPM#4

BPM#5

ITP_RST#

ITP_TCK

ITP_CLK

ITP_CLK#

BPM#5

VCCP

R31

56_1%

FERR#

MSI

R32 470

2N3904S

VCCP

R35

56_1%

2N3904S

MICRO-STAR INt'L CO., LTD.

2

H_PROCHOT#

<0.75"

Title

ITP_CLK#

Size Document Number Rev

Date: Sheet

GND GND

3

BPM#0

5

BPM#1

7

BPM#2

9

BPM#3

11

BPM#4

13

BPM#5

15 16

RESET# TCK

17 18

FBO FBI

19

BCLK

21 22

BCLK# VCC

23 24

BPM5DR# TDO

25

GND

JTAG

VCC3

VCC3

R741 0

R211 150

R743 1.5K

R744 49.9

R746 X_220

R30

470

R34

470

PROCHOT#

ITP_DBR#

ITP_DBA#

ITP_VCC

ITP_RST#

ITP_FBI

CB281

0.1u

ALL COMPONENTS CLOSE TO CPU

Q2

R36

470

Q4

Intel mPGA478B - Signals

(MS-6766)

Page 5

8

7

6

5

4

3

2

1

CPU VOLTAGE BLOCK

VCC_VID{27}

C5

D15

D17

VCC

VCC

VSS

VSS

E7E9F10

D19D7D9

VCC

VSS

VCC

VSS

VCC

VSS

F12

4.7u_0805

E10

VCC

VCC

VSS

VSS

F14

F16

E12

E14

VCC

VCC

VSS

VSS

F18F2F22

E16

VCC

VSS

E18

F25F5F8

D D

VCCP

CPU1B

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

C C

B B

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AD18

AD21

AD4

AD23

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

C11

C13

C15

C17C2C19

C22

C25C5C7C9D12

D14

D16

D18

D20

D21D3D24D6D8E1E11

E13

E15

E17

E19

E23

E4

E26

E20E8F11

VCC

VCC

VSS

VSS

VCC

VSS

F13

VCC

VSS

G21G6G24

1.2V 150mA

F15

F17

VCC

VCC

VCC

VSS

VSS

VSS

G3H1H23

C6

0.1u

F19

VCC

VSS

F9

VCC

VSS

H26H4J2

VSS

AF4

VCC-VID

VSS

VSS

AF3

J22

VCC-VIDPRG

VSS

R690

0

VSS

J25J5K21

It must close bulk caps.

It support DC current if 100mA.

VSSA

EC2

10u/1206

L1 10uH_0805_100mA

L2 10uH_0805_100mA

DC voltage drop should

be less than 70mV.

VCCP

CPU_IOPLL

EC1

10u/1206

AE23

AD20

XX12

XX13

XX14

XX15

XX16

XX17

XX18

XX19

XX20

XX21

XX22

XX23

XX24

XX25

XX26

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

AD22D10

VSSAVSS

Y5

VSS

Y25

VSS

Y22

VSS

Y2

VSS

W6

VSS

W3

VSS

W24

VSS

W21

VSS

V4

VSS

V26

VSS

V23

VSS

V1

VSS

U5

VSS

U25

VSS

U22

VSS

U2

VSS

T6

VSS

T3

VSS

T24

VSS

T21

VSS

R4

VSS

R26

VSS

R23

VSS

R1

VSS

P5

VSS

P25

VSS

P22

VSS

P2

VSS

N6

VSS

N3

VSS

N24

VSS

N21

VSS

M5

VSS

M25

VSS

M22

VSS

M2

VSS

L4

VSS

L26

VSS

L23

VSS

L1

VSS

K6

VSS

K3

VSS

K24

VSS

XX32

HVSS

XX31

HVSS

HVSS

HVSS

HVSS

HVSS

HVSS

XX11

XX27

XX28

XX29

XX30

VCC-IOPLL

VSS

VSS

VCCA

XX1

HVSS

XX2

HVSS

XX3

HVSS

XX4

HVSS

XX5

HVSS

XX6

HVSS

XX7

HVSS

XX8

HVSS

XX9

HVSS

XX10

NORTHWOOD/PRESCOTT

CPU DECOUPLING CAPACITORS

VCCP

EC3

10u/1206

EC11

10u/1206

EC19

10u/1206

EC26

10u/1206

EC33

A A

10u/1206

EC39

10u/1206

Place these caps within socket cavity Place these caps within south side of processor

8

VCCP VCCP VCCP VCCP VCCPVCCP

EC4

10u/1206

EC12

10u/1206

EC20

10u/1206

EC27

10u/1206

EC34

10u/1206

EC40

10u/1206

EC5

10u/1206

EC13

10u/1206

EC21

10u/1206

EC28

10u/1206

EC35

10u/1206

EC41

10u/1206

12pcs 17pcs

Place these caps within north side of processor

7

6

EC6

10u/1206

EC14

X_10u/1206

EC22

X_10u/1206

EC29

X_10u/1206

5

EC7

X_10u/1206

EC15

X_10u/1206

EC23

X_10u/1206

EC30

X_10u/1206

EC37

10u/1206

EC8

10u/0805

EC16

10u/0805

EC24

10u/0805

EC31

10u/0805

4pcs and dual-layout

with EC32, EC38

4

3

+

+

Solder side

VCCP

EC10

X_150u_2.5V(S/S)

EC18

X_150u_2.5V(S/S)

MSI

Title

Size Document Number Rev

Date: Sheet

+

EC38

X_150u_2.5V(S/S)

+

EC32

X_150u_2.5V(S/S)

Component

side

MICRO-STAR INt'L CO., LTD.

Intel mPGA478B - Power

(MS-6766)

2

531Wednesday, March 12, 2003

1

0A

of

Page 6

8

7

6

5

4

3

2

1

U1A

HA#[3..31]{4}

D D

HREQ#[0..4]{4}

HADSTB#0{4}

C C

HADSTB#1{4}

HADS#{4}

HBNR#{4}

HBPRI#{4}

HDEFER#{4}

HDRDY#{4}

HDBSY#{4}

HBR#0{4}

HLOCK#{4}

CPURST#{4}

HRS#[0..2]{4}

HTRDY#{4}

HIT#{4}

HITM#{4}

NB_RST#{10}

VCC1.8_NB

8

NB_PWRGD{27,29}

VCCP

L3 26Ohm_600mA

NB_THRMDA{13}

THERMDC_CPU{4,13}

SUS_STAT#{11}

B B

Routing NB_THRMDA and HW_AGND

as differential pair.

A A

HA#3

M31

HA#4

P29

HA#5

M29

HA#6

N34

HA#7

N33

HA#8

M30

HA#9

N32

HA#10

P32

HA#11

P30

HA#12

R34

HA#13

P33

HA#14

R33

HA#15

N30

HA#16

N31

HREQ#0

M34

HREQ#1

N29

HREQ#2

R30

HREQ#3

M33

HREQ#4

L32

R31

HA#17

U33

HA#18

T33

HA#19

R32

HA#20

R29

HA#21

U29

HA#22

T31

HA#23

V32

HA#24

T30

HA#25

U32

HA#26

U30

HA#27

V30

HA#28

T29

HA#29

V29

HA#30

U31

HA#31

V33

T34

L31

K29

H30

J31

L30

G31

F29

K30

A21

HRS#0

G29

HRS#1

G30

HRS#2

J29

F30

J30

R38 412RST

SUS_STAT#

R39 49.9RST

R40 24.9_1%

C7 0.1u/S

GTLREF1

R43 0

O = Normal mode

H29

D10

AE5

AE6

E12

W32

W33

H26

J27

Y33

AA33

Y32

B21

VCC_DDR

R45

SUS_STAT# GTLREF1

2.2K

R47

5.6K

7

RS300 IGP

AD3#

AD4#

AD5#

AD6#

AD7#

AD8#

AD9#

AD10#

AD11#

AD12#

AD13#

AD14#

AD15#

AD16#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADSTB0#

AD17#

AD18#

AD19#

AD20#

AD21#

AD22#

AD23#

AD24#

AD25#

AD26#

AD27#

AD28#

AD29#

AD30#

AD31#

ADSTB1#

ADS#

BNR#

BPR#

DEFER#

DRDY#

DBSY#

BR0#

LOCK#

CPURST#

RS2#

RS1#

RS0#

TRDY#

HIT#

HITM#

RSET

SUS_STAT#

SYSRST#

POWERGOOD

COMP_P

COMP_N

CPVDD

CPVSS

P4_VREF

THERMA_D_P

THERMAL_D_N

TESTMODE

Close to RS300

T/S : 10/10

Part 1 of 7

Address Group 0Address Group 1ControlMISC.

C9

0.1u

L33

D0#

K34

D1#

J34

D2#

J33

D3#

K32

D4#

K33

D5#

H31

D6#

J32

D7#

F32

D8#

H33

D9#

E33

D10#

D32

DATA Group 0DATA Group 1DATA Group 2DATA Group 3

D11#

G32

D12#

E32

D13#

D33

D14#

F34

D15#

F33

DBI0#

G33

DSTBN0#

G34

DSTBP0#

B30

D16#

C32

D17#

A31

D18#

C33

D19#

B33

D20#

C34

D21#

B32

D22#

D34

D23#

D30

D24#

B31

D25#

C30

D26#

E29

D27#

E30

D28#

A30

D29#

B29

D30#

C29

D31#

A32

DBI1#

D31

DSTBN1#

E31

DSTBP1#

F28

D32#

D28

D33#

E27

D34#

E28

D35#

F27

D36#

C28

D37#

P4 AGTL+ Interface

CL-ATI-RS300

VCCP

R46

2/3*Vccp

49.9RST

R48

C10

100RST

105P

6

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

B28

A28

F25

A27

B27

C26

B26

C25

E25

D26

D27

E26

F26

B25

F24

A25

C24

E24

D24

A24

D23

C22

B24

E22

B23

D22

B22

C21

A22

F23

E23

F22

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HDBI#0

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HDBI#1

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HDBI#2

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDBI#3

HEAT SINK

HD#[0..63] {4}

HDBI#0 {4}

HDSTBN#0 {4}

HDSTBP#0 {4}

HDBI#1 {4}

HDSTBN#1 {4}

HDSTBP#1 {4}

HDBI#2 {4}

HDSTBN#2 {4}

HDSTBP#2 {4}

HDBI#3 {4}

HDSTBN#3 {4}

HDSTBP#3 {4}

5

A_AD[0..31]{9,10}

A_CBE#[0..3]{10}

A_PAR{9,10}

A_FRAME#{10}

A_IRDY#{10}

A_TRDY#{10}

A_DEVSEL#{10}

A_STOP#{10}

A_SBREQ#{10}

A_SBGNT#{10}

VCC3

(012803 Update)

GGNT#{22}

GREQ#{22}

AGP8X_DET#{22}

AGP_REF{22}

AGP_4X_8X_SEL{22}

4

R37 6.8K

AGP_COMP

C8 0.1u

VCC_AGP

G

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE#0

A_CBE#1

A_CBE#2

A_CBE#3

P_IRQ#A

SD

U1B

AE4

A_AD0

AE2

A_AD1

AE3

A_AD2

AD2

A_AD3

AD1

A_AD4

AD3

A_AD5

AD5

A_AD6

AD6

A_AD7

AC1

A_AD8

AC2

A_AD9

AC4

A_AD10

AC5

A_AD11

AC6

A_AD12

AB2

A_AD13

AB4

A_AD14

AB5

A_AD15

AA4

A_AD16

AA2

A_AD17

AA3

A_AD18

W3

A_AD19

W4

A_AD20

W5

A_AD21

W6

A_AD22

V2

A_AD23

V1

A_AD24

V5

A_AD25

V6

A_AD26

U1

A_AD27

U2

A_AD28

U3

A_AD29

U4

A_AD30

U5

A_AD31

AC3

A_CBE#0

AB6

A_CBE#1

W2

A_CBE#2

V4

A_CBE#3

AA5

A_PAR

Y3

A_FRAME#

Y2

A_IRDY#

Y6

A_TRDY#

U6

A_INTA#

Y5

A_DEVSEL#

AA6

A_STOP#

T5

A_SBREQ#

T6

A_SBGNT#

R5

A_REQ0#

R6

A_GNT0#

G6

AGP_GNT#

G5

AGP_REQ#

F5

AGP_COMP

J6

AGP8X_DET#

F6

AGP_VERF4X

R41 169RST

Q5

NDS335N

R44 71.5RST

3

RS300 IGP

A_LINK Interface

AGP_COMP

Q64

GAD0

T2

GAD1

T3

GAD2

R2

GAD3

R3

GAD4

P2

GAD5

P3

GAD6

N3

GAD7

N2

GAD8

M3

GAD9

L2

GAD10

L3

GAD11

K2

GAD12

K3

GAD13

J2

GAD14

J1

GAD15

J3

GAD16

H3

GAD17

G2

GAD18

G3

GAD19

F2

GAD20

F1

GAD21

F3

GAD22

E1

GAD23

E2

GAD24

C1

GAD25

C2

GAD26

C3

GAD27

B2

GAD28

D4

GAD29

B3

GAD30

A3

GAD31

C4

A6

C6

M1

M2

D3

D2

GC_BE#0

L1

GC_BE#1

H1

GC_BE#2

H2

GC_BE#3

E3

M5

L6

L5

N5

B4

A4

RBF#

K6

GSTOP#

N6

M6

WBF#

K5

SBA0

B8

SBA1

C7

SBA2

B7

SBA3

A7

SBA4

B6

SBA5

C5

SBA6

B5

SBA7

D5

ST0

H6

ST1

H5

ST2

J5

VCC3

R683

10K

(MS-6766)

SB_STB {22}

SB_STB# {22}

AD_STB0 {22}

AD_STB#0 {22}

AD_STB1 {22}

AD_STB#1 {22}

GC_BE#0 {22}

GC_BE#1 {22}

GC_BE#2 {22}

GC_BE#3 {22}

GDEVSEL# {22}

GFRAME# {22}

GIRDY# {22}

GPAR {22}

AGP_DBI_HI/PIPE# {22}

AGP_DBI_LO {22}

RBF# {22}

GSTOP# {22}

GTRDY# {22}

WBF# {22}

ST0 {22}

ST1 {22}

ST2 {22}

PIRQ#A

Pop R683,Q64 for A11.

Part 2 of 7

A_LINK/AGP Interface

Title

Size Document Number Rev

Date: Sheet

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP 8X Interface

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_SBSTB

AGP_SBSTB#

AGP_ADSTB0

AGP_ADSTB0#

AGP_ADSTB1

AGP_ADSTB1#

AGP_CBE#0

AGP_CBE#1

AGP_CBE#2

AGP_CBE#3

AGP_DEVSEL#

AGP_FRAME#

AGP_IRDY#

AGP_PAR

AGP_PIPE#DBI_HI

AGP_DBI_LO

AGP_RBF#

AGP_STOP#

AGP_TRDY#

AGP_WBF#

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_ST0

AGP_ST1

AGP_ST2

CL-ATI-RS300

P_IRQ#A

2N3904S

R684 X_0

MSI

MICRO-STAR INt'L CO., LTD.

ATi rs300 - CPU & AGP & A_LINK Signals

2

GAD[0..31] {12,22}

SBA[0..7] {22}

PIRQ#A {10,21}

631Wednesday, March 12, 2003

of

1

0A

Page 7

8

D D

7

6

5

4

3

2

1

AK21

AJ21

AL20

AJ19

AJ18

AK15

AL15

AL13

AJ14

AK12

AJ22

AJ12

AK10

AL26

AK22

AG28

AH5

AL6

AL12

AK18

AK25

AJ31

AE30

AA30

AK28

AK31

AJ29

AJ6

AK6

AK11

AL17

AJ25

AH30

AE31

AA31

AJ23

AL22

AL8

AJ9

AL30

AL31

AJ30

AL32

AG3

AA34

AP25

U1D

MEMB_A0

MEMB_A1

MEMB_A2

MEMB_A3

MEMB_A4

MEMB_A5

MEMB_A6

MEMB_A7

MEMB_A8

MEMB_A9

MEMB_A10

MEMB_A11

MEMB_A12

MEMB_A13

MEMB_A14

MEMB_A15

MEMB_DM0

MEMB_DM1

MEMB_DM2

MEMB_DM3

MEMB_DM4

MEMB_DM5

MEMB_DM6

MEMB_DM7

MEMB_RAS#

MEMB_CAS#

MEMB_WE#

MEMB_DQS0

MEMB_DQS1

MEMB_DQS2

MEMB_DQS3

MEMB_DQS4

MEMB_DQS5

MEMB_DQS6

MEMB_DQS7

MEMB_CK#

MEMB_CK

MEMB_CKE0

MEMB_CKE1

MEMB_CS0#

MEMB_CS1#

MEMB_CS2#

MEMB_CS3#

MEM_CAP1

MEM_CAP2

MEM_COMP

RS300 IGP

Part 4 of 7

MEM_B_ Interface

MEMB_DQ0

MEMB_DQ1

MEMB_DQ2

MEMB_DQ3

MEMB_DQ4

MEMB_DQ5

MEMB_DQ6

MEMB_DQ7

MEMB_DQ8

MEMB_DQ9

MEMB_DQ10

MEMB_DQ11

MEMB_DQ12

MEMB_DQ13

MEMB_DQ14

MEMB_DQ15

MEMB_DQ16

MEMB_DQ17

MEMB_DQ18

MEMB_DQ19

MEMB_DQ20

MEMB_DQ21

MEMB_DQ22

MEMB_DQ23

MEMB_DQ24

MEMB_DQ25

MEMB_DQ26

MEMB_DQ27

MEMB_DQ28

MEMB_DQ29

MEMB_DQ30

MEMB_DQ31

MEMB_DQ32

MEMB_DQ33

MEMB_DQ34

MEMB_DQ35

MEMB_DQ36

MEMB_DQ37

MEMB_DQ38

MEMB_DQ39

MEMB_DQ40

MEMB_DQ41

MEMB_DQ42

MEMB_DQ43

MEMB_DQ44

MEMB_DQ45

MEMB_DQ46

MEMB_DQ47

MEMB_DQ48

MEMB_DQ49

MEMB_DQ50

MEMB_DQ51

MEMB_DQ52

MEMB_DQ53

MEMB_DQ54

MEMB_DQ55

MEMB_DQ56

MEMB_DQ57

MEMB_DQ58

MEMB_DQ59

MEMB_DQ60

MEMB_DQ61

MEMB_DQ62

MEMB_DQ63

CL-ATI-RS300

AG6

AH6

AJ4

AL3

AG5

AG4

AJ5

AK3

AK4

AM4

AJ8

AK8

AL4

AL5

AJ7

AK7

AJ10

AL10

AJ13

AK14

AK9

AJ11

AK13

AJ15

AJ16

AJ17

AK19

AJ20

AK16

AK17

AL19

AK20

AK23

AK24

AJ26

AK27

AJ24

AL24

AK26

AJ27

AJ28

AL29

AH28

AG29

AL27

AK29

AH29

AG30

AG31

AF29

AD30

AC30

AF30

AF31

AD29

AC29

AB31

AA29

Y30

W30

AB29

AB30

Y29

W29

MDQ_B0

MDQ_B1

MDQ_B2

MDQ_B3

MDQ_B4

MDQ_B5

MDQ_B6

MDQ_B7

MDQ_B8

MDQ_B9

MDQ_B10

MDQ_B11

MDQ_B12

MDQ_B13

MDQ_B14

MDQ_B15

MDQ_B16

MDQ_B17

MDQ_B18

MDQ_B20

MDQ_B21

MDQ_B22

MDQ_B23

MDQ_B24

MDQ_B25

MDQ_B26

MDQ_B27

MDQ_B28

MDQ_B29

MDQ_B30

MDQ_B31

MDQ_B32

MDQ_B33

MDQ_B34

MDQ_B35

MDQ_B36

MDQ_B37

MDQ_B38

MDQ_B39

MDQ_B40

MDQ_B41

MDQ_B42

MDQ_B43

MDQ_B44

MDQ_B45

MDQ_B46

MDQ_B47

MDQ_B48

MDQ_B49

MDQ_B50

MDQ_B51

MDQ_B52

MDQ_B53

MDQ_B54

MDQ_B55

MDQ_B56

MDQ_B57

MDQ_B58

MDQ_B59

MDQ_B60

MDQ_B61

MDQ_B62

MDQ_B63

MDQ_B[0..63] {18,19}

U1C

MA_A0

MA_A[0..15]{17,19}

VCC1.8_NB

VCC_DDR

MDQM_A[0..7]{17,19}

MRAS_A#{17}

MCAS_A#{17}

MWE_A#{17}

MDQS_A[0..7]{17,19}

R50

1K_1%

R51

1K_1%

MA_CLKOUT#

MA_CLKOUT

MA_CLKOUT#{16}

MA_CLKOUT{16}

MCKE_A0{17}

MCKE_A1{17}

MCS_A#0{17}

MCS_A#1{17}

MCS_A#2{17}

MCS_A#3{17}

C14

0.1u

C15

0.1u

L4 26Ohm_600mA

C C

B B

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MA_A13

MA_A14

MA_A15

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

MCKE_A0

MCKE_A1

MEM_VREF

AN21

AM21

AN20

AM18

AN17

AN14

AM15

AN12

AM13

AM11

AM22

AP10

AM9

AM27

AN22

AK33

AJ3

AP4

AP11

AP17

AN25

AM34

AG32

AC32

AN29

AP31

AM30

AK1

AN4

AN10

AM17

AM25

AM33

AG33

AC33

AM23

AP22

AM7

AN7

AN32

AN33

AN31

AP32

AG19

1u/SC13

AH19

AP26

MEMA_A0

MEMA_A1

MEMA_A2

MEMA_A3

MEMA_A4

MEMA_A5

MEMA_A6

MEMA_A7

MEMA_A8

MEMA_A9

MEMA_A10

MEMA_A11

MEMA_A12

MEMA_A13

MEMA_A14

MEMA_A15

MEMA_DM0

MEMA_DM1

MEMA_DM2

MEMA_DM3

MEMA_DM4

MEMA_DM5

MEMA_DM6

MEMA_DM7

MEMA_RAS#

MEMA_CAS#

MEMA_WE#

MEMA_DQS0

MEMA_DQS1

MEMA_DQS2

MEMA_DQS3

MEMA_DQS4

MEMA_DQS5

MEMA_DQS6

MEMA_DQS7

MEMA_CK#

MEMA_CK

MEMA_CKE0

MEMA_CKE1

MEMA_CS0#

MEMA_CS1#

MEMA_CS2#

MEMA_CS3#

MPVDD

MPVSS

MEM_VREF

RS300 IGP

Part 3 of 7

MEMA_DQ10

MEMA_DQ11

MEMA_DQ12

MEMA_DQ13

MEMA_DQ14

MEMA_DQ15

MEMA_DQ16

MEMA_DQ17

MEMA_DQ18

MEMA_DQ19

MEMA_DQ20

MEMA_DQ21

MEMA_DQ22

MEMA_DQ23

MEMA_DQ24

MEMA_DQ25

MEMA_DQ26

MEMA_DQ27

MEMA_DQ28

MEMA_DQ29

MEMA_DQ30

MEMA_DQ31

MEMA_DQ32

MEMA_DQ33

MEMA_DQ34

MEMA_DQ35

MEM_A_ Interface

MEMA_DQ36

MEMA_DQ37

MEMA_DQ38

MEMA_DQ39

MEMA_DQ40

MEMA_DQ41

MEMA_DQ42

MEMA_DQ43

MEMA_DQ44

MEMA_DQ45

MEMA_DQ46

MEMA_DQ47

MEMA_DQ48

MEMA_DQ49

MEMA_DQ50

MEMA_DQ51

MEMA_DQ52

MEMA_DQ53

MEMA_DQ54

MEMA_DQ55

MEMA_DQ56

MEMA_DQ57

MEMA_DQ58

MEMA_DQ59

MEMA_DQ60

MEMA_DQ61

MEMA_DQ62

MEMA_DQ63

CL-ATI-RS300

MEMA_DQ0

MEMA_DQ1

MEMA_DQ2

MEMA_DQ3

MEMA_DQ4

MEMA_DQ5

MEMA_DQ6

MEMA_DQ7

MEMA_DQ8

MEMA_DQ9

AH2

AJ1

AL1

AM1

AH3

AJ2

AK2

AL2

AM2

AN3

AM6

AN6

AN2

AP3

AN5

AP5

AN8

AN9

AN11

AN13

AM8

AM10

AM12

AM14

AN15

AN16

AN18

AN19

AM16

AP16

AM19

AM20

AP23

AM24

AM26

AM28

AN23

AN24

AN26

AN27

AM29

AM31

AL33

AK32

AN28

AN30

AL34

AK34

AJ32

AH32

AF33

AE33

AJ33

AH33

AF32

AE32

AD34

AD33

AB33

AA32

AE34

AD32

AB32

AB34

MDQ_A0

MDQ_A1

MDQ_A2

MDQ_A3

MDQ_A4

MDQ_A5

MDQ_A6

MDQ_A7

MDQ_A8

MDQ_A9

MDQ_A10

MDQ_A11

MDQ_A12

MDQ_A13

MDQ_A14

MDQ_A15

MDQ_A16

MDQ_A17

MDQ_A18

MDQ_A19

MDQ_A20

MDQ_A21

MDQ_A22

MDQ_A23

MDQ_A24

MDQ_A25

MDQ_A26

MDQ_A27

MDQ_A28

MDQ_A29

MDQ_A30

MDQ_A31

MDQ_A32

MDQ_A33

MDQ_A34

MDQ_A35

MDQ_A36

MDQ_A37

MDQ_A38

MDQ_A39

MDQ_A40

MDQ_A41

MDQ_A42

MDQ_A43

MDQ_A44

MDQ_A45

MDQ_A46

MDQ_A47

MDQ_A48

MDQ_A49

MDQ_A50

MDQ_A51

MDQ_A52

MDQ_A53

MDQ_A54

MDQ_A55

MDQ_A56

MDQ_A57

MDQ_A58

MDQ_A59

MDQ_A60

MDQ_A61

MDQ_A62

MDQ_A63

MDQ_A[0..63] {17,19}

MA_B[0..15]{18,19}

MDQM_B[0..7]{18,19}

MRAS_B#{18}

MCAS_B#{18}

MWE_B#{18}

MDQS_B[0..7]{18,19}

MCKE_B0{18}

MCKE_B1{18}

MCS_B#0{18}

MCS_B#1{18}

MCS_B#2{18}

MCS_B#3{18}

PLACE CLOSE TO RS300

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

MA_B13

MA_B14

MA_B15

MDQM_B0

MDQM_B1

MDQM_B2 MDQ_B19

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MRAS_B#

MCAS_B#

MWE_B#

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

MCKE_B0

MCKE_B1

C11 0.47u

C12 0.47u

R49 49.9_1%

PLACE CLOSE TO RS300

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

ATi IGP - Memory Signals

(MS-6766)

2

731Wednesday, March 12, 2003

0A

of

1

Page 8

8

L5 200Ohm_200mA

VCC3

CP1

1 2

AVSSN

CP2

D D

C C

NB_DDRCLK_EXT{16}

NC7WZ14-SC70

B B

VCC_AGP

VCCP

A A

1 2

AVSSDI

CP3

1 2

AVSSQ

CP4

1 2

PLLVSS

NB_CLK_EXT{16}

NB_CLK#_EXT{16}

AGPCLK0_EXT{16}

VCC3_SB VCC3_SB

U29A

1 6

R291 10M

C426

22p

Signal end crystal will not work

C35

0.1u/S

C42

0.1u/S

C49

0.1u/S

C56

0.1u/S

C63

0.1u/S

CB258

0.1u

C76

0.1u/S

C82

0.1u/S

C94

0.1u/S

C100

0.1u/S

R730 0

R731 0

52

R740

270K

8

C16 1u

C17 0.1u

C18 0.1u

AVSSN

VCC1.8_NB

C21 0.1u

C23 0.1u

AVSSDI

C25 0.1u

C26 0.1u

AVSSQ

C27 1u

C28 0.1u/S

C29 0.1u/S

CRT_R{14}

CRT_G{14}

CRT_B{14}

CRT_VSYNC{14}

CRT_HSYNC{14}

3VDDCDA{14}

3VDDCCL{14}

HCLKIN

HCLKIN#

R56 X_0

R57 X_0

R691 0

R693 0

3 4

X8

27Mhz/20pf/30ppm

C427

22p

R692 X_0

R59 0

U29B

52

NC7WZ14-SC70

VCC_NB VCC_DDR

C37

0.1u/S

C44

0.1u/S

C51

0.1u/S

C58

0.1u/S

C65

0.1u/S

C71

0.1u/S

VCC_NB

C78

0.1u/S

C84

0.1u/S

AVDD

(2.5V)

(1.8V)

AVDDQ

(1.8V)

PLVDD

(1.8V)

PLLVSS

R52 715_1%

3VDDCDA

3VDDCCL

R53 33

R55 33

SYS_FB_CO

SYS_FB_CO#

ALINK_CLK_R

AGP_CLK_R

AGP_FB_CI

AGP_FB_CO

USB_CLK_R

R61 33

VCC_NB

7

U1E

H9

VDDR3_1

G9

VDDR3_2

A18

AVDD

B18

AVSS

B17

AVDDDI

C17

AVSSDI

A19

AVDDQ

B19

AVSSQ

H14

PLLVDD

H15

PLLVSS

D18

RED

E18

GREEN

F18

BLUE

E13

DACVSYNC

D13

DACHSYNC

C18

RSET

E11

DACSDA

A10

HCLKIN

B10

HCLKIN#

B11

SYS_FBCLKOUT

C11

SYS_FBCLKOUT#

F9

ALINK_CLK

C8

AGPCLKOUT

D9

AGPCLKIN

C9

EXT_MEM_CLK

F10

USBCLK

D11

REF27

SB_OSC_INT_R SB_OSC_INT

ALINK_CLK_R ALINK_CLK_INT

AGP_CLK_R AGPCLK1_INT

CPU_CLK_INT

CPU_CLK#_INT

C38

0.1u/S

C52

0.1u/S

C59

0.1u/S

C66

0.1u/S

C72

0.1u/S

7

RS300 IGP

Part 5 of 7

CRT

Clock

R63 X_22

R64 X_22

R65 X_22

R66 X_22

R767 X_0

R768 X_0

VCC_DDR

USBCLK_INTUSB_CLK_R

ITP_CLK_INT

ITP_CLK#_INT

C39

0.1u

C46

0.1u

C53

0.1u

C60

0.1u

C67

0.1u

C73

0.1u

C40

0.1u/S

C47

0.1u/S

C54

0.1u/S

C61

0.1u/S

C68

0.1u/S

C74

0.1u/S

6

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

VDD18

VDD18

VDD18

VDD18

VDD18

VDD18

VDD18

GND

GND

GND

C_R

Y_G

COMP_BDACSCL

SVID

CPUSTOP#

SYSCLK

SYSCLK#

OSC

XTLOUT

XTLIN

CL-ATI-RS300

6

D15

E15

F15

D16

F16

E16

F17

E17

F14

E14

C13

B13

C12

A13

C14

VCC1.8_NB

B14

J26

J9

AF26

AF9

A16

B16

C16

A15

B15

C15

F19

D19

E19F12

R54 0

E9

CPU_CLK_INT

A12

CPU_CLK#_INT

B12

SB_OSC_INT_R

E10

PLL_XO

R58 0

B9

A9

PLL_XI

R62 0

SB_OSC_INT {16}

ALINK_CLK_INT {16}

AGPCLK1_INT {16}

USBCLK_INT {16}

ITP_CLK_INT {4}

ITP_CLK#_INT {4}

VCC3

C41

0.1u

C48

0.1u/S

C55

0.1u/S

VCC1.8_NB

5

VCC1.8_NB

C30

0.1u

CPU_STOP# {10,12}

CPU_CLK_INT {4}

CPU_CLK#_INT {4}

P_XO

R60

1M

P_XI

X1

14M-32pf-HC49S-D

VCC_NB

5

C31

0.1u

VCC3

VCCP

C19

0.1u/S

C20

0.1u/S

C22

0.1u/S

C24

0.1u/S

+

EC45

10u-16V

EC46

+

100u_6.3V

EC48

10u_0805

4

U1F

VCC_NB VCC_DDR

22pC32

22pC33

VCC_AGP

AA13

AA14

AA15

AA16

AA19

AA20

AA21

AA22

AB13

AB14

AB15

AB16

AB19

AB20

AB21

AB22

G10

G12

G16

H10

H12

H16

N13

N14

N15

N16

N19

N20

N21

N22

P13

P14

P15

P16

P19

P20

P21

P22

R13

R14

R15

R16

R19

R20

R21

R22

Y13

Y14

Y15

Y16

Y19

Y20

Y21

Y22

D7

E7

H8

A2

E4

G4

J4

K8

L4

L7

L8

N4

N8

P1

P5

P6

R4

R7

R8

4

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDP33

VDDP33

VDDP33

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

RS300 IGP

Part 6 of 7

3

CORE PWR

MEM I/F PWR

POWER

A_LINK PWRCPU I/F PWR

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

AGP PWR

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

VDDR2

CL-ATI-RS300

3

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDR

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

VDDL

AB27

AB28

AC31

AD27

AD28

AF27

AG1

AG7

AG8

AG10

AG12

AG14

AG16

AG18

AG22

AG24

AG26

AG27

AG34

AH10

AH14

AH16

AH22

AH26

AL9

AL16

AL23

AP2

AP7

AP13

AP19

AP28

AP33

W31

Y27

AA7

AA8

AD7

AD8

AF4

AF5

AF6

U7

U8

W8

Y1

C20

D20

D21

E20

E21

F20

F21

H20

H21

H23

H25

H27

G21

G25

G27

G28

K27

K28

M27

M28

N27

N28

T27

T28

U27

W34

2

U1G

A33

AA1

AA18

AA27

AA28

AB3

AB8

AC7

AC8

AC27

AD4

AD31

AE8

AE27

AE28

AE29

AF1

AF2

AF3

AF7

AF8

AG2

AG9

AG11

AG13

AG15

AG17

AG20

AG21

AG23

AG25

AH4

AH8

AH11

AH13

AH17

VCC3

VCCP

Title

Size Document Number Rev

Date: Sheet

AH20

AH23

AH25

AH31

AH34

AK5

AK30

AL7

AL11

AL14

AL18

AL21

AL25

AL28

AM3

AM5

AM32

AN1

AN34

AP8

AP14

AP20

AP29

B1

B20

B34

C10

C19

C23

C27

C31

D6

D8

D12

D14

D17

D25

D29

E5

E6

E8

F4

F7

F8

F11

F13

F31

G8

G13

G15

G18

G19

G22

G24

H4

H7

AA17

MSI

MICRO-STAR INt'L CO., LTD.

ATi IGP - Video & Clock & Power Signals

2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RS300 IGP

Part 7 of 7

GND

(MS-6766)

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

CL-ATI-RS300

831Wednesday, March 12, 2003

1

H11

H13

H17

H18

H19

H22

H24

H32

J7

J8

J28

K4

K31

L27

L29

M4

M7

M8

M32

N17

N18

P4

P7

P8

P17

P18

P27

P31

R1

R17

R18

R27

R28

T4

T8

T13

T14

T15

T16

T17

T18

T19

T20

T21

T22

T32

U13

U14

U15

U16

U17

U18

U19

U20

U21

U22

V3

V7

V8

V13

V14

V15

V16

V17

V18

V19

V20

V21

V22

V27

V28

V31

V34

W13

W14

W15

W16

W17

W18

W19

W20

W21

W22

W27

W28

Y4

Y7

Y8

Y17

Y18

Y31

AB17

AB18

of

1

0A

Page 9

8

7

6

5

4

3

2

1

D D

R67 X_2.7K

A_AD31

A_AD30

A_AD29

C C

A_AD28

A_AD27

A_AD26

B B

A_AD25

A_AD17

VCC3

VCC3

R69 4.7K

R71 4.7K

R73 X_2.7K

R75 4.7K

R76 4.7K

R79 4.7K

R80 X_4.7K

R83 X_4.7K

R84 4.7K

R87 4.7K

R88 X_4.7K

R91 4.7K

R92 X_4.7K

R95 4.7K

R96 X_4.7K

R99 X_4.7K

R100 4.7K

R777 X_0

R778 0

R779 X_0

R780 0

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

BSEL1 {4}

AD[30:31] : FSB CLK SPEED

(DEFAULT)

BSEL0 {4}

00 : 100 MHZ

01 : 133 MHZ

10 : 166 MHZ

11 : 200 MHZ

AD29 : STRAP CONFIGURATION

0 : REDUCEDE SET

1 : FULL SET

(DEFAULT)

AD28 : SPREAD SPECTURM ENABLE

0 : DISABLE SS

1 : ENABLE SS

(DEFAULT)

AD27 : FrcShortReset#

0 : TEST MODE

1 : NORMAL MODE

(DEFAULT)

AD26 : ENABLE IOQ

0:IOQ=1

1:IOQ=12

(DEFAULT)

AD25, AD17 : CPU VOLTAGE[1],CPU VOLTAGE[0]

00 : 1.05V (MOBILE CPU)

01 : 1.35V (MOBILE CPU)

10 : 1.45V (DESKTOP)

11 : 1.75V (DESKTOP)

(DEFAULT)

A_PAR{6,10}

A_AD24

A_AD23

A_AD22

A_AD21

A_AD20

A_AD19

A_AD18

A_PAR

R68 4.7K

R72 4.7K

R77 4.7K

R78 X_4.7K

R81 4.7K

R82 X_4.7K

R85 4.7K

R86 X_4.7K

R89 4.7K

R93 4.7K

R94 X_4.7K

R97 4.7K

R98 X_4.7K

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

AD24 : RESERVED

1 : DEFAULT (DEFAULT)

AD23 : CLOCK BYPASS ENABLE

0 : TEST MODE

1 : NORMAL (DEFAULT)

AD22 : OSC PAD OUTPUT PCICLK

0 : OSC PIN DRIVES OSC CLK (=66MHz)

1 : OSC PIN DRIVES PCI CLK (=14.318MHz)

NOTE : SET AD22 = 1 WHEN USE GIGABIT ENTHERNET

AD21 : AUTO CAL. ENABLE

0 : DISABLE AUTO-CAL.

AD20 : INTERNAL CLK GEN. ENABLE

0 : EXTERNAL CLK GEN.

AD19 : MEMORY I/O VOLTAGE

0 : 1.8V

1 : 2.5V

AD18 : ENABLE PHASE CALIBRATION

0 : ENABLE

1 : DISABLE

A_PAR : ENTENDED DEBUG MODE

0 : DEBUG MODE

A_AD[0..31] {6,10}

(DEFAULT)

(DEFAULT)1 : ENABLE AUTO-CAL.

(DEFAULT)1 : INTERNAL CLK GEN.

(DEFAULT)

(DEFAULT)

(DEFAULT)1 : NORMAL OPERATION

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

ATi RS300 - Straps Signals

(MS-6766)

2

931Wednesday, March 12, 2003

0A

of

1

Page 10

A_AD[0..31]{6,9}

A_CBE#[0..3]{6}

R113 20M

Pull down for S3

LPC_RST#{13}

ALINK_CLK{16}

NB_RST#{6}

A_FRAME#{6}

A_DEVSEL#{6}

A_IRDY#{6}

A_TRDY#{6}

A_PAR{6,9}

A_STOP#{6}

VCC3

A_SBREQ#{6}

A_SBGNT#{6}

CPU_STOP#{8,16}

PCI_STP#{16}

PIRQ#A{6,21,22}

PIRQ#B{21,22}

PIRQ#C{21}

PIRQ#D{21,25}

12pC151

12pC152

VCC3

CPU_GD{4}

INTR{4}

H_NMI{4}

HINIT#{4}

H_SMI#{4}

SLP#{4}

IGNNE#{4}

A20M#{4}

H_FERR#{4}

STPCLK#{4}

GPI0

R101 8.2K

R103 33

R106 33

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE#0

A_CBE#1

A_CBE#2 AD28

A_CBE#3

R112 8.2K

PCI_STP#

32.768KHz-12.5pF-20PPM

R114

20M

32K_X1

X3

32K_X2

R115 10K

CPU_GD

R117 0

GPI0

CMOS CLEAR JUMPER

JBAT1

1

2

3

YJ103

CB284

X_104P

U2A

B22

PCICLKF

R22

A_RST#

H22

A_AD0

P23

A_AD1

L23

A_AD2

N23

A_AD3

N22

A_AD4

M23

A_AD5

M22

A_AD6

K22

A_AD7

M21

A_AD8

M20

A_AD9

L21

A_AD10

K21

A_AD11

L20

A_AD12

N21

A_AD13

K23

A_AD14

K20

A_AD15

F23

A_AD16

G21

A_AD17

F20

A_AD18

H21

A_AD19

F22

A_AD20

F21

A_AD21

G20

A_AD22

E21

A_AD23

E20

A_AD24

D23

A_AD25

D22

A_AD26

E22

A_AD27

D20

A_AD28

C23

A_AD29

D21

A_AD30

C22

A_AD31

L22

A_CBE#0

J23

A_CBE#1

G22

A_CBE#2

E23

A_CBE#3

H20

A_STROBE#

J21

A_DEVSEL#

G23

A_ACAT#

H23

A_END#

J20

A_PAR

J22

A_OFF#

P22

A_SERR#

B21

A_SBREQ#

B20

A_SBGNT#

N20

CPU_STP#/DPSLP#

R23

PCI_STP#

C20

A_INTA#

P20

INTB#

B23

INTC#

P21

INTD#

AC12

X1

AC11

X2

B18

CPURSTIN#

E4

CPU_PWRGD

B17

INTR/LINT0

B16

NMI/LINT1

C17

INIT

C16

SMI#

F19

SLP#

D17

IGNNE#

D18

A20M#

E19

FERR#

E16

STPCLK#

E17

SSMUXSEL/GPIO0

E18

DPRSLPVR

C19

APIC_D0

C18

APIC_D1

B19

APIC_CLK

CL-ATI-SB200

JBAT1 Clear CMOS

Normal

1 - 2

2 - 3

Clear CMOS

*

SB200 SB

Part 1 of 3

A-LINK

INTERFACE

XTAL

CPU

RTC

LPC

PCI

CLKS

PCICLK_FB

AD0/ROMA18

AD1/ROMA17

AD2/ROMA16

AD3/ROMA15

AD4/ROMA14

AD5/ROMA13

AD6/ROMA12

AD7/ROMA11

AD8/ROMA9

AD9/ROMA8

AD10/ROMA7

AD11/ROMA6

AD12/ROMA5

AD13/ROMA4

AD14/ROMA3

AD15/ROMA2

AD16/ROMD0

AD17/ROMD1

AD18/ROMD2

AD19/ROMD3

AD20/ROMD4

AD21/ROMD5

AD22/ROMD6

AD23/ROMD7

AD24/RTC_AD0

AD25/RTC_AD1

AD26/RTC_AD2

AD27/RTC_AD3

PCI

INTERFACE

AD28/RTC_AD4

AD29/RTC_AD5

AD30/RTC_AD6

AD31/RTC_AD7

CBE#0/ROMA10

CBE#1/ROMA1

CBE#2/ROMWE#

CBE#3/RTC_RD#

DEVSEL#/ROMA0

TRDY#/ROMOE#

REQ#3/PDMAREQ0#

REQ#4/PLLBP33/PDMAREQ1#

GNT#3/PDMAGNT0#

GNT#4/PLLBP50/PDMAGNT1#

GPIO1/ROMCS#

USBOC5#/GPM1

RTC_ALE/USBOC4#/GPIO3

RTC_WR#/RTC_CLKOUT

RTC_CS#/USBOC3#/GPIO2

RTC_VCC

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

PCICLK7

PCIRST#

FRAME#

IRDY#

PAR

STOP#

PERR#

SERR#

REQ#0

REQ#1

REQ#2

GNT#0

GNT#1

GNT#2

CLKRUN#

LAD0

LAD1

LAD2

LAD3

LFRAME#

LDRQ#0

LDRQ#1

SERIRQ

VBAT

RTC_GND

B15

D16

A14

A15

A16

A17

D15

A18

A19

C15

B1

C1

A1

D2

B2

C2

A2

D3

C3

A3

D4

B4

C4

A4

D5

B5

C8

D8

B8

A8

C9

D9

B9

A9

C10

B10

D11

A10

C11

B11

D12

A11

B3

C5

A7

D10

B7

A6

C7

D7

A5

B6

C6

D6

B12

C12

D13

A12

C13

A13

B13

C14

D14

B14

A20

AB5

Y14

AA14

AB14

AA13

AB13

AC14

Y13

AC13

AA2

AB7

AB8

AC8

AC10

AB11

20mil

BAT1

PCLK0

PCLK1

PCLK2

PCLK3

PCLK4

PCLK8

PCLK8_FB

PCI_RST#

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD29

AD30

AD31

C_CBE#0

C_CBE#1

C_CBE#2

C_CBE#3

PREQ#0

PREQ#2

PREQ#3

PREQ#4

PGNT#0

PGNT#1

PGNT#2

PGNT#3

PGNT#4

PCI_CLKRUN#

R116 4.7K

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

LPC_DRQ#0

LPC_DRQ#1

SERIRQ

C161

1u

SERIRQ

PCI_CLKRUN#

LPC_DRQ#0

LPC_DRQ#1

GPI0

R105 33

PCLK2 PCI_CLK2

PCLK3

PCLK0

PCLK1

PCLK4

R111 33

As short as possible <1"

CN10 X_10p

2

4

6

8

X_10p_NPOC441

ROM_CS#

OC#3

OC#3

OC#2

3VDUAL

R118 0

R119 X_0

R185 1K_1%

Close to

VBAT pin.

C162

0.1u

D2

R126

1N4148S

0

R180 10K

R124 10K

R125 4.7K

R127 4.7K

R188 10K

SIO_PCLK

1 2

PCI_CLK0

3 4

PCI_CLK1

5 6

1394_PCLK

7 8

RN69 33_8P4R

PCI_RST# {27}

AD[0..31] {21,24,25}

For EMI(022703)

1

SIO_PCLK {13}

3

PCI_CLK0 {21}

5

PCI_CLK1 {21}

7

1394_PCLK {25}

PCI_CLK2 {21}

C_CBE#[0..3] {24}

FRAME# {21,25}

DEVSEL# {21,24,25}

IRDY# {21,25}

TRDY# {21,24,25}

PAR {21,25}

STOP# {21,25}

PERR# {21,25}

SERR# {21,25}

PREQ#0 {21}

PREQ#1 {21}

PREQ#2 {21}

PREQ#3 {21}

PREQ#4 {21,25}

PGNT#0 {21}

PGNT#1 {21}

PGNT#2 {21}

PGNT#3 {21}

PGNT#4 {25}

PCI_CLKRUN# {13}

ROM_CS# {24}

LPC_AD0 {13}

LPC_AD1 {13}

LPC_AD2 {13}

LPC_AD3 {13}

LPC_FRAME# {13}

SERIRQ {13}

OC#3 {23}

OC#2 {23}

VBAT

1N4148S

LPCDRQ#0 {13}

VCC3

D1

VCC3

EC49

+

100u_6.3V

EC51

10u-16V

3VDUAL

L7

26/600mA-0805

USB_AVDD

>30mil

C163

0.1u/S

C165

0.1u/S

C166

0.1u/S

C167

0.1u

C164

0.1u/S

VCC3 VCC_SB

C112

0.1u

C114

0.1u

C116

0.1u

C120

0.1u

C122

0.1u/S

C124

0.1u

C128

0.1u

C131

0.1u/S

C134

0.1u/S

C137

0.1u/S

C140

0.1u

C142

0.1u/S

C130

0.1u/S

C133

0.1u/S

C143

0.1u/S

L6

26/600mA-0805

USB_AVDD

CT2

100u_6.3V

+

3.3V_AVDDC

C149

4.7u-0805

USB_AVDDPREQ#1

C150

4.7u-0805

ONE CAP FOR EACH BALL

C154

0.1u

>20mil

>30mil

C155

0.1u/S

5V_REF

+VCC2.5

VCC3_SB

C113

0.1u/S

C115

0.1u/S

C117

0.1u/S

C119

0.1u/S

C121

0.1u/S

C123

0.1u/S

C125

0.1u/S

C127

0.1u

C135

0.1u/S

C138

0.1u

U2C

VCC3

VCC_SB

2_5DUAL

3VDUAL

C157

C156

0.1u/S

0.1u/S

VCC_SB

C159 1u-0805

AVDD_CK

I=100mA

Title

Size Document Number Rev

Date: Sheet

E11

E12

E15

E7

E8

F11

F12

F15

F16

F17

F7

F8

G18

G19

H18

H19

M18

M19

N18

N19

T18

T19

U18

U19

V17

V18

W17

W18

J10

J11

J13

J14

K15

K9

L15

L9

N15

N9

P15

P9

R10

R11

R13

R14

P6

>30mil>30mil

R6

V13

W13

V12

L6

H6

3.3V_AVDDC

J6

P5

T6

U6

V9

V10

V11

W9

W10

F4

J4

K5

F3

K4

L5

D19

D1

A21

Y9

AA9

R685 1K_1%

Add a diode to meet power up sequence

for SB200 5V_REF with respect to VDDQ

MSI

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

STB_2.5V

STB_2.5V

STB_2.5V

STB_2.5V

STB_2.5V

VDD_USB

VDD_USB

VDD_USB

AVDDC

STB_3.3V

STB_3.3V

STB_3.3V

STB_3.3V

STB_3.3V

STB_3.3V

STB_3.3V

AVDDTX0

AVDDTX1

AVDDTX2

AVDDRX0

AVDDRX1

AVDDRX2

VREF_CPU

5V_VREF

AVDD_CK

S5_2.5V

S5_3.3V

5V_REF

D30 1N5817

SB200 SB

MICRO-STAR

SB250 - ALINK,PCI,CPU,LPC,PWR

Part 3 of 3

POWER

020603

VCC3VCC5

(MS-6766)

VSS_USB

VSS_USB

AVSSRX2

AVSSRX1

AVSSRX0

AVSSTX2

AVSSTX1

AVSSTX0

AVSSCK

CL-ATI-SB200

10 31Wednesday, March 12, 2003

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AVSSC

E10

E13

E14

E6

E9

F10

F13

F14

F18

F6

F9

G6

J12

J15

J18

J19

J9

K10

K11

K12

K13

K14

K18

K19

L10

L11

L12

L13

L14

L18

L19

M10

M11

M12

M13

M14

M15

M6

M9

N10

N11

N12

N13

N14

N6

P10

P11

P12

P13

P14

P18

P19

R12

R15

R18

R19

R9

V14

V15

V16

V19

V6

V7

V8

W14

W15

W16

W19

W7

W8

H5

G5

N5

M5

J5

G4

K6

H4

F5

A22

0A

of

VCC3

USB CORE will drain 90mA per port in Standby mode

3VDUAL

2_5DUAL

+

2_5DUAL

VBATRTC_VCC

Page 11

8

7

6

5

4

3

2

1

U2B

P3

USBCLK/CLK48

R1

USB_RCOMP

P1

USB_VREFOUT

N4

USB_ATEST1

N3

USB_ATEST0

P4

USBOC0#/GPM7

M2

USB_HSDP5+

M1

USB_FLDP5+

N2

USB_HSDM5-

N1

USB_FLDM5-

L4

USB_HSDP4+

L3

USB_FLDP4+

M4

USB_HSDM4-

M3

USB_FLDM4-

K2

USB_HSDP3+

K1

USB_FLDP3+

L2

USB_HSDM3-

L1

USB_FLDM3-

H2

USB_HSDP2+

H1

USB_FLDP2+

J2

USB_HSDM2-

J1

USB_FLDM2-

G3

USB_HSDP1+

J3

USB_FLDP1+

H3

USB_HSDM1-

K3

USB_FLDM1-

F1

USB_HSDP0+

F2

USB_FLDP0+

G1

USB_HSDM0-

G2

USB_FLDM0-

R5

MCOL

W1

MCRS

V4

MDCK

V2

MDIO

T1

RX_CLK

T3

RXD3

U2

RXD2

T5

RXD1

W4

RXD0

T2

RX_DV

U1

RX_ERR

T4

TX_CLK

U4

TXD3

V1

TXD2

U3

TXD1

V3

TXD0

W2

TX_EN

W3

PHY_PD

U5

PHY_RST#

Y7

CLK_25M

P2

EE_CS

R3

EE_DI

R2

EE_DO

R4

EE_CK

AB9

RSMRST#

A23

OSC_IN

W6

SIO_CLK

AB2

BLINK/GPM0

AA3

FANOUT1/USBOC2#/GPM2

W11

32KHZ_IN/GPM3

AB1

USBOC1#/GPM4

Y4

SPEAKER/GPM5

AA1

FANOUT0/GPM6

AC1

GPIO_X0/AGP_STP#

AC6

GPIO_X1/AGP_BUSY#

AC2

GPIO_X2/GHI#

AC3

GPIO_X3/VGATE

AC4

GPIO_X4

AC5

GPIO_X5

6

SB200 SB

Part 2 of 3

ACPI / WAKE UP EVENTS

USB

INTERFACE

PRIMARY

ETHERNET

MII

EEPROMCLK /

RST

SECONDARY ATA

GPIOGPIO_XTRA

TALERT#/ETH_TALERT#

PME#/EXT_EVNT0#

RI#/EXT_EVNT1#

SLP_S3#

SLP_S5#

PWR_BTN#

PWR_GOOD

PCI_REQACT#

SUS_STAT#

TEST1

TEST0

GA20_IN/GEVNT0#

SMI_IN#/GEVNT1#

SMB_ALERT#/GEVNT2#

LPC_PME#/GEVNT3#

LPC_SMI#/GEVNT4#

GEVENT5#/ETH_VALERT#

GEVENT6#/ETH_FALERT#

GEVENT7#/ETH_CALERT#

GPOC0#/SCL0

GPOC1#/SDA0

GPOC2#/SCL1

GPOC3#/SDA1

RTC_IRQ#/PWR_STRP

PIDE_IORDY

PIDE_IRQ

PIDE_A0

PIDE_A1

PIDE_A2

PIDE_DACK#

PIDE_DRQ

PIDE_IOR#

PIDE_IOW#

PIDE_CS1#

PIDE_CS3#

PIDE_D0

PIDE_D1

PIDE_D2

PIDE_D3

PIDE_D4

PIDE_D5

PIDE_D6

5

PIDE_D7

PIDE_D8

PIDE_D9

PIDE_D10

PIDE_D11

PIDE_D12

PIDE_D13

PIDE_D14

PIDE_D15

SIDE_IORDY

SIDE_IRQ

SIDE_A0

SIDE_A1

SIDE_A2

SIDE_DACK#

SIDE_DRQ

SIDE_IOR#

SIDE_IOW#

SIDE_CS1#

SIDE_CS3#

SIDE_D0

SIDE_D1

SIDE_D2

SIDE_D3

SIDE_D4

SIDE_D5

SIDE_D6

SIDE_D7

SIDE_D8

SIDE_D9

SIDE_D10

SIDE_D11

SIDE_D12

SIDE_D13

SIDE_D14

SIDE_D15

AC_BITCLK

AC_SDOUT

AC_SDIN0

AC_SDIN1

AC_SDIN2

AC_SYNC

AC_RST#

SPDIF_OUT

CL-ATI-SB200

ATA 66/100

66/100

AC97

AB4

AC9

AC7

AA11

AB10

AA10

Y11

C21

Y10

AA5

AA6

Y5

AA4

AB3

Y6

W5

Y8

AA7

AB6

AA12

W12

Y12

AB12

AA8

AB17