Page 1

5

MS-1412 VER:2.0

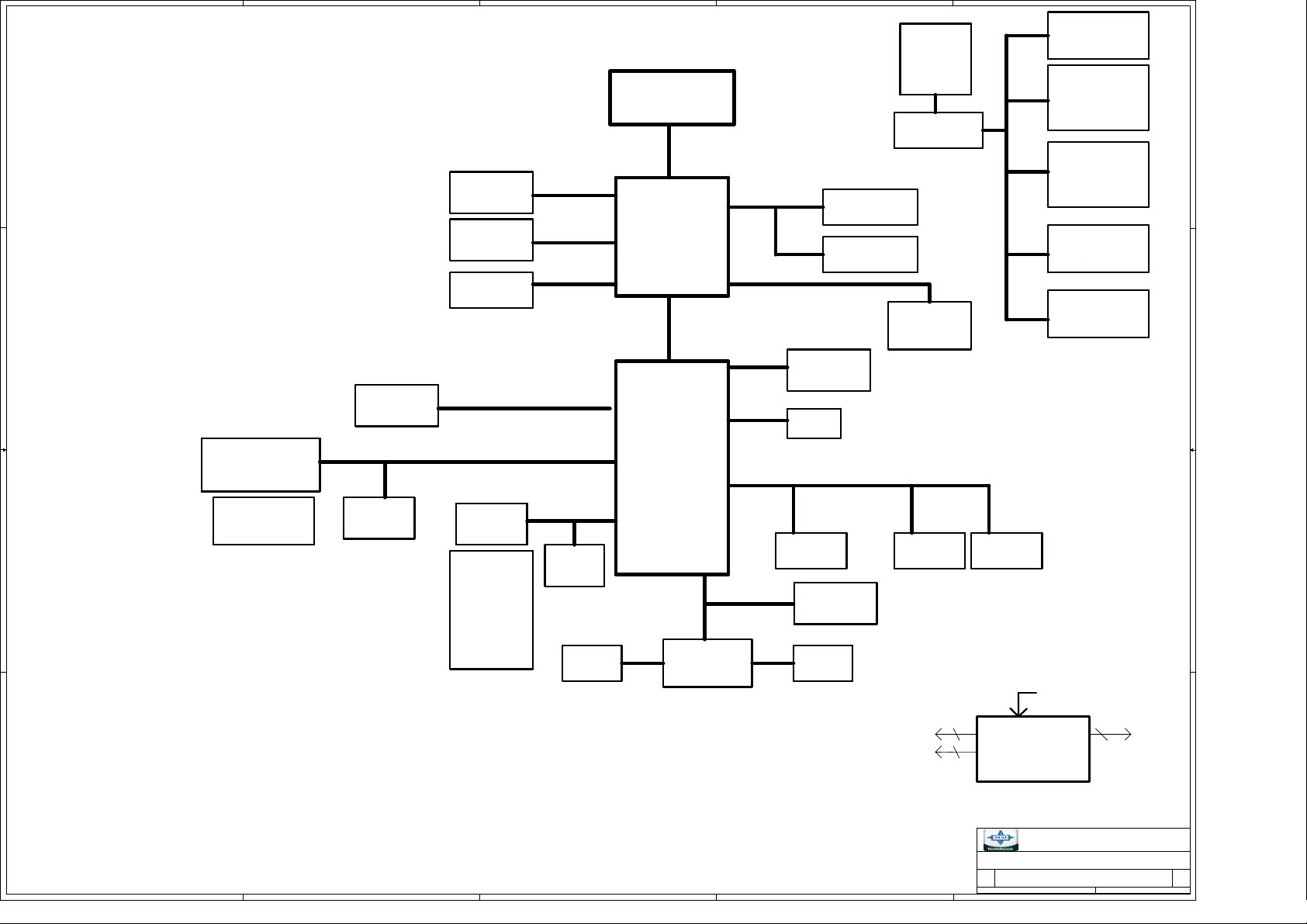

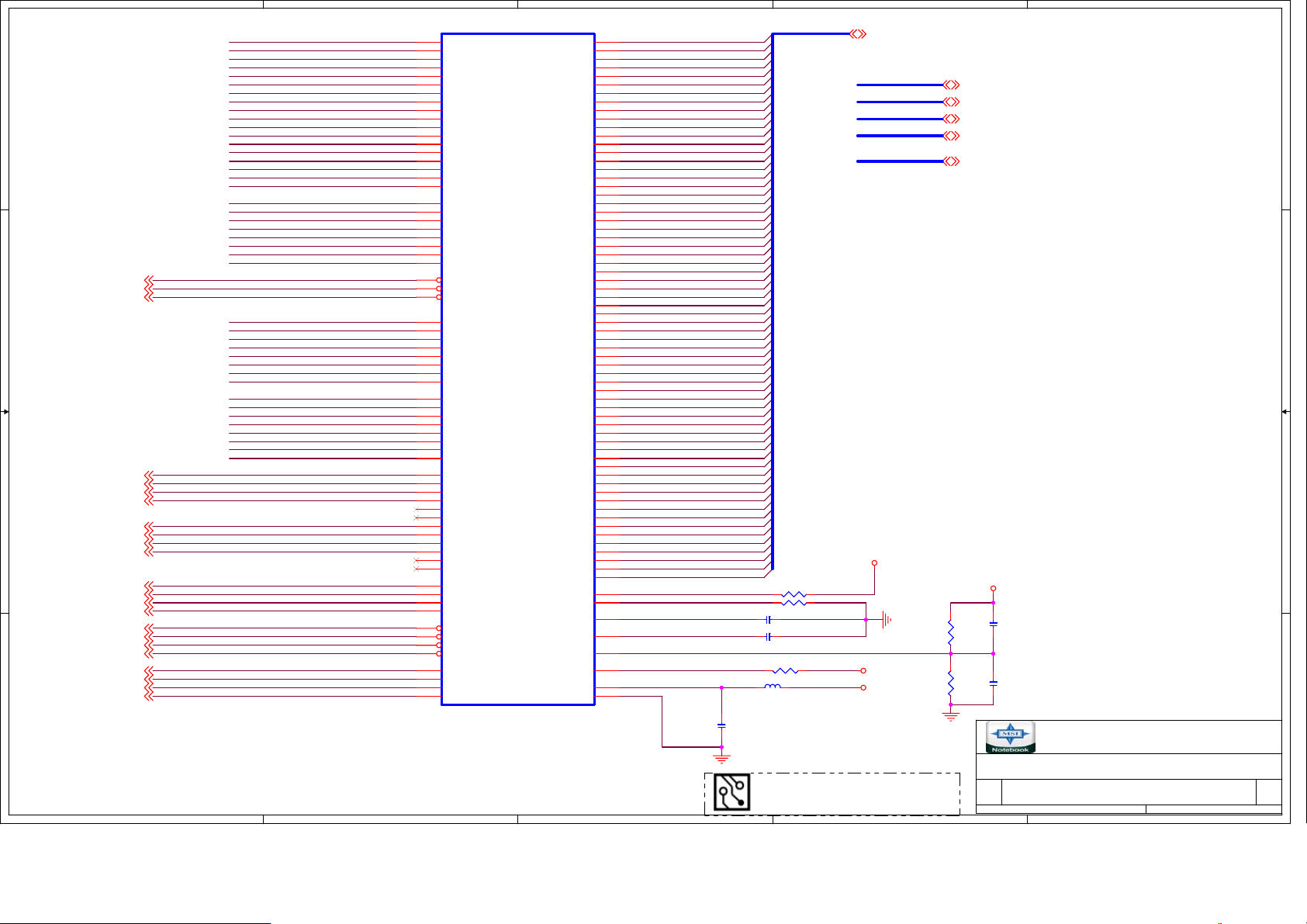

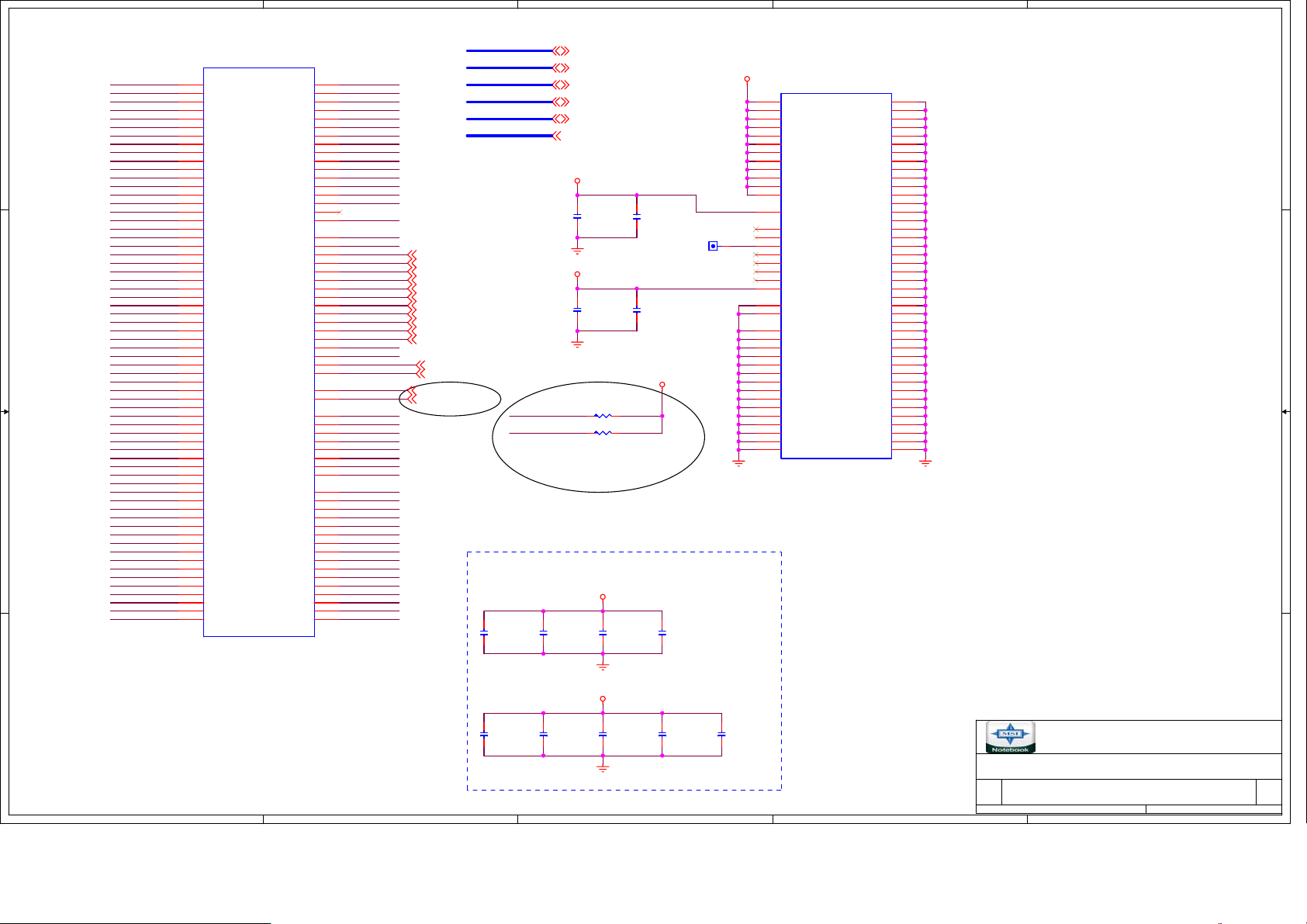

Intel Yonha CPU+ ATi RC410ME&SB450 Chipset

01:BLOCK DIAGRAM

02:PLATFORM

03:Yonah-1 CPU (HOST BUS)

04:Yonah-2 CPU (POWER/GND)

D D

05:Yonah-3

06:RC410ME(HOST)

07:RC410ME(DDR)

08:RC410ME(VIDEO/PCI-E)

09:RC410ME(POWER/STRAPS)

10:DDR2_SODIMM0

11:DDR2_SODIMM1

12:DDR2_Termination

13:CLOCK GEN(ICS 951413CGLFTB)

14:CRT & LVDS & TV CONN

15:SB450(AZALIA/USB)

16:SB450(PCI/CPU/LPC/RTC)

17:SB450(SATA/IDE/POWER)

18:SB450(SATA)

19:SB450(HW STRAPS)

20:USB2.0 CON x 3

21:HDD & CDROM Connect

22:PCI BUS/1394

23:CARDBUS

C C

24:PCI LAN RTL8100C

25:MINI PCI

26:NEW CARD& MDC Connect

27:CODEC/AMP

28:AUDIO/AMP

29:KBC/EC/UP

30:M_Battery Select

31:M_Battery Charger

32:M_System Power

33:M_VDDR & +1.8VDIMM

34:M_1.05V,1.2V

35:M_CPU power

36:Screw1

37:Screw2

38:EMI

39:KBC POWER SEQUENCE

40:POWER SEQUENCE

B B

1394 & 6 IN 1 CARD

OZ711MP

Page 23

SD/MMC/

XD/MS/MSPRO

4

MINI PCI

Conn.

Page 24

PCI-LAN

RTL8100C

Page 26

TV OUT

Page 14

LVDS

Page 14

CRT

Page 14

PCI Interface

PCI BUS

ALC883

Page 27

Internal SPK

MIC

LINE IN

Earphone

SPDIF Out

S-VIDEO

LVDS

VGA

Azalia

MDC

Page 25

3

Yonah 479

Page 6,7,8,9

15,16,17,18,19

Page 3,4,5

HOST

133/166MHZ 4X

NORTH

BRIDGE

ATI

RC410ME

A_Link Interface

SOUTH

BRIDGE

ATI

SB450

Page

Single Channel

DDRII 400/533/667

MHZ

PCI-E Interface

PATA

IDE2

SATA

LPC BUS

2

DDR-SODIMM0

DDR-SODIMM1

DVD/CDROM

Page 20

HDD

Page 20

USB1.1/2.0

Connectors

USB 0,1,2

Page 22

LPC DUBUG

Page 29

Page 10

Page 11

DC JACK

&

Selector

Page 30

SYS POWER

NEW

CARD

Page 25

Mini_PCI

USB 6

Page 22

New_CARD

USB 3

Page22

1

+3V +5V

MAX 1999

Page 32

VTT(1.05V)

+1.2VRUN

OZ813LP

Page 34

+1.8VDIMM

SMDDR_VTERM

SC486

Page 33

CPU POWER

MAX8736

Page 35

CHARGER

MAX 1772

Page 31

Internal MIC

Page 28

TP & KB

Page 29

KBC

ENE 3910

Page 29

ISA

BIOS

Page 29

14MHZ CRYSTAL

133/166MHZ HOST

100MHZ PCIE

CLK GEN

ICS 951413CGLFT

14MHZ SB

Page 13

A A

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

BLOCK DIAGRAM

MS-1412

1

1.1

of

141Wednesday, November 29, 2006

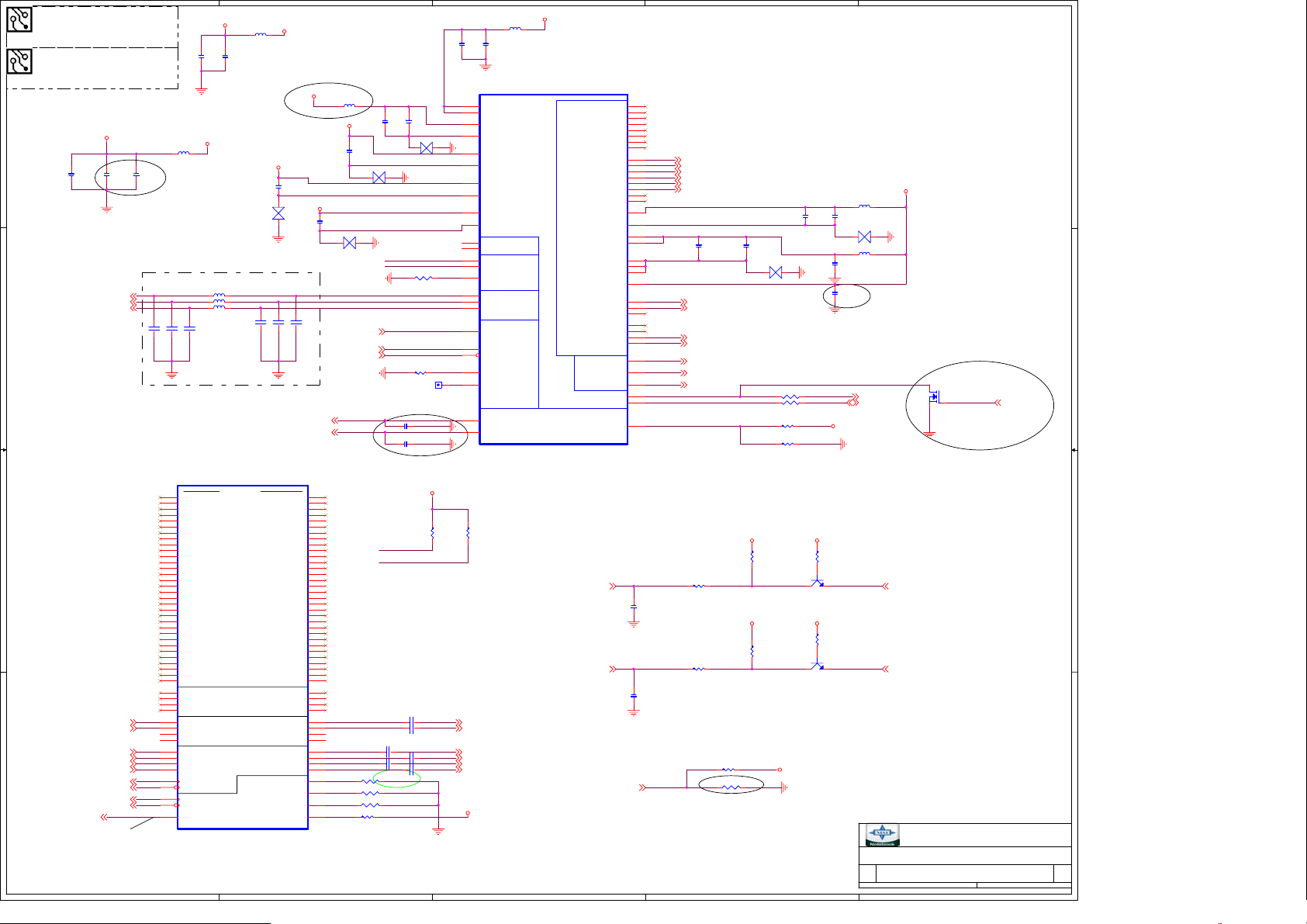

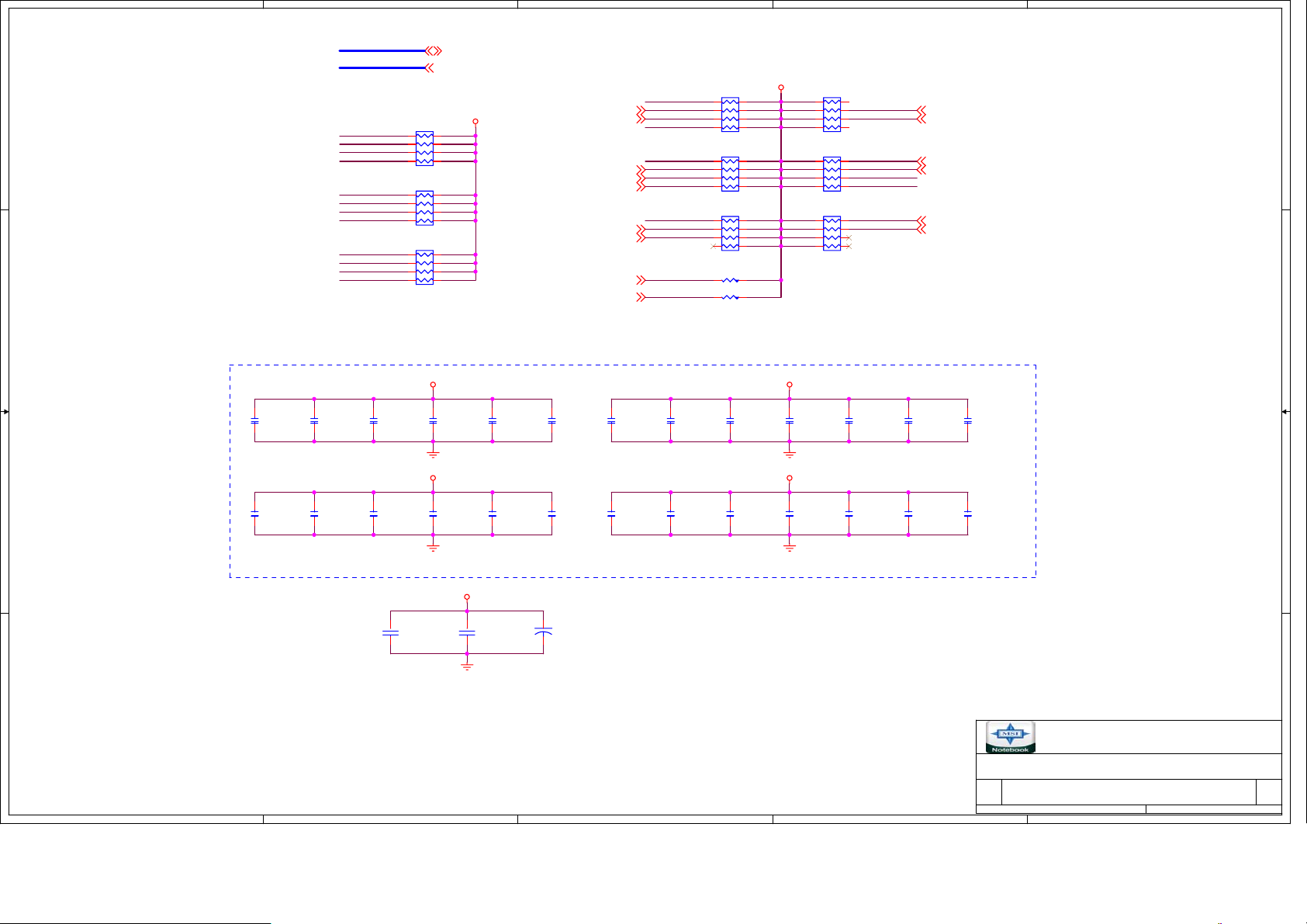

Page 2

5

4

3

2

1

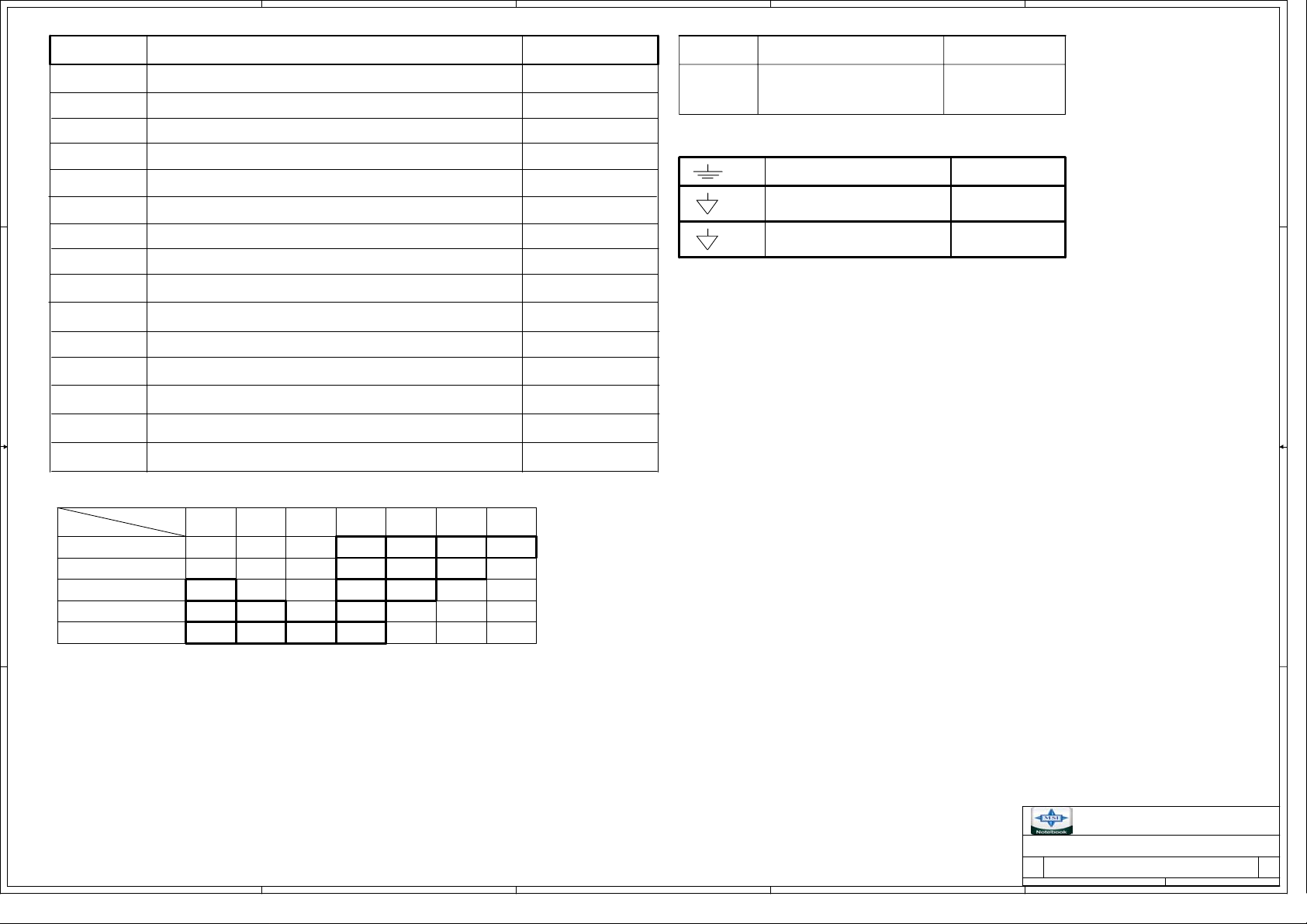

Voltage Rails

Voltage Description

Control Signal

PWR_SRC AC ADAPTER OR BATTERY IN

D D

VHCORE

VTT 1.05 rail for Processor & RC410ME I/O RUND

Core Voltage for Processor

RUNPWROK

Voltage Description

ADD5V

5.0V Power rail Audio

codec(off in S3-S5)

Control Signal

RUND

+1.2VRUN 1.2V powe rail RC410ME, CRT AND LVDS (off in S3- S5 )

+3VRUN

3.3V switched power rail(off in S3 -S5 )

+5VRUN 5.0V switched power rail(off in S 3-S 5)

+1.8VDIMM 1.8V power rail DDR2 (off in S4-S5) DIMM_ON

SMDDR_VTERM 0.9V DDR Termination voltag e (o ff i n S 4-S 5)

+1.8VSUS 1.8V power rail for SB450

+3VSUS 3.3V power rail (off in S4-S5)

C C

+5VSUS

5.0V power rail (off in S4-S5)

+3VALW 3.3V always on power rai l

+5VALW 5.0V always on power rai l

RUND

RUND

RUND

RUN_ON

+3VSUS

SUS_ON

SUS_ON

PWR_SRC

PWR_SRC

GND DIGTIAL GROUD

AGND AUDIO GND

PGND

POWER Analogy GND

POWER STATES

STATE

B B

Full ON

S1M(Power On Suspend)

S3( Suspend to RAM)

S4( Suspend to Disk)

S5 / Soft OFF

SIGNAL Clocks

SLP_S3#

HIGH ON

HIGH

LOW

LOW

LOW

SLP_S4#

HIGH

HIGH

LOW

LOW

SLP_S5#

HIGH

HIGH

HIGH

HIGH

+V*ALWAYS

ON

ON

ON

ONLOW

+V*SUS

ON

ON

ON

OFF

OFF

+V*RUN

ON

ON

OFF

OFF

OFF

ONHIGH

LOW

OFF

OFF

OFF

Note : WHEN AC MODE , System turn on then +V*SUS will always keep

high

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

PLATFORM

MS-1412

1

241Wednesday, November 29, 2006

1.1

of

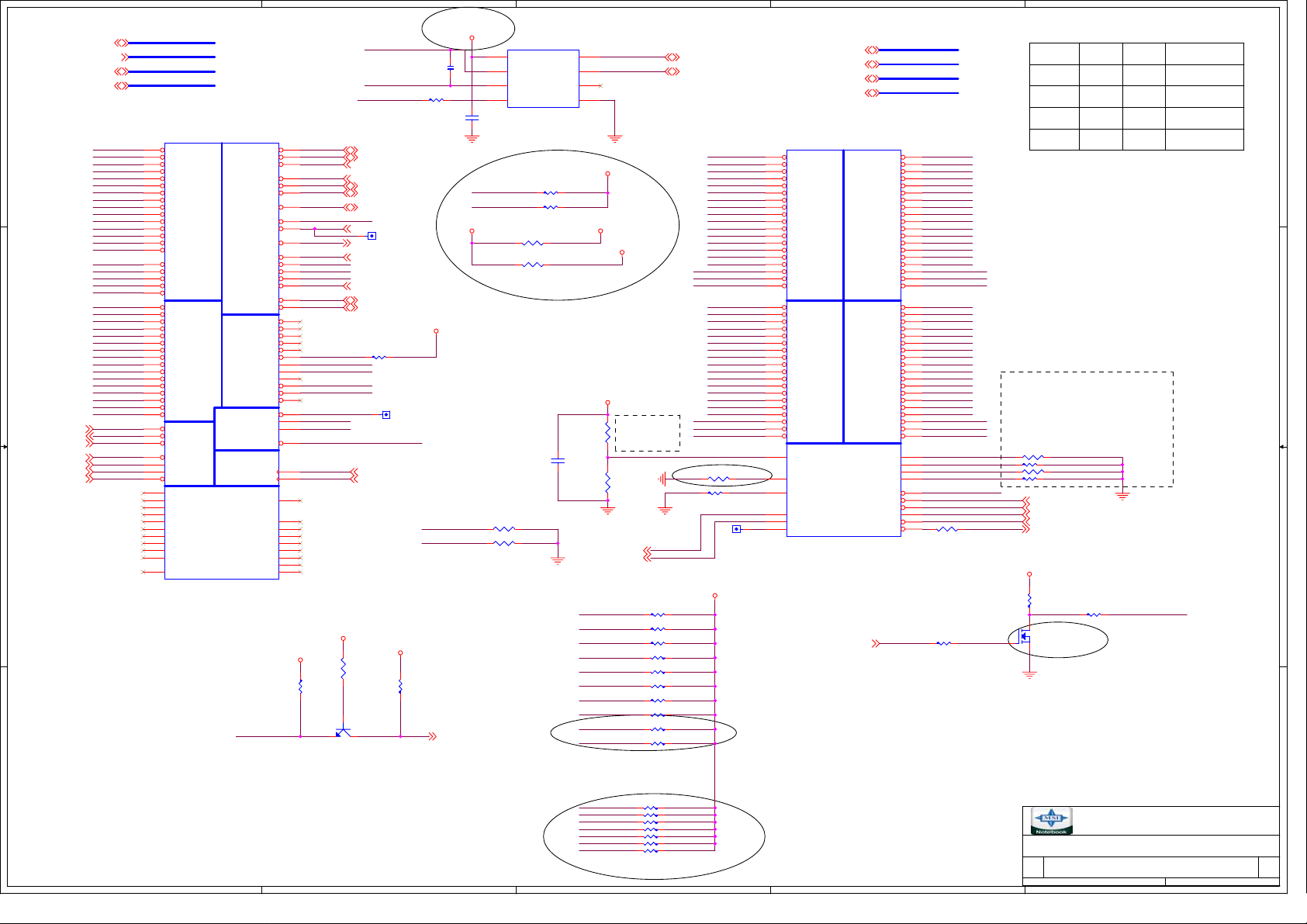

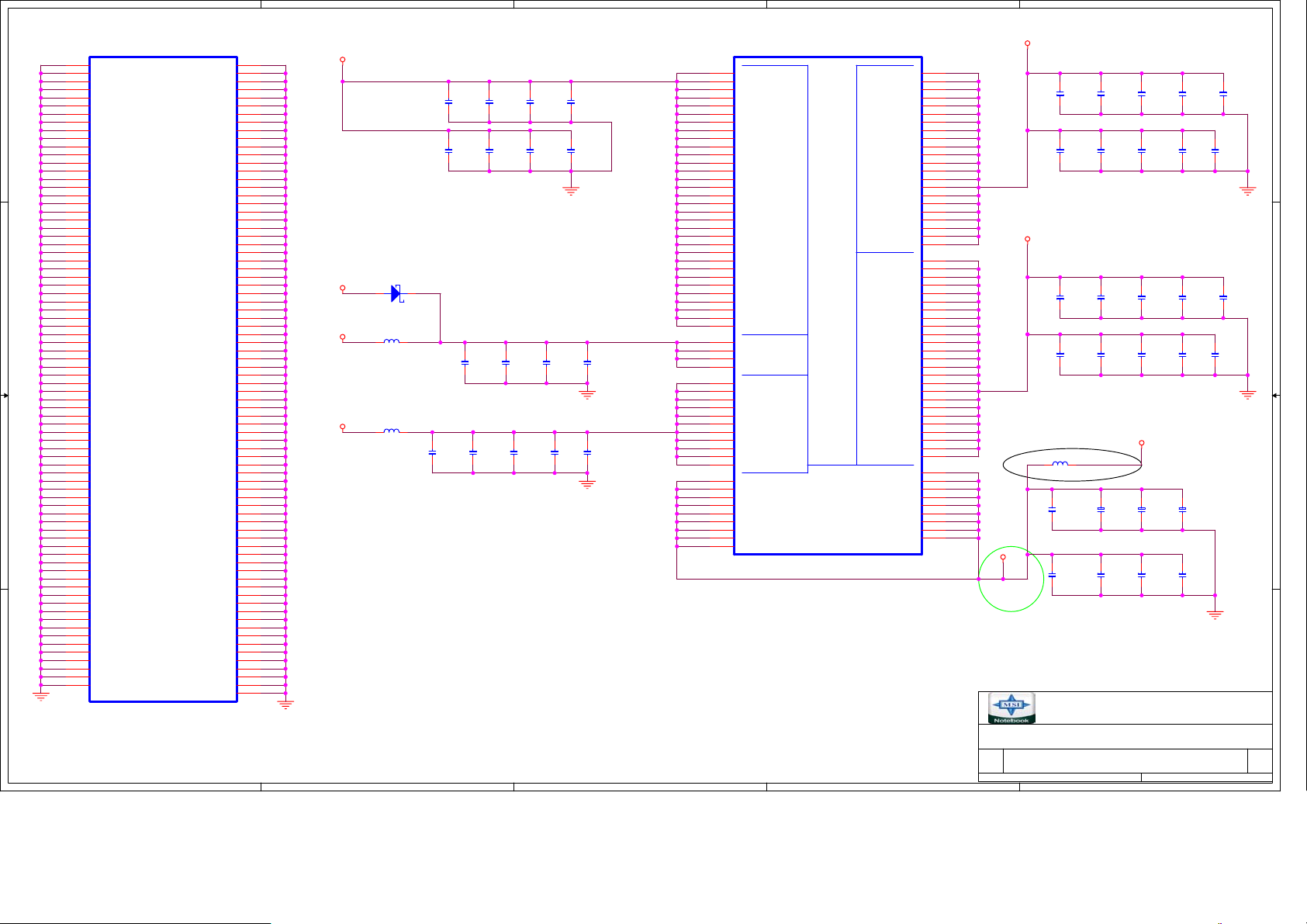

Page 3

5

4

3

2

1

06'05'26 ABLE

C1

2200PF

R832 0R_0603_NC

C2

0.1UF_0402

VTT

HTCK

HTRST-

R859

THERMTRIPSB- 15

+3V_LM86

SMB_CPU_CLK

SMB_CPU_DATA

R620 27

R323 680

U112

D+

DT_CRIT_A#

LM86_MSOP8

SMBCLKVDD

SMBDATA

ALERT#

GND

2

3

4

Close to CPU socket

R315 10K_0402

R316 10K_0402

R955 0R0402

R956 0R0402_NC

06'05'26 ABLE

1K_1%_0402

C3

0.1UF_0402

2K_1%_0402

SMB_CPU_CLK

81

SMB_CPU_DATA

7

6

5

+3V_LM86

+3VALW+3V_LM86

+3VRUN

VTT

R324

R328

IERRHTMS

HTDI

PROCHOTFERRCPUSLPCPU_PWRGD

H_DPSLPCPURSTBREQ0-

05'10'28 ABLE

CPU_INITA20MINTR

NMI

SMISTPCLKIGNNE-

0.5" max

length

BSEL08,13

BSEL18,13

R317 56_040 2

R318 39_0402

R319 150_1%_0402

R321 62R_0402

R636 62R_0402

R637 200_1%_0402

R320 330_0402

R639 200_1%_0402

R898 62R_0402

R899 200_1%_0402

R885 390_1%_0402_NC

R886 390_1%_0402_NC

R887 390_1%_0402_NC

R888 390_1%_0402_NC

R889 390_1%_0402_NC

R890 390_1%_0402_NC

R891 390_1%_0402_NC

05'10'20 ABLE

3

SMB_CPU_DATA 29

HD-0

HD-1

HD-2

HD-3

HD-4

HD-5

HD-6

HD-7

HD-8

HD-9

HD-10

HD-11

HD-12

HD-13

HD-14

HD-15

HDSTBN-0

HDSTBP-0

DBI-0

HD-16

HD-17

HD-18

HD-19

HD-20

HD-21

HD-22

HD-23

HD-24

HD-25

HD-26

HD-27

HD-28

HD-29

HD-30

HD-31

HDSTBN-1

HDSTBP-1

DBI-1

GTLREF

05'11'16 ABLE

R330 51R

1KR901

TP11

VTT

AD26

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

H26

F26

K22

H25

H23

G22

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

M24

N25

M26

C26

D25

B22

B23

C21

J24

J23

J26

U113B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

Yonah

HD-[0..63]6

HDSTBP-[0..3]6

HDSTBN-[0..3]6

DBI-[0..3]6

DATA GRP0 DATA GRP1

DATA GRP2DATA GRP3

DSTBN[2]#

DSTBP[2]#

DSTBN[3]#

DSTBP[3]#

MISC

PWRGOOD

DPRSLPVR16,35

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

PSI#

HD-[0..63]

HDSTBP-[0..3]

HDSTBN-[0..3]

DBI-[0..3]

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

2

HD-32

HD-33

HD-34

HD-35

HD-36

HD-37

HD-38

HD-39

HD-40

HD-41

HD-42

HD-43

HD-44

HD-45

HD-46

HD-47

HDSTBN-2

HDSTBP-2

DBI-2

HD-48

HD-49

HD-50

HD-51

HD-52

HD-53

HD-54

HD-55

HD-56

HD-57

HD-58

HD-59

HD-60

HD-61

HD-62

HD-63

HDSTBN-3

HDSTBP-3

DBI-3

HCOMP0

HCOMP1

HCOMP2

HCOMP3

H_DPRSTPH_DPSLPH_DPWRCPU_PWRGD

CPUSLP-

PR1 0R0402

R108 470R_0402

BSEL[2] BSEL[1] BSEL[0] BCLK

LLL

LL

L

H

L

HH

RESERVED

H

L

RESERVED

0.5" max length

25 MIL AWAY FROM HIGH

SPEED SIGNAL

HCOMP0,2==>18MIL

HCOMP1,3==>5MIL

R325 27.4_1%

R326 54.9_1%_0402

R327 27.4_1%

R329 54.9_1%_0402

H_DPSLP- 16

H_DPWR- 6

CPU_PWRGD 16

PSI-

CPUSLP- 16

PSI- 35

VTT

R142

G

470R_0402

DS

Q107

N-2N7002_SOT23

R140 0R_0603

H_DPRSTP-

05'10'20 ABLE

Title

Size Document Number Rev

Custom

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

Yonah-1 (HOST BUS)

MS-1412

1

133MHZ

166MHZ

341Wednesday, November 29, 2006

1.1

of

HA-[3..31]6

RS-[0..2]6 SMB_CPU_CLK 29

HREQ-[0..4]6

HASTB-[0..1]6

D D

C C

A20M-16

FERR-16

IGNNE-16

STPCLK-16

INTR16

NMI16

SMI-16

B B

A A

HA-[3..31]

RS-[0..2]

HREQ-[0..4]

HASTB-[0..1]

HA-3

HA-4

HA-5

HA-6

HA-7

HA-8

HA-9

HA-10

HA-11

HA-12

HA-13

HA-14

HA-15

HA-16

HASTB-0

HREQ-0

HREQ-1

HREQ-2

HREQ-3

HREQ-4

HA-17

HA-18

HA-19

HA-20

HA-21

HA-22

HA-23

HA-24

HA-25

HA-26

HA-27

HA-28

HA-29

HA-30

HA-31

HASTB-1

A20MFERRIGNNE-

STPCLKINTR

NMI CPUCLK0

SMI-

U113A

J4

A[3]#

L4

A[4]#

M3

K5

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

5

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RSVD[10]

RSVD[11]

Yonah

ADDR GROUP 0

ADDR GROUP 1

Cap close to

thermal

sensor

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALS

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

THERM

BCLK[0]

BCLK[1]

H CLK

RSVD[12]

RSVD[13]

RSVD[14]

RSVD[15]

RSVD[16]

RSVD[17]

RESERVED

RSVD[18]

RSVD[19]

RSVD[20]

THERMTRIP-

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

A25

C7

A22

A21

T22

D2

F6

D3

C1

AF1

D22

C23

C24

VTT

ADSBNRBPRI-

DEFERDRDYDBSY-

BREQ0IERR-

CPU_INITHLOCKCPURST-

RS-0

RS-1

RS-2

H_TRDY-

HITHITM-

HTCK

HTDI

HTMS

HTRST-

PROCHOTTHERMDA

THERMDC

CPUCLK-0

R857

R858

62R_0402

VTT

B

E C

Q121

MMBT3904

THERMDA

THERMDC

THERMTRIP-

ADS- 6

BNR- 6

BPRI- 6

DEFER- 6

DRDY- 6

DBSY- 6

BREQ0- 6

CPU_INIT- 16

TP1

HLOCK- 6

CPURST- 6

H_TRDY- 6

HIT- 6

HITM- 6

R833 56_0402

THERMTRIP-

CPUCLK0 13

CPUCLK-0 13

+3VSUS

1K_1%_0402

4

TP130

10K_0402

Page 4

5

U113D

A4

VSS1

A8

VSS2

A11

VSS3

A14

VSS4

A16

VSS5

A19

VSS6

D D

C C

B B

A23

A26

B11

B13

B16

B19

B21

B24

C11

C14

C16

C19

C22

C25

D11

D13

D16

D19

D23

D26

E11

E14

E16

E19

E21

E24

F11

F13

F16

F19

F22

F25

G23

G26

H21

H24

K23

K26

L21

L24

M22

M25

N23

N26

VSS7

VSS8

B6

VSS9

B8

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

C5

VSS17

C8

VSS18

VSS19

VSS20

VSS21

VSS22

C2

VSS23

VSS24

VSS25

D1

VSS26

D4

VSS27

D8

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

E3

VSS35

E6

VSS36

E8

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

F5

VSS44

F8

VSS45

VSS46

VSS47

VSS48

VSS49

F2

VSS50

VSS51

VSS52

G4

VSS53

G1

VSS54

VSS55

VSS56

H3

VSS57

H6

VSS58

VSS59

VSS60

J2

VSS61

J5

VSS62

J22

VSS63

J25

VSS64

K1

VSS65

K4

VSS66

VSS67

VSS68

L3

VSS69

L6

VSS70

VSS71

VSS72

M2

VSS73

M5

VSS74

VSS75

VSS76

N1

VSS77

N4

VSS78

VSS79

VSS80

P3

VSS81

Yonah

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

GND

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

VHCORE VHCORE

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

4

U113C

A7

VCC[1]

A9

VCC[2]

A10

VCC[3]

A12

VCC[4]

A13

VCC[5]

A15

VCC[6]

A17

VCC[7]

A18

VCC[8]

A20

VCC[9]

B7

VCC[10]

B9

VCC[11]

B10

VCC[12]

B12

VCC[13]

B14

VCC[14]

B15

VCC[15]

B17

VCC[16]

B18

VCC[17]

B20

VCC[18]

C9

VCC[19]

VCC[20]

VCC[21]

VCC[22]

VCC[23]

VCC[24]

VCC[25]

D9

VCC[26]

VCC[27]

VCC[28]

VCC[29]

VCC[30]

VCC[31]

VCC[32]

E7

VCC[33]

E9

VCC[34]

E10

VCC[35]

E12

VCC[36]

E13

VCC[37]

E15

VCC[38]

E17

VCC[39]

E18

VCC[40]

E20

VCC[41]

F7

VCC[42]

F9

VCC[43]

F10

VCC[44]

F12

VCC[45]

F14

VCC[46]

F15

VCC[47]

F17

VCC[48]

F18

VCC[49]

F20

VCC[50]

VCC[51]

VCC[52]

VCC[53]

VCC[54]

VCC[55]

VCC[56]

VCC[57]

VCC[58]

VCC[59]

VCC[60]

VCC[61]

VCC[62]

VCC[63]

VCC[64]

VCC[65]

VCC[66]

VCC[67]

Yonah

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

POWER

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[100]

VCCP[1]

VCCP[2]

VCCP[3]

VCCP[4]

VCCP[5]

VCCP[6]

VCCP[7]

VCCP[8]

VCCP[9]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

VTT

CPU_VID0 35

CPU_VID1 35

CPU_VID2 35

CPU_VID3 35

CPU_VID4 35

CPU_VID5 35

CPU_VID6 35

3

+1.5VRUN

C4

10UF/10V_0805

C5

0.01UF_0402

VHCORE

0.01uf and 10uf of a pair capacitors

place near PIN B26

R331

100_1%_0402

VCCSENSE_2 35

VSSSENSE_2 35

R332

100_1%_0402

LAYOUT NOTE:

Route VCCSENSE and VSSSENSE traces at 27.4Ohms

with 50 mil spacing.

Place PU and PD within 1 inch of CPU.

2

1

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

Yonah-2 (Power / GND)

MS-1412

1

441Wednesday, November 29, 2006

1.1

of

Page 5

5

4

VHCORE

3

2

1

C6

D D

C C

22UF/6.3V_0805

C7

22UF/6.3V_0805

C26

22UF/6.3V_0805

C8

22UF/6.3V_0805

C27

22UF/6.3V_0805

VTT

C9

22UF/6.3V_0805

C28

22UF/6.3V_0805

C10

22UF/6.3V_0805

C17

22UF/6.3V_0805

C29

22UF/6.3V_0805

close to cpu socket

C11

22UF/6.3V_0805

C18

22UF/6.3V_0805

C30

22UF/6.3V_0805

C12

22UF/6.3V_0805

C19

22UF/6.3V_0805

C32

22UF/6.3V_0805

C13

22UF/6.3V_0805

VHCORE

C21

22UF/6.3V_0805

VHCORE

C33

22UF/6.3V_0805

C14

22UF/6.3V_0805

C22

22UF/6.3V_0805

C34

22UF/6.3V_0805

C15

22UF/6.3V_0805

C23

22UF/6.3V_0805

C35

22UF/6.3V_0805

C16

22UF/6.3V_0805

C24

22UF/6.3V_0805

C36

22UF/6.3V_0805

C25

22UF/6.3V_0805

C37

22UF/6.3V_0805

電容要放對襟

+

12

0.1UF_0402

C44

330UF/6.3V

B B

C38

0.1UF_0402

C40

C39

0.1UF_0402

0.1UF_0402

C42

C41

0.1UF_0402

C43

0.1UF_0402

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

Yonah-3

MS-1412

1

1.1

of

541Wednesday, November 29, 2006

Page 6

5

HA-[3..31]3

D D

D18

2

BAT54A_SOT23

3

1

R646

49.9R1%_0402

R647

100_0402

HDSTBP-[0..3]

HDSTBN-[0..3]

DBI-[0..3]

VTT

+1.8VRUN

06'02'16 ATi

suggest

+1.8VDIMM

R643

220K_0402

RC410_SUS_STATRC410_SYSRESET-

NB_GTLREF

C742

1UF_0402

HREQ-[0..4]3

HASTB-03

HASTB-13

ADS-3

BNR-3

BPRI-3

DEFER-3

DRDY-3

DBSY-3

H_DPWR-3

HLOCK-3

H_TRDY-3

HITM-3

HIT-3

RS-03

RS-13

RS-23

BREQ0-3

CPURST-3

VTT

L34

200Ohm500mA_0805

NB_PWRGD

R644 49.9R1%_0402

R645 24.9R_0402

C741 220PF_0402 R613 0R

HDSTBP-[0..3]3

HDSTBN-[0..3]3

DBI-[0..3]3

C C

SUS_STAT-15

05'10'20 ABLE

B B

NB_RST-16

4

HA-3

HA-4

HA-5

HA-6

HA-7

HA-8

HA-9

HA-10

HA-11

HA-12

HA-13

HA-14

HA-15

HA-16

HREQ-0

HREQ-1

HREQ-2

HREQ-3

HREQ-4

HASTB-0

HA-17

HA-18

HA-19

HA-20

HA-21

HA-22

HA-23

HA-24

HA-25

HA-26

HA-27

HA-28

HA-29

HA-30

HA-31

HASTB-1

ADSBNRBPRIDEFERDRDYDBSYH_DPWRHLOCKH_TRDYHITMHITRS-0

RS-1

RS-2

BREQ0-

R642 0R0402

TP131

RC410_CPVDD

C740 1UF_0402

R648

1.8K_0402

AH14

AH13

AJ13

G28

H26

G27

G30

G29

G26

H28

J28

H25

K28

H29

J29

K24

K25

F29

G25

F26

F28

E29

H27

M28

K29

K30

J26

L28

L29

M30

K27

M29

K26

N28

L26

N25

L25

N24

L27

F25

F24

E23

E25

G24

F23

G22

E27

F22

E24

D26

E26

G23

D23

D25

C11

E11

A3

E3

B11

D11

H21

H20

H22

C4

U205A

CPU_A3#

CPU_A4#

CPU_A5#

CPU_A6#

CPU_A7#

CPU_A8#

CPU_A9#

CPU_A10#

CPU_A11#

CPU_A12#

CPU_A13#

CPU_A14#

CPU_A15#

CPU_A16#

CPU_REQ0#

CPU_REQ1#

CPU_REQ2#

CPU_REQ3#

CPU_REQ4#

CPU_ADSTB0#

CPU_A17#

CPU_A18#

CPU_A19#

CPU_A20#

CPU_A21#

CPU_A22#

CPU_A23#

CPU_A24#

CPU_A25#

CPU_A26#

CPU_A27#

CPU_A28#

CPU_A29#

CPU_A30#

CPU_A31#

CPU_ADSTB1#

CPU_ADS#

CPU_BNR#

CPU_BPRI#

CPU_DEFER#

CPU_DRDY#

CPU_DBSY#

CPU_DPWR#

CPU_LOCK#

CPU_TRDY#

CPU_HITM#

CPU_HIT#

CPU_RS0#

CPU_RS1#

CPU_RS2#

RESERVED0

CPU_CPURST#

RESERVED1

SUS_STAT#

SYSRESET#

POWERGOOD

CPU_COMP_P

CPU_COMP_N

CPVDD

CPVSS

CPU_VREF

THERMALDIODE_P

THERMALDIODE_N

TESTMODE

RC410MB_2

PART 1 OF 6

ADDR. GROUP 1 ADDR. GROUP 0CONTROLMISC.

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

CPU_D12#

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

CPU_D13#

CPU_D14#

CPU_D15#

CPU_DBI0#

CPU_DSTB0N#

CPU_DSTB0P#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

CPU_D30#

CPU_D31#

CPU_DBI1#

CPU_DSTB1N#

CPU_DSTB1P#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_DBI2#

CPU_DSTB2N#

CPU_DSTB2P#

CPU_D48#

CPU_D49#

AGTL+ I/F

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

CPU_DBI3#

CPU_DSTB3N#

CPU_DSTB3P#

3

HD-[0..63]

HD-0

E28

HD-1

D28

HD-2

D29

HD-3

C29

HD-4

D30

HD-5

C30

HD-6

B29

HD-7

C28

HD-8

C26

HD-9

B25

HD-10

B27

HD-11

C25

HD-12

A27

HD-13

C24

HD-14

A24

HD-15

B26

C27

A28

B28

HD-16

C19

HD-17

C23

HD-18

C20

HD-19

C22

HD-20

B22

HD-21

B23

HD-22

C21

HD-23

B24

HD-24

E21

HD-25

B21

HD-26

B20

HD-27

G19

HD-28

F21

HD-29

B19

HD-30

E20

HD-31

D21

A21

D22

E22

HD-32

C18

HD-33

F19

HD-34

E19

HD-35

A18

HD-36

D19

HD-37

B18

HD-38

C17

HD-39

B17

HD-40

E17

HD-41

B16

HD-42

C15

HD-43

A15

HD-44

B15

HD-45

F16

HD-46

G18

HD-47

F18

C16

D18

E18

HD-48

E16

HD-49

D16

HD-50

C14

HD-51

B14

HD-52

E15

HD-53

D15

HD-54

C13

HD-55

E14

HD-56

F13

HD-57

B13

HD-58

A12

HD-59

C12

HD-60

E12

HD-61

D13

HD-62

D12

HD-63

B12

E13

F15

G15

DBI-0

HDSTBN-0

HDSTBP-0

DBI-1

HDSTBN-1

HDSTBP-1

DBI-2

HDSTBN-2

HDSTBP-2

DBI-3

HDSTBN-3

HDSTBP-3

HD-[0..63] 3

FAN_PWM029

IMVP_PWRGD27,35

RB11 10K_0402

RUN_ON29,32,33

CB22

10UF/10V_0805

NB_PWRGD

RUN_ON

R860

0R0402

U120

NC7S08_SC70_5

CB23 0.1uF_0402_NC

+3VSUS

2

1

+1.2VRUN_PWRGD34

UB7A

LM358_SOIC8

RB13 100K

RB14

100K

C745 1UF

3 5

VTT_PWRGD34

2

PWR_SRC

8

3

1

2

4

2

S-BAT54C_SOT23_NC

NB PWRGD比SB

PWRGD

R861 470K

4

D26 BAS40WS

R614 0R

R615 0R

1

UB7B

+5VRUN

CB24

0.1uF_0402

C977 0.1UF_0402

5

U209A

1 6

ALLSYSPG 29+1.8VSUS_PWRGD33

+3VRUN

QB5

65241

3

SI3456DV

VCCFAN1

VCCFAN1

10UF/10V_0805

1

早

33MS

SB_PWRGD-

AC

+3VRUN

CB25

C978

0.1UF_0402

R610

100K_0402

ALLSYSPG

NC7WZ14-SC70

For latch MOBILE

CPU,05'12'19

Able

3

DB5

LM358_SOIC8

RB16

10K_0402

FAN1

CONB7

1

2

3

FOXCONN ( HS8103E )

<CONN NAME>

+3VSUS+3VSUS

5

U209B

3 4

NC7WZ14-SC70

5

6

SB_PWRGD1- 8

8

7

4

FAN_TACH1 29

SB_PWRGD 15

CHECK

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

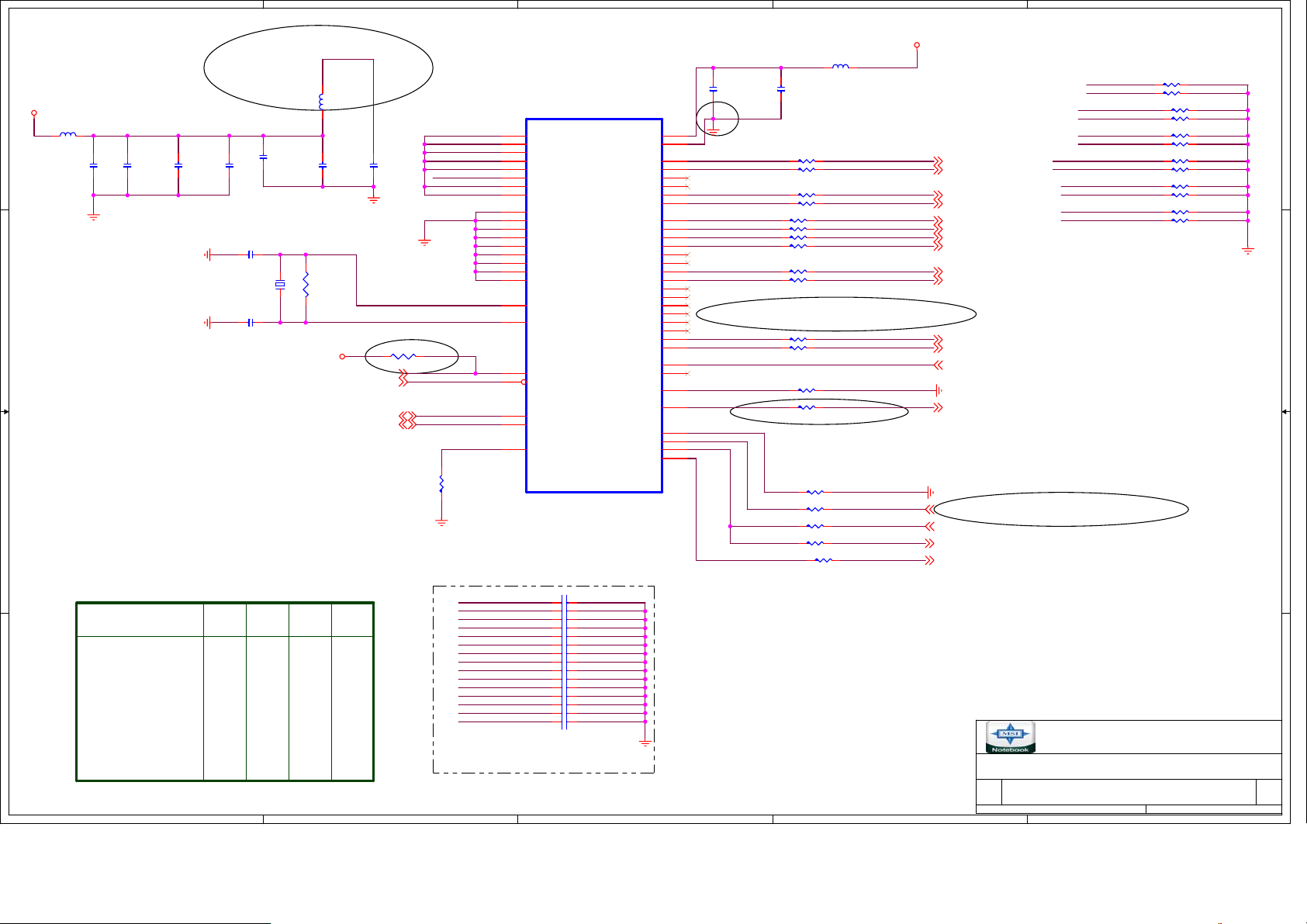

RC410ME(CPU)/PWRGD&FAN

MS-1412

1

of

641Wednesday, November 29, 2006

1.1

Page 7

5

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

D D

SA_RAS-10,11,12

SA_CAS-10,11,12

SA_WE-10,11,12

C C

CLK_SDRAM-010

CLK_SDRAM010

CLK_SDRAM-110

B B

A A

CLK_SDRAM110

CLK_SDRAM-211

CLK_SDRAM211

CLK_SDRAM-311

CLK_SDRAM311

CKE010,12

CKE110,12

CKE211,12

CKE311,12

SM_CS-010,12

SM_CS-110,12

SM_CS-211,12

SM_CS-311,12

SM_ODT010,12

SM_ODT111,12

SM_ODT210,12

SM_ODT311,12

5

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_BS-0

SA_BS-1

SA_BS-2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_RASSA_CASSA_WE-

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS-0

SA_DQS-1

SA_DQS-2

SA_DQS-3

SA_DQS-4

SA_DQS-5

SA_DQS-6

SA_DQS-7

CLK_SDRAM-0

CLK_SDRAM0

CLK_SDRAM-1

CLK_SDRAM1

CLK_SDRAM-2

CLK_SDRAM2

CLK_SDRAM-3

CLK_SDRAM3

CKE0

CKE1

CKE2

CKE3

SM_CS-0

SM_CS-1

SM_CS-2

SM_CS-3

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

4

U205C

AK27

MEM_A0

AJ27

MEM_A1

AH26

MEM_A2

AJ26

MEM_A3

AH25

MEM_A4

AJ25

MEM_A5

AH24

MEM_A6

AH23

MEM_A7

AJ24

MEM_A8

AJ23

MEM_A9

AH27

MEM_A10

AH22

MEM_A11

AJ22

MEM_A12

AF28

MEM_A13

AJ21

MEM_A14

AG27

MEM_A15

AJ28

MEM_A16

AH21

MEM_A17

AJ17

MEM_DM0

AG15

MEM_DM1

AE20

MEM_DM2

AF25

MEM_DM3

Y27

MEM_DM4

AB28

MEM_DM5

R26

MEM_DM6

R28

MEM_DM7

AJ29

MEMB_RAS#

AG28

MEMB_CAS#

AH30

MEMB_WE#

AJ18

MEM_DQS0P

AE14

MEM_DQS1P

AF22

MEM_DQS2P

AE25

MEM_DQS3P

W27

MEM_DQS4P

AB29

MEM_DQS5P

P25

MEM_DQS6P

R29

MEM_DQS7P

AH17

MEM_DQS0N

AF15

MEM_DQS1N

AE22

MEM_DQS2N

AF26

MEM_DQS3N

W26

MEM_DQS4N

AB30

MEM_DQS5N

R25

MEM_DQS6N

R30

MEM_DQS7N

AC26

MEM_CK0N

AC25

MEM_CK0P

AF16

MEM_CK1N

AE16

MEM_CK1P

V29

MEM_CK2N

V30

MEM_CK2P

AC24

MEM_CK3N

AC23

MEM_CK3P

AG17

MEM_CK4N

AF17

MEM_CK4P

W29

MEM_CK5N

W28

MEM_CK5P

AH20

MEM_CKE0

AJ20 AE29

MEM_CKE1 MEM_COMPN

AE24

MEM_CKE2

AE21

MEM_CKE3

AH29

MEM_CS0#

AG29

MEM_CS1#

AH28

MEM_CS2#

AF29

MEM_CS3#

AG30

MEM_ODT0

AE28

MEM_ODT1

AC30

MEM_RSRV2

Y30

MEM_RSRV3

RC410MB_2

4

PART 3 OF 6

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_B I/F

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_COMPP

MEM_CAP2

MEM_CAP1

MEM_VREF

MEM_VMODE

MPVDD

MPVSS

SA_MD0

AJ16

SA_MD1

AH16

SA_MD2

AJ19

SA_MD3

AH19

SA_MD4

AH15

SA_MD5

AK16

SA_MD6

AH18

SA_MD7

AK19

SA_MD8

AF13

SA_MD9

AF14

SA_MD10

AE19

SA_MD11

AF19

SA_MD12

AE13

SA_MD13

AG13

SA_MD14

AF18

SA_MD15

AE17

SA_MD16

AF20

SA_MD17

AF21

SA_MD18

AG23

SA_MD19

AF24

SA_MD20

AG19

SA_MD21

AG20

SA_MD22

AG22

SA_MD23

AF23

SA_MD24

AD25

SA_MD25

AG25

SA_MD26

AE27

SA_MD27

AD27

SA_MD28

AE23

SA_MD29

AD24

SA_MD30

AE26

SA_MD31

AD26

SA_MD32

AA25

SA_MD33

Y26

SA_MD34

W24

SA_MD35

U25

SA_MD36

AA26

SA_MD37

Y25

SA_MD38

V26

SA_MD39

W25

SA_MD40

AC28

SA_MD41

AC29

SA_MD42

AA29

SA_MD43

Y29

SA_MD44

AD30

SA_MD45

AD29

SA_MD46

AA30

SA_MD47

Y28

SA_MD48

U27

SA_MD49

T27

SA_MD50

N26

SA_MD51

M27

SA_MD52

U26

SA_MD53

T26

SA_MD54

P27

SA_MD55

P26

SA_MD56

U29

SA_MD57

T29

SA_MD58

P29

SA_MD59

N29

SA_MD60

U28

SA_MD61

T28

SA_MD62

P28

SA_MD63

N27

RC410_MEM_COMPN

RC410_MEM_COMPP

AJ15

N30

AJ14

AB27

AD28

RC410_MEM_MPVDD

AB26

AA27

3

SA_MD[0..63]

R651 61.9_1%_0402

R652 61.9_1%_0402

C750 470nF_0402_NC

C752 470nF_0402_NC

RC410_MEM_VREF

R654 1K_1%_0402

L35

200Ohm500mA_0805

C754

1UF_0402

MPVSS need to connect to GND plane

immediately through

3

a dedicated VIA

2

SA_MD[0..63] 10,11

SA_DM[0..7]

SA_DQS[0..7]

SA_DQS-[0..7]

SA_MA[0..14]

SA_BS-[0..2]

+1.8VDIMM

1K_1%_0402

+1.8VDIMM

+1.8VRUN

1K_1%_0402

2

R653

R655

1

SA_DM[0..7] 10,11

SA_DQS[0..7] 10,11

SA_DQS-[0..7] 10,11

SA_MA[0..14] 10,11,12

SA_BS-[0..2] 10,11,12

+1.8VDIMM

C751

100nF_0402

C753

100nF_0402

MICRO-STAR INT'L CO.,LTD.

Title

RC410ME(DDR)

Size Document Number Rev

B

Date: Sheet

MS-1412

741Wednesday, November 29, 2006

1

of

1.1

Page 8

C780

1UF_0402

VGA_RED14

VGA_GRN14

VGA_BLU14

PLVDD

5

C781

22UF/6.3V_0805

解

CRT

06'02'06 Able

C1024

22UF/6.3V_0805

有水波汶

CI845

10PF

C778

1UF_0402

+1.8VRUN

L41

200Ohm500mA_0.3Ohm

LI2 60S/0603

LI3 60S/0603

LI4 60S/0603

CI846

CI847

10PF

10PF

AVDDQ

L40

C779

10UF/10V_0805

100nF_0402

+1.8VRUN

200Ohm500mA_0.3Ohm

AVDDQ

C770

12

CI842

10PF

PUT AVDD, AVDDDI, AVDDQ,

PLVDD DECOUPLING CAPS ON THE

BOTTOM SIDE, CLOSE TO BALLS

RSET resistor R246 need 10mils

trace with at least 10mils spacing.

Also need to connect GND

at AVSSQ HF cap.

D D

C C

For EMI

U205B

J5

J4

K4

L4

L6

L5

M5

M4

N4

P4

P6

為另外

AG10

AF10

AA5

AA4

AB4

AB3

AC6

AC5

AD5

AD4

AF8

AG8

AG6

AG7

AK7

AJ7

AG4

AH4

AG9

AE9

P5

R5

R4

T4

T3

U6

U5

V5

V4

W4

W3

Y6

Y5

K2

L2

M2

M1

H2

RC410MB_2

B B

PCIE_RXP025

PCIE_RXN025

A_RX0P16

A_RX0N16

A_RX1P16

A_RX1N16

A A

SBLINKCLK13

SBLINKCLK-13

NBSRCCLK13

NBSRCCLK-13

BMREQ-16

設定外3頻 隻腳其中依之

HSYNC#,VSYNC#

兩支

,

亦有接到南橋

5

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_CLKP

SB_CLKN

GFX_CLKP

GFX_CLKN

BMREQ#

PART 2 OF 6

PCIE I/F TO SLOT

PCIE I/F TO SB

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

PCE_TXSET

PCE_ISET

PCE_PCAL

PCE_NCAL

(1.8V)

JP3

SHORT

CI843

10PF

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

4

+3VRUN

L37

28L900m_100_0805

PLVDD

CI844

10PF

LDDC_CLK14

LDDC_DATA14

100nF_0402

+1.8VRUN

C769

C773

100nF_0402

JP4

1 2

VGA_RED_L

VGA_GRN_L

VGA_BLU_L

14M_ICH13

NBCLK13

NBCLK-13

C767

10UF/10V_0805

JP2

1 2

SHORT

EMI request 05'12'30

N1

N2

P2

R2

R1

T1

T2

U2

V2

V1

W1

W2

Y2

AA2

AA1

AB1

AB2

AC2

AD2

AD1

AE1

AE2

AF2

AG2

AG1

AH1

AH2

AJ2

AJ3

AJ4

AK4

AJ5

AJ8

AJ9

AE6

AF6

PCIE_TXP0_C

AJ6

PCIE_TXN0_C

AK6

AE4

AF4

SB_TX0P_C

AJ10

AJ11

AK9

AK10

AK13

AJ12

AH12

AG12

C759 0.1UF_0402

SB_TX0N_C

SB_TX1P_C

C761 0.1UF_0402

SB_TX1N_C

R656 8.25K_0402_1%

R657 10K_0402

R659 100R_0402

4

RC410_AVDD

C768

100nF_0402

JP1 SHORT

1 2

SHORT

VGA_VSYNC

VGA_HSYNC

R883 4.7K_0402

TP175

CI848 10PF_0402

CI849 10PF_0402

+3VRUN

R665

4.7K_0402

LDDC_CLK

LDDC_DATA

C755 0.1UF_0402

C756 0.1UF_0402

C760 0.1UF_0402

C762 0.1UF_0402

150R_0402R658

715_1%_0402R662

4.7K_0402

C763

100nF_0402

G5

G4

C9

C10

D8

C8

B8

B9

H10

H9

J2

H3

B3

C3

B10

F10

E10

D10

G1

J1

K1

G2

F1

D2

C1

R666

PCIE_TXP0 25

PCIE_TXN0 25

A_TX0P 16

A_TX0N 16

A_TX1P 16

A_TX1N 16

06'02'16 ATi

suggest

+VDDA12

C764

1UF_0402

U205D

VDDR3_1

VDDR3_2

AVDD

AVSSN

AVDDDI

AVSSDI

AVDDQ

AVSSQ

PLLVDD

PLLVSS

TMDS_HPD

DDC_DATA

DACVSYNC

DACHSYNC

RSET

RED

GREEN

BLUE

OSCIN

CPU_CLKP

CPU_CLKN

TVCLKIN

OSCOUT

I2C_CLK

I2C_DATA

RC410MB_2

3

+3VRUN

L53

200Ohm500mA_0.3Ohm

PART 4 OF 6

CRT

CLK. GEN.

3

SVID

VGA_HSYNC14

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXOUT_U3N

TXOUT_U3P

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXOUT_L3N

TXOUT_L3P

LPVDD

LPVSS

LVDDR18A_1

LVDDR18A_2

LVSSR_1

LVSSR_2

LVSSR_3

LVDDR18D

LVDS_DIGON

LVDS_BLON

LVDS_BLEN

TXCLK_UP

TXCLK_UN

TXCLK_LP

TXCLK_LN

COMP

DACSCL

DACSDA

STRP_DATA

BMREQ-16

B4

A4

B5

C6

B6

A6

B7

A7

E5

F5

D5

C5

E6

D6

E7

E8

J8

J7

H8

H7

G9

G8

G7

C7

E2

G3

F2

F8

F7

F6

G6

D9

C

F9

Y

E9

B2

C2

D1

VGA_HSYNC

VGA_VSYNC

TXL0- 14

TXL0+ 14

TXL1- 14

TXL1+ 14

TXL2- 14

TXL2+ 14

STRP_DATA

STRP_DATA:Debug strap

DEFAULT:1

0: MEMORY CHANNEL STRAPING

1: E2PROM STRAPING

R670 4.7K_0402

CI850

For EMI

10PF_0402_NC

R673 4.7K_0402

CI851

For EMI

10PF_0402_NC

4.7k can't down to 0V, so

change to 1k. 05'12'19

Able

RC410_LPVDD

RC410_LVDDR18A

C774

100nF_0402

LVDS_VDDEN 14

ELON 14

TXL_CLK+ 14

TXL_CLK- 14

SVIDEO_C 14

SVIDEO_Y 14

TV_CVBS 14

R676 4.7K_0402_NC

R667 1K_0402

2

C771

100nF_0402

C775

100nF_0402

SHORT

JP8

1 2

DAC_SCL is totem-pole output

R663 0R_0402

R664 0R_0402

R680 4.7K_0402

R681 4.7K_0402_NC

+3VRUN

+3VRUN

4.7K_0402

R672

4.7K_0402

2

R668

+3VRUN

VTT

R669

4.7K_0402

B

Q108

MMBT3904

VTT

R671

4.7K_0402

B

Q109

MMBT3904

EC

EC

1

+1.8VRUN

L38

200Ohm500mA_0.3Ohm

C772

1UF_0402

SHORT

JP7

1 2

L39

200Ohm500mA_0.3Ohm

C776

1UF_0402

C777

1UF_0402

DAC_SCL: CPU VCC

DEFAULT:0

0: MOBILE CPU

1: DESKTOP CPU

SCL_STRAP

VGA_CLK 14

VGA_DATA 14

+3VRUN

BSEL1 3,13

BSEL0 3,13VGA_VSYNC14

BMREQ#&HSYNC&VSYNC: FSB CLK SPEED

000: 100 MHZ

001: 133 MHZ (CK410)

010: --- MHZ

011: 166 MHZ (CK410)

100: 100 MHZ

101: 100 MHZ (CK410)

110: --- MHZ

111: --- MHZ

Note1: For A 11 , 100M and 133M need to strap at 101or 001 .

Note2: A12 changed 101 to be 100MHZ

instead of 133MHZ in A11 ASIC.

Title

RC410ME(VIDEO)&PCI-E

Size Document Number Rev

Custom

Date: Sheet

Q127

DS

N-2N7002_SOT23

SB_PWRGD1-

G

For latch MOBILE

CPU,05'12'19 Able

SB_PWRGD1- 6

MICRO-STAR INT'L CO.,LTD.

MS-1412

841Wednesday, November 29, 2006

1

1.1

of

Page 9

5

U205F

W5

VSSA#U5

W6

VSSA#U6

AB5

VSSA#Y5

AB6

VSSA#Y6

V8

VSSA#P8

V7

D D

C C

B B

A A

VSSA#P7

AA8

VSSA#U8

AA7

VSSA#U7

AD7

VSSA#Y7

AD8

VSSA#Y8

R8

VSSA#L8

N8

VSSA#K7

R7

VSSA#AD7

N7

VSSA#A2

AF7

VSSA#AF5

AE8

VSSA#AC6

AG5

VSSA#AC5

T6

VSSA#P6

T5

VSSA#P5

N6

VSSA#L6

N5

VSSA#L5

AH5

VSSA#H6

K5

VSSA#H5

AH3

VSSA#P4

AH8

VSSA#AE3

AH7

VSSA#AD3

AH6

VSSA#AC3

AD3

VSSA#AA3

AC3

VSSA#Y3

AA3

VSSA#V3

Y3

VSSA#U3

V3

VSSA#R3

U3

VSSA#P3

R3

VSSA#M3

P3

VSSA#L3

M3

VSSA#J3

L3

VSSA#H3

AF5

VSSA#F3

AF3

VSSA#N3

AF9

VSSA#AG3

AH9

VSSA#AE9

AH10

VSSA#AH7

AC20

VSS#A15

J23

VSS#A24

A29

VSS#A29

W30

VSS#AA23

W23

VSS#AA24

AA28

VSS#AA30

AJ30

VSS#AB27

AC12

VSS#AC12

AC15

VSS#AC16

K8

VSS#AC8

AD12

VSS#AD12

AD15

VSS#AD16

AD18

VSS#AD19

AC17

VSS#AD23

AE30

VSS#AD30

AD14

VSS#AD8

AC11

VSS#AD9

AF12

VSS#AE12

AF27

VSS#AE27

AC18

VSS#AC19

AG14

VSS#AG12

F4

VSS#AF7

AG18

VSS#AG18

AG21

VSS#AG21

AK25

VSS#AG9

V27

VSS#AH28

AJ1

VSS#AJ1

AD20

VSS#AK10

AK12

VSS#AK13

AK15

VSS#AK16

AK18

VSS#AK19

AK2

VSS#AK2

AH11

VSS#AH11

J3

VSS#AJ11

AC27 AK29

VSS#AK25 VSS#AK29

RC410MB_2

PART 6 OF 6

GND

5

VSS#AD11

VSS#AH26

VSS#AH25

VSS#AG25

VSS#AK22

VSS#M15

VSS#G14

VSS#G18

VSS#G27

VSS#G3

VSS#H13

VSS#H14

VSS#H18

VSS#H23

VSS#H4

VSS#J23

VSS#J24

VSS#J30

VSS#K27

VSS#V30

VSS#U19

VSS#M16

VSS#M30

VSS#N15

VSS#N16

VSS#N23

VSS#N27

VSS#G5

VSS#P15

VSS#P16

VSS#P23

VSS#P24

VSS#R12

VSS#R13

VSS#R14

VSS#R15

VSS#R16

VSS#R17

VSS#R18

VSS#R19

VSS#R23

VSS#R24

VSS#R30

VSS#T12

VSS#T13

VSS#T14

VSS#T15

VSS#T16

VSS#T17

VSS#T18

VSS#T19

VSS#T27

VSS#U15

VSS#U16

VSS#V15

VSS#V16

VSS#W16

VSS#W27

VSS#V12

VSS#W13

VSS#V14

VSS#W15

VSS#Y23

VSS#Y24

VSS#C19

VSS#C17

VSS#F30

VSS#F25

VSS#D27

VSS#D25

VSS#D23

VSS#D20

VSS#D17

VSS#C3

VSS#C28

VSS#B30

VSS#B1

M14

AC14

AG16

A22

A2

D27

AG26

H18

A16

A9

AD17

J24

R27

D24

T30

U19

M16

AD11

H15

N15

N19

D3

A25

F3

R15

P16

G10

M24

M12

R13

P12

P14

U13

R17

V18

R19

R23

R24

J30

T12

N13

T14

P18

T16

U17

T18

W19

J27

U15

N17

M18

V16

W17

M26

V12

W13

V14

W15

U23

U24

A13

V28

AG24

AA24

AA23

F30

K23

D20

A19

D17

D14

F27

D4

M23

B30

B1

AK22

+1.2VRUN

+3VRUN

+1.8VRUN

+1.8VRUN

4

C787

10UF/10V_0805

100nF_0402

C788

10UF/10V_0805

C791

100nF_0402

C789

10UF/10V_0805

C792

100nF_0402

Power sequence requirement

DB15 RB551V-30_NC

A C

L42 28L900m_100_0805

C811

C810

1UF_0402

1UF_0402

L43 28L900m_100_0805

C814

10UF/10V_0805

4

C815

1UF_0402

C816

1UF_0402

C793

C812

1UF_0402

C790

10UF/10V_0805

C794

100nF_0402

C817

1UF_0402

VDD18

C813

1UF_0402

VDDA18

C818

1UF_0402

3

U205E

U16

M13

M15

M17

R16

V15

N12

T15

N14

N16

N18

M19

R12

P13

P15

P17

P19

U12

T13

U14

T17

U18

T19

V13

R14

V17

R18

V19

W12

W14

W16

W18

AB22

AB9

J22

AB8

AE11

AC9

AD10

AC10

AG11

AF11

AC7

AB7

J9

Y8

U8

Y7

U7

H5

H4

P8

P7

L7

L8

J6

VDD_CORE#M12

VDD_CORE#M13

VDD_CORE#M14

VDD_CORE#M17

VDD_CORE#M18

VDD_CORE#M19

VDD_CORE#N12

VDD_CORE#N13

VDD_CORE#N14

VDD_CORE#N17

VDD_CORE#N18

VDD_CORE#N19

VDD_CORE#P12

VDD_CORE#P13

VDD_CORE#P14

VDD_CORE#P17

VDD_CORE#P19

VDD_CORE#U12

VDD_CORE#U13

VDD_CORE#U14

VDD_CORE#U17

VDD_CORE#U18

VDD_CORE#U19

VDD_CORE#V13

VDD_CORE#V14

VDD_CORE#V17

VDD_CORE#V18

VDD_CORE#V19

VDD_CORE#W12

VDD_CORE#W14

VDD_CORE#W17

VDD_CORE#W18

VDD_18

VDD_18#AF26

VDD_18#AF9

VDD_18#J26

VDDA_18#U8

VDDA_18#AD8

VDDA_18#W6

VDDA_18#AA8

VDDA_18#AA7

VDDA_18#AE7

VDDA_18#AD7

VDDA_18#AC8

VDDA_18#AC7

VDDA_18#AG6

VDDA_18#AF6

VDDA_12#K6

VDDA_12#K4

VDDA_12#F6

VDDA_12#F5

VDDA_12#B3

VDDA_12#A3

VDDA_12#B4

VDDA_12#M8

VDDA_12#W5

RC410MB_2

PART 5 OF 6

CORE POWER

POWER

PCIE

IF

PCIE POWER

VDD_MEM#AB30

VDD_MEM#AJ21

VDD_MEM#AK21

VDD_MEM#AC13

VDD_MEM#AC14

VDD_MEM#AC15

VDD_MEM#AC18

VDD_MEM#AC21

VDD_MEM#AD10

VDD_MEM#AD13

VDD_MEM#AD15

VDD_MEM#AD18

VDD_MEM#AD21

VDD_MEM#AE15

VDD_MEM#AE18

VDD_MEM#AE21

VDD_MEM#AG27

VDD_MEM#AJ30

VDD_MEM#AK18

VDD_MEM#AK24

VDD_MEM#AK9

VDD_MEM#W23

VDD_CPU#H17

VDD_CPU#H19

VDD_CPU#K23

VDD_CPU#L23

VDD_CPU#L24

VDD_CPU#M23

VDD_CPU#M24

VDD_CPU#T23

VDD_CPU#U23

VDD_CPU#U24

VDD_CPU#V23

VDD_CPU#V24

VDD_CPU#G16

VDD_CPU#G15

VDD_CPU#F22

VDD_CPU#F19

VDD_CPU#F16

MEM

POWER

VDD_CPU#F15

VDD_CPU#E15

VDD_CPU#A16

VDD_CPU#H16

VDD_CPU#H15

VDD_CPU#G22

VDD_CPU#G21

VDD_CPU#G19

VDDA_12#N8

VDDA_12#C3

VDDA_12#R7

VDDA_12#R8

VDDA_12#U7

CPU IF

POWER

VDDA_12#B2

VDDA_12#K8

VDDA_12#L7

VDDA_12#L8

2

+1.8VDIMM

Y24

AC21

AD21

AC13

AD23

AC16

AD19

AD22

V23

AD13

AD16

AC19

AB24

AK24

T24

AK28

AB23

Y23

AK21

T23

V24

AC22

H11

H13

G20

L23

L24

P23

N23

H17

G17

H14

F17

G14

A10

H16

H23

H12

F12

G12

F11

P24

H19

G11

H24

G16

G13

AC8

K6

M8

T8

T7

M7

W8

W7

AD9

10UF/10V_0805

10UF/10V_0805

+VDDA12

C782

10UF/10V_0805

C795

100nF_0402

100nF_0402

VTT

C800

10UF/10V_0805

C805

100nF_0402

100nF_0402

板子出來後換小電流的來做!!實驗

05'10'20 ABLE

L63 150ohm2.5A_0805

C819

10UF/10V_0805

C823

10UF/10V_0805

C783

C796

C801

C806

C820

1UF_0402

C824

1UF_0402

1

C784

100nF_0402

100nF_0402

C802

100nF_0402

C807

100nF_0402

+1.2VRUN

C821

1UF_0402

C825

1UF_0402

C797

C785

100nF_0402

C798

100nF_0402

C803

100nF_0402

C808

100nF_0402

C822

1UF_0402

C826

1UF_0402

C786

100nF_0402

C799

100nF_0402

C804

100nF_0402

C809

100nF_0402

05'10'21 ABLE

MICRO-STAR INT'L CO.,LTD.

Title

RC410ME(POWER)

Size Document Number Rev

Custom

3

2

Date: Sheet

MS-1412

of

941Wednesday, November 29, 2006

1

1.1

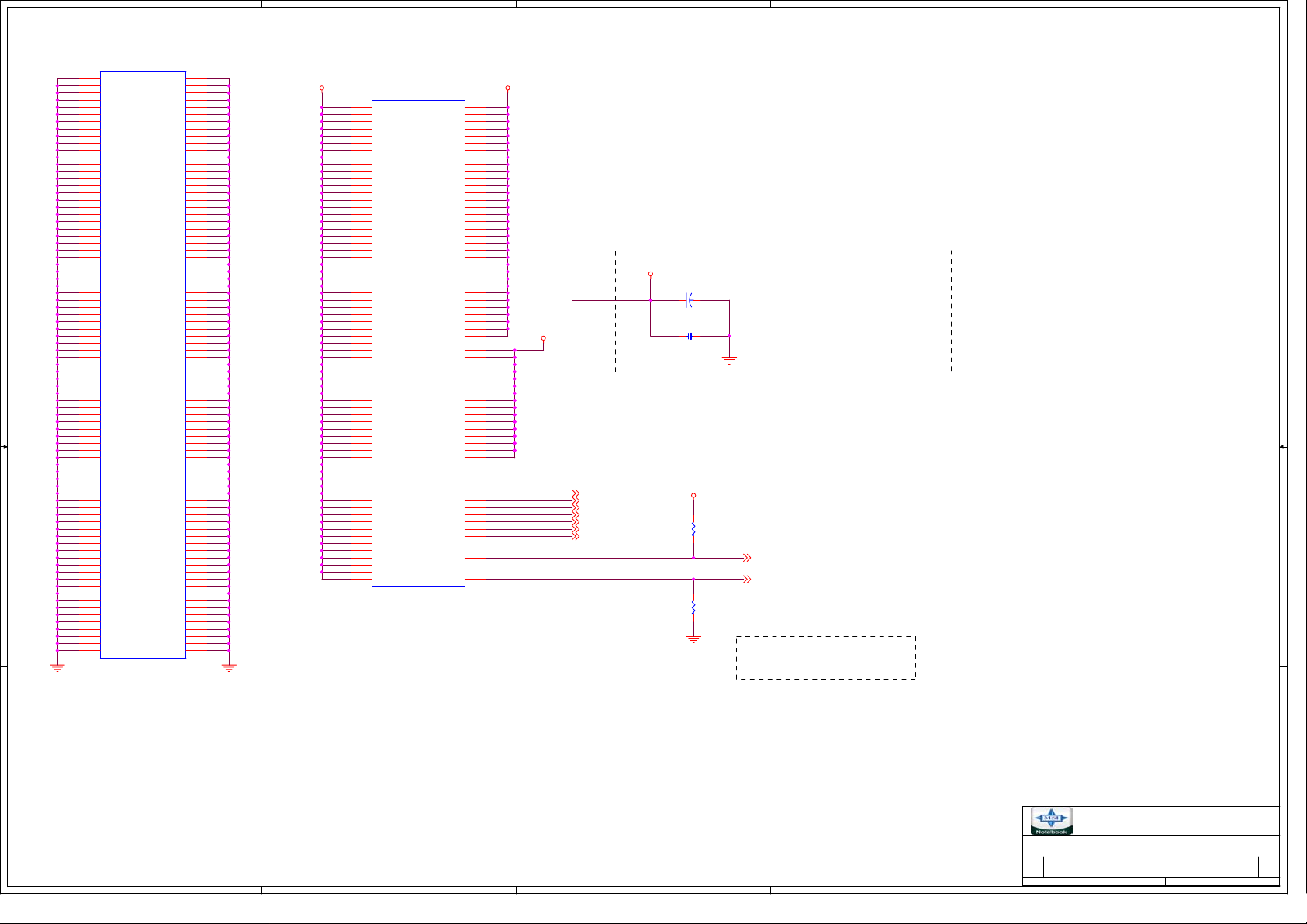

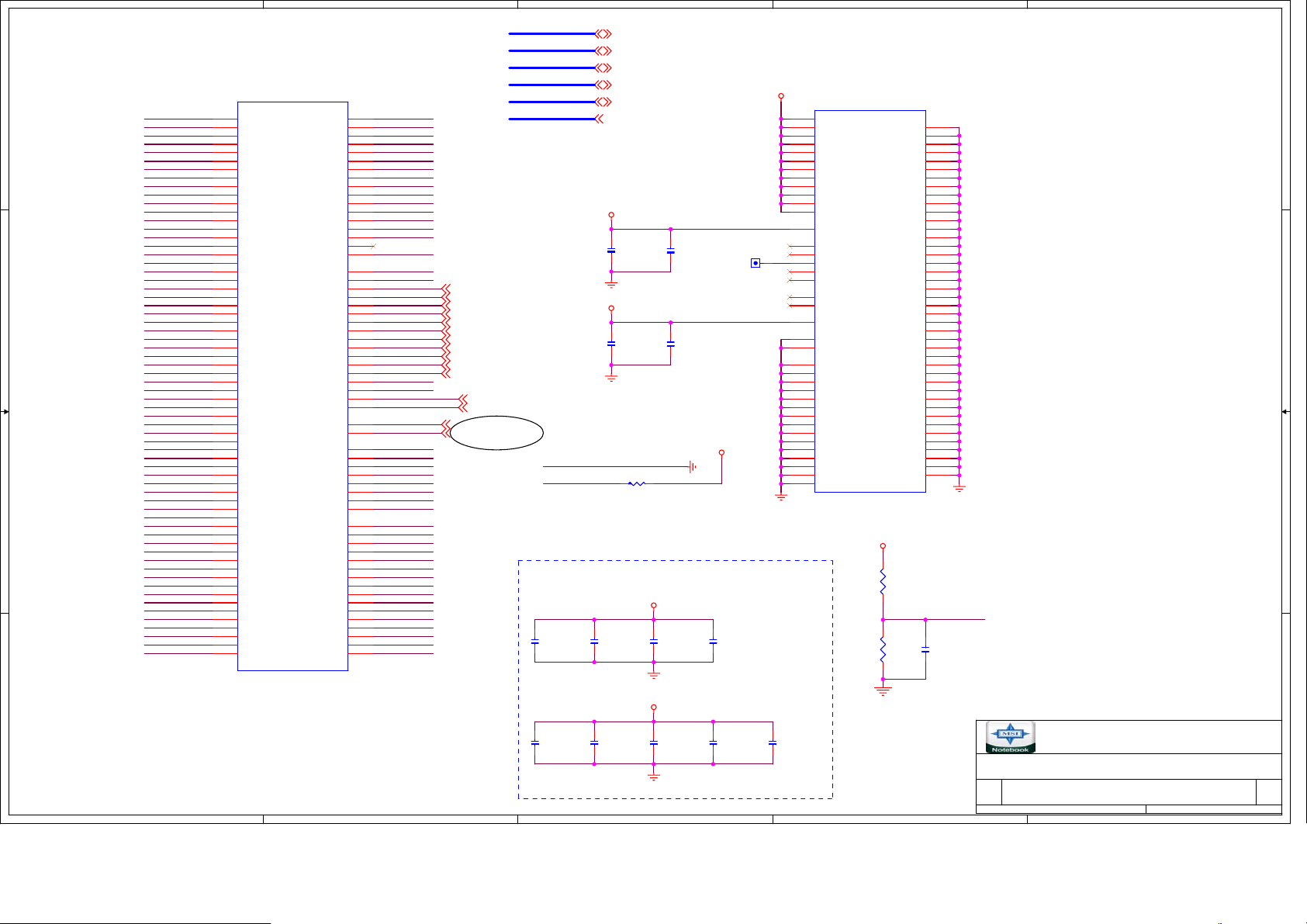

Page 10

5

D D

C C

B B

A A

5

SA_MD0

SA_MD1

SA_MD2

SA_MD3

SA_MD4

SA_MD5

SA_MD6

SA_MD7

SA_MD8

SA_MD9

SA_MD10

SA_MD11

SA_MD12

SA_MD13

SA_MD14

SA_MD15

SA_MD16

SA_MD17

SA_MD18

SA_MD19

SA_MD20

SA_MD21

SA_MD22

SA_MD23

SA_MD24

SA_MD25

SA_MD26

SA_MD27

SA_MD28

SA_MD29

SA_MD30

SA_MD31

SA_MD32

SA_MD33

SA_MD34

SA_MD35

SA_MD36

SA_MD37

SA_MD38

SA_MD39

SA_MD40

SA_MD41

SA_MD42

SA_MD43

SA_MD44

SA_MD45

SA_MD46

SA_MD47

SA_MD48

SA_MD49

SA_MD50

SA_MD51

SA_MD52

SA_MD53

SA_MD54

SA_MD55

SA_MD56

SA_MD57

SA_MD58

SA_MD59

SA_MD60

SA_MD61

SA_MD62

SA_MD63

DIMMB5A

5

DQ0

7

DQ1

17

DQ2

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

DDR2_SO-DIMM_STD1

A10/AP

A11

A12

A13

A14

A15

A16_BA2

BA0

BA1

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

85

107

106

110

115

30

32

164

166

79

80

113

108

109

198

200

197

195

114

119

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

4

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_BS-2

SA_BS-0

SA_BS-1

SM_CS-0

SM_CS-1

CLK_SDRAM0

CLK_SDRAM-0

CLK_SDRAM1

CLK_SDRAM-1

CKE0

CKE1

SA_CASSA_RASSA_WESA_SA0

SA_SA1

RUN_SMBCLK

RUN_SMBDATA

SM_ODT0

SM_ODT2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS-0

SA_DQS-1

SA_DQS-2

SA_DQS-3

SA_DQS-4

SA_DQS-5

SA_DQS-6

SA_DQS-7

4

SA_MD[0..63]

SA_DM[0..7]

SA_DQS[0..7]

SA_DQS-[0..7]

SA_MA[0..14]

SA_BS-[0..2]

SM_CS-0 7,12

SM_CS-1 7,12

CLK_SDRAM0 7

CLK_SDRAM-0 7

CLK_SDRAM1 7

CLK_SDRAM-1 7

CKE0 7,12

CKE1 7,12

SA_CAS- 7,11,12

SA_RAS- 7,11,12

SA_WE- 7,11,12

RUN_SMBCLK 11,13,15,25,26

RUN_SMBDATA 11,13,15,25,26

SM_ODT0 7,12

SM_ODT2 7,12

CB228

0.1UF_0402

CB229

2.2UF/6.3V

3

SA_MD[0..63] 7,11

SA_DM[0..7] 7,11

SA_DQS[0..7] 7,11

SA_SA0

SA_SA1

SA_DQS-[0..7] 7,11

SA_MA[0..14] 7,11,12

SA_BS-[0..2] 7,11,12

+3VRUN

C99

2.2UF/6.3V

SMDDR_VREF

SMDDR_VREF

CT299

2.2UF/6.3V

RB136 4.7K_0402

CT302

0.1UF_0402

CT339

0.1UF_0402

+3VRUN

+1.8VDIMM

TP46

DIMM0 address : 01

05'12'19 Able

Layout note: Place capacitors between and

near DDR connector if possible.

+1.8VDIMM

CT280

0.1UF_0402

+1.8VDIMM

CT360

2.2UF/6.3V

3

CB230

0.1UF_0402

CT263

2.2UF/6.3V

CB173

0.1UF_0402

CT281

2.2UF/6.3V

CB227

2.2UF/6.3V

DIMMB5B

112

VDD1

111

VDD2

117

VDD3

96

VDD4

95

VDD5

118

VDD6

81

VDD7

82

VDD8

87

VDD9

103

VDD10

88

VDD11

104

VDD12

199

VDDSPD

83

NC1

120

NC2

50

NC3

69

NC4

163

NCTEST

MEC1

NC5

MEC2

NC6

1

VREF

201

GND0

202

GND1

47

VSS1

133

VSS2

183

VSS3

77

VSS4

12

VSS5

48

VSS6

184

VSS7

78

VSS8

71

VSS9

72

VSS10

121

VSS11

122

VSS12

196

VSS13

193

VSS14

8

VSS15

DDR2_SO-DIMM_STD1

+1.8VDIMM

10K_1%

RT116

10K_1%

2

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

RT110

2

1

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

SMDDR_VREF

C107

0.1UF_0402

as close as

SO-DIMM

MICRO-STAR INT'L CO.,LTD.

Title

DDR2-SODIMM-0

Size Document Number Rev

B

Date: Sheet

MS-1412

1

1.1

10 41Wednesday, November 29, 2006

of

Page 11

5

4

3

2

1

SA_MD[0..63]

DIMMB6A

SA_MD0

SA_MD1

SA_MD2

D D

C C

B B

SA_MD3

SA_MD4

SA_MD5

SA_MD6

SA_MD7

SA_MD8

SA_MD9

SA_MD10

SA_MD11

SA_MD12

SA_MD13

SA_MD14

SA_MD15

SA_MD16

SA_MD17

SA_MD18

SA_MD19

SA_MD20

SA_MD21

SA_MD22

SA_MD23

SA_MD24

SA_MD25

SA_MD26

SA_MD27

SA_MD28

SA_MD29

SA_MD30

SA_MD31

SA_MD32

SA_MD33

SA_MD34

SA_MD35

SA_MD36

SA_MD37

SA_MD38

SA_MD39

SA_MD40

SA_MD41

SA_MD42

SA_MD43

SA_MD44

SA_MD45

SA_MD46

SA_MD47

SA_MD48

SA_MD49

SA_MD50

SA_MD51

SA_MD52

SA_MD53

SA_MD54

SA_MD55

SA_MD56

SA_MD57

SA_MD58

SA_MD59

SA_MD60

SA_MD61

SA_MD62

SA_MD63

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

DDR2-Reverse

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

A10/AP

A11

A12

A13

A14

A15

A16_BA2

BA0

BA1

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

85

107

106

110

115

30

32

164

166

79

80

113

108

109

198

200

197

195

114

119

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_BS-2

SA_BS-0

SA_BS-1

SM_CS-2

SM_CS-3

CLK_SDRAM3

CLK_SDRAM-3

CLK_SDRAM2

CLK_SDRAM-2

CKE2

CKE3

SA_CASSA_RASSA_WESB_SA0

SB_SA1

RUN_SMBCLK

RUN_SMBDATA

SM_ODT1

SM_ODT3

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS-0

SA_DQS-1

SA_DQS-2

SA_DQS-3

SA_DQS-4

SA_DQS-5

SA_DQS-6

SA_DQS-7

SM_CS-2 7,12

SM_CS-3 7,12

CLK_SDRAM3 7

CLK_SDRAM-3 7

CLK_SDRAM2 7

CLK_SDRAM-2 7

CKE2 7,12

CKE3 7,12

SA_CAS- 7,10,12

SA_RAS- 7,10,12

SA_WE- 7,10,12

RUN_SMBCLK 10,13,15,25,26

RUN_SMBDATA 10,13,15,25,26

SM_ODT1 7,12

SM_ODT3 7,12

SA_DM[0..7]

SA_DQS[0..7]

SA_DQS-[0..7]

SA_MA[0..14]

SA_BS-[0..2]

SB_SA1

SB_SA0

DIMM1 address set 11

05'12'19 Able

Layout note: Place capacitors between and

near DDR connector if possible.

CT279

0.1UF_0402

SA_MD[0..63] 7,10

SA_DM[0..7] 7,10

SA_DQS[0..7] 7,10

SA_DQS-[0..7] 7,10

SA_MA[0..14] 7,10,12

SA_BS-[0..2] 7,10,12

+3VRUN

C113

2.2UF/6.3V

SMDDR_VREF

CT354

2.2UF/6.3V

RB166 4.7K_0402

RB167 4.7K_0402

+1.8VDIMM

CT359

0.1UF_0402

CB174

0.1UF_0402

CB259

0.1UF_0402

CT346

0.1UF_0402

+3VRUN

CT253

0.1UF_0402

TP47

+1.8VDIMM

112

111

117

118

103

104

199

120

163

MEC1

MEC2

203

204

133

183

184

121

122

196

193

DIMMB6B

VDD1

VDD2

VDD3

96

VDD4

95

VDD5

VDD6

81

VDD7

82

VDD8

87

VDD9

VDD10

88

VDD11

VDD12

VDDSPD

83

NC1

NC2

50

NC3

69

NC4

NCTEST

NC5

NC6

1

VREF

GND0

GND1

47

VSS1

VSS2

VSS3

77

VSS4

12

VSS5

48

VSS6

VSS7

78

VSS8

71

VSS9

72

VSS10

VSS11

VSS12

VSS13

VSS14

8

VSS15

DDR2-Reverse

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

+1.8VDIMM

A A

CT282

2.2UF/6.3V

5

4

CB172

2.2UF/6.3V

CT347

2.2UF/6.3V

3

CT361

2.2UF/6.3V

CB171

2.2UF/6.3V

Title

MICRO-STAR INT'L CO.,LTD.

DDR2-SODIMM-1

Size Document Number Rev

B

2

Date: Sheet

MS-1412

11 41Wednesday, November 29, 2006

1

of

1.1

Page 12

5

4

3

2

1

SA_MA[0..14]

SA_BS-[0..2]

D D

SA_MA5

SA_MA3

SA_MA1

SA_MA10

SA_MA6

SA_MA4

SA_MA2

SA_MA0

SA_BS-2

SA_MA12

SA_MA9

SA_MA8

C C

SMDDR_VTERM

CT368

0.1UF_0402

CT372

0.1UF_0402

CT373

0.1UF_0402

SMDDR_VTERM

RNT9

1

3

5

7

8P4R-56R

RNT12

7

5

3

1

8P4R-56R

RNT16

1

3

5

7

8P4R-56R

SA_MA[0..14] 7,10,11

SA_BS-[0..2] 7,10,11

SMDDR_VTERM

2

4

6

8

8

6

4

2

2

4

6

8

CT380

0.1UF_0402

CT296

0.1UF_0402

SMDDR_VTERM

SA_BS-1

CKE27,11

CKE37,11

CT332

0.1UF_0402

SM_CS-0

SM_ODT0

SA_MA13

SA_BS-0

SA_CASSM_CS-1

SM_ODT1

SA_MA14

CKE2

CKE3

SA_RASSA_WE-

SM_CS-07,10 SM_CS-2 7,11

SM_ODT07,10

SA_CAS-7,10,11

SM_CS-17,10

SM_ODT17,11

SA_RAS-7,10,11

SA_WE-7,10,11

CT292

0.1UF_0402

RNT15

7

5

3

1

8P4R-56R

RNT10

1

3

5

7

8P4R-56R

RNT13

2

4

6

8

8P4R-56R

RT138 56_0402

RT117 56_0402

CT333

0.1UF_0402

8

6

4

2

2

4

6

8

1

3

5

7

SMDDR_VTERM

CT331

0.1UF_0402

SMDDR_VTERM

RNT5

1

3

5

7

8P4R-56R

RNT11

1

3

5

7

8P4R-56R

RNT8

1

3

5

7

8P4R-56R

CT349

0.1UF_0402

2

4

6

8

2

4

6

8

2

4

6

8

CT293

0.1UF_0402

SM_CS-2

SM_ODT2

CKE1

CKE0

SA_MA11

SA_MA7

SM_ODT3

SM_CS-3

CT294

0.1UF_0402

SM_ODT2 7,10

CKE1 7,10

CKE0 7,10

SM_ODT3 7,11

SM_CS-3 7,11

CT291

0.1UF_0402

B B

CT379

0.1UF_0402

CT369

0.1UF_0402

CT353

0.1UF_0402

CT370

0.1UF_0402

CT352

0.1UF_0402

CT351

0.1UF_0402

CT350

0.1UF_0402

CT348

0.1UF_0402

CT371

0.1UF_0402

CT334

0.1UF_0402

CT335

0.1UF_0402

CT336

0.1UF_0402

CT329

0.1UF_0402

Layout note: Place one cap close to every 2 pullup resistors terminated to +0.9V.

SMDDR_VTERM

12

CT374

10UF/10V_0805

A A

CT290

10UF/10V_0805

CT395

100UF/2V_7343_NC

MICRO-STAR INT'L CO.,LTD.

Title

DDR2 Terminator

Size Document Number Rev

B

5

4

3

2

Date: Sheet

MS-1412

12 41Wednesday, November 29, 2006

1

of

1.1

Page 13

5

05'10'20 ABLE

+3VRUN

D D

LT30 80L3_100_0805

CT381

22UF/10V_1206

C C

B B

CB195

0.1UF_0402

0.1UF_0402

200Ohm500mA_0.3Ohm

CLKGVDD

CB218

0.1UF_0402

CT357 33PF_0402

YT8