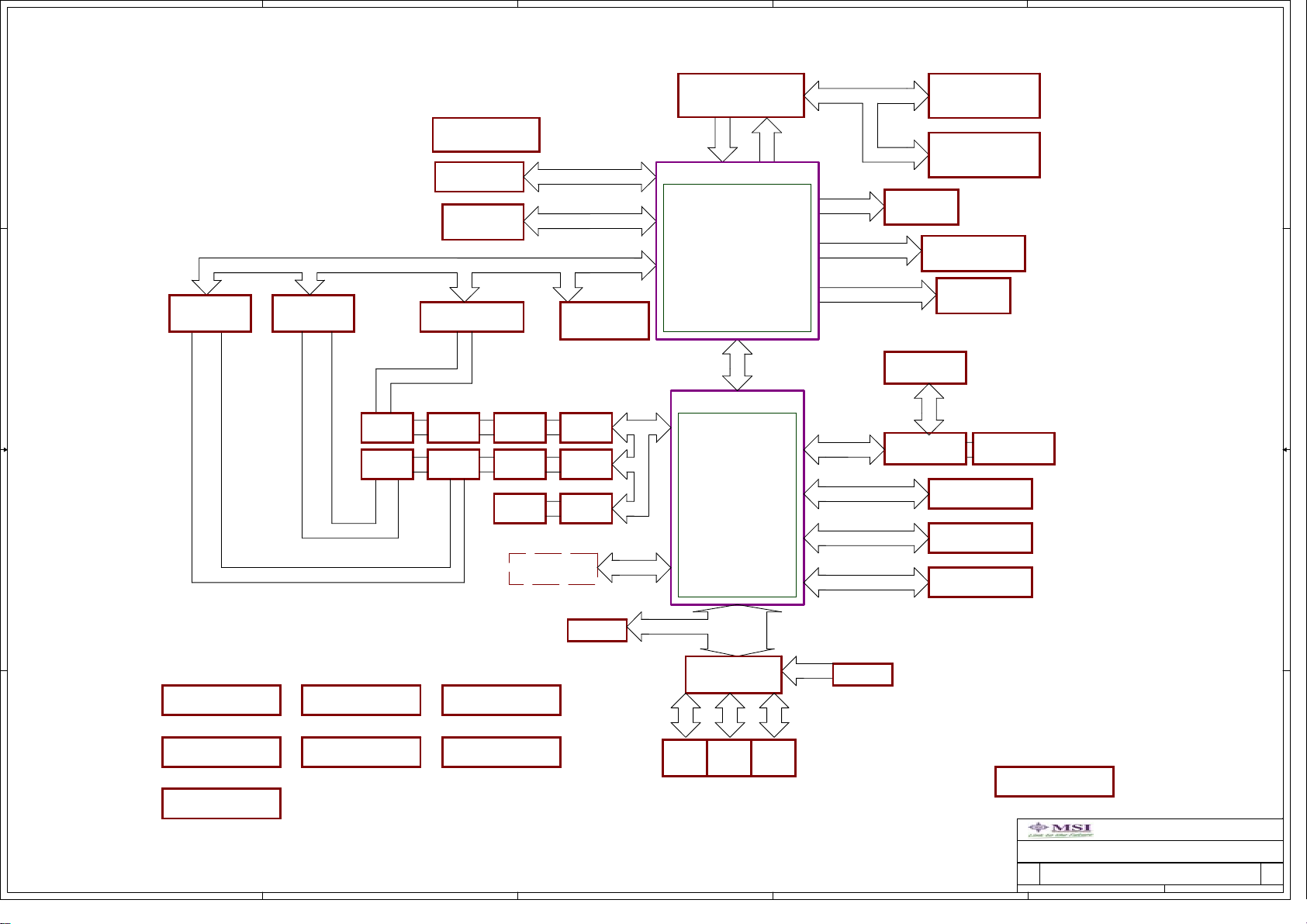

Page 1

5

4

3

2

1

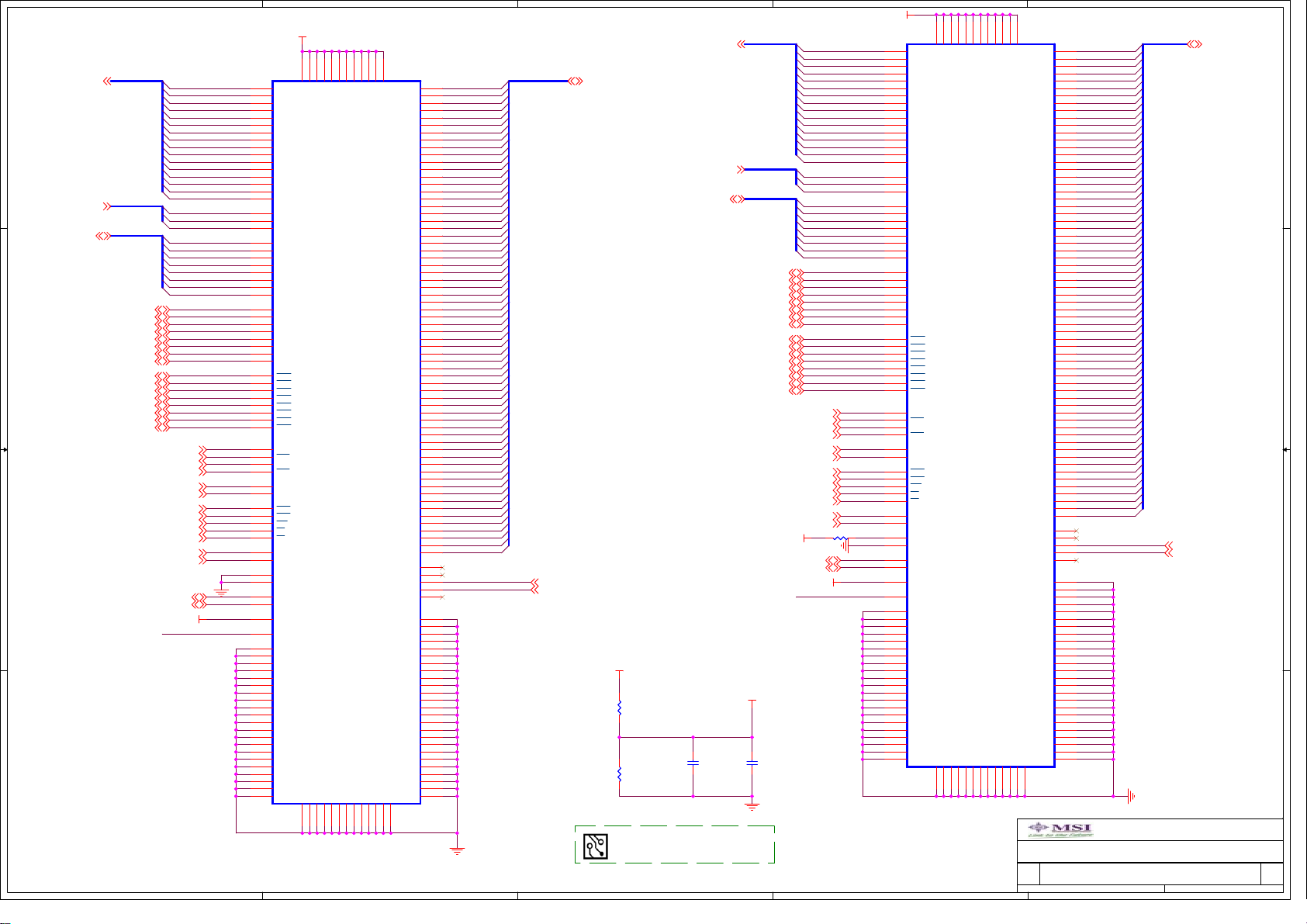

AMD S1 PROCESSOR

D D

1.0

EXTERNAL CLOCK GENERATOR

ICS951462

LVDS CON

16

32

LVDS

638-Pin uFCPGA 638

HyperTransport

LINK0

ATI NB - RS690T

OUT

5,6,7,8

IN

DDR II 400/533/667

16x16

CRT

BOOTSTRAPS

ROM(DNI)

13

I2C I/F

X1 PCIE INTERFACE

HyperTransport LINK0 CPU I/F

INTEGRATED GRAPHICS

LVDS/TVOUT/TMDS

1 X16 PCIE VIDEO/SDVO I/F

DDRII 400MHz

UNBUFFERED

DDR2 NEAR

SODIMM

200-PIN DDR2 SODIMM

200-PIN DDR2 SODIMM

VGA CON

SIDE PORT

MEMORY

UNBUFFERED

DDR2 FAR

SODIMM

32

9,10

9,10

15

1 X4 PCIE I/F WITH SB

MINIPCIE SLOT

C C

30

MINIPCIE SLOT

30

NEW CARD

23

RTL8111B

PCIE ETHERNET

X1

25

11,12,13,14,15

A-LINK

X4

4 X1 PCIE I/F

NewCard

USB#3

MiniPCI

USB#6

23

30

USBPORT

USB#2

USBPORT

USB#5

28

30

USBPORT

USB#1

USBPORT

USB#4

28

28

USBPORT

USB#0

USBPORT

USB#7

28

28

USB 2.0

ATI SB - SB600

USB 2.0 (10 PORTS)

SATA II (4 PORTS)

AZALIA HD AUDIO

AC97 2.3

ATA 66/100/133

USBPORT

USB#9

DNI

B B

USBPORT

BOOTSTRAPS

ROM (SB)

USB#8

21

28

I2C I/F

LPC I/F

ACPI 2.0

INT RTC

HW MONITOR

PCI/PCI BDGE

17, 18, 19, 20, 21

SPI I/F

EXTRA DISPLAY

HD AUDIO I/F

ATA 66/100/133 I/F

ATA 66/100/133 I/F

PCI

Array Mic

ALC888

AZALIA CODEC

HDMI

32

45

AMP & AUDIO

26

CONN

SATA CONNECTOR

IDE CONNECTOR

MR510

CARDREADER

27

29

29

22

24

TPM

LPC BUS

28

KBC ENE3910

BATTERY CHAGER

SYSTEM MAIN POWER

A A

SB600 & PCIE POWER

5

CPU CORE POWER

41

CPU&RS690T HT VLDT

POWER

37

35

CPU MEMORY POWER

36

RS690T CORE POWER

35

4

38

3

KBD

MOUSE

31

39

ISA I/FPS2

BIOS 4M

31

31

ISA I/F

BIOS 8M

31

CIR

DISCHARGE CIRCUIT

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

37

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MS-12221

MS-12221

MS-12221

1

1.0

1.0

145Thursday, February 01, 2007

145Thursday, February 01, 2007

145Thursday, February 01, 2007

1.0

of

of

of

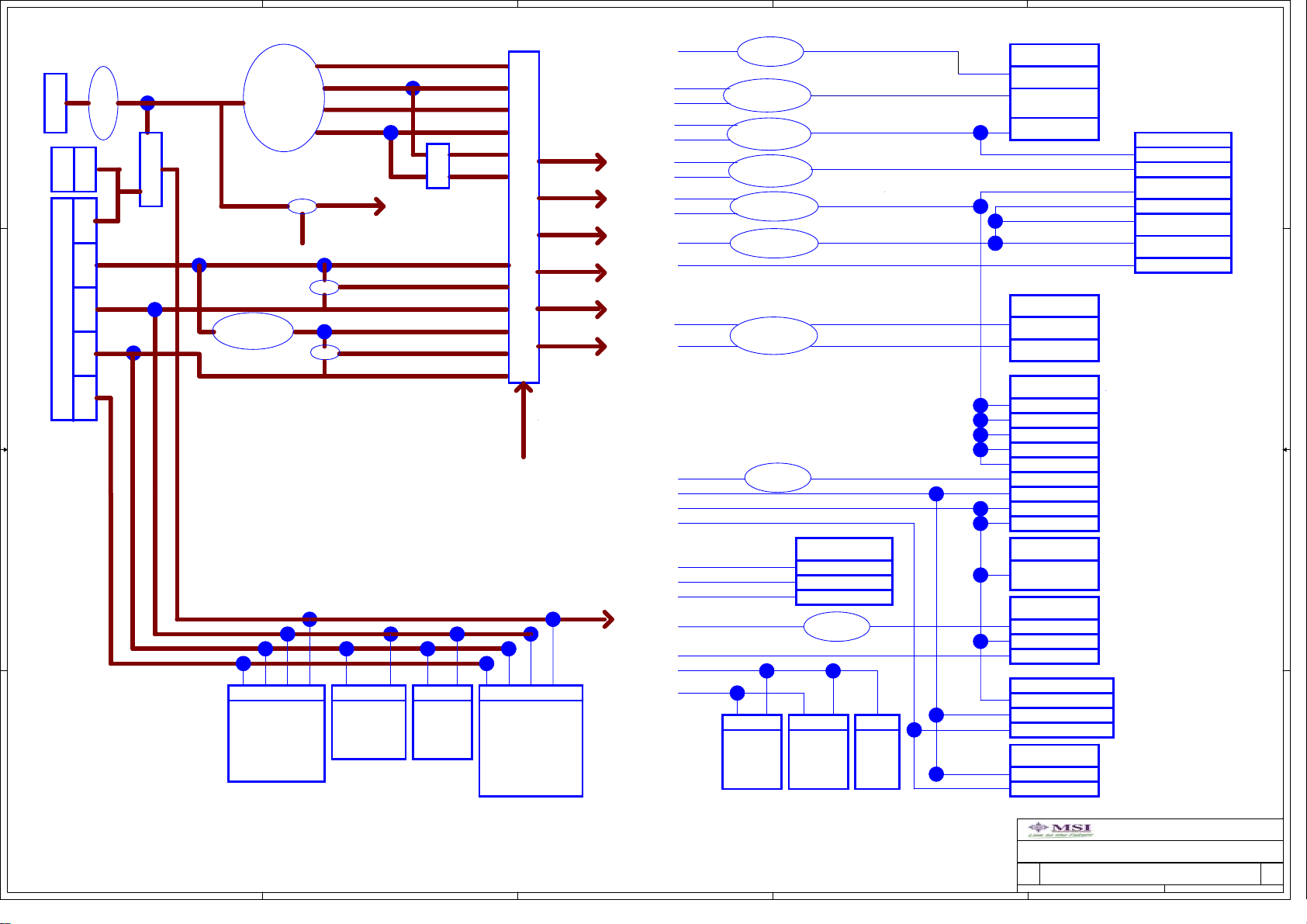

Page 2

5

4

3

2

1

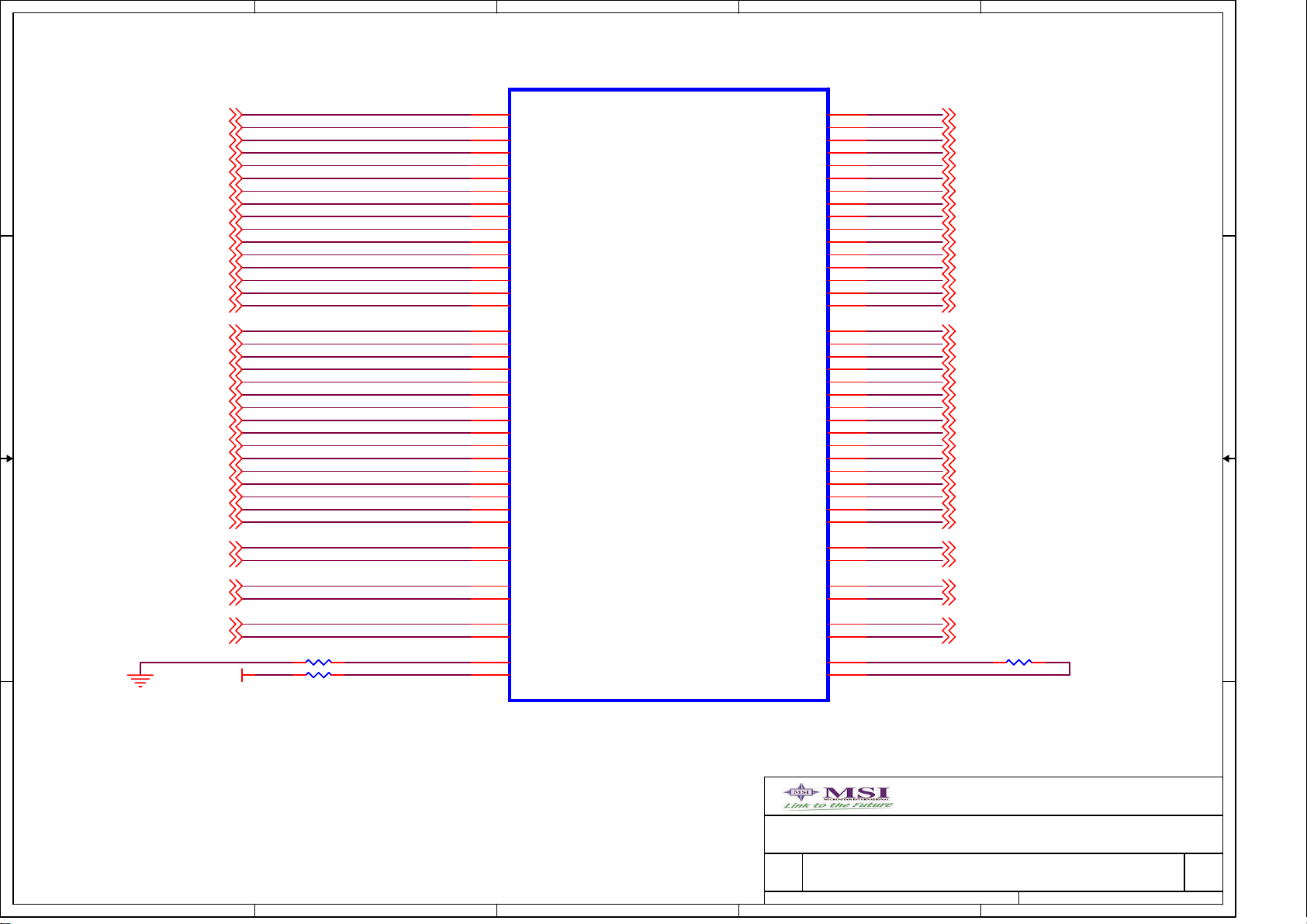

+3.3VALW_NTB

+5V

+VDC

D D

C C

BATTERY

BATTERY

CPU

PWR

12V

+/-5%

12V

+/-5%

5VSB

+/-5%

5V

+/-5%

ATX POWER SUPPLY

3.3V

+/-5%

CHARGER

SWITCH

MAIN PWR SW

REGULATOR

+3.3VALW LDO

REGULATOR

SW

+5VALW_NTB

+5VSUS_NTB

+VIN_MEM

+5VSUS

SW

SW

+5VALW_ATX

+5VDUAL_ATX

+5V_ATX

+3.3VALW_ATX

+3.3VDUAL_ATX

+3.3V_ATX

+3.3V_NTB

+5V_NTB

SWITCH

+3.3VALW

+3.3VDUAL

+3.3V

POWER SWITCH

+5VALW

+5VDUAL

+5V

+3.3VSUS_NTB

+VIN

+5V

+VIN

+5V

+VIN

+5V

+VIN

+5V

+5V

+3.3V

+VIN

+5VSUS

2.5V LDO

REGULATOR

SW REGULATOR

VLDT 1.2V SW

REGULATOR

NB CORE SW

REGULATOR

PCIE&SB SW

REGULATOR

1.8V SW

REGULATOR

1.8V VDD&VTT

SW REGULATOR

CPU_VDDA_RUN (S0, S1)

CPU_VDD_RUN (S0, S1)

VLDT_RUN (S0, S1)

VCC_NB (S0, S1)

VDDA_1V2(S0, S1)

+1.8V(S0, S1)

AVDD (S0, S1)

CPU_VDDIO_SUS (S0, S1, S3)

CPU_VTT_SUS (S0, S1, S3)

AMD CPU S1g1

VCCA 2.5V 500mA

VDDCORE

0.375-1.500V 35A

VLDT 1.2V 1A

DDR2 SODIMMX2

VDD MEM 6A

VTT_MEM 1A

NB RS690T/485T

HT VLDT 1.2V 1A

NB CORE 10A

PCI-E CORE

&PCI-E IO 5A

HTPLL (1.8V) 200mA

PLL & DAC-Q(1.8V)

200mA

TRANSFORMER

400mA

DAC 300mA

SB SB600

-12V

+/-5%

CONTROL SIGNAL:

MOBILE: BATTERY

DESKTOP: ATX

+3.3VALW

+3.3V

+3.3VALW

1.2V LDO

REGULATOR

+1.2VALW

+5V

X4 PCI-E 0.8A

ATA I/O 0.2A

VCC_SB (S0,

S1)

ATA PLL 0.01A

PCI-E PVDD 80mA

SB CORE 0.6A

1.2V S5 PW 0.22A

3.3V I/O 0.45A

3.3V S5 PW 0.01A

USB CORE I/O 0.2A

B B

+3.3V

+5V

+3.3VALW

+VIN

+5V

MINI PCI SLOT

3.3V(S0, S1)1.5A

5V (S0, S1) 0.1A

3.3V(S3, S5) 0.2A

1.5V SW

REGULATOR

+3.3V

+5V

+5VALW

USB X7 FR

USB X2 RL

VDD VDD

5VDual 5VDual

3.5A

3

1.0A

2XPS/2

5VDual

1.0A

2

5.0A

7.6A

0.5A

0.375A

0.1A

X1 PCIE per

3.3V

12V

3.3Vaux

PCI Slot (per slot)

5V

3.3V

12V

3.3Vaux

A A

5

-12V

3.0A

0.5A

0.1A

4

X16 PCIE

3.3V

12V

3.0A

5.5A

CNR CONNECTOR

5V

3.3V

12V

3.3Vaux

-12V

5VDual

1.0A

1.0A

0.5A

1.0A

0.1A

0.5A

GBIT ENTHENET

3.3V 0.5A

(S0, S1, S3, S4, S5)

PCI-E CARD

1.5V (S0, S1) 0.7A

3.3V (S3, S5) 0.3A

3.3V (S0, S1) 1.3A

SUPER I/O

+3.3VDUAL (S3) 0.01A

+3.3V (S0, S1) 0.01A

+5V (S0, S1) 0.1A

HD CODEC

3.3V CORE 0.3A

5V ANALOG 0.1A

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

POWER DELIVERY CHART

POWER DELIVERY CHART

POWER DELIVERY CHART

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-12221

MS-12221

MS-12221

1

245Thursday, February 01, 2007

245Thursday, February 01, 2007

245Thursday, February 01, 2007

of

of

of

1.0

1.0

1.0

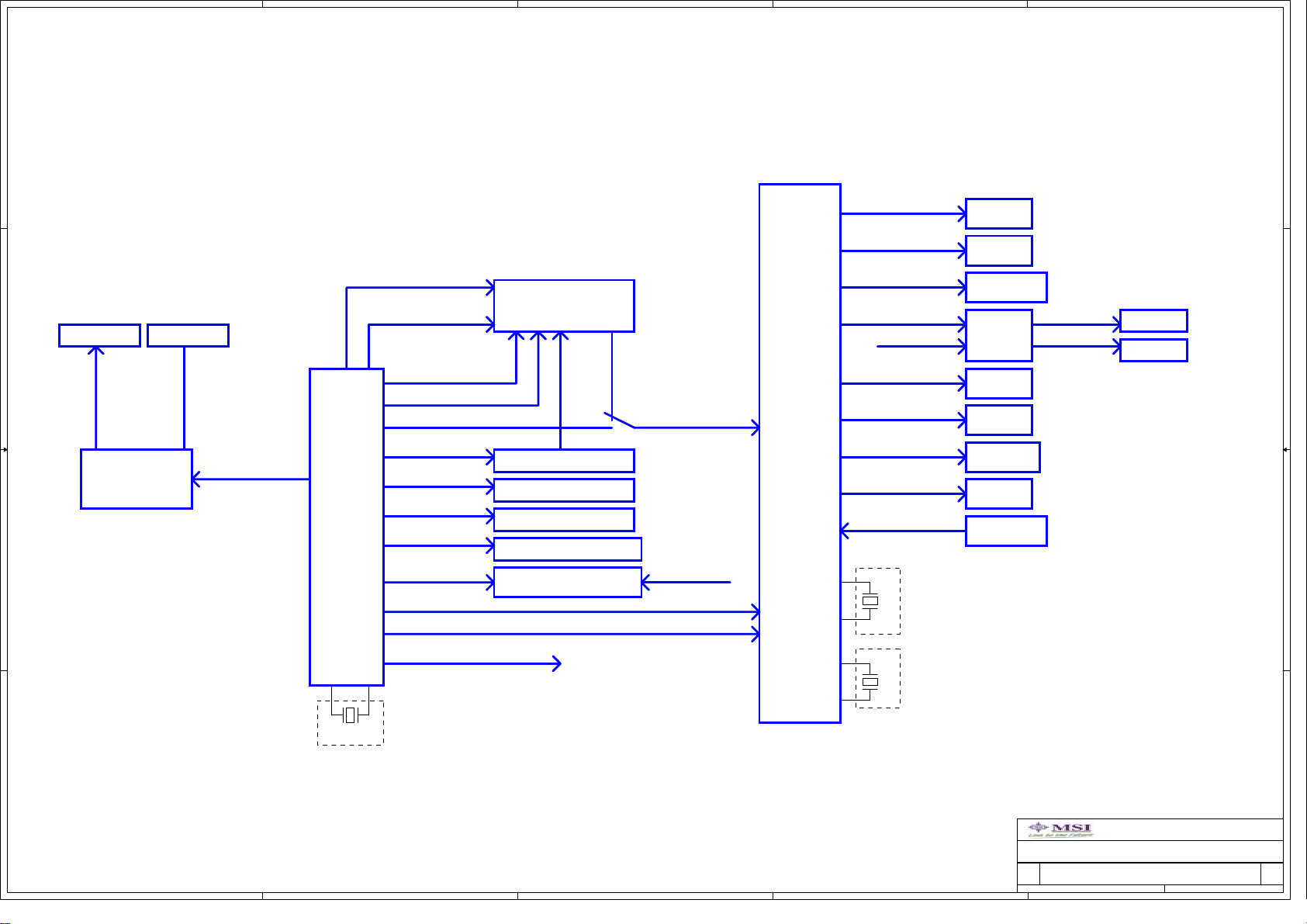

Page 3

5

4

3

2

1

ADAPTER 19 VOLTAGE

D D

AC_OK#

CHARGER MAX

1772

Page 41

ADAPTER &

BATTERY

SELECTOR

PWR_SRC

VID(0~5)

VDD_EN

V_CHG

Page 40 RUND

BATTERY 4

SM BUS to KBC

C C

or 8 CELL

BATTERY 12~16.8V

SUS_ON

+5VRUN

VDD

V CORE MAX8774GTL+

Output Select

Enable

Page 36

VDD

System power TPS51120

LDO

Swicth Dual

Enable

Page 37

+5VSUS

CPU_VDD_RUN

+3VALW

+5VALW

+5VSUS

+3VSUS

RUN_ON

AVDD_USB(SB)

+3.3V_AVDDC(SB)

S5_3.3V(SB)

VDD33(LAN)

VIN

+3VSUS

SHDN

VDDA_EN

Page 35

Run power rail Swicth

+5V_CAMERA

AVDD_5V

+5VRUN

+3VRUN

OUT

+VDDA

+3VRUN

+1_5VRUN

+3VSUS

VCCFAN1

+5VRUN_HDMI

+CRT5V

CRT5V

USB5V_A

USB5V_C

V5_VREF(SB)

+5VRUN

PCIE power SW P2231

3.3V IN

1.5VIN

3.3VAUX_IN

3.3V PCIE

1.5V PCIE

+3VSUS_PCIE

Enable

+3VRUN_PCIE

+1_5VRUN_PCIE

+3VSUS_PCIE

Page 23

VDDSPD(DIM)

AVDD(NB)

LVDDR18A(NB)

VDDR3(NB)

CLK_VDD(CLK GEN)

CLK_VDDA(CLK GEN)

VDD_48(CLK GEN)

+3VRUN

VDD_REF(CLK GEN)

XTLVDD_ATA(SB)

AVDD(SB)

VDDQ(SB)

+3V_SOCKET

VTT_VDDIO_EN

CPU_VDDIO_SUS

Enable

SC486I

VDD

CPU_VDDIO_SUS

CPU_VTT_SUS

MEM_VDDQ

MEM_VTT

singel LDO

B B

VTT_VDDIO_EN

+5VSUS

Enable

Enable

+5VSUS

OZ813LP

Page 38

VDD

+1.2VSUS

S5_1.2V(SB)

USB_PHY_1.2V(SB)

+1.2VRUN

VLDT_EN

+1.2VRUN

Page 35

Page 39

+VLDT

VCC_NB

+1.8VRUN

Swicth power

Enable

+3VRUN

Page 39

+5VRUN

A A

+5VRUN

VIN

Enable

VDD

APL5912

Page 39

+1_5VRUN

CODEC_3V

+3V_SPDIF

+V3.3S_LVDS_PANEL

PLLVDD12(NB)

VDDPLL(NB)

VDDA12(NB)

PCIE_VDDR(SB)

PCIE_PVDD(SB)

PLLVDD_ATA(SB)

AVDD_SATA(SB)

VDD(SB)

+1.2VRUN

AVDDQ(NB)

PLLVDD(NB)

HTPVDD(NB)

VDD18(NB)

IOPLLVDD18(side port)

LVDDR18D(NB)

LPVDD(NB)

AVDDDI(NB)

+1.8VRUN

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

POWER DELIVERY CHART

POWER DELIVERY CHART

POWER DELIVERY CHART

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-12221

MS-12221

MS-12221

1

1.0

1.0

345Thursday, February 01, 2007

345Thursday, February 01, 2007

345Thursday, February 01, 2007

1.0

of

of

of

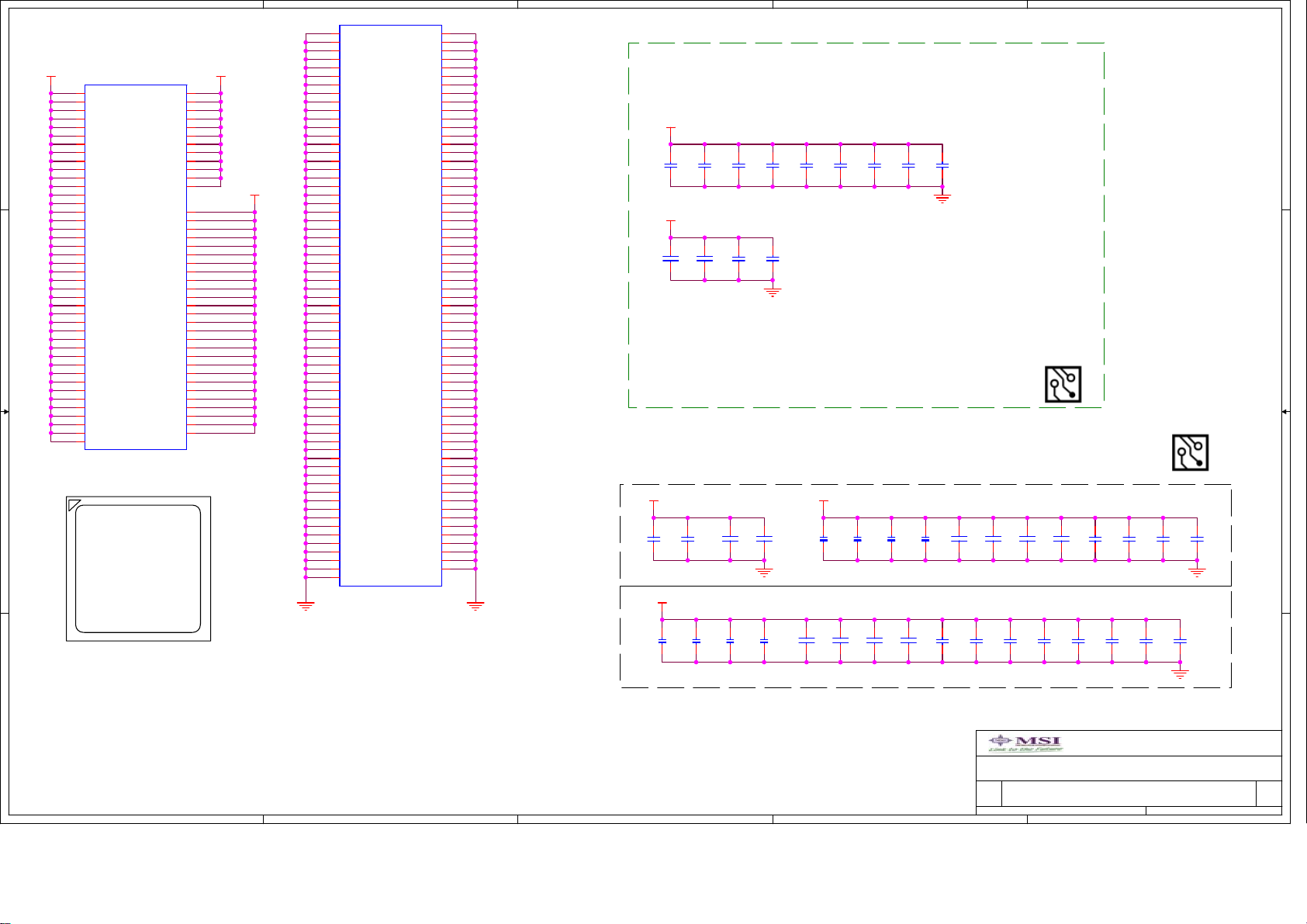

Page 4

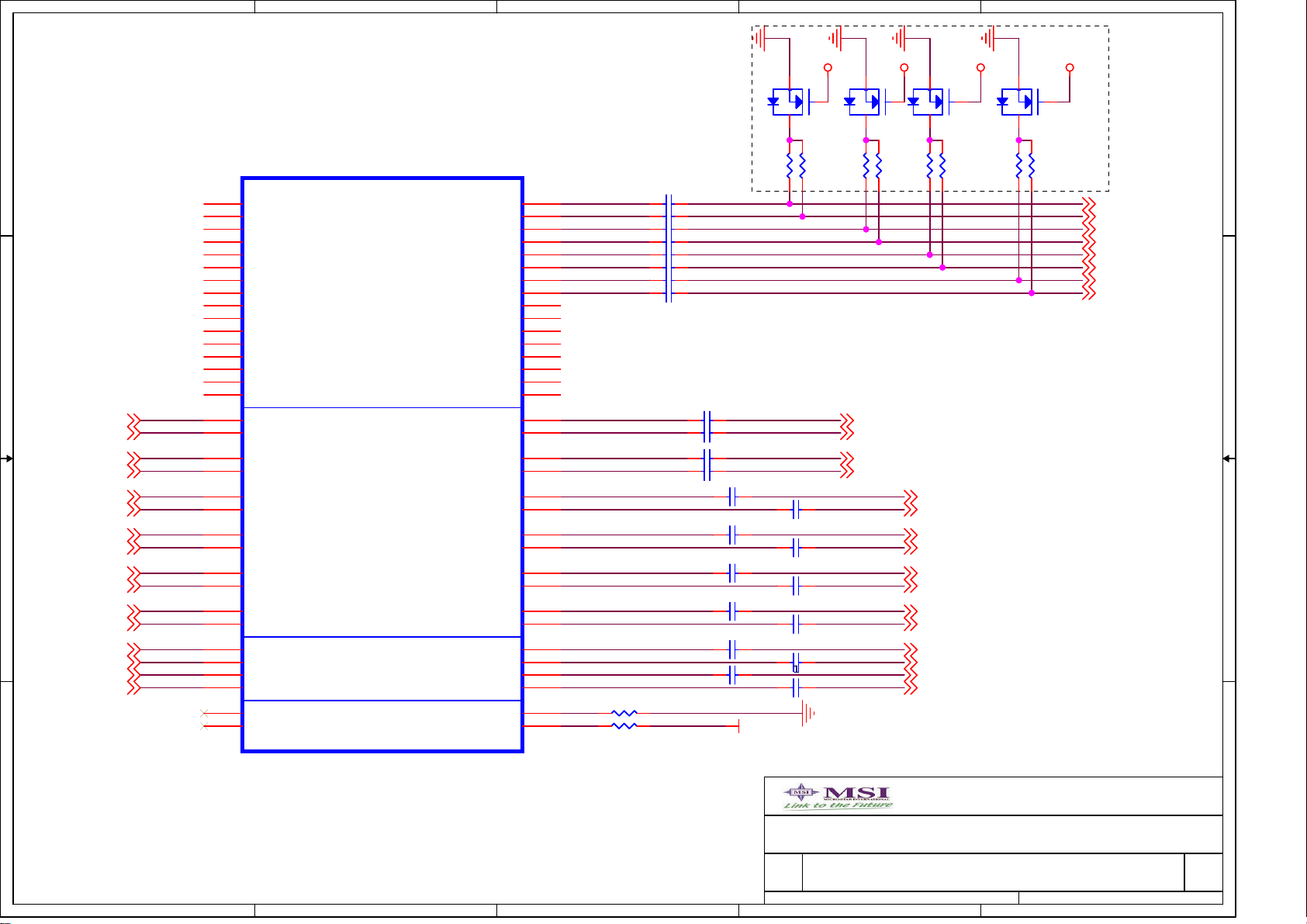

5

D D

4

3

2

1

PCI CLK0

33MHZ

PCI CLK1

33MHZ

HTREFCLK

66MHZ

NB-OSC

C C

B B

NEAR SO-DIMM REV SO-DIMM

2 PAIR MEM CLK

2 PAIR MEM CLK

ATHLON64 S1 CPU

LGA638 PACKAGE

1 PAIR CPU CLK

200MHZ

EXTERNAL

CLK GEN.

14.318MHZ

NB PCIE CLK

100MHZ

SB PCIE CLK

100MHZ

SB-OSCIN

14.318MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

SUPER IO CLK

48MHZ

ATI NB - RS690T

TVCLKIN

TVCLKIN

PCIE GFX SLOT - 16 LANES

PCIE GPP SLOT 1 - 1 LANE

PCIE GPP SLOT 2 - 1 LANE

PCI EXPRESS CARD - 1 LANE

GIGABIT ETHERNET - 1 LANE

SB-OSCIN

14.318MHZ

SB-OSCIN

14.318MHZ

25MHZ OSC INPUT

PCIE CLK

100MHZ

USB CLK

48MHZ

ATI SB

SB600

AZALIA_BITCLK

PCI CLK2

33MHZ

PCI CLK3

33MHZ

SUPER IO CLK

48MHZ

PCI CLK4

33MHZ

PCI CLK5

33MHZ

PCI CLK6

33MHZ

PCI CLK7

33MHZ

25M Hz

PCI SLOT0

PCI SLOT1

MINI PCI SLOT

SUPER IO

IT8712F

LPC SLOT

LPC BIOS

DEBUG POST

PCI SLOT2

AZALIA CODEC

KB_CLK

MS_CLK

KEYBOARD

MOUSE

32.768K Hz

14.31818MHz

A A

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-12221

MS-12221

MS-12221

1

1.0

1.0

445Thursday, February 01, 2007

445Thursday, February 01, 2007

445Thursday, February 01, 2007

1.0

of

of

of

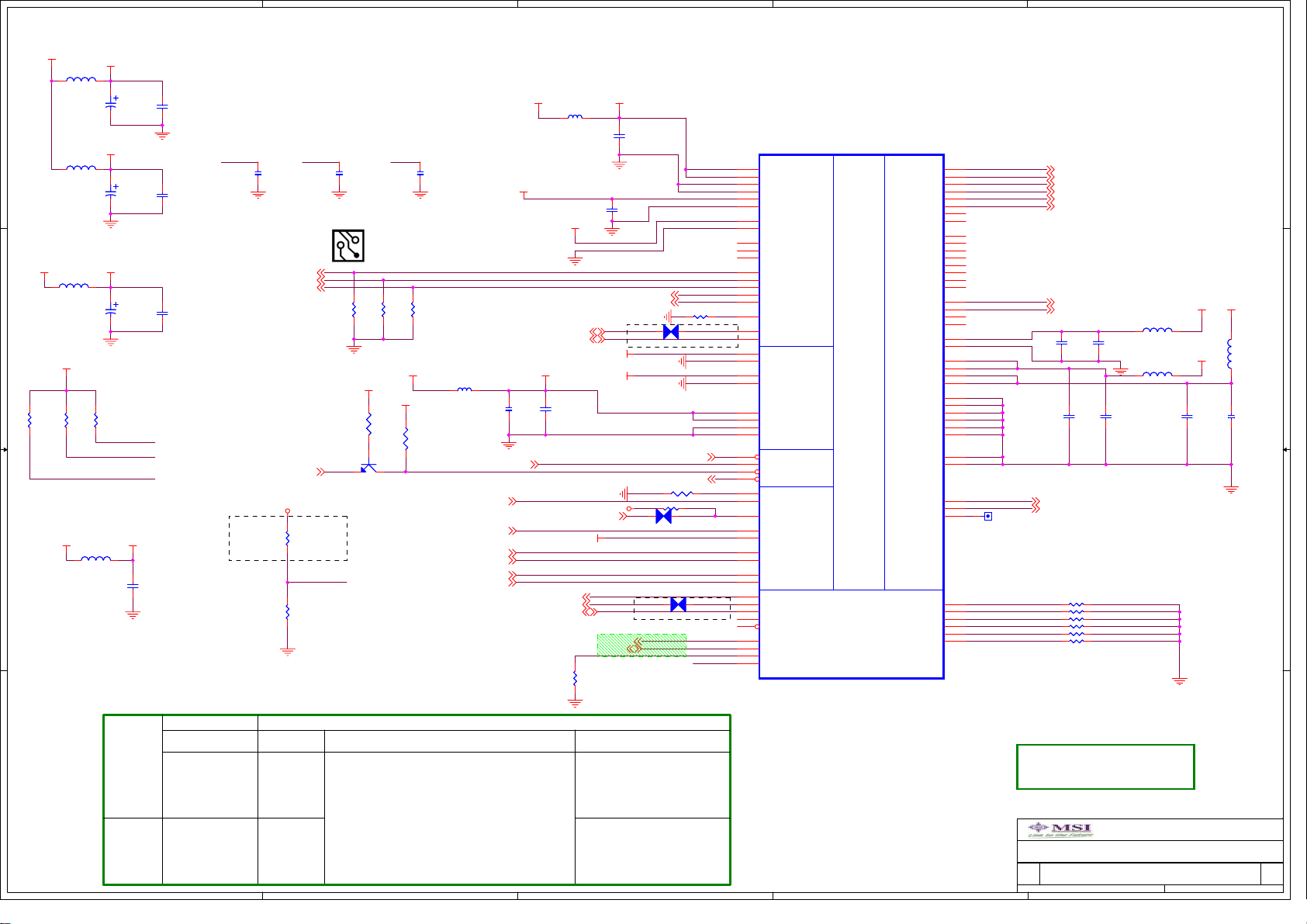

Page 5

5

4

3

2

1

PROCESSOR HYPERTRANSPORT INTERFACE

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

D D

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

+VLDT

D4

VLDT_A3

D3

VLDT_A2

D2

VLDT_A1

D1

VLDT_A0

HT_CADIN15_P11

HT_CADIN15_N11

HT_CADIN14_P11

HT_CADIN14_N11

HT_CADIN13_P11

C C

B B

+VLDT

HT_CADIN13_N11

HT_CADIN12_P11

HT_CADIN12_N11

HT_CADIN11_P11

HT_CADIN11_N11

HT_CADIN10_P11

HT_CADIN10_N11

HT_CADIN9_P11

HT_CADIN9_N11

HT_CADIN8_P11

HT_CADIN8_N11

HT_CADIN7_P11

HT_CADIN7_N11

HT_CADIN6_P11

HT_CADIN6_N11

HT_CADIN5_P11

HT_CADIN5_N11

HT_CADIN4_P11

HT_CADIN4_N11

HT_CADIN3_P11

HT_CADIN3_N11

HT_CADIN2_P11

HT_CADIN2_N11

HT_CADIN1_P11

HT_CADIN1_N11

HT_CADIN0_P11

HT_CADIN0_N11

HT_CLKIN1_P11

HT_CLKIN1_N11

HT_CLKIN0_P11

HT_CLKIN0_N11

N5

L0_CADIN_H15

P5

L0_CADIN_L15

M3

L0_CADIN_H14

M4

L0_CADIN_L14

L5

L0_CADIN_H13

M5

L0_CADIN_L13

K3

L0_CADIN_H12

K4

L0_CADIN_L12

H3

L0_CADIN_H11

H4

L0_CADIN_L11

G5

L0_CADIN_H10

H5

L0_CADIN_L10

F3

L0_CADIN_H9

F4

L0_CADIN_L9

E5

L0_CADIN_H8

F5

L0_CADIN_L8

N3

L0_CADIN_H7

N2

L0_CADIN_L7

L1

L0_CADIN_H6

M1

L0_CADIN_L6

L3

L0_CADIN_H5

L2

L0_CADIN_L5

J1

L0_CADIN_H4

K1

L0_CADIN_L4

G1

L0_CADIN_H3

H1

L0_CADIN_L3

G3

L0_CADIN_H2

G2

L0_CADIN_L2

E1

L0_CADIN_H1

F1

L0_CADIN_L1

E3

L0_CADIN_H0

E2

L0_CADIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

U1AU1A

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

AE5

AE4

AE3

AE2

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

Y4

Y3

Y1

W1

C1

C1

4.7u_6V_0603

4.7u_6V_0603

HT_CADOUT15_P 11

HT_CADOUT15_N 11

HT_CADOUT14_P 11

HT_CADOUT14_N 11

HT_CADOUT13_P 11

HT_CADOUT13_N 11

HT_CADOUT12_P 11

HT_CADOUT12_N 11

HT_CADOUT11_P 11

HT_CADOUT11_N 11

HT_CADOUT10_P 11

HT_CADOUT10_N 11

HT_CADOUT9_P 11

HT_CADOUT9_N 11

HT_CADOUT8_P 11

HT_CADOUT8_N 11

HT_CADOUT7_P 11

HT_CADOUT7_N 11

HT_CADOUT6_P 11

HT_CADOUT6_N 11

HT_CADOUT5_P 11

HT_CADOUT5_N 11

HT_CADOUT4_P 11

HT_CADOUT4_N 11

HT_CADOUT3_P 11

HT_CADOUT3_N 11

HT_CADOUT2_P 11

HT_CADOUT2_N 11

HT_CADOUT1_P 11

HT_CADOUT1_N 11

HT_CADOUT0_P 11

HT_CADOUT0_N 11

HT_CLKOUT1_P 11

HT_CLKOUT1_N 11

HT_CLKOUT0_P 11

HT_CLKOUT0_N 11

+VLDT

C2

C2

4.7u_6V_0603

4.7u_6V_0603

AMD check list 4-24~4-27

0.22u_10V_0402 (DNI)

0.22u_10V_0402 (DNI)

C5

C3

C3

4.7u_6v_0603

4.7u_6v_0603

C4

C4

C5

0.22u_10V_0402

0.22u_10V_0402

180pF_50v_0402 (DNI)

180pF_50v_0402 (DNI)

C6

C6

C7

C7

180pF_50v_0402

180pF_50v_0402

LAYOUT: Place bypass cap on topside of board

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

5

HT_CTLIN1_P

HT_CTLIN1_N

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

Athlon 64 S1

Processor

Socket

4

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

R1 51_0402R1 51_0402

A A

R2 51_0402R2 51_0402

HT_CTLIN0_P11

HT_CTLIN0_N11

HT_CPU_CTLOUT1_P

T5

HT_CPU_CTLOUT1_N

R5

R2

R3

TP1TP1

TP2TP2

HT_CTLOUT0_P 11

HT_CTLOUT0_N 11

3

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

SOCKET S1 HT I/F

SOCKET S1 HT I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

SOCKET S1 HT I/F

Custom

Custom

Custom

MS-12221

MS-12221

MS-12221

2

of

of

of

545Thursday, February 01, 2007

545Thursday, February 01, 2007

545Thursday, February 01, 2007

1

1.0

1.0

1.0

Page 6

A

B

C

D

E

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

4 4

3 3

2 2

CPU_VDDIO_SUS

R3

R3

39.2_0402 1%

39.2_0402 1%

R4

R4

39.2_0402 1%

39.2_0402 1%

PLACE THEM CLOSE TO

CPU WITHIN 1"

CPU_VTT_SUS

CPU_M_VREF_SUS

C8 1n_50v_0402 (DNI)C8 1n_50v_0402 (DNI)

SNS_+0.9VTT

M_ZN

M_ZP

MEM_MA0_CS#39,10

MEM_MA0_CS#29,10

MEM_MA0_CS#19,10

MEM_MA0_CS#09,10

MEM_MB0_CS#39,10

MEM_MB0_CS#29,10

MEM_MB0_CS#19,10

MEM_MB0_CS#09,10

MEM_MB_CKE19,10

MEM_MB_CKE09,10

MEM_MA_CKE19,10

MEM_MA_CKE09,10

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_BANK29,10

MEM_MA_BANK19,10

MEM_MA_BANK09,10

MEM_MA_RAS#9,10

MEM_MA_CAS#9,10

MEM_MA_WE#9,10

AE10

AF10

W17

W24

M19

M20

M24

M22

Y10

V19

J22

V22

T19

Y26

J24

U23

H26

J23

J20

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

N22

N21

R21

K22

R20

T22

T20

U20

U21

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MB0_CS_L3

MB0_CS_L2

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

U1B

U1B

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_ODT1

MB0_ODT0

MA0_ODT1

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

Athlon 64 S1

Processor Socket

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

D10

C10

B10

AD10

W10

AC10

AB10

AA10

A10

Y16

AA16

E16

F16

AF18

AF17

A17

A18

W23

W26

V20

U19

MEM_MB_ADD15

J25

MEM_MB_ADD14

J26

MEM_MB_ADD13

W25

MEM_MB_ADD12

L23

MEM_MB_ADD11

L25

MEM_MB_ADD10

U25

MEM_MB_ADD9

L24

MEM_MB_ADD8

M26

MEM_MB_ADD7

L26

MEM_MB_ADD6

N23

MEM_MB_ADD5

N24

MEM_MB_ADD4

N25

MEM_MB_ADD3

N26

MEM_MB_ADD2

P24

MEM_MB_ADD1

P26

MEM_MB_ADD0

T24

K26

T26

U26

U24

V26

U22

CPU_VTT_SUS

MEM_MA0_CLK2_P 9

MEM_MA0_CLK2_N 9

MEM_MA0_CLK1_P 9

MEM_MA0_CLK1_N 9

MEM_MB0_CLK2_P 9

MEM_MB0_CLK2_N 9

MEM_MB0_CLK1_P 9

MEM_MB0_CLK1_N 9

MEM_MB0_ODT1 9,10

MEM_MB0_ODT0 9,10

MEM_MA0_ODT1 9,10

MEM_MA0_ODT0 9,10

MEM_MB_ADD[15..0] 9,10MEM_MA_ADD[15..0]9,10

MEM_MB_BANK2 9,10

MEM_MB_BANK1 9,10

MEM_MB_BANK0 9,10

MEM_MB_RAS# 9,10

MEM_MB_CAS# 9,10

MEM_MB_WE# 9,10

MEM_MB_DATA[63..0]9

VDD_VREF_SUS_CPU

CPU_VDDIO_SUS

CPU_M_VREF_SUS

Processor DDR2 Memory Interface

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DM[7..0]9

MEM_MB_DQS7_P9

MEM_MB_DQS7_N9

MEM_MB_DQS6_P9

MEM_MB_DQS6_N9

MEM_MB_DQS5_P9

MEM_MB_DQS5_N9

MEM_MB_DQS4_P9

MEM_MB_DQS4_N9

MEM_MB_DQS3_P9

MEM_MB_DQS3_N9

MEM_MB_DQS2_P9

MEM_MB_DQS2_N9

MEM_MB_DQS1_P9

MEM_MB_DQS1_N9

MEM_MB_DQS0_P9

MEM_MB_DQS0_N9

MEM_MB_DATA0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AD11

AF11

AF14

AE14

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

AD12

AC16

AE22

AB26

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

Y11

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

E25

A22

B16

A12

F26

E26

A24

A23

D16

C16

C12

B12

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

U1C

U1C

DDR: DATA

DDR: DATA

Athlon 64 S1

Processor Socket

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y13

AB16

Y19

AC24

F24

E19

C15

E12

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DATA[63..0] 9

MEM_MA_DM[7..0] 9

MEM_MA_DQS7_P 9

MEM_MA_DQS7_N 9

MEM_MA_DQS6_P 9

MEM_MA_DQS6_N 9

MEM_MA_DQS5_P 9

MEM_MA_DQS5_N 9

MEM_MA_DQS4_P 9

MEM_MA_DQS4_N 9

MEM_MA_DQS3_P 9

MEM_MA_DQS3_N 9

MEM_MA_DQS2_P 9

MEM_MA_DQS2_N 9

MEM_MA_DQS1_P 9

MEM_MA_DQS1_N 9

MEM_MA_DQS0_P 9

MEM_MA_DQS0_N 9

R5

1K_0402 1%R51K_0402 1%

1n_50v_0402 (DNI)

C14

C14

1n_50v_0402

1n_50v_0402

1n_50v_0402 (DNI)

C15

C15

LAYOUT:PLACE CLOSE TO CPU

B

R6

1K_0402 1%R61K_0402 1%

1 1

A

MEM_MB0_CLK2_P9

MEM_MB0_CLK2_N9

MEM_MB0_CLK1_P9

MEM_MB0_CLK1_N9

AMD check list 2-1

MEM_MA0_CLK2_P9

MEM_MA0_CLK2_N9

MEM_MA0_CLK1_P9

MEM_MA0_CLK1_N9

C13

C13

1.5p_50v_0402

1.5p_50v_0402

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

C19

C19

1.5p_50v_0402

1.5p_50v_0402

C20

C20

1.5p_50v_0402

1.5p_50v_0402

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

C21

C21

1.5p_50v_0402

1.5p_50v_0402

A1

A26

Athlon 64 S1g1

uPGA638

Top View

AF1

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

SOCKET S1 DDR2 MEMORY I/F

SOCKET S1 DDR2 MEMORY I/F

SOCKET S1 DDR2 MEMORY I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-12221

MS-12221

MS-12221

E

1.0

1.0

645Thursday, February 01, 2007

645Thursday, February 01, 2007

645Thursday, February 01, 2007

1.0

of

of

of

Page 7

5

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

CPU_VDDA_2.5_RUN

D D

LDT_STOP#13,17

C C

B B

+3VSUS

A A

T_CRIT_CPU#33

SB_CPUPWRGD17

Harry 2007/01/18

R473

R473

715_0402

715_0402

LDT_RST#17

RN1 8P4R-10K_RN0402RN1 8P4R-10K_RN0402

1

3

5

7

Cap close to

thermal

sensor

CPU_TEST4_THERMDA

C30

C30

2200p_50V_0402

2200p_50V_0402

CPU_TEST5_THERMDC

T_CRIT_CPU#

2

CPU_THRM_ALERT-

4

SMB_THRMCPU_DATA

6

SMB_THRMCPU_CLK

8

C31

C31

0.1u_10V_0402

0.1u_10V_0402

5

R471

R471

D27

D27

3

1

S-BAT54C_SOT23

S-BAT54C_SOT23

R631

R631

8.2K_0402

8.2K_0402

R475

R475

715_0402

715_0402

+3VSUS

JNC2 0R_0402 (DNI)JNC2 0R_0402 (DNI)

715_0402

715_0402

2

C984

C984

47p_50V_0402

47p_50V_0402

JNC6 0R_0402 (DNI)JNC6 0R_0402 (DNI)

U5

U5

1

VDD

2

D+

3

D-

4

T_CRIT_A#

LM86CIMMXNOPB_MSOP8-RH

LM86CIMMXNOPB_MSOP8-RH

Close to CPU socket

1

2

3

SMBCLK

SMBDATA

ALERT#

GND

CPU_ALL_PWROK

PN N/A

NC

NC

A

A

GND

GND

SN74LVC1G17DBV

SN74LVC1G17DBV

CPU_HT_RESET#

8

7

6

5

4

+1.8VRUN

U51

U51

VCC

VCC

5

Y

Y

4

CPUCLK16

CPUCLK#16

CPU_PROCHOT#_1.8

SMB_THRMCPU_CLK

SMB_THRMCPU_DATA

4

CPU_VDDIO_SUS

CPU_LDTSTOP#

C26 3.9n_50V_0603C26 3.9n_50V_0603

C27 3.9n_50V_0603C27 3.9n_50V_0603

CPU_VDDIO_SUS

CPU_PH_G

B

E C

Q3

Q3

SMBT3904

SMBT3904

maximun

+VDDA

40 ohm

AMD check list 4-22

L1

L1

10L1000m_50_0402

10L1000m_50_0402

R12 300_0402 (DNI)R12 300_0402 (DNI)

R14

R14

300_0402 (DNI)

300_0402 (DNI)

ATI change at Herring 1.5 0C version on 10/26/2006ATI Errata ER_RS690B2&PA_IPX600AD12

+VLDT

place them to CPU within 1"

R20

R20

169_0402 1%

169_0402 1%

R38

R38

+3VRUN

10K_0402

10K_0402

R42 4.7K_0402R42 4.7K_0402

SB_TALERT# 19

SMB_THRMCPU_CLK 31

SMB_THRMCPU_DATA 31

CPU_THRM_ALERT- 31

3

ATHLON Control and Debug

C23

C23

C22

C22

3300p_50V_0402

4.7u_6V_0603

4.7u_6V_0603

R15 44.2_0603 1%R15 44.2_0603 1%

R16 44.2_0603 1%R16 44.2_0603 1%

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_TEST5_THERMDC

CPU_TEST4_THERMDA

3300p_50V_0402

CPU_HT_RESET#

R13

R13

CPU_ALL_PWROK

300_0402

300_0402

TP3TP3

TP4TP4

TP5TP5

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_SIC_R

CPU_SID_R

CPU_VDD_RUN_FB_H36

CPU_VDD_RUN_FB_L36

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

3

CPU_LDTSTOP#

CPU_DBRDY

TEST19

TEST18

TP7TP7

TP9TP9

TP11TP11

TP13TP13

TP14TP14

CPU_HTREF1

CPU_HTREF0

C24

C24

0.22u_10V_0402

0.22u_10V_0402

F8

F9

B7

A7

F10

AF4

AF5

P6

R6

F6

E6

W9

Y9

A9

A8

G10

AA9

AC9

AD9

AF9

E9

E8

G9

H10

AA7

C2

D7

E7

F7

C7

AC8

C3

AA6

W7

W8

Y6

AB6

P20

P19

N20

N19

R26

R25

P22

R22

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

SIC

SID

HT_REF1

HT_REF0

VDD_FB_H

VDD_FB_L

VDDIO_FB_H

VDDIO_FB_L

CLKIN_H

CLKIN_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

AMD NPT S1 SOCKET

Processor Socket

U1D

U1D

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

DBREQ_L

JTAC

JTAC

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

MISC

MISC

VID5

VID4

VID3

VID2

VID1

VID0

PSI_L

TDO

TEST8

RSVD8

RSVD9

2

CPU_VDDIO_SUS

300_0402

300_0402

CPU_THERMTRIP#_R

AF6

CPU_PROCHOT#_1.8

AC7

CPU_VID5

A5

CPU_VID4

C6

CPU_VID3

A6

CPU_VID2

A4

CPU_VID1

C5

CPU_VID0

B5

CPU_PRESENT#

AC6

CPU_PSI#

A3

CPU_DBREQ#

E10

CPU_TDO

AE9

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

Trace impedance 80ohm

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

TEST26

AE6

K8

C4

H16

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

2

1

CPU_VDDIO_SUS

+3VSUS

R7

R7

10K_0402

10K_0402

R9

R9

R10

R8

R8

TP8TP8

TP10TP10

TEST21

TP12TP12

TP15TP15

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

R10

300_0402

300_0402

300_0402

300_0402

CPU_PSI# 36

TP6TP6

R22 80.6_0402 1%R22 80.6_0402 1%

TEST26

CPU_DBREQ#

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

TEST18

TEST19

TEST21

SOCKET S1 CTRL

SOCKET S1 CTRL

SOCKET S1 CTRL

Harry 10/02

Harry 10/02 ERRATA#133

MS-12221

MS-12221

MS-12221

R11 4.7K_0402 (DNI)R11 4.7K_0402 (DNI)

B

E C

Q1

Q1

SMBT3904

SMBT3904

CPU_VID5 36

CPU_VID4 36

CPU_VID3 36

CPU_VID2 36

CPU_VID1 36

CPU_VID0 36

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

PLACE IT CLOSE TO CPU WITHIN 1"

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

CPU_THERMTRIP# 18

CPU_VDDIO_SUS

ERRATA#133

R625 300_0402R625 300_0402

R28 510_0402 (DNI)R28 510_0402 (DNI)

R29 510_0402 (DNI)R29 510_0402 (DNI)

R30 510_0402 (DNI)R30 510_0402 (DNI)

R31 510_0402 (DNI)R31 510_0402 (DNI)

R33 510_0402 (DNI)R33 510_0402 (DNI)

R35 1K_0402R35 1K_0402

R36 510_0402R36 510_0402

R39 510_0402R39 510_0402

R626 300_0402R626 300_0402

R627 300_0402R627 300_0402

R628 300_0402R628 300_0402

745Thursday, February 01, 2007

745Thursday, February 01, 2007

745Thursday, February 01, 2007

1

of

of

of

1.0

1.0

1.0

Page 8

5

AA4

AA11

AA13

AA15

CPU_VDD_RUN CPU_VDD_RUN

AC4

AD2

J11

J13

K10

K12

K14

L11

L13

M10

N11

P10

R11

T10

T12

T14

U11

U13

V10

G4

H2

J9

K6

L4

L7

L9

M2

M6

M8

N7

N9

P8

R4

R7

R9

T2

T6

T8

U7

U9

V6

V8

D D

C C

A1

B B

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

U1E

U1E

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

POWER

POWER

Athlon 64 S1

Processor Socket

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

A26

CPU_VDDIO_SUS

Athlon 64 S1g1

uPGA638

AA17

AA19

AB2

AB7

AB9

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

F11

F13

F15

F17

F19

F21

F23

F25

H21

H23

B4

B6

B8

B9

D6

D8

D9

E4

F2

H7

H9

J4

Top View

AF1

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

4

U1F

U1F

GROUND

GROUND

Athlon 64 S1

Processor

Socket

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

3

2

BOTTOMSIDE DECOUPLING

CPU_VDD_RUN

22u_6V_0805

22u_6V_0805

C34

C34

C33

C33

22u_6V_0805

22u_6V_0805

0.01u_16V_0402

0.01u_16V_0402

C42

C42

C43

C43

22u_6V_0805

22u_6V_0805

C35

C35

C36

C36

22u_6V_0805

22u_6V_0805

C44

C44

180pF_50v_0402

180pF_50v_0402

22u_6V_0805

22u_6V_0805

C37

C37

22u_6V_0805

22u_6V_0805

C39

C39

C38

C38

22u_6V_0805

22u_6V_0805

AMD check list 4-16~4-20

22u_6V_0805

22u_6V_0805

C40

C40

CPU_VDD_RUN

C41

C41

0.22u_10V_0402

0.22u_10V_0402

22u_6V_0805

22u_6V_0805

C32

C32

0.22u_10V_0402

0.22u_10V_0402

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

CPU_VDDIO_SUS

C45

C45

22u_6V_0805

22u_6V_0805

CPU_VTT_SUS

4.7u_6V_0603

4.7u_6V_0603

C61

C61

0.22u_10V_0402

0.22u_10V_0402

C47

C47

C46

C46

22u_6V_0805

22u_6V_0805

4.7u_6V_0603

4.7u_6V_0603

C63

C63

C62

C62

4.7u_6V_0603

4.7u_6V_0603

C48

C48

4.7u_6V_0603

4.7u_6V_0603

CPU_VDDIO_SUS

4.7u_6V_0603

4.7u_6V_0603

C49

C49

0.22u_10V_0402

0.22u_10V_0402

AMD Check list 4-1~4-5

0.22u_10V_0402

0.22u_10V_0402

C65

C65

C64

C64

C66

C66

0.22u_10V_0402

0.22u_10V_0402

AMD check list 4-6~4-8,4-11

4.7u_6V_0603

4.7u_6V_0603

C50

C50

C51

C51

4.7u_6V_0603

4.7u_6V_0603

0.22u_10V_0402

0.22u_10V_0402

C67

C67

0.22u_10V_0402

0.22u_10V_0402

4.7u_6V_0603

4.7u_6V_0603

C52

C52

C68

C68

0.22u_10V_0402

0.22u_10V_0402

C54

C54

C53

C53

0.22u_10V_0402

0.22u_10V_0402

1n_50V_0402

1n_50V_0402

C69

C69

C70

C70

1n_50V_0402

1n_50V_0402

0.22u_10V_0402

0.22u_10V_0402

C56

C56

C55

C55

0.22u_10V_0402

0.22u_10V_0402

180pF_50v_0402

180pF_50v_0402

1n_50V_0402

1n_50V_0402

C72

C72

C71

C71

1n_50V_0402

1n_50V_0402

0.01u_16V_0402

0.01u_16V_0402

C57

C57

0.01u_16V_0402

0.01u_16V_0402

C73

C73

C74

C74

180pF_50v_0402

180pF_50v_0402

1

C58

C58

C59

C59

180pF_50v_0402

180pF_50v_0402

180pF_50v_0402

180pF_50v_0402

C75

C75

180pF_50v_0402

180pF_50v_0402

180pF_50v_0402

180pF_50v_0402

C60

C60

C76

C76

A A

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

SOCKET S1 PWR & GND

SOCKET S1 PWR & GND

SOCKET S1 PWR & GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

5

PROCESSOR POWER AND GROUND

4

3

2

B

Date: Sheet

Date: Sheet

Date: Sheet

MS-12221

MS-12221

MS-12221

MICRO-STAR INT'L CO.,LTD.

845Thursday, February 01, 2007

845Thursday, February 01, 2007

845Thursday, February 01, 2007

of

of

1

of

1.0

1.0

1.0

Page 9

5

CPU_VDDIO_SUS

MEM_MA_ADD[15..0]6,10

D D

MEM_MA_BANK[2..0]6,10

MEM_MA_DM[7..0]6

MEM_MA_DQS0_P6

MEM_MA_DQS1_P6

MEM_MA_DQS2_P6

MEM_MA_DQS3_P6

C C

B B

A A

MEM_MA_DQS4_P6

MEM_MA_DQS5_P6

MEM_MA_DQS6_P6

MEM_MA_DQS7_P6

MEM_MA_DQS0_N6

MEM_MA_DQS1_N6

MEM_MA_DQS2_N6

MEM_MA_DQS3_N6

MEM_MA_DQS4_N6

MEM_MA_DQS5_N6

MEM_MA_DQS6_N6

MEM_MA_DQS7_N6

MEM_MA0_CLK1_P6

MEM_MA0_CLK2_P6

MEM_MA0_CLK1_N6

MEM_MA0_CLK2_N6

MEM_MA_CKE06,10

MEM_MA_CKE16,10

MEM_MA_RAS#6,10

MEM_MA_CAS#6,10

MEM_MA_WE#6,10

MEM_MA0_CS#06,10

MEM_MA0_CS#16,10

MEM_MA0_ODT06,10

MEM_MA0_ODT16,10

SDATA016,18,45

5

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

SCLK016,18,45

+3VRUN

MEM_M_VREF_SUS

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10

90

A11

89

A12

116

A13

86

A14/NC

84

A15/NC

107

BA0

106

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

129

DQS4

146

DQS5

167

DQS6

186

DQS7

30

CK0

32

CK0

164

CK1

166

CK1

79

CKE0

80

CKE1

108

RAS

113

CAS

109

WE

110

S0

115

S1

114

ODT0

119

ODT1

198

SA0

200

SA1

195

SDA

197

SCL

199

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

SO-DIMM

SO-DIMM

59

DDR2_SODIMM_RVS_H=5.2mm

DDR2_SODIMM_RVS_H=5.2mm

103

111

104

112

117

118

VDD8

VDD7

VDD9

VDD10

(RVS)

(RVS)

VSS31

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

128

127

122

121

4

VDD11

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC/TEST

VSS57

VSS58

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

132

4

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

NC1

NC2

NC3

NC4

J2

J2

MEM_MA_DATA0

5

MEM_MA_DATA1

7

MEM_MA_DATA2

17

MEM_MA_DATA3

19

MEM_MA_DATA4

4

MEM_MA_DATA5

6

MEM_MA_DATA6

14

MEM_MA_DATA7

16

MEM_MA_DATA8MEM_MA_ADD8

23

MEM_MA_DATA9

25

MEM_MA_DATA10

35

MEM_MA_DATA11

37

MEM_MA_DATA12

20

MEM_MA_DATA13

22

MEM_MA_DATA14

36

MEM_MA_DATA15

38

MEM_MA_DATA16

43

MEM_MA_DATA17

45

MEM_MA_DATA18

55

MEM_MA_DATA19

57

MEM_MA_DATA20

44

MEM_MA_DATA21

46

MEM_MA_DATA22

56

MEM_MA_DATA23

58

MEM_MA_DATA24

61

MEM_MA_DATA25

63

MEM_MA_DATA26

73

MEM_MA_DATA27

75

MEM_MA_DATA28

62

MEM_MA_DATA29

64

MEM_MA_DATA30

74

MEM_MA_DATA31

76

MEM_MA_DATA32

123

MEM_MA_DATA33

125

MEM_MA_DATA34

135

MEM_MA_DATA35

137

MEM_MA_DATA36

124

MEM_MA_DATA37

126

MEM_MA_DATA38

134

MEM_MA_DATA39

136

MEM_MA_DATA40

141

MEM_MA_DATA41

143

MEM_MA_DATA42

151

MEM_MA_DATA43

153

MEM_MA_DATA44

140

MEM_MA_DATA45

142

MEM_MA_DATA46

152

MEM_MA_DATA47

154

MEM_MA_DATA48

157

MEM_MA_DATA49

159

MEM_MA_DATA50

173

MEM_MA_DATA51

175

MEM_MA_DATA52

158

MEM_MA_DATA53

160

MEM_MA_DATA54

174

MEM_MA_DATA55

176

MEM_MA_DATA56

179

MEM_MA_DATA57

181

MEM_MA_DATA58

189

MEM_MA_DATA59

191

MEM_MA_DATA60

180

MEM_MA_DATA61

182

MEM_MA_DATA62

192

MEM_MA_DATA63

194

50

69

83

120

163

201

202

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

MEM_MA_DATA[63..0] 6

MEM_MA0_CS#2 6,10

MEM_MA0_CS#3 6,10

CPU_VDDIO_SUS

3

MEM_MB_ADD[15..0]6,10

MEM_MB_BANK[2..0]6,10

MEM_MB_DM[7..0]6

MEM_MB_DQS0_P6

MEM_MB_DQS1_P6

MEM_MB_DQS2_P6

MEM_MB_DQS3_P6

MEM_MB_DQS4_P6

MEM_MB_DQS5_P6

MEM_MB_DQS6_P6

MEM_MB_DQS7_P6

MEM_MB_DQS0_N6

MEM_MB_DQS1_N6

MEM_MB_DQS2_N6

MEM_MB_DQS3_N6

MEM_MB_DQS4_N6

MEM_MB_DQS5_N6

MEM_MB_DQS6_N6

MEM_MB_DQS7_N6

MEM_VREF_SUS

R44

R44

1K_0402 1%

1K_0402 1%

R45

R45

1K_0402 1%

1K_0402 1%

LAYOUT: PLACE CLOSE TO DIMMs

3

MEM_M_VREF_SUS

C90

C90

0.1u_10V_0402

0.1u_10V_0402

MEM_MB0_CLK1_P6

MEM_MB0_CLK1_N6

MEM_MB0_CLK2_P6

MEM_MB0_CLK2_N6

MEM_MB_CKE06,10

MEM_MB_CKE16,10

MEM_MB_RAS#6,10

MEM_MB_CAS#6,10

MEM_MB0_CS#06,10

MEM_MB0_CS#16,10

MEM_MB0_ODT06,10

MEM_MB0_ODT16,10

+3VRUN

C92

C92

1n_50v_0402

1n_50v_0402

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_WE#6,10

R43 4.7K_0402R43 4.7K_0402

SDATA016,18,45

SCLK016,18,45

+3VRUN

MEM_M_VREF_SUS

CPU_VDDIO_SUS

102

101

100

105

116

107

106

130

147

170

185

131

148

169

188

129

146

167

186

164

166

108

113

109

110

115

114

119

198

200

195

197

199

99

98

97

94

92

93

91

90

89

86

84

85

10

26

52

67

13

31

51

70

11

29

49

68

30

32

79

80

1

2

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

2

2

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14/NC

A15/NC

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

103

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

59

1

111

104

112

117

118

J1

J1

MEM_MB_DATA0

5

DQ0

MEM_MB_DATA1

7

DQ1

VDD8

VDD7

VDD9

VDD10

VDD11

NC/TEST

VSS57

VSS58

VSS56

SO-DIMM(RVS)

SO-DIMM(RVS)

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

132

128

127

122

121

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MEM_MB_DATA2

17

DQ2

MEM_MB_DATA3

19

DQ3

MEM_MB_DATA4

4

DQ4

MEM_MB_DATA5

6

DQ5

MEM_MB_DATA6

14

DQ6

MEM_MB_DATA7

16

DQ7

MEM_MB_DATA8

23

DQ8

MEM_MB_DATA9

25

DQ9

MEM_MB_DATA10

35

DQ10

MEM_MB_DATA11

37

DQ11

MEM_MB_DATA12

20

DQ12

MEM_MB_DATA13

22

DQ13

MEM_MB_DATA14

36

DQ14

MEM_MB_DATA15

38

DQ15

MEM_MB_DATA16

43

DQ16

MEM_MB_DATA17

45

DQ17

MEM_MB_DATA18

55

DQ18

MEM_MB_DATA19

57

DQ19

MEM_MB_DATA20

44

DQ20

MEM_MB_DATA21

46

DQ21

MEM_MB_DATA22

56

DQ22

MEM_MB_DATA23

58

DQ23

MEM_MB_DATA24

61

DQ24

MEM_MB_DATA25

63

DQ25

MEM_MB_DATA26

73

DQ26

MEM_MB_DATA27

75

DQ27

MEM_MB_DATA28

62

DQ28

MEM_MB_DATA29

64

DQ29

MEM_MB_DATA30

74

DQ30

MEM_MB_DATA31

76

DQ31

MEM_MB_DATA32

123

DQ32

MEM_MB_DATA33

125

DQ33

MEM_MB_DATA34

135

DQ34

MEM_MB_DATA35

137

DQ35

MEM_MB_DATA36

124

DQ36

MEM_MB_DATA37

126

DQ37

MEM_MB_DATA38

134

DQ38

MEM_MB_DATA39

136

DQ39

MEM_MB_DATA40

141

DQ40

MEM_MB_DATA41

143

DQ41

MEM_MB_DATA42

151

DQ42

MEM_MB_DATA43

153

DQ43

MEM_MB_DATA44

140

DQ44

MEM_MB_DATA45

142

DQ45

MEM_MB_DATA46

152

DQ46

MEM_MB_DATA47

154

DQ47

MEM_MB_DATA48

157

DQ48

MEM_MB_DATA49

159

DQ49

MEM_MB_DATA50

173

DQ50

MEM_MB_DATA51

175

DQ51

MEM_MB_DATA52

158

DQ52

MEM_MB_DATA53

160

DQ53

MEM_MB_DATA54

174

DQ54

MEM_MB_DATA55

176

DQ55

MEM_MB_DATA56

179

DQ56

MEM_MB_DATA57

181

DQ57

MEM_MB_DATA58

189

DQ58

MEM_MB_DATA59

191

DQ59

MEM_MB_DATA60

180

DQ60

MEM_MB_DATA61

182

DQ61

MEM_MB_DATA62

192

DQ62

MEM_MB_DATA63

194

DQ63

50

NC1

69

NC2

83

NC3

120

NC4

163

201

202

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

DDR2_SODIMM_RVS_H=9.2mm

DDR2_SODIMM_RVS_H=9.2mm

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

DDR2 SODIMMS A/B CHANNEL

DDR2 SODIMMS A/B CHANNEL

DDR2 SODIMMS A/B CHANNEL

MS-12221

MS-12221

MS-12221

MEM_MB0_CS#2 6,10

MEM_MB0_CS#3 6,10

1

945Thursday, February 01, 2007

945Thursday, February 01, 2007

945Thursday, February 01, 2007

MEM_MB_DATA[63..0] 6

1.0

1.0

1.0

of

of

of

Page 10

5

MEM_MA_ADD[15..0]6,9

D D

MEM_MA_BANK[2..0]6,9

C C

MEM_MB_ADD[15..0]6,9

B B

MEM_MB_BANK[2..0]6,9

A A

MEM_MA_ADD[15..0]

MEM_MA_BANK[2..0]

MEM_MA_CAS#6,9

MEM_MA_WE#6,9

MEM_MA_RAS#6,9

MEM_MA0_CS#06,9

MEM_MA0_CS#16,9

MEM_MA0_CS#26,9

MEM_MA0_CS#36,9

MEM_MA0_ODT06,9

MEM_MA0_ODT16,9

MEM_MA_CKE16,9

MEM_MA_CKE06,9

MEM_MB_ADD[15..0]

MEM_MB_BANK[2..0]

MEM_MB_CAS#6,9

MEM_MB_WE#6,9

MEM_MB_RAS#6,9

MEM_MB0_CS#06,9

MEM_MB0_CS#16,9

MEM_MB0_CS#26,9

MEM_MB0_CS#36,9

MEM_MB0_ODT06,9

MEM_MB0_ODT16,9

MEM_MB_CKE16,9

MEM_MB_CKE06,9

5

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CAS#

MEM_MA_WE#

MEM_MA_RAS#

MEM_MA0_CS#0

MEM_MA0_CS#1

MEM_MA0_CS#2

MEM_MA0_CS#3

MEM_MA0_ODT0

MEM_MA0_ODT1

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0 MEM_MB_ADD15

MEM_MB_CAS#

MEM_MB_WE#

MEM_MB_RAS#

MEM_MB0_CS#0

MEM_MB0_CS#1

MEM_MB0_CS#2

MEM_MB0_CS#3

MEM_MB0_ODT0

MEM_MB0_ODT1

MEM_MB_CKE1

MEM_MB_CKE0

4

MEM_MA_CKE0

MEM_MA_ADD12

MEM_MA_BANK2

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD3

MEM_MA_ADD5

MEM_MA_ADD2

MEM_MA_BANK0

MEM_MA_ADD10

MEM_MA_WE#

MEM_MA_CAS#

MEM_MA_ADD13

MEM_MA0_CS#3

MEM_MA0_ODT1

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_CKE1

MEM_MA0_CS#2

MEM_MA_ADD6

MEM_MA_ADD4

MEM_MA_ADD11

MEM_MA_ADD7

MEM_MA_RAS#

MEM_MA_BANK1

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA0_ODT0

MEM_MA0_CS#1

MEM_MA0_CS#0

MEM_MB_CKE0

MEM_MB0_CS#2

MEM_MB_BANK2

MEM_MB_ADD12

MEM_MB_ADD9

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD3

MEM_MB_ADD5

MEM_MB_ADD1

MEM_MB_BANK0

MEM_MB_WE#

MEM_MB0_CS#1

MEM_MB0_ODT1

MEM_MB_CAS#

MEM_MB_ADD11

MEM_MB_ADD14

MEM_MB_CKE1

MEM_MB_ADD0

MEM_MB_ADD2

MEM_MB_ADD6

MEM_MB_ADD4

MEM_MB0_CS#0

MEM_MB_RAS#

MEM_MB_ADD10

MEM_MB_BANK1

MEM_MB0_CS#3

MEM_MB_ADD13

MEM_MB0_ODT0

4

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

3

CPU_VTT_SUS

RN2

RN2

RN3

RN3

RN4

RN4

RN5

RN5

RN6

RN6

RN7

RN7

RN8

RN8

RN9

RN9

CPU_VTT_SUS

RN11

RN11

RN12

RN12

RN13

RN13

RN14

RN14

RN15

RN15

RN16

RN16

RN17

RN17

RN18

RN18

C93 0.1u_10V_0402C93 0.1u_10V_0402

C94 0.1u_10V_0402C94 0.1u_10V_0402

C95 0.1u_10V_0402C95 0.1u_10V_0402

C96 0.1u_10V_0402C96 0.1u_10V_0402

C97 0.1u_10V_0402C97 0.1u_10V_0402

C98 0.1u_10V_0402C98 0.1u_10V_0402

C106 0.1u_10V_0402C106 0.1u_10V_0402

C107 0.1u_10V_0402C107 0.1u_10V_0402

C108 0.1u_10V_0402C108 0.1u_10V_0402

C116 0.1u_10V_0402C116 0.1u_10V_0402

C117 0.1u_10V_0402C117 0.1u_10V_0402

C118 0.1u_10V_0402C118 0.1u_10V_0402

C119 0.1u_10V_0402C119 0.1u_10V_0402

C127 0.1u_10V_0402C127 0.1u_10V_0402

C128 0.1u_10V_0402C128 0.1u_10V_0402

C129 0.1u_10V_0402C129 0.1u_10V_0402

C144 0.1u_10V_0402C144 0.1u_10V_0402

C145 0.1u_10V_0402C145 0.1u_10V_0402

C153 0.1u_10V_0402C153 0.1u_10V_0402

C154 0.1u_10V_0402C154 0.1u_10V_0402

C155 0.1u_10V_0402C155 0.1u_10V_0402

C163 0.1u_10V_0402C163 0.1u_10V_0402

C164 0.1u_10V_0402C164 0.1u_10V_0402

C165 0.1u_10V_0402C165 0.1u_10V_0402

C173 0.1u_10V_0402C173 0.1u_10V_0402

C174 0.1u_10V_0402C174 0.1u_10V_0402

C175 0.1u_10V_0402C175 0.1u_10V_0402

C176 0.1u_10V_0402C176 0.1u_10V_0402

C181 0.1u_10V_0402C181 0.1u_10V_0402

C182 0.1u_10V_0402C182 0.1u_10V_0402

C183 0.1u_10V_0402C183 0.1u_10V_0402

C184 0.1u_10V_0402C184 0.1u_10V_0402

3

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

2

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

DDR2 SODIMMS TERMINATIONS

DDR2 SODIMMS TERMINATIONS

DDR2 SODIMMS TERMINATIONS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MS-12221

MS-12221

MS-12221

MICRO-STAR INT'L CO.,LTD.

1

1.0

1.0

1.0

10 45Thursday, February 01, 2007

10 45Thursday, February 01, 2007

10 45Thursday, February 01, 2007

of

of

1

of

Page 11

5

4

U43A

U43A

3

2

1

HT_CADOUT15_P5

D D

C C

B B

HT_CADOUT15_N5

HT_CADOUT14_P5

HT_CADOUT14_N5

HT_CADOUT13_P5

HT_CADOUT13_N5

HT_CADOUT12_P5

HT_CADOUT12_N5

HT_CADOUT11_P5

HT_CADOUT11_N5

HT_CADOUT10_P5

HT_CADOUT10_N5

HT_CADOUT9_P5

HT_CADOUT9_N5

HT_CADOUT8_P5

HT_CADOUT8_N5

HT_CADOUT7_P5

HT_CADOUT7_N5

HT_CADOUT6_P5

HT_CADOUT6_N5

HT_CADOUT5_P5

HT_CADOUT5_N5

HT_CADOUT4_P5

HT_CADOUT4_N5

HT_CADOUT3_P5

HT_CADOUT3_N5

HT_CADOUT2_P5

HT_CADOUT2_N5

HT_CADOUT1_P5

HT_CADOUT1_N5

HT_CADOUT0_P5

HT_CADOUT0_N5

HT_CLKOUT1_P5

HT_CLKOUT1_N5

HT_CLKOUT0_P5

HT_CLKOUT0_N5

HT_CTLOUT0_P5

HT_CTLOUT0_N5

HT_RXCALP

VDDHT_PKG

R48 49.9_0402R48 49.9_0402

HT_RXCALN

R19

HT_RXCAD15P

R18

HT_RXCAD15N

R21

HT_RXCAD14P

R22

HT_RXCAD14N

U22

HT_RXCAD13P

U21

HT_RXCAD13N

U18

HT_RXCAD12P

U19

HT_RXCAD12N

W19

HT_RXCAD11P

W20

HT_RXCAD11N

AC21

HT_RXCAD10P

AB22

HT_RXCAD10N

AB20

HT_RXCAD9P

AA20

HT_RXCAD9N

AA19

HT_RXCAD8P

Y19

HT_RXCAD8N

T24

HT_RXCAD7P

R25

HT_RXCAD7N

U25

HT_RXCAD6P

U24

HT_RXCAD6N

V23

HT_RXCAD5P

U23

HT_RXCAD5N

V24

HT_RXCAD4P

V25

HT_RXCAD4N

AA25

HT_RXCAD3P

AA24

HT_RXCAD3N

AB23

HT_RXCAD2P

AA23

HT_RXCAD2N

AB24

HT_RXCAD1P

AB25

HT_RXCAD1N

AC24

HT_RXCAD0P

AC25

HT_RXCAD0N

W21

HT_RXCLK1P

W22

HT_RXCLK1N

Y24

HT_RXCLK0P

W25

HT_RXCLK0N

P24

HT_RXCTLP

P25

HT_RXCTLN

A24

HT_RXCALP

C24

HT_RXCALN

ATI ( 216TQA6AVA12FG )

ATI ( 216TQA6AVA12FG )

PART 1 OF 6

PART 1 OF 6

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

P21

P22

P18

P19

M22

M21

M18

M19

L18

L19

G22

G21

J20

J21

F21

F22

N24

N25

L25

M24

K25

K24

J23

K23

G25

H24

F25

F24

E23

F23

E24

E25

L21

L22

J24

J25

N23

P23

C25

D24

HT_TXCALP

HT_TXCALN

HT_CADIN15_P 5

HT_CADIN15_N 5

HT_CADIN14_P 5

HT_CADIN14_N 5

HT_CADIN13_P 5

HT_CADIN13_N 5

HT_CADIN12_P 5

HT_CADIN12_N 5

HT_CADIN11_P 5

HT_CADIN11_N 5

HT_CADIN10_P 5

HT_CADIN10_N 5

HT_CADIN9_P 5

HT_CADIN9_N 5

HT_CADIN8_P 5

HT_CADIN8_N 5

HT_CADIN7_P 5

HT_CADIN7_N 5

HT_CADIN6_P 5

HT_CADIN6_N 5

HT_CADIN5_P 5

HT_CADIN5_N 5

HT_CADIN4_P 5

HT_CADIN4_N 5

HT_CADIN3_P 5

HT_CADIN3_N 5

HT_CADIN2_P 5

HT_CADIN2_N 5

HT_CADIN1_P 5

HT_CADIN1_N 5

HT_CADIN0_P 5

HT_CADIN0_N 5

HT_CLKIN1_P 5

HT_CLKIN1_N 5

HT_CLKIN0_P 5

HT_CLKIN0_N 5

HT_CTLIN0_P 5

HT_CTLIN0_N 5

R47 100_0402R47 100_0402R46 49.9_0402R46 49.9_0402

A A

Title

Title

Title

RS690T HT LINK I/F

RS690T HT LINK I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

RS690T HT LINK I/F

A

A

A

MS-12221

MS-12221

MS-12221

2

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

11 45Thursday, February 01, 2007

11 45Thursday, February 01, 2007

11 45Thursday, February 01, 2007

of

of

of

1

1.0

1.0

1.0

Page 12

5

4

3

2

1

Errata PA_IGPGENF5

715_0402

715_0402

715_0402

715_0402

715_0402

715_0402

715_0402

715_0402

715_0402

D D

U43B

U43B

G5

GFX_RX0P

G4

GFX_RX0N

J8

GFX_RX1P

J7

GFX_RX1N

J4

GFX_RX2P

J5

GFX_RX2N

L8

GFX_RX3P

L7