5

4

3

2

1

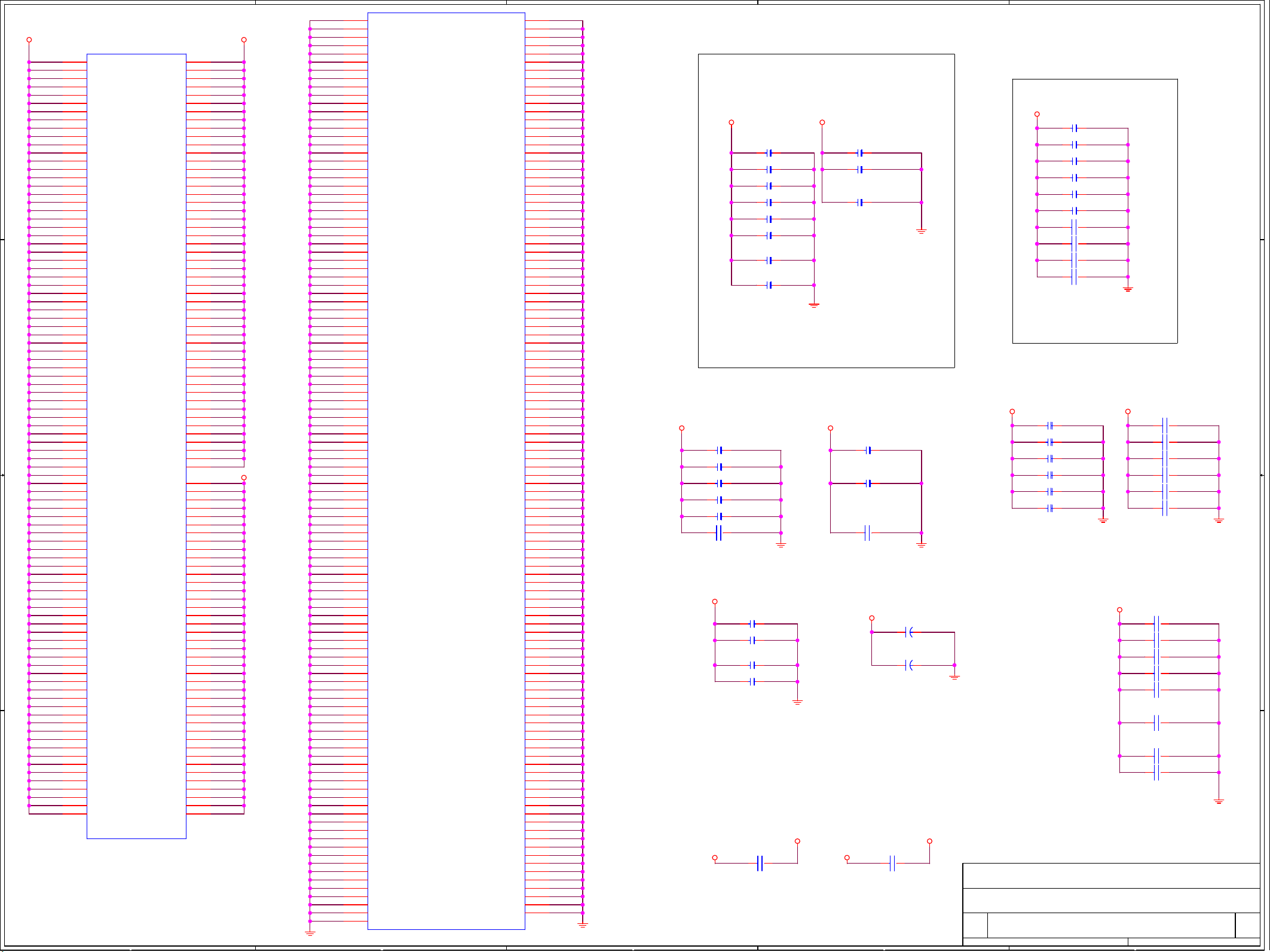

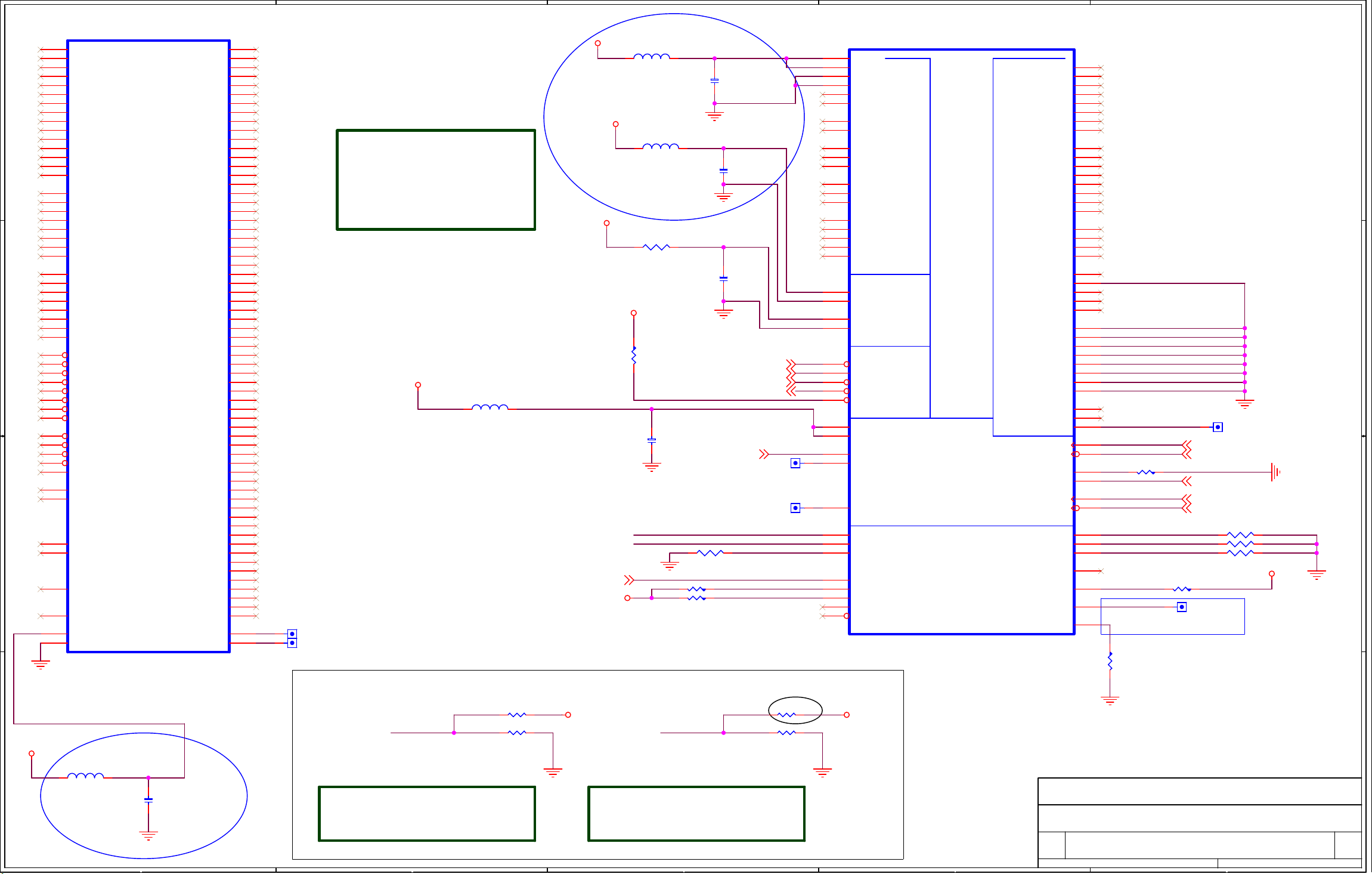

MSI

MS-1039 Ver:0B

D D

DDR 333/400

GDDR3

16MX32bit*4PCS

15~16

AMD K8 Socket 754

3~6

HT

8

7

DDR SODIMM * 2

Clock Generator

17

LCD

LVDS

32

VGA

C C

DVI

32

TV OUT

32

RGB

ATI M56-P

12~14

PCIE

North Bridge

ATI RX480

9~11

PCIE

PCIE

NEW CARD (PCI-E/USB PCI-E)

26

LAN

RTL8111B

30

Mini PCI

CAMEARA(USBX1)

31

Socket

29

Oz711MP

CARDBUS

CARDREADER

USB 2.0 x4

31

USB

PCI

1394a

27 28

South Bridge

SATA HD

33

B B

CD-ROM

33

SATA

SIDE

ATI SB450

18~22

LPC

KBC

ENE3910

23

X-BUS

BIOS

23

FANX1

26

MDC

31

AZALIA

Keyboard

23

AUDIO CODEC

Internal MIC

25

A A

MIC IN

25

ALC882

24

Audio Amp

FAN7031

25

Touch PAD

23

Speaker

25

LINE IN

25

HP & SPDIF

25

5

4

3

2

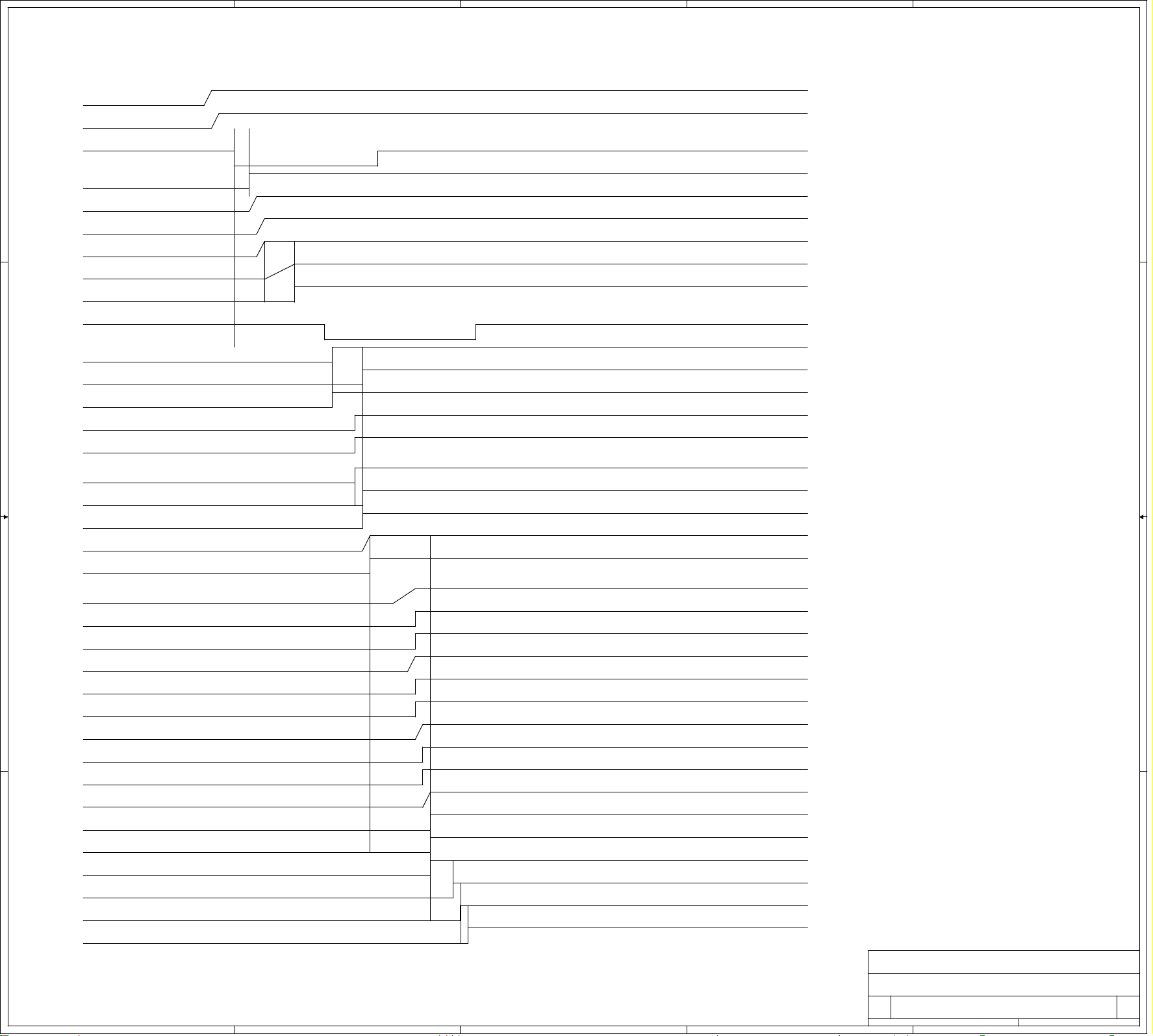

Title

BLOCK DIAGRAM

Size Document Number Rev

C

Date: Sheet of

MSI CORPORATION

MS-1039

1

1 46Tuesday, November 29, 2005

0.A

5

4

3

2

1

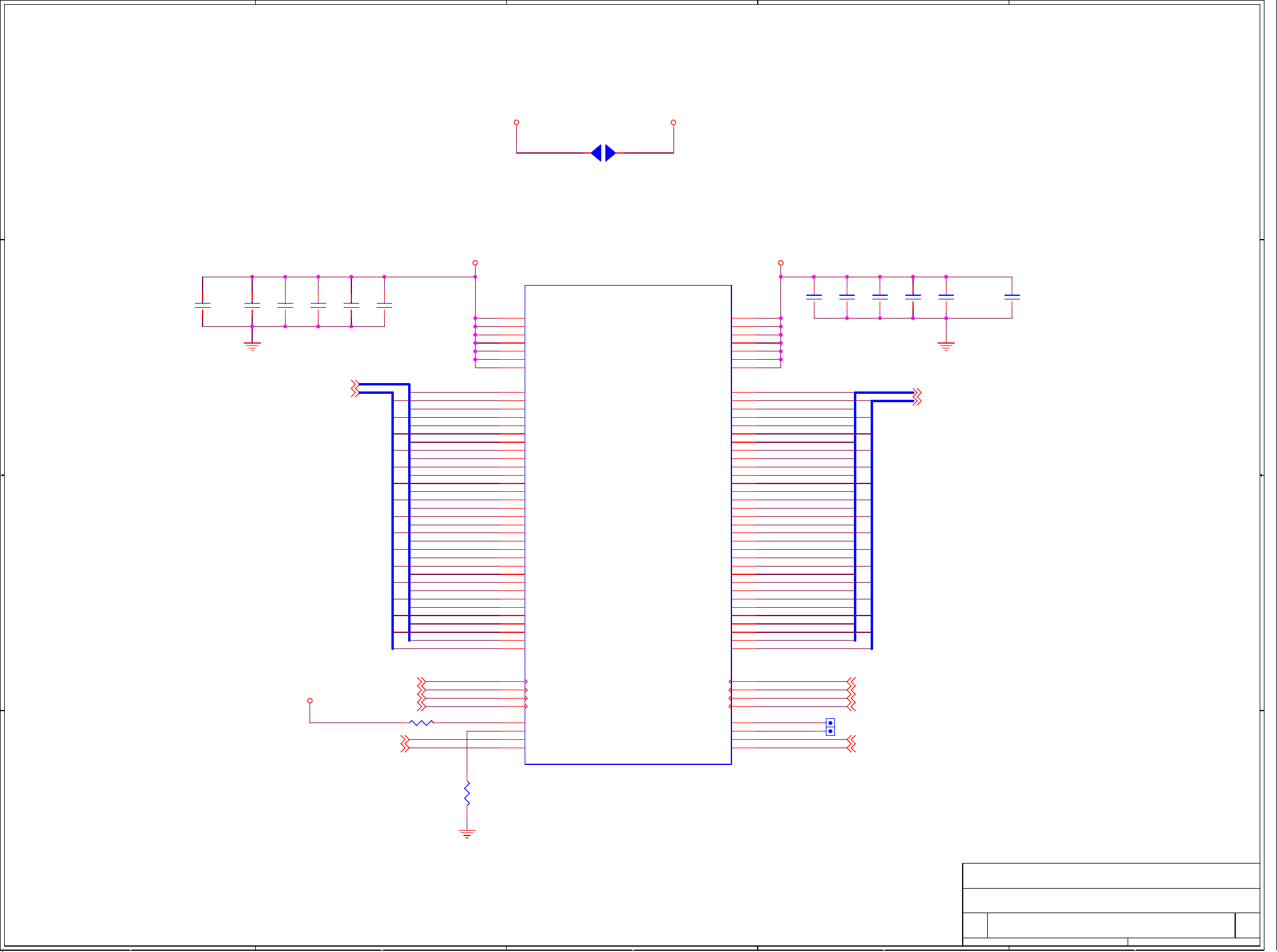

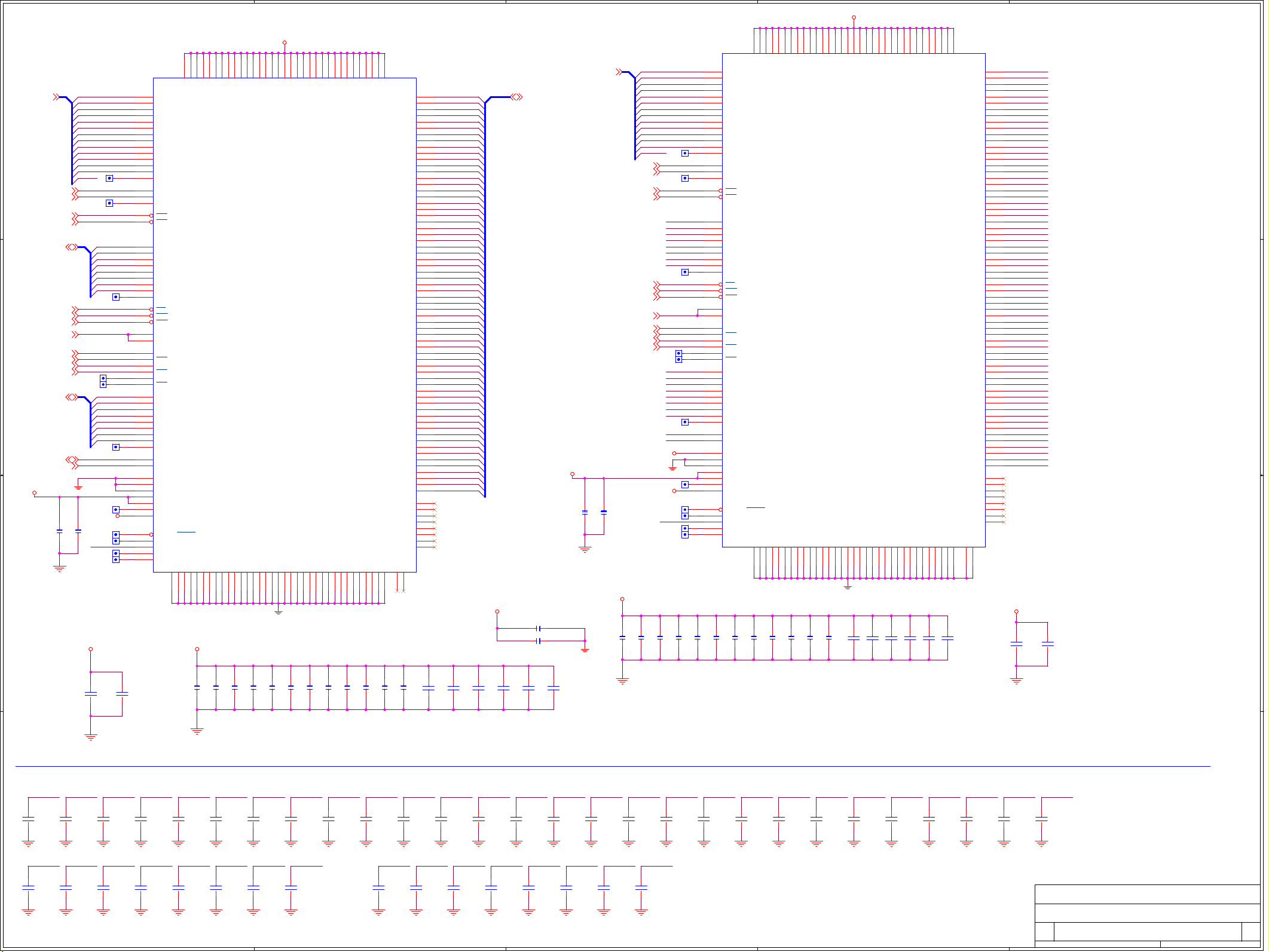

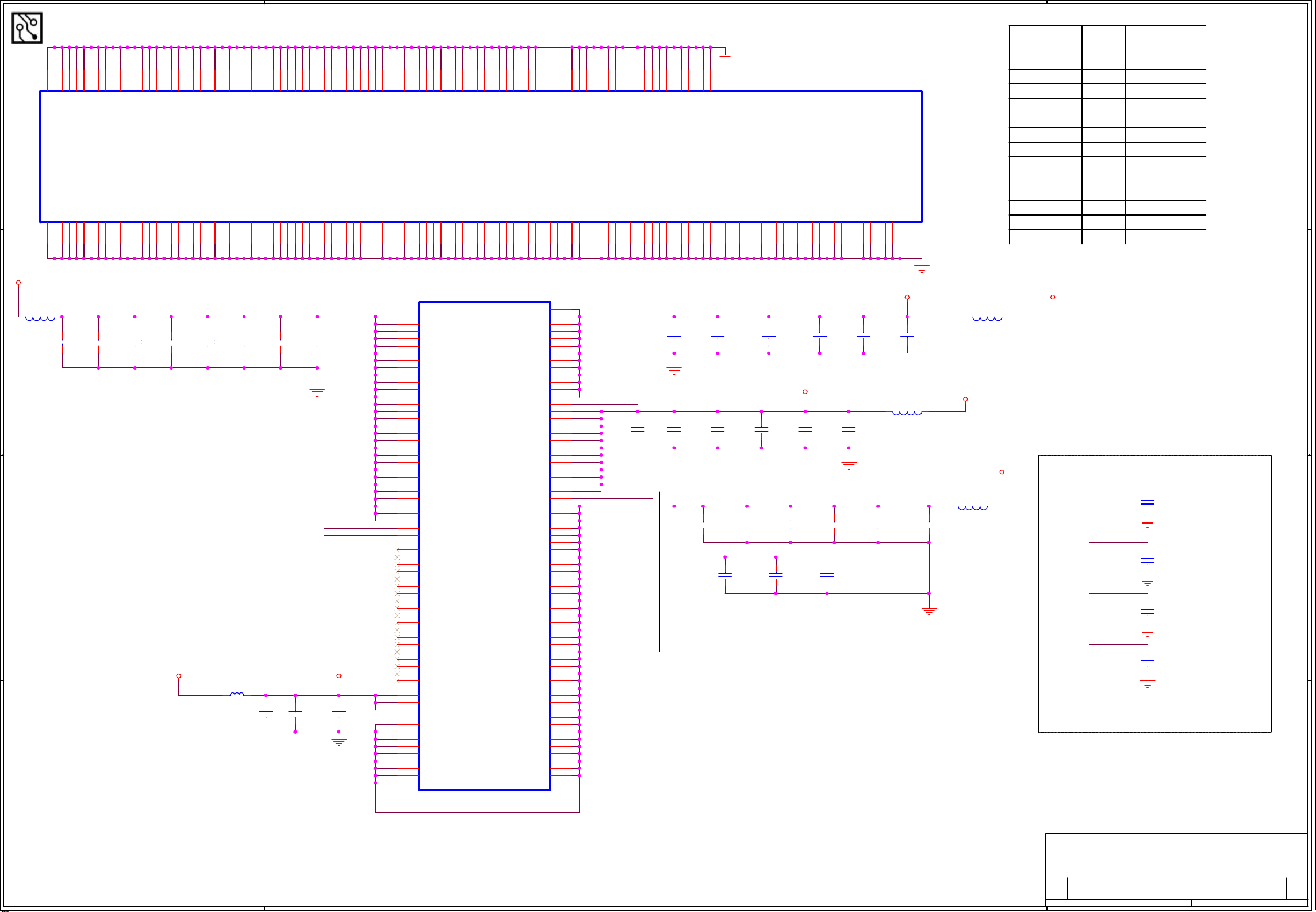

MS-1039 System Power on Sequency From PC Mode

PWR_SRC

+3VALW/+5VALW

D D

PWRBTN#(TO EC) T>10mS

SUS_ON(FROM EC)

+3VSUS/+5VSUS

+1.8VSUS/+1.2VSUS

+2_5VSUS

T>20mS

+1.8VSUS_PG

SUSPWROK

PWRBTN_SB#(TO EC)

S5_DELAY(FORM EC)

delay 100 ms by EC

T=8mS

PM_SLP_S5#(TO EC)

C C

PM_SLP_S3#(TO EC)

RUN_ON(FROM EC)

+5VRUN

M56_CORE

T>1mS

RUND/+3VRUN/+1.2VRUN/+1.8VRUN

VDDIO/VTT_EN

VDDIO/VTT_PG

+2.5VRUN

VGA_PG

PWOER_OK

B B

VDDA_EN

+VDDA

VDDA_PG

VDD_EN

V_CORE

VDD_PG

VLDT_EN

+VLDT

VLDT_PG

NB_PWRGO

SB_PWRGO

CPU_PWRGD(FROM SB)

A A

A,PCIRST#(FROM SB)

T>15mS

T>33mS

T>48mS

T>51mS

T>2mS

CPURST#(FROM SB)

MSI CORPORATION

Title

POWER SEQUENCE

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

MS-1039

2 46Tuesday, November 29, 2005

1

0.A

A

B

C

D

E

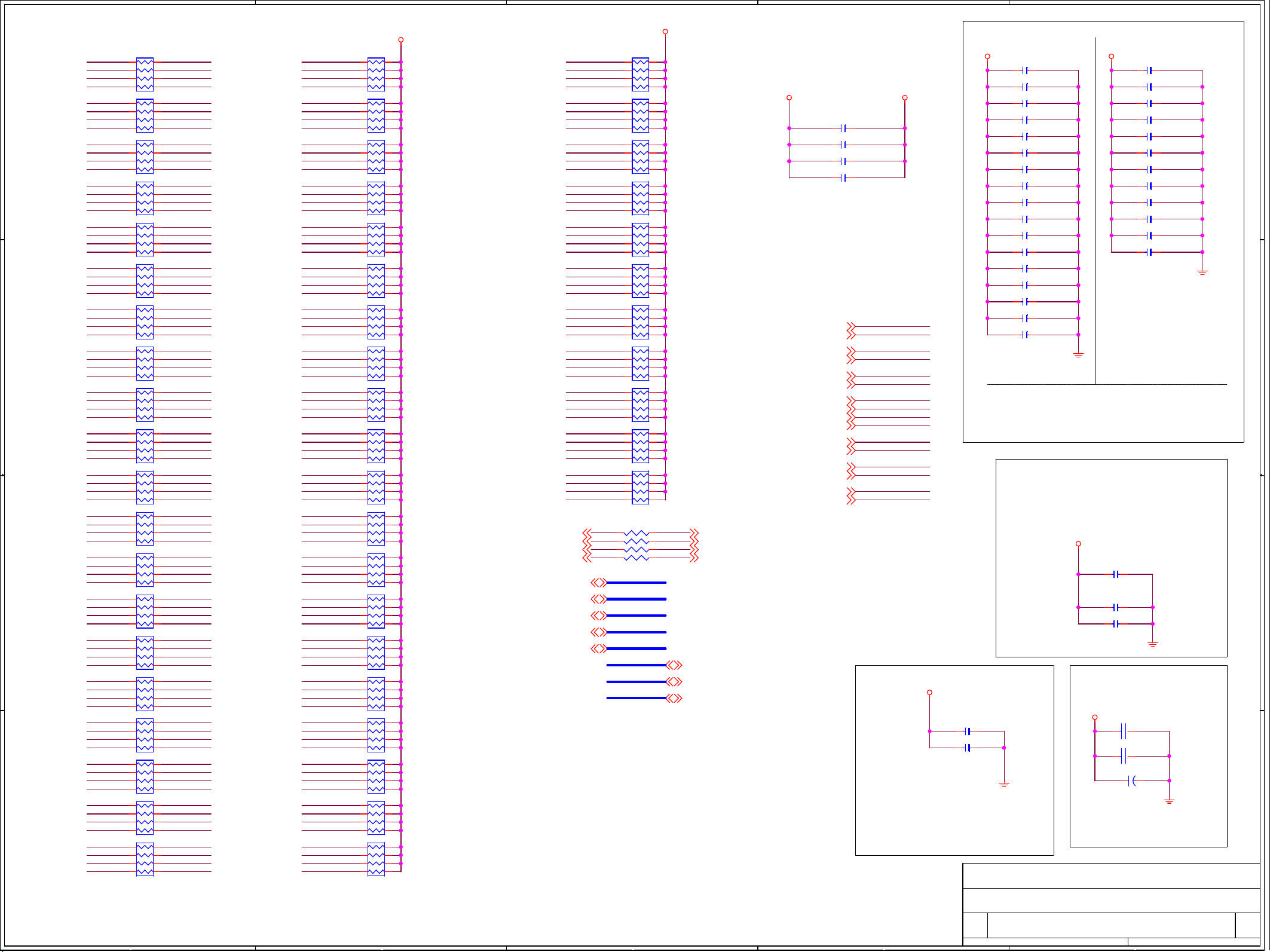

Clawhammer HT Interface

LAYOUT: Place HT bypass caps on topside

near unconnected Clawhammer HT Link

4 4

G6

2 1

+VLDT_OUT+VLDT

VLDT Power Decoupling

VLDT Plane Rout with 250 mil trace or a plane

VLDT plane In CPU pins rout >100 mil

AH29

AH27

AG28

AG26

AF29

AE28

AF25

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

+VLDT_OUT+VLDT

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

0.1UF_0402

C395

C383

0.1UF_0402 C827

C389

0.1UF_0402

0.1UF_0402

C382

HT_CADOUT_H[15:0] 9

HT_CADOUT_L[15:0] 9

C385

47UF_1206

47UF_1206

0.1UF_0402

0.1UF_0402

U2A

C397

C384

C396

C828

47UF_1206

3 3

2 2

C381

47UF_1206

0.1UF_0402

HT_CADIN_H[15:0]9

HT_CADIN_L[15:0]9

0.1UF_0402

C386

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

VLDT_A6

VLDT_A5

VLDT_A4

VLDT_A3

VLDT_A2

VLDT_A1

VLDT_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

J26

J27

J29

K29

N25

P25

P28

P27

CTLOP1

CTLON1

HT_CLKOUT_H1 9

HT_CLKOUT_L1 9

HT_CLKOUT_H0 9

HT_CLKOUT_L0 9

TP53

TP52

HT_CTLOUT_H0 9

HT_CTLOUT_L0 9

+VLDT

CTLIP1

CTLIN1

Y25

W25

Y27

Y28

R27

R26

T29

R29

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

HT_CLKIN_H19

HT_CLKIN_L19

HT_CLKIN_H09

HT_CLKIN_L09

R201 49.9R1%0402

HT_CTLIN_H09

HT_CTLIN_L09

ZIF_SOCKET754

R200

49.9R1%0402

1 1

MSI CORPORATION

Title

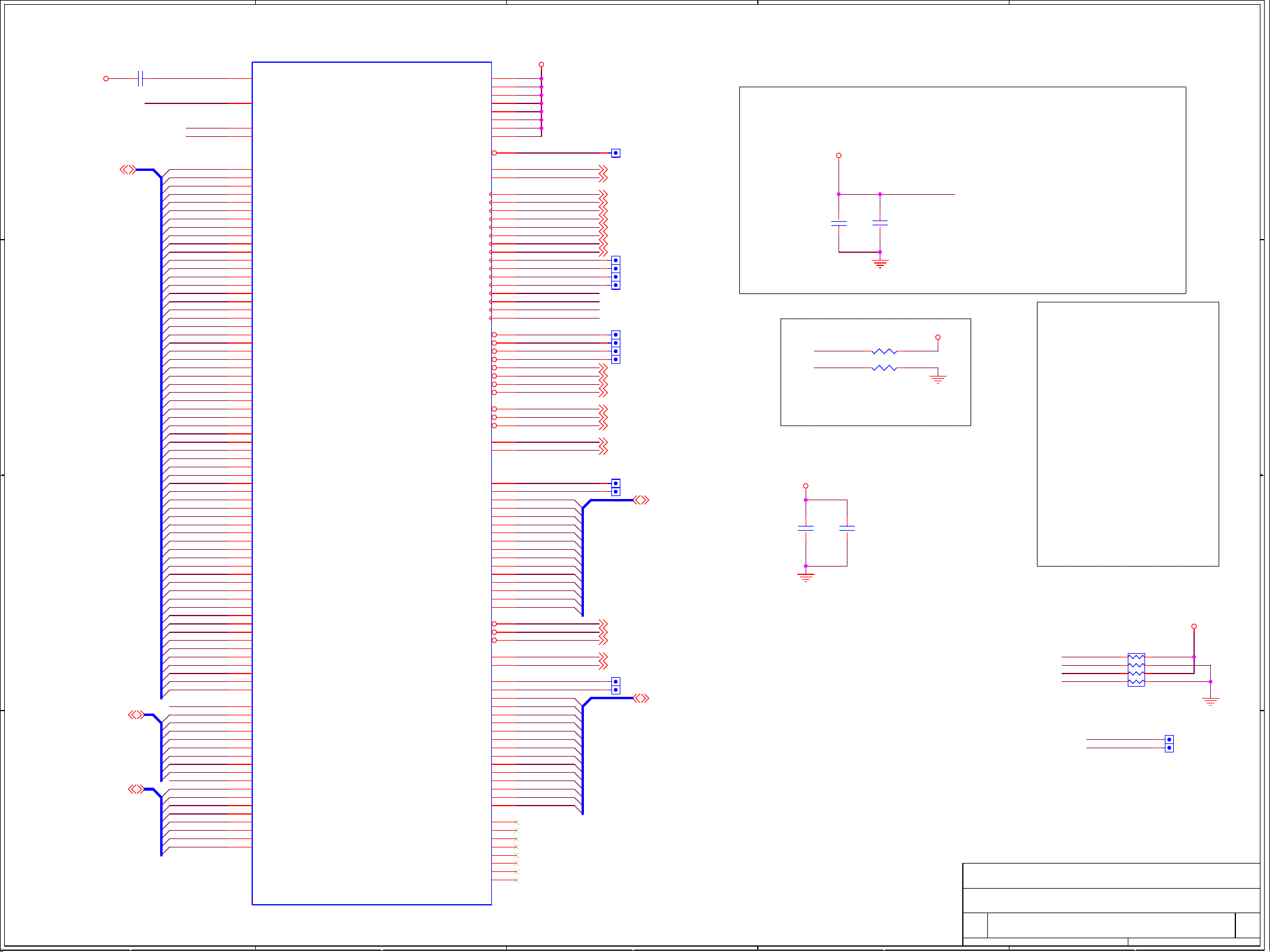

CPU SocketA (Host)

Size Document Number Rev

C

A

B

C

D

Date: Sheet of

MS-1039

3 46Thursday, December 01, 2005

E

0.A

A

B

C

D

E

Clawhammer DDR Interface

SMDDR_VREF

DDRVREF_CPU

C447

1000PF_0402

MEMZN

MEMZP

MEMZN,MEMZP with

5/10,<1000 mils

+VTT

C435

FOR EMI

C452

0.1UF_0402

+VDDIO

R222 34.8_1%

R221 34.8_1%

C423

0.1UF_0402

D

Title

CPU SocketA (DDR Interface)

Size Document Number Rev

Custom

Date: Sheet of

MS-1039

DDRVREF with

40~50 mil, 25

mil clearance

or shielded by

GND

0.1 UF, 0603, X7R

1000 PF, 0603, X7R

Near Socket

Routing

in the top layer

MEMDATA[63:0] with 5/15

MEMDQS[8:0] with 5/20

in the bottom layer

MEMADDA[13:0] with 5/15

MA COMMAND with 5/15

MEMCLK_H/L are routed

20/5/5/5/20 trace

width/spacing., 20 mil

spacing

Rout DDR nets 50 mil

sapcing to their own

net

+VDDIO

DM8

DQS8

1 2

3 4

5 6

7 8

RN1

10K_8P4R_0402

TP84

TP83

DCLK1DCLK1+

DCLK0DCLK0+

MSI CORPORATION

4 46Thursday, December 01, 2005

E

0.A

1000PF_0402_NC

+VTT

4 4

MD[63:0]8

3 3

2 2

DM[7:0]8

DQS[7:0]8

1 1

C442

A

SNS_+1.25VTT

DDRVREF_CPU

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

DM8

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

DQS8

DQS7

DQS6

DQS5

DQS4

DQS3

DQS2

DQS1

DQS0

AE13

AG12

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

B9

C7

A6

C11

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

G3

M1

W1

W3

AC1

AC3

W2

Y1

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

R1

A13

A7

C2

H1

AA1

AG1

AH7

AH13

T1

A14

A8

D1

AB1

AJ2

AJ8

AJ13

L3

L1

J2

L2

J1

U2B

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

ZIF_SOCKET754

RSVD_MEMADDA15

RSVD_MEMADDA14

RSVD_MEMADDB_B15

RSVD_MEMADDB_B14

B

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB_B13

MEMADDB_B12

MEMADDB_B11

MEMADDB_B10

MEMADDB_B9

MEMADDB_B8

MEMADDB_B7

MEMADDB_B6

MEMADDB_B5

MEMADDB_B4

MEMADDB_B3

MEMADDB_B2

MEMADDB_B1

MEMADDB_B0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

+VTT

MEMRST#

DCLK7+

DCLK7DCLK6+

DCLK6DCLK5+

DCLK5DCLK4+

DCLK4DCLK3+

DCLK3DCLK2+

DCLK2DCLK1+

DCLK1DCLK0+

DCLK0-

CS7#

CS6#

CS5#

CS4#

CS3#

CS2#

CS1#

CS0#

MA15

MA14

MA13

MA12

MA11

MA10

MA9

MA8

MA7

MA6

MA5

MA4

MA3

MA2

MA1

MA0

MB15

MB14

MB13

MB12

MB11

MB10

MB9

MB8

MB7

MB6

MB5

MB4

MB3

MB2

MB1

MB0

TP74

CKE0 7,8

CKE1 7,8

DCLK7+ 7,8

DCLK7- 7,8

DCLK6+ 7,8

DCLK6- 7,8

DCLK5+ 7,8

DCLK5- 7,8

DCLK4+ 7,8

DCLK4- 7,8

TP82

TP81

TP79

TP80

TP76

TP77

TP75

TP78

CS3# 7,8

CS2# 7,8

CS1# 7,8

CS0# 7,8

SRASA# 7,8

SCASA# 7,8

SWEA# 7,8

MEMBAA1 7,8

MEMBAA0 7,8

TP65

TP68

MA[13:0] 7,8

SRASB# 7,8

SCASB# 7,8

SWEB# 7,8

MEMBAB1 7,8

MEMBAB0 7,8

TP69

TP66

MB[13:0] 7,8

C

0.1UF_0402

A

B

C

D

E

+VDDA

4 4

Near CPU in 0.5" .

C419

3900PF

R207

169_1%

3900PF

CPUCLK0_H17

CPUCLK0_L17

C414

Rout 5/5/5 mil,

Long:<500 mils and

Max current 300 mA

L44 180nH/1210

CPUCK+

CPUCK-

+VLDT_OUT

Place near CPU in 1" , Routed

=> 5:10/Trace:Space , Same

Length

Long:500~750mil

R203 44.2_1%

R8 44.2_1%

C405

10UF_0805

C8

1000PF_0402

20 mils spacing

3 3

+3VALW

SMB_THRMCPU_CLK

SMB_THRMCPU_DATA

CPU_THRM_ALERTT_CRIT_CPU#

2 2

RN54

1 2

3 4

5 6

7 8

10K_8P4R_0402

+3VSUS

V_CORE

+VDDIO

+3VALW

1000PF_0402_NC

C406

1000PF_0402_NC

C475

CORE_SENSE

SNS_+2.5VDIMM

+VTT

Width:50mil and Long:500milWidth:50mil and

1000PF_0402

C394

1000PF_0402

+VDDIO

+2.5VRUN

11/16

C393

COREFB+37

COREFB-37

TP71

TP67

R205 820

R206 820

TP55

TP54

TP62

TP63

TP59

TP61

TP58

TP57

R27 1K_0402

R23 1K_0402

C392

0.1UF_0402

CORE_SENSE

SNS_+2.5VDIMM

CPURST#

CPU_PWRGD

HTSTOP#

COREFB+

COREFB-

VDDIOFB+

VDDIOFB-

CPUCK+

CPUCK-

BPSCLK+

BPSCLK-

PLLCHRZ+

PLLCHRZ-

DBRDY

DCLKTWO

TMS

TCK

TRST#

TDI

NC_C18

NC_A19

AH25

AJ25

AF20

AE18

AJ27

AF27

AE26

A23

A24

B23

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

C16

AG15

AH17

C15

E20

E17

B21

A21

C18

A19

A28

AJ28

U2C

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC

NC

NC

NC

VTT_A5

VTT_B5

DBRDY

NC

TMS

TCK

TRST_L

TDI

NC

NC

KEY1

KEY0

Clawhammer Control and Debug

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC

NC

NC

NC

G_FBCLKOUT_H

G_FBCLKOUT_L

DBREQ_L

NC

NC

NC

NC

NC

TDO

NC

A20

A26

A27

AG13

AF14

AG14

AF15

AE15

AG18

AH18

AG17

AJ18

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

AF18

THERMDA

THERMDC

FBCLKOUT+

TDO

THERMTRIP#

VID4

VID3

VID2

VID1

VID0

NC_AG17

NC_AJ18

FBCLKOUT-

DBREQ#

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

VID4 37

VID3 37

VID2 37

VID1 37

VID0 37

R211 80.6_1%

Zdiff = 80 ohm

TP60

+VDDIO

TP56

LAYOUT: Route

FBCLKOUT_H/L differentially

with 20/8/5/8/20 spacing and

trace width. ( In CPU

breakout => routed 5:5:5 )

AE23

Cap close to

thermal

sensor

T_CRIT_CPU#34

1 1

LDT_RST#20

SB_CPUPWRGD20

LDTSTOP#10,20 H_THERMTRIP# 18

THERMDA

C391

1000PF_0402

0_0402_NC

R204

11/18

R209

A

0.1UF_0402

0_0402

0_0402R213

0_0402R199

0_0402R372

C420

CPURST#

CPU_PWRGD

HTSTOP#

U20

SMBCLKVDD

2

D+

3

D-

4

T_CRIT_A#

LM86_MSOP8

SMBDATA

ALERT#

GND

Close to CPU socket

RS480M_RST# 10NB_RST#20

SMB_THRMCPU_CLK

81

SMB_THRMCPU_DATA

7

6

5

+2.5VRUN

R526

1K_0402

THERMTRIP#

B

SMB_THRMCPU_CLK 23

SMB_THRMCPU_DATA 23

CPU_THRM_ALERT- 23

+2.5VRUN

R19

1K_0402

B

E C

Q39

MMBT3904

+3VSUS

R22

10K_0402

C

AF23

AF22

AF21

C1

R3

AA2

D3

AG2

B18

AH1

AE21

C20

AG4

C6

AG6

AE9

AG9

J3

NC

NC

NC

NC

FREE29

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

FREE13

FREE14

FREE40

ZIF_SOCKET754

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

D

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

NC_AJ18THERMDC

NC_AG17

NC_C21

NC_D20

NC_D18

NC_C19

NC_B19

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R26 1K_0402

RN55

1K_8P4R_0402

RN53

1K_8P4R_0402

MSI CORPORATION

Title

CPU SocketA (Control and Debug)

Size Document Number Rev

B

Date: Sheet of

MS-1039

E

5 46Thursday, December 01, 2005

0.A

A

V_CORE +VDDIO

U2D

L7

VDD1

AC15

VDD2

H18

VDD3

B20

VDD4

E21

VDD5

H22

VDD6

J23

VDD7

H24

4 4

3 3

2 2

1 1

F26

N7

V10

G13

K14

Y14

AB14

G15

J15

AA15

H16

K16

Y16

AB16

G17

J17

AA17

AC17

AE17

F18

K18

Y18

AB18

AD18

AG19

E19

G19

AC19

AA19

J19

F20

H20

K20

M20

P20

T20

V20

Y20

AB20

AD20

G21

J21

L21

N21

R21

U21

W21

AA21

AC21

F22

K22

M22

P22

T22

V22

Y22

AB22

AD22

E23

G23

L23

N23

R23

U23

W23

AA23

AC23

B24

D24

F24

K24

M24

P24

T24

V24

Y24

AB24

AD24

AH24

AE25

K26

P26

V26

L9

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

ZIF_SOCKET754

A

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD96

VDD97

VDD98

VDD99

VDD93

VDD94

VDD95

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

V_CORE

AH20

AB21

AG25

AG27

AA10

AE16

AA20

AC20

AE20

AG20

AJ20

AD21

AG21

AG29

AA22

AC22

AG22

AH22

AJ22

AB23

AD23

AG23

AA24

AC24

AG24

AJ24

AD26

AF26

AH26

AB17

AD17

AA18

AC18

AB19

AD19

AF19

U2E

B2

VSS1

VSS3

VSS4

W22

VSS5

M23

VSS6

L24

VSS7

VSS8

VSS9

D2

VSS10

AF2

VSS11

W6

VSS12

Y7

VSS13

AA8

VSS14

AB9

VSS15

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

VSS20

J18

VSS21

G20

VSS22

R20

VSS23

U20

VSS24

W20

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

D21

VSS31

F21

VSS32

H21

VSS33

K21

VSS34

M21

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

VSS40

VSS41

B22

VSS42

E22

VSS43

G22

VSS44

J22

VSS45

L22

VSS46

N22

VSS47

R22

VSS48

U22

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

D23

VSS56

F23

VSS57

H23

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

VSS64

VSS65

VSS66

E24

VSS67

G24

VSS68

J24

VSS69

N24

VSS70

R24

VSS71

U24

VSS72

W24

VSS73

VSS74

VSS75

VSS76

VSS77

B25

VSS78

C25

VSS79

B26

VSS80

D26

VSS81

H26

VSS82

M26

VSS83

T26

VSS84

Y26

VSS85

VSS86

VSS87

VSS88

C27

VSS89

B28

VSS90

D28

VSS91

G28

VSS92

F15

VSS187

H15

VSS188

VSS206

VSS207

B16

VSS208

G18

VSS209

VSS210

VSS211

D19

VSS212

F19

VSS213

H19

VSS214

K19

VSS215

Y19

VSS216

VSS217

VSS218

VSS219

J20

VSS220

L20

VSS221

N20

VSS222

ZIF_SOCKET754

B

L28

VSS93

R28

VSS94

W28

VSS95

AC28

VSS96

AF28

VSS97

AH28

VSS98

C29

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

B

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

C

D

E

Clawhammer Power and Ground Connections

EMI

V_CORE

6.8PF_0402C402

6.8PF_0402C390

6.8PF_0402C418

6.8PF_0402C408

6.8PF_0402C388

6.8PF_0402C411

6.8PF_0402C403

V_CORE

1000PF_0402C4576.8PF_0402C387

1000PF_0402C448

1000PF_0402C470

backside

+VDDIO +VDDIO

V_CORE V_CORE

C461 0.1UF_0402

C436 0.1UF_0402

C489 0.1UF_0402

C416 0.1UF_0402

C440 0.1UF_0402

C437 10UF_0805

+VDDIO

C488 0.1UF_0402

C500 0.1UF_0402

C501 0.1UF_0402

C459 0.1UF_0402

C415 0.1UF_0402

C401 0.1UF_0402

C454 10UF_0805

+VDDIO

C73 220UF/6.3V

C74 220UF/6.3V

Near

DIMM

Place these decoupling capacitors on solder

layer of processor

V_CORE V_CORE

+VDDIO

EMIC57

0.1UF_0402

+3VRUN

EMIC58

0.1UF_0402

Title

CPU SocketA (CPU_POWER)

Size Document Number Rev

Custom

C

D

Date: Sheet of

V_CORE

C24 0.1UF_0402

C23 0.1UF_0402

C22 0.1UF_0402

C15 0.1UF_0402

C16 0.1UF_0402

C17 0.1UF_0402

C25 10UF_0805

C20 10UF_0805

C19 10UF_0805

C13 10UF_0805

Place these capacitors in

uPGA socket cavity

C493 0.1UF_0402

C509 0.1UF_0402

C492 0.1UF_0402

C496 0.1UF_0402

C443 0.1UF_0402

C425 0.1UF_0402

Near

Socket

Close

to

socket

C624 10UF_0805

C516 10UF_0805

C513 10UF_0805

C503 10UF_0805

C464 10UF_0805

C622 10UF_0805

2 Near

DIMM; 4

Near Socket

V_CORE

C450 10UF_0805

C446 10UF_0805

C439 10UF_0805

C413 10UF_0805

C407 10UF_0805

C431 10UF_0805

C460 10UF_0805

C412 10UF_0805

Place these capacitors near socket

MSI CORPORATION

MS-1039

E

0.A

6 46Thursday, December 01, 2005

A

B

C

D

E

+VDDIO

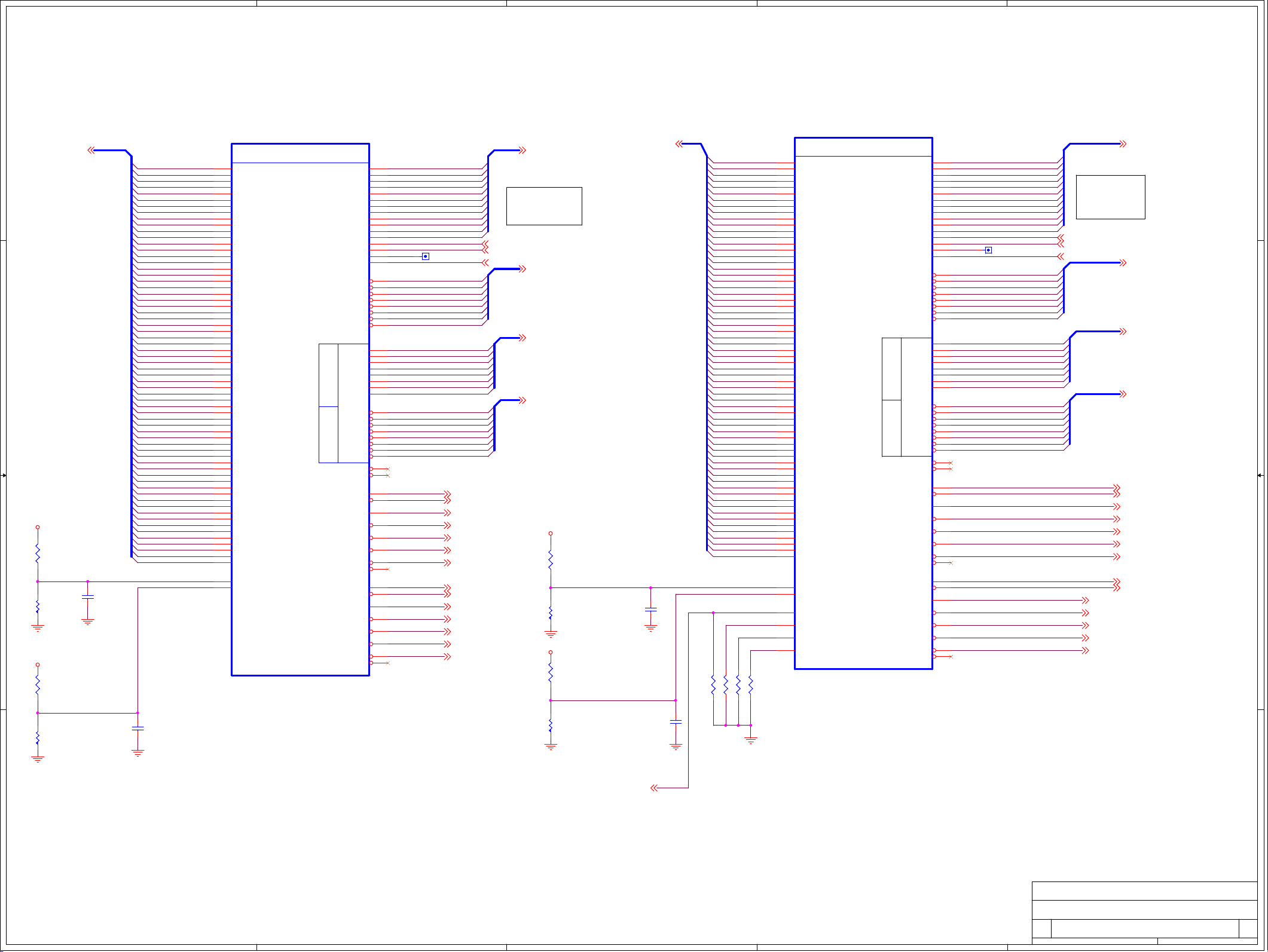

Unbuffered DDR333 SODIMM Sockets

+VDDIO

DIMM1

VDD

GND

192

132

144

156

168

180

VDD

VDD

VDD

VDD

VDD

VDDQ

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

GND

GND

GND

GND

GND

GND

GND

GND

138

150

162

174

126

186

201

202

MD_0

5

MD_1

7

MD_2

13

MD_3

17

MD_4

6

MD_5

8

MD_6

14

MD_7

18

MD_8

19

MD_9

23

MD_10

29

MD_11

31

MD_12

20

MD_13

24

MD_14

30

MD_15

32

MD_16

41

MD_17

43

MD_18

49

MD_19

53

MD_20

42

MD_21

44

MD_22

50

MD_23

54

MD_24

55

MD_25

59

MD_26

65

MD_27

67

MD_28

56

MD_29

60

MD_30

66

MD_31

68

MD_32

127

MD_33

129

MD_34

135

MD_35

139

MD_36

128

MD_37

130

MD_38

136

MD_39

140

MD_40

141

MD_41

145

MD_42

151

MD_43

153

MD_44

142

MD_45

146

MD_46

152

MD_47

154

MD_48

163

MD_49

165

MD_50

171

MD_51

175

MD_52

164

MD_53

166

MD_54

172

MD_55

176

MD_56

177

MD_57

181

MD_58

187

MD_59

189

MD_60

178

MD_61

182

MD_62

188

MD_63

190

71

73

79

83

72

74

80

84

AMP_DDR-SO-DIMM-REVERSE

MD_[63:0] 8

0.1UF_0402

SMDDR_VREF

C677

1000PF_0402

MB[13:0]4,8

C747

+VDDIO

921334557698193113

MA13

MEMBAA0

MEMBAA1

TP130

TP131

TP7

TP8

TP121

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

DM_0

DM_1

DM_2

DM_3

DM_4

DM_5

DM_6

DM_7

SWEA#

SCASA#

SRASA#

CKE0

DCLK5+

DCLK5DCLK7+

DCLK7-

DQS_0

DQS_1

DQS_2

DQS_3

DQS_4

DQS_5

DQS_6

DQS_7

MA[13:0]4,8

4 4

MEMBAA04,8

MEMBAA14,8

CS0#4,8

CS1#4,8

DM_[7:0]8

SWEA#4,8

SCASA#4,8

SRASA#4,8

CKE04,8

3 3

DCLK5+4,8

DCLK5-4,8

DCLK7+4,8

DCLK7-4,8

DQS_[7:0]8

SMB_DATA17,18,26

SMB_CLK17,18,26

SMDDR_VREF

TP119

C604

+VDDIO

TP5

MA13

TP132

TP128

C613

0.1UF_0402

1000PF_0402

2 2

TP6

SMB_DATA

SMB_CLK

TP129

112

111

110

109

108

107

106

105

102

101

115

100

117

116

121

122

134

148

170

184

119

120

118

160

158

133

147

169

183

193

195

194

196

198

199

197

123

124

200

99

97

98

12

26

48

62

78

96

95

35

37

89

91

11

25

47

61

77

1

2

86

85

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VREF

VDDID

VDDSPD

NC//DU/RESET

NC/DU

NC/DU

NC/DU

NC/DU

GND

GND

3

203

204

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

15273951637587

VDDQ

GND

VDDQ

VDDQ

GND

GND

103

131

VDDQ

VDDQ

GND

GND

125

143

VDDQ

GND

137

155

VDDQ

GND

149

157

159

167

VDDQ

VDDQ

GND

GND

161

179

173

1911022343646587082

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

VDD

GND

VDDQ

GND

GND

GND

1854162838405264768890

9294114

VDD

VDD

GND

GND

VDD

GND

104

MB0

MB1

MB2

MB3

MB4

MB5

MB6

MB7

MB8

MB9

MB10

MB11

MB12

MB13

MEMBAB04,8

MEMBAB14,8

SWEB#4,8

SCASB#4,8

SRASB#4,8

MEMBAB0

MEMBAB1

TP142

CS2#4,8

CS3#4,8

DM_0

DM_1

DM_2

DM_3

DM_4

DM_5

DM_6

DM_7

TP140

SWEB#

SCASB#

SRASB#

CKE1

CKE14,8

DCLK4+4,8

DCLK4-4,8

DCLK6+4,8

DCLK6-4,8

TP137

TP134

TP136

+VDDIO

TP133

+VDDIO

TP141

TP138

MB13

TP143

TP139

TP135

DQS_0

DQS_1

DQS_2

DQS_3

DQS_4

DQS_5

DQS_6

DQS_7

SMB_DATA

SMB_CLK

112

111

110

109

108

107

106

105

102

101

115

100

117

116

121

122

134

148

170

184

119

120

118

160

158

133

147

169

183

193

195

194

196

198

199

197

123

124

200

99

97

98

12

26

48

62

78

96

95

35

37

89

91

11

25

47

61

77

1

2

86

85

921334557698193113

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VREF

VDDID

VDDSPD

NC//DU/RESET

NC/DU

NC/DU

NC/DU

NC/DU

3

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

15273951637587

VDDQ

VDDQ

GND

GND

VDDQ

GND

103

SMDDR_VREF

+VDDIO

C626

22UF_1206

C687

22UF_1206

+VDDIO

0.1UF_0402

C620

C628

C682

C668

C681

C684

C667

C662

C740

C735

C676

C738

C599 4.7U/10V_0805

C663 0.1UF_0402

Place these two decoupling caps near DIMMs

C741

1000PF_0402

1000PF_0402

C739

C627

1000PF_0402

1000PF_0402

C691

C742

1000PF_0402

1000PF_0402

C737

C683

0.1UF_0402

C618

0.1UF_0402

C743

0.1UF_0402

C686

0.1UF_0402

C678

0.1UF_0402

C736

0.1UF_0402

C661

0.1UF_0402

C665

C685

0.1UF_0402

0.1UF_0402

C631

0.1UF_0402

131

143

VDDQ

VDDQ

VDDQ

GND

GND

GND

125

137

C666

0.1UF_0402

179

155

157

167

1911022343646587082

VDD

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

149

159

161

173

1854162838405264768890

C633

C629

47PF_0402

0.1UF_0402

VDD

VDD

VDD

GND

GND

GND

47PF_0402

C625

VDD

VDD

VDD

GND

GND

GND

47PF_0402

9294114

VDD

VDD

VDD

GND

GND

GND

47PF_0402

C660

C654

132

VDD

VDD

GND

GND

104

126

47PF_0402

144

156

VDD

VDD

GND

GND

138

150

C659

47PF_0402

VDD

GND

DIMM2

192

168

180

VDD

VDD

VDDQ

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

GND

GND

GND

GND

GND

162

174

186

201

202

MD_0

5

MD_1

7

MD_2

13

MD_3

17

MD_4

6

MD_5

8

MD_6

14

MD_7

18

MD_8

19

MD_9

23

MD_10

29

MD_11

31

MD_12

20

MD_13

24

MD_14

30

MD_15

32

MD_16

41

MD_17

43

MD_18

49

MD_19

53

MD_20

42

MD_21

44

MD_22

50

MD_23

54

MD_24

55

MD_25

59

MD_26

65

MD_27

67

MD_28

56

MD_29

60

MD_30

66

MD_31

68

MD_32

127

MD_33

129

MD_34

135

MD_35

139

MD_36

128

MD_37

130

MD_38

136

MD_39

140

MD_40

141

MD_41

145

MD_42

151

MD_43

153

MD_44

142

MD_45

146

MD_46

152

MD_47

154

MD_48

163

MD_49

165

MD_50

171

MD_51

175

MD_52

164

MD_53

166

MD_54

172

MD_55

176

MD_56

177

MD_57

181

MD_58

187

MD_59

189

MD_60

178

MD_61

182

MD_62

188

MD_63

190

71

73

79

83

72

74

80

84

AMP_DDR-SO-DIMM-STANDARD

+VDDIO

C744

C746

22UF_1206

C658

22UF_1206

0.1UF_0402

0.1UF_0402

0.1UF_0402

0.1UF_0402

0.1UF_0402

0.1UF_0402

0.1UF_0402

0.1UF_0402

0.1UF_0402

0.1UF_0402

0.1UF_0402

MA0 MA1 MA2 MA3 MA7MA5MA4 MA6 MB0MA11 MA13MA9MA8 MB1MA12MA10 MB8MB5 MB7MB3MB2 MB9MB6MB4 MB10 MB13MB12MB11

EMIC131

10P_0402

1 1

MEMBAA0 MEMBAA1 MEMBAB1

EMIC160

10P_0402

EMIC132

10P_0402

EMIC161

10P_0402

EMIC133

10P_0402

MEMBAB0

EMIC162

10P_0402

EMIC134

10P_0402

EMIC163

10P_0402

A

EMIC135

10P_0402

EMIC136

10P_0402

EMIC137

10P_0402

EMIC138

10P_0402

CS0# CS1# CS2# CS3# SRASB# CKE0SWEA# CKE1SWEB# SCASA# SRASA#SCASB#

EMIC164

10P_0402

EMIC165

10P_0402

EMIC166

10P_0402

EMIC167

10P_0402

EMIC139

10P_0402

EMIC140

10P_0402

EMIC168

10P_0402

B

EMIC141

10P_0402

EMIC169

10P_0402

EMIC142

10P_0402

EMIC170

10P_0402

EMIC143

10P_0402

EMIC171

10P_0402

EMIC144

10P_0402

EMIC172

10P_0402

EMIC145

10P_0402

EMIC173

10P_0402

EMIC146

10P_0402

EMIC174

10P_0402

EMIC147

10P_0402

C

EMIC175

10P_0402

EMIC148

10P_0402

EMIC149

10P_0402

EMIC150

10P_0402

EMIC151

10P_0402

EMIC152

10P_0402

11/18 FOR EMI IMPROVAL DDR NOISE

EMIC153

10P_0402

D

EMIC154

10P_0402

EMIC155

10P_0402

EMIC156

10P_0402

EMIC157

10P_0402

EMIC158

10P_0402

Title

DIMM1 & DIMM2 (DDR SODIMM)

Size Document Number Rev

C

Date: Sheet of

MSI CORPORATION

MS-1039

E

7 46Thursday, December 01, 2005

0.A

A

B

C

D

E

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

MD_[63:0]

DQS_[7:0]

DM_[7:0]

+VTT

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

R235121_1%_0402

R229121_1%_0402

R236121_1%_0402

R232121_1%_0402

RN34

47_8P4R_0402

RN37

47_8P4R_0402

RN36

47_8P4R_0402

RN35

47_8P4R_0402

RN32

47_8P4R_0402

RN44

47_8P4R_0402

RN33

47_8P4R_0402

RN40

47_8P4R_0402

RN42

47_8P4R_0402

RN38

47_8P4R_0402

RN43

47_8P4R_0402

DCLK7+ 4,7

DCLK6+ 4,7

DCLK5+ 4,7

DCLK4+ 4,7

MD_[63:0] 7

DQS_[7:0] 7

DM_[7:0] 7

+VTT

MEMBAB04,7

MEMBAB14,7

MEMBAA04,7

MEMBAA14,7

SCASA#4,7

SCASB#4,7

SWEA#4,7

SWEB#4,7

SRASA#4,7

SRASB#4,7

C441

For EMI

CKE04,7

CKE14,7

CS0#4,7

CS1#4,7

CS2#4,7

CS3#4,7

+VDDIO

0.1UF_0402

0.1UF_0402C705

0.1UF_0402C434

0.1UF_0402C432

MEMBAB0

MEMBAB1

MEMBAA0

MEMBAA1

CKE0

CKE1

CS0#

CS1#

CS2#

CS3#

SCASA#

SCASB#

SWEA#

SWEB#

SRASA#

SRASB#

+VTT

LAYOUT: Add 100pF and 1000pF

VTT fill near Clawhammer and

near DIMMs (Both Sides)

+VTT

1000PF_0402C179

1000PF_0402C173

+VTT

0.1UF_0402C184

0.1UF_0402C182

0.1UF_0402C186

0.1UF_0402C185

0.1UF_0402C171

0.1UF_0402C178

0.1UF_0402C176

0.1UF_0402C175

0.1UF_0402C174

0.1UF_0402C168

0.1UF_0402C170

0.1UF_0402C172

0.1UF_0402C165

0.1UF_0402C151

0.1UF_0402C189

0.1UF_0402C163

0.1UF_0402C162

0.1UF_0402C156

0.1UF_0402C153

0.1UF_0402C154

0.1UF_0402C1480.1UF_0402C180

0.1UF_0402C152

0.1UF_0402C167

0.1UF_0402C188

0.1UF_0402C187

0.1UF_0402C159

0.1UF_0402C177

0.1UF_0402C160

backside

LAYOUT: Place alternating caps to GND and

+2.5VDIMM in a single line along VTT island.

LAYOUT: Place a cap every 1 inch on VTT

trace between Clawhammer and DDR.

+VTT

0.1UF_0402

C143

0.1UF_0402

C155

C142

4.7U/10V_0805

47UF_1206

+VTT

C723

C144

100UF/6.3V_1210

C822

47UF_1206

LAYOUT: Locate close to

ClawHammer socket.

From CPU

MD0

MD4

MD5

MD1

DQS0

DM0

4 4

3 3

2 2

1 1

MD2

MD6

MD14

MD15

MD10

MD11

MD20

MD16

MD17

DQS2

MD21

DM2

MD18

MD22

MD26

MD30

MD27

MD31

MD19

MD23

MD24

MD28

MD25

MD29

DQS3

DM3

MD32

MD36

MD33

MD37

DQS4

MD34

DM4

MD38

MD41

DQS5

DM5

MD45

MD48

MD49

MD52

MD53

DM6

DQS6

MD54

MD50

MD55

MD51

MD60

MD56

MD61

MD57

DM7

DQS7

MD62

MD58

MD63

MD59

MD7

MD3

MD8

MD9

MD42

MD43

MD46

MD47

MD12

DQS1

MD13

DM1

MD39

MD35

MD40

MD44

To DDR Socket

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

MD_0

MD_4

MD_5

MD_1

DQS_0

DM_0

MD_2

MD_6

MD_14

MD_15

MD_10

MD_11

MD_20

MD_16

MD_17

DQS_2

MD_21

DM_2

MD_18

MD_22

MD_26

MD_30

MD_27 MD_32

MD_31

MD_19

MD_23

MD_24

MD_28

MD_25

MD_29

DQS_3

DM_3

MD_32

MD_36

MD_33

MD_37

DQS_4

MD_34

DM_4

MD_38

MD_41

DQS_5

DM_5

MD_45

MD_48

MD_49

MD_52

MD_53

DM_6

DQS_6

MD_54

MD_50

MD_55

MD_51

MD_60

MD_56

MD_61

MD_57

DM_7

DQS_7

MD_62

MD_58

MD_63

MD_59

MD_7

MD_3

MD_8

MD_9

MD_42

MD_43

MD_46

MD_47

MD_12

DQS_1

MD_13

DM_1

MD_39

MD_35

MD_40

MD_44

RN21

10_8P4R_0402

RN20

10_8P4R_0402

RN17

10_8P4R_0402

RN16

10_8P4R_0402

RN15

10_8P4R_0402

RN12

10_8P4R_0402

RN14

10_8P4R_0402

RN13

10_8P4R_0402

RN11

10_8P4R_0402

RN10

10_8P4R_0402

RN8

10_8P4R_0402

RN6

10_8P4R_0402

RN5

10_8P4R_0402

RN4

10_8P4R_0402

RN3

10_8P4R_0402

RN2

10_8P4R_0402

RN19

10_8P4R_0402

RN7

10_8P4R_0402

RN18

10_8P4R_0402

RN9

10_8P4R_0402

MD_1

MD_0

MD_2

DQS_0

MD_27

MD_26

DQS_3

MD_25

MD_24

MD_19

MD_18

DQS_2

MD_4

MD_5

DM_0

MD_6

MD_29

DM_3

MD_30

MD_31

MD_36

MD_37

MD_33

MD_40

MD_35

MD_46

MD_47

MD_52

MD_53

DM_6

MD_54

MD_41

DQS_5

MD_43

MD_42

MD_62

MD_63

MD_49

MD_48

DM_4

MD_38

MD_39

MD_44

MD_14

MD_15

MD_20

MD_21

MD_34

DQS_4

MD_45

DM_5

MD_10

MD_11

MD_16

MD_17

MD_7

MD_12

MD_13

DM_1

DM_2

MD_22

MD_23

MD_28

MD_55

MD_60

MD_61

DM_7

MD_50

DQS_6

MD_56

MD_51

MD_8

MD_3

DQS_1

MD_9

DQS_7

MD_57

MD_59

MD_58

+VTT

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

RN52

68_8P4R_0402

RN49

68_8P4R_0402

RN48

68_8P4R_0402

RN47

68_8P4R_0402

RN39

68_8P4R_0402

RN31

68_8P4R_0402

RN28

68_8P4R_0402

RN26

68_8P4R_0402

RN27

68_8P4R_0402

RN24

68_8P4R_0402

RN30

68_8P4R_0402

RN45

68_8P4R_0402

RN29

68_8P4R_0402

RN50

68_8P4R_0402

RN46

68_8P4R_0402

RN41

68_8P4R_0402

RN25

68_8P4R_0402

RN23

68_8P4R_0402

RN51

68_8P4R_0402

RN22

68_8P4R_0402

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

To DDR Socket

DCLK7-4,7

DCLK6-4,7

DCLK5-4,7

DCLK4-4,7

MA[13:0]4,7

MB[13:0]4,7

MD[63:0]4

DQS[7:0]4

DM[7:0]4

MB2

MB0

MA13

MB10

MA6

MA4

MB3

MA3

MA2

MA1

MB1

MA0

MA10

CS0#

MB6

MB4

SCASB#

CS3#

SWEB#

CS2#

MB12

CKE0

MA7

MA12

MEMBAB1

SRASB#

MEMBAB0

MB13

MA8

MB5

SCASA#

CS1#

SRASA#

MEMBAA1

SWEA#

MEMBAA0

CKE1

MB11

MB8

MA5

MA11

MA9

MB7

MB9

MD[63:0]

DQS[7:0]

DM[7:0]

MA[13:0]

MB[13:0]

MSI CORPORATION

Title

DDR TERMINATION

Size Document Number Rev

C

A

B

C

D

Date: Sheet of

MS-1039

8 46Thursday, December 01, 2005

E

0.A

5

4

3

2

1

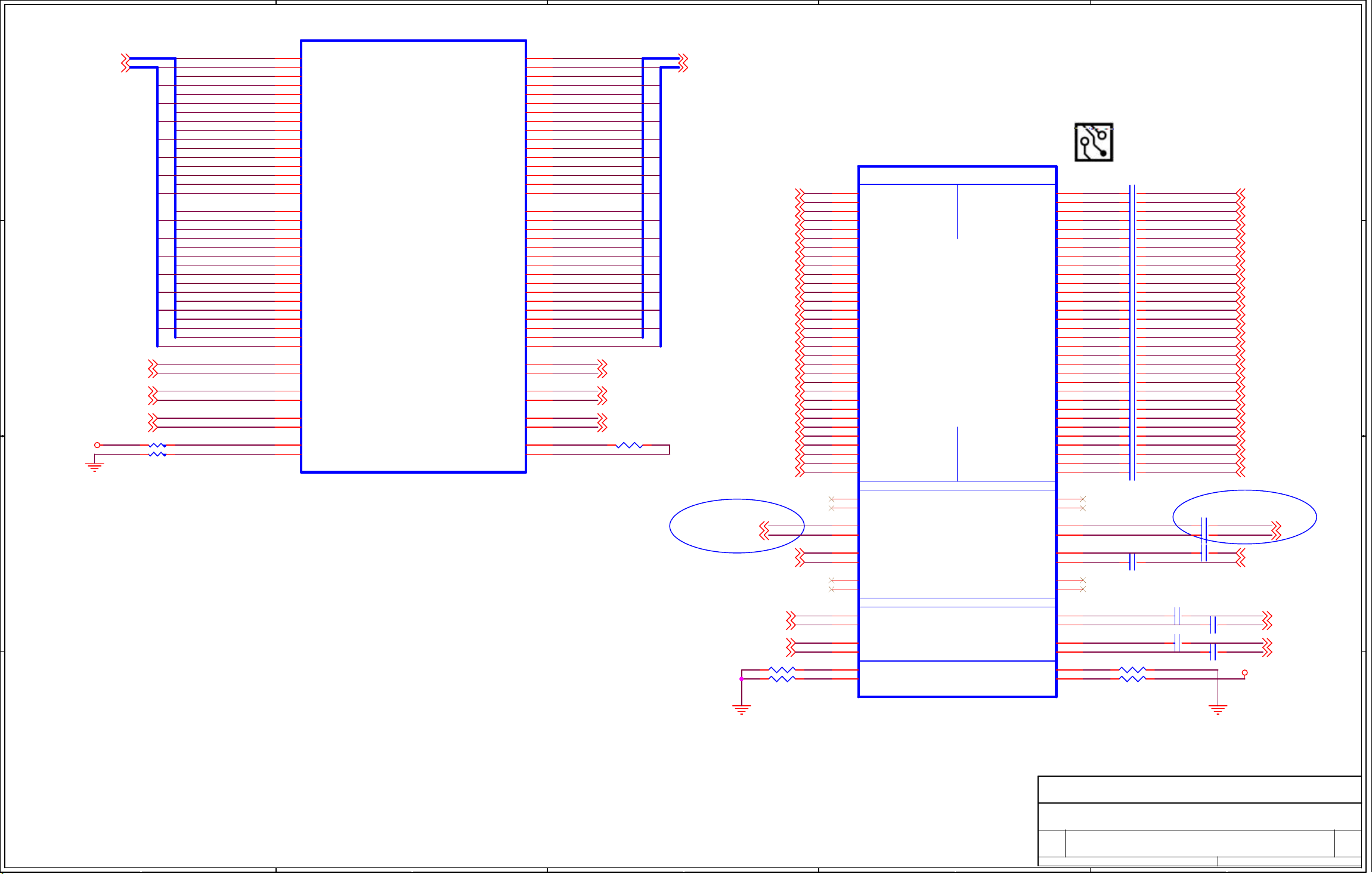

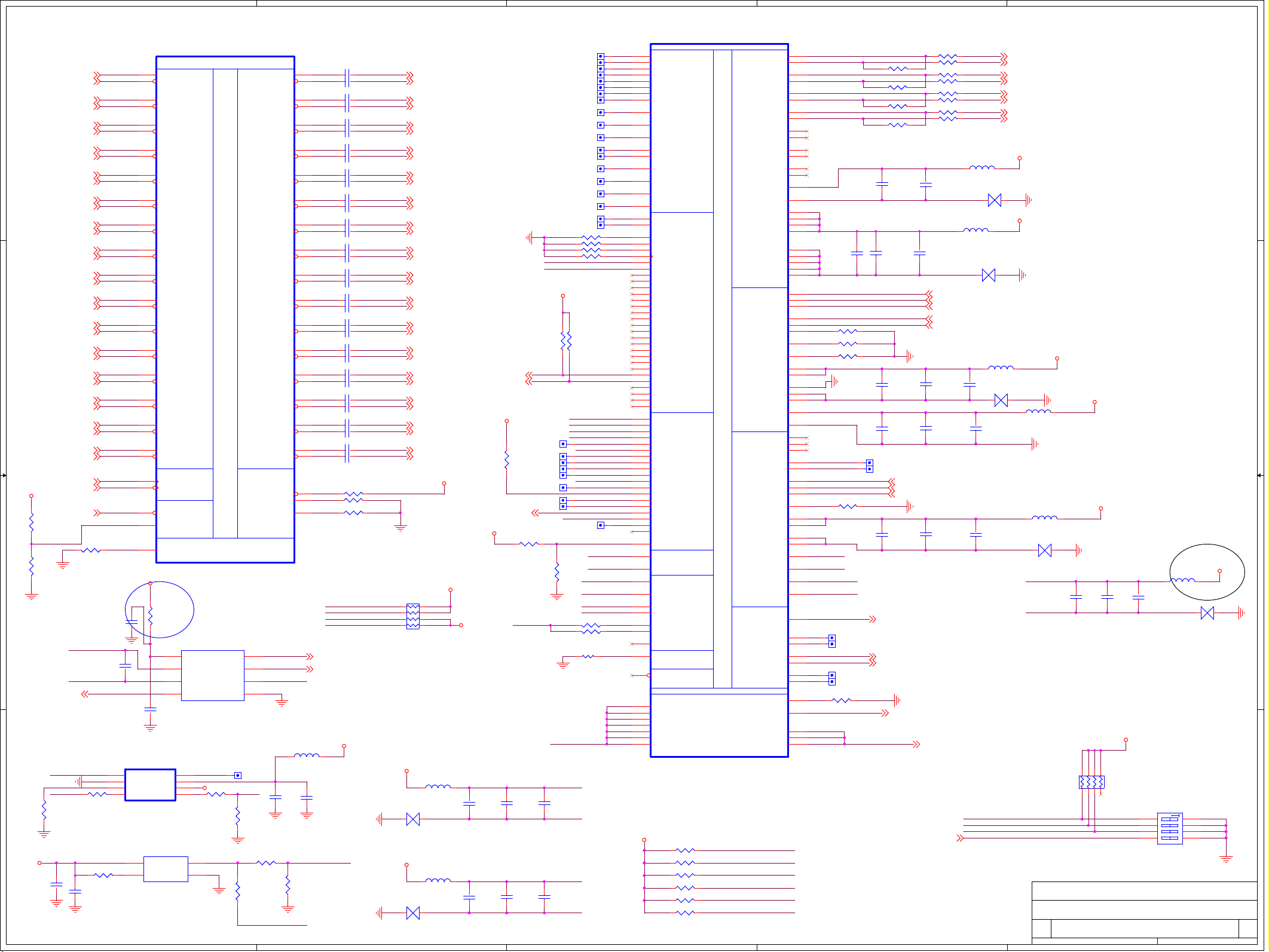

U3A

HT_CADOUT_H[15:0]3

D D

C C

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

HT_CLKOUT_H13

HT_CLKOUT_H03

HT_CLKOUT_L03

HT_CTLOUT_H03

HT_CTLOUT_L03

+1.2VRUN

R11 49.9R1%0402 100R_1%_0402R10

R12 49.9R1%0402

HT_RXCALN

HT_RXCALP

T26

R26

U25

U24

V26

U26

W25

W24

AA25

AA24

AB26

AA26

AC25

AC24

AD26

AC26

R29

R28

T30

R30

T28

T29

V29

U29

Y30

W30

Y28

Y29

AB29

AA29

AC29

AC28

Y26

W26

W29

W28

P29

N29

D27

E27

HT_RXCAD15P

HT_RXCAD15N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD0P

HT_RXCAD0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCTLP

HT_RXCTLN

HT_RXCALN

HT_RXCALP

R24

R25

N26

P26

N24

N25

L26

M26

J26

K26

J24

J25

G26

H26

G24

G25

L30

M30

L28

L29

J29

K29

H30

H29

E29

E28

D30

E30

D28

D29

B29

C29

L24

L25

F29

G29

M29

M28

B28

A28

I/F

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

PART 1OF6

HYPER TRANSPORT CPU

RS480M_A13

B B

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

HT_TXCALP

HT_TXCALN

HT_CLKIN_H1 3

HT_CLKIN_L1 3HT_CLKOUT_L13

HT_CLKIN_H0 3

HT_CLKIN_L0 3

HT_CTLIN_H0 3

HT_CTLIN_L0 3

0402

HT_CADIN_H[15:0] 3

HT_CADIN_L[15:0] 3HT_CADOUT_L[15:0]3

PCIE_RXP130

PCIE_RXN130

PLACE THESE CAP CLOSE

U3B

TO CONNECTOR

PART 2 OF 6

GFX_RX0P12

GFX_RX0N12

GFX_RX1P12

GFX_RX1N12

GFX_RX2P12

GFX_RX2N12

GFX_RX3P12 GFX_TX3P 12

GFX_RX3N12

GFX_RX4P12

GFX_RX4N12

GFX_RX5P12

GFX_RX5N12

GFX_RX6P12

GFX_RX6N12

GFX_RX7P12

GFX_RX7N12

GFX_RX8P12

GFX_RX8N12

GFX_RX9P12

GFX_RX9N12

GFX_RX10P12

GFX_RX10N12

GFX_RX11P12

GFX_RX11N12

GFX_RX12P12

GFX_RX12N12

GFX_RX13P12

GFX_RX13N12

GFX_RX14P12

GFX_RX14N12

GFX_RX15P12

GFX_RX15N12

GPP_RX2P26

GPP_RX2N26

D8

GFX_RX0P

D7

GFX_RX0N

D5

GFX_RX1P

D4

GFX_RX1N

E4

GFX_RX2P

F4

GFX_RX2N

G5

GFX_RX3P

G4

GFX_RX3N

H4

GFX_RX4P

J4

GFX_RX4N

H5

GFX_RX5P

H6

GFX_RX5N

G1

GFX_RX6P

G2

GFX_RX6N

K5

GFX_RX7P

K4

GFX_RX7N

L4

GFX_RX8P

M4

GFX_RX8N

N5

GFX_RX9P

N4

GFX_RX9N

P4

GFX_RX10P

R4

GFX_RX10N

P5

GFX_RX11P

P6

GFX_RX11N

P2

GFX_RX12P

R2

GFX_RX12N

T5

GFX_RX13P

T4

GFX_RX13N

U4

GFX_RX14P

V4

GFX_RX14N

W1

GFX_RX15P

W2

GFX_RX15N

AE1

GPP_RX0P/SB_RX2P

AE2

GPP_RX0N/SB_RX2N

AB2

GPP_RX1P/SB_RX3P

AC2

GPP_RX1N/SB_RX3N

AB5

GPP_RX2P

AB4

GPP_RX2N

Y4

GPP_RX3P

AA4

GPP_RX3N

PCIE I/F TO

VIDEO

GPP_TX0P/SB_TX2P

GPP_TX0N/SB_TX2N

GPP_TX1P/SB_TX3P

GPP_TX1N/SB_TX3N

PCIE I/F TO SLOT

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

A7

B7

B6

B5

A5

A4

B3

B2

C1

D1

D2

E2

F2

F1

H2

J2

J1

K1

K2

L2

M2

M1

N1

N2

R1

T1

T2

U2

V2

V1

Y2

AA2

AD2

AD1

AA1

AB1

Y5

Y6

W5

W4

C21 0.1UF_0402

C27 0.1UF_0402

C29 0.1UF_0402

C31 0.1UF_0402

C32 0.1UF_0402

C34 0.1UF_0402

C36 0.1UF_0402

C38 0.1UF_0402

C46 0.1UF_0402

C49 0.1UF_0402

C52 0.1UF_0402

C53 0.1UF_0402

C54 0.1UF_0402

C57 0.1UF_0402

C58 0.1UF_0402

C59 0.1UF_0402

C60 0.1UF_0402

C62 0.1UF_0402

C63 0.1UF_0402

C64 0.1UF_0402

C65 0.1UF_0402

C67 0.1UF_0402

C68 0.1UF_0402

C69 0.1UF_0402

C70 0.1UF_0402

C72 0.1UF_0402

C75 0.1UF_0402

C82 0.1UF_0402

C85 0.1UF_0402

C86 0.1UF_0402

C87 0.1UF_0402

C88 0.1UF_0402

SB_PETP1

SB_PETN1

C538 0.1UF_0402

C841 0.1UF_0402

C842 0.1UF_0402

C535 0.1UF_0402

GFX_TX0P 12

GFX_TX0N 12

GFX_TX1P 12

GFX_TX1N 12

GFX_TX2P 12

GFX_TX2N 12

GFX_TX3N 12

GFX_TX4P 12

GFX_TX4N 12

GFX_TX5P 12

GFX_TX5N 12

GFX_TX6P 12

GFX_TX6N 12

GFX_TX7P 12

GFX_TX7N 12

GFX_TX8P 12

GFX_TX8N 12

GFX_TX9P 12

GFX_TX9N 12

GFX_TX10P 12

GFX_TX10N 12

GFX_TX11P 12

GFX_TX11N 12

GFX_TX12P 12

GFX_TX12N 12

GFX_TX13P 12

GFX_TX13N 12

GFX_TX14P 12

GFX_TX14N 12

GFX_TX15P 12

GFX_TX15N 12

11/1611/16

PCIE_TXP1 30

PCIE_TXN1 30

GPP_TX2P 26

GPP_TX2N 26

A_RX0P20

A_RX0N20

A_RX1P20

A_RX1N20

10K_1%R48

8.25K_1%R50

AG1

AH1

AC5

AC6

AH3

AJ3

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

PCE_ISET

PCE_TXISET

PCIE I/F TO SB

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

PCE_PCAL

PCE_NCAL

AF2

AG2

AC4

AD4

AH2

AJ2

SB_TX0P_C

SB_TX0N_C

SB_TX1P_C

SB_TX1N_C

R263

RS480M_A13

A A

C544 0.1UF_0402

C539 0.1UF_0402

150R_1%R49

82.5R_1%_0402

C550 0.1UF_0402

C541 0.1UF_0402

+1.2VRUN

A_TX0P 20

A_TX0N 20

A_TX1P 20

A_TX1N 20

MSI CORPORATION

Title

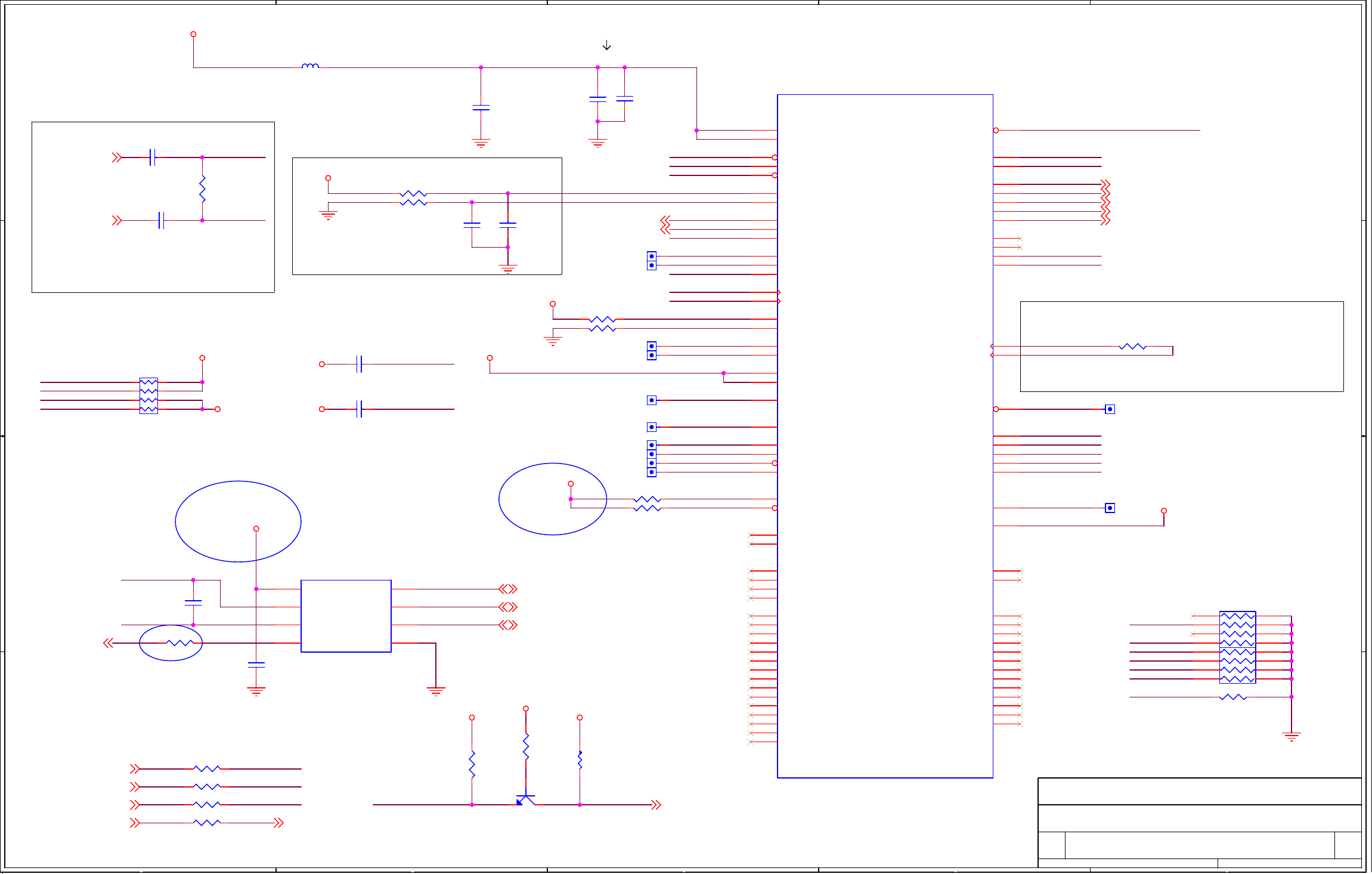

RX480-HT/PCIE

Size Document Number Rev

B

5

4

3

2

Date: Sheet of

MS-1039

1

9 46Thursday, December 01, 2005

0.A

5

4

3

2

1

U3C

AF17

MEM_A0

AK17

MEM_A1

AH16

MEM_A2

AF16

MEM_A3

AJ22

MEM_A4

AJ21

MEM_A5

AH20

MEM_A6

D D

C C

B B

AH21

AK19

AH19

AJ17

AG16

AG17

AH17

AJ18

AG26

AJ29

AE21

AH24

AH12

AG13

AH8

AE8

AF25

AH30

AG20

AJ25

AH13

AF14

AJ7

AG8

AG25

AH29

AF21

AK25

AJ12

AF13

AK7

AF9

AE17

AH18

AE18

AJ19

AF18

AK16

AJ16

AE28

AJ4

AJ20

AK20

AJ15

AJ14

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_A11

MEM_A12

MEM_A13

MEM_A14

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEM_DQS0P

MEM_DQS1P

MEM_DQS2P

MEM_DQS3P

MEM_DQS4P

MEM_DQS5P

MEM_DQS6P

MEM_DQS7P

MEM_DQS0N

MEM_DQS1N

MEM_DQS2N

MEM_DQS3N

MEM_DQS4N

MEM_DQS5N

MEM_DQS6N

MEM_DQS7N

MEM_RAS#

MEM_CAS#

MEM_WE#

MEM_CS#

MEM_CKE

MEM_CKP

MEM_CKN

MEM_CAP1

MEM_CAP2

MEM_VMODE

MEM_VREF

MPVDD

MPVSS

PART 3 OF 6

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_A I/F

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_COMPP

MEM_COMPN

AF28

AF27

AG28

AF26

AE25

AE24

AF24

AG23

AE29

AF29

AG30

AG29

AH28

AJ28

AH27

AJ27

AE23

AG22

AF23

AF22

AE20

AG19

AF20

AF19

AH26

AJ26

AK26

AH25

AJ24

AH23

AJ23

AH22

AK14

AH14

AK13

AJ13

AJ11

AH11

AJ10

AH10

AE15

AF15

AG14

AE14

AE12

AF12

AG11

AE11

AJ9

AH9

AJ8

AK8

AH7

AJ6

AH6

AJ5

AG10

AF11

AF10

AE9

AG7

AF8

AF7

AE7

AH5

AD30

RS480M_A13

TP85

TP73

AVDD

DAC VDD (2.5V)

DIGITAL VDD (1.8V)AVDDDI

DAC2 BANDGAP REF (1.8V)

PLL VDD (1.8V)PLLVDD

HT PLL VDD (1.2V)HTPVDD

+3VRUN

1 2

L46 FB_220_0.2A

NB STRAP PIN

AP NOTE RECOMMAND

RS480 side port

RX480 NC Pin

+1.8VRUN

A A

1 2

L88

C896

2.2UF

FB_220_0.2A

11/16

5

LOAD_ROM#:LOAD ROM STRAP ENABLE strap

High, LOAD ROM STRAP DISABLE

Low, LOAD ROM STRAP ENABLE

ATI has internal pull up

R218 3K_NC

LOAD_ROM# SPMEM_EN#

4

R219 3K_NC

+3VRUN

L86 FB_220_0.2A

VDDA18

L87

VDDA18

+1.8VSUS

C451

2.2UF

BMREQ#20

+3VRUN

11/16

1 2

FB_220_0.2A

1 2

150R_1%R228

R47

4.7K_0402

C895

2.2UF

C18

2.2UF

C455

2.2UF

RS480M_RST#5

NB_PWRGD34

ALLOW_LDTSTOP20

OSC14M17

SPMEM_EN#

LOAD_ROM#

R25 10K_0402

R233 10K_0402

LDTSTOP#5,20

3K_NCR220

TP64

TP1

DFT_GPIO2

DDC1_SCLK

DDC1_SDATA

harry 0322

U3D

B27

AVDD1

C27

AVDD2

D26

AVSSN1

D25

AVSSN2

C24

AVDDDI

B24

AVSSDI

E24

AVDDQ

D24

AVSSQ

B25

C

A25

Y

A24

COMP

C25

RED

A26

GREEN

B26

BLUE

A11

DACVSYNC

B11

DACHSYNC

C26

RSET

E11

DACSCL

F11

DACSDA

A14

PLLVDD

B14

PLLVSS

M23

HTPVDD

L23

HTPVSS

D14

SYSRESET#

B15

POWERGOOD

B12

LDTSTOP#

C12

ALLOW_LDTSTOP

AH4

SUS_STAT#

H13

VDDR3_1

H12

VDDR3_2

A13

OSCIN

B13

OSCOUT

B9

TVCLKIN

F12

DFT_GPIO0/RSV

E13

DFT_GPIO1/RSV

D13

DFT_GPIO2/RSV

F10

BMREQb

C10

I2C_CLK

C11

I2C_DATA

AF4

THERMALDIODE_P

AE4

THERMALDIODE_N

RS480M_A13

ATI has internal pull up

+3VRUN +3VRUN

SPMEM_EN#:SIDE PORT MEMORY ENABLE strap

R224 3K_NC

R226 3K_NC

High, SIDE PORT MEMORY DISABLE

Low, SIDE PORT MEMORY ENABLE

3

PART 4 OF 6

CRT/TVOUT

LVDS

LVDDR18A_1

LVDDR18A_2

PLL PWR

PM

LVDS_DIGON

CLOCKs

DFT_GPIO3/RSV

DFT_GPIO4/RSV

DFT_GPIO5/RSV

MIS.

2

TXOUT_U0P

TXOUT_U0N

TXOUT_U1P

TXOUT_U1N

TXOUT_U2P

TXOUT_U2N

TXOUT_U3P

TXOUT_U3N

TXOUT_L0P

TXOUT_L0N

TXOUT_L1P

TXOUT_L1N

TXOUT_L2P

TXOUT_L2N

TXOUT_L3P

TXOUT_L3N

TXCLK_UP

TXCLK_UN

TXCLK_LP

TXCLK_LN

LPVDD

LPVSS

LVDDR18D

LVSSR1

LVSSR2

LVSSR3

LVSSR4

LVSSR5

LVSSR6

LVSSR7

LVSSR8

LVDS_BLON

LVDS_BLEN

GFX_CLKP

GFX_CLKN

HTTSTCLK

HTREFCLK

SB_CLKP

SB_CLKN

TMDS_HPD

STRP_DATA

DDC_DATA

TESTMODE

D18

C18

B19

A19

D19

C19

D20

C20

B16

A16

D16

C16

B17

A17

E17

D17

B20

A20

B18

C17

E18

F17

E19

G20

H20

G19

E20

F20

H18

G18

F19

H19

F18

E14

F14

F13

B8

A8

P23

N23

E8

E7

C13

C14

C15

A10

E10

B10

E12

LVDS_BLEN

R231 10K_0402

DFT_GPIO3

DFT_GPIO4

DFT_GPIO5

STRP_DATA

DDC_DATA

R234 10K_0402

R230

4.7K_0402

TP72

NBSRCCLK 17

NBSRCCLK# 17

HTREFCLK 17

SBLINKCLK 17

SBLINKCLK# 17

TP70

3K_NCR24

3K_NCR18

3K_NCR13

+3VRUN

MSI CORPORATION

Title

RX480-SIDE PORT MEMORY I/F

Size Document Number Rev

B

Date: Sheet of

MS-1039

1

10 46Thursday, December 01, 2005

0.A

5

4

3

2

1

NB RX480 POWER STATES

S1

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

S3

OFF

OFF

OFF

OFF

OFF

OFF

OFFAVDD

OFF

OFF

OFF

OFF

OFF

OFF

S4/S5

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

C42

4.7U/10V_0805

C93

4.7U/10V_0805

C9

4.7U/10V_0805

C30

4.7U/10V_0805

Power Signal

VDDHT

VDDR,VDDRCK

VDD18

R5

AE5V5N3F7F5R3AA6T3M6C5F8M8Y8V3C3W3K8D3C6

VSSA1

VSSA2

VSSA3

VSSA4

VSSA5

VSSA6

VSSA7

VSSA8

D D

VSSA9

VSSA10

VSSA11

VSSA12

VSSA13

VSSA14

VSSA15

VSSA16

VSSA17

VSSA18

VSSA19

AA3A2AB3P8J6C8AD3V8F3

VSSA20

VSSA21

VSSA22

VSSA23

VSSA24

VSSA25

VSSA26

VSSA27

AE3

AF3M5AB7G3B4P7AA5C9C7J5R6J3AD5D6C4K3AB8T7Y7