Page 1

5

www.schematic-x.blogspot.com

4

3

2

1

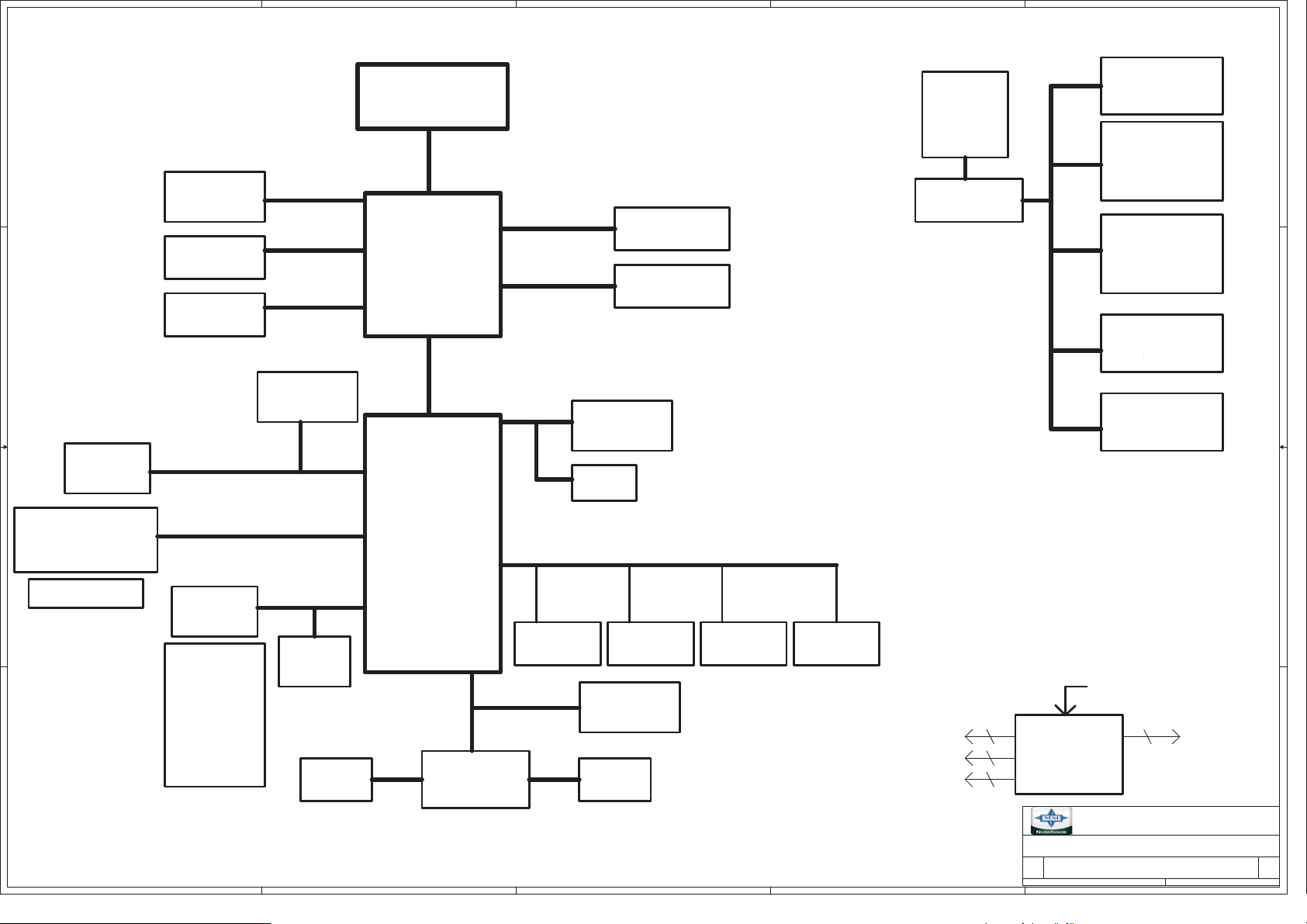

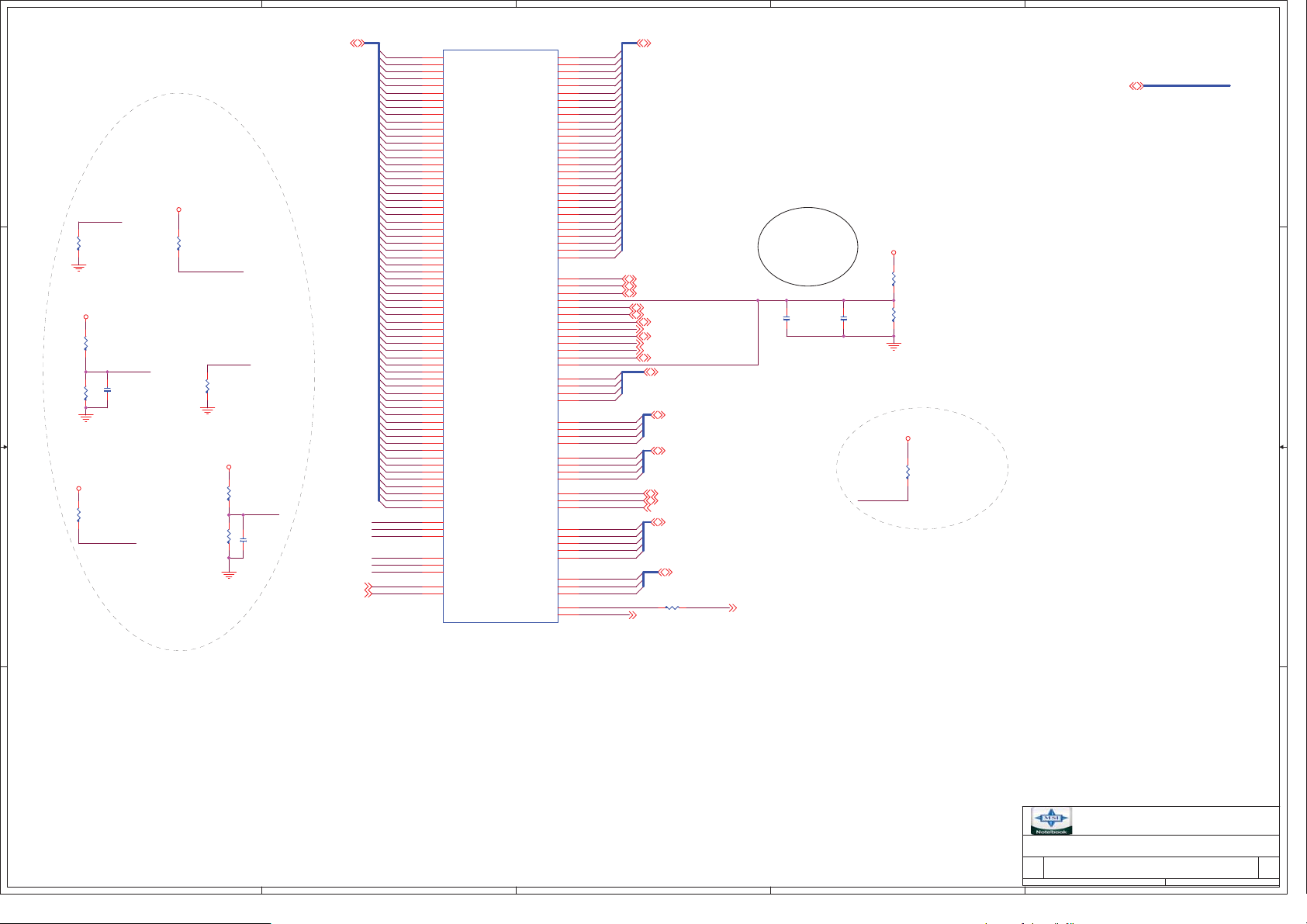

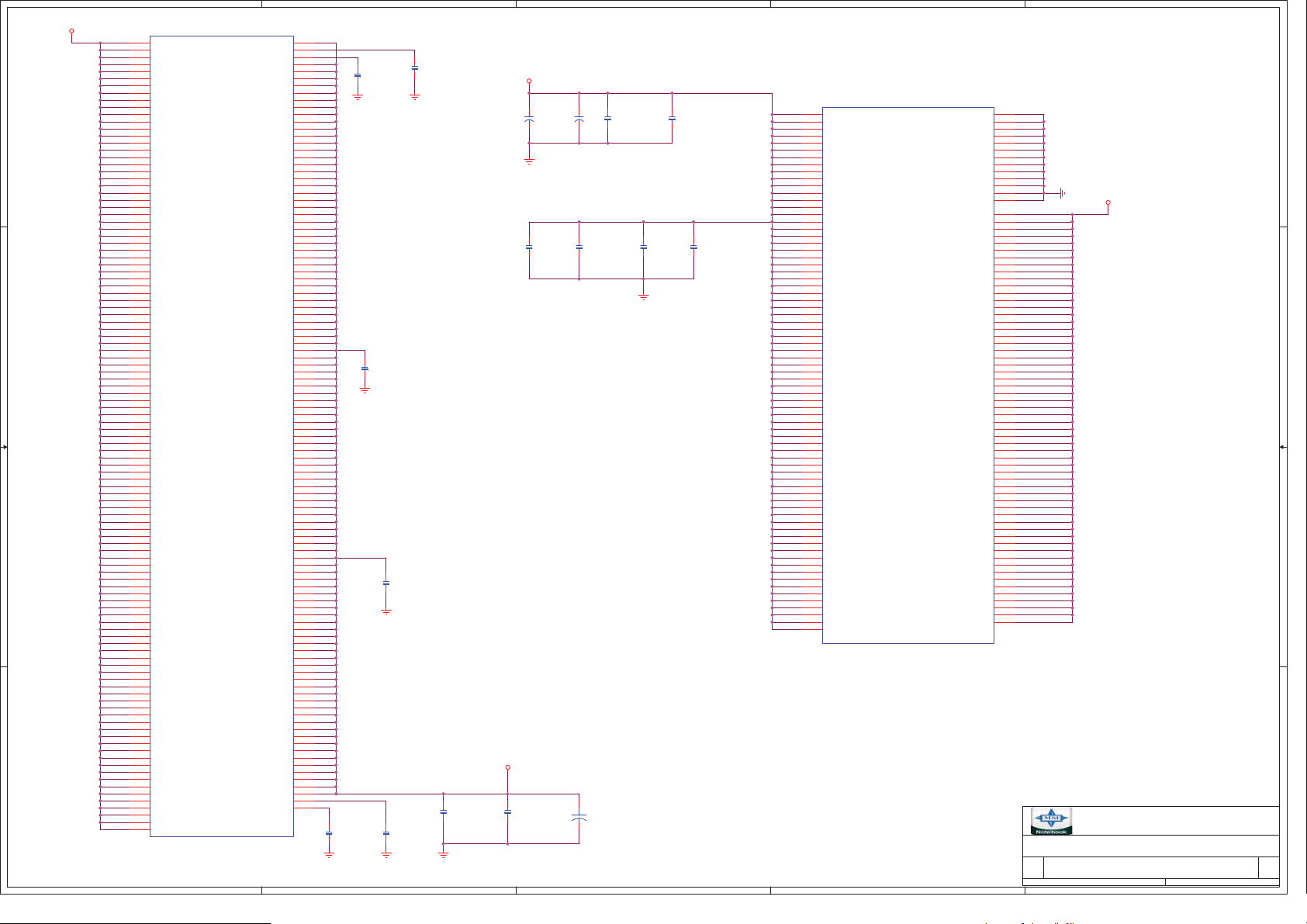

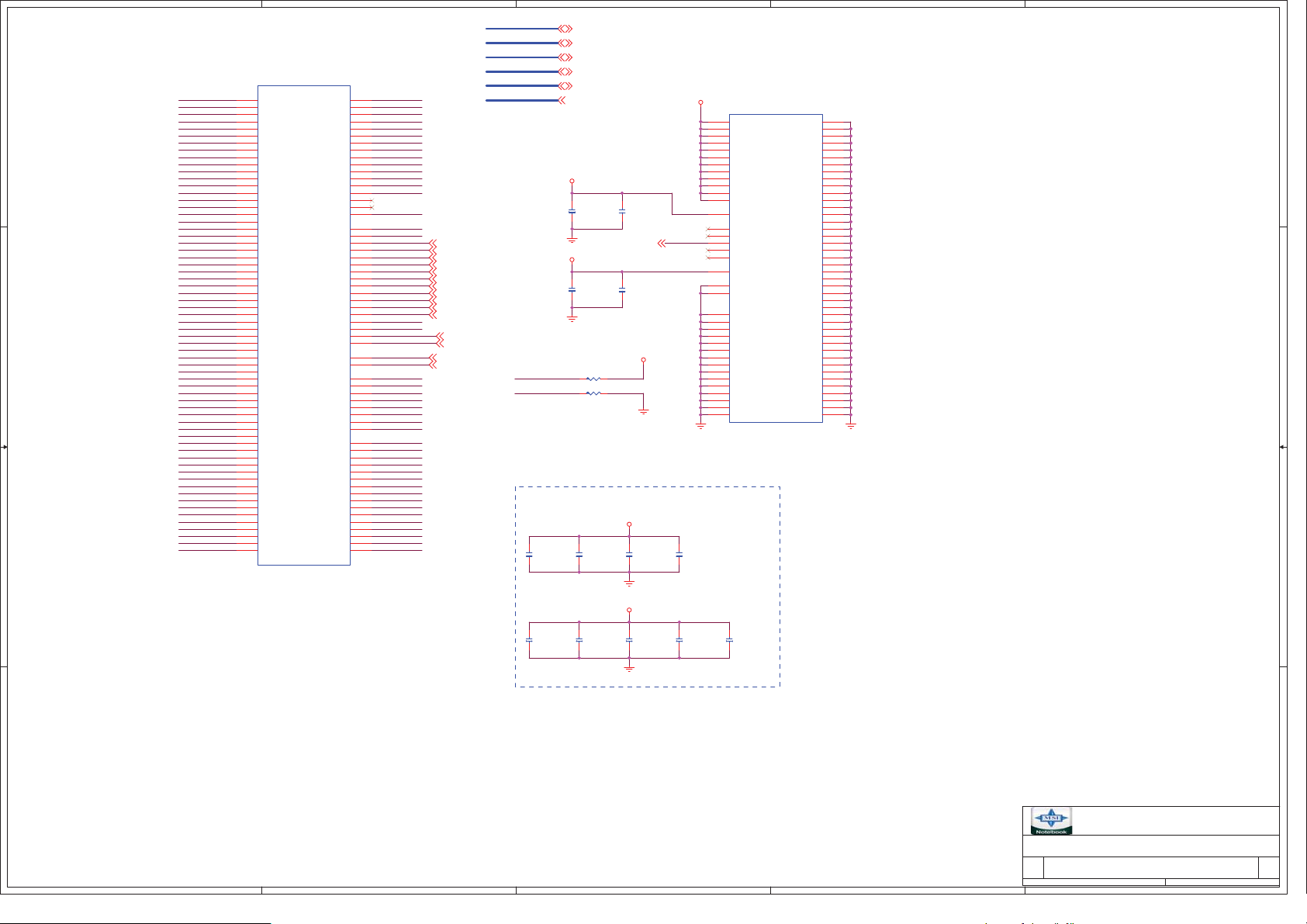

MS1034 VER:0.A

Yonah 479

D D

LVDS

LVDS

Page 16

CRT

VGA

Page 16

TV_OUT

VGA

Page 14

C C

Page 3,4,5

HOST

133/166MHZ 4X

NORTH

BRIDGE

INTEL

945GM

1466

Page 6,7,8,9,10

Dual Channel DDRII

400/533/667 MHZ

Dual Channel DDRII

400/533/667 MHZ

DDR-SODIMM0

Page 12

DDR-SODIMM1

Page 13

DC JACK

&

Selector

Page 35

SYS POWER

DMI

Interface

MINI CARD

Page 27

PATA

DVD/CDROM

Page 23

PCIE-LAN

RTL8111B

Page 26

PCI-EXPRESS

SOUTH

HDD

Page 23

BRIDGE

1394 & 3 IN 1 CARD

OZ711MP

B B

Page 24,25

PCI BUS

INTEL

ICH7-M

USB1.1/2.0

652

SD/MMC/MS

ALC882D

Page 29

Internal SPK

MIC

LINE IN

Earphone

SPDIF Out

Internal MIC

A A

Page 30 BIOS

Azalia

MDC

Page 28

TP & KB

Page

17,18,19,20,21

KBC

ENE 3910

Page 31

USB 0,1,2,3

Page 22

LPC BUS

Connectors

LPC DUBUG

ISA

Page 31Page 31

Bluetooth

USB 4

Page 28

Page 31

Mini_PCIE

USB 5

Page 27

Camera

USB 7

Page 22

(ቃఎ)

133/166MHZ HOST

100MHZ PCIE

33MHZ PCI

CLK GEN

ICS 954310

Page 15

+3V +5V

MAX1999

Page 35

VTT(1.05V)

+1_5VRUN

OZ813

Page 37

+1_8VSUN

SMDDR_VTERM

SC486

Page 36

CPU POWER

ISL6262

Page 38

CHARGER

MAX1772

Page 34

14MHZ CRYSTAL

14MHZ SB

5

Title

Size Document Number Rev

Custom

4

3

2

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

BLOCK DIAGRAM

MS-1034

1

144Thursday, September 22, 2005

0.A

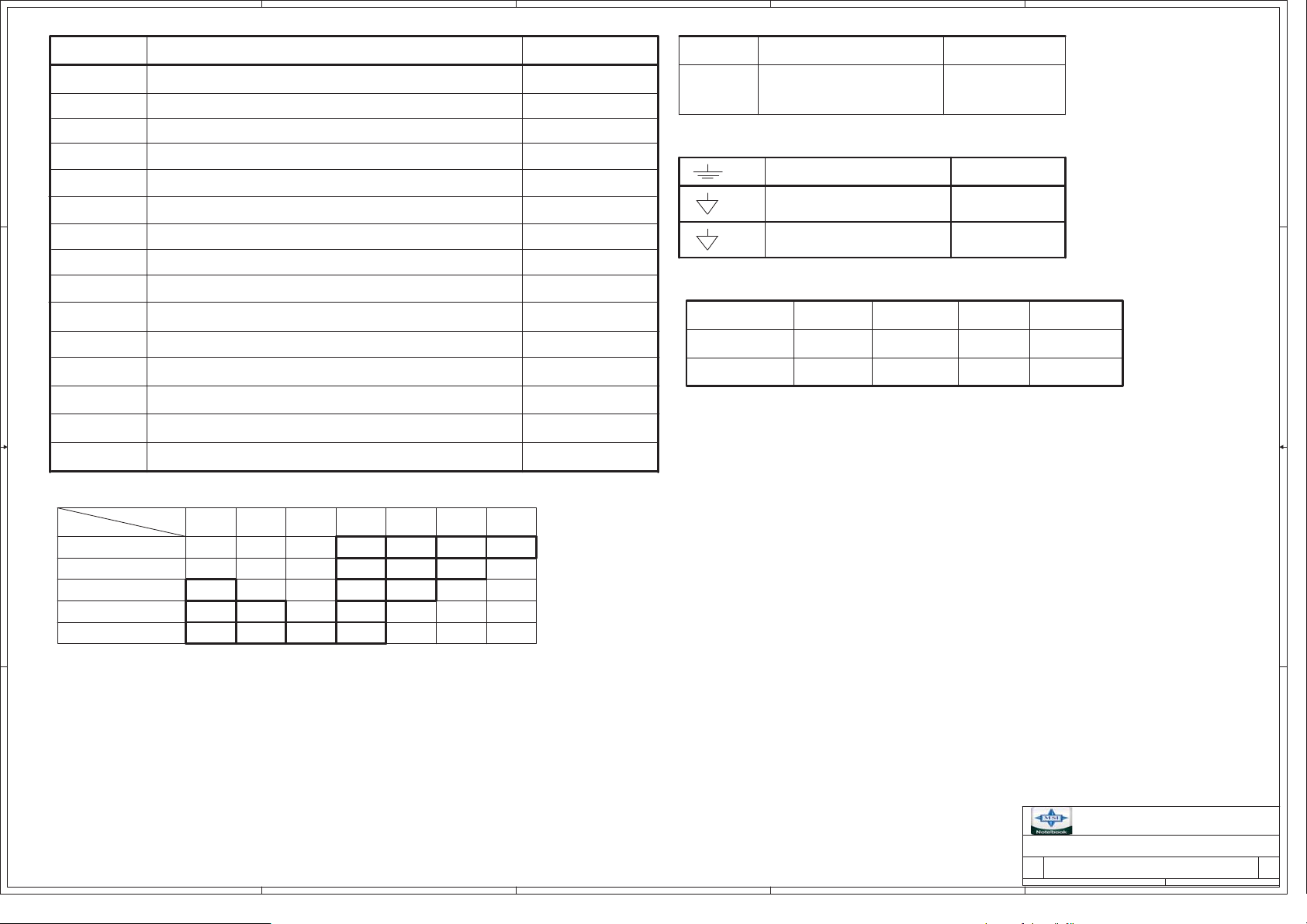

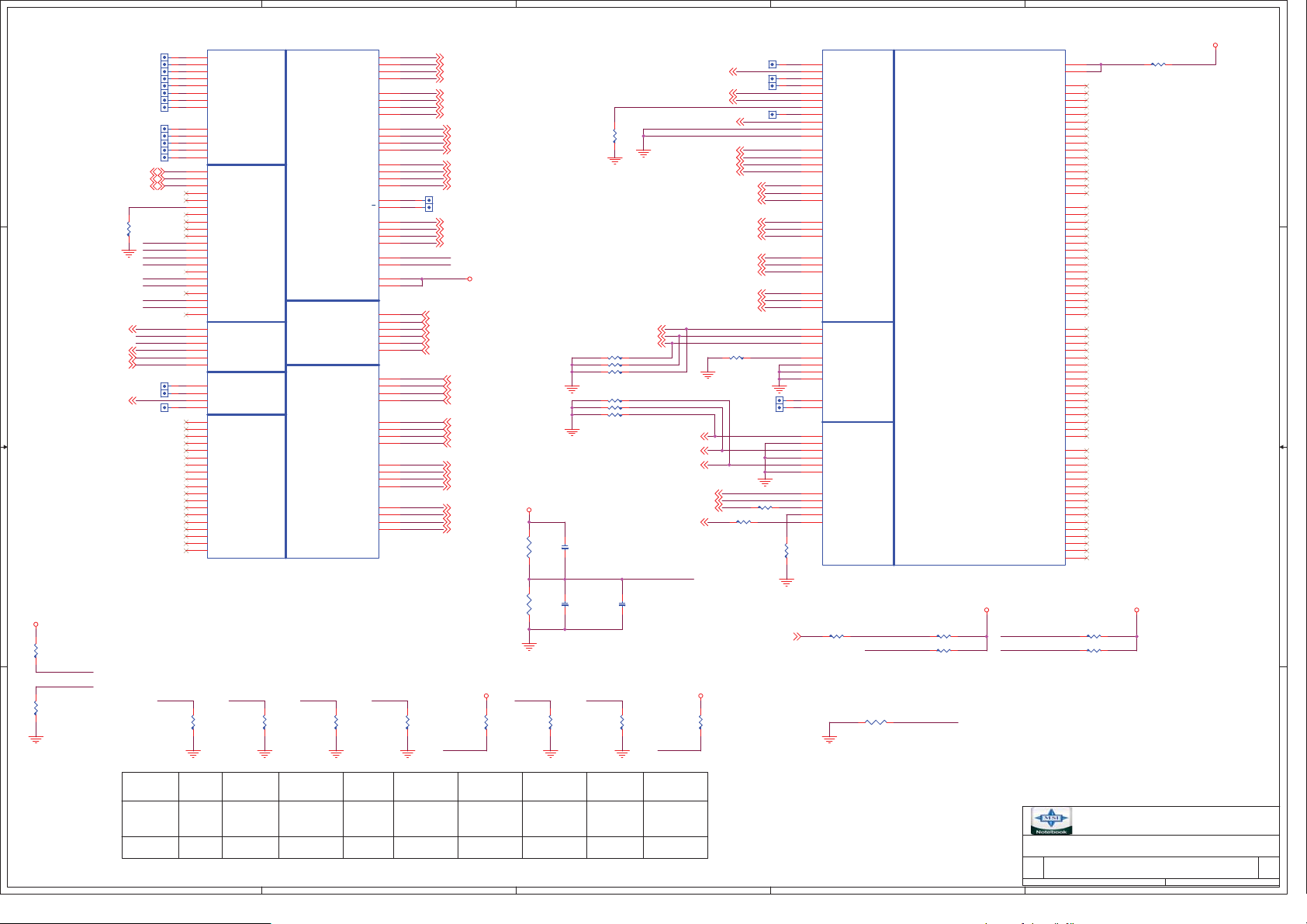

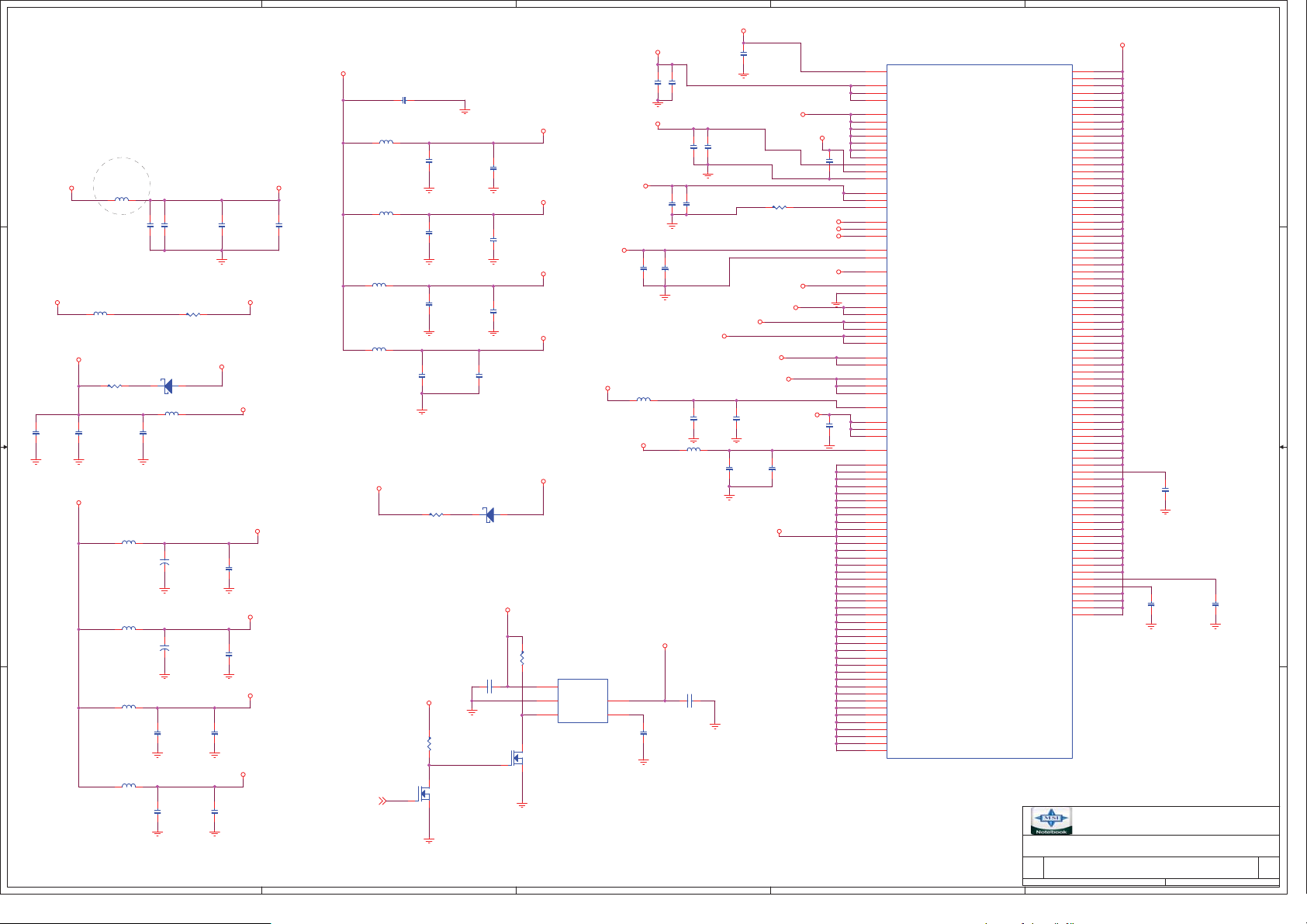

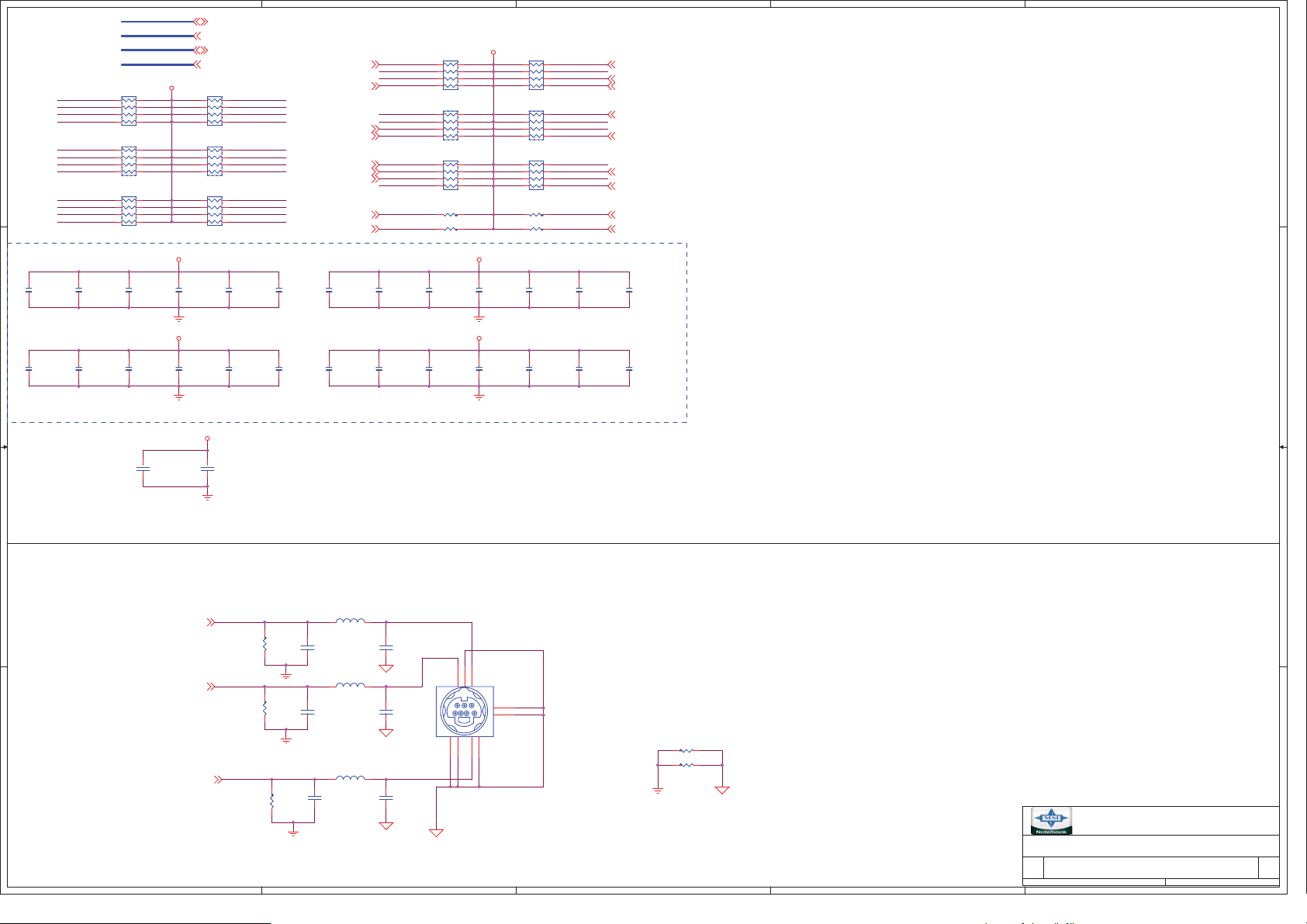

Page 2

5

4

3

2

1

Voltage Rails

Voltage Description

Control Signal

PWR_SRC AC ADAPTER OR BATTERY IN

D D

VHCORE

VTT 1.05 rail for Processor & 945GM I/O RUN_ON

Core Voltage for Processor

VR_ON

+1_5VRUN 1.5V switched power rail(off in S3-S5) RUN_ON

+3VRUN

+5VRUN 5.0V switched power rail(off in S3-S5)

3.3V switched power rail(off in S3-S5)

RUND

RUND

Voltage Description

+V5_AUDIO

5.0V Power rail Audio

codec(off in S3-S5)

GND DIGTIAL GROUD

AGND AUDIO GND

Control Signal

+5VSUS

SMDDR_VTERM 0.9V DDRII Termination voltage (off in S4-S5) DIMM_ON

+1_8VSUS 1.8V power rail DDRII (off in S4-S5)

+2_5VRUN

2.5V power rail for 945GM LVDS

+3VSUS 3.3V power rail (off in S4-S5)

C C

+5VSUS 5.0V power rail (off in S4-S5)

+3VALW 3.3V always on power rail

+5VALW 5.0V always on power rail

DIMM_ON

+3VRUN

SUS_ON

SUS_ON

PWR_SRC

PWR_SRC

PCI RESOURCE

DEVICE IDSEL# REQ/GNT# PCI_INT# CLOCK

SOUTHBRIDGE

CARDREADER

POWER Analogy GND

AD31(INT) NA NA

AD20 0 A

PCLK_CARD

POWER STATES

STATE

B B

Full ON

S1M(Power On Suspend)

S3( Suspend to RAM)

S4( Suspend to Disk)

S5 / Soft OFF

Note : WHEN AC MODE , System turn on then +V*SUS will always keep

high

SIGNAL Clocks

SLP_S3#

HIGH ON

HIGH

LOW

LOW

LOW

SLP_S4#

HIGH

HIGH

LOW

LOW

SLP_S5#

HIGH

HIGH

HIGH

HIGH

+V*ALWAYS

ON

ON

ON

ONLOW

+V*SUS

ON

ON

ON

OFF

OFF

+V*RUN

ON

ON

OFF

OFF

OFF

ONHIGH

LOW

OFF

OFF

OFF

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

PLATFORM

MS-1034

1

244Thursday, September 22, 2005

0.A

of

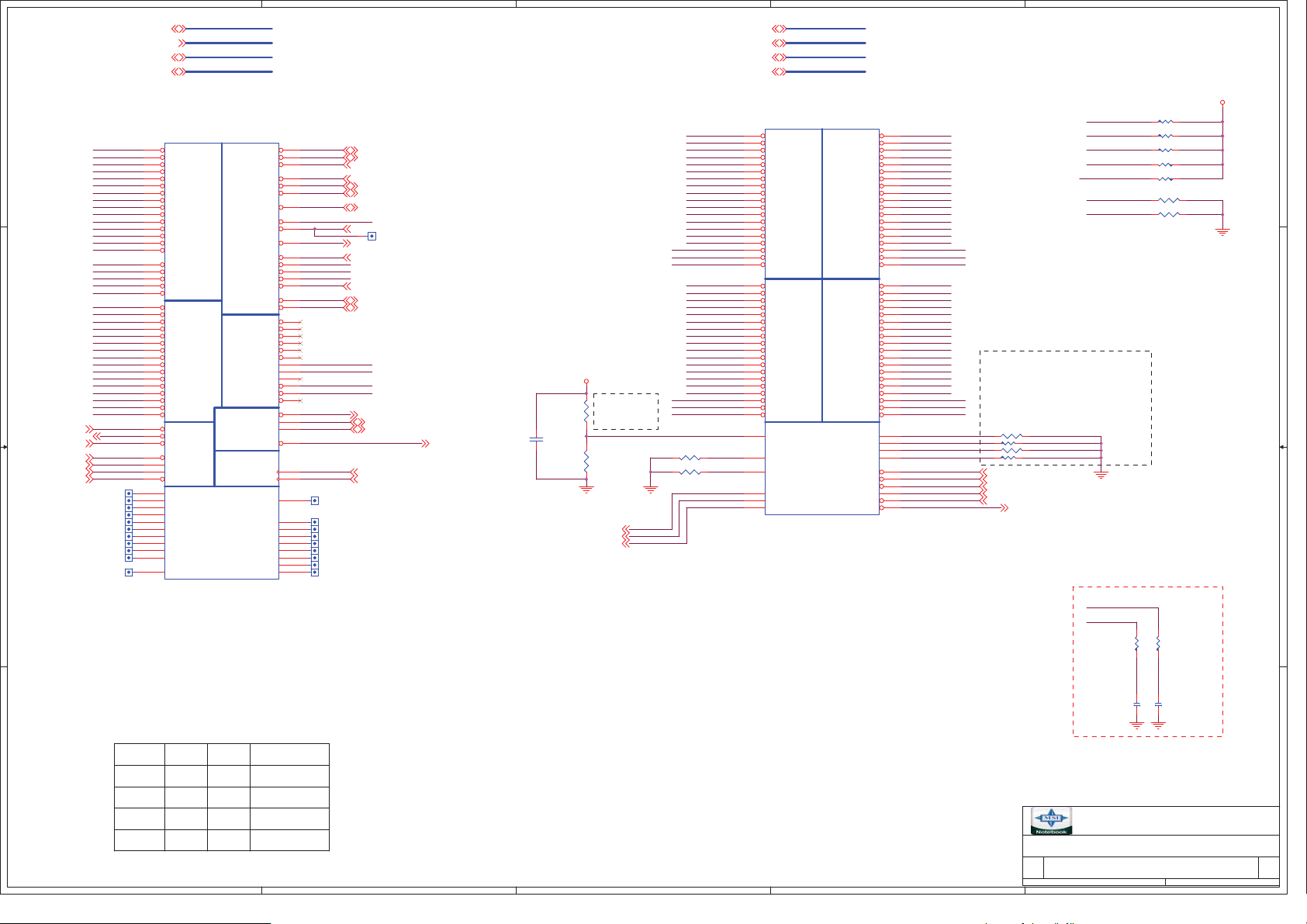

Page 3

5

U22A

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RSVD[10]

RSVD[11]

1

HA#[3..31]

HREQ#[0..4]

HASTB#[0..1]

ADDR GROUP

0

DEFER#

DRDY#

DBSY#

LOCK#

CONTROL

RESET#

TRDY#

ADDR GROUP

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

XDP/ITP SIGNALS

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

THERM

BCLK[0]

BCLK[1]

H CLK

RSVD[12]

RSVD[13]

RSVD[14]

RSVD[15]

RSVD[16]

RSVD[17]

RSVD[18]

RSVD[19]

RSVD[20]

socket_478

ADS#

BNR#

BPRI#

BR0#

IERR#

INIT#

RS[0]#

RS[1]#

RS[2]#

HIT#

HITM#

TCK

TDO

TMS

TRST#

DBR#

ADS#

H1

BNR#

E2

BPRI#

G5

DEFER#

H5

DRDY#

F21

DBSY#

E1

BREQ0#

F1

IERR#

D20

CPU_INIT#

B3

HLOCK#

H4

CPURST#

B1

RS#0

F3

RS#1

F4

RS#2

G3

HTRDY#

G2

HIT#

G6

HITM#

E4

AD4

AD3

AD1

AC4

AC2

AC1

HTCK

AC5

HTDI

AA6

TDI

AB3

HTMS

AB5

HTRST#

AB6

C20

PROCHOT#

D21

THERMDA

A24

THERMDC

A25

C7

CPUCLK0

A22

CPUCLK#0

A21

T22

TP49

D2

TP27TP34

F6

TP39

D3

TP30TP26

C1

TP22

AF1

TP18TP23

D22

TP48

C23

TP50

C24

TP52

HA#[3..31]6

RS#[0..2]6

HREQ#[0..4]6

HASTB#[0..1]6

D D

HA#3

J4

HA#4

L4

HA#5

M3

HA#6

K5

HA#7

M1

HA#8

N2

HA#9

J1

HA#10

N3

HA#11

P5

HA#12

P2

HA#13

L1

HA#14

P4

HA#15

P1

HA#16

R1

HASTB#0

L2

HREQ#0

K3

HREQ#1

H2

HREQ#2

K2

HREQ#3

J3

HREQ#4

L5

HA#17

Y2

HA#18

U5

HA#19

R3

HA#20

W6

HA#21

C C

A20M#17

FERR#17

IGNNE#17

STPCLK#17

INTR17

NMI17

SMI#17

B B

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HASTB#1

A20M#

FERR#

IGNNE#

STPCLK#

INTR

NMI

TP19

TP35

TP24

TP32

TP36

TP31

TP29

TP51

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

4

ADS# 6

BNR# 6

BPRI# 6

DEFER# 6

DRDY# 6

DBSY# 6

BREQ0# 6

CPU_INIT# 17

TP28

HLOCK# 6

CPURST# 6

HTRDY# 6

HIT# 6

HITM# 6

0822

Modify

PROCHOT# 38

THERMDA 32

THERMDC 32

THERMTRIP#

CPUCLK0 15

CPUCLK#0 15

THERMTRIP# 17

close thermal

sensor

C372

R308

1K_1%

R302

0.1UF_0402

2K_1%

VTT

0.5" max

length

imp=55ohm

BSEL015

BSEL115

BSEL215

3

CPU_GTLREF

R307 X_1K

R306 51R

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HDSTBN#0

HDSTBP#0

DBI#0

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HDSTBN#1

HDSTBP#1

DBI#1

2

U22B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

socket_478

HD#[0..63]

HDSTBP#[0..3]RS#[0..2]

HDSTBN#[0..3]

DBI#[0..3]

DATA GRP0 DATA GRP1

MISC

AA23

D[32]#

AB24

D[33]#

V24

D[34]#

V26

D[35]#

W25

D[36]#

U23

D[37]#

U25

D[38]#

U22

D[39]#

AB25

D[40]#

W22

D[41]#

Y23

D[42]#

AA26

D[43]#

Y26

D[44]#

Y22

D[45]#

DATA GRP2DATA GRP3

AC26

D[46]#

AA24

D[47]#

W24

DSTBN[2]#

Y25

DSTBP[2]#

V23

DINV[2]#

AC22

D[48]#

AC23

D[49]#

AB22

D[50]#

AA21

D[51]#

AB21

D[52]#

AC25

D[53]#

AD20

D[54]#

AE22

D[55]#

AF23

D[56]#

AD24

D[57]#

AE21

D[58]#

AD21

D[59]#

AE25

D[60]#

AF25

D[61]#

AF22

D[62]#

AF26

D[63]#

AD23

DSTBN[3]#

AE24

DSTBP[3]#

AC20

DINV[3]#

R26

COMP[0]

U26

COMP[1]

U1

COMP[2]

V1

COMP[3]

E5

DPRSTP#

B5

DPSLP#

D24

DPWR#

D6

PWRGOOD

D7

SLP#

AE6

PSI#

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HDSTBN#2

HDSTBP#2

DBI#2

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDSTBN#3

HDSTBP#3

DBI#3

HCOMP0

HCOMP1

HCOMP2

HCOMP3

H_DPRSTP#

H_DPSLP#

H_DPWR#

CPU_PWRGD

CPUSLP#

PSI#

0822

Modify

IERR#

HTMS

HTDI

CPU_PWRGD

0822

Modify

PROCHOT#

HTCK

HTRST#

Reserve : CPU_PWRGD

CPU_PWRGD :

Demo board no EPU

0.5" max length

25 MIL AWAY FROM HIGH

SPEED SIGNAL

HCOMP0,2==>18MIL

HCOMP1,3==>5MIL

R305 27.4_1%

R304 54.9_1%_0402

R38 27.4_1%

R37 54.9_1%_0402

H_DPRSTP# 17,38

H_DPSLP# 17

H_DPWR# 6

CPU_PWRGD 17

CPUSLP# 6

PSI# 38

CPUCLK#0

CPUCLK0

R297

X_33_0402

HD#[0..63]6

HDSTBP#[0..3]6

HDSTBN#[0..3]6

DBI#[0..3]6

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

J24

J23

H26

F26

K22

H25

H23

G22

J26

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

M24

N25

M26

AD26

C26

D25

B22

B23

C21

1

VTT=1_05V

R79 56_0402

R49 39_0402

R45 1 50_1%_0402

R58 X_200_1%_0402

R80 68_0402

R35 27

R34 680

For EMI

R293

X_33_0402

VTT

C366

X_10PF_0402

C363

X_10PF_0402

BSEL[2] BSEL[1] BSEL[0] BCLK

A A

LLL

LL

L

H

L

HH

5

RESERVED

133MHZ

H

RESERVED

L

166MHZ

4

3

2

Title

Size Document Number Rev

Custom

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

Yonah-1 (HOST BUS)

MS-1034

1

344Monday, September 26, 2005

0.A

of

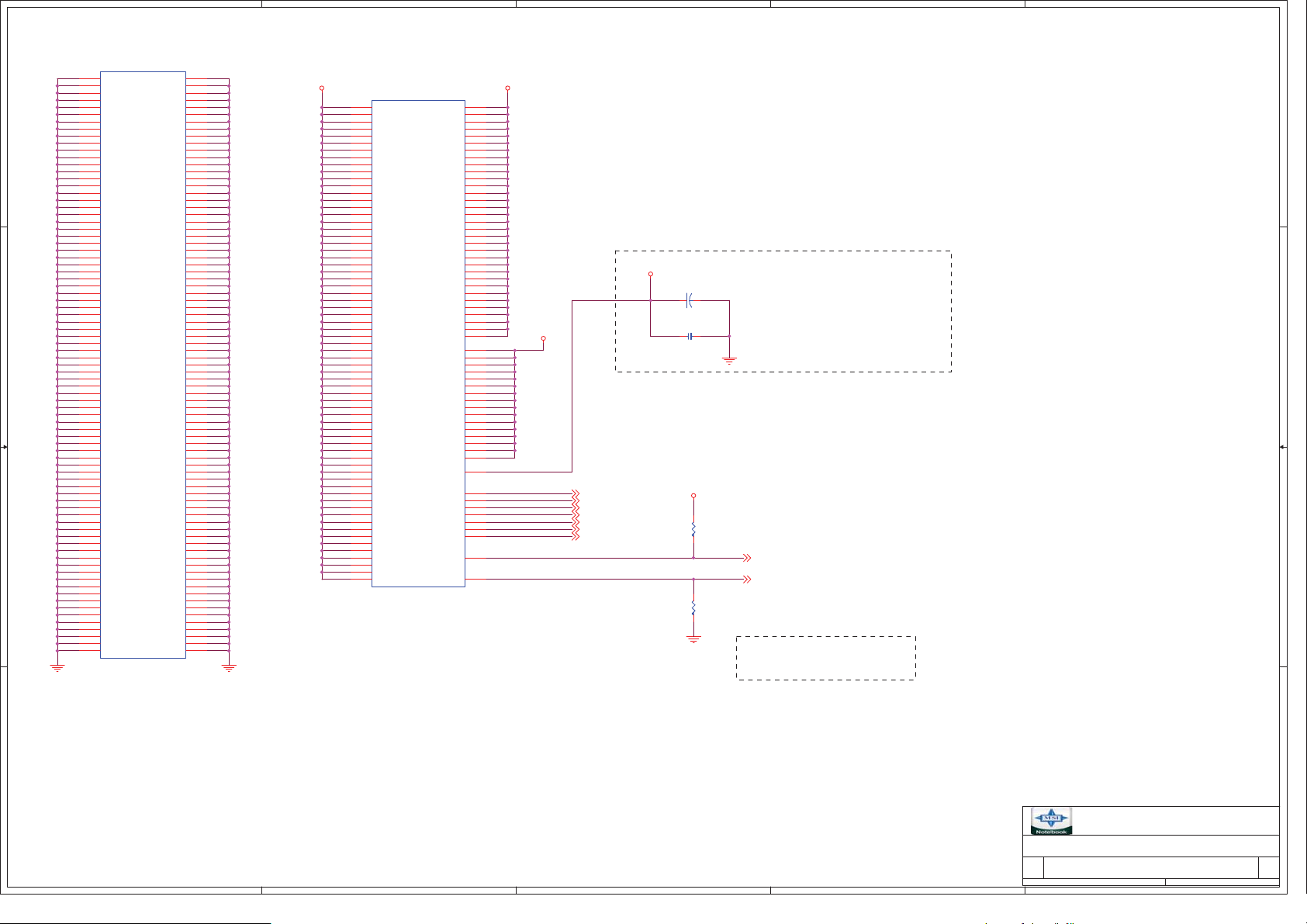

Page 4

5

U22D

A4

VSS1

A8

VSS2

A11

VSS3

A14

VSS4

A16

VSS5

A19

VSS6

D D

C C

B B

A23

A26

B11

B13

B16

B19

B21

B24

C11

C14

C16

C19

C22

C25

D11

D13

D16

D19

D23

D26

E11

E14

E16

E19

E21

E24

F11

F13

F16

F19

F22

F25

G23

G26

H21

H24

K23

K26

L21

L24

M22

M25

N23

N26

VSS7

VSS8

B6

VSS9

B8

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

C5

VSS17

C8

VSS18

VSS19

VSS20

VSS21

VSS22

C2

VSS23

VSS24

VSS25

D1

VSS26

D4

VSS27

D8

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

E3

VSS35

E6

VSS36

E8

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

F5

VSS44

F8

VSS45

VSS46

VSS47

VSS48

VSS49

F2

VSS50

VSS51

VSS52

G4

VSS53

G1

VSS54

VSS55

VSS56

H3

VSS57

H6

VSS58

VSS59

VSS60

J2

VSS61

J5

VSS62

J22

VSS63

J25

VSS64

K1

VSS65

K4

VSS66

VSS67

VSS68

L3

VSS69

L6

VSS70

VSS71

VSS72

M2

VSS73

M5

VSS74

VSS75

VSS76

N1

VSS77

N4

VSS78

VSS79

VSS80

P3

VSS81

socket_478

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

GND

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

VHCORE VHCORE

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

4

U22C

A7

VCC[1]

A9

VCC[2]

A10

VCC[3]

A12

VCC[4]

A13

VCC[5]

A15

VCC[6]

A17

VCC[7]

A18

VCC[8]

A20

VCC[9]

B7

VCC[10]

B9

VCC[11]

B10

VCC[12]

B12

VCC[13]

B14

VCC[14]

B15

VCC[15]

B17

VCC[16]

B18

VCC[17]

B20

VCC[18]

C9

VCC[19]

VCC[20]

VCC[21]

VCC[22]

VCC[23]

VCC[24]

VCC[25]

D9

VCC[26]

VCC[27]

VCC[28]

VCC[29]

VCC[30]

VCC[31]

VCC[32]

E7

VCC[33]

E9

VCC[34]

E10

VCC[35]

E12

VCC[36]

E13

VCC[37]

E15

VCC[38]

E17

VCC[39]

E18

VCC[40]

E20

VCC[41]

F7

VCC[42]

F9

VCC[43]

F10

VCC[44]

F12

VCC[45]

F14

VCC[46]

F15

VCC[47]

F17

VCC[48]

F18

VCC[49]

F20

VCC[50]

VCC[51]

VCC[52]

VCC[53]

VCC[54]

VCC[55]

VCC[56]

VCC[57]

VCC[58]

VCC[59]

VCC[60]

VCC[61]

VCC[62]

VCC[63]

VCC[64]

VCC[65]

VCC[66]

VCC[67]

socket_478

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

POWER

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[100]

VCCP[1]

VCCP[2]

VCCP[3]

VCCP[4]

VCCP[5]

VCCP[6]

VCCP[7]

VCCP[8]

VCCP[9]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

VTT

CPU_VID0 38

CPU_VID1 38

CPU_VID2 38

CPU_VID3 38

CPU_VID4 38

CPU_VID5 38

CPU_VID6 38

3

+1_5VRUN

C373

10UF/10V_0805

C370

0.01UF_0402

VHCORE

0.01uf and 10uf of a pair capacitors

place near PIN B26

R56

100_1%_0402

VCCSENSE_2 38

VSSSENSE_2 38

R55

100_1%_0402

LAYOUT NOTE:

Route VCCSENSE and VSSSENSE traces at 27.4Ohms

with 50 mil spacing.

Place PU and PD within 1 inch of CPU.

2

1

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

Yonah-2 (Power / GND)

MS-1034

1

444Thursday, September 22, 2005

0.A

of

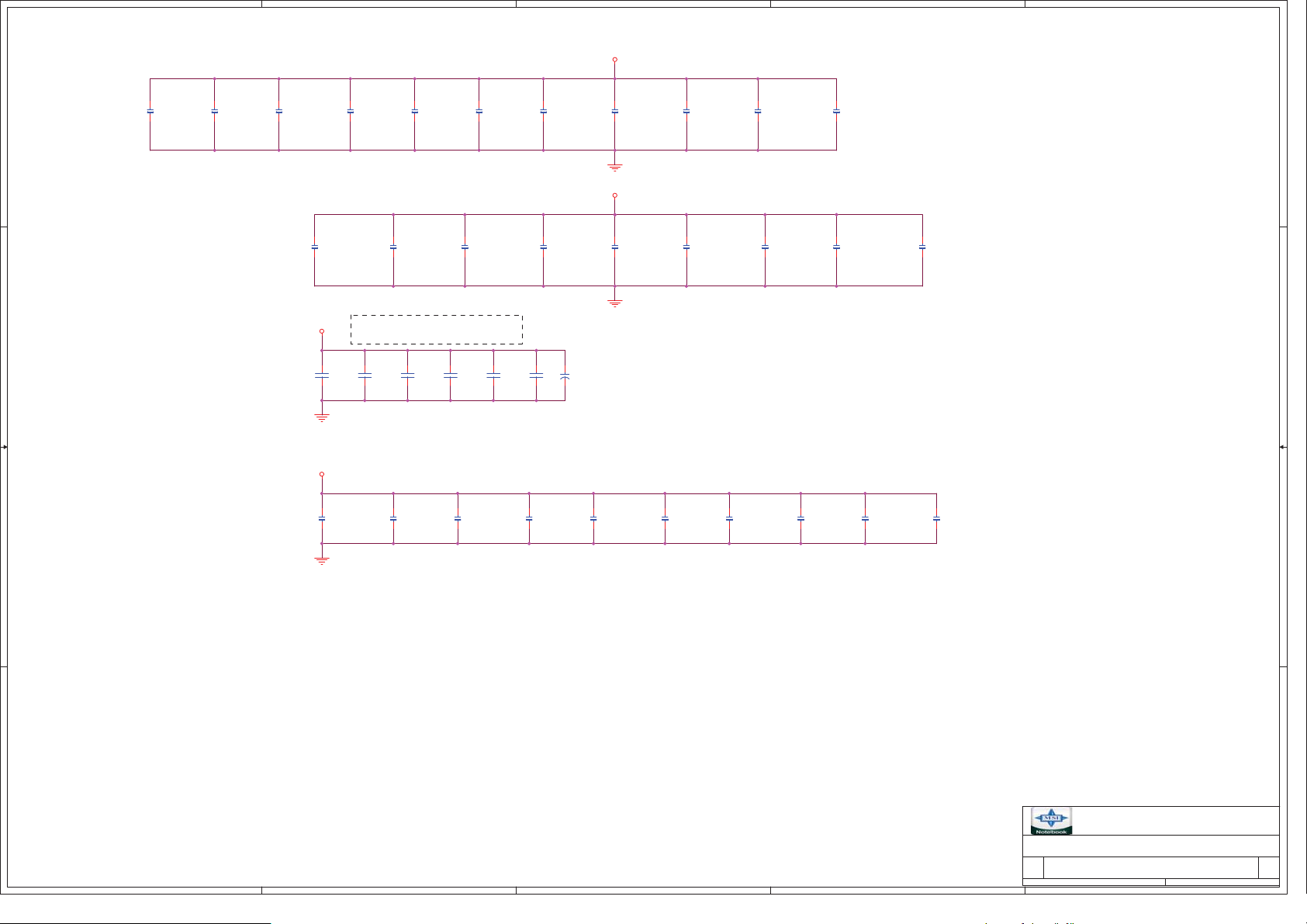

Page 5

5

4

VHCORE

3

2

1

VHCORE

C321

C220U2.5SP-LF

C335

22UF/6.3V_0805

C120

22UF/6.3V_0805

C344

22UF/6.3V_0805

C98

22UF/6.3V_0805

C348

22UF/6.3V_0805

C119

22UF/6.3V_0805

C121

22UF/6.3V_0805

C345

22UF/6.3V_0805

C75

22UF/6.3V_0805

C108

22UF/6.3V_0805

VTT

C134

0.1UF_0402

C330

22UF/6.3V_0805

C128

22UF/6.3V_0805

C350

22UF/6.3V_0805

C99

22UF/6.3V_0805

close to cpu socket

C132

C84

0.1UF_0402

0.1UF_0402

C57

22UF/6.3V_0805

0.1UF_0402

C356

22UF/6.3V_0805

C106

22UF/6.3V_0805

C349

22UF/6.3V_0805

C85

0.1UF_0402

C86

C113

22UF/6.3V_0805

C347

22UF/6.3V_0805

12

+

0.1UF_0402

C135

22UF/6.3V_0805

C341

D D

C C

22UF/6.3V_0805

C355

22UF/6.3V_0805

C342

22UF/6.3V_0805

C133

VHCORE

C351

22UF/6.3V_0805

C115

22UF/6.3V_0805

C343

22UF/6.3V_0805

C127

22UF/6.3V_0805

C340

22UF/6.3V_0805

C93

22UF/6.3V_0805

B B

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

Yonah-3

MS-1034

1

0.A

of

544Thursday, September 22, 2005

Page 6

5

4

3

2

1

HD#[0..63]3

D D

0.5" max

length

VTT

R290

54.9_1%_0402

221_1%_0402

100_1%_0402

HXSCOMP

24.9_1%_0402

R294

R295

HYRCOMP

R291

VTT

HYSWING

C358

0.1UF_0402

HCLK_MCH15

HCLK_MCH#15

HXRCOMP

R292

24.9_1%_0402

VTT

C C

100_1%_0402

B B

R82

221_1%_0402

HXSWING

R81

VTT

0.1UF_0402

R289

54.9_1%_0402

HYSCOMP

C129

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

HCLK_MCH

HCLK_MCH#

W11

AB7

AA9

AB8

AA4

AA7

AA2

AA6

AA10

AA1

AB4

AC9

AB11

AC11

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD10

AD4

AC8

AG2

AG1

H1

H3

G1

G2

H4

K11

G4

T10

U7

U9

U11

T11

W9

W7

U5

W6

W4

W3

W5

Y10

W2

U1

W1

F1

J1

J6

K2

K9

K1

K7

J8

J3

T3

T1

T8

T4

T9

T5

Y3

Y7

Y8

E1

E2

E4

Y1

U21A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

945GM_A1

H9

H_A#_3

C9

H_A#_4

E11

H_A#_5

G11

H_A#_6

F11

H_A#_7

G12

H_A#_8

F9

H_A#_9

H11

H_A#_10

J12

H_A#_11

G14

H_A#_12

D9

H_A#_13

J14

H_A#_14

H13

H_A#_15

J15

H_A#_16

F14

H_A#_17

D12

H_A#_18

A11

H_A#_19

C11

H_A#_20

A12

H_A#_21

A13

H_A#_22

E13

H_A#_23

G13

H_A#_24

F12

H_A#_25

B12

H_A#_26

B14

H_A#_27

C12

H_A#_28

A14

H_A#_29

C14

H_A#_30

D14

H_A#_31

E8

H_ADS#

H_AVREF

H_BNR#

H_BPRI#

H_BREQ#0

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_DVREF

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_CPUSLP#

H_TRDY#

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

H_ADSTB#_0

H_ADSTB#_1

H_CPURST#

HOST

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

ADS#

HASTB#0

HASTB#1

BNR#

BPRI#

BREQ0#

CPURST#

DBSY#

DEFER#

H_DPWR#

DRDY#

DBI#0

DBI#1

DBI#2

DBI#3

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HIT#

HITM#

HLOCK#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

RS#0

RS#1

RS#2

HCPUSLP#_GMCH

HTRDY#

HA#[3..31] 3

ADS# 3

HASTB#0 3

HASTB#1 3

BNR# 3

BPRI# 3

BREQ0# 3

CPURST# 3

DBSY# 3

DEFER# 3

H_DPWR# 3

DRDY# 3

DBI#[0..3] 3

HDSTBN#[0..3] 3

HDSTBP#[0..3] 3

HIT# 3

HITM# 3

HLOCK# 3

HREQ#[0..4] 3

RS#[0..2] 3

R296 0R_0603

HTRDY# 3

CPUSLP# 3

as close as to

GMCH J13 pin

HVREF

C346

0.1UF_0402

C105

0.1UF_0402

CPURST#

VTT

100_1%_0402

VTT

R286

R287

200_1%_0402

R77

X_54.9_1%_0402

HASTB#[0..1]3

HASTB#[0..1]

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

Calistoga-1 (HOST)

MS-1019

1

0.A

of

644Thursday, September 22, 2005

Page 7

5

4

3

2

1

CFG[3:17] Internal Pull up

CFG[18:19] Internal Pull down

U21B

TP8

TP9

TP47

TP46

TP42

TP43

TP45

D D

X_2.2K_0402

LOW=DMIX2

HIGH=DMIX4

R288

80.6_1%

R76

80.6_1%

PM_BMBUSY#19

THERMTRIP_GMCH#17

MCH_ICH_SYNC#18

M_RCOMPN

M_RCOMPP

NB_PWRGD32

NB_RST#18

C C

B B

+1_8VSUS

TP37

TP4

TP6

TP7

TP17

TP21

MCH_BSEL015

MCH_BSEL115

MCH_BSEL215

CFG_5

R66

PM_EXTTS-0

PM_EXTTS-1

NB_PWRGD

TP16

TP20

TP10

X_2.2K_0402

T32

R32

F3

F7

AG11

AF11

H7

J19

A41

A35

A34

D28

D27

K16

K18

J18

F18

E15

F15

E18

D19

D16

G16

CFG_10

E16

CFG_11

D15

CFG_12

G15

CFG_13

K15

C15

CFG_15

H16

CFG_16

G18

H15

CFG_18

J25

CFG_19

K27

J26

G28

F25

H26

G6

AH33

AH34

H28

H27

K28

H32

D1

C41

C1

BA41

BA40

BA39

BA3

BA2

BA1

B41

B2

AY41

AY1

AW41

AW1

A40

A4

A39

A3

NB strapping

R70

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

PM_THRMTRIP#

PWROK

RSTIN#

SDVO_CTRLCLK

SDVO_CTRLDATA

ICH_SYNC#

CLK_REQ#

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

945GM_A1

R73

X_2.2K_0402

RSVD CFG

PM

MISC

NC

X_2.2K_0402

SM_OCDCOMP_0

SM_OCDCOMP_1

DDR MUXING

SM_RCOMP#

D_REFCLKIN#

D_REFCLKIN

D_REFSSCLKIN#

D_REFSSCLKIN

DMI CLK

CFG_15CFG_13CFG_12 CFG_16

R54

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP

SM_VREF_0

SM_VREF_1

G_CLKIN#

G_CLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

X_2.2K_0402

R59

AY35

AR1

AW7

AW40

AW35

AT1

AY7

AY40

AU20

AT20

BA29

AY29

AW13

AW12

AY21

AW21

AL20

AF10

BA13

BA12

AY20

AU21

AV9

AT9

AK1

AK41

AF33

AG33

A27

A26

C40

D41

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

CKE0

CKE1

CKE2

CKE3

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

M_RCOMPN

M_RCOMPP

CLK_PCIE_3GPLL# 15

CLK_PCIE_3GPLL 15

DOT96# 15

DOT96 15

DREFSSCLK# 15

DREFSSCLK 15

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

CLK_SDRAM0 12

CLK_SDRAM1 12

CLK_SDRAM2 13

CLK_SDRAM3 13

CLK_SDRAM#0 12

CLK_SDRAM#1 12

CLK_SDRAM#2 13

CLK_SDRAM#3 13

CKE0 12,14

CKE1 12,14

CKE2 13,14

CKE3 13,14

SM_CS#0 12,14

SM_CS#1 12,14

SM_CS#2 13,14

SM_CS#3 13,14

TP38

TP44

SM_ODT0 12,14

SM_ODT1 12,14

SM_ODT2 13,14

SM_ODT3 13,14

945GMDDR_VREF

DMI_TXN0 2 0

DMI_TXN1 2 0

DMI_TXN2 2 0

DMI_TXN3 2 0

DMI_TXP0 20

DMI_TXP1 20

DMI_TXP2 20

DMI_TXP3 20

DMI_RXN0 20

DMI_RXN1 20

DMI_RXN2 20

DMI_RXN3 20

DMI_RXP0 20

DMI_RXP1 20

DMI_RXP2 20

DMI_RXP3 20

R39

X_2.2K_0402

CFG_19

Place 150 ohm termination

resistors close to GMCH

+1_8VSUS

R276

10K_1%

R275

10K_1%

+3VRUN +3VRUN

R68

X_2.2K_0402

R278

1.5K_1%

Place 150 ohm termination

resistors close to GMCH

SVIDEO_A14

SVIDEO_B14

SVIDEO_C14

R283 150_1%

R284 150_1%

R285 150_1%

R282 150_1%_0402

R281 150_1%_0402

R280 150_1%_0402

C310

0.1UF_0402

945GMDDR_VREF

C316

0.1UF_0402

as close as

915GM(ALVISO)

CFG_11CFG_10

R67

X_2.2K_0402

VGA_VSYNC16

C357

0.1UF_0402

X_2.2K_0402

VGA_BLU16

VGA_GRN16

VGA_RED16

VGA_DATA16

VGA_HSYNC16

R42

CFG_18

LDDC_CLK16

LDDC_DATA16

LVDS_VDDEN16

TXL_A_CLK#16

TXL_A_CLK+16

TXL_B_CLK#16

TXL_B_CLK+16

VGA_CLK16

TP13

ELON16

TP14

TP12

TP5

A_TXL0#16

A_TXL1#16

A_TXL2#16

A_TXL0+16

A_TXL1+16

A_TXL2+16

B_TXL0#16

B_TXL1#16

B_TXL2#16

B_TXL0+16

B_TXL1+16

B_TXL2+16

R52 4.99K_1%

VGA_CLK

VGA_DATA

R46 39_0402

R51 39_0402

EXTTS-D12,13

TP11

TP15

R53

255_1%

TV_IREF

U21C

D32

L_BKLTCTL

J30

L_BKLTEN

H30

L_CTLACLK

H29

L_CTLB_DATA

G26

L_DDC_CLK

G25

L_DDC_DATA

B38

L_IBG

C35

L_VBG

F32

L_VDDEN

C33

L_VREFH

C32

L_VREFL

A33

LA_CLK#

A32

LA_CLK

E27

LB_CLK#

E26

LB_CLK

C37

LA_DATA#_0

B35

LA_DATA#_1

A37

LA_DATA#_2

B37

LA_DATA_0

B34

LA_DATA_1

A36

LA_DATA_2

G30

LB_DATA#_0

D30

LB_DATA#_1

F29

LB_DATA#_2

F30

LB_DATA_0

D29

LB_DATA_1

F28

LB_DATA_2

A16

TV_DACA_OUT

C18

TV_DACB_OUT

A19

TV_DACC_OUT

J20

TV_IREF

B16

TV_IRTNA

B18

TV_IRTNB

B19

TV_IRTNC

K30

TV_DCONSEL0

J29

TV_DCONSEL1

E23

CRT_BLUE

D23

CRT_BLUE#

C22

CRT_GREEN

B22

CRT_GREEN#

A21

CRT_RED

B21

CRT_RED#

C26

CRT_DDC_CLK

C25

CRT_DDC_DATA

G23

CRT_HSYNC

J22

CRT_IREF

H23

CRT_VSYNC

945GM_A1

R36 0R_0603

0R_0402

SDVO_TVCLKIN# / EXP_A_RXN_0

SDVO_FLDSTALL# / EXP_A_RXN_2

LVDS TV VGA

SDVO_TVCLKIN / EXP_A_RXP_0

SDVO_FLDSTALL / EXP_A_RXP_2

SDVOB_RED# / EXP_A_TXN_0

SDVOB_GREEN# / EXP_A_TXN_1

SDVOB_BLUE# / EXP_A_TXN_2

PCI-EXPRESS GRAPHICS / SDVO

SDVOC_RED# / SDVOB_ALPHA# / EXP_A_TXN_4

SDVOC_RED / SDVOB_ALPHA / EXP_A_TXP_4

PM_EXTTS-0

R41 10K_0402

R40 10K_0402

MCH_BSEL2

R61

SDVOB_CLKN / EXP_A_TXN_3

SDVOC_GREEN# / EXP_A_TXN_5

SDVOC_BLUE# / EXP_A_TXN_6

SDVOC_CLKN / EXP_A_TXN_7

SDVOB_RED / EXP_A_TXP_0

SDVOB_GREEN / EXP_A_TXP_1

SDVOB_BLUE / EXP_A_TXP_2

SDVOB_CLKP / EXP_A_TXP_3

SDVOC_GREEN / EXP_A_TXP_5

SDVOC_BLUE / EXP_A_TXP_6

SDVOC_CLKP / EXP_A_TXP_7

EXP_A_COMPI

EXP_A_COMPO

SDVO_INT# / EXP_A_RXN_1

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

SDVO_INT / EXP_A_RXP_1

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_8

EXP_A_TXN_9

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

LDDC_CLK

LDDC_DATAPM_EXTTS-1

EXP_COMP

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

R44 10K_0402

R48 10K_0402

R277 24.9_1%_0402

Please within

500mils of

ICH

+3VRUN+3VRUN

+1_5VRUN

A A

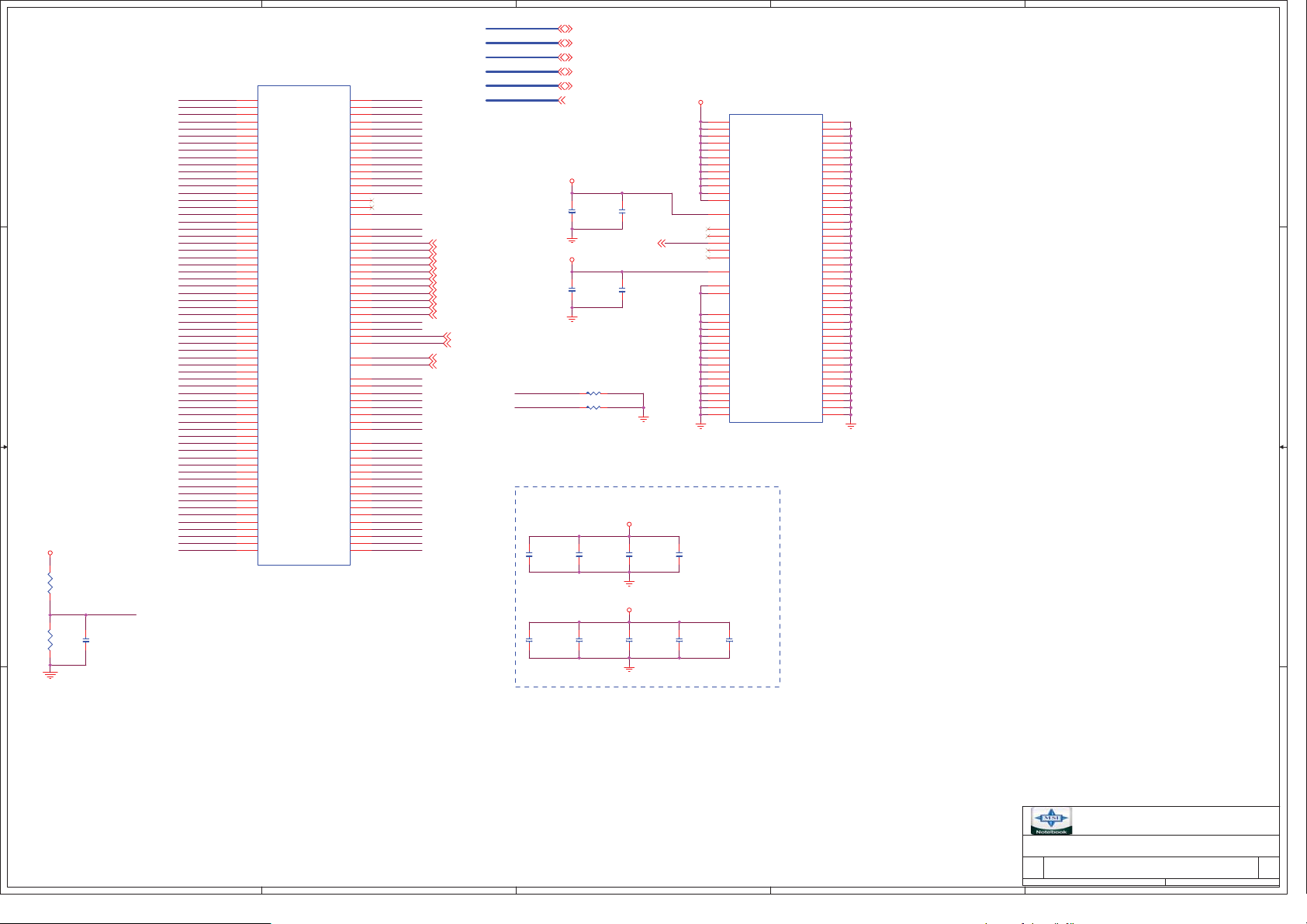

CFG2~0

001=FSB533

011=FSB667

5

CFG4~3

RES

IPU

CFG5

0=DMI x 2

1=DMI x 4

(default)

IPU

CFG6

0=Moby Dick

1=Calistoga

IPU

CFG7

0=Res

1=Mobile

CPU

IPU

CFG8,10,11

14,15,17

RES

IPU

4

CFG9

0=reverse

1=normal

PCI-E Graphic lane

IPU

CFG16

0=disable

1=enable

FSB dynamic ODT

CFG18

0=1.05V

1=1.5V

(default)

IPU IPD IPD

CFG19

0=normal

1=reverse

DMI lane reverse

3

Title

Size Document Number Rev

Custom

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

Calistoga-2 (DMI/VGA)

MS-1034

1

0.A

of

744Thursday, September 22, 2005

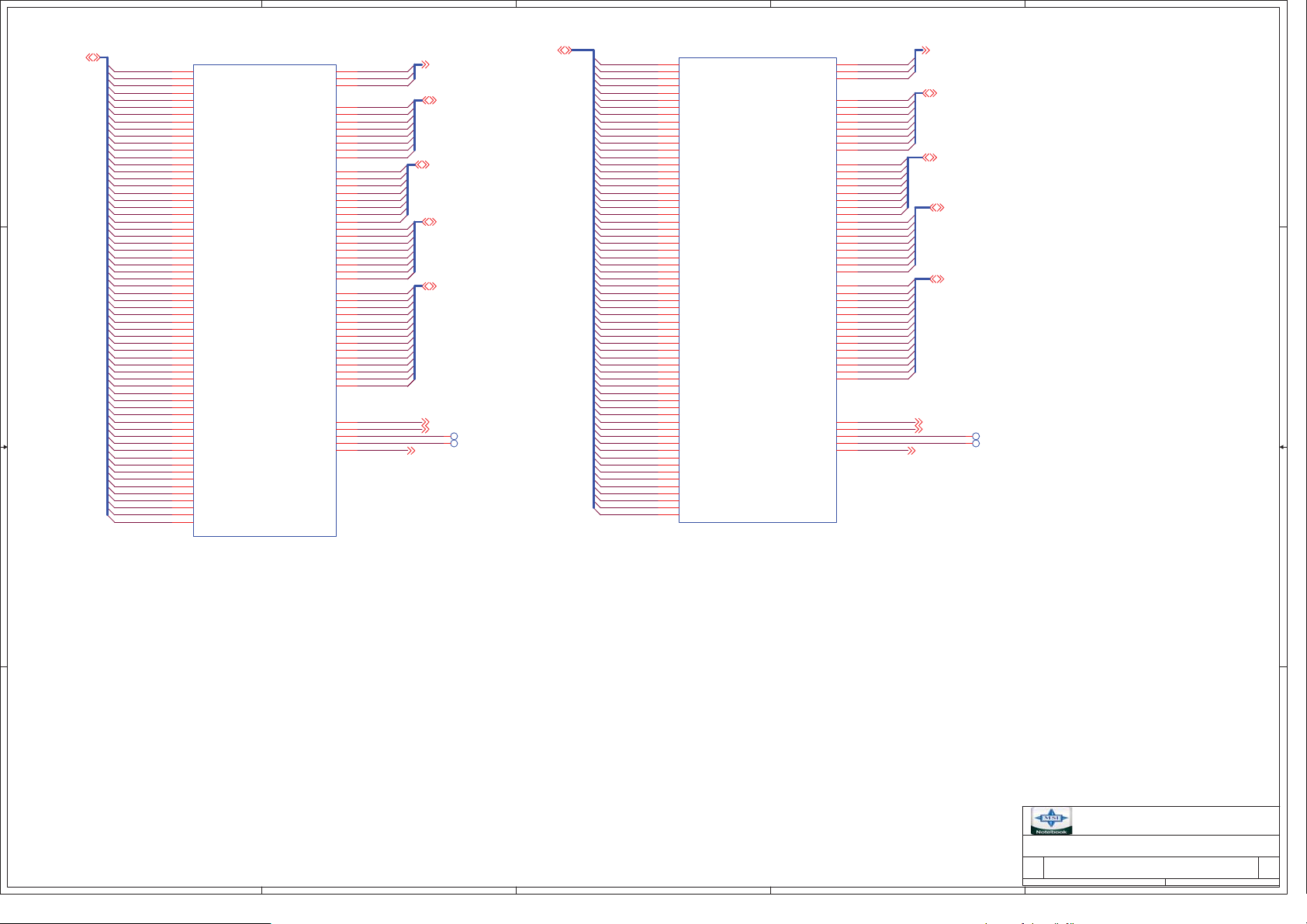

Page 8

5

4

3

2

1

SA_MD[0..63]12

D D

C C

B B

SA_MD0

SA_MD1

SA_MD2

SA_MD3

SA_MD4

SA_MD5

SA_MD6

SA_MD7

SA_MD8

SA_MD9

SA_MD10

SA_MD11

SA_MD12

SA_MD13

SA_MD14

SA_MD15

SA_MD16

SA_MD17

SA_MD18

SA_MD19

SA_MD20

SA_MD21

SA_MD22

SA_MD23

SA_MD24

SA_MD25

SA_MD26

SA_MD27

SA_MD28

SA_MD29

SA_MD30

SA_MD31

SA_MD32

SA_MD33

SA_MD34

SA_MD35

SA_MD36

SA_MD37

SA_MD38

SA_MD39

SA_MD40

SA_MD41

SA_MD42

SA_MD43

SA_MD44

SA_MD45

SA_MD46

SA_MD47

SA_MD48

SA_MD49

SA_MD50

SA_MD51

SA_MD52

SA_MD53

SA_MD54

SA_MD55

SA_MD56

SA_MD57

SA_MD58

SA_MD59

SA_MD60

SA_MD61

SA_MD62

SA_MD63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

U21D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

945GM_A1

SA_BS_0

SA_BS_1

SA_BS_2

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

DDR SYSTEM MEMORY A

SA_CAS#

SA_RAS#

SA_RCVEMIN#

SA_RCVENOUT#

SA_WE#

AV14

BA20

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AY13

AW14

AK23

AK24

AY14

SA_BS#1

SA_BS#2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

SA_BS#0

AU12

SA_BS#[0..2] 12,14

SA_DM[0..7] 12

SA_DQS[0..7] 12

SA_DQS#[0..7] 12

SA_MA[0..13] 12,14

SA_CAS# 12,14

SA_RAS# 12,14

1

1

SA_WE# 12,14

TP33

.

TP25

.

SB_MD[0..63]13 SB_BS#[0..2] 13,14

SB_MD0

SB_MD1

SB_MD2

SB_MD3

SB_MD4

SB_MD5

SB_MD6

SB_MD7

SB_MD8

SB_MD9

SB_MD10

SB_MD11

SB_MD12

SB_MD13

SB_MD14

SB_MD15

SB_MD16

SB_MD17

SB_MD18

SB_MD19

SB_MD20

SB_MD21

SB_MD22

SB_MD23

SB_MD24

SB_MD25

SB_MD26

SB_MD27

SB_MD28

SB_MD29

SB_MD30

SB_MD31

SB_MD32

SB_MD33

SB_MD34

SB_MD35

SB_MD36

SB_MD37

SB_MD38

SB_MD39

SB_MD40

SB_MD41

SB_MD42

SB_MD43

SB_MD44

SB_MD45

SB_MD46

SB_MD47

SB_MD48

SB_MD49

SB_MD50

SB_MD51

SB_MD52

SB_MD53

SB_MD54

SB_MD55

SB_MD56

SB_MD57

SB_MD58

SB_MD59

SB_MD60

SB_MD61

SB_MD62

SB_MD63

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AN10

AK13

AH11

AK10

BA10

AW10

AW4

AY10

AW5

BA4

AY9

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ9

AJ8

AJ5

AJ3

U21E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

945GM_A1

SB_BS_0

SB_BS_1

SB_BS_2

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

DDR SYSTEM MEMORY B

SB_MA_13

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

AV23

AY28

AK36

AR38

AT36

BA31

AL17

AH8

BA5

AN4

AM39

AT39

AU35

AR29

AR16

AR10

AR7

AN5

AM40

AU39

AT35

AP29

AP16

AT10

AT7

AP5

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

AR24

AU23

AK16

AK18

AR27

SB_BS#1

SB_BS#2

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

SB_DM[0..7] 13

SB_DQS[0..7] 13

SB_CAS# 13,14

SB_RAS# 13,14

SB_WE# 13,14

SB_BS#0

AT24

SB_DQS#[0..7] 13

SB_MA[0..13] 13,14

1

TP41

.

1

TP40

.

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

Calistoga-3 (DDR)

MS-1034

1

0.A

of

844Thursday, September 22, 2005

Page 9

5

VTT

D D

C C

B B

A A

AA33

W33

AA32

W32

M32

AA31

W31

M31

AA30

W30

M30

AA29

W29

M29

AB28

AA28

M28

M27

M25

M24

AB23

AA23

M23

AC22

AB22

W22

M22

AC21

AA21

W21

M21

AC20

AB20

W20

M20

AB19

AA19

M19

M18

M17

M16

P33

N33

L33

J33

Y32

V32

P32

N32

L32

J32

V31

T31

R31

P31

N31

Y30

V30

U30

T30

R30

P30

N30

L30

Y29

V29

U29

R29

P29

L29

Y28

V28

U28

T28

R28

P28

N28

L28

P27

N27

L27

P26

N26

L26

N25

L25

P24

N24

Y23

P23

N23

L23

Y22

P22

N22

L22

N21

L21

Y20

P20

N20

L20

Y19

N19

L19

N18

L18

P17

N17

N16

L16

5

U21F

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

945GM_A1

VCC

VCC_SM_0

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_SM_13

VCC_SM_14

VCC_SM_15

VCC_SM_16

VCC_SM_17

VCC_SM_18

VCC_SM_19

VCC_SM_20

VCC_SM_21

VCC_SM_22

VCC_SM_23

VCC_SM_24

VCC_SM_25

VCC_SM_26

VCC_SM_27

VCC_SM_28

VCC_SM_29

VCC_SM_30

VCC_SM_31

VCC_SM_32

VCC_SM_33

VCC_SM_34

VCC_SM_35

VCC_SM_36

VCC_SM_37

VCC_SM_38

VCC_SM_39

VCC_SM_40

VCC_SM_41

VCC_SM_42

VCC_SM_43

VCC_SM_44

VCC_SM_45

VCC_SM_46

VCC_SM_47

VCC_SM_48

VCC_SM_49

VCC_SM_50

VCC_SM_51

VCC_SM_52

VCC_SM_53

VCC_SM_54

VCC_SM_55

VCC_SM_56

VCC_SM_57

VCC_SM_58

VCC_SM_59

VCC_SM_60

VCC_SM_61

VCC_SM_62

VCC_SM_63

VCC_SM_64

VCC_SM_65

VCC_SM_66

VCC_SM_67

VCC_SM_68

VCC_SM_69

VCC_SM_70

VCC_SM_71

VCC_SM_72

VCC_SM_73

VCC_SM_74

VCC_SM_75

VCC_SM_76

VCC_SM_77

VCC_SM_78

VCC_SM_79

VCC_SM_80

VCC_SM_81

VCC_SM_82

VCC_SM_83

VCC_SM_84

VCC_SM_85

VCC_SM_86

VCC_SM_87

VCC_SM_88

VCC_SM_89

VCC_SM_90

VCC_SM_91

VCC_SM_92

VCC_SM_93

VCC_SM_94

VCC_SM_95

VCC_SM_96

VCC_SM_97

VCC_SM_98

VCC_SM_99

VCC_SM_100

VCC_SM_101

VCC_SM_102

VCC_SM_103

VCC_SM_104

VCC_SM_105

VCC_SM_106

VCC_SM_107

AU41

AT41

AM41

AU40

BA34

AY34

AW34

AV34

AU34

AT34

AR34

BA30

AY30

AW30

AV30

AU30

AT30

AR30

AP30

AN30

AM30

AM29

AL29

AK29

AJ29

AH29

AJ28

AH28

AJ27

AH27

BA26

AY26

AW26

AV26

AU26

AT26

AR26

AJ26

AH26

AJ25

AH25

AJ24

AH24

BA23

AJ23

BA22

AY22

AW22

AV22

AU22

AT22

AR22

AP22

AK22

AJ22

AK21

AK20

BA19

AY19

AW19

AV19

AU19

AT19

AR19

AP19

AK19

AJ19

AJ18

AJ17

AH17

AJ16

AH16

BA15

AY15

AW15

AV15

AU15

AT15

AR15

AJ15

AJ14

AJ13

AH13

AK12

AJ12

AH12

AG12

AK11

BA8

AY8

AW8

AV8

AT8

AR8

AP8

BA6

AY6

AW6

AV6

AT6

AR6

AP6

AN6

AL6

AK6

AJ6

AV1

AJ1

C362

0.47UF

C317

0.47UF

C326

0.47UF

4

C339

0.47UF

C359

0.47UF

4

C312

0.47UF

0822

Modify

C331

10UF/10V_0805

EC5

C220U2.5SP-LF

0822

Modify

+1_8VSUS

C101

10UF/10V_0805

VTT

12

+

EC4

C220U2.5SP-LF

C114

0.22UF/10V

12

+

C49

10UF/10V_0805

0822

Modify

12

+

X_C220U2.5SP-LF

C111

10UF/10V_0805

C28

3

C67

0.22UF/10V

C123

1UF

3

C78

0.22UF/10V

AD27

AC27

AB27

AA27

W27

AD26

AC26

AB26

AA26

W26

AD25

AC25

AB25

AA25

W25

AD24

AC24

AB24

AA24

W24

AD23

AD22

AD21

AD20

AD19

AD18

AC18

AB18

AA18

W18

Y27

V27

U27

T27

R27

Y26

V26

U26

T26

R26

Y25

V25

U25

T25

R25

Y24

V24

U24

T24

R24

V23

U23

T23

R23

V22

U22

T22

R22

V21

U21

T21

R21

V20

U20

T20

R20

V19

U19

T19

Y18

V18

U18

T18

U21G

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF68

VCC_NCTF69

VCC_NCTF70

VCC_NCTF71

VCC_NCTF72

945GM_A1

2

NCTF

2

VSS_NCTF0

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VCCAUX_NCTF0

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VCCAUX_NCTF39

VCCAUX_NCTF40

VCCAUX_NCTF41

VCCAUX_NCTF42

VCCAUX_NCTF43

VCCAUX_NCTF44

VCCAUX_NCTF45

VCCAUX_NCTF46

VCCAUX_NCTF47

VCCAUX_NCTF48

VCCAUX_NCTF49

VCCAUX_NCTF50

VCCAUX_NCTF51

VCCAUX_NCTF52

VCCAUX_NCTF53

VCCAUX_NCTF54

VCCAUX_NCTF55

VCCAUX_NCTF56

VCCAUX_NCTF57

1

AE27

AE26

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AC17

Y17

U17

AG27

AF27

AG26

AF26

AG25

AF25

AG24

AF24

AG23

AF23

AG22

AF22

AG21

AF21

AG20

AF20

AG19

AF19

R19

AG18

AF18

R18

AG17

AF17

AE17

AD17

AB17

AA17

W17

V17

T17

R17

AG16

AF16

AE16

AD16

AC16

AB16

AA16

Y16

W16

V16

U16

T16

R16

AG15

AF15

AE15

AD15

AC15

AB15

AA15

Y15

W15

V15

U15

T15

R15

Title

Calistoga (Power-1)

Size Document Number Rev

Custom

Date: Sheet

+1_5VRUN

MICRO-STAR INT'L CO.,LTD.

MS-1034

1

944Thursday, September 22, 2005

0.A

of

Page 10

5

+3_3VCCA_TVDAC

D D

C315

0.1UF_0402

R21 1_1%

AC

L14

180L200m_500

+

12

+

12

C364

22UF/6.3V_0805

C365

22UF/6.3V_0805

0822

Modify

C311

22UF/6.3V_0805

VCCA_3GPLL

VTT

VCCA_CRTDAC

+1_5VRUN_DPLLA

C65

0.1UF_0402

+1_5VRUN_DPLLB

C36

0.1UF_0402

+1_5VRUN_HPLL

C354

0.1UF_0402

+1_5VRUN_MPLL

C353

0.1UF_0402

C313

X_10UF/10V_0805

RUN_ON31,35,37

+1_5VRUN +1_5VRUN_VCC3G

L40 90nH1500m_1206

C314

10UF/10V_0805

+1_5VRUN

L9 1U500m_0805

C C

B B

A A

+2_5VRUN

0822

Modify

C73

0.1UF_0402

+1_5VRUN

0822

Modify

R33 10

C68

22UF/6.3V_0805

D6 RB551V-30

L42 10U100m_0805

EC7

100UF/2V

L41 10U100m_0805

EC6

100UF/2V

L46 120L500m_350_0402

L45 120L500m_350_0402

5

C62

22UF/6.3V_0805

4

L16

180L200m_500

L15

180L200m_500

L44

180L200m_500

L13

180L200m_500

+3_3VCCA_TVDAC

0822

Modify

Q7

2N7002

4

C91

10UF/10V_0805

C102

0.1UF_0402

C100

0.1UF_0402

C332

0.1UF_0402

C83

0.1UF_0402

R63 10

0822

Modify

+5VRUN

DS

G

R47

10K_0402

+3_3VCCA_TVDACA

C92

22000pF_0402

+3_3VCCA_TVDACB

C88

22000pF_0402

+3_3VCCA_TVDACC

C87

22000pF_0402

C79

22000pF_0402

D29 RB551V-30

AC

+5VRUN

C322

1UF

Q6

2N7002

G

+3_3VCCA_TVBG

+1_5VRUN

R43

10K_0402

1

VIN

2

GND

3

SHDN#

APL5151-33BC-TRL

DS

VCCA_CRTDAC

+2_5VRUN

10UF/10V_0805

+1_5VRUN

U20

VOUT

BP

C58

0.1UF_0402

0.1UF_0402

C39

0822

Modify

L43

180L200m_500

+1_5VRUN

150mA

5

4

3

+2_5VRUN

2.2UF/6.3V

VCCA_3GPLL

C48

0.1UF_0402

C89

C40

0.1UF_0402

+3_3VCCA_TVDACC

0822

Modify

180L200m_500

L18

0822

Modify

+3_3VCCA_TVDAC

C325

0.33UF_0603

3

+2_5VRUN

C72

0.1UF_0402

C54

C30

10UF/10V_0805

C338

22000pF_0402

0822

Modify

+3_3VCCA_TVDACB

+1_5V_TVDAC

C328

0.1UF_0402

SPEC.=120mA

C333

1UF

+1_5VRUN_VCC3G

R62 0R_0603

+1_5VRUN_DPLLA

+1_5VRUN_DPLLB

+3_3VCCA_TVBG

+3_3VCCA_TVDACA

+1_5VRUN

+1_5VRUN

C329

22000pF_0402

C97

C107

0.1UF_0402

22000pF_0402

+1_5VRUN

+2_5VRUN

C38

0.1UF_0402

+1_5VRUN_HPLL

+1_5VRUN_MPLL

+3VRUN

C324

2.2UF/6.3V

AJ41

AB41

AC33

AK31

AF31

AE31

AC31

AL30

AK30

AJ30

AH30

AG30

AF30

AE30

AD30

AC30

AG29

AF29

AE29

AD29

AC29

AG28

AF28

AE28

AH22

AJ21

AH21

AJ20

AH20

AH19

AH15

AH14

AG14

AF14

AE14

AF13

AE13

AF12

AE12

AD12

H22

C30

B30

A30

Y41

V41

R41

N41

G41

H41

F21

E21

G21

B26

C39

AF1

A38

B39

AF2

H20

G20

E19

F19

C20

D20

E20

F20

AH1

AH2

A28

B28

C28

D21

A23

B23

B25

H19

P19

P16

P15

Y14

L41

2

U21H

VCCSYNC

VCC_TXLVDS0

VCC_TXLVDS1

VCC_TXLVDS2

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL

VCCA_3GBG

VSSA_3GBG

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_LVDS

VSSA_LVDS

VCCA_MPLL

VCCA_TVBG

VSSA_TVBG

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCD_HMPLL0

VCCD_HMPLL1

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCD_TVDAC

VCC_HV0

VCC_HV1

VCC_HV2

VCC_QTVDAC

VCCAUX0

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCAUX5

VCCAUX6

VCCAUX7

VCCAUX8

VCCAUX9

VCCAUX10

VCCAUX11

VCCAUX12

VCCAUX13

VCCAUX14

VCCAUX15

VCCAUX16

VCCAUX17

VCCAUX18

VCCAUX19

VCCAUX20

VCCAUX21

VCCAUX22

VCCAUX23

VCCAUX24

VCCAUX25

VCCAUX26

VCCAUX27

VCCAUX28

VCCAUX29

VCCAUX30

VCCAUX31

VCCAUX32

VCCAUX33

VCCAUX34

VCCAUX35

VCCAUX36

VCCAUX37

VCCAUX38

VCCAUX39

VCCAUX40

945GM_A1

2

POWER

1

VTT

AC14

VTT_0

AB14

VTT_1

W14

VTT_2

V14

VTT_3

T14

VTT_4

R14

VTT_5

P14

VTT_6

N14

VTT_7

M14

VTT_8

L14

VTT_9

AD13

VTT_10

AC13

VTT_11

AB13

VTT_12

AA13

VTT_13

Y13

VTT_14

W13

VTT_15

V13

VTT_16

U13

VTT_17

T13

VTT_18

R13

VTT_19

N13

VTT_20

M13

VTT_21

L13

VTT_22

AB12

VTT_23

AA12

VTT_24

Y12

VTT_25

W12

VTT_26

V12

VTT_27

U12

VTT_28

T12

VTT_29

R12

VTT_30

P12

VTT_31

N12

VTT_32

M12

VTT_33

L12

VTT_34

R11

VTT_35

P11

VTT_36

N11

VTT_37

M11

VTT_38

R10

VTT_39

P10

VTT_40

N10

VTT_41

M10

VTT_42

P9

VTT_43

N9

VTT_44

M9

VTT_45

R8

VTT_46

P8

VTT_47

N8

VTT_48

M8

VTT_49

P7

VTT_50

N7

VTT_51

M7

VTT_52

R6

VTT_53

P6

VTT_54

M6

VTT_55

A6

VTT_56

R5

VTT_57

P5

VTT_58

N5

VTT_59

M5

VTT_60

P4

VTT_61

N4

VTT_62

M4

VTT_63

R3

VTT_64

P3

VTT_65

N3

VTT_66

M3

VTT_67

R2

VTT_68

P2

VTT_69

M2

VTT_70

D2

VTT_71

AB1

VTT_72

R1

VTT_73

P1

VTT_74

N1

VTT_75

M1

VTT_76

Title

Size Document Number Rev

Custom

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

Calistoga-5 (Power)

MS-1034

1

C361

0.47UF

C352

0.47UF

C360

0.22UF/10V

of

10 44Thursday, September 22, 2005

0.A

Page 11

5

U21I

AC41

VSS_0

AA41

VSS_1

W41

VSS_2

T41

VSS_3

P41

VSS_4

M41

VSS_5

J41

VSS_6

F41

VSS_7

AV40

VSS_8

AP40

VSS_9

AN40

VSS_10

AK40

VSS_11

D D

C C

B B

AJ40

AH40

AG40

AF40

AE40

AY39

AW39

AV39

AR39

AN39

AJ39

AC39

AB39

AA39

W39

M39

G39

AT38

AM38

AH38

AG38

AF38

AE38

AK37

AH37

AB37

AA37

W37

M37

G37

AY36

AW36

AN36

AH36

AG36

AF36

AE36

AC36

BA35

AV35

AR35

AH35

AB35

AA35

W35

M35

G35

AN34

B40

Y39

V39

T39

R39

P39

N39

L39

J39

H39

F39

D39

C38

Y37

V37

T37

R37

P37

N37

L37

J37

H37

F37

D37

C36

B36

Y35

V35

T35

R35

P35

N35

L35

J35

H35

F35

D35

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

945GM_A1

VSS

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

AK34

AG34

AF34

AE34

AC34

C34

AW33

AV33

AR33

AE33

AB33

Y33

V33

T33

R33

M33

H33

G33

F33

D33

B33

AH32

AG32

AF32

AE32

AC32

AB32

G32

B32

AY31

AV31

AN31

AJ31

AG31

AB31

Y31

AB30

E30

AT29

AN29

AB29

T29

N29

K29

G29

E29

C29

B29

A29

BA28

AW28

AU28

AP28

AM28

AD28

AC28

W28

J28

E28

AP27

AM27

AK27

J27

G27

F27

C27

B27

AN26

M26

K26

F26

D26

AK25

P25

K25

H25

E25

D25

A25

BA24

AU24

AL24

AW23

4

AT23

AN23

AM23

AH23

AC23

W23

AA22

G22

BA21

AV21

AR21

AN21

AL21

AB21

AW20

AR20

AM20

AA20

AN19

AC19

W19

G19

AH18

AY17

AR17

AP17

AM17

AK17

AV16

AN16

AL16

AN15

AM15

AK15

M15

BA14

AT14

AK14

AD14

AA14

AV13

AR13

AN13

AM13

AL13

AG13

AY12

AC12

AD11

AA11

AV10

3

U21J

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

K23

VSS_186

J23

VSS_187

F23

VSS_188

C23

VSS_189

VSS_190

K22

VSS_191

VSS_192

F22

VSS_193

E22

VSS_194

D22

VSS_195

A22

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

Y21

VSS_203

P21

VSS_204

K21

VSS_205

J21

VSS_206

H21

VSS_207

C21

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

K20

VSS_213

B20

VSS_214

A20

VSS_215

VSS_216

VSS_217

VSS_218

K19

VSS_219

VSS_220

C19

VSS_221

VSS_222

P18

VSS_223

H18

VSS_224

D18

VSS_225

A18

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

J16

VSS_235

F16

VSS_236

C16

VSS_237

VSS_238

VSS_239

VSS_240

N15

VSS_241

VSS_242

L15

VSS_243

B15

VSS_244

A15

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

U14

VSS_251

K14

VSS_252

H14

VSS_253

E14

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

P13

VSS_261

F13

VSS_262

D13

VSS_263

B13

VSS_264

VSS_265

VSS_266

K12

VSS_267

H12

VSS_268

E12

VSS_269

VSS_270

VSS_271

Y11

VSS_272

J11

VSS_273

D11

VSS_274

B11

VSS_275

VSS_276

945GM_A1

VSS

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354