Page 1

5

www.schematic-x.blogspot.com

4

3

2

1

SYS POWER

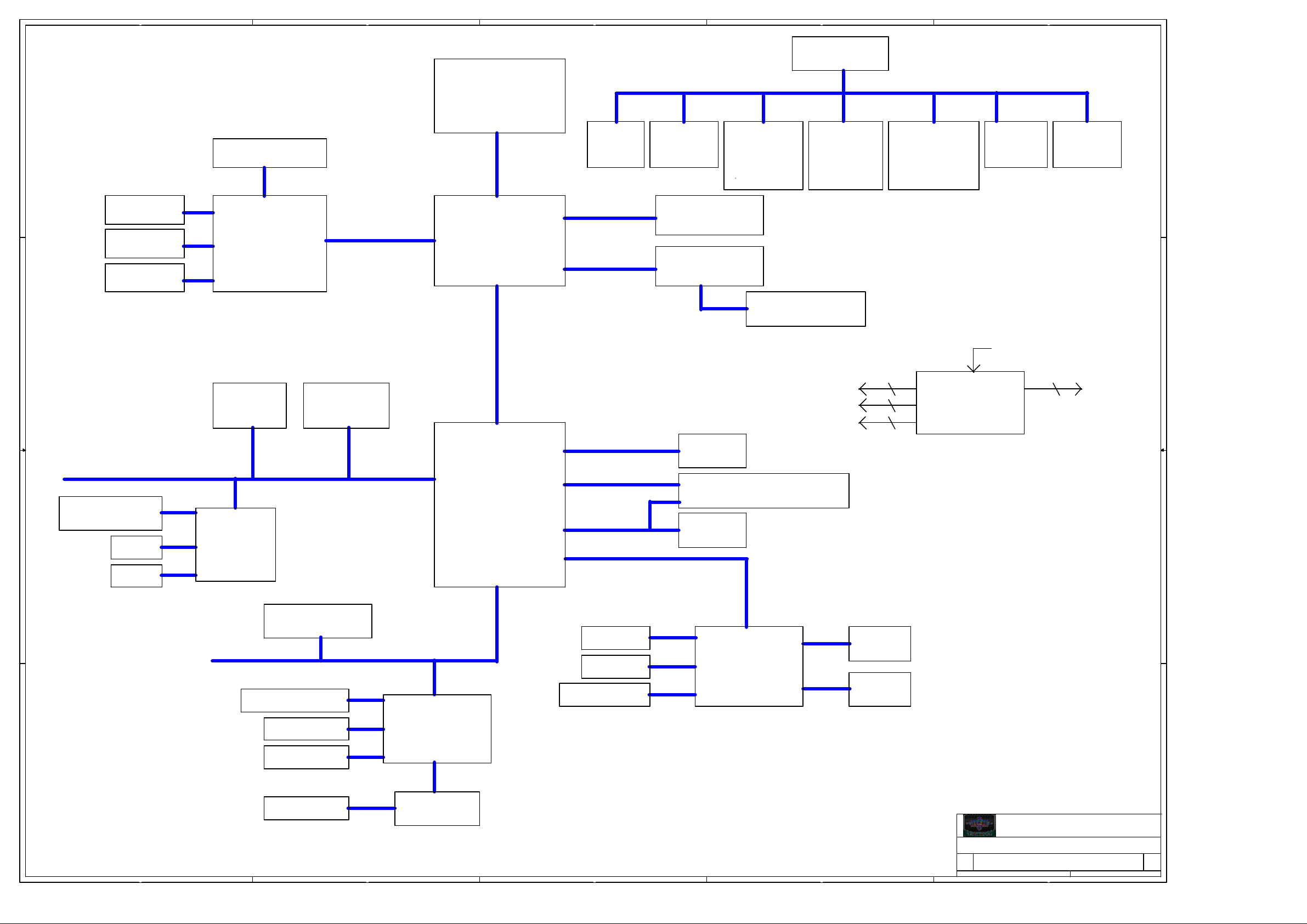

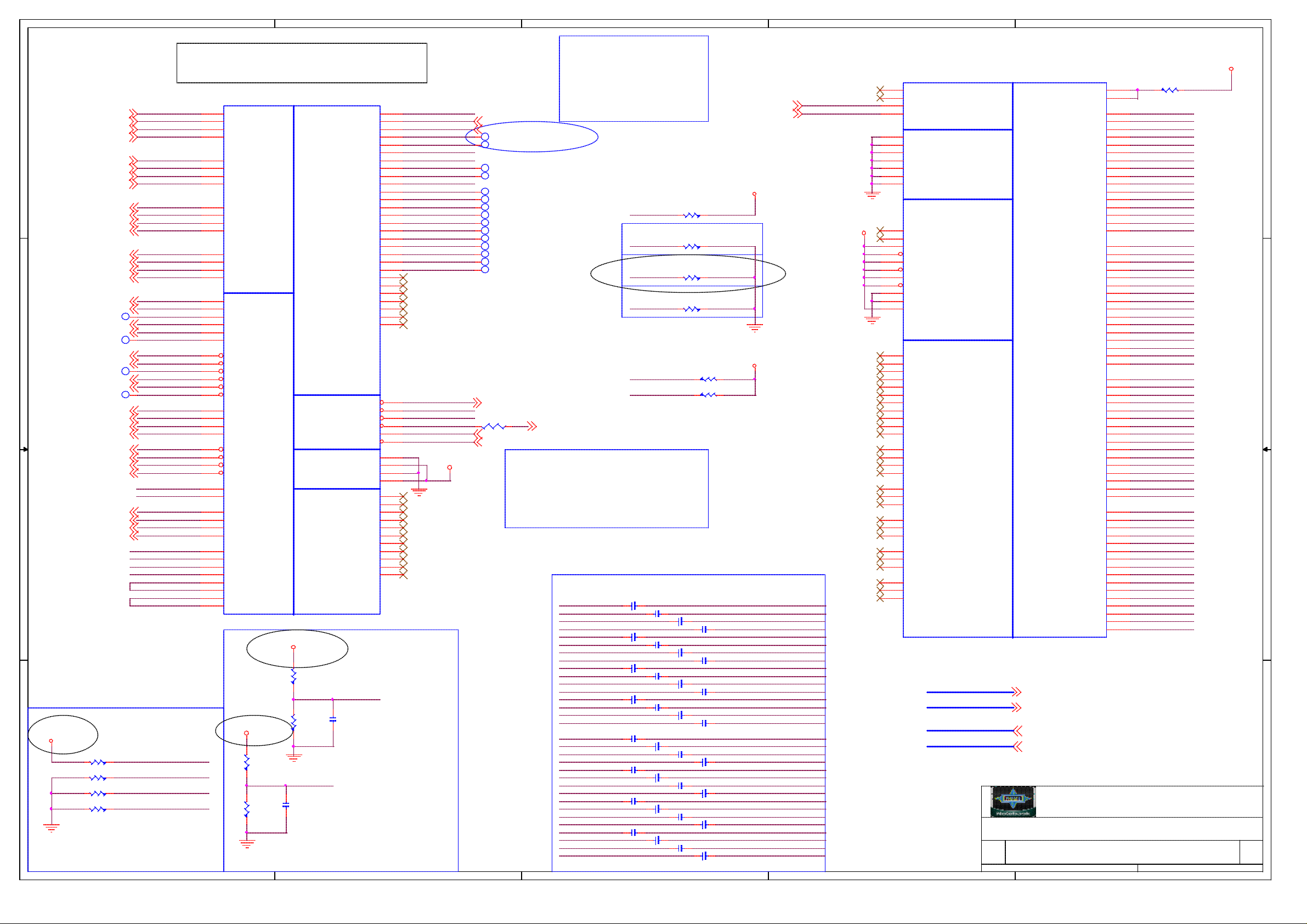

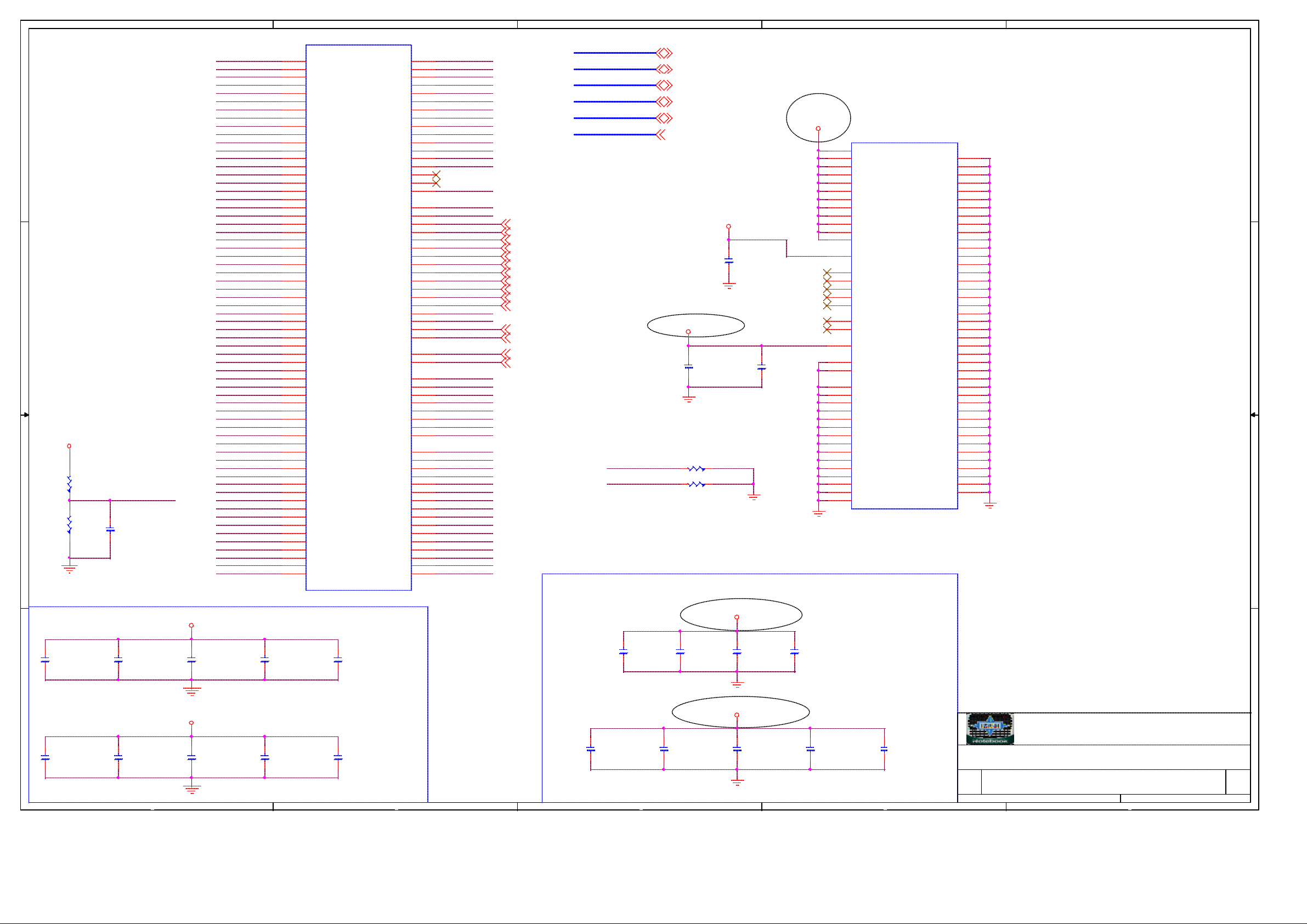

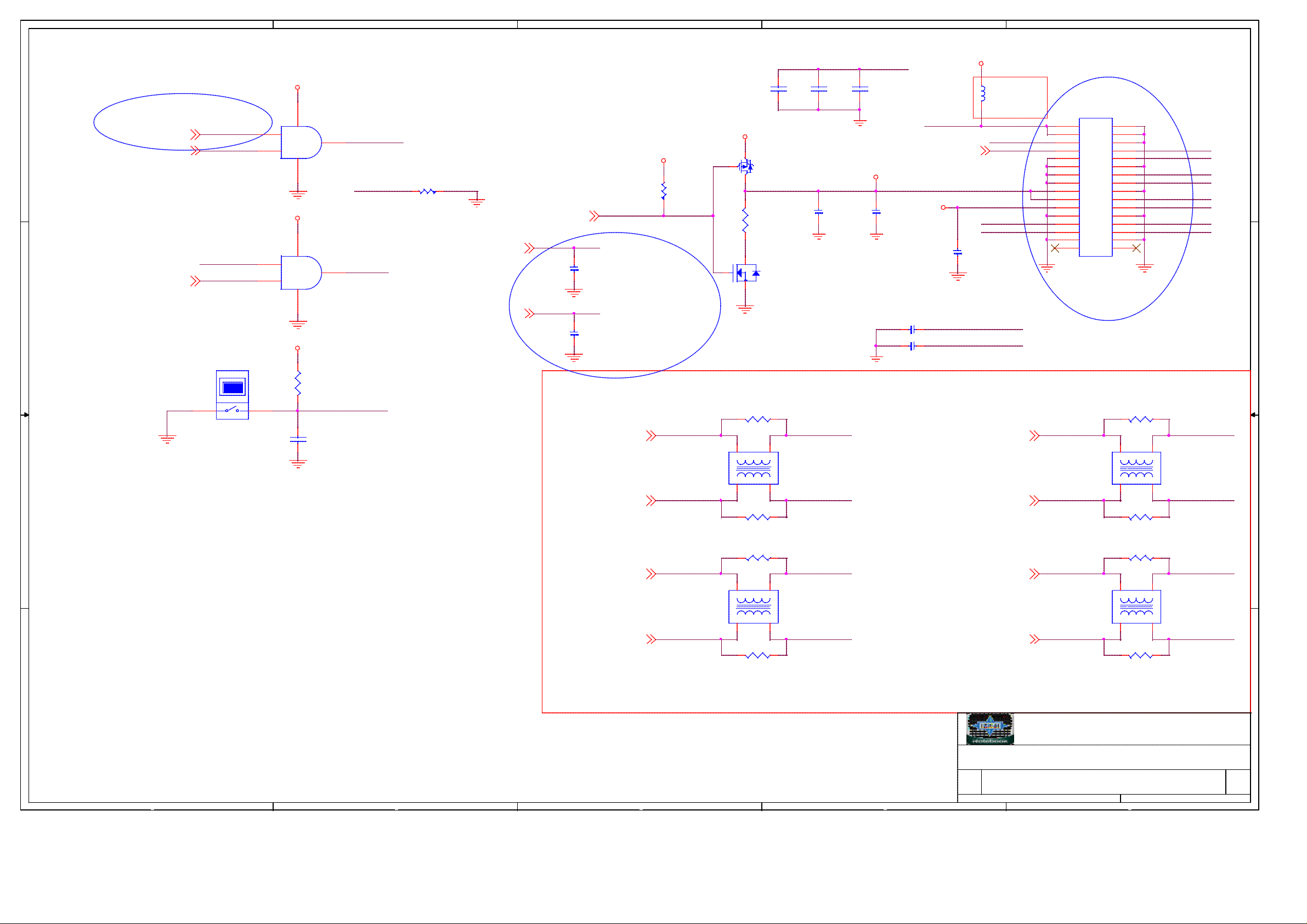

MS1022 BLOCK DIAGRAM

Dothan

SOCKET 479

Rev. 0B

D D

VRAM

PAGE 44 , 45 , 46

LCD DISPLAY

PAGE 15

CRT DISPLAY

PAGE 16

TV OUT

PAGE 23

C C

VGA

nVDIA

NV44M

PAGE 40,41,42,43

PCI LAN

RTL 8101L

PAGE 26

PCI Express

MINI PCI

PAGE 27

478 uFCPGA

PAGE 3,4,5

HOST BUS

FSB

400 / 533 MHz

NORTH BRIDGE

INTEL

915PM

PAGE 6,7,8,9,10

DMI

CHARGER

PAGE 33

Channel A

400/533 MHz

Channel B

400/533 MHz

DC JACK &

SELECTOR

PAGE 34

+1.1/1.25V

VGA Power

PCI-E Power

PAGE 35

DDR II SO-DIMM 0

PAGE 11

DDR II SO-DIMM 1

PAGE 12

+1.5V +3V +5V

+1.8VDDRM

+1.2V

OZ816

PAGE 36

TERMINAL RESISTOR

PAGE 13

100/133MHZ HOST

100MHZ PCIE

33MHZ PCI

VTT

+2.5VSMDDR_VTERM

LM1117MPX-ADJ

PAGE 37

CLK GENERATOR

ICS 954206

PAGE 14

SC1403SC1470

PAGE 38

14MHZ CRYSTAL

CPU POWER

MAX1907

PAGE 39

14MHZ SB

ATA 100

SOUTH BRIDGE

PCI BUS

INTEL

FLASH CARD

SD / MS / MMC

1394

B B

PCMCIA

O2

OZ711MP1

PAGE 24,25

ICH6-M

PAGE 17,18,19,20

PCI EXPRESS

USB 2.0 / 1.1

LPC BUS

HDD & ODD

PAGE 21

NEW CARD (PCI-E/USB PCI-E)

PAGE 22

USB2.0 x3

PAGE 23

MDC & BLUETOOTH

PAGE 28

AZALIA

LINE OUT & SPDIF

PAGE 30

MIC IN

PAGE 30

Internal MIC

A A

PAGE 30

AUDIO CODEC

REALTEK

ALC880

PAGE 29

SMART FAN

PAGE 32

TOUCH PAD

PAGE 31

INTERNAL K/B

PAGE 31

K/B CONTROLLER

ENE 3910

PAGE 31

BIOS ROM

PAGE 31

CIR

PAGE 31

5

Internal SPK

PAGE 30

Audio AMP

PAGE 30

Title

Size Document Number Rev

C

4

3

2

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

BLOCK DIAGRAM

MS-1022

1

0.B

1 48Thursday, June 09, 2005

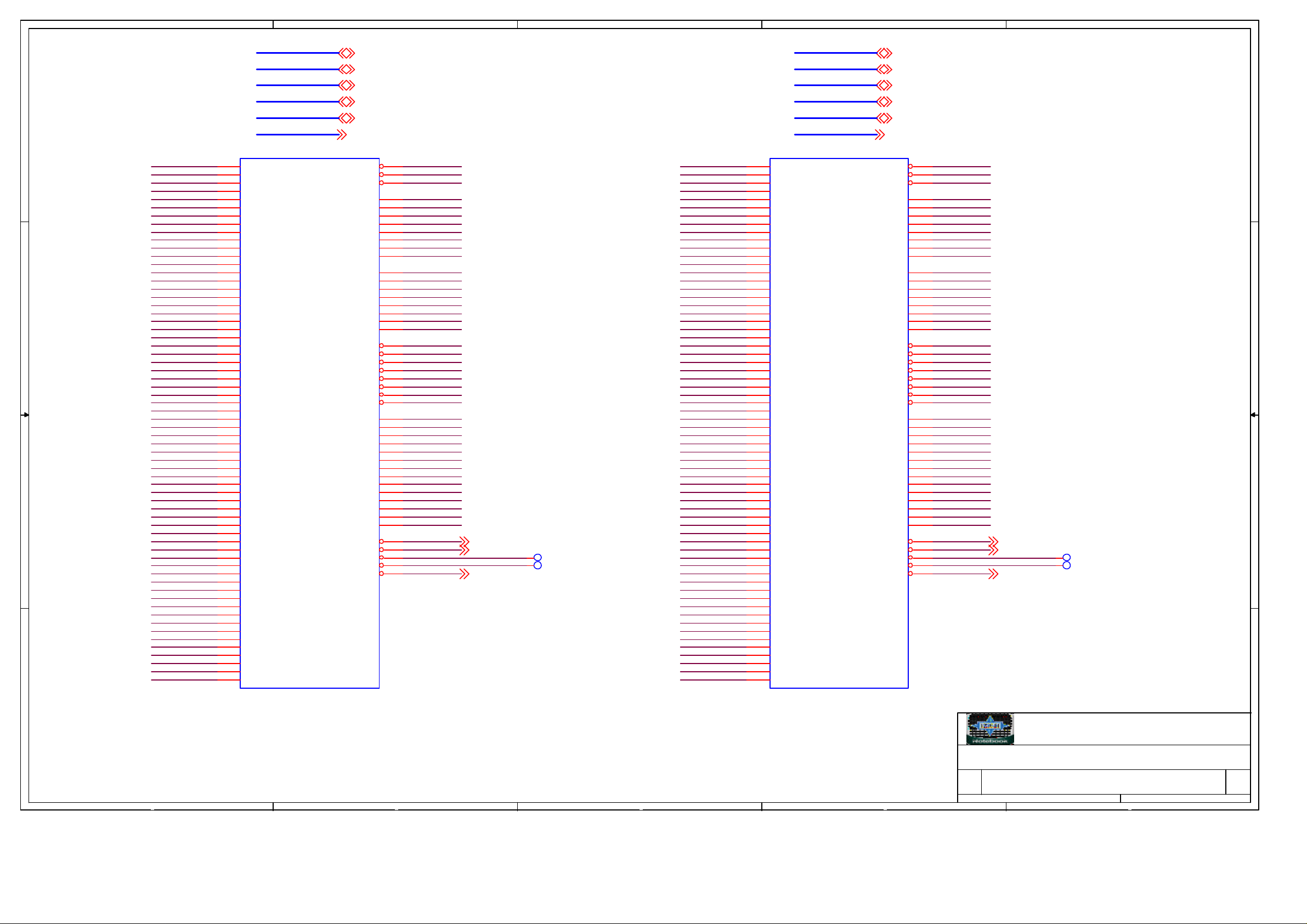

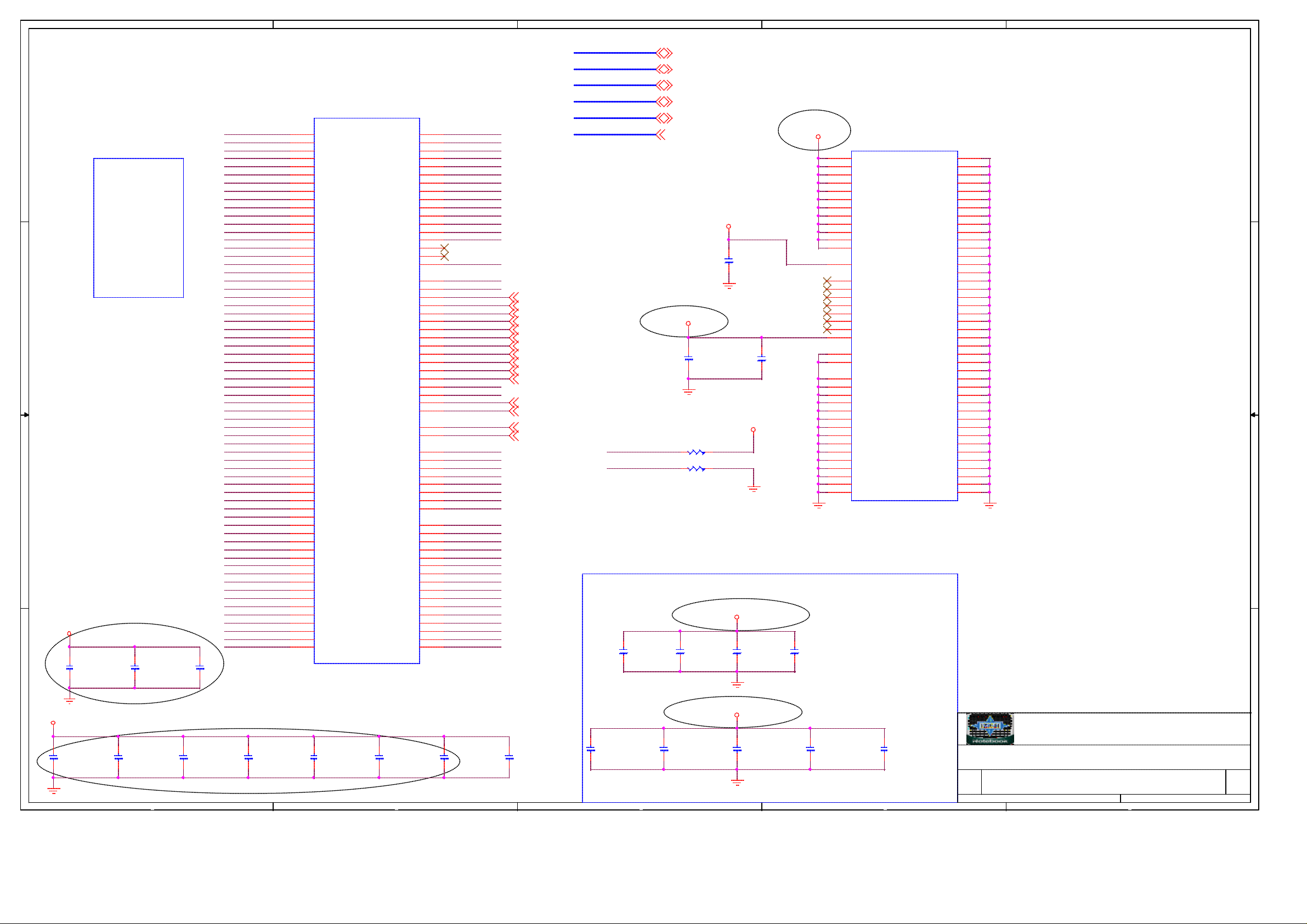

Page 2

5

4

3

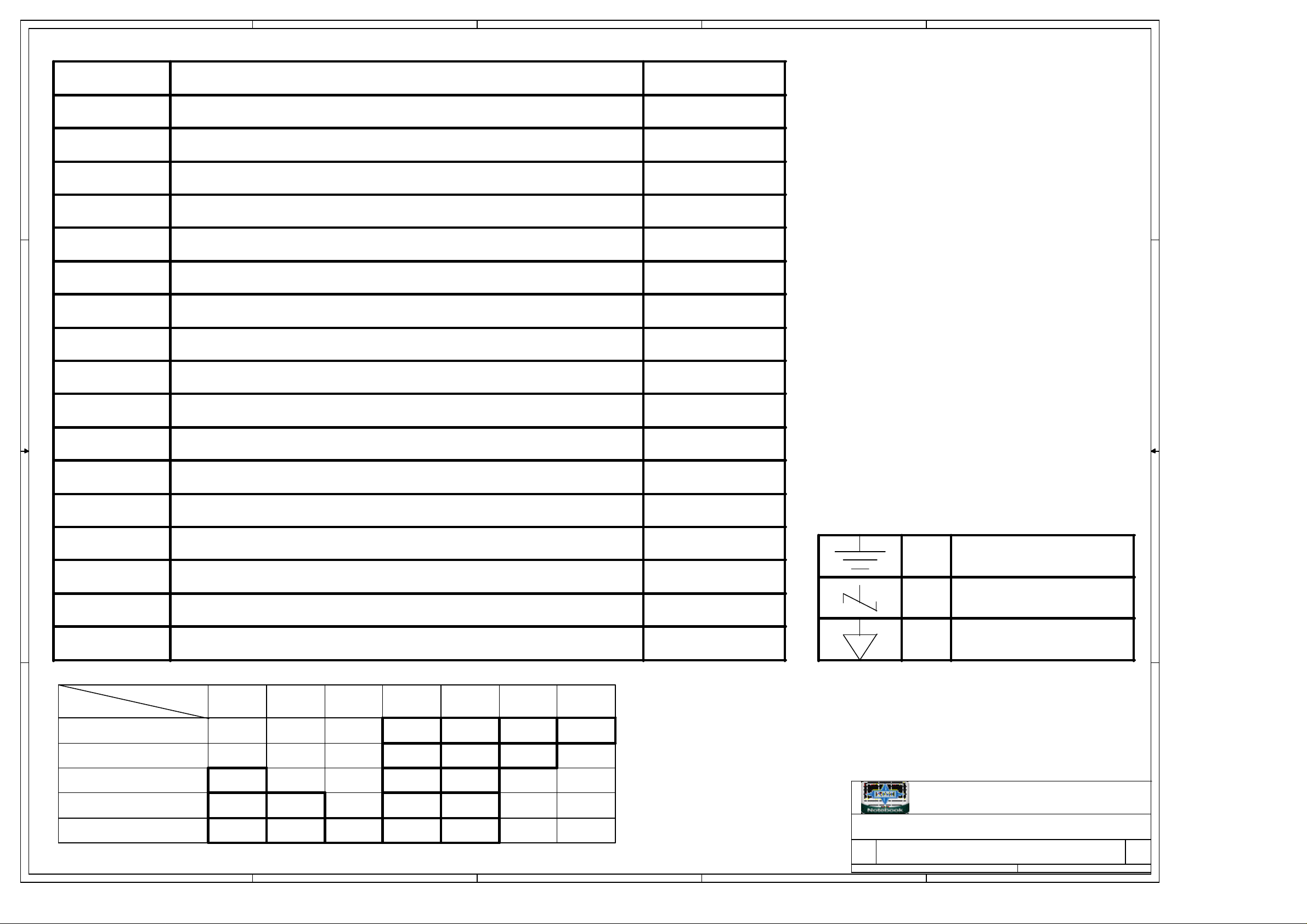

Voltage Rails

Voltage Description Control Signal

2

1

PWR_SRC

D D

+5VALW

+5VSUS

+5VRUN

+3VALW

+3VSUS

+3VRUN

C C

+2_5VSUS

+1_8VDDRM

AC ADAPTER OR BATTERY IN

5.0V always on power rail

5.0V switched power rail(off in S3-S5)

3.3V always on power rail

3.3V power rail

3.3V switched power rail(off in S3-S5)

2.5V power rail

2.5V switched power rail(off in S3-S5)

1.8V power rail DDR (off in S4-S5)

ON5

SUS_ON5.0V power rail

RUN_ON

ON3

SUS_ON

RUN_ON

+3VSUS

+3VRUN+2_5VRUN

PM_SLP_S4#

+1_8VRUN

+1_5VRUN

SMDDR_VTERM

VTT

B B

VHCORE

1.8V switched power rail(off in S3-S5)

1.5V switched power rail(off in S3-S5)

0.9V DDR Termination voltage (off in S3-S5)

1.05V rail for Processor & Alviso I/O(off in S3-S5)

Core Voltage for Processor(off in S3-S5)

ADD5V 5.0V Power rail Audio codec(off in S3-S5)

+1_2VPEX 1.2V switched power rail(off in S3-S5) +5VRUN

RUN_ON

+5VRUN

RUN_ON

+5VRUN

VTT_PWRGD

PM_SLP_S3#

GND

DIGTIAL GROUD

AGND AUDIO GND

PGND POWER Analogy GND

POWER STATES

STATE

Full ON

S1M(Power On Suspend)

A A

S3( Suspend to RAM)

SIGNAL Clocks

SLP_S3#

HIGH ON

HIGH

LOW

SLP_S4#

HIGH

HIGH

SLP_S5#

HIGH

HIGH

HIGH

+V*ALWAYS

ON

ON

+V*SUS

ON

ON

ON

+V*RUN

ON

ON

OFF

ONHIGH

LOW

OFF

S4( Suspend to Disk)

S5 / Soft OFF

Note : WHEN AC MODE , System turn on then +V*SUS will always keep high

5

LOW

LOW

LOW

LOW

HIGH

ON

ONLOW

4

ON

ON

OFF

OFF

OFF

OFF

3

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

Custom

2

Date: Sheet of

PLATFORM

MS-1022

0.B

2 48Thursday, June 09, 2005

1

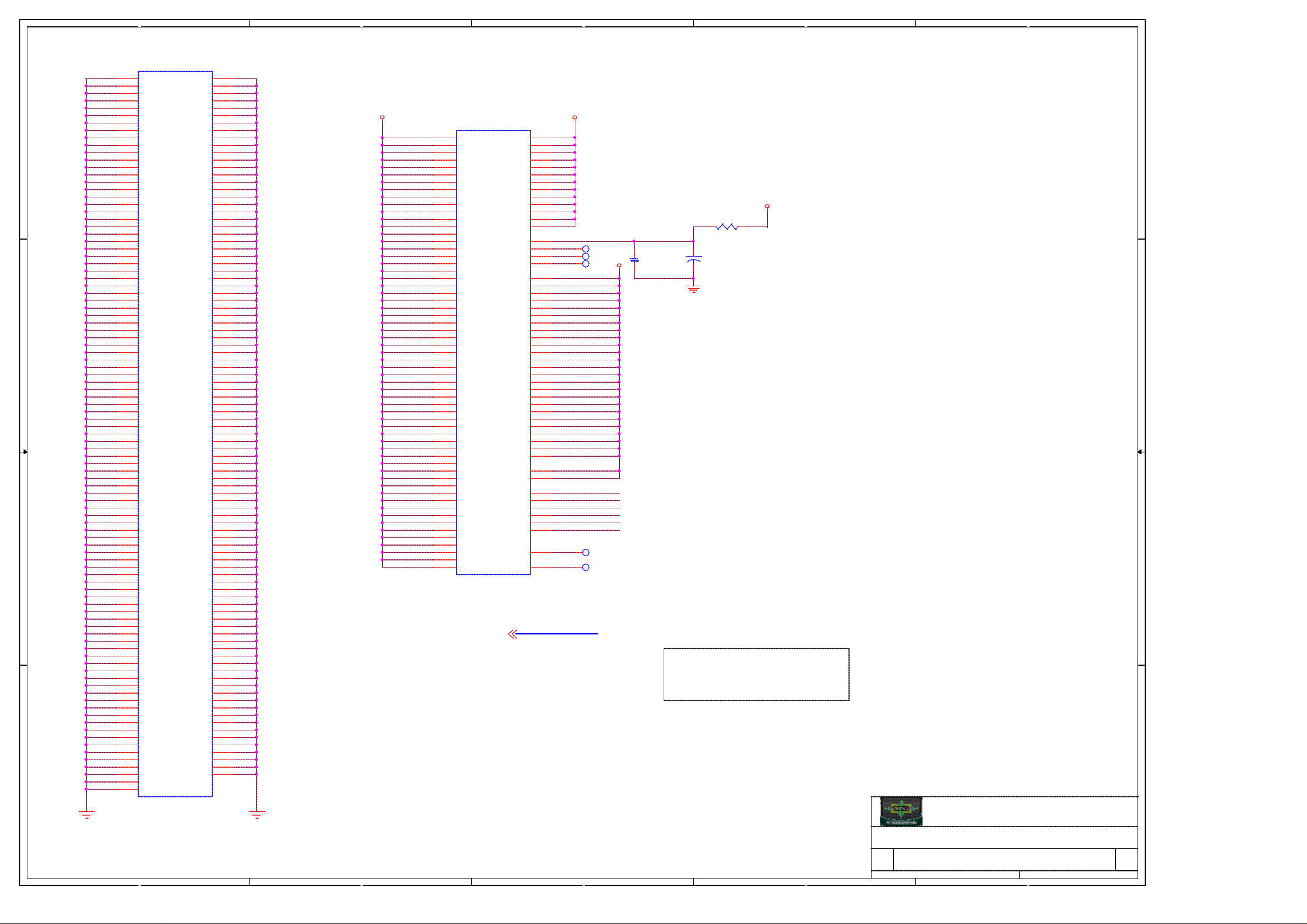

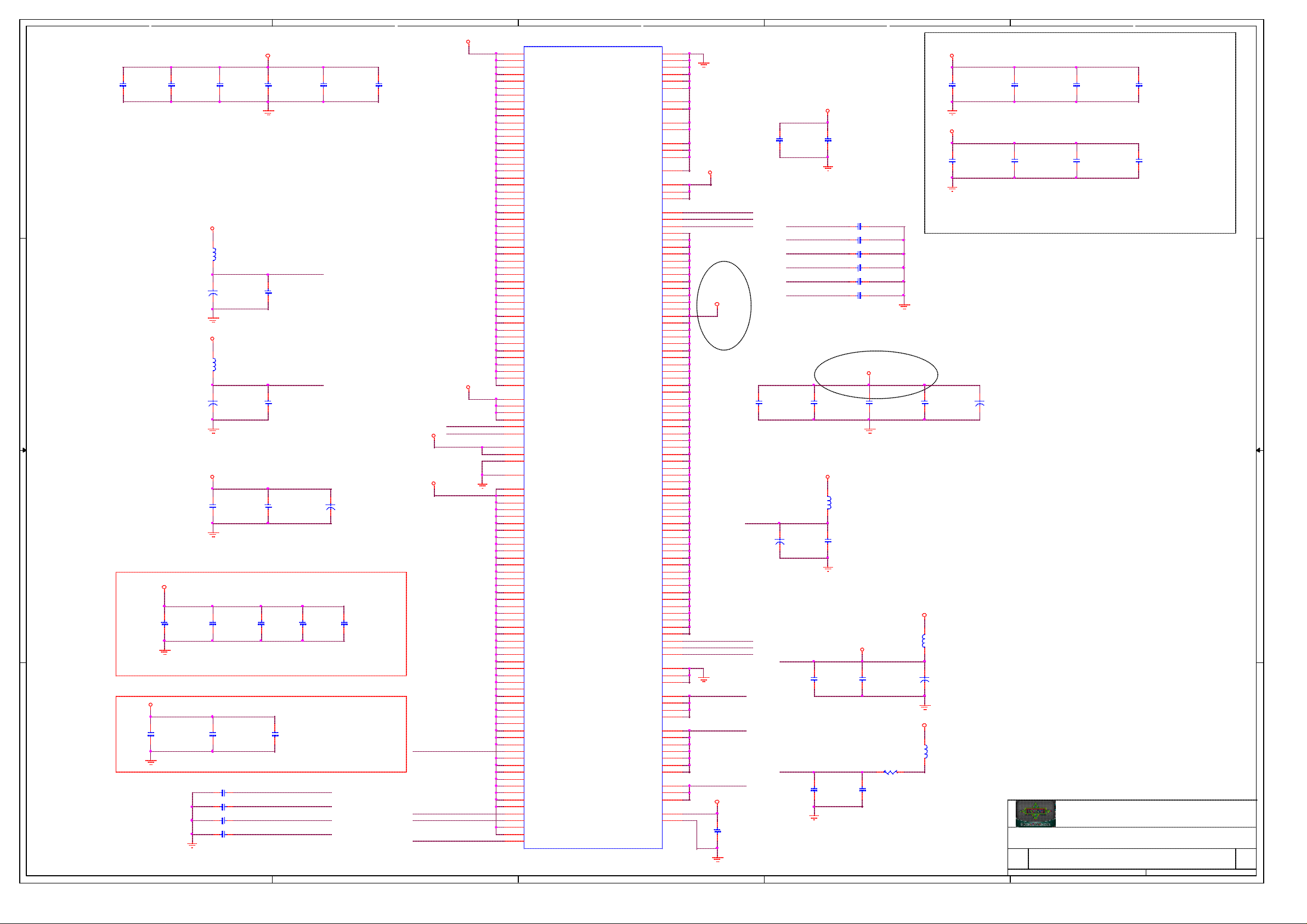

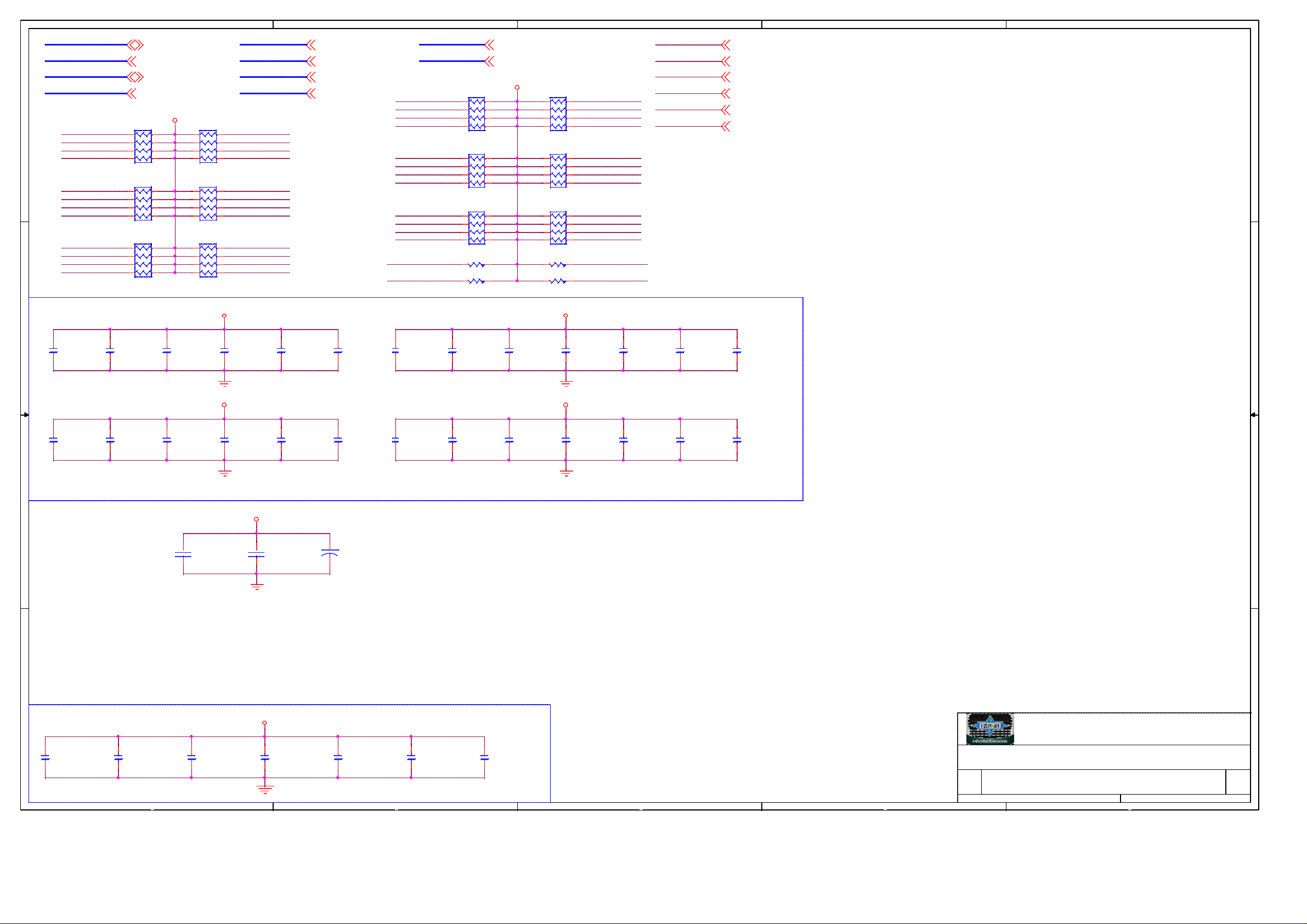

Page 3

5

THERMDA

Cap must close to

thermal sensor

THERMDC

T_CRIT_CPU-31

D D

T_CRIT_CPUTHERMTRIP-

RB37 0_NC

RB35 0

Close to CPU socket

HA-3

HA-4

HA-5

HA-6

HA-7

HA-8

HA-9

HA-10

HA-11

HA-12

HA-13

HA-14

HA-15

HA-16

HASTB-0

HREQ-0

HREQ-1

HREQ-2

HREQ-3

HREQ-4

HA-17

C C

A20M-17

FERR-17

IGNNE-17

STPCLK-17

INTR17

NMI17

SMI-17

B B

HA-18

HA-19

HA-20

HA-21

HA-22

HA-23

HA-24

HA-25

HA-26

HA-27

HA-28

HA-29

HA-30

HA-31

HASTB-1

A20M-

FERR-

IGNNESTPCLK-

INTR

NMI

HA-[3..31]6

RS-[0..2]6

HREQ-[0..4]6

HASTB-[0..1]6 HDSTBP-[0..3]6

U2EB5A

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

U3

ADSTB#0

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

AE5

ADSTB#1

C2

A20M#

D3

FERR#

A3

IGNNE#

C6

STPCLK#

D1

LINT0

D4

LINT1

B4

SMI#

Dothan_Yonah_Processor_Skt

ADDR GROUP 0 ADDR GROUP 1

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

IERR#

CONTROL

LOCK#

RESET#

TRDY#

HITM#

BPM#0

BPM#1

BPM#2

BPM#3

PRDY#

PREQ#

ITP SIGNALS

TRST#

DBR#

PROCHOT#

THERMDA

THERMDC

THERM

THERMTRIP#

ITP_CLK0

ITP_CLK1

BCLK0

BCLK1

H CLK

HA-[3..31]

RS-[0..2]

HREQ-[0..4]

ADS#

BR0#

INIT#

RS0#

RS1#

RS2#

HIT#

TCK

TDI

TDO

TMS

N2

L1

J3

L4

H2

M2

N4

A4

B5

J2

B11

H1

K1

L2

M3

K3

K4

C8

B8

A9

C9

A10

B10

A13

C12

A12

C11

B13

A7

B17

B18

A18

C17

A16

A15

B15

B14

ADSBNRBPRI-

DEFERDRDYDBSY-

BREQ0IERR-

CPU_INITHLOCKCPURST-

RS-0

RS-1

RS-2

HTRDY-

HITHITM-

BPM0BPM1BPM2BPM3BPM4_PRDYBPM5_PREQHTCK

HTDI

HTDO

HTMS

HTRSTDBR-

PROCHOTTHERMDA

THERMDC

THERMTRIP-

ITP_CLK0

ITP_CLK1

CPUCLK0

CPUCLK-0

4

+3VRUN

CB63

2200PF

T_CRIT_A_CPU-

ADS- 6

BNR- 6

BPRI- 6

DEFER- 6

DRDY- 6

DBSY- 6

BREQ0- 6

CPU_INIT- 17

1

.

HLOCK- 6

CPURST- 6

HTRDY- 6

HIT- 6

HITM- 6

1

.

1

.

1

.

1

.

1

.

1

.

1

.

1

.

CPUCLK0 14

CPUCLK-0 14

UB8

1

VDD

2

D+

3

D-

4

T_CRIT_A#

LM86_MSOP8

CB66

0.1UF_0402

TPB16

TPB14

TPB17

TPB20

TPB13

TPB19

TPB15

TPB22

TPB21

THERMTRIP- 7,17

THERMTRIP# :

When the signal transition

SMBCLK

SMBDATA

ALERT#

GND

8

7

6

5

IERRHTMS

HTDI

PROCHOT-

ITP_CLK0

ITP_CLK1

HTCK

HTRST-

to Low ,the ICH6 will

immediately transition to

a S5 state.

EC_SMB_CLK2

EC_SMB_DAT2

R_CPU_THRM_ALERT-

RB26 56

RB30 39_0402

RB29 150_1%_0402

RB32 56

RB27 49.9_1%_0402

RB28 49.9_1%_0402

RB33 27

RB34 680

3

EC_SMB_CLK2 31

EC_SMB_DAT2 31

RB36 0_NC

2/24

VTT

CPU_THRM_ALERT-

VTT

RB18 1K_1%

CB36

0.1UF_0402

RB17 2K_1%

4/8

CPU_THRM_ALERT- 31

HD-0

HD-1

HD-2

HD-3

HD-4

HD-5

HD-6

HD-7

HD-8

HD-9

HD-10

HD-11

HD-12

HD-13

HD-14

HD-15

HDSTBN-0

HDSTBP-0

DBI-0

HD-16

HD-17

HD-18

HD-19

HD-20

HD-21

HD-22

HD-23

HD-24

HD-25

HD-26

HD-27

HD-28

HD-29

HD-30

HD-31

HDSTBN-1

HDSTBP-1

DBI-1

GTLREF

1

1

1

1

1

1

1

TPB10 .

TPB11 .

TPB12 .

TPB18 .

TPB5 .

TPT6 .

TPT7 .

GTLREF < 500 mils

PSIBSEL0

BSEL1

HD-[0..63]6

HDSTBN-[0..3]6

DBI-[0..3]6

2

U2EB5B

A19

#D0

A25

#D1

A22

#D2

B21

#D3

A24

#D4

B26

#D5

A21

#D6

B20

#D7

C20

#D8

B24

#D9

D24

#D10

E24

#D11

C26

#D12

B23

#D13

E23

#D14

C25

#D15

C23

DSTBN0#

C22

DSTBP0#

D25

DINV0#

H23

#D16

G25

#D17

L23

#D18

M26

#D19

H24

#D20

F25

#D21

G24

#D22

J23

#D23

M23

#D24

J25

#D25

L26

#D26

N24

#D27

M25

#D28

H26

#D29

N25

#D30

K25

#D31

K24

DSTBN1#

L24

DSTBP1#

J26

DINV1#

E1

PSI#

C16

BSEL0

C14

BSEL1

B2

NC1

A1

NC2

C3

RSVD2

AF7

RSVD3

AC1

RSVD [GTLREF3]

E26

RSVD [GTLREF1]

AD26

GTLREF0

Dothan_Yonah_Processor_Skt

HD-[0..63]

HDSTBP-[0..3]HASTB-[0..1]

HDSTBN-[0..3]

DBI-[0..3]

Y26

#D32

AA24

#D33

T25

#D34

U23

#D35

DATA GRP 2

DATA GRP 0

DSTBN2#

DSTBP2#

DATA GRP 3

DATA GRP 1

DSTBN3#

DSTBP3#

MISC

DPRSTP#

PWRGOOD

#D36

#D37

#D38

#D39

#D40

#D41

#D42

#D43

#D44

#D45

#D46

#D47

DINV2#

#D48

#D49

#D50

#D51

#D52

#D53

#D54

#D55

#D56

#D57

#D58

#D59

#D60

#D61

#D62

#D63

DINV3#

COMP0

COMP1

COMP2

COMP3

DPSLP#

DPWR#

SLP#

TEST1

TEST2

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

W25

W24

T24

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

AE24

AE25

AD20

P25

P26

AB2

AB1

G1

B7

C19

E4

A6

C5

F23

G1: NC for Dothan and

DPRSTP# for Yonah

HD-32

HD-33

HD-34

HD-35

HD-36

HD-37

HD-38

HD-39

HD-40

HD-41

HD-42

HD-43

HD-44

HD-45

HD-46

HD-47

HDSTBN-2

HDSTBP-2

DBI-2

HD-48

HD-49

HD-50

HD-51

HD-52

HD-53

HD-54

HD-55

HD-56

HD-57

HD-58

HD-59

HD-60

HD-61

HD-62

HD-63

HDSTBN-3

HDSTBP-3

DBI-3

HCOMP0

HCOMP1

HCOMP2

HCOMP3

H_DPRSTPH_DPSLPH_DPWRCPU_PWRGD

CPUSLP-

RB31 1K_NC

RB24 1K_NC

CPU_PWRGD

1

0.5" max length

25 MIL AWAY FROM

HIGH SPEED SIGNAL

RB22 27.4_1%

RB21 54.9_1%_0402

RB19 27.4_1%

RB20 54.9_1%_0402

H_DPRSTP- 17

H_DPSLP- 17

H_DPWR- 6

CPU_PWRGD 17

CPUSLP- 6,17

RB25 200_1%_0402

VTT

A A

MICRO-STAR INT'L CO.,LTD.

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Dothan-1(HOST BUS)

Custom

MS-1022

0.B

1

3 48Thursday, June 09, 2005

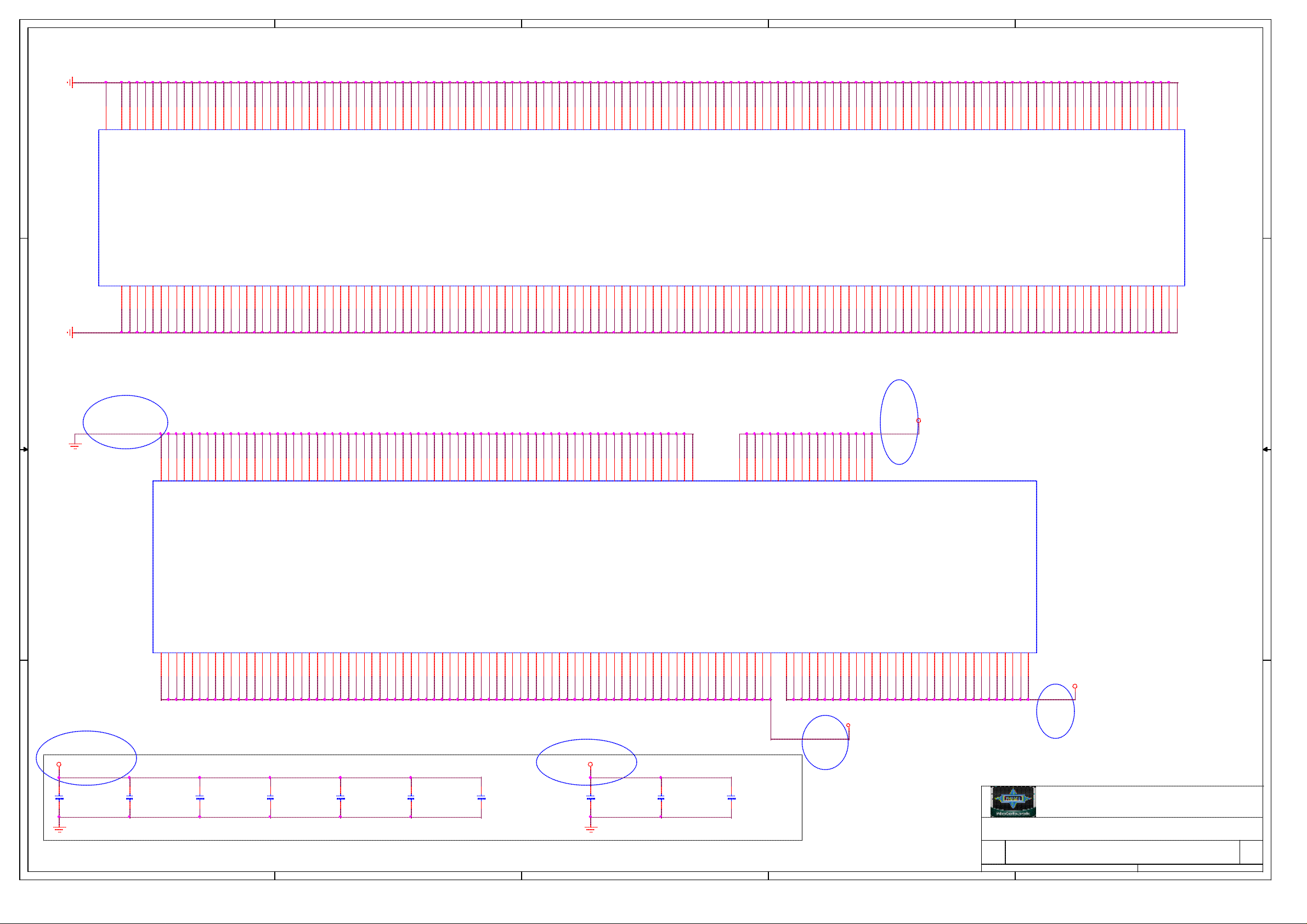

Page 4

5

U2EB5D

A2

VSS0

A5

VSS1

A8

VSS2

A11

VSS3

A14

VSS4

A17

VSS5

A20

VSS6

A23

VSS7

D D

C C

B B

A A

A26

VSS8

AA1

VSS9

AA4

VSS10

AA6

VSS11

AA8

VSS12

AA10

VSS13

AA12

VSS14

AA14

VSS15

AA16

VSS16

AA18

VSS17

AA20

VSS18

AA22

VSS19

AA25

VSS20

AB3

VSS21

AB5

VSS22

AB7

VSS23

AB9

VSS24

AB11

VSS25

AB13

VSS26

AB15

VSS27

AB17

VSS28

AB19

VSS29

AB21

VSS30

AB23

VSS31

AB26

VSS32

AC2

VSS33

AC5

VSS34

AC8

VSS35

AC10

VSS36

AC12

VSS37

AC14

VSS38

AC16

VSS39

AC18

VSS40

AC21

VSS41

AC24

VSS42

AD1

VSS43

AD4

VSS44

AD7

VSS45

AD9

VSS46

AD11

VSS47

AD13

VSS48

AD15

VSS49

AD17

VSS50

AD19

VSS51

AD22

VSS52

AD25

VSS53

AE3

VSS54

AE6

VSS55

AE8

VSS56

AE10

VSS57

AE12

VSS58

AE14

VSS59

AE16

VSS60

AE18

VSS61

AE20

VSS62

AE23

VSS63

AE26

VSS64

AF2

VSS65

AF5

VSS66

AF9

VSS67

AF11

VSS68

AF13

VSS69

AF15

VSS70

AF17

VSS71

AF19

VSS72

AF21

VSS73

AF24

VSS74

B3

VSS75

B6

VSS76

B9

VSS77

B12

VSS78

B16

VSS79

B19

VSS80

B22

VSS81

B25

VSS82

C1

VSS83

C4

VSS84

C7

VSS85

C10

VSS86

C13

VSS87

C15

VSS88

C18

VSS89

C21

VSS90

C24

VSS91

D2

VSS92

D5

VSS93

D7

VSS94

D9

VSS95

D11

VSS96

Dothan_Yonah_Processor_Skt

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

R6

R22

R25

T3

T5

T21

T23

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

4

VHCORE VHCORE

U2EB5C

D6

VCC0

D8

VCC1

D18

VCC2

D20

VCC3

D22

VCC4

E5

VCC5

E9

VCC6

E17

VCC7

E19

VCC8

E21

VCC9

F6

VCC10

F8

VCC11

F18

VCC12

F20

VCC13

F22

VCC14

G5

VCC15

G21

VCC16

H6

VCC17

H22

VCC18

J5

VCC19

J21

VCC20

K22

VCC21

U5

VCC22

V6

VCC23

V22

VCC24

W5

VCC25

W21

VCC26

Y6

VCC27

Y22

VCC28

AA5

VCC29

AA7

VCC30

AA9

VCC31

AA11

VCC32

AA13

VCC33

AA15

VCC34

AA17

VCC35

AA19

VCC36

AA21

VCC37

AB6

VCC38

AB8

VCC39

AB10

VCC40

AB12

VCC41

AB14

VCC42

AB16

VCC43

AB18

VCC44

AB20

VCC45

AB22

VCC46

AC9

VCC47

AC11

VCC48

AC13

VCC49

AC15

VCC50

AC17

VCC51

AD8

VCC52

AD10

VCC53

AD12

VCC54

AD14

VCC55

AD16

VCC56

AD18

VCC57

AE9

VCC58

Dothan_Yonah_Processor_Skt

CPU_VID[0..5]39

VCCSENSE

VSSSENCE

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCCA0

VCCA1

VCCA2

VCCA3

VCCP0

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCQ0

VCCQ1

VID0

VID1

VID2

VID3

VID4

VID5

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

E7

AC19

F26

B1

N1

AC26

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

K6

L21

L5

M22

M6

N21

N5

P22

P6

R21

R5

T22

T6

U21

P23

W4

E2

F2

F3

G3

G4

H4

AE7

AF6

CPU_VID[0..5]

3

1

1

1

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

1

1

2

+VCCA

FSB : 400MHz

RB23 0

TPT8

.

TPB9

.

VTT

TPT5

.

TPB7

.

TPB6

.

CB61

0.01UF_0402

LAYOUT NOTE: Provide a test point (with no stub)

LAYOUT NOTE: Provide a test point (with no stub)LAYOUT NOTE: Provide a test point (with no stub)

to connent differential probe between VCCSENSE and

VSSSENSE at the location where the two 54.9 ohm

resistors terminate the 55 ohm tranmisssion lines.

CB62

10UF/10V_0805

FSB : 533MHz

+VCCA_PROC :

+VCCA_PROC : 1.5V

1.8V

1

MICRO-STAR INT'L CO.,LTD.

Title

Dothan-2 (Power / GND)

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

MS-1022

4 48Thursday, June 09, 2005

1

0.B

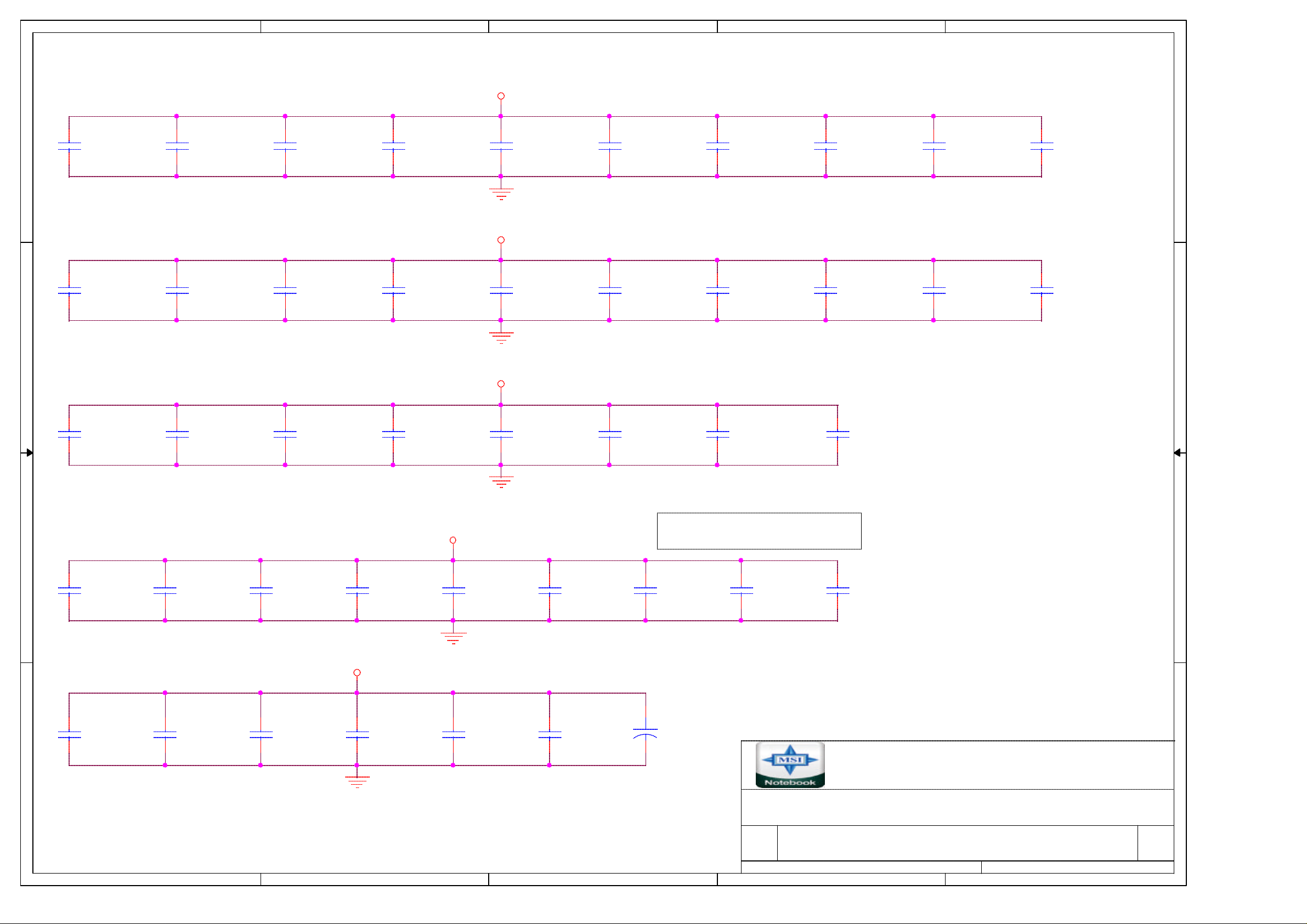

Page 5

5

4

VHCORE

3

2

1

D D

C C

CB28

10UF/6.3V_0805

CB40

10UF/6.3V_0805

CB33

10UF/6.3V_0805

CB56

10UF/6.3V_0805

CB29

10UF/6.3V_0805

CB34

10UF/6.3V_0805

CB57

10UF/6.3V_0805

CT33

10UF/6.3V_0805

CB35

10UF/6.3V_0805

CB55

10UF/6.3V_0805

VHCORE

CB59

10UF/6.3V_0805

VHCORE

CB32

10UF/6.3V_0805

CB60

10UF/6.3V_0805

CB30

10UF/6.3V_0805

CB31

10UF/6.3V_0805

CB58

10UF/6.3V_0805

CT31

10UF/6.3V_0805

CB39

10UF/6.3V_0805

CB38

10UF/6.3V_0805

CT41

10UF/6.3V_0805

CB42

10UF/6.3V_0805_NC

CB37

10UF/6.3V_0805

CT40

10UF/6.3V_0805

CB41

10UF/6.3V_0805

CT35

10UF/6.3V_0805

CT32

10UF/6.3V_0805

CT34

10UF/6.3V_0805

CT42

10UF/6.3V_0805

VTT

B B

CB53

0.1UF_0402

CT37

0.1UF_0402

A A

CB50

0.1UF_0402

CB47

0.1UF_0402

CT36

0.1UF_0402

CB48

0.1UF_0402

CB51

0.1UF_0402

VTT

CB46

0.1UF_0402

CB52

0.1UF_0402

CB45

0.1UF_0402

CB49

0.1UF_0402

CB54

0.1UF_0402

close to cpu socket

CT38

0.1UF_0402

+

CB65

150UF/2.5V

CB43

0.1UF_0402

Title

CB44

0.1UF_0402

MICRO-STAR INT'L CO.,LTD.

Dothan-3

Size Document Number Rev

A

0.B

MS-1022

5

4

3

Date: Sheet of

2

5 48Thursday, June 09, 2005

1

Page 6

5

4

UB10A

3

2

1

HD-0

HD-1

HD-2

D D

VTT

CB84

0.1UF_0402

CB103

0.1UF_0402

HXSCOMP

HYSCOMP

HXRCOMP

HYRCOMP

RB43 54.9_1%_0402

RB66 54.9_1%_0402

C C

B B

RB59 24.9_1%_0402

RB72 24.9_1%_0402

VTT

RB62

221_1%_0402

RB64

100_1%_0402

VTT

RB68

221_1%_0402

RB70

100_1%_0402

HXSWING

HYSWING

HD-3

HD-4

HD-5

HD-6

HD-7

HD-8

HD-9

HD-10

HD-11

HD-12

HD-13

HD-14

HD-15

HD-16

HD-17

HD-18

HD-19

HD-20

HD-21

HD-22

HD-23

HD-24

HD-25

HD-26

HD-27

HD-28

HD-29

HD-30

HD-31

HD-32

HD-33

HD-34

HD-35

HD-36

HD-37

HD-38

HD-39

HD-40

HD-41

HD-42

HD-43

HD-44

HD-45

HD-46

HD-47

HD-48

HD-49

HD-50

HD-51

HD-52

HD-53

HD-54

HD-55

HD-56

HD-57

HD-58

HD-59

HD-60

HD-61

HD-62

HD-63

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

As possible as close to

NB chipset

A A

Trace length max 500 mils

E4

E1

F4

H7

E2

F1

E3

D3

K7

F2

H6

F3

K8

H5

H1

H2

K5

K6

G3

H3

K4

P7

P5

U7

V6

R6

R5

P3

R7

R8

U8

R4

R1

V8

U6

W6

U3

V5

W8

W7

U2

U1

Y5

Y2

V4

Y7

W1

W3

Y3

Y6

W2

C1

C2

D1

P1

J7

J8

J4

J1

L5

J5

L7

J3

L3

T8

T4

T5

T3

T1

L1

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

ALVISO

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HADSTB0#

HADSTB1#

HVREF

HBNR#

HBPRI#

BREQ0#

HCPURST#

HOST

HCLKINN

HCLKINP

HDBSY#

HDEFER#

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDPWR#

HDRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HEDRDY#

HHIT#

HHITM#

HLOCK#

HPCREQ#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HCPUSLP#

HTRDY#

HA-3

G9

HA-4

C9

HA-5

E9

HA-6

B7

HA-7

A10

HA-8

F9

HA-9

D8

B10

HA-10

HA-11

E10

HA-12

G10

HA-13

D9

HA-14

E11

HA-15

F10

HA-16

G11

HA-17

G13

HA-18

C10

HA-19

C11

D11

HA-20

HA-21

C12

HA-22

B13

HA-23

A12

HA-24

F12

HA-25

G12

HA-26

E12

HA-27

C13

HA-28

B11

HA-29

D13

A13

HA-30

HA-31

F13

ADS-

F8

HASTB-0

B9

HASTB-1

E13

HVREF

J11

BNR-

A5

BPRI-

D5

BREQ0-

E7

H10

CPURST-

HCLK_MCH-

AB1

HCLK_MCH

AB2

DBSY-

C6

DEFER-

E6

DBI-0

H8

K3

DBI-1

DBI-2

T7

DBI-3

U5

H_DPWR-

G6

DRDY-

F7

HDSTBN-0

G4

HDSTBN-1

K1

HDSTBN-2

R3

HDSTBN-3

V3

HDSTBP-0

G5

K2

HDSTBP-1

HDSTBP-2

R2

HDSTBP-3

W4

F6

HIT-

D4

HITM-

D6

HLOCK-

B3

A11

HREQ-0

A7

HREQ-1

D7

B8

HREQ-2

HREQ-3

C7

HREQ-4

A8

RS-0

A4

RS-1

C5

RS-2

B4

HCPUSLP#_GMCH CPUSLP-

G8

HTRDY-

B5

ADS- 3

HASTB-0 3

HASTB-1 3

BNR- 3

BPRI- 3

BREQ0- 3

CPURST- 3

HCLK_MCH- 14

HCLK_MCH 14

DBSY- 3

DEFER- 3

H_DPWR- 3

DRDY- 3

1

TPB30

.

HIT- 3

HITM- 3

HLOCK- 3

1

TPB23

.

RB39 0R_NC

HTRDY- 3

R2407 NC for Dothan-A

or for Dothan-B

5

4

3

HA-[3..31]

HD-[0..63]

DBI-[0..3]

HDSTBN-[0..3]

HDSTBP-[0..3]

HREQ-[0..4]

RS-[0..2]

2

HA-[3..31] 3

HD-[0..63] 3

DBI-[0..3] 3

HDSTBN-[0..3] 3

HDSTBP-[0..3] 3

HREQ-[0..4] 3

RS-[0..2] 3

CPUSLP- 3,17

as close as to GMCH J11 PAD

VTT

RT70

100_1%_0402

HVREF

CT71

0.01UF_0402

CPURST-

CT76

0.1UF_0402

RT69 54.9_1%_0402_NC

RT73

200_1%_0402

VTT

MICRO-STAR INT'L CO.,LTD.

Title

915GM/PM-1 (HOST)

Size Document Number Rev

B

Date: Sheet of

MS-1022

1

6 48Thursday, June 09, 2005

0.B

Page 7

5

4

3

2

1

SDVO Design guide :

CFG[3:17] have internal pullup resistors

CFG[18:19] have internal pulldown resistors

DMI_TXN 019

DMI_TXN 119

D D

C C

B B

DMI_TXN 219

DMI_TXN 319

DMI_TXP019

DMI_TXP119

DMI_TXP219

DMI_TXP319

DMI_RXN 019

DMI_RXN 119

DMI_RXN 219

DMI_RXN 319

DMI_RXP019

DMI_RXP119

DMI_RXP219

DMI_RXP319

CLK_SDRAM011

CLK_SDRAM111

CLK_SDRAM312

CLK_SDRAM412

CLK_SDRAM-011

CLK_SDRAM-111

CLK_SDRAM-312

CLK_SDRAM-412

CKE011,13

CKE111,13

CKE212,13

CKE312,13

SM_CS-011,13

SM_CS-111,13

SM_CS-212,13

SM_CS-312,13

SM_ODT011,13

SM_ODT111,13

SM_ODT212,13

SM_ODT312,13

TPB46 .

TPB43 .

TPB45 .

TPB44 .

DMI_TXN 0

DMI_TXN 1

DMI_TXN 2

DMI_TXN 3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN 0

DMI_RXN 1 CFG13

DMI_RXN 2

DMI_RXN 3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

CLK_SDRAM0

CLK_SDRAM1

CLK_SDRAM2

1

CLK_SDRAM3

CLK_SDRAM4

1

CLK_SDRAM5

CLK_SDRAM-0

CLK_SDRAM-1

1

CLK_SDRAM-2

CLK_SDRAM-3

CLK_SDRAM-4

1

CLK_SDRAM-5

CKE0

CKE1

CKE2

CKE3

SM_CS-0

SM_CS-1

SM_CS-2

SM_CS-3

M_OCDCOMP0

M_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

M_RCOMPN

M_RCOMPP

915PMDDR_VREF0

915PMDDR_VREF1

SMXSLEW

SMYSLEW

It's point to

point, 55ohm

trace,keep as short

as possible.

2/17

+1_8VDDRM

A A

RB85 80.6_1%

RB86 80.6_1%

RT97 40.2_1%

RT96 40.2_1%

Trace must < 500 mils

M_RCOMPN

M_RCOMPP

M_OCDCOMP0

M_OCDCOMP1

As possible as close NB

chipset

5

AA31

AB35

AC31

AD35

Y31

AA35

AB31

AC35

AA33

AB37

AC33

AD37

Y33

AA37

AB33

AC37

AM33

AL1

AE11

AJ34

AF6

AC10

AN33

AK1

AE10

AJ33

AF5

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AD1

AE27

AE28

AF9

AF10

UB10C

DMIRXN 0

DMIRXN 1

DMIRXN 2

DMIRXN 3

DMIRXP0

DMIRXP1

DMIRXP2

DMIRXP3

DMITXN 0

DMITXN 1

DMITXN 2

DMITXN 3

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK4

SM_CK5

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CK4#

SM_CK5#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

ALVISO

+1_8VDDRM

DMIDDR MUXING

CFG/RSVDPMCLKNC

DREF_SSCLKN

+1_8VDDRM

2/17

RB77

1K

915PMDDR_VREF0

RB76

1K

2/17

RB79

Trace must < 500 mils

1K

915PMDDR_VREF1

RB78

1K

CB120

0.1UF_0402

As possible as close NB

chipset

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

RSTIN#

DREF_CLKN

DREF_CLKP

DREF_SSCLKP

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

Trace must < 500 mils

CB118

0.1UF_0402

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

4

CFG0

SELPSB1_CLK

SELPSB2_NB

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

PM_BMBUSYPM_EXTTS-0

PM_EXTTS-1

R_THERMTRIPNB_PWRGD

NB_RST-

+1_5VRUN

SELPSB1_CLK 14

SELPSB2_NB 14

1

TPB31

.

1

TPB32

.

1

TPB29

.

1

TPB40

.

1

TPB26

.

1

TPB25

.

1

TPB28

.

1

TPB38

.

1

TPB24

.

1

TPB35

.

1

TPB39

.

1

TPB34

.

1

TPB36

.

1

TPB33

.

1

TPB27

.

PM_BMBUSY- 19

RB38 0_NC

NB_PWRGD 32

NB_RST- 18

Note:

If internal graphics is not used

but VCCA_DPLLA and VCCA_DPLLB are

still powered, then DREF_CLKP and

DREF_SSCLKP to +1_5VRUN ,DREF_CLKN

and DREF_SSCLKN to GND.(915Design

guidelines P.356)

If SDVO Interface Unused:

If not implemented,the

SDVO interface signals

can be No Connect.

(915Design guidelines

P.213)

CLK_MCH_3GPLL-14

CLK_MCH_3GPLL14

4/8

CFG0

RT53 10K_0402

HIGH=DMIX4

LOW=DMIX2

CFG5

RB40 2.2K_0402_NC

HIGH=DDR1

LOW=DDR2

2/17

THERMTRIP- 3,17

CFG6

RB42 2.2K_0402

HIGH=Normal operation

LOW=Reverse Lane

CFG9

RB41 2.2K_0402_NC

PM_EXTTS-0

PM_EXTTS-1

RT55 10K_0402

RT54 10K_0402

+2_5VRUN

As possible as close 915PM

PEG_TXN 0

PEG_TXN 1

PEG_TXN 2

PEG_TXN 3

PEG_TXN 4

PEG_TXN 5

PEG_TXN 6

PEG_TXN 7

PEG_TXN 8

PEG_TXN 9

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4 PEX_RXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7 PEX_RXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP14

PEG_TXP15

CB73 0.1UF_0402_X5R

CB77 0.1UF_0402_X5R

CB81 0.1UF_0402_X5R

CB87 0.1UF_0402_X5R

CB91 0.1UF_0402_X5R

CB99 0.1UF_0402_X5R

CB1010.1UF_0402_X5R

CB1080.1UF_0402_X5R

CB1110.1UF_0402_X5R

CB72 0.1UF_0402_X5R

CB74 0.1UF_0402_X5R

CB86 0.1UF_0402_X5R

CB88 0.1UF_0402_X5R

CB98 0.1UF_0402_X5R

CB1000.1UF_0402_X5R

CB1070.1UF_0402_X5R

CB1090.1UF_0402_X5R

3

CB85 0.1UF_0402_X5R

CB94 0.1UF_0402_X5R

CB97 0.1UF_0402_X5R

CB1040.1UF_0402_X5R

CB1060.1UF_0402_X5R

CB1140.1UF_0402_X5R

CB1160.1UF_0402_X5R

CB76 0.1UF_0402_X5R

CB82 0.1UF_0402_X5R

CB92 0.1UF_0402_X5R

CB95 0.1UF_0402_X5R

CB1020.1UF_0402_X5R

CB1050.1UF_0402_X5R

CB1120.1UF_0402_X5R

CB1150.1UF_0402_X5R

VTT

CLK_MCH_3GPLLCLK_MCH_3GPLL

PEX_RXN 0

PEX_RXN 1

PEX_RXN 2

PEX_RXN 3

PEX_RXN 4

PEX_RXN 5

PEX_RXN 6

PEX_RXN 7

PEX_RXN 8

PEX_RXN 9

PEX_RXN 10PEG_TXN10

PEX_RXN 11

PEX_RXN 12

PEX_RXN 13

PEX_RXN 14

PEX_RXN 15

PEX_RXP0

PEX_RXP1

PEX_RXP2

PEX_RXP3

PEX_RXP5

PEX_RXP6

PEX_RXP8

PEX_RXP9

PEX_RXP10

PEX_RXP11

PEX_RXP12

PEX_RXP13PEG_TXP13

PEX_RXP14

PEX_RXP15

VTT

H24

H25

AB29

AC29

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

2

UB10F

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTRL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

ALVISO

PEX_RXN[0..15]

PEX_RXP[0..15]

PEG_RXN[0..15]

PEG_RXP[0..15]

VCC3G_PCIE

MISC

TV VGA LVDS

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

PCI-EXPRESS GRAPHICS

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

PEX_RXN[0..15] 40

PEX_RXP[0..15] 40

PEG_RXN[0..15] 40

PEG_RXP[0..15] 40

D36

RT64 24.9_1%_0402

D34

PEG_RXN 0

E30

F34

PEG_RXN 1

PEG_RXN 2

G30

H34

PEG_RXN 3

PEG_RXN 4

J30

K34

PEG_RXN 5

PEG_RXN 6

L30

M34

PEG_RXN 7

PEG_RXN 8

N30

P34

PEG_RXN 9

PEG_RXN 10

R30

T34

PEG_RXN 11

PEG_RXN 12

U30

V34

PEG_RXN 13

PEG_RXN 14

W30

Y34

PEG_RXN 15

D30

PEG_RXP0

PEG_RXP1

E34

F30

PEG_RXP2

PEG_RXP3

G34

H30

PEG_RXP4

PEG_RXP5

J34

K30

PEG_RXP6

PEG_RXP7

L34

M30

PEG_RXP8

PEG_RXP9

N34

P30

PEG_RXP10

PEG_RXP11

R34

T30

PEG_RXP12

PEG_RXP13

U34

V30

PEG_RXP14

PEG_RXP15

W34

PEG_TXN 0

E32

F36

PEG_TXN 1

PEG_TXN 2

G32

H36

PEG_TXN 3

PEG_TXN 4

J32

K36

PEG_TXN 5

PEG_TXN 6

L32

M36

PEG_TXN 7

PEG_TXN 8

N32

P36

PEG_TXN 9

PEG_TXN 10

R32

T36

PEG_TXN 11

PEG_TXN 12

U32

V36

PEG_TXN 13

PEG_TXN 14

W32

Y36

PEG_TXN 15

D32

PEG_TXP0

PEG_TXP1

E36

F32

PEG_TXP2

PEG_TXP3

G36

H32

PEG_TXP4

PEG_TXP5

J36

K32

PEG_TXP6

PEG_TXP7

L36

M32

PEG_TXP8

PEG_TXP9

N36

P32

PEG_TXP10

PEG_TXP11

R36

T32

PEG_TXP12

PEG_TXP13

U36

V32

PEG_TXP14

PEG_TXP15

W36

MICRO-STAR INT'L CO.,LTD.

Title

915GM/PM-2 (DMI/VGA)

Size Document Number Rev

Custom

Date: Sheet of

MS-1022

1

7 48Thursday, June 09, 2005

0.B

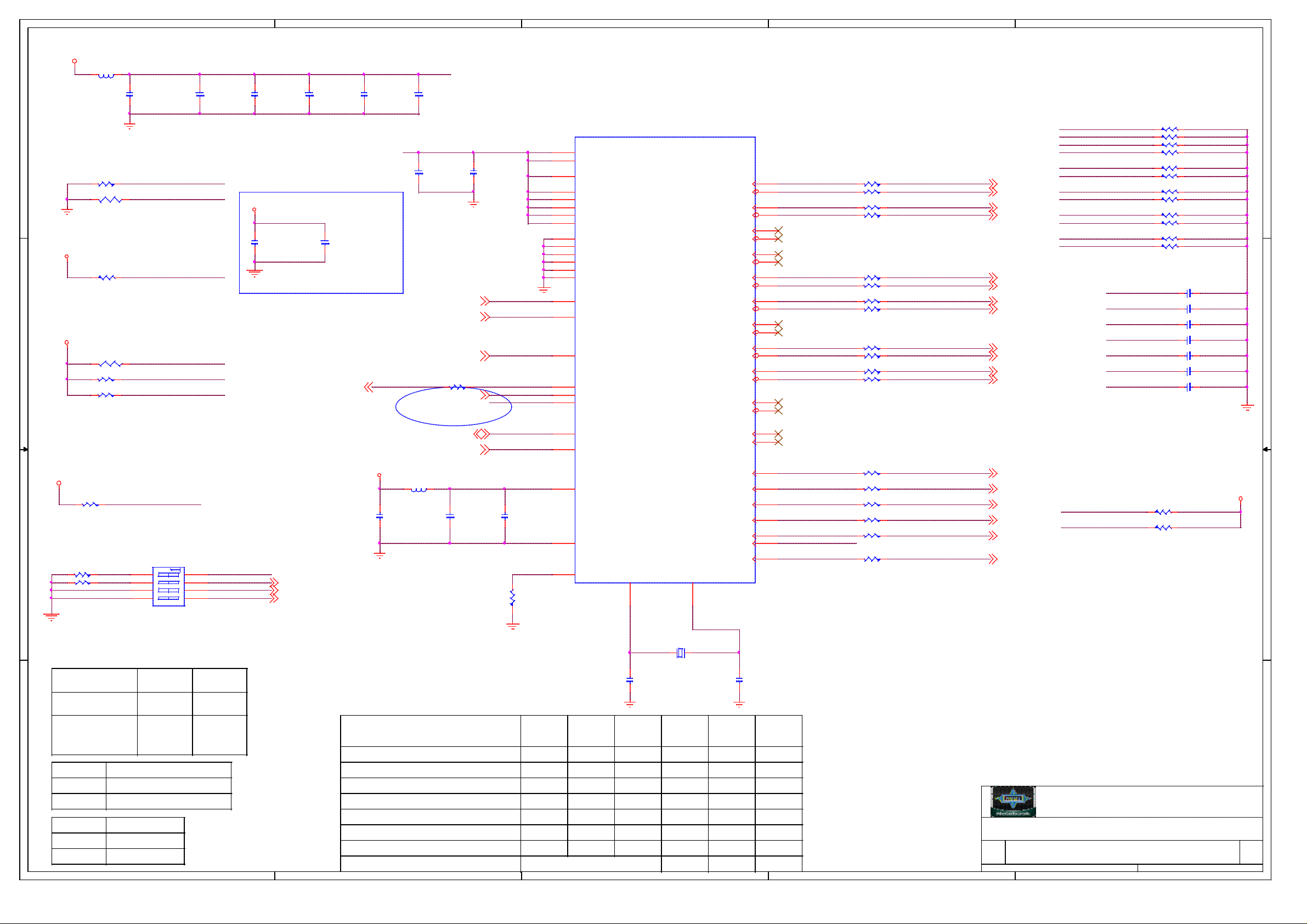

Page 8

5

4

3

2

1

ALVISO

SB_MD[0..63]

SB_DM[0..7]

SB_DQS[0..7]

SB_DQS-[0..7]

SB_MA[0..13]

SB_BS-[0..2]

SB_RCVENOUT#

SB_MD[0..63] 12

SB_DM[0..7] 12

SB_DQS[0..7] 12

SB_DQS-[0..7] 12

SB_MA[0..13] 12,13

SB_BS-[0..2] 12,13

SB_BS-0

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

DDR SYSTEM MEMORY B

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_WE#

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

SB_BS-1

SB_BS-2

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS-0

SB_DQS-1

SB_DQS-2

SB_DQS-3

SB_DQS-4

SB_DQS-5

SB_DQS-6

SB_DQS-7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CASSB_RASSB_RCVENINSB_RCVENOUTSB_WE-

SB_RAS- 12,13

SB_WE- 12,13

1

1

.

.

TPB50

TPB47

SA_MD[0..63]

SA_DM[0..7]

SA_DQS[0..7]

SA_DQS-[0..7]

SA_MA[0..13]

D D

SA_MD0

SA_MD1

SA_MD2

SA_MD3

SA_MD4

SA_MD5

SA_MD6

SA_MD7

SA_MD8

SA_MD9

SA_MD10

SA_MD11

SA_MD12

SA_MD13

SA_MD14

SA_MD15

SA_MD16

SA_MD17

SA_MD18

C C

B B

A A

SA_MD19

SA_MD20

SA_MD21

SA_MD22

SA_MD23

SA_MD24

SA_MD25

SA_MD26

SA_MD27

SA_MD28

SA_MD29

SA_MD30

SA_MD31

SA_MD32

SA_MD33

SA_MD34

SA_MD35

SA_MD36

SA_MD37

SA_MD38

SA_MD39

SA_MD40

SA_MD41

SA_MD42

SA_MD43

SA_MD44

SA_MD45

SA_MD46

SA_MD47

SA_MD48

SA_MD49

SA_MD50

SA_MD51

SA_MD52

SA_MD53

SA_MD54

SA_MD55

SA_MD56

SA_MD57

SA_MD58

SA_MD59

SA_MD60

SA_MD61

SA_MD62

SA_MD63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

UB10B

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

ALVISO

SA_BS-[0..2]

DDR SYSTEM MEMORY A

SA_RCVENIN#

SA_RCVENOUT#

SA_MD[0..63] 11

SA_DM[0..7] 11

SA_DQS[0..7] 11

SA_DQS-[0..7] 11

SA_MA[0..13] 11,13

SA_BS-[0..2] 11,13

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_WE#

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

SA_BS-0

SA_BS-1

SA_BS-2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS-0

SA_DQS-1

SA_DQS-2

SA_DQS-3

SA_DQS-4

SA_DQS-5

SA_DQS-6

SA_DQS-7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CASSA_RASSA_RCVENINSA_RCVENOUTSA_WE-

SB_MD0

SB_MD1

SB_MD2

SB_MD3

SB_MD4

SB_MD5

SB_MD6

SB_MD7

SB_MD8

SB_MD9

SB_MD10

SB_MD11

SB_MD12

SB_MD13

SB_MD14

SB_MD15

SB_MD16

SB_MD17

SB_MD18

SB_MD19

SB_MD20

SB_MD21

SB_MD22

SB_MD23

SB_MD24

SB_MD25

SB_MD26

SB_MD27

SB_MD28

SB_MD29

SB_MD30

SB_MD31

SB_MD32

SB_MD33

SB_MD34

SB_MD35

SB_MD36

SB_MD37

SB_MD38

SB_MD39

SB_MD40

SB_MD41

SB_MD42

SB_MD43

SB_MD44

SB_MD45

SA_CAS- 11,13 SB_CAS- 12,13

SA_RAS- 11,13

SA_WE- 11,13

1

TPB48

.

1

TPB49

.

SB_MD46

SB_MD47

SB_MD48

SB_MD49

SB_MD50

SB_MD51

SB_MD52

SB_MD53

SB_MD54

SB_MD55

SB_MD56

SB_MD57

SB_MD58

SB_MD59

SB_MD60

SB_MD61

SB_MD62

SB_MD63

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

UB10G

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

MICRO-STAR INT'L CO.,LTD.

Title

915GM/PM-3 (DDR)

Size Document Number Rev

B

5

4

3

2

Date: Sheet of

MS-1022

1

8 48Thursday, June 09, 2005

0.B

Page 9

5

VTT

CT140

0.1UF_0402

D D

C C

B B

CT141

0.1UF_0402

VTT

0.1UF_0402_NC

CB64

0.1UF_0402_NC

CT89

0.1UF_0402

+1_5VRUN

LT25

1U500m_0805

+

12

ECT8

470UF/2.5V

+1_5VRUN

LT26

1U500m_0805

+

12

ECT7

470UF/2.5V

VTT

CT131

2.2UF/6.3V

Close to North Bridge Chip

CB90

CT112

10UF/10V_0805

VCCA_HPLL

CT170

0.1UF_0402

VCCA_MPLL

CT182

0.1UF_0402

CT128

4.7UF/6.3V_0805

0.1UF_0402_NC

CT45

0.1UF_0402_NC

CT46

CT169

10UF/10V_0805

+

12

CB93

220UF/2V

CT67

0.1UF_0402_NC

For EMI 4/6

+1_5VRUN

Close to North Bridge Chip

CT321

0.1UF_0402_NC

A A

5

CT78

0.1UF_0402_NC

For EMI 4/6

CB68 0.47UF

CB69 0.47UF

CB110 0.22UF

CB89 0.22UF

CT144

0.1UF_0402_NC

VCCP_GMCH_CAP1

VCCP_GMCH_CAP2

VCCP_GMCH_CAP3

VCCP_GMCH_CAP4

4

CT55

10UF/10V_0805

VTT

VTT

VCCP_GMCH_CAP1

VCCP_GMCH_CAP2

VCCP_GMCH_CAP3

VCCP_GMCH_CAP4

4

VTT

+1_5VRUN

VCCA_HPLL

VCCA_MPLL

UB10H

T29

VCC0

R29

VCC1

N29

VCC2

M29

VCC3

K29

VCC4

J29

VCC5

V28

VCC6

U28

VCC7

T28

VCC8

R28

VCC9

P28

VCC10

N28

VCC11

M28

VCC12

L28

VCC13

K28

VCC14

J28

VCC15

H28

VCC16

G28

VCC17

V27

VCC18

U27

VCC19

T27

VCC20

R27

VCC21

P27

VCC22

N27

VCC23

M27

VCC24

L27

VCC25

K27

VCC26

J27

VCC27

H27

VCC28

K26

VCC29

H26

VCC30

K25

VCC31

J25

VCC32

K24

VCC33

K23

VCC34

K22

VCC35

K21

VCC36

W20

VCC37

U20

VCC38

T20

VCC39

K20

VCC40

V19

VCC41

U19

VCC42

K19

VCC43

W18

VCC44

V18

VCC45

T18

VCC46

K18

VCC47

K17

VCC48

AC2

VCCH_MPLL1

AC1

VCCH_MPLL0

B23

VCCA_DPLLA

C35

VCCA_DPLLB

AA1

VCCA_HPLL

AA2

VCCA_MPLL

F19

VCCA_CRTDAC0

E19

VCCA_CRTDAC1

G19

VSSA_CRTDAC

H20

VCC_SYNC

K13

VTT0

J13

VTT1

K12

VTT2

W11

VTT3

V11

VTT4

U11

VTT5

T11

VTT6

R11

VTT7

P11

VTT8

N11

VTT9

M11

VTT10

L11

VTT11

K11

VTT12

W10

VTT13

V10

VTT14

U10

VTT15

T10

VTT16

R10

VTT17

P10

VTT18

N10

VTT19

M10

VTT20

K10

VTT21

J10

VTT22

Y9

VTT23

W9

VTT24

U9

VTT25

R9

VTT26

P9

VTT27

N9

VTT28

M9

VTT29

L9

VTT30

J9

VTT31

N8

VTT32

M8

VTT33

N7

VTT34

M7

VTT35

N6

VTT36

M6

VTT37

A6

VTT38

N5

VTT39

M5

VTT40

N4

VTT41

M4

VTT42

N3

VTT43

M3

VTT44

N2

VTT45

M2

VTT46

B2

VTT47

V1

VTT48

N1

VTT49

M1

VTT50

G1

VTT51

ALVISO

3

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCA_TVBG

VSSA_TVBG

VCCD_TVDAC

VCCDQ_TVDAC

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCA_LVDS

VCCHV0

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

POWER

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

VCCA_3GBG

VSSA_3GBG

3

F17

E17

D18

C18

F18

E18

H18

G18

D19

H17

B26

B25

A25

A35

B22

B21

A21

AM37

AH37

AP29

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AP13

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

AN12

AM12

AL12

AK12

AJ12

AH12

AG12

AF12

AE12

AD11

AC11

AB11

AB10

AB9

AP8

AM1

AE1

B28

A28

A27

AF20

AP19

AF19

AF18

AE37

W37

U37

R37

N37

L37

J37

Y29

Y28

Y27

F37

G37

+2_5VRUN

DDR_CAP1

DDR_CAP2

DDR_CAP5

+1_8VDDRM

2/17

DDR_CAP6

DDR_CAP4

DDR_CAP3

VCC_DDRDLL

VCC3G_PCIE

VCCA_3GPLL

+2_5VRUN

CT56

0.1UF_0402

CB67

0.1UF_0402

CB134

10UF/10V_0805

VCC_DDRDLL

+

12

ECT9

100UF/2V

VCC3G_PCIE

VCCA_3GPLL

+2_5VRUN

DDR_CAP1

DDR_CAP2

DDR_CAP3

DDR_CAP4

DDR_CAP5

DDR_CAP6

CB133

10UF/10V_0805

+1_5VRUN

CB117

0.1UF_0402

CT162

0.1UF_0402

2

CB71

10UF/10V_0805

CB124 0.1UF_0402

CB122 0.1UF_0402

CB121 0.1UF_0402

CB129 0.1UF_0402

CB138 0.1UF_0402

CB130 0.1UF_0402

+1_8VDDRM

CT228

0.1UF_0402

LT24

1U500m_0805

CT226

0.1UF_0402

VCC3G_PCIE

CT127

10UF/10V_0805

RT95 1_1%

CT198

10UF/10V_0805

2

2/17

+1_8VDDRM

+1_8VDDRM

CT208

0.1UF_0402

+1_5VRUN

LT20

80L-0805-6A

+

12

ECT5

220UF/2V

+1_5VRUN

LT22

1U500m_0805

CT375

0.1UF_0402_NC

CT366

0.1UF_0402_NC

+

12

ECT6

330UF/6.3V

1

Close To NB

CT367

0.1UF_0402_NC

CT275

0.1UF_0402_NC

CT274

0.1UF_0402_NC

CB146

0.1UF_0402_NC

CB123

0.1UF_0402_NC

CB6

0.1UF_0402_NC

For EMI 4/6

MICRO-STAR INT'L CO.,LTD.

Title

915GM/PM-4 (Power)

Size Document Number Rev

Custom

Date: Sheet of

MS-1022

1

9 48Thursday, June 09, 2005

0.B

Page 10

5

U4

L4

C4

AJ3

AC3

AB3

AA3

A3

AN2

AL2

AH2

AE2

AD2

V2

P2

B27

J26

G26

E26

A26

AN24

AL24

G2

Y1

B36

D D

VSS242P4VSS243

VSS244H4VSS245

VSS246

VSS247

VSS248

VSS249

VSS250C3VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258T2VSS259

VSS260L2VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268J2VSS269

VSS270D2VSS271

VSSALVDS

AN4

AF4

VSS239

VSS240Y4VSS241

4

T9

H9

AL8

P8

E8

AN7

AK7

AG7

AA7

V7

AJ6

AE6

AC6

AA6

T6

L6

B6

AP5

AL5

E5

VSS210K9VSS211

VSS212A9VSS213

VSS214Y8VSS215

VSS216L8VSS217

VSS218C8VSS219

VSS220

VSS221

VSS222

VSS223

VSS224G7VSS225

VSS226

VSS227

VSS228

VSS229

VSS230P6VSS231

VSS232J6VSS233

VSS234

VSS235

VSS236W5VSS237

VSS238

AC9

AA9

VSS207

VSS208V9VSS209

3

AH9

AE9

VSS205

VSS206

D10

AN9

VSS203

VSS204

Y10

L10

VSS201

VSS202

F11

AA10

VSS199

VSS200

Y11

H11

VSS197

VSS198

AF11

AA11

VSS195

VSS196

AJ11

AG11

VSS193

VSS194

AN11

AL11

VSS191

VSS192

D12

B12

VSS189

VSS190

A14

J12

VSS187

VSS188

F14

B14

VSS185

VSS186

K14

J14

VSS183

VSS184

AJ14

AG14

VSS181

VSS182

AN14

AL14

VSS179

VSS180

K15

C15

VSS177

VSS178

D16

A16

VSS175

VSS176

2

K16

H16

VSS173

VSS174

C17

AL16

VSS171

VSS172

AF17

G17

VSS169

VSS170

AN17

AJ17

VSS167

VSS168

B18

A18

VSS165

VSS166

AL18

U18

VSS163

VSS164

H19

C19

VSS161

VSS162

T19

J19

VSS159

VSS160

AG19

W19

VSS157

VSS158

A20

AN19

VSS155

VSS156

E20

D20

VSS153

VSS154

G20

F20

VSS151

VSS152

AK20

V20

VSS149

VSS150

F21

C21

VSS147

VSS148

AN21

AF21

VSS145

VSS146

D22

A22

VSS143

VSS144

1

J22

E22

VSS141

VSS142

AL22

AH22

VSS139

VSS140

AF23

H23

VSS137

VSS138

UB10E

ALVISO

VSS136

VSS

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS135

B24

D24

VSS133

VSS134

J24

F24

VSS131

VSS132

AJ24

AG24

VSS129

VSS130

E27

G27

VSS127

VSS128

W27

AA27

VSS125

VSS126

AF27

AB27

VSS123

VSS124

AJ27

AG27

VSS121

VSS122

AL27

AN27

VSS119

VSS120

E28

W28

VSS117

VSS118

AB28

AA28

VSS115

VSS116

A29

AC28

VSS113

VSS114

E29

D29

VSS111

VSS112

F29

G29

VSS109

VSS110

L29

H29

VSS107

VSS108

P29

U29

VSS105

VSS106

V29

W29

VSS103

VSS104

AA29

AD29

VSS101

VSS102

AJ29

AG29

VSS99

VSS100

AM29

C30

Y30

AB30

AA30

AE30

AC30

D31

AP30

E31

F31

G31

H31

J31

K31

L31

M31

N31

P31

R31

T31

U31

V31

W31

AG31

AD31

A32

AL31

C32

Y32

AB32

AA32

AD32

AC32

AJ32

AN32

D33

E33

F33

G33

H33

J33

K33

L33

M33

N33

P33

R33

T33

U33

V33

W33

AF33

AD33

C34

AL33

AB34

AA34

AD34

AC34

AN34

AH34

B35

D35

E35

F35

G35

H35

J35

K35

L35

M35

N35

P35

R35

T35

U35

V35

W35

Y35

C36

AE35

AB36

AA36

AD36

AC36

AF36

AE36

AL36

AJ36

VSS9

E37

AN36

VSS8

H37

VSS6

VSS7

K37

M37

VSS5

P37

VSS4

T37

VSS2

VSS3

Y37

V37

VSS0

VSS1

AG37

C C

4/14

4/14

W13

V13

U13

T13

R13

P13

N13

M13

L13

W12

V12

U12

T12

R12

P12

N12

M12

AB26

AA26

Y26

AB25

AA25

Y25

AB24

AA24

Y24

AB23

AA23

Y23

AB22

AA22

Y22

AB21

AA21

Y21

R21

AB20

AA20

AB19

AA19

AB18

AA18

AB17

AA17

Y17

R17

AB16

AA16

Y16

W16

V16

U16

T16

R16

P16

N16

M16

L16

AB15

AA15

Y15

W15

V15

U15

T15

R15

P15

N15

M15

L15

AB14

AA14

Y14

W14

V14

U14

T14

R14

P14

N14

M14

L14

AA13

Y13

AA12

Y12

VSS_NCTF0

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17

VSS_NCTF18

VSS_NCTF19

VSS_NCTF20

VSS_NCTF21

VSS_NCTF22

VSS_NCTF23

VSS_NCTF24

VSS_NCTF25

VSS_NCTF26

VSS_NCTF27

VSS_NCTF28

VSS_NCTF29

VSS_NCTF30

VSS_NCTF31

VSS_NCTF32

VSS_NCTF33

VSS_NCTF34

VSS_NCTF35

VSS_NCTF36

VSS_NCTF37

VSS_NCTF38

VSS_NCTF39

VSS_NCTF40

VSS_NCTF41

VSS_NCTF42

VSS_NCTF43

VSS_NCTF44

VSS_NCTF45

VSS_NCTF46

VSS_NCTF47

VSS_NCTF48

VSS_NCTF49

VSS_NCTF50

VSS_NCTF51

VSS_NCTF52

VSS_NCTF53

VSS_NCTF54

VSS_NCTF55

VSS_NCTF56

VSS_NCTF57

VSS_NCTF58

VSS_NCTF59

VSS_NCTF60

VSS_NCTF61

VSS_NCTF62

VSS_NCTF63

VSS_NCTF64

VSS_NCTF65

VSS_NCTF66

VSS_NCTF67

VSS_NCTF68

B B

L12

VTT_NCTF15

VTT_NCTF16

VTT_NCTF17

VTT_NCTF10

VTT_NCTF11

VTT_NCTF12

VTT_NCTF13

VTT_NCTF14

VTT_NCTF6

VTT_NCTF7

VTT_NCTF8

VTT_NCTF9

VTT_NCTF2

VTT_NCTF3

VTT_NCTF4

VTT_NCTF5

VTT_NCTF0

VTT_NCTF1

VTT

UB10D

ALVISO

NCTF

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF74

VCC_NCTF75

VCC_NCTF76

VCC_NCTF77

VCC_NCTF78

VCC_NCTF68

VCC_NCTF69

VCC_NCTF70

VCC_NCTF71

VCC_NCTF72

VCC_NCTF73

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCCSM_NCTF26

VCCSM_NCTF27

VCCSM_NCTF28

VCCSM_NCTF29

VCCSM_NCTF30

VCCSM_NCTF31

VCCSM_NCTF20

VCCSM_NCTF21

VCCSM_NCTF22

VCCSM_NCTF23

VCCSM_NCTF24

VCCSM_NCTF25

VCCSM_NCTF14

VCCSM_NCTF15

VCCSM_NCTF16

VCCSM_NCTF17

VCCSM_NCTF18

VCCSM_NCTF19

VCCSM_NCTF8

VCCSM_NCTF9

VCCSM_NCTF10

VCCSM_NCTF11

VCCSM_NCTF12

VCCSM_NCTF13

VCCSM_NCTF5

VCCSM_NCTF6

VCCSM_NCTF7

VCCSM_NCTF0

VCCSM_NCTF1

VCCSM_NCTF2

VCCSM_NCTF3

VCCSM_NCTF4

L17

M17

N17

P17

T17

U17

V17

W17

L18

M18

N18

P18

R18

Y18

L19

M19

N19

P19

R19

Y19

L20

M20

N20

P20

R20

Y20

L21

M21

N21

P21

T21

U21

V21

W21

L22

M22

N22

P22

R22

T22

U22

V22

W22

L23

M23

N23

P23

R23

T23

U23

V23

W23

L24

M24

N24

P24

R24

T24

U24

V24

W24

L25

M25

N25

P25

R25

4/144/14

A A

CT90

0.1UF_0402_NC

CT117

0.1UF_0402_NC

CT139

0.1UF_0402_NC

Close To NB

CT93

0.1UF_0402_NC

CT155

0.1UF_0402_NC

CT150

0.1UF_0402_NC

CT74

0.1UF_0402_NC

+1_8VDDRMVTT

CT211

0.1UF_0402_NC

CT179

0.1UF_0402_NC

For EMI 4/6

5

4

3

T25

U25

V25

W25

L26

M26

T26

P26

R26

N26

CT190

0.1UF_0402_NC

U26

V26

W26

AB12

AC12

AB13

AD12

4/14

AD13

AC13

AD14

AC14

VTT

AD15

AC15

AD16

AC16

AD17

AC17

AC18

2

AC19

AD18

AC20

AD19

AC21

AD20

AD21

+1_8VDDRM

AD26

AC26

AD25

AC25

AD24

AC24

AD23

AC23

AD22

AC22

4/14

MICRO-STAR INT'L CO.,LTD.

Title

915GM/PM-5 (GND)

Size Document Number Rev

Custom

Date: Sheet of

MS-1022

1

10 48Thursday, June 09, 2005

0.B

Page 11

5

DIMMB5A

SA_MD0

SA_MD1

SA_MD2

SA_MD3

SA_MD4

SA_MD5

SA_MD6

SA_MD7

D D

C C

+1_8VDDRM

RT110

1K

B B

RT116

1K

SMDDR_VREF

CT284

0.1u_0402

as close as

SO-DIMM

+1_8VDDRM

SA_MD8

SA_MD9

SA_MD10

SA_MD11

SA_MD12

SA_MD13

SA_MD14

SA_MD15

SA_MD16

SA_MD17

SA_MD18

SA_MD19

SA_MD20

SA_MD21

SA_MD22

SA_MD23

SA_MD24

SA_MD25

SA_MD26

SA_MD27

SA_MD28

SA_MD29

SA_MD30

SA_MD31

SA_MD32

SA_MD33

SA_MD34

SA_MD35

SA_MD36

SA_MD37

SA_MD38

SA_MD39

SA_MD40

SA_MD41

SA_MD42

SA_MD43

SA_MD44

SA_MD45

SA_MD46

SA_MD47

SA_MD48

SA_MD49

SA_MD50

SA_MD51

SA_MD52

SA_MD53

SA_MD54

SA_MD55

SA_MD56

SA_MD57

SA_MD58

SA_MD59

SA_MD60

SA_MD61

SA_MD62

SA_MD63

5

DQ0

7

DQ1

17

DQ2

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

DDR2_SO-DIMM_STD1

5/27 For EMI

4

A10/AP

A11

A12

A13

A14

A15

A16_BA2

BA0

BA1

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

102

101

100

99

98

97

94

92

93

91

105

90