Page 1

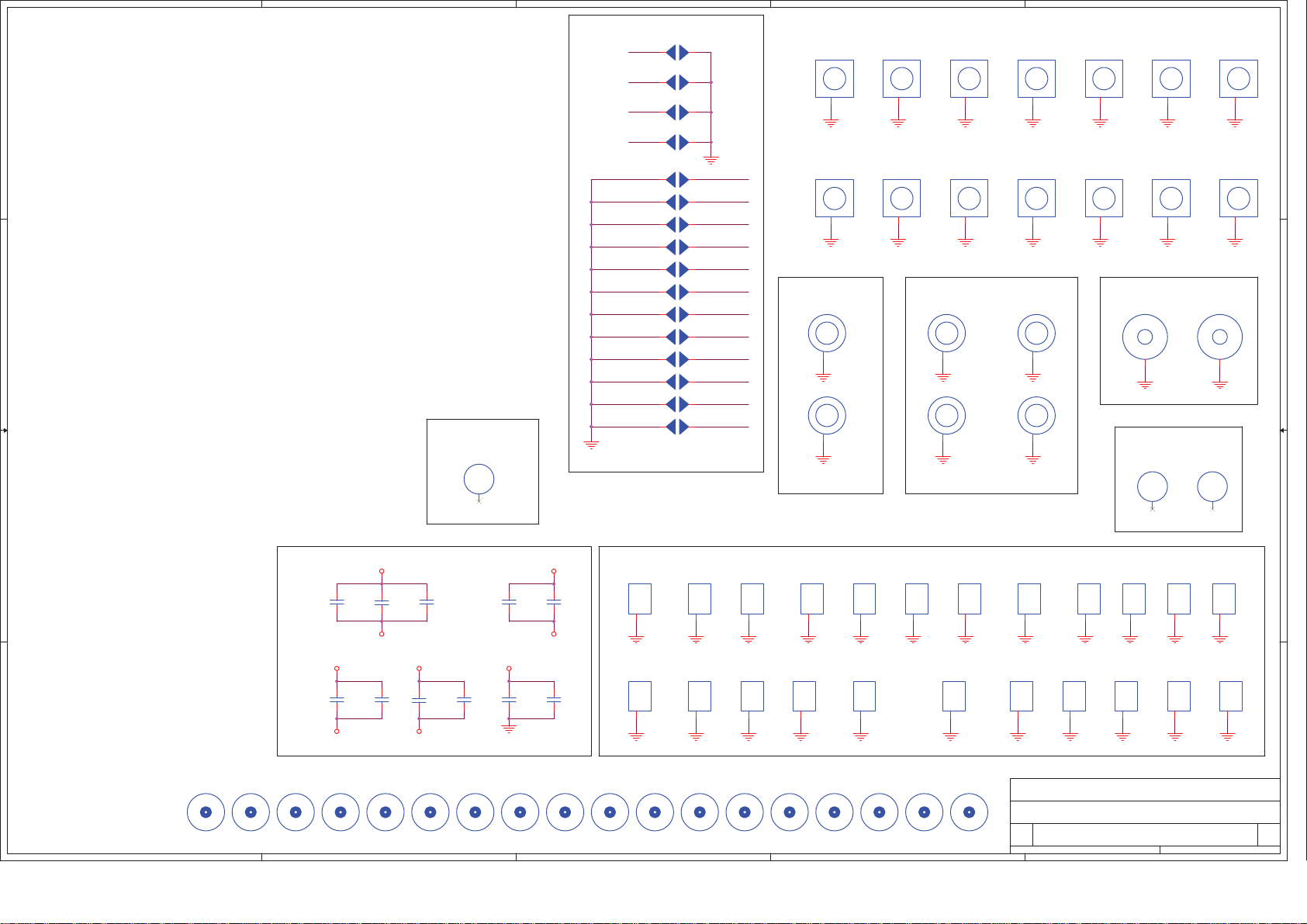

5

01_COVER

02_Block Diagram

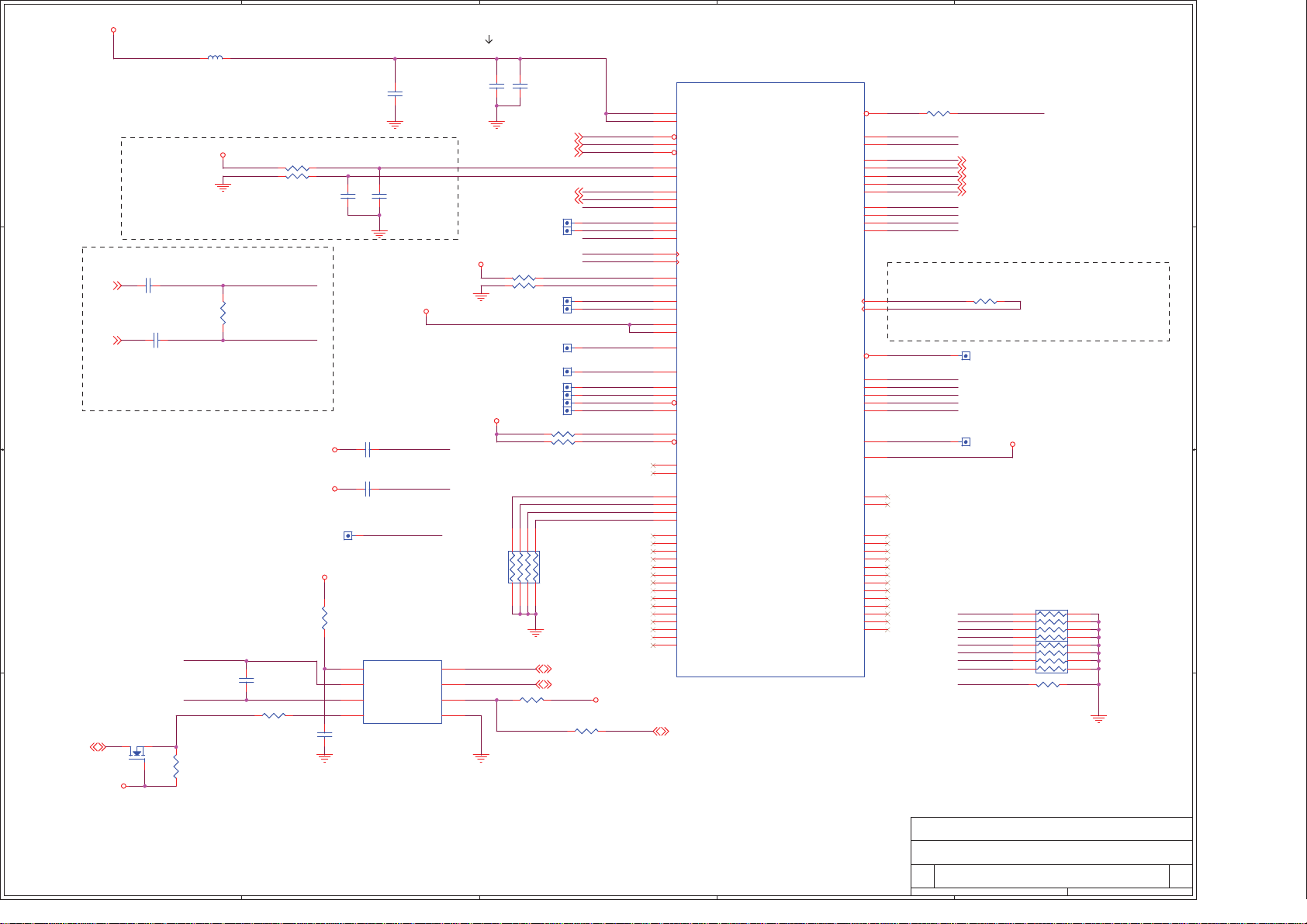

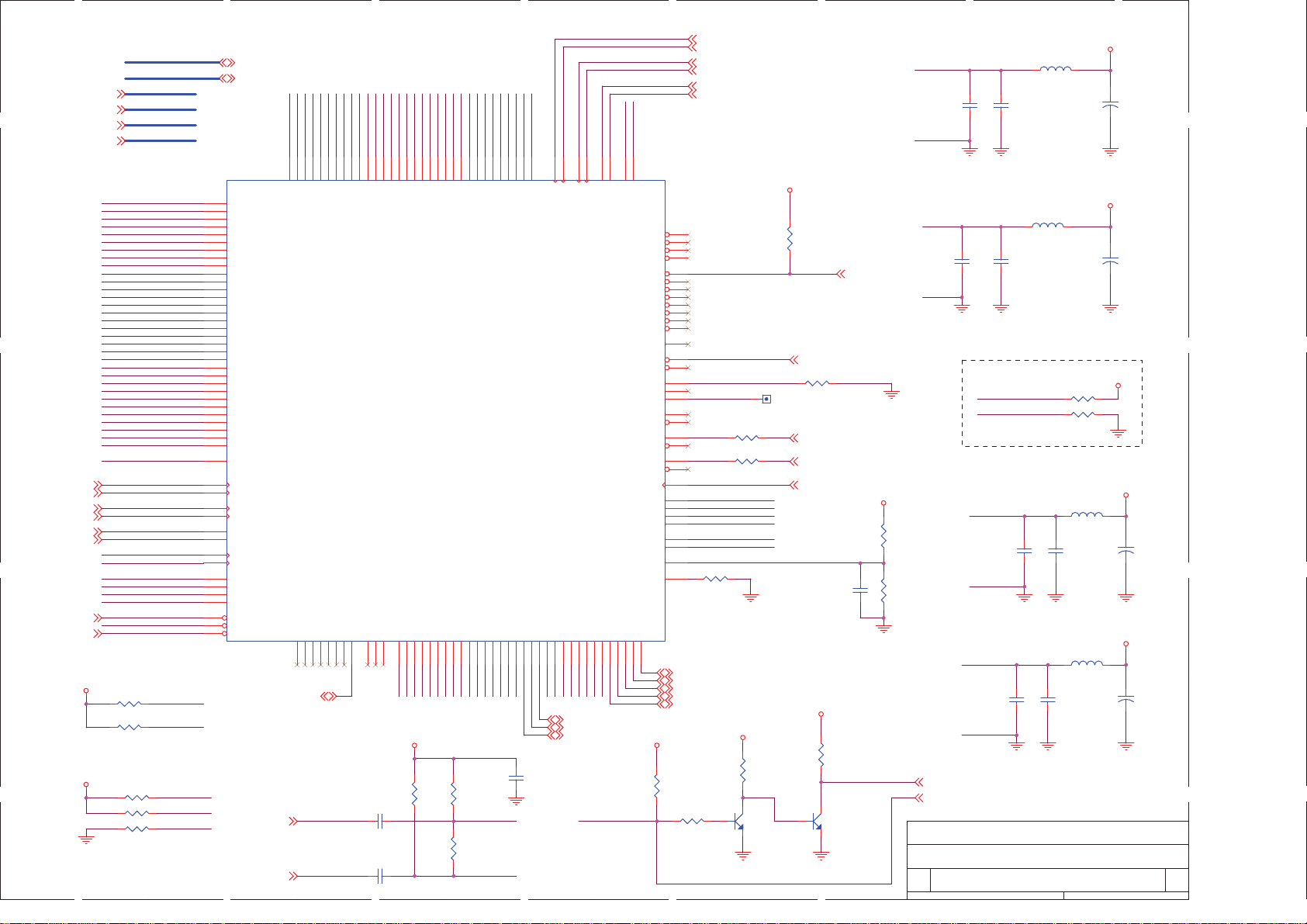

03_Power Rail

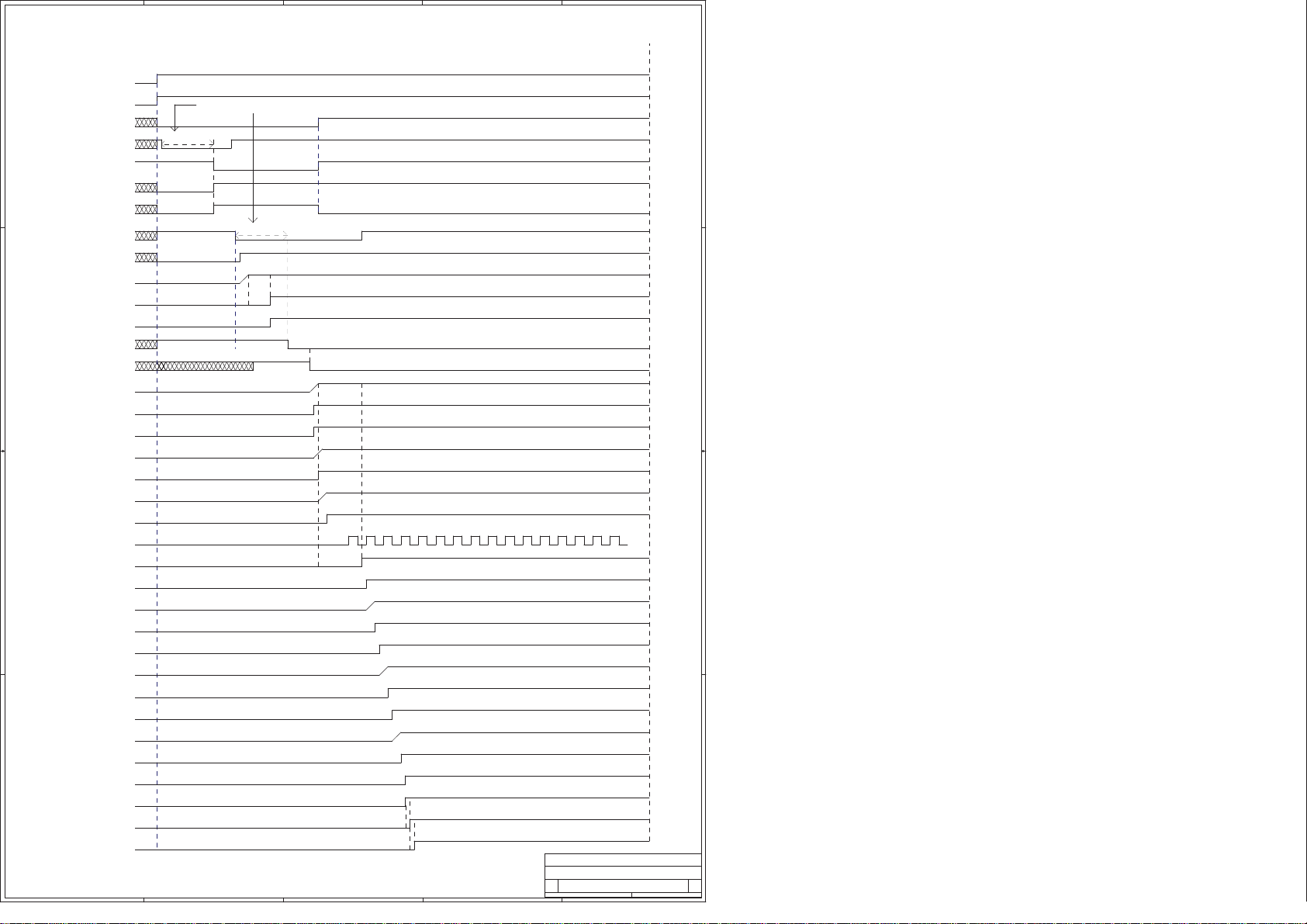

04_Power on Sequency

D D

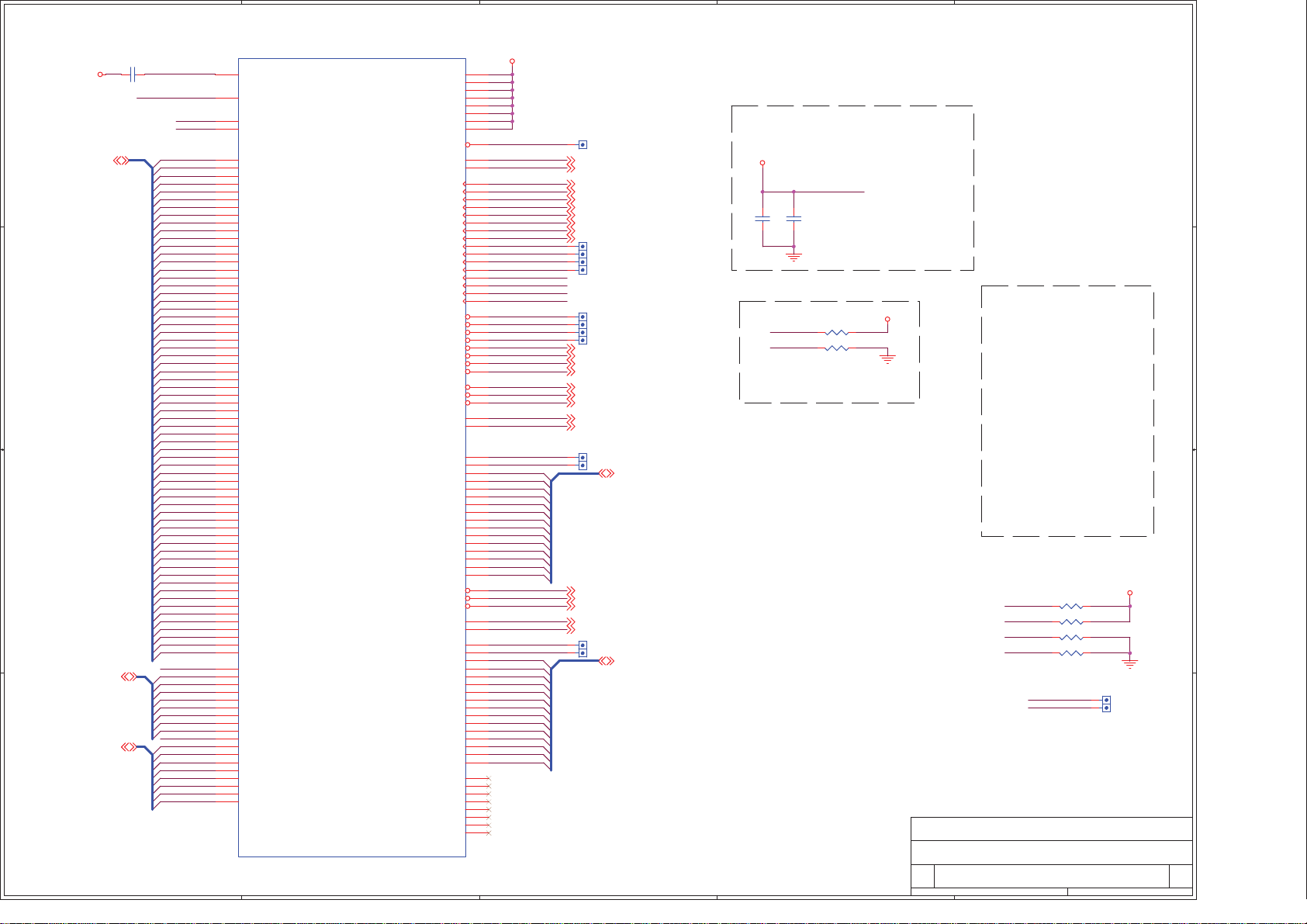

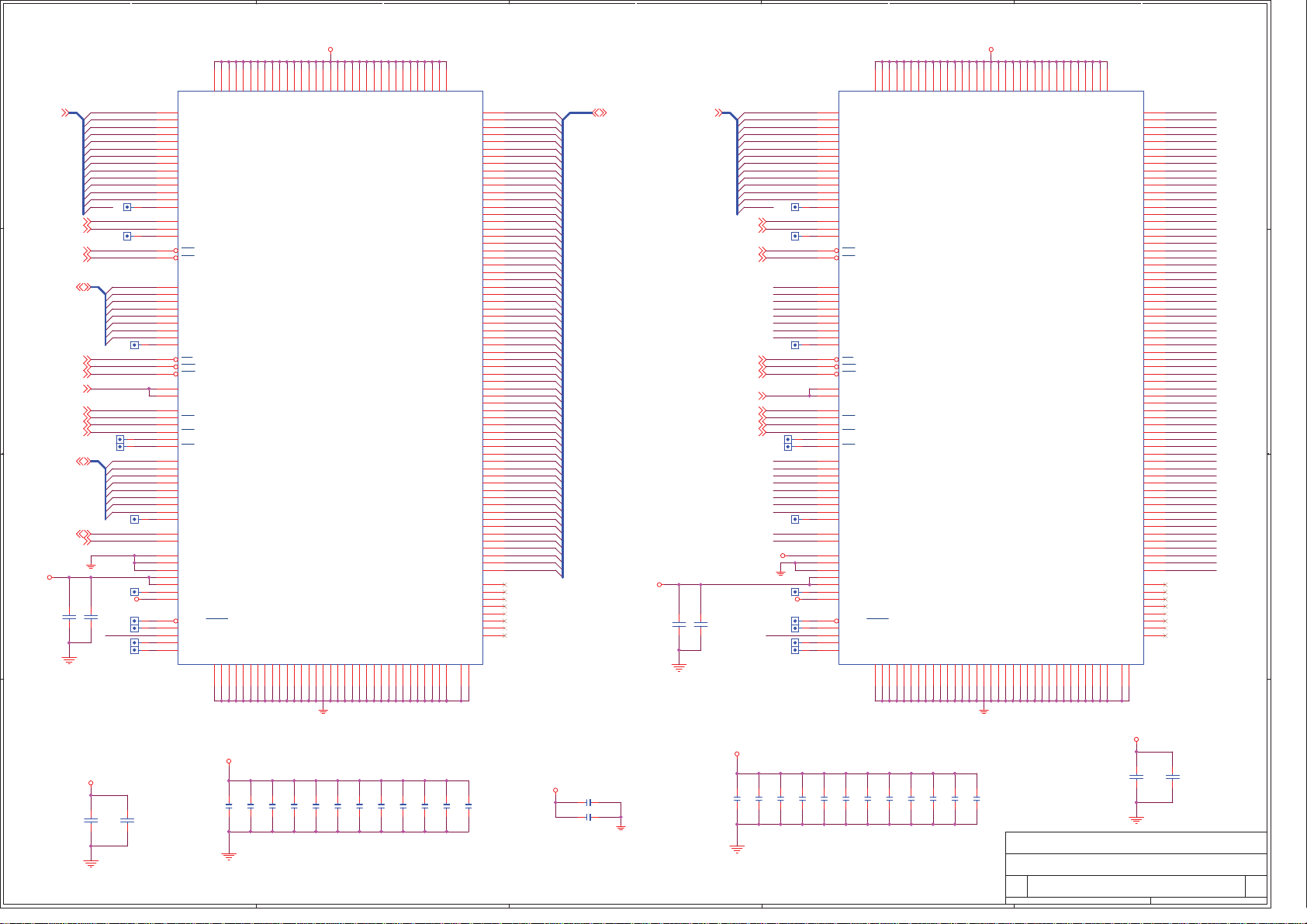

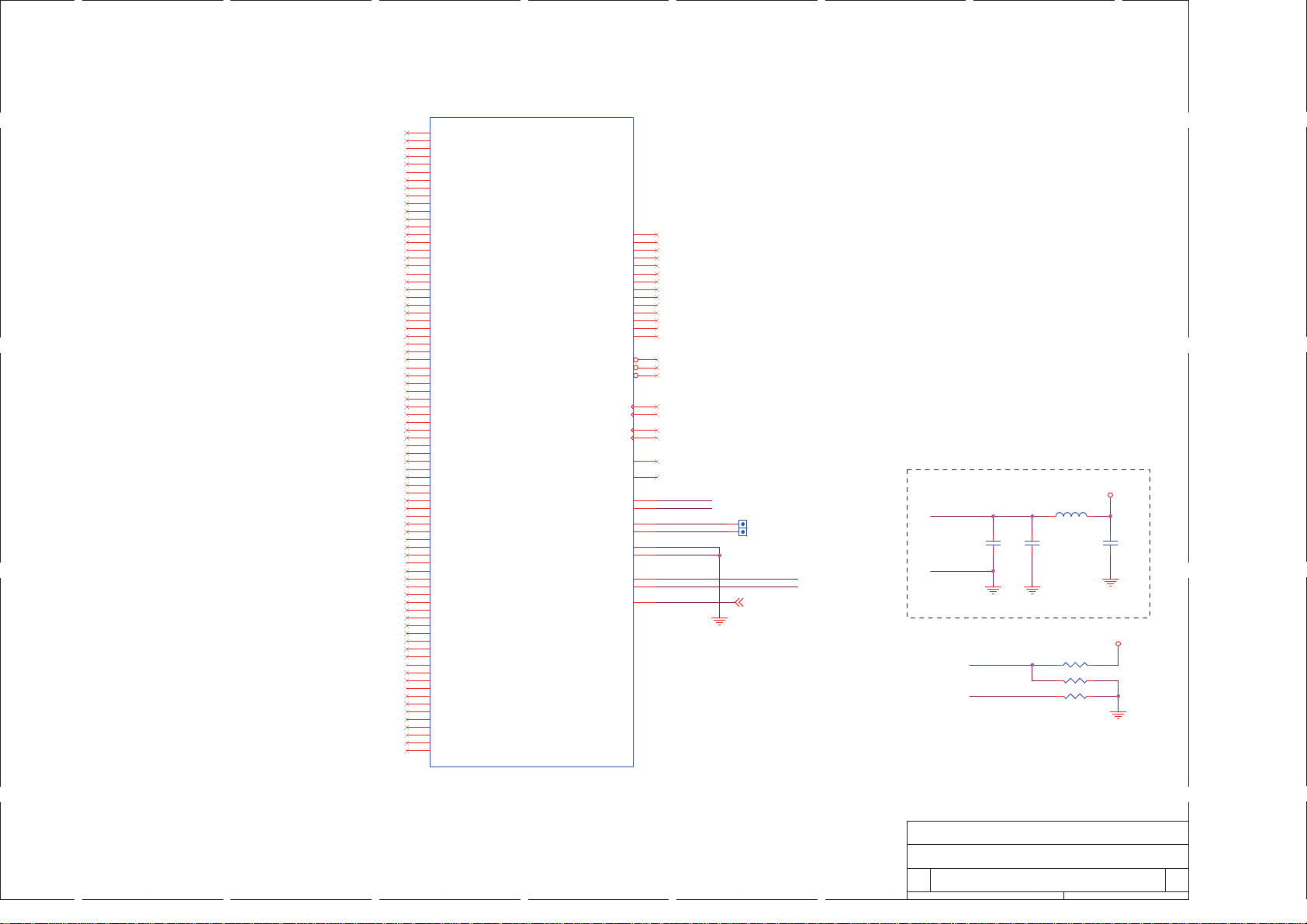

05_CPU1

06_CPU2

07_CPU3

08_CPU4

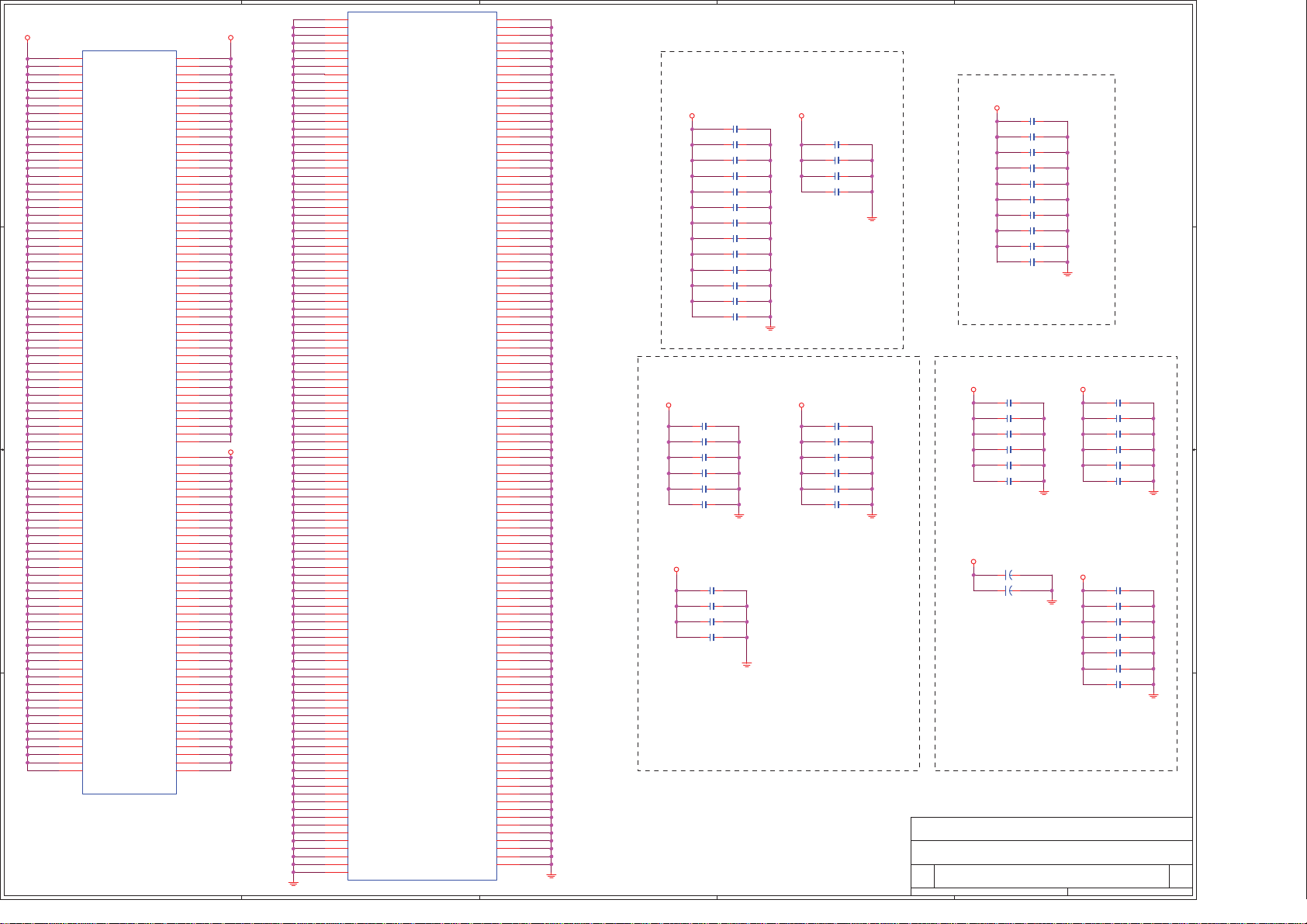

09_DDR SODIMMs

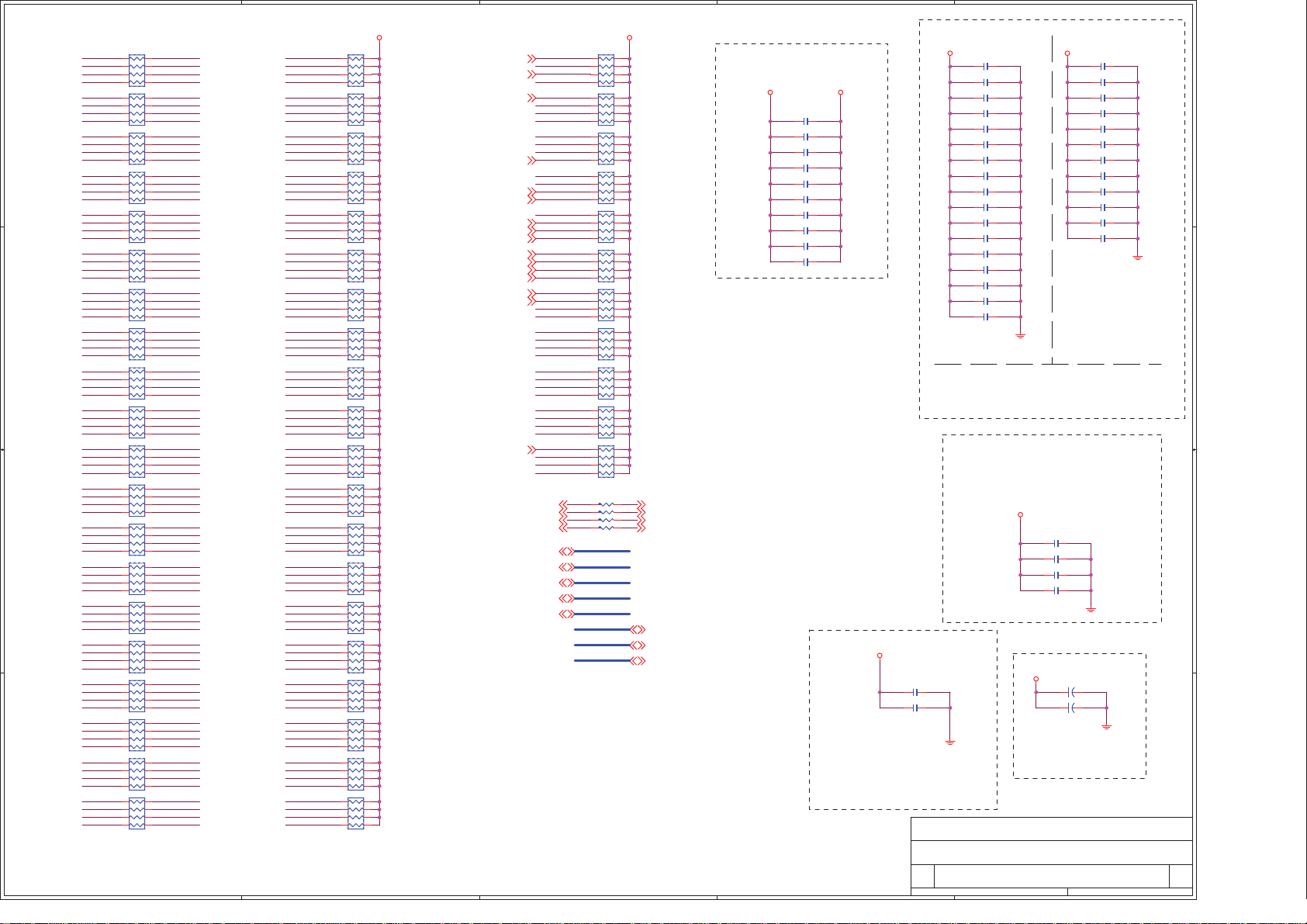

10_DDR TERMINATION

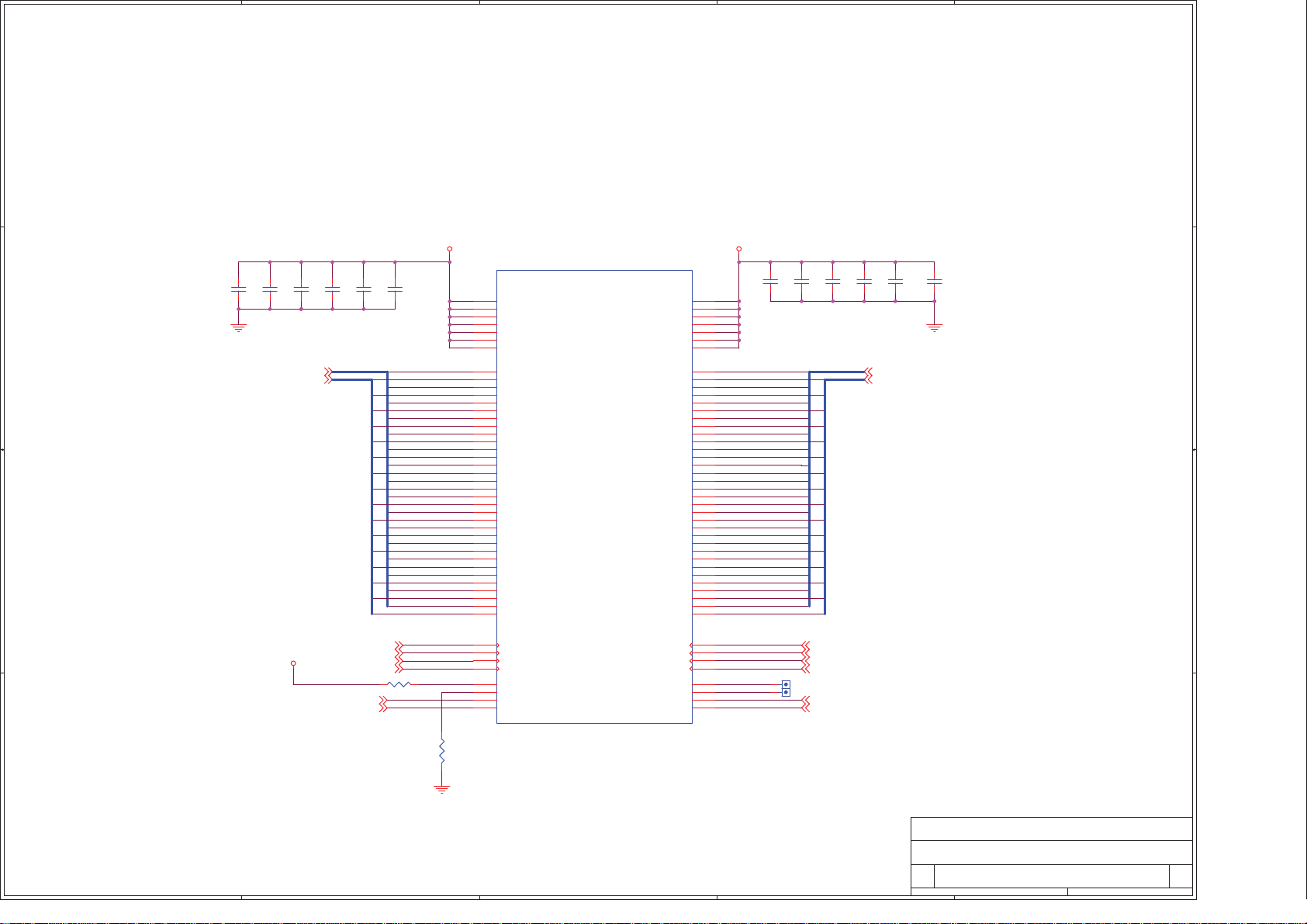

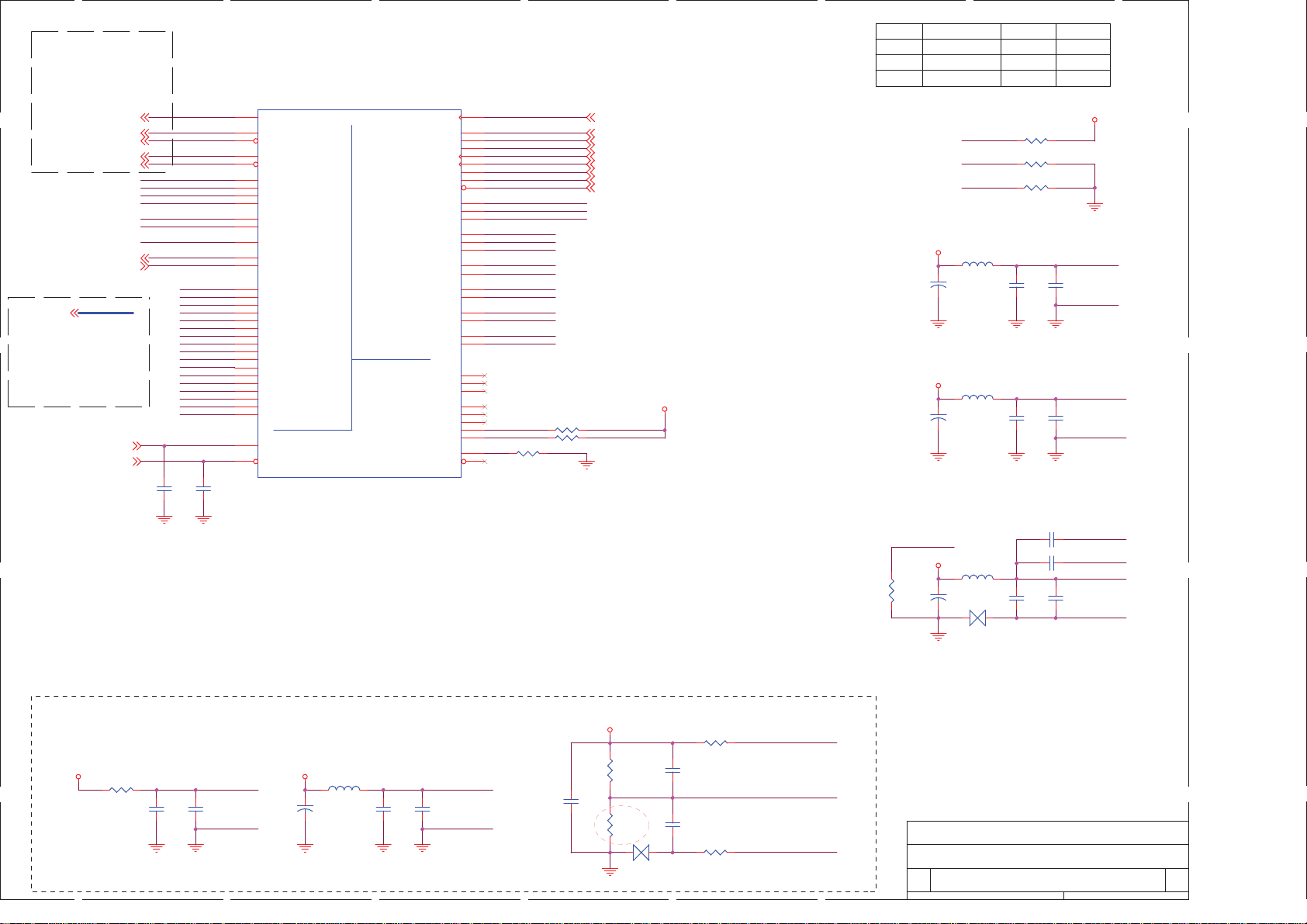

11_M760-1(Host/AGP)

12_M760-2 (for Frame Buffer)

13_M760-3 (MuTIOL/VGA)

14_M760-4 (Power)

C C

15_SIS-301C

16_963L-1 PCI / IDE / MuTIOL

31_ES60x8_MEM&EPROM

32_EX60x8_System / Output

33_EX60x8_Power

34_MST9131

35_Vol. Control / LCD Inverter

36_CRT & S-Video CONN.

37_uP / LCM CONN.

38_M_+1.8V

39_M_+2.5V, +1.25V

40_M_Battery Charger

41_M_Battery Selector

42_M_CPU power

43_M_System Power

44_M_1.2V,1.5V

45_M_Daughter Board

46_History

17_963L-2 MISC Signals

18_963L-3 USB/Others

19_963L-4 Power

20_Main Clock Generator

4

Impedence Test

Antenna Hole

H7

NPTH_200

l3_4mil

l6_4mil

l1_4mil

l8_4mil

3

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

2 1

JP6

JP12

JP4

JP15

JP7

JP17

JP8

JP16

JP13

JP21

JP11

JP20

JP3

JP18

JP14

JP19

l1_diff_6mil

l1_diff_6mil#

l1_diff_5mil

l1_diff_5mil#

l8_diff_6mil

l8_diff_6mil#

l8_diff_5mil

l8_diff_5mil#

l3_diff_4mil

l3_diff_4mil#

l6_diff_4mil

l6_diff_4mil#

H25

HOLES_S276D118

1

H22

HOLES_S276D118

1

holes_r213d118_pt

H5

1

holes_r213d118_pt

H6

1

2

H13

HOLES_S276D118

1

H8

HOLES_S276D118

1

holes_r276d185

H10

holes_r276d185

H9

H16

HOLES_S276D118

1

H3

HOLES_S276D118

1

CPU'sNB

1

1

H1

HOLES_S276D118

1

H17

HOLES_S276D118

1

holes_r276d185

H14

1

holes_r276d185

H15

1

H23

HOLES_S276D118

1

H11

HOLES_S276D118

1

HOLES_R244D142PT

H18

1

H19

HOLES_S276D118

1

H24

HOLES_S276D118

1

MDC Stand off

HOLES_R244D142PT

H20

1

MB position fixed rib

H21

NPTH_80

H2

NPTH_80

H4

HOLES_S276D118

1

H12

HOLES_S276D118

1

1

21_KBC W83950D / FAN

C391

C_NC

0.1UF/25V

C408

C_NC

1

PWR_SRC

C512

C_NC

C783

C_NC

+3VS

V_CORE

C549

C_NC

C138

C_NC

PV22

PAD-98X197_NC

GND

1

PV23

PAD-20X40X53

GND

1

PV13

PAD-98X197_NC

GND

1

PV8

PAD-20X40X53

GND

1

PV7

PAD-98X197_NC

GND

1

PV20

PAD-20X40X53

GND

1

For EMI

PV21

PAD-20X40X53

GND

1

PV9

PAD-20X40X53

GND

1

PV3

PAD-98X197_NC

GND

1

PV18

PAD-20X40X53_NC

GND

1

PV4

PAD-98X197_NC

GND

1

PV10

PAD-98X197_NC

GND

1

PV17

PAD-20X40X53_NC

GND

1

PV1

PAD-98X197_NC

GND

1

PV15

PAD-98X197_NC

GND

1

PV12

PAD-98X197_NC

1

PV16

PAD-98X197_NC

GND

1

PAD-98X197_NC

GND

PAD-98X197_NC

PV11

PV19

1

GND

1

1

GND

PAD-98X197_NC

PV2

PAD-98X197

GND

1

PV6

GND

1

1

PV5

PAD-98X197_NC

GND

1

PV14

PAD-98X197_NC

GND

1

22_Power Control

23_AV Power / Switches & LEDs

B B

24_ENE 1410

25_Audio CODEC

26_Audio AMP & Jack

27_Mini PCI & MDC conn.

28_USB Ports / LPC BIOS

29_HDD & CDROM conn.

30_LAN PHY RTL8201

A A

For EMI

+1.8VS

+3VS

C392

C_NC

C135

C_NC

+3VS

+VDDIO

C277

0.1UF/25V

C630

C_NC

+3VS

C140

PWR_SRC

FM13

X

X_FM

5

FM17

X

X_FM

FM10

X

X_FM

FM18

X

X_FM

FM14

X

X_FM

FM11

X

X_FM

4

FM9

X

X_FM

FM12

X

X_FM

X

X_FM

FM15

X

X_FM

FM1

X

X_FM

3

FM2

X

X_FM

FM6

X

X_FM

FM5

X

X_FM

FM8

FM3

X

X_FM

FM4

X

X_FM

FM16

FM7

X

X

X_FM

X_FM

2

Title

Cover

Size Document Number Rev

Custom

Date: Sheet of

MSI CORPORATION

MS-1011

145Thursday, October 07, 2004

0.B

1

Page 2

5

4

3

2

1

U100

D D

CPU BRACKET MYLAR

U101

CPU BRACKET

U102

DDR MYLAR

C C

U104

PCMCIA BRACKET

U105

PCMCIA MYLAR

U106

SCREW1

PCMCIA SCREW

SCREW8

CRT SCREW

U108

Rubber_10x10x1T

U103

SCREW2

PCMCIA SCREW

SCREW9

CRT SCREW

U109

Rubber_10x10x1T

SCREW3

MDC SCREW

U110

Rubber_10x10x1T

SCREW4

MDC SCREW

U111

Rubber_10x10x1T

SCREW5

HDD CONN SCREW

U112

Rubber_10x10x1T

SCREW6

HDD CONN SCREW

U113

Rubber_10x10x1T

U114

Rubber_10x10x1T

B B

RTC battery

Rubber_10x5x5T

U107

A A

MDC

Title

<Title>

Size Document Number Rev

<Doc> <RevCode>

B

11Thursday, October 07, 2004

5

4

3

2

Date: Sheet

1

of

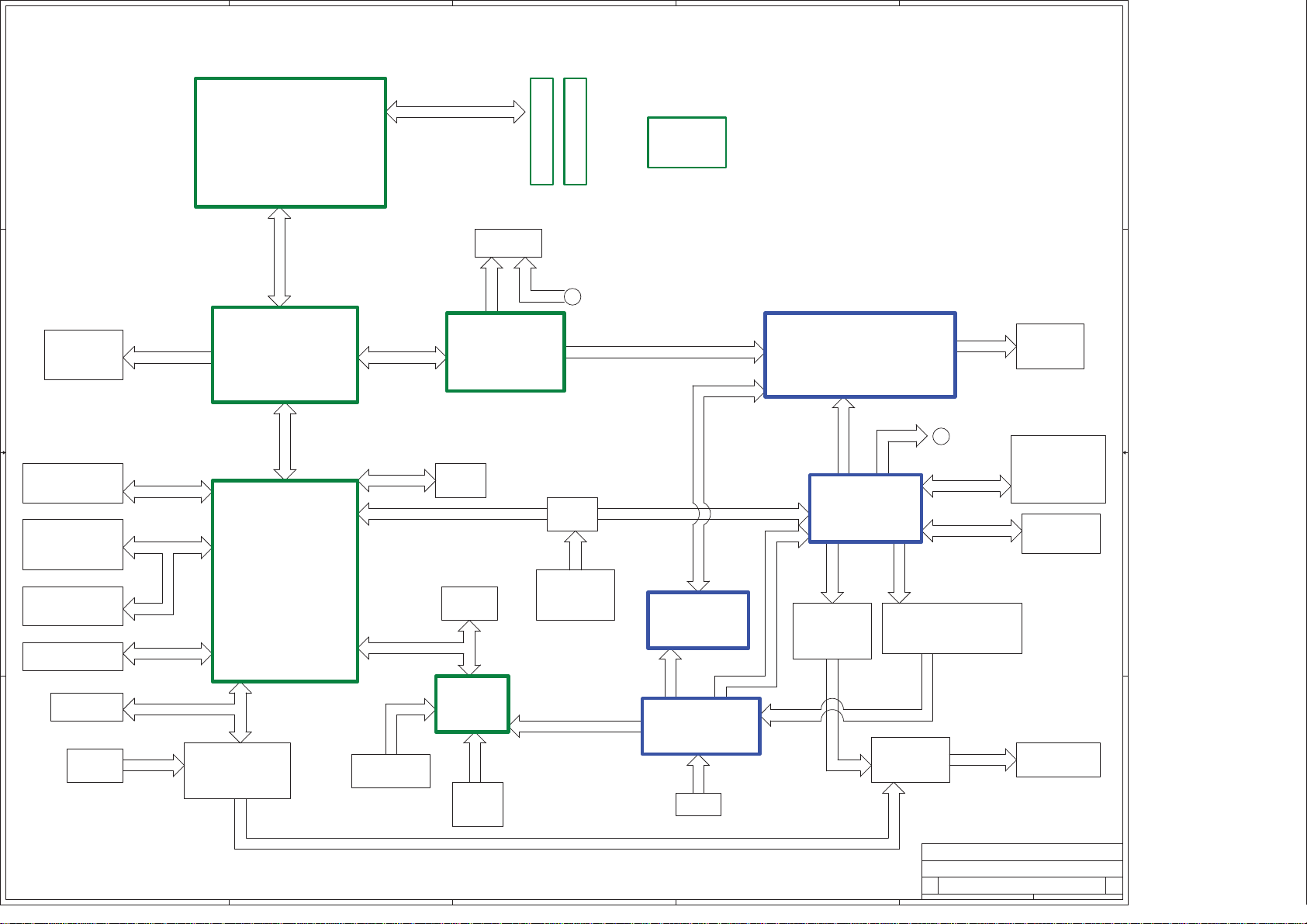

Page 3

5

www.schematic-x.blogspot.com

4

3

2

1

MS-1011 System Block Diagram

DDR 333/400

D D

AMD K8 Socket 754

DDR SODIMM * 2

Clock

Generator

HT

C C

CRT

RGB

North Bridge

VB

SIS M760

MuTIOL

USB 2.0 x4

CardBus

ENE1410

B B

USB

PCI

South Bridge

SIS963L

Mini PCI

Socket

MII

LAN PHY

MDC

AC Link

PIDE

SIDE

LPC

W83950D

S-video

301C

HDD

BIOS

KBC/ uP

SiS

CVBS

2

Switch

DVD-ROM

JIM Bus

OSD

Selection

DVI

I2C

uP

MX10E8050

uP

ATAPI

IR

Scaler

MStar MST9131

CVBS

RGB

DVD Player

ES6028

I2S VFD

Audio DAC

PCM1742

Key Matrix

LVDS

2

LCM & Key PAD

Modual

TFT LCD

Panel

Frame Buffer

SDRAM

4Mx16

ROM

1Mx8

EM78P447SAS

Mic

A A

AC'97 CODEC

ALC655

Keyboard

Touch

PAD

CIR

Audio Amp

APA2121

Speaker/HP

5

Title

Size Document Number Rev

Custom

4

3

2

Date: Sheet of

MSI CORPORATION

System Block Diagram

MS-1011

1

245Thursday, October 07, 2004

0.B

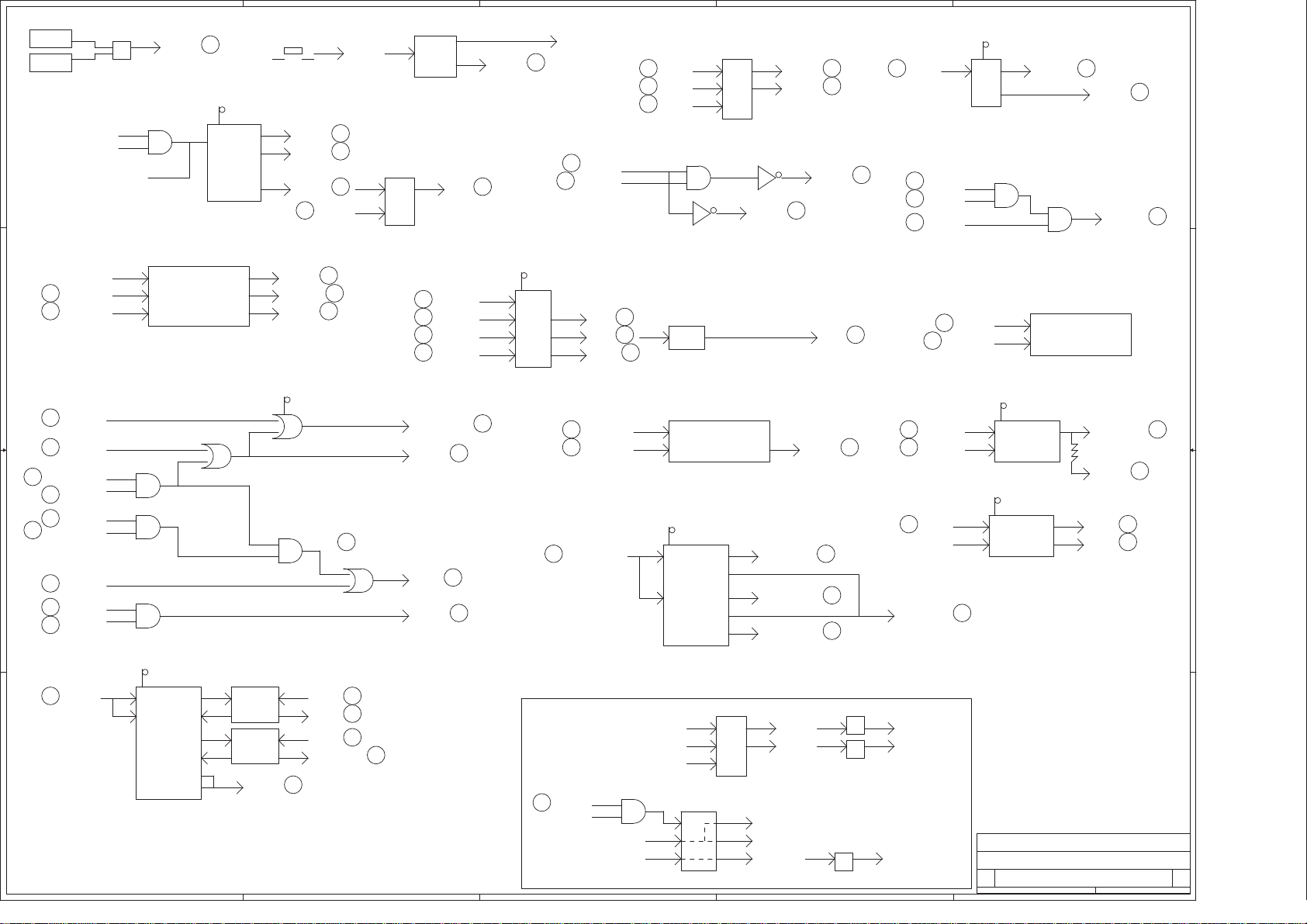

Page 4

5

4

3

2

1

W83L950D

7 PS_ON#

+5VALW

2

+3VALW

2

+1.8VAUX5

VTT_VDDIO_EN

VDDA_EN

VDD_EN

14

VLDT_EN

(delay 100ms by KBC)

AUX_ON 3

9+12V

9

12

16

PWRBTN_SB#

7

PS_ON#

S3AUXSW#5

+3VALW

2

+5VALW

2

AUX_ON3

EN

SLP_S4

8SLP_S3#

4+3VAUX

4+5VAUX

SLP_S4# 8

2 +5VAUX

13.5

AND_PG

VLDT_PG17

SLP_S3#8

MAX1844

PWR_SRC

(RC delay 47ms)

5+1.8VAUX

AUX_OK

6

ALL_PWRGD 18

+12V

EN

+5VS

+3VS

+1.8VS

10

10

(delay 200ms by MAX809)

MAX809

11P_OK

10

CPURST#20

18 ALL_PWRGD

RESET_L

PWROK

AMD K8 M-64

+12VAUX

PCIRST#19

PCIRST#

PWROK18 CPURST# 20

LDTRESET#ALL_PWRGD

SISM760

VDDA_EN12 VOUTEN

+2.5VS(VDDA) 13

VINVDDIO10

VDDA_PG 13

PWR_SRC

PWR_SRC

VTT_VDDIO_EN9EN

VTT

VTT(+1.25V)

PG

EN

VOUT

VDDIO(+2.5V)

PG

VTT_PG

VDDIO_PG

14 VDD_EN

10

VID[4:0]

10

VTT_VDDIO_PG 10

SHDN# VOUT

VID[4:0]

MAX1544

VHCOREPG15

VDD_PG 15

VTTR 10VREF(VDDIO/2)

ADATPER

BATTERY

D D

LM86's CRIT#

K8's THRMTRIP#

PWR_SRC

PWRBTN_SB#

6 AUX_OK 5

AUX_OK

ALL_PWRGD

C C

PWR_SRC 1

PWRBTN#

PWROK

SIS963L

SHDN#

MAX1632

PS_ON#

PCIRST#

PWR_SRC

POWER

BUTTON

PS_ON#

S3AUXSW#GPIO14

PCIRST#

PWRBTN#

2+3VALW

2+5VALW

2+12VALW

SLP_S4#

8

EN

7

1918

+3VAUX

8 SLP_S4#

VDD_PG

15

VTT_VDDIO_PG

10

P_OK

11

VDDA_PG

13

VTT_VDDIO_PG10

B B

VLDT_PG

17

VDD_PG

15

SLP_S3#

8

AND_PG

13.5

MAX8550

+5VAUX

VLDT_EN16

A A

5

DRV1EN1

EN2

DRV2

ADJ2 ADJ

PG1

PG2 VLDT_PG 17

SC338

EN

VIN

VOUTADJADJ1

EN

VIN

VOUT

+1.8VS 10

+1.5VS

+1.8VS 10

VLDT(+1.2V)1717

4

DIRECT

PLAY

PS_ON#

7

AV_ON#

+3V_DVD+3VALW

+5VALW +5V_DVD

AV_ON#

EN

EN

+5V_CDR

+5V_AMP+5VALW

+3VALW

3

+3V_SCALER

2

+2.8V_ESS

+3.6V_ESS

+2.5V_SCALER

Title

Size Document Number Rev

C

Date: Sheet of

MSI CORPORATION

BLOCK DIAGRAM

MS-1011

1

345Thursday, October 07, 2004

0.B

Page 5

5

4

3

2

1

MS-1011 System Power on Sequency From AV Mode to PC Mode

PWR_SRC

D D

PC_MODE

AV_PWRBTN#

AV_ON#

+3VALW/+5VALW

Scaler, Amplify and

DVD-ROM Power

DVD Power

PWR_SW#

AUX_ON

+5VAUX,+3VAUX,+1.8VAUX

AUX_OK

S3AUXSW#

C C

PWRBTN_SB#

PS_ON#

+5VS,+3VS,+1.8VS

SLP_S3#

SLP_S4#

+12V

VTT_VDDIO_EN

+VTT,+VDDIO

VTT_VDDIO_PG

CLK_GEN

B B

PWORK_OK

VDDA_EN

+2.5VS

VDDA_PG

VDD_EN

VHCORE

VDD_PG

VLDT_EN

+1.5VS,+1.2VS

VLDT_PG

A A

CPU_PWRGD

PWRGD_NB_SB

PCIRST#

CPURST#

5

Switch de-bounce time

100 ms

4

100 ms

delay

47ms

by RC

delay 100ms

by KBC

63ms~

94ms

delay 200ms

by MAX809

9ms~12ms

12ms~14ms

Title

Size Document Number Rev

3

2

Date: Sheet

MSI CORPORATION

POWER UP SEQUENCE

Custom

MS-1011

0.B

445Thursday, October 07, 2004

of

1

Page 6

A

B

C

D

E

LAYOUT: Place HT bypass caps on topside

Clawhammer HT Interface

near unconnected Clawhammer HT Link

4 4

VLDT Power Decoupling

VLDT Plane Rout with 250 mil trace or a plane

VLDT plane In CPU pins rout >100 mil

+1.2VS+1.2VS

U37A

C563

C565

100UF/6.3V_1210

0.22UF

0.22UF

3 3

CADIP[0..15]11

CADIN[0..15]11

2 2

C564

0.22UF

C559

0.22UF

C569

C562

4.7UF_1206

CADIP15

CADIN15

CADIP14

CADIN14

CADIP13

CADIN13

CADIP12

CADIN12

CADIP11

CADIN11

CADIP10

CADIN10

CADIP9

CADIN9

CADIP8

CADIN8

CADIP7

CADIN7

CADIP6

CADIN6

CADIP5

CADIN5

CADIP4

CADIN4

CADIP3

CADIN3

CADIP2

CADIN2

CADIP1

CADIN1

CADIN0

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

T27

T28

V29

U29

V27

V28

Y29

VLDT_A6

VLDT_A5

VLDT_A4

VLDT_A3

VLDT_A2

VLDT_A1

VLDT_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

AH29

AH27

AG28

AG26

AF29

AE28

AF25

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

CADOP15

CADON15

CADOP14

CADON14

CADOP13

CADON13

CADOP12

CADON12

CADOP11

CADON11

CADOP10

CADON10

CADOP9

CADON9

CADOP8

CADON8

CADOP7

CADON7

CADOP6

CADON6

CADOP5

CADON5

CADOP4

CADON4

CADOP3

CADON3

CADOP2

CADON2

CADOP1

CADON1

CADOP0CADIP0

CADON0

0.22UF

C552

0.22UF

C557

0.22UF

C554

0.22UF

C553

C528

4.7UF_0805

CADOP[0..15] 11

CADON[0..15] 11

C531

100UF/6.3V_1210

CTLOP1

CTLON1

CLKOP1

CLKON1

CLKOP0

CLKON0

CTLOP0

CTLON0

TP45

TP44

CLKOP1 11

CLKON1 11

CLKOP0 11

CLKON0 11

CTLOP0 11

CTLON0 11

+1.2VS

CTLIP011

CTLIN011

CLKIP111

CLKIN111

CLKIP011

CLKIN011

R257 49.9_1%

CTLIP1

CTLIN1

W25

Y25

Y27

Y28

R27

R26

T29

R29

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

J26

J27

J29

K29

N25

P25

P28

P27

ZIF_SOCKET754

R260

49.9_1%

1 1

Title

CPU SocketA (Host)

Size Document Number Rev

C

A

B

C

D

Date: Sheet of

MSI CORPORATION

MS-1011

545Thursday, October 07, 2004

0.B

E

Page 7

A

B

C

D

E

Clawhammer DDR Interface

1000PF_NC

+VTT

4 4

MD[63:0]10

3 3

2 2

DM[7:0]10

DQS[7:0]10

1 1

C600

A

SNS_+1.25VTT

DDRVREF_CPU

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

DM8

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

DQS8

DQS7

DQS6

DQS5

DQS4

DQS3

DQS2

DQS1

DQS0

AE13

AG12

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

A13

AA1

AG1

AH7

AH13

A14

AB1

AJ2

AJ8

AJ13

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

U37B

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

ZIF_SOCKET754

RSVD_MEMADDA15

RSVD_MEMADDA14

RSVD_MEMADDB_B15

RSVD_MEMADDB_B14

B

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB_B13

MEMADDB_B12

MEMADDB_B11

MEMADDB_B10

MEMADDB_B9

MEMADDB_B8

MEMADDB_B7

MEMADDB_B6

MEMADDB_B5

MEMADDB_B4

MEMADDB_B3

MEMADDB_B2

MEMADDB_B1

MEMADDB_B0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

+VTT

MEMRST#

DCLK7+

DCLK7DCLK6+

DCLK6DCLK5+

DCLK5DCLK4+

DCLK4DCLK3+

DCLK3DCLK2+

DCLK2DCLK1+

DCLK1DCLK0+

DCLK0-

CS7#

CS6#

CS5#

CS4#

CS3#

CS2#

CS1#

CS0#

MA15

MA14

MA13

MA12

MA11

MA10

MA9

MA8

MA7

MA6

MA5

MA4

MA3

MA2

MA1

MA0

MB15

MB14

MB13

MB12

MB11

MB10

MB9

MB8

MB7

MB6

MB5

MB4

MB3

MB2

MB1

MB0

TP65

CKE0 9,10

CKE1 9,10

DCLK7+ 9,10

DCLK7- 9,10

DCLK6+ 9,10

DCLK6- 9,10

DCLK5+ 9,10

DCLK5- 9,10

DCLK4+ 9,10

DCLK4- 9,10

TP114

TP113

TP119

TP118

TP66

TP69

TP67

TP68

CS3# 9,10

CS2# 9,10

CS1# 9,10

CS0# 9,10

SRASA# 9,10

SCASA# 9,10

SWEA# 9,10

MEMBAA1 9,10

MEMBAA0 9,10

TP60

TP59

MA[13:0] 9,10

SRASB# 9,10

SCASB# 9,10

SWEB# 9,10

MEMBAB1 9,10

MEMBAB0 9,10

TP63

TP62

MB[13:0] 9,10

C

+VREF

DDRVREF_CPU

C601

C602

1000PF

0.1UF

MEMZN

R285 34.8_1%

MEMZP

R287 34.8_1%

MEMZN,MEMZP with

5/10,<1000 mils

DDRVREF with

40~50 mil, 25

mil clearance

or shielded by

GND

0.1 UF, 0603, X7R

1000 PF, 0603, X7R

Near Socket

+VDDIO

D

Routing

in the top layer

MEMDATA[63:0] with 5/15

MEMDQS[8:0] with 5/20

in the bottom layer

MEMADDA[13:0] with 5/15

MA COMMAND with 5/15

MEMCLK_H/L are routed

20/5/5/5/20 trace

width/spacing., 20 mil

spacing

Rout DDR nets 50 mil

sapcing to their own

net

DCLK1-

R306 10K

DCLK0-

R304 10K

DCLK1+

R307 10K

DCLK0+

R305 10K

DM8

DQS8

Title

CPU SocketA (DDR Interface)

Size Document Number Rev

Custom

Date: Sheet

MSI CORPORATION

MS-1011

+VDDIO

TP71

TP116

645Thursday, October 07, 2004

E

of

0.B

Page 8

A

VDDA

4 4

CPUCLK0_H20

3 3

2 2

1 1

CPUCLK0_L20

Cap close to

thermal

sensor

THERM_THDN#39,43

2N7002

+3VS

C573

C571

Q48

D S

3900PF

3900PF

G

Max current

105 mA

L58 180nH/1210

+1.2VS

Place near CPU in 1" , Routed

=> 5:10/Trace:Space , Same

Length

R284

169_1%

Rout 5/5/5 mil,

Long:<500 mils and

20 mils spacing

THERMDA

C555

2200PF_0402

THERMDC

THERMTRIP#

R269

4.7K

R437 0

Width:50mil and

Long:500~750mil

R274 44.2_1%

R277 44.2_1%

CPUCK+

Near CPU in 0.5" .

CPUCK-

V_CORE

+VDDIO

C551

0.1UF_0402

+3VALW

B

C558

1000PF_0402

1000PF_NC

C572

1000PF_NC

C193

TP55

R439

0

2

D+

3

D-

4

T_CRIT_A#

LM86_MSOP8

Close to CPU socket

C556

1000PF_0402

CPURST#

U33

Width:50mil and Long:500mil

81

7

6

5

C567

3300PF

+VDDIO

+2.5VS

SMB_CLK_EC

SMB_DATA_EC

R280 820

R279 820

R270 4.7K

C560

4.7UF_0805

+VTT

CORE_SENSE

SNS_+2.5VDIMM

SMBCLKVDD

SMBDATA

ALERT#

GND

C566

0.22UF

CPURST#11

CPU_PWRGD22

HTSTOP_L11

COREFB+42

COREFB-42

TP61

TP64

TP46

TP47

TP56

TP58

TP52

TP57

TP51

TP53

R281 1K_0402

R283 1K_0402

NC_AE23

NC_AF21

NC_AF22

NC_AF23

123456

78

C

COREFB+

COREFB-

CORE_SENSE

VDDIOFB+

VDDIOFB-

SNS_+2.5VDIMM

CPUCK+

CPUCK-

BPSCLK+

BPSCLK-

PLLCHRZ+

PLLCHRZ-

DBRDY

DCLKTWO

TMS

TCK

TRST#

TDI

NC_C18

NC_A19

RN16

1K_8P4R_0402

SMB_CLK_EC 21,41

SMB_DATA_EC 21,41

+3VS

R440 0

U37C

AH25

VDDA1

AJ25

VDDA2

AF20

RESET_L

AE18

PWROK

AJ27

LDTSTOP_L

AF27

L0_REF1

AE26

L0_REF0

A23

COREFB_H

A24

COREFB_L

B23

CORE_SENSE

AE12

VDDIOFB_H

AF12

VDDIOFB_L

AE11

VDDIO_SENSE

AJ21

CLKIN_H

AH21

CLKIN_L

AJ23

NC

AH23

NC

AE24

NC

AF24

NC

C16

VTT_A5

AG15

VTT_B5

AH17

DBRDY

C15

NC

E20

TMS

E17

TCK

B21

TRST_L

A21

TDI

C18

NC

A19

NC

A28

KEY1

AJ28

KEY0

AE23

NC

AF23

NC

AF22

NC

AF21

NC

C1

FREE29

J3

FREE31

R3

FREE33

AA2

FREE35

D3

FREE1

AG2

FREE37

B18

FREE4

AH1

FREE38

AE21

FREE41

C20

FREE7

AG4

FREE11

C6

FREE12

AG6

FREE13

AE9

FREE14

AG9

FREE40

ZIF_SOCKET754

THERMTRIP_SB# 17

D

E

Clawhammer Control and Debug

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

G_FBCLKOUT_H

G_FBCLKOUT_L

DBREQ_L

TDO

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

R436

A20

THERMDA

A26

THERMDC

A27

VID4

AG13

VID3

AF14

VID2

AG14

VID1

AF15

VID0

AE15

NC_AG18

AG18

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

AH18

AG17

AJ18

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

AF18

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

NC_AH18

NC_AG17

NC_AJ18

FBCLKOUT+

FBCLKOUT-

DBREQ#

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

THERMTRIP#

0

VID4 42

VID3 42

VID2 42

VID1 42

VID0 42

R289 80.6_1%

Zdiff = 80 ohm

TP54

TP48

NC_AG18

NC_AJ18

NC_AH18

NC_AG17

NC_D18

NC_C19

NC_D20

NC_C21

NC_B19

LAYOUT: Route

FBCLKOUT_H/L differentially

with 20/8/5/8/20 spacing and

trace width. ( In CPU

breakout => routed 5:5:5 )

+VDDIO

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R282 1K_0402

RN17

1K_8P4R_0402

RN14

1K_8P4R_0402

Title

CPU SocketA (Control and Debug)

Size Document Number Rev

C

A

B

C

D

Date: Sheet of

MSI CORPORATION

MS-1011

745Thursday, October 07, 2004

0.B

E

Page 9

A

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

+VDDIO

V_CORE

V_CORE

U37D

L7

VDD1

AC15

VDD2

H18

VDD3

B20

VDD4

E21

VDD5

H22

VDD6

J23

VDD7

H24

4 4

3 3

2 2

1 1

F26

V10

G13

K14

Y14

AB14

G15

AA15

H16

K16

Y16

AB16

G17

AA17

AC17

AE17

F18

K18

Y18

AB18

AD18

AG19

E19

G19

AC19

AA19

F20

H20

K20

M20

P20

T20

V20

Y20

AB20

AD20

G21

N21

R21

U21

W21

AA21

AC21

F22

K22

M22

P22

T22

V22

Y22

AB22

AD22

E23

G23

N23

R23

U23

W23

AA23

AC23

B24

D24

F24

K24

M24

P24

T24

V24

Y24

AB24

AD24

AH24

AE25

K26

P26

V26

N7

L9

J15

J17

J19

J21

L21

L23

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

ZIF_SOCKET754

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

A

AH20

AB21

W22

M23

AG25

AG27

AF2

AA8

AB9

AA10

B14

Y15

AE16

G20

R20

U20

W20

AA20

AC20

AE20

AG20

AJ20

D21

H21

K21

M21

P21

T21

V21

Y21

AD21

AG21

B22

E22

G22

N22

R22

U22

AG29

AA22

AC22

AG22

AH22

AJ22

D23

H23

K23

P23

T23

V23

Y23

AB23

AD23

AG23

E24

G24

N24

R24

U24

W24

AA24

AC24

AG24

AJ24

B25

C25

B26

D26

H26

M26

T26

Y26

AD26

AF26

AH26

C27

B28

D28

G28

H15

AB17

AD17

B16

G18

AA18

AC18

D19

H19

K19

Y19

AB19

AD19

AF19

N20

B2

L24

D2

W6

Y7

J12

J18

F21

J22

L22

F23

J24

F15

F19

J20

L20

B

U37E

VSS1

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS187

VSS188

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

ZIF_SOCKET754

B

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

C

D

E

Clawhammer Power and Ground Connections

EMI

V_CORE

6.8PF_0402C542

6.8PF_0402C543

6.8PF_0402C153

6.8PF_0402C154

6.8PF_0402C164

6.8PF_0402C155

6.8PF_0402C535

6.8PF_0402C158

6.8PF_0402C156

6.8PF_0402C165

6.8PF_0402C180

6.8PF_0402C157

V_CORE

0.22UFC191

0.22UFC200

0.22UFC192

0.22UFC170

0.22UFC171

C126 10UF_1206

+VDDIO

0.22UFC186

0.22UFC217

0.22UFC194

Place these decoupling capacitors on solder

layer of processor

C

V_CORE

V_CORE

C127 10UF_1206

backside

1000PF_0402C159

1000PF_0402C5416.8PF_0402C189

1000PF_0402C179

1000PF_0402C198

0.22UFC201

0.22UFC203

0.22UFC547

0.22UFC539

0.22UFC183

D

backside

Title

Size Document Number Rev

Custom

Date: Sheet

V_CORE

0.22UFC589

0.22UFC587

0.22UFC584

0.22UFC583

0.22UFC580

0.22UFC579

C586 10UF_1206

C582 10UF_1206

C581 10UF_1206

C585 10UF_1206

Place these capacitors in

uPGA socket cavity

+VDDIO

0.22UFC204

0.22UFC213

0.22UFC202

0.22UFC210

0.22UFC614

0.22UFC218

Near Socket

+VDDIO

C279 220UF/6.3V

C278 220UF/6.3V

Near DIMM

+VDDIO

C221 4.7UF_0805

C608 4.7UF_0805

C214 4.7UF_0805

C605 4.7UF_0805

C209 4.7UF_0805

C613 4.7UF_0805

2 Near DIMM; 4

Near Socket

V_CORE

C199 4.7UF_08050.22UFC220

C187 4.7UF_0805

C168 4.7UF_0805

C169 4.7UF_0805

C176 4.7UF_0805

C167 4.7UF_0805

C188 4.7UF_0805

Close to socket

Place these capacitors near socket

MSI CORPORATION

CPU SocketA (CPU_POWER / GROUND)

MS-1011

845Thursday, October 07, 2004

E

of

0.B

Page 10

A

B

C

D

E

+VDDIO

DIMM1

192

132

144

156

168

180

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

GND

GND

GND

GND

GND

GND

GND

GND

GND

104

138

150

162

174

126

186

201

202

MD_0

5

MD_1

7

MD_2

13

MD_3

17

MD_4

6

MD_5

8

MD_6

14

MD_7

18

MD_8

19

MD_9

23

MD_10

29

MD_11

31

MD_12

20

MD_13

24

MD_14

30

MD_15

32

MD_16

41

MD_17

43

MD_18

49

MD_19

53

MD_20

42

MD_21

44

MD_22

50

MD_23

54

MD_24

55

MD_25

59

MD_26

65

MD_27

67

MD_28

56

MD_29

60

MD_30

66

MD_31

68

MD_32

127

MD_33

129

MD_34

135

MD_35

139

MD_36

128

MD_37

130

MD_38

136

MD_39

140

MD_40

141

MD_41

145

MD_42

151

MD_43

153

MD_44

142

MD_45

146

MD_46

152

MD_47

154

MD_48

163

MD_49

165

MD_50

171

MD_51

175

MD_52

164

MD_53

166

MD_54

172

MD_55

176

MD_56

177

MD_57

181

MD_58

187

MD_59

189

MD_60

178

MD_61

182

MD_62

188

MD_63

190

71

73

79

83

72

74

80

84

SO-DIMM1-REVERSE

MD_[63:0] 10

C309

MB[13:0]6,10

C310

0.1UF

1000PF

MB0

MB1

MB2

MB3

MB4

MB5

MB6

MB7

MB8

MB9

MB10

MB11

MB12

MB13

MEMBAB06,10

MEMBAB16,10

MEMBAB0

MEMBAB1

TP100

CS2#6,10

CS3#6,10

TP97

SWEB#6,10

SCASB#6,10

SRASB#6,10

SWEB#

SCASB#

SRASB#

CKE1

CKE16,10

DCLK4+6,10

DCLK4-6,10

DCLK6+6,10

DCLK6-6,10

TP92

TP95

TP91

+VDDIO

TP158

+VDDIO

TP98

TP93

MB13

TP96

DM_0

DM_1

DM_2

DM_3

DM_4

DM_5

DM_6

DM_7

DQS_0

DQS_1

DQS_2

DQS_3

DQS_4

DQS_5

DQS_6

DQS_7

SMBDAT

SMBCLK

TP94

112

111

110

109

108

107

106

105

102

101

115

100

99

97

117

116

98

121

122

12

26

48

62

134

148

170

184

78

119

120

118

96

95

35

37

160

158

89

91

11

25

47

61

133

147

169

183

77

193

195

194

196

198

1

2

199

197

86

85

123

124

200

VDDQ

GND

103

131

VDDQ

GND

125

143

137

155

VDDQ

GND

149

VDDQ

GND

179

157

167

1911022343646587082

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

159

161

173

1854162838405264768890

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

9294114

VDD

VDD

GND

GND

VDD

GND

921334557698193113

MA[13:0]6,10

4 4

MEMBAA06,10

MEMBAA16,10

CS0#6,10

CS1#6,10

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MEMBAA0

MEMBAA1

TP87

DM_[7:0]10

3 3

TP89

SWEA#6,10

SCASA#6,10

SRASA#6,10

CKE06,10

DCLK5+6,10

DCLK5-6,10

DCLK7+6,10

DCLK7-6,10

TP132

SMBDAT17,20,37

SMBCLK17,20,37

C375

TP137

TP145

TP130

+VDDIO

C353

TP88

TP141

1000PF

MA13

TP90

TP155 TP99

DQS_[7:0]10

2 2

+VREF +VREF

0.1UF

DM_0

DM_1

DM_2

DM_3

DM_4

DM_5

DM_6

DM_7

SWEA#

SCASA#

SRASA#

CKE0

DCLK5+

DCLK5DCLK7+

DCLK7-

DQS_0

DQS_1

DQS_2

DQS_3

DQS_4

DQS_5

DQS_6

DQS_7

SMBDAT

SMBCLK

TP140

112

111

110

109

108

107

106

105

102

101

115

100

99

97

117

116

98

121

122

12

26

48

62

134

148

170

184

78

119

120

118

96

95

35

37

160

158

89

91

11

25

47

61

133

147

169

183

77

193

195

194

196

198

1

2

199

197

86

85

123

124

200

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VREF

VDDID

VDDSPD

NC//DU/RESET

NC/DU

NC/DU

NC/DU

NC/DU

3

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

15273951637587

VDDQ

GND

VDDQ

GND

921334557698193113

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VREF

VDDID

VDDSPD

NC//DU/RESET

NC/DU

NC/DU

NC/DU

NC/DU

3

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

15273951637587

VDDQ

VDDQ

GND

GND

VDDQ

GND

VDDQ

GND

103

131

VDDQ

GND

125

143

VDDQ

GND

137

155

149

157

VDDQ

GND

159

VDDQ

GND

+VDDIO

179

167

1911022343646587082

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

161

173

1854162838405264768890

VDD

GND

VDD

GND

VDD

GND

9294114

VDD

GND

VDD

GND

VDD

GND

DIMM2

192

132

144

156

168

180

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

GND

GND

GND

GND

GND

GND

GND

GND

GND

104

138

150

162

174

126

186

201

202

MD_0

5

MD_1

7

MD_2

13

MD_3

17

MD_4

6

MD_5

8

MD_6

14

MD_7

18

MD_8

19

MD_9

23

MD_10

29

MD_11

31

MD_12

20

MD_13

24

MD_14

30

MD_15

32

MD_16

41

MD_17

43

MD_18

49

MD_19

53

MD_20

42

MD_21

44

MD_22

50

MD_23

54

MD_24

55

MD_25

59

MD_26

65

MD_27

67

MD_28

56

MD_29

60

MD_30

66

MD_31

68

MD_32

127

MD_33

129

MD_34

135

MD_35

139

MD_36

128

MD_37

130

MD_38

136

MD_39

140

MD_40

141

MD_41

145

MD_42

151

MD_43

153

MD_44

142

MD_45

146

MD_46

152

MD_47

154

MD_48

163

MD_49

165

MD_50

171

MD_51

175

MD_52

164

MD_53

166

MD_54

172

MD_55

176

MD_56

177

MD_57

181

MD_58

187

MD_59

189

MD_60

178

MD_61

182

MD_62

188

MD_63

190

71

73

79

83

72

74

80

84

SO-DIMM2-REVERSE

Unbuffered DDR333 SODIMM Sockets

+VDDIO

1 1

C346

47UF/6.3V_1210

C361

47UF/6.3V_1210

A

C342

0.1UF_0402

C312

0.1UF_0402

C356

0.1UF_0402

C339

0.1UF_0402

C360

0.1UF_0402

C357

0.1UF_0402

C377

0.1UF_0402

C345

0.1UF_0402

B

C373

0.1UF_0402

C338

0.1UF_0402

C355

0.1UF_0402

C372

0.1UF_0402

+VDDIO

+VREF

C365 4.7UF

0.22UFC341

Place these two decoupling caps near DIMMs

C

+VDDIO

0.1UF_0402

C315

C319

0.1UF_0402

C371

0.1UF_0402

C358

0.1UF_0402

C359

0.1UF_0402

C374

0.1UF_0402

C340

0.1UF_0402

C313

0.1UF_0402

D

C334

0.1UF_0402

C311

0.1UF_0402

C344

0.1UF_0402

C352

C376

Title

0.1UF_0402

Size Document Number Rev

Custom

Date: Sheet

47UF/6.3V_1210

MSI CORPORATION

DIMM1 & DIMM2 (200 PIN DDR SODIMM)

MS-1011

C337

E

47UF/6.3V_1210

945Thursday, October 07, 2004

of

0.B

+VDDIO

Page 11

A

B

C

D

E

From CPU To DDR Socket

MD_0

MD0

1

MD4

MD5

MD1

DQS0

DM0

4 4

3 3

2 2

1 1

MD2

MD6

MD14

MD15

MD10

MD11

MD20

MD16

MD17

DQS2

MD21

DM2

MD18

MD22

MD26

MD30

MD27

MD31

MD19

MD23

MD24

MD28

MD25

MD29

DQS3

DM3

MD32

MD36

MD33

MD37

DQS4

MD34 MD_34

DM4 DM_4

MD38

MD48

MD49

MD52

MD53

DM6

DQS6

MD54

MD50

MD55

MD51

MD60

MD56

MD61

MD57

DM7

DQS7

MD62

MD58

MD63

MD59

MD7

MD3

MD8

MD9

MD42

MD43

MD46

MD12

DQS1

MD13

DM1

MD39

MD35

MD40

MD44

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

A

MD_4

MD_5

MD_1

DQS_0

DM_0

MD_2

MD_6

MD_14

MD_15

MD_10

MD_11

MD_20

MD_16

MD_17

DQS_2

MD_21

DM_2

MD_18

MD_22

MD_26

MD_30

MD_27

MD_31

MD_19

MD_23

MD_24

MD_28

MD_25

MD_29

DQS_3

DM_3

MD_32

MD_36

MD_33

MD_37

DQS_4

MD_38

MD_41MD41

DQS_5DQS5

DM_5DM5

MD_45MD45

MD_48

MD_49

MD_52

MD_53

DM_6

DQS_6

MD_54

MD_50

MD_55

MD_51

MD_60

MD_56

MD_61

MD_57

DM_7

DQS_7

MD_62

MD_58

MD_63

MD_59

MD_7

MD_3

MD_8

MD_9

MD_42

MD_43

MD_46

MD_47MD47

MD_12

DQS_1

MD_13

DM_1

MD_39

MD_35

MD_40

MD_44

RN31

10_8P4R_0402

RN40

10_8P4R_0402

RN33

10_8P4R_0402

RN38

10_8P4R_0402

RN29

10_8P4R_0402

RN27

10_8P4R_0402

RN37

10_8P4R_0402

RN28

10_8P4R_0402

RN26

10_8P4R_0402

RN25

10_8P4R_0402

RN24

10_8P4R_0402

RN23

10_8P4R_0402

RN34

10_8P4R_0402

RN22

10_8P4R_0402

RN41

10_8P4R_0402

RN32

10_8P4R_0402

RN30

10_8P4R_0402

RN35

10_8P4R_0402

RN39

10_8P4R_0402

RN36

10_8P4R_0402

MD_0

MD_1

DQS_0

MD_2

MD_4

MD_5

DM_0

MD_6

MD_13

DM_1

MD_16

MD_17

MD_14

MD_15

DQS_2

MD_18

MD_29

DM_3

MD_30

MD_31

MD_37

MD_34

DM_4

MD_38

MD_32

MD_33

MD_36

DQS_4

MD_52

MD_53

DM_6

MD_54

MD_46

MD_47

MD_42

MD_43

DQS_6

MD_61

DM_7

MD_50

MD_39

MD_35

MD_44

MD_40

MD_26

MD_27

MD_20

MD_21

MD_45

DM_5

MD_41

DQS_5

MD_10

MD_11

MD_7

MD_12

MD_19

MD_24

MD_25

DQS_3

DM_2

MD_22

MD_23

MD_28

MD_48

MD_49

MD_55

MD_60

MD_51

MD_62

MD_63

MD_56

MD_3

MD_8

MD_9

DQS_1

MD_57

DQS_7

MD_58

MD_59

+VTT

B

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

RN72

68_8P4R_0402

RN70

68_8P4R_0402

RN68

68_8P4R_0402

RN67

68_8P4R_0402

RN62

68_8P4R_0402

RN53

68_8P4R_0402

RN54

68_8P4R_0402

RN48

68_8P4R_0402

RN50

68_8P4R_0402

RN46

68_8P4R_0402

RN52

68_8P4R_0402

RN65

68_8P4R_0402

RN51

68_8P4R_0402

RN69

68_8P4R_0402

RN66

68_8P4R_0402

RN63

68_8P4R_0402

RN47

68_8P4R_0402

RN45

68_8P4R_0402

RN71

68_8P4R_0402

RN44

68_8P4R_0402

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

To DDR Socket

CS3#6,9

CS1#6,9

MEMBAA16,9

SRASB#6,9

MEMBAB16,9

SCASB#6,9

MEMBAB06,9

CS2#6,9

SWEB#6,9

CS0#6,9

MEMBAA06,9

SWEA#6,9

CKE16,9

SRASA#6,9

SCASA#6,9

CKE06,9

DCLK7-6,9

DCLK5-6,9 DCLK5+ 6,9

DCLK4-6,9

MA[13:0]6,9

MB[13:0]6,9

MD[63:0]6

DQS[7:0]6

DM[7:0]6

CS3#

MB5

CS1#

MA5

MEMBAA1

MB11

MB8

MA0

MA10

MA1

MA2

SRASB#

MB2

MB0

MEMBAB1

SCASB#

MA13

MEMBAB0

CS2#

SWEB#

CS0#

MEMBAA0

SWEA#

CKE1

SRASA#

SCASA#

MB6

MB4

MB13

MB1

MA4

MA3

MA8

MA6

MB3

MB10

MB7

MA11

MA9

MA7

CKE0

MB12

MB9

MA12

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

R317 120

R303 120

R302 120

R301 120

MD[63:0]

DQS[7:0]

DM[7:0]

MA[13:0]

MB[13:0]

MD_[63:0]

DQS_[7:0]

DM_[7:0]

C

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

+VTT

RN11

47_8P4R_0402

RN57

47_8P4R_0402

RN12

47_8P4R_0402

RN55

47_8P4R_0402

RN49

47_8P4R_0402

RN58

47_8P4R_0402

RN56

47_8P4R_0402

RN59

47_8P4R_0402

RN60

47_8P4R_0402

RN61

47_8P4R_0402

RN64

47_8P4R_0402

DCLK7+ 6,9

DCLK6+ 6,9DCLK6-6,9

DCLK4+ 6,9

MD_[63:0] 9

DQS_[7:0] 9

DM_[7:0] 9

For EMI

+VTT +VDDIO

0.1UF_0402C603

0.1UF_0402C274

0.1UF_0402C335

0.1UF_0402C387

0.1UF_0402C388

0.1UF_0402C382

0.1UF_0402C383

0.1UF_0402C384

0.1UF_0402C385

0.1UF_0402C185

LAYOUT: Add 100pF and 1000pF

VTT fill near Clawhammer and

near DIMMs (Both Sides)

D

+VTT

+VTT

0.1UF_0402C750

0.1UF_0402C749

0.1UF_0402C748

0.1UF_0402C747

0.1UF_0402C746

+VTT

0.1UF_0402C760

0.1UF_0402C771

0.1UF_0402C769

0.1UF_0402C770

0.1UF_0402C767

0.1UF_0402C7680.1UF_0402C756

0.1UF_0402C758

0.1UF_0402C751

0.1UF_0402C395

0.1UF_0402C744

0.1UF_0402C7450.1UF_0402C752

0.1UF_0402C753

0.1UF_0402C754

0.1UF_0402C755

0.1UF_0402C762

0.1UF_0402C763

0.1UF_0402C764

0.1UF_0402C757

0.1UF_0402C759

0.1UF_0402C765

0.1UF_0402C766

0.1UF_0402C761

backside

LAYOUT: Place alternating caps to GND and

+2.5VDIMM in a single line along VTT island.

LAYOUT: Place a cap every 1 inch on VTT

trace between Clawhammer and DDR.

+VTT

C604 0.22UF

C588 0.22UF

C615 0.22UF

C590 4.7UF_0805

+VTT

1000PF_0402C181

1000PF_0402C330

Title

DDR TERMINATION

Size Document Number Rev

C

Date: Sheet

MSI CORPORATION

MS-1011

C577 100UF/6.3V_1210

C592 100UF/6.3V_1210

LAYOUT: Locate close to

ClawHammer socket.

10 45Thursday, October 07, 2004

E

of

0.B

Page 12

8

A

7

6

5

4

3

2

1

CLKIN0 5

VAD[0..11]

VBD[0..11]

CADIN[0..15]5

D D

CADIP[0..15]5

CADOP[0..15]5

CADON[0..15]5

C C

CLKON15

CLKOP15

CLKON05

CLKOP05

CTLON05

CTLOP05

B B

HTSTOP_L7

CPURST#7

+2.5VS

+1.2VS

8

CADIN[0..15]

CADIP[0..15]

CADOP[0..15]

CADON[0..15]

CADON0

CADOP0

CADON1

CADOP1

CADON2

CADOP2

CADON3

CADOP3

CADON4

CADOP4

CADON5

CADOP5

CADON6

CADOP6

CADON7

CADOP7

CADON8

CADOP8

CADON9

CADOP9

CADON10

CADOP10

CADON11

CADOP11

CADON12

CADOP12

CADON13

CADOP13

CADON14

CADOP14

CADON15

CADOP15

LRCOMP

755CLK755CLK+

HTAVDD

HTAVSS

HTPHYAVDD

HTPHYAVSS

HTSTOP_L

LDTREQ#

LDTREST#

R232 1K

R250 1K

R256 100

R255 49.9_1%

R251 49.9_1%

HTSTOP_L

LDTREST#

LRCOMP

LTCOMPN

LTCOMPP

M29

M27

G27

G29

M25

M26

G24

G25

N27

P27

N29

L27

K29

L29

H29

H27

F29

E27

F27

N24

P24

N25

L26

K24

L24

H26

H24

F25

E26

C28

K25

K27

D29

E29

A11

A12

C11

B11

C12

B12

E11

D12

D11

J29

J26

F26

J25

J27

VAD[0..11] 15

VBD[0..11] 15

U30A

LRCAD_N0

LRCAD_P0

LRCAD_N1

LRCAD_P1

LRCAD_N2

LRCAD_P2

LRCAD_N3

LRCAD_P3

LRCAD_N4

LRCAD_P4

LRCAD_N5

LRCAD_P5

LRCAD_N6

LRCAD_P6

LRCAD_N7

LRCAD_P7

LRCAD_N8

LRACD_P8

LRCAD_N9

LRCAD_P9

LRCAD_N10

LRCAD_P10

LRCAD_N11

LRCAD_P11

LRCAD_N12

LRCAD_P12

LRCAD_N13

LRCAD_P13

LRCAD_N14

LRCAD_P14

LRCAD_N15

LRCAD_P15

LRCOMP

LRCLK_N1

LRCLK_P1

LRCLK_N0

LRCLK_P0

LRCTLN

LRCTLP

HTCLKN

HTCLKP

HTAVDD

HTAVSS

HTPHYAVDD

HTPHYAVSS

LDTSTOP#

LDTREQ#

LDTRESET#

M760

CPUCLK1_L20

CPUCLK1_H20

7

CADIN13

CADIN11

CADIN15

CADIN14

CADIP15

CADIP14

CADIP13

D24

D25

E23

E24

F22

F23

LTCAD_P15

LTCAD_P14

LTCAD_P13

LTCAD_N15

LTCAD_N14

LTCAD_N13

HOST_RX

CADIP9

CADIN10

CADIP7

CADIN12

CADIP12

D21

D22

LTCAD_P12

LTCAD_N12

CADIP8

CADIP11

CADIP10

CADIN9

CADIN8

CADIN7

F19

F20

D18

D19

E17

E18

F16

F17

A24

LTCAD_P9

LTCAD_P8

LTCAD_P7

LTCAD_N9

LTCAD_P10

LTCAD_N11

LTCAD_N10

LTCAD_N8

LTCAD_P11

HOST_TX

A25

CADIP6

C23

LTCAD_N7

CADIP3

CADIP5

CADIP4

CADIN5

CADIN4

CADIN6

C24

A22

A23

C21

C22

C19

LTCAD_P6

LTCAD_P5

LTCAD_P4

LTCAD_N6

LTCAD_N5

LTCAD_N4

CADIP0

CADIP2

CADIP1

CADIN3

CADIN2

CADIN1

CADIN0

A20

C20

A18

A19

C17

C18

A16

A17

LTCAD_P3

LTCAD_P2

LTCAD_P1

LTCAD_P0

LTCAD_N3

LTCAD_N2

LTCAD_N1

LTCAD_N0

E20

E21

A21

LTCLK_N0

C25

C26

LTCTLP

LTCTLN

LTCLK_P0

LTCLK_P1

LTCLK_N1

PIPE#/ADBIH

M760-1

AGPCOMP_P

AGPCOMP_N

LVDS/AGP

SBA7

SBA6

SBA5

SBA4

SBA3

SBA2

SBA1

SBA0

ST0

ST1

ST2

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

AAD7

AAD8

AAD9

AAD10

AAD11

AAD12

AAD13

AAD14

AAD15

AAD16

AAD17

AAD18

AAD19

AAD20

AAD21

D2G5D3F4F5E4B3D5C5A5B4V5U6U1U4U3T5T3T6R2P1R5P3P4N2P6N3L3K2K5K6K3J4J1J5G2H4G3F1F2H6E1E3

VAD7

VBD6

VBD5

VBCLK15

CPUCLK1_L 755CLK-

CPUCLK1_H

VBD7

+1.2VS

C471 3900PF

C473 3900PF

VAD6

VAD5

VBD3

VBD4

VBD2

R226

R229

75

R228

VBD0

VBD1

6

VAD4

75

169_1%

755CLK+

VAD11

VAD9

VAD10

VAD8

VBD11

C468

0.1UF_0402

VBD9

VBD8

VBD10

VAHSYNC 15

VAVSYNC 15

VADE 15

5

AAD22

VAD1

AAD23

AAD24

AAD25

VAD0

VAD2

LDTREQ#

AAD26

VAD3

AGPVSSREF

AAD27

LTCOMPN

LTCOMPP

A27

B28

LTCOMP_P

LTCOMP_N

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

RBF#

WBF#

GC_DET#

ADBIL

SB_STB

SB_STB#

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

AGPCLK

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AAD28

AAD29

AAD30

AAD31

+2.5VS

CLKIP0 5

CLKIN1 5

CLKIP1 5

CTLIN0 5

CTLIP0 5

H3

L4

N5

R4

VBCAD

A6

B6

L6

L1

M4

M5

M1

M2

N6

C4

A3

GC_DET#

D6

G6

VBRCLK_NB

E6

C1

C2

T2

R1

J2

H1

AA1

V2

V3

AA4

AA5

AA2

AA3

V1

V4

VBVSYNC 15

VBHSYNC 15

VBCTL1 15

VBCTL0 15

VBDE 15

R396

1K

R397

10K

4

R218 10

R219 10

AGPCLK0

AGPRCOMP

AGPRCOMN

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

R217

0

+3VS

R395

10K

B

Q57

MMBT3904

E C

+1.8VS

R220

4.7K_NC

VBHCLK 15

R16 0_NC

TP33

VAGCLK 15

VBGCLK 15

AGPCLK0 20

AGP_VREF

0.1UF_0402

+3VS

R394

10K

B

E C

3

VBCAD 15

C445

Q58

MMBT3904

A1XAVDD

C38

0.1UF_0402

A1XAVSS

A4XAVDD

C450

0.1UF_0402

A4XAVSS

+1.8VS

HTPHYAVDD

R215

124_1%

R216

124_1%

LDTREQ_GP# 17

LDTREQ# 17

Title

M760_1(HOST/LVDS)

Size Document Number Rev

Custom

MS-1011

Date: Sheet of

C518

0.1UF_0402

HTPHYAVSS

HTAVDD

C65

0.1UF_0402

HTAVSS

MSI CORPORATION

L14

1 2

FB_120_0.6A

C46

0.01UF_0402

L37

1 2

FB_120_0.6A

C442

0.01UF_0402

AGP3.0 = 50 ohm

AGPRCOMN

AGPRCOMP

2

+3VS

+3VS

+1.8VS

R214 49.9_1%

R213 43_1%

L56

1 2

FB_120_0.6A

C514

0.01UF_0402

L15

1 2

FB_120_0.6A

C64

0.01UF_0402

11 45Thursday, October 07, 2004

C66

+

10UF_0805

C432

+

10UF_0805

+3VS

C519

10UF_0805

+3VS

C480

10UF_0805

1

0.B

A

Page 13

8

A

7

6

5

4

3

2

1

D D

C C

B B

AA27

AB28

AB29

AC29

AB26

AA26

AA25

AA29

AF28

AH28

AG27

AH27

AF26

AE25

AD25

AD24

AE26

AG29

AC27

AD29

AD28

AD27

AE29

AC26

AC25

AB24

AE27

AF29

AJ27

AG26

AJ26

AG25

AH25

AG24

AF24

AE23

AF23

AJ24

AJ15

AG16

AH16

AJ16

AE16

AD16

AF17

AD17

AE18

AJ17

AG11

AJ11

AG12

AH12

AF11

AD11

AE12

AD12

AE13

AJ12

AG15

AJ14

AH14

AJ13

AE15

AF15

AF14

AD14

AF13

AG13

AJ10

AH10

AG9

AF10

AE10

AD10

AD9

AH8

Y25

Y24

AJ9

AF9

U30B

DQB0

DQB1

DQB2

DQB3

DQB4

DQB5

DQB6

DQB7

DQMB0

DDRBSTB0

DQB8

DQB9

DQB10

DQB11

DQB12

DQB13

DQB14

DQB15

DQMB1

DDRBSTB1

DQB16

DQB17

DQB18

DQB19

DQB20

DQB21

DQB22

DQB23

DQMB2

DDRBSTB2

DQB24

DQB25

DQB26

DQB27

DQB28

DQB29

DQB30

M760-2

DQB31

DQMB3

DDRBSTB3

DQB32

DQB33

DQB34

DQB35

DQB36

DQB37

DQB38

DQB39

DQMB4

DDRBSTB4

DQB40

DQB41

DQB42

DQB43

DQB44

DQB45

DQB46

DQB47

DQMB5

DDRBSTB5

DQB48

DQB49

DQB50

DQB51

DQB52

DQB53

DQB54

DQB55

DQMB6

DDRBSTB6

DQB56

DQB57

DQB58

DQB59

DQB60

DQB61

DQB62

DQB63

DQMB7

DDRBSTB7

M760

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

WEB

RASB

CASB

SDCLKBN0

SDCLKBN1

SDCLKBP0

SDCLKBP1

CKEB

CSB

DRAMTRAP0

DRAMTRAP1

DRAMTRAP2

DRAMTRAP3

DDRVREFB0

DDRVREFB1

ECLKAVDD

ECLKAVSS

VOSCIE

AJ21

AG22

AH22

AJ23

AH23

AD22

AF22

AD21

AG21

AE21

AE20

AF20

AH20

AJ20

AH18

AG19

AJ19

AG18

AD19

AG17

AD18

AF19

AG20

W26

Y26

Y27

Y28

AJ8

Y29

W28

W29

W27

They need connected

for SiS760 with or

without Local frame

buffer.

DRAMTRAP0

DRAMTRAP1

DDRVREFA

DDRVREFB

VOSCIE

VOSCIE 20

TP38

TP105

ECLKAVDD

ECLKAVSS

SiS760 without Local Frame Buffer

1. Vref -Tie ground (R47,R48 open)

2. MD,DQS,MA,CLK - floation

3. OVDDM connect to VCC3

4. SiS760 seven pins of VBTRAP[3:0],

ECLKAVDD/AVSS, VOSCIE must connect on

board

+3VS

ECLKAVDD

0.1UF_0402

ECLKAVSS

C533

DRAMTRAP0

DRAMTRAP1

L57

1 2

FB_120_0.6A

C538

0.01UF_0402

R59 4.7K

R57 0_NC

R51 0_NC

C534

10UF_0805

+3VS

A

Title

M760_2(Memory For Frame Buffer)

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet

MSI CORPORATION

MS-1011