Page 1

5

www.schematic-x.blogspot.com

4

3

2

1

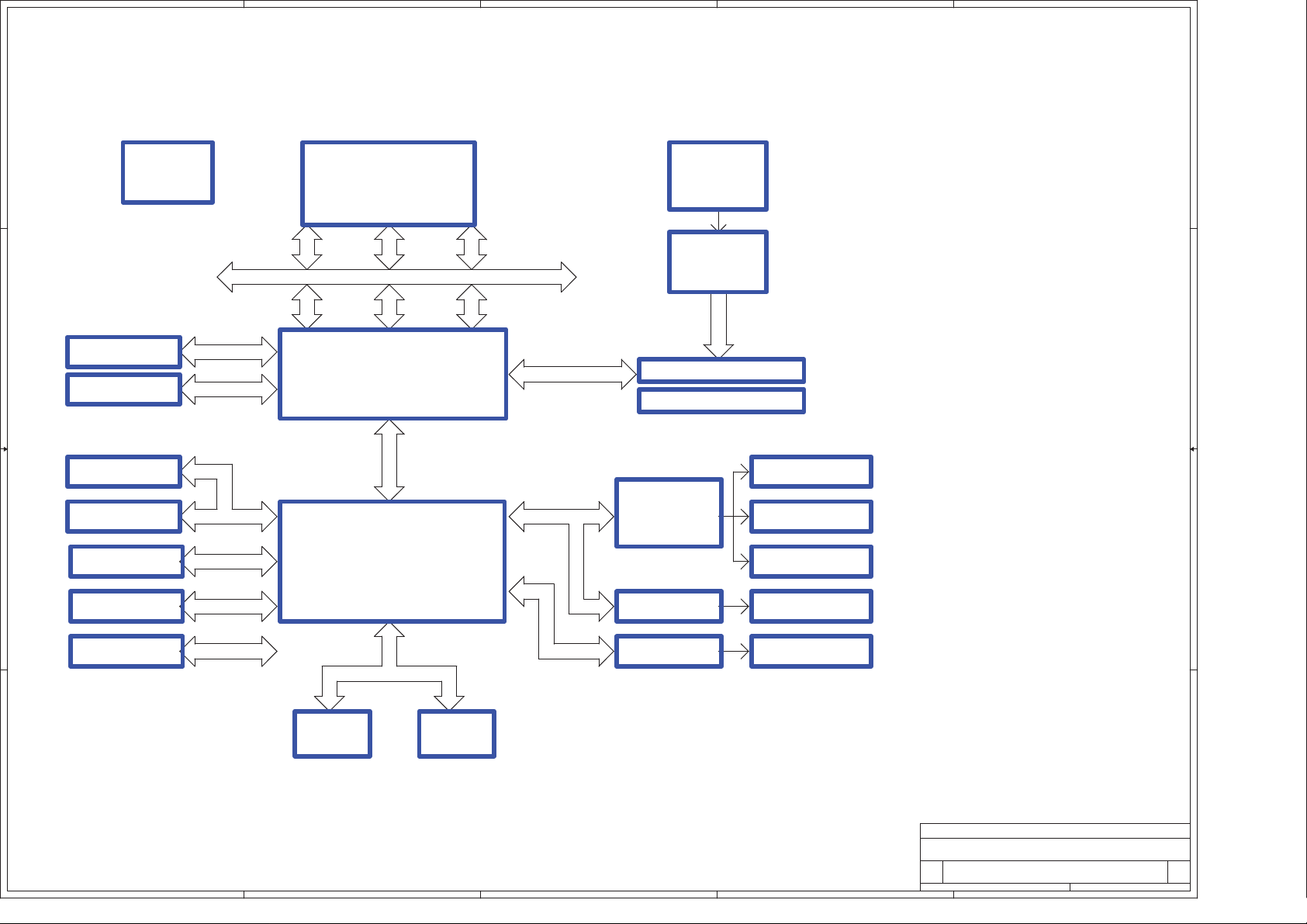

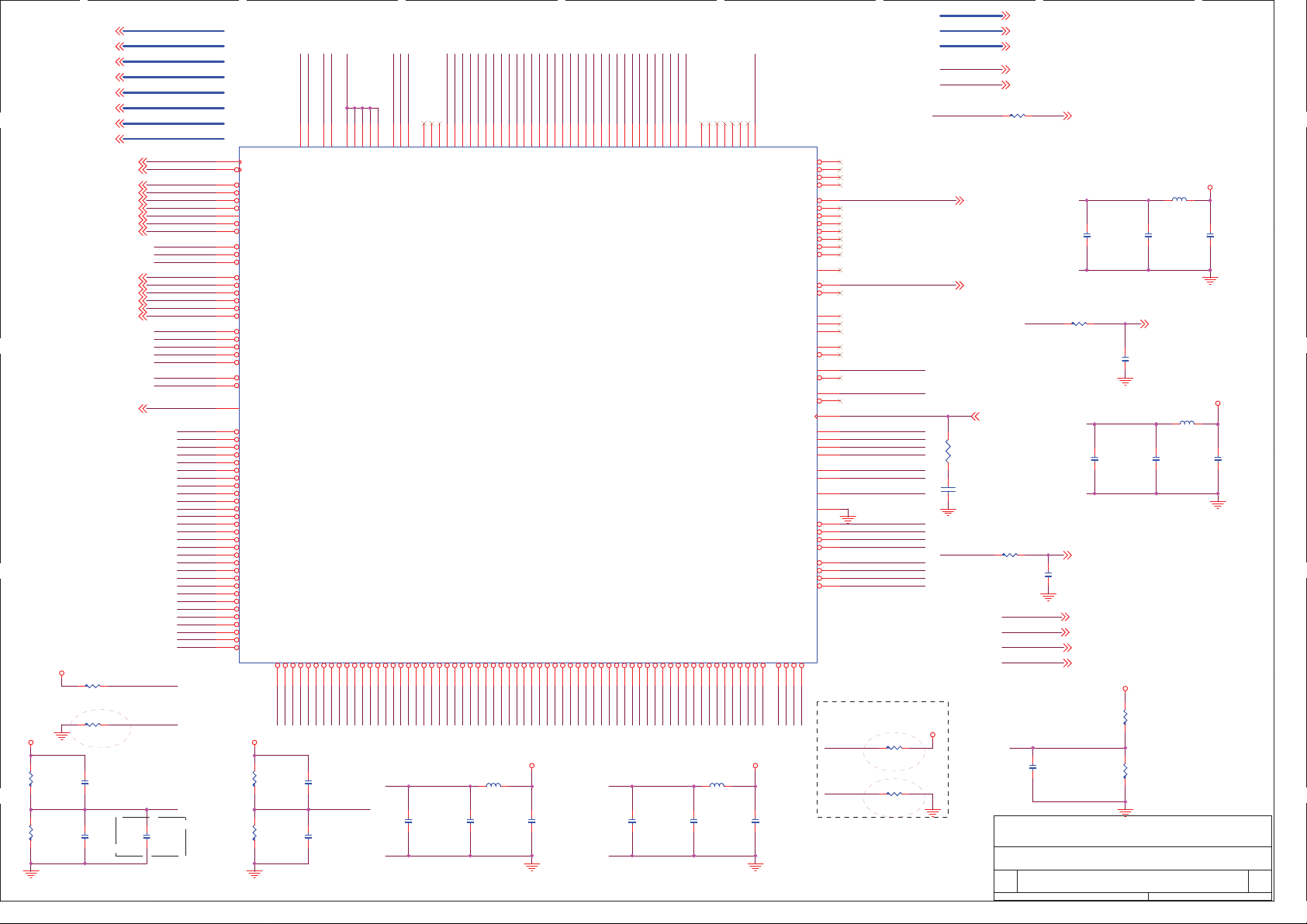

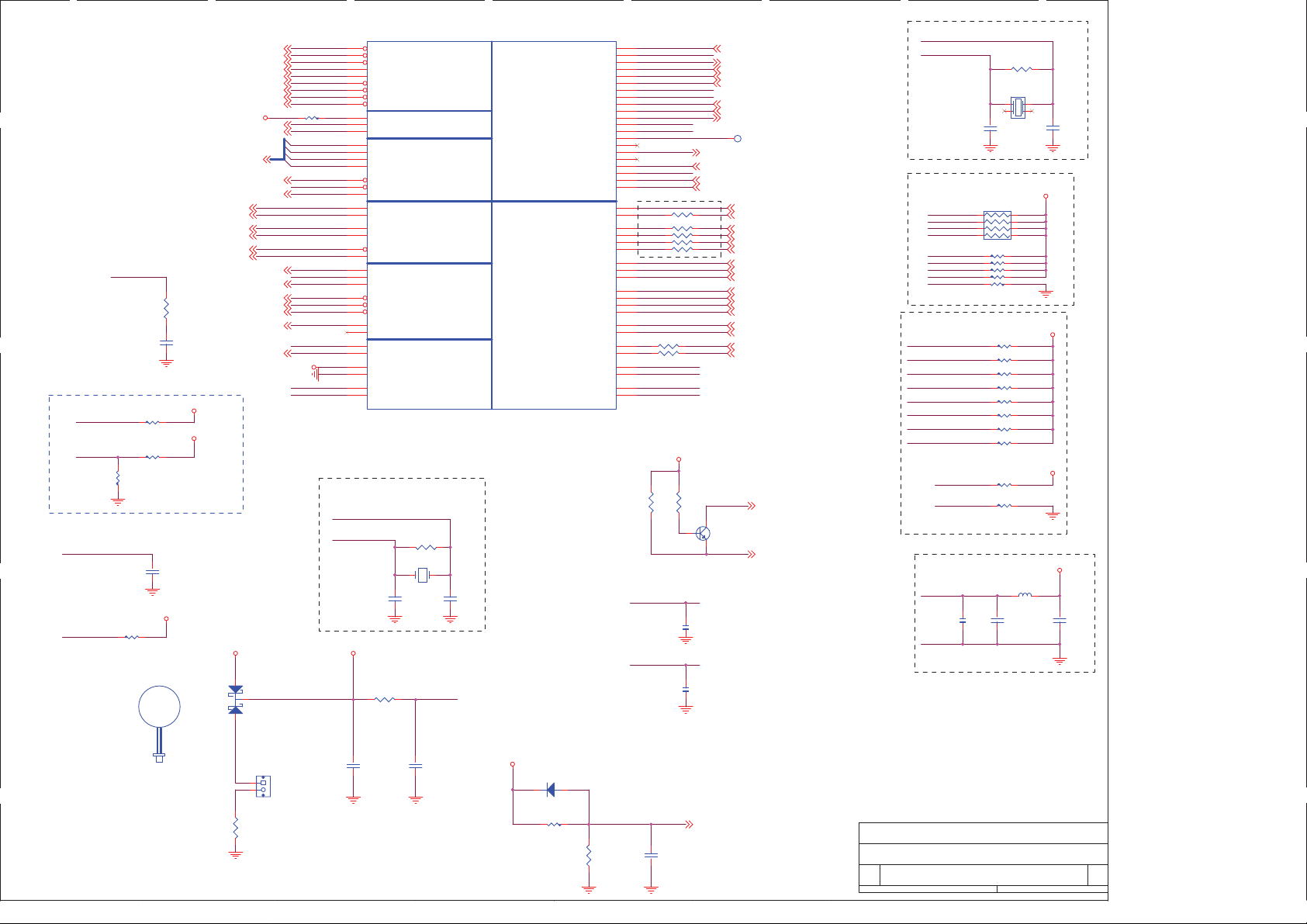

MS-1006 Schematics

Revision : R11A

D D

Page01

IMVP4

VCORE

ADDRADDR

C C

LVDS CONNECTOR

RGB CONNECTOR

LVDS INTER FACE

RGB

HDD

CD-ROM

IDE BUS Page25

Banias

Processor

478 uFCPGA

CTRL

400 MHz

PSB

CTRL

SIS661MX

MuTIOL

DATA

DATA

PCI BUS

MEMORY BUS

33 MHz

R5C593

IEEE1394+

CARD BUS+

CLOCK

GENERATOR

DDR CLOCK

BUFFER

CLOCK

DDR SO-DIMM 0

DDR SO-DIMM 1

3 IN 1 CONNECTOR

IEEE1394 CONNECTOR

CARD READER

B B

3 USB PORTS

AC97 ACL655

MDC HEADR

USB

AC97

MC97

SIS963L

LPC

MII INTERFACE

MINI PCI

LAN PHY

PCMCIA CONNECTOR

WIRELESS LAN MODULE

RJ45 CONNECTOR

SMC/KBCBIOS

BLOCK DIAGRAM

Page02

POWER MAP

Page03

PROCESSOR-1

Page04

PROCESSOR-2

Page05

SIS 661MX-1

Page06

SIS 661MX-2

Page07

SIS 661MX-3

Page08

SIS 661MX-4

Page09

SIS 963L-1

SIS 963L-2

Page10

Page11

SIS 963L-3

Page12

SIS 963L-4

Page13

MAIN CLOCK GEN

Page14

DDR CLOCK BUFFER

SODIMM0,1

Page15

Page16

DDR TERMINATION

Page17

LVDS TRANSMITTER

Page18

VGA , LVDS, INVERTER CONNECTOR

LAN PHY AND RJ45/RJ11

Page19

Page20

MINI PCI CONNECTOR

Page21

R5C593 PART OF IEEE1394 AND CONNECTOR

Page22

R5C593 PART OF CARD BUS AND CON NE CT OR

Page23

R5C593 PART OF CARD READER AND CON NE CT OR

HDD AND CDROM

Page24

KBC

Page26

MDC

Page27

HARDWARE MONITOR AND FAN

USB CONNECTOR

Page28

Page29

LPC ROM

Page30

ALC655 AC97 CODEC

Page31

DCIN & BATTERY SELECTOR

Page32

BATTERY CHARGER

Page33

SYSTEM POWER +V3S & +V5S

Page34

SYSTEM POWER +2.5 & +1.25

Page35

SYSTEM POWER +V1.8

Page36

CPU +VCCP & S0 POWER SW

Page37

CPU +VCORE

Page38

POWERGOOD

A A

Title

BLOCK DIAGRAM

Size Document Number Rev

Custom

Monday, June 28, 2004

5

4

3

2

Date: Sheet of

138

1

R110

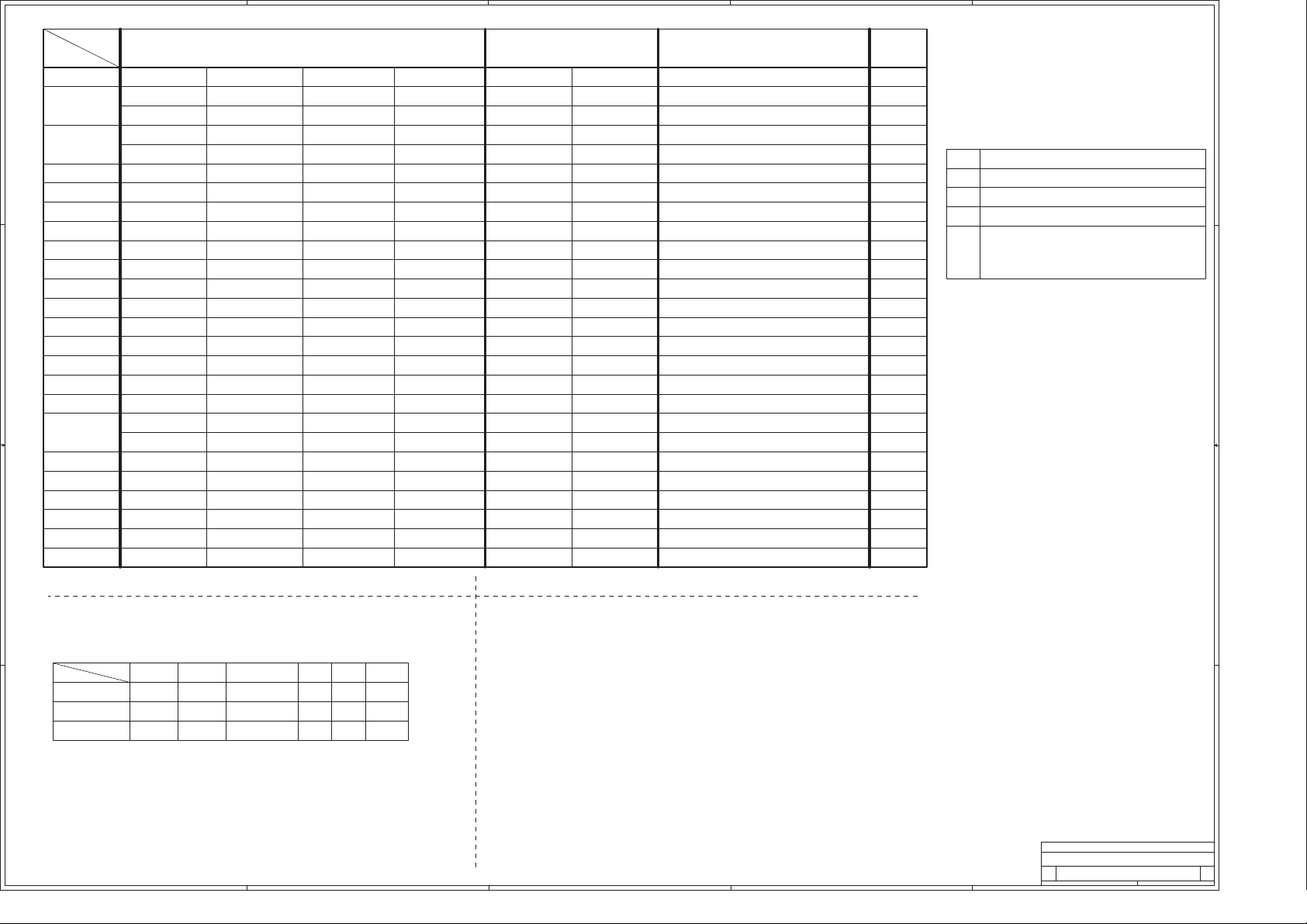

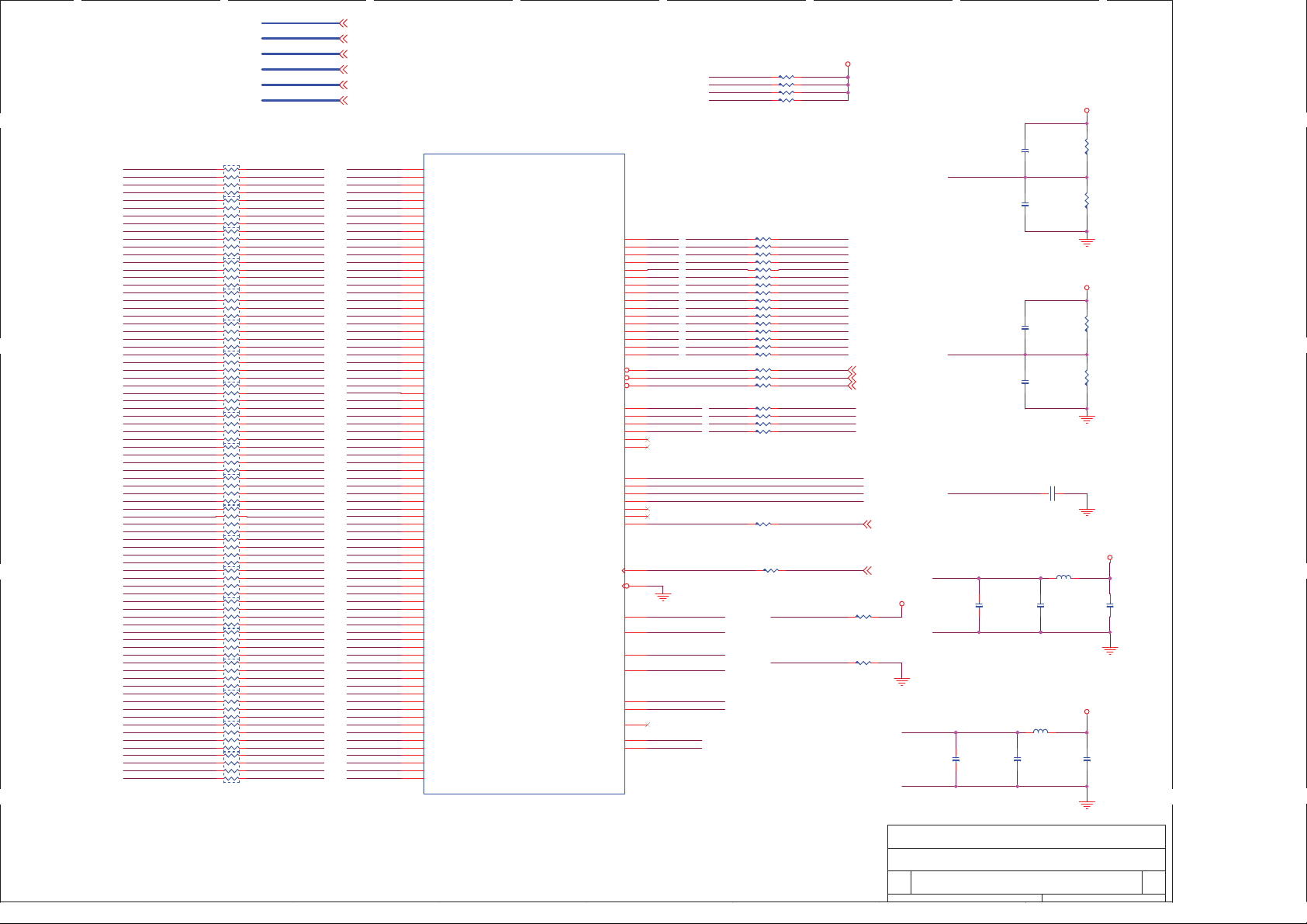

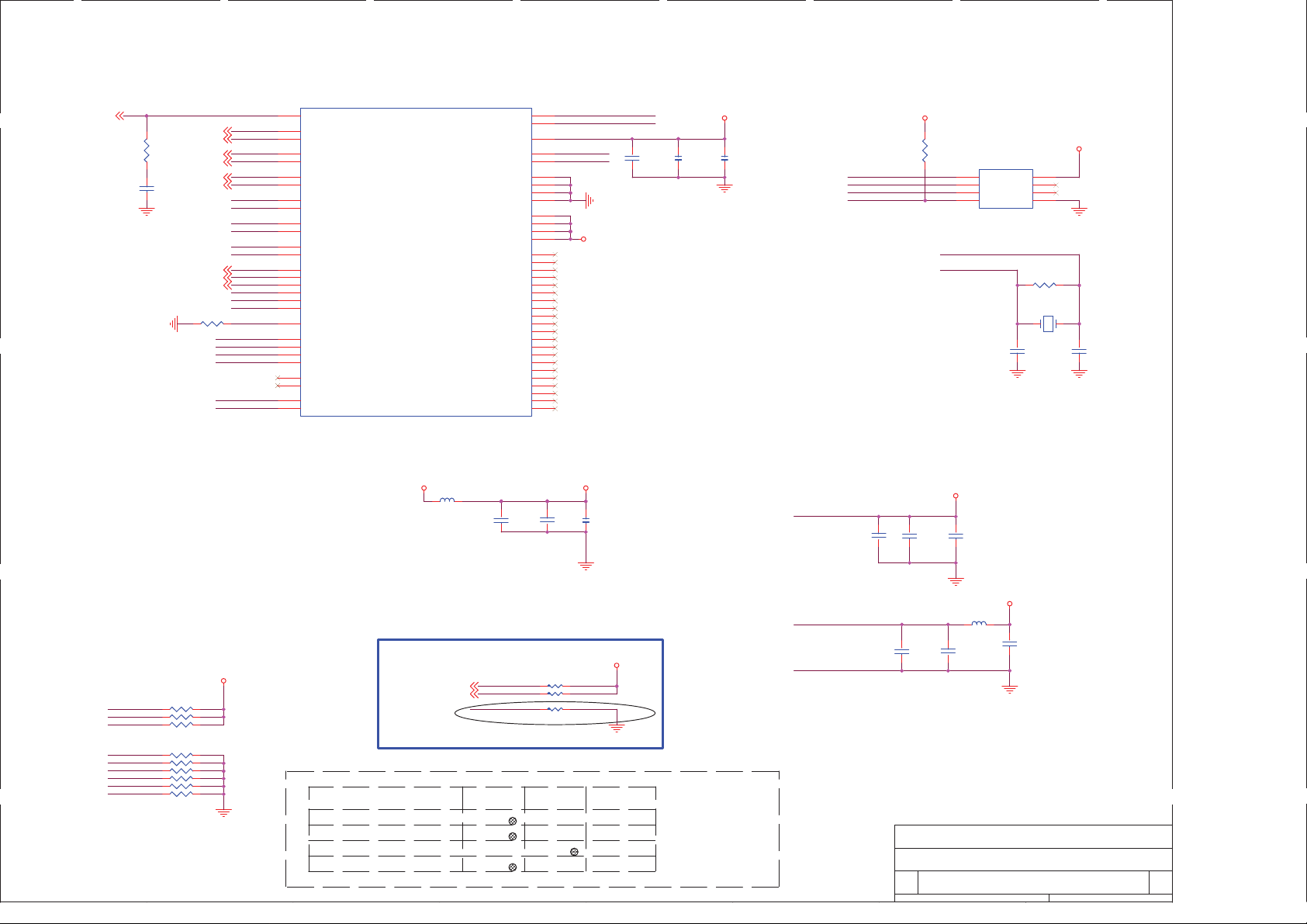

Page 2

5

SYSTEM DEVICE POWER MAP

4

3

2

1

S0

CPU

D D

SIS661MX

SIS963L

CLK GEN.

CLK BUFFER

DIMM

LVDS

LAN PHY

Mini PCI

CARD BUS

IEEE1394

CARD READER

C C

HDD

CDROM

KBC

MDC

HW MONITOR

USB

BIOS

AUDIO

+VCORE +VCCP_CPU +V1.8

+VCCP_NB +V1.8 +V3.3 +V3.3S +V3.3S +V3.3ALWAYS

+V2.5S_MEM

+V1.8 +V3.3 +V3.3S +V1.8S

+VCCP

+V3.3

+V2.5

+V2.5S_MEM +V2.5S_MEM

+V3.3 +V5

+V3.3S +V3.3S +V3.3S +V3.3S +V3.3ALWAYS

+V5 +V3.3 +V3.3S +V3.3S

+V3.3S +V5S +V3.3S +V5S

+V3.3 +V2.5S +V3.3S +V2.5S +V3.3S

+V3.3S +V3.3S

+V5

+V5

+V3.3S +V3.3 +V3.3S +V5 +V3.3S +V3.3ALWAYS

+V3.3S +V3.3S+V3.3 +V5

+VCORE +V2.5S +V12 +V2.5S+V5

+V3.3

+V5 +V3.3

+V3.3

+V5_AUDIO +V3.3

S3 S6S4/S5

+V2.5S_MEM

+V1.8S +V1.8ALWAYS+V3.3S +V3.3ALWAYS

State Power Rails

RTCVDD

S6

+V3.3ALWAYS

S4/S5

S3

S0

+VCORE

+V1.8

+V5_AUDIO

+V1.25_VTT

+V3.3

+V1.8ALWAYS

+V3.3S+V2.5S_MEM

+V2.5S

+V2.5 +V5

+V12

+VCCP

+V1.25_VTT

DDR TERMINAL +V1.25_VTT

VDD_VID +V1.2

B B

POWER Rails

POWER STATE

SIGNAL

STATE

FULL ON

S3 State

S4/S5 State

HIGH

SLP_S3# +V*ALWAYSSLP_S5# +V*S +V* Clocks

HIGHHIGH

LOW

LOWLOW

ON

ON

ON

ONONON ON

OFF

OFF

OFF

OFFOFF

+VCORE

+VCCP

+V1.8

+V1.25_VTT

+V1.2 1.25V DDR Termination voltage(off in S3~S5)

+V1.8S

+V1.8ALWAYS 1.8V always on power rail

+V2.5S_MEM

+V2.5S 2.5V power rail(off in S4~S5)

A A

+V3.3ALWAYS

+V3.3S

+V3.3

+V5S

+V5

+V12

5

4

Core voltage for processor

1.05V rail for processor PSB, Montara-G PSB

1.8V for processor PLL and VID circuitry(off in S3~S5)

1.25V DDR Termination voltage(off in S3~S5)

1.8V power rail(off in S4~S5)

2.5V power rail for DDR(off in S4~S5)

2.5V power rail(off in S3~S5)+V2.5

3.3V always on power rail

3.3V power rail(off in S4~S5)

3.3V switched power rail(off in S3~S5)

5.0V power rail(off in S4~S5)

5.0V switched power rail(off in S3~S5)

12.0V switched power rail(off in S3~S5)

3

Title

Power Map

Size Document Number Rev

MS-1006

Custom

2

Date: Sheet

1

R110

238Monday, June 28, 2004

of

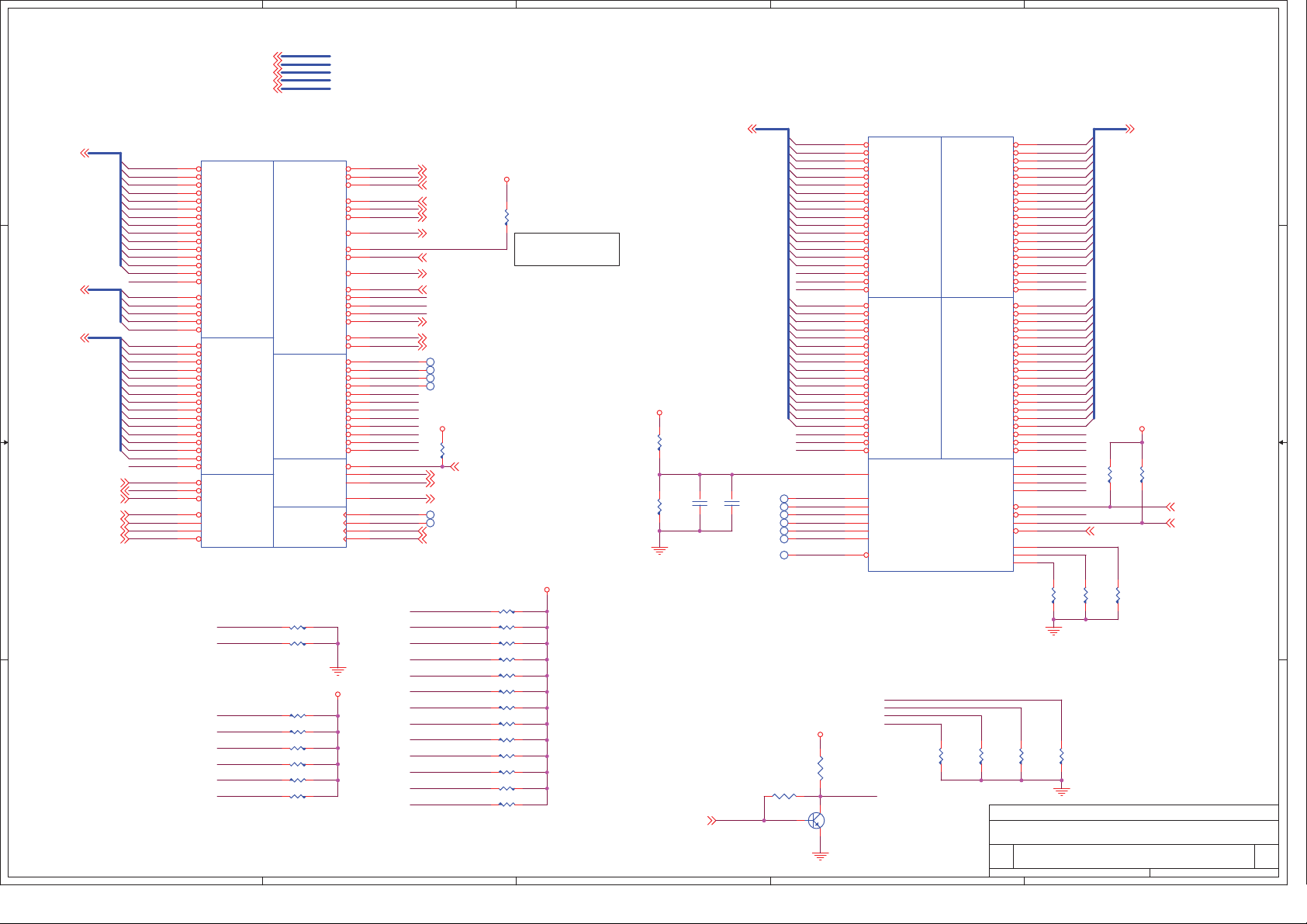

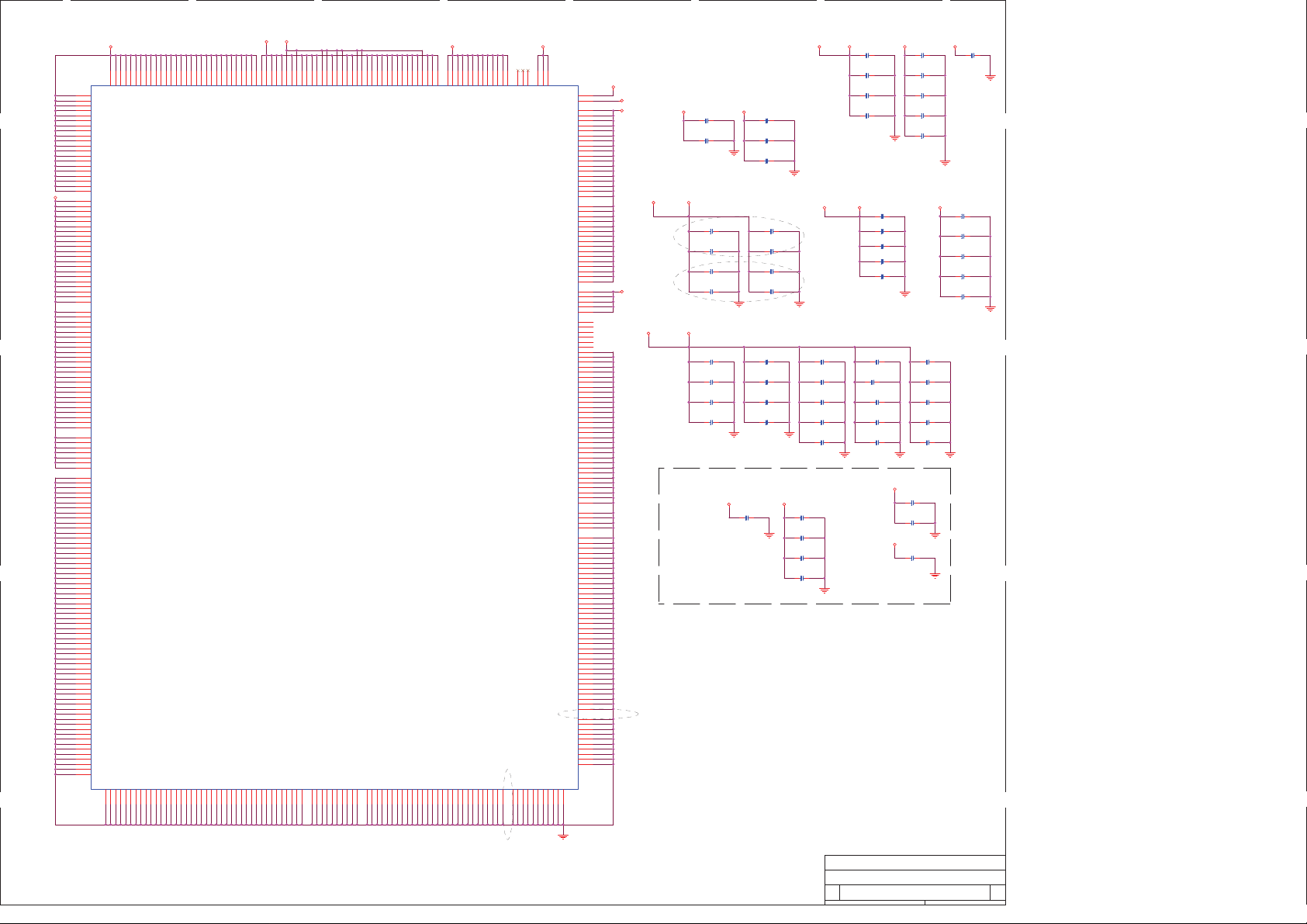

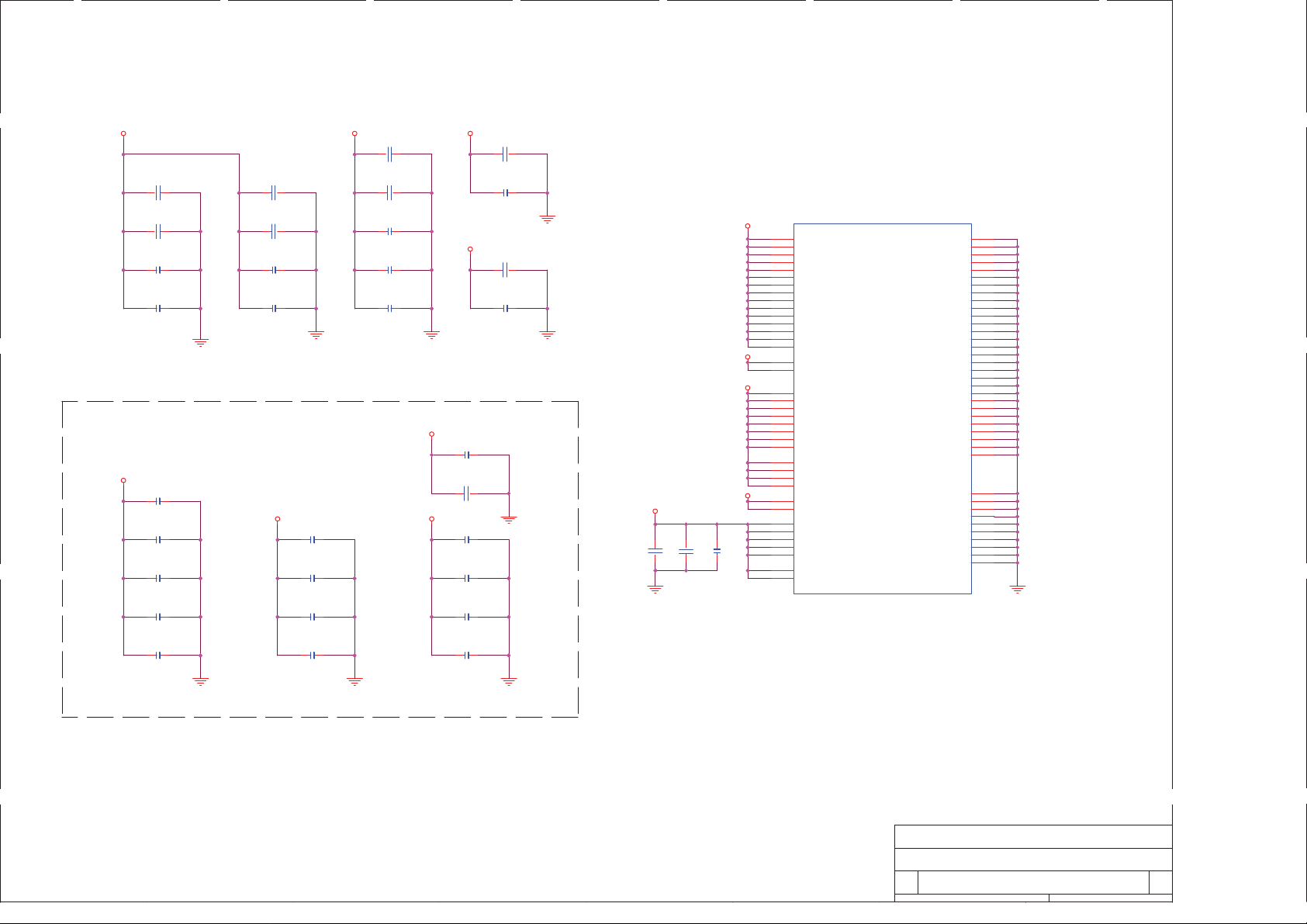

Page 3

5

RS-[0..2]5

DBI-[0..3]5

HDSTBP-[0..3]5

HDSTBN-[0..3]5

HASTB-[0..1]5

4

3

2

1

D D

HA-[3..31]5

HREQ-[0..4]5

C C

HA-[3..31]5

A20M-10

FERR-10

IGNNE-10

STPCLK-10

INTR10

NMI10

B B

A A

SMI-10

HA-10

HA-11

HA-12

HA-13

HA-14

HA-15

HA-16

HASTB-0

HREQ-0

HREQ-1

HREQ-2

HREQ-3

HREQ-4

HA-17

HA-18

HA-19

HA-20

HA-21

HA-22

HA-23

HA-24

HA-25

HA-26

HA-27

HA-28

HA-29

HA-30

HA-31

HASTB-1

5

HA-3

HA-4

HA-5

HA-6

HA-7

HA-8

HA-9

U6A

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

U3

ADSTB#0

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

AE5

ADSTB#1

C2

A20M#

D3

FERR#

A3

IGNNE#

C6

STPCLK#

D1

LINT0/INTR

D4

LINT1/NMI

B4

SMI#

PENTIUM M-PROCESSOR

ITP_TRST#

ITP_TCK

ITP_PRDY#

ITP_PREQ#

ITP_TDO

ITP_TDI

ITP_TMS

ITP_DBRST#

ADDRESS GROUP 0

ADDRESS GROUP 1

R182 680R

R181 27.4R1%

R187 X_56R1%0402

R188 X_56R1%0402

R183 54.9R1%

R184 150R

R185 39.2R1%

R191 150R

BPRI#

DEFER#

DRDY#

DBSY#

IERR#

LOCK#

RESET#

TRDY#

HITM#

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TRST#

PROCHOT#

THERMDA

THERMDC

THERM ITP SIGNALS CONTROL

THERMTRIP#

ITP_CLK1

ITP_CLK0

BCLK1

HCLK

BCLK0

+VCCP_CPU

ADS#

BNR#

BR0#

INIT#

RS0#

RS1#

RS2#

HIT#

TCK

TDO

TMS

DBR#

TDI

N2

L1

J3

L4

H2

M2

N4

A4

B5

J2

B11

H1

K1

L2

M3

K3

K4

C8

B8

A9

C9

A10

B10

A13

C12

A12

C11

B13

A7

B17

B18

A18

C17

A15

A16

B14

B15

RS-0

RS-1

RS-2

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_PRDY#

ITP_PREQ#

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_DBRST#

H_THERMDA

H_THERMDC

THERMTRIP-

4

ADS- 5

BNR- 5

BPRI- 5

DEFER- 5

DRDY- 5

DBSY- 5

BREQ0- 5

INIT- 10,29

HLOCK- 5

CPURST- 5

HTRDY- 5

HIT- 5

HITM- 5

1

TP7

.

1

TP6

.

1

TP8

.

1

TP5

.

+VCCP_CPU +VCCP_CPU

R173

56

DXP 27

DXN 27

THERMTRIP- 10

1

TP3

.

1

TP2

.

CPUCLK-0 13

CPUCLK0 13

BREQ0FERRA20MSTPCLKCPUSLPSMIINITIGNNEINTR

NMI

NBDPWR#

CPURSTTHERMTRIP-

+VCCP_CPU

PROCHOT- 10

R198 51.1R1%

R186 51.1R1%

R199

56

Place testpoint

on H_IERR# with a

GND 0.1" away.

+VCCP_CPU

R20762R

R20556R1%0402

R19456R1%0402

R19356R1%0402

R20256R1%0402

R19756R1%0402

R20056R1%0402

R21256R1%0402

R21156R1%0402

R17156R1%0402

R17562R

+VCCP_CPU

3

HD-[0..63]5

R162

1KR1%

0.5" max length

C184

R165

2KR1%

1u

NOT USE. VRM ENTER TO

LIGHT LOAD STAGE BY

ITSELF.

NBDPWR#

DPWR#5

HD-0

HD-1

HD-2

HD-3

HD-4

HD-5

HD-6 HD-38

HD-7 HD-39

HD-8

HD-9

HD-10

HD-11

HD-12

HD-13

HD-14

HD-15 HD-47

HDSTBN-0

HDSTBP-0

HD-16

HD-17

HD-18

HD-19

HD-20

HD-21

HD-22

HD-23

HD-24

HD-25

HD-26

HD-27

HD-28

HD-29

HD-30

HD-31

HDSTBN-1 HDSTBN-3

HDSTBP-1

DBI-1 DBI-3

C185

2200P

TP_CPU_REV1

1

TP4

.

TP_CPU_REV2

1

TP10

.

TP_CPU_REV3

1

TP9

.

TP_CPU_REV4

1

TP11

.

TP_CPU_REV5

1

TP1

.

TP_CPU_REV6

1

TP13

.

TP_PM_PSI#

1

TP12

.

Layout note:

COMP0 and COMP2 need to be Zo=27.4ohm

traces. Best

estimate is 18mil wide trace for outer

layers and 14mil if on internal layer. See

RDDP of Banias.Traces should be shorter than

0.5". Refer to latest CS layout COMP1, COMP3

should be routed as Zo=55ohm traces shorter

than 0.5"

+VCCP_CPU

R172 0R

U6B

A19

D0#

A25

D1#

A22

D2#

B21

D3#

A24

D4#

B26

D5#

A21

D6#

B20

D7#

C20

D8#

B24

D9#

D24

D10#

E24

D11#

C26

D12#

B23

D13#

E23

D14#

C25

D15#

C23

DSTBN0#

C22

DSTBP0#

D25

DINV0#

H23

D16#

G25

D17#

L23

D18#

M26

D19#

H24

D20#

F25

D21#

G24

D22#

J23

D23#

M23

D24#

J25

D25#

L26

D26#

N24

D27#

M25

D28#

H26

D29#

N25

D30#

K25

D31#

K24

DSTBN1#

L24

DSTBP1#

J26

DINV1#

AD26

GTLREF0

C14

RSVD1

C3

RSVD2

AF7

RSVD3

G1

RSVD4

E26

RSVD5

AC1

RSVD6

E1

PSI#

PENTIUM M-PROCESSOR

COMP0

COMP1

COMP2

COMP3

R176

1K

HDPWR#

Q12

X_N-MMBT3904_SOT23

2

DATA GROUP 2

DATA GROUP 0DATA GROUP 1

DSTBN2#

DSTBP2#

DATA GROUP 3

DSTBN3#

DSTBP3#

MISC

PWRGOOD

R222

54.9R1%

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV3#

COMP0

COMP1

COMP2

COMP3

DPSLP#

DPWR#

SLP#

TEST1

TEST2

TEST3

R210

27.4R1%

Title

Size Document Number Rev

Custom

Date: Sheet

HD-33

AA24

HD-34

T25

HD-35

U23

HD-36

V23

HD-37

R24

R26

R23

HD-40

AA23

HD-41

U26

HD-42

V24

HD-43

U25

HD-44

V26

HD-45

Y23

HD-46

AA26

Y25

HDSTBN-2

W25

HDSTBP-2

W24

DBI-2DBI-0

T24

HD-48

AB25

HD-49

AC23

HD-50

AB24

HD-51

AC20

HD-52

AC22

HD-53

AC25

HD-54

AD23

HD-55

AE22

HD-56

AF23

HD-57

AD24

HD-58

AF20

HD-59

AE21

HD-60

AD21

HD-61

AF25

HD-62

AF22

HD-63

AF26

AE24

HDSTBP-3

AE25

AD20

COMP0

P25

COMP1

P26

COMP2

AB2

COMP3

AB1

B7

HDPWR#

C19

E4

A6

C5

F23

C16

R167

R179

X_1K

X_1K

TEST2 & TEST1 are to be stuffed

for A0 silicon and no_stuffed

for A1 and follow-on silicon

NO_STUFF_1K

R164

R163

54.9R1%

27.4R1%

Processor-1

MS-1006

HD-32

Y26

HD-[0..63] 5

R192

51.1R1%

CPUSLP- 10

R196

X_1K

R206

330

H_DPSLP# 10

CPUPWRGD 5

1

R110

338Monday, June 28, 2004

of

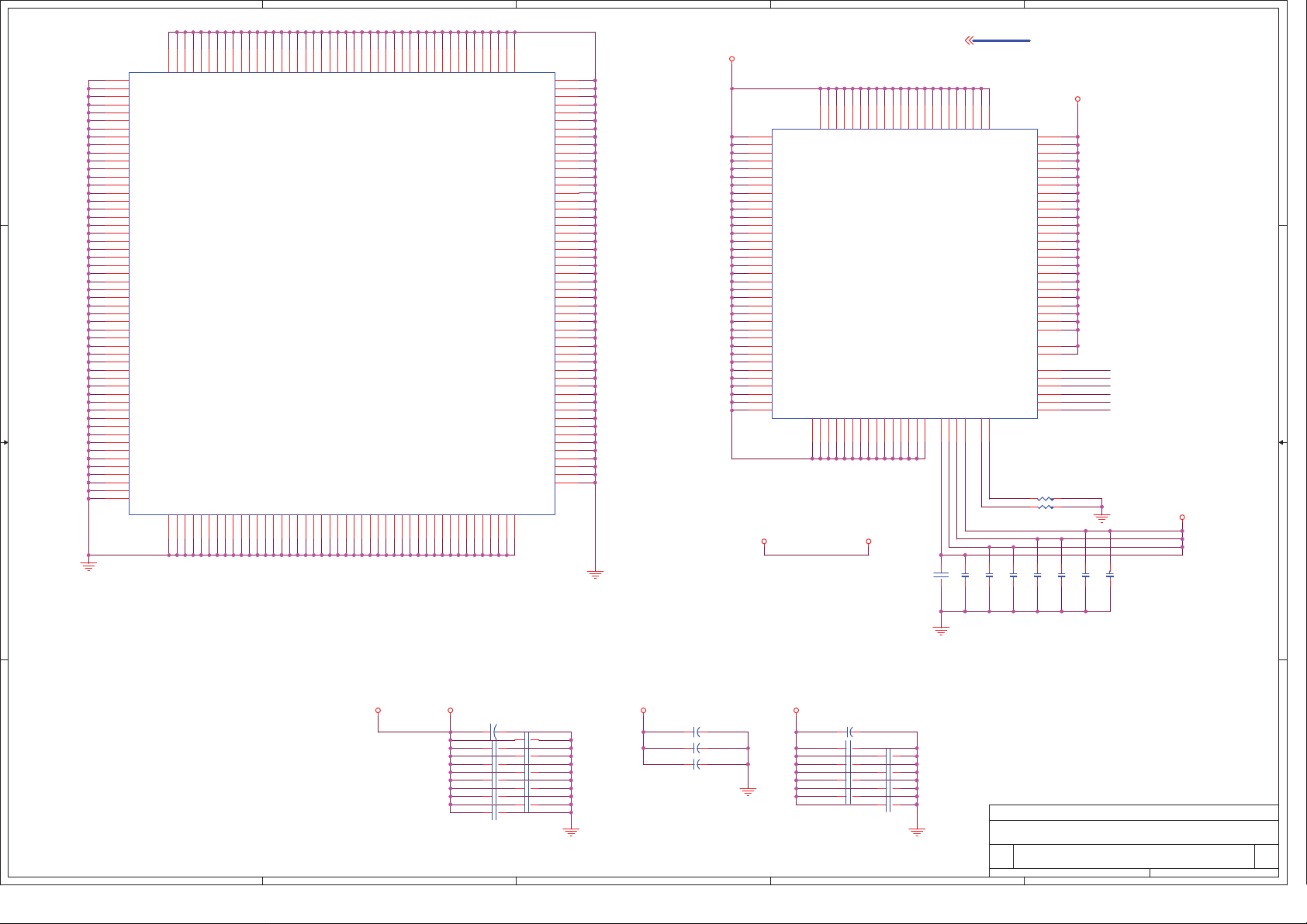

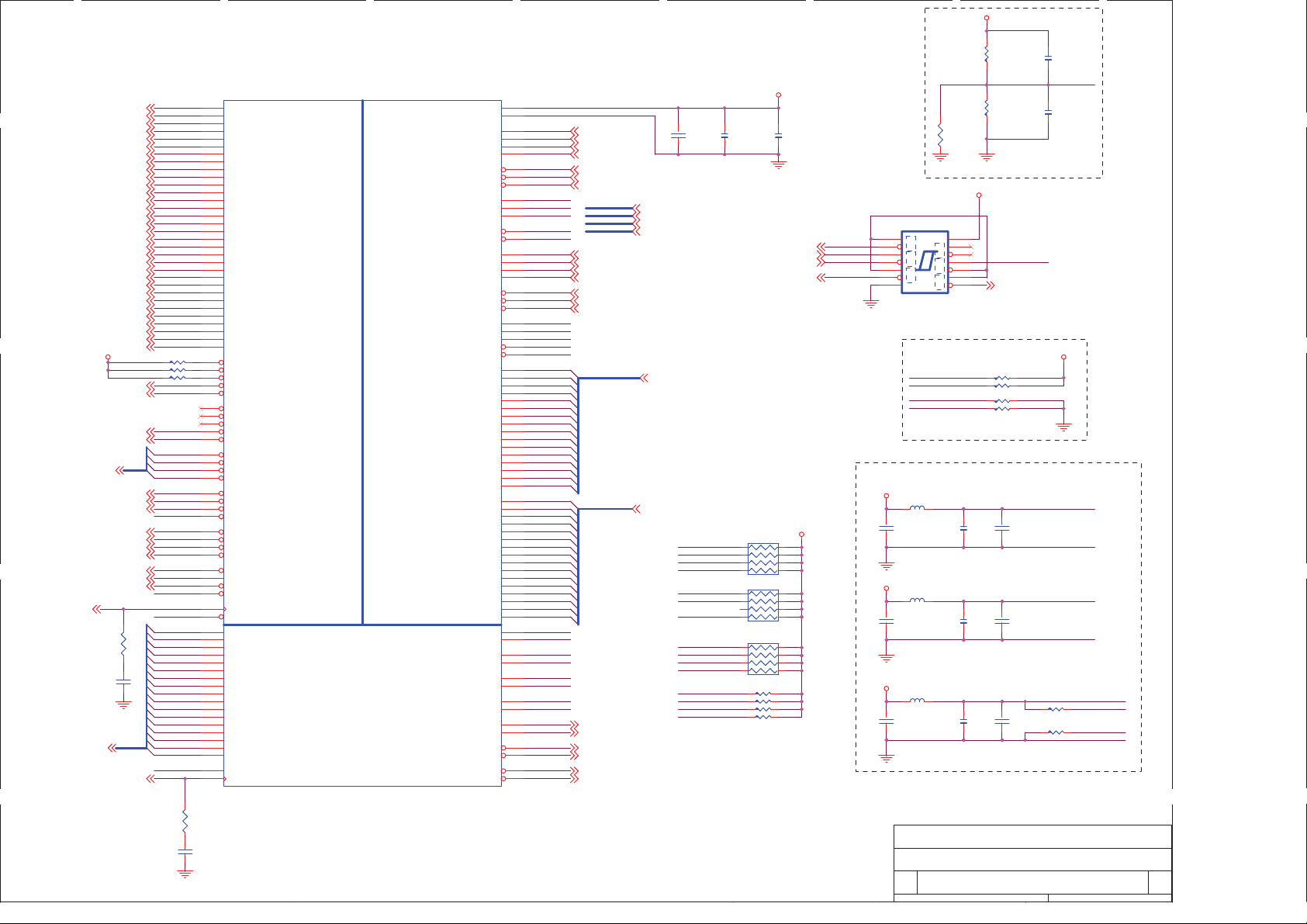

Page 4

5

4

3

2

1

AB22

VCC15

VCC16

VCC63

VCC64

AB20

VCC14

VCC65

AB18

VCC13

VCC66

AB14

AB16

VCC12

VCC67

CPU_VID[0..5]37

AB12

VCC10

VCC11

VCC68

VCC69

AB10

VCC9

VCC70

AA9

VCC8

VCC71

AA7

AD4

VSS44

AD7

VSS45

AD9

AD11

AD13

D D

C C

B B

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

B12

B16

B19

B22

B25

C10

C13

C15

C18

C21

C24

D11

B3

B6

B9

C1

C4

C7

D2

D5

D7

D9

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS43

VSS191

Y24

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

PENTIUM M-PROCESSOR

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

W22

W23

W26

Y2Y5Y21

VSS35

VSS36

VSS183

VSS184

V25W3W6

VSS33

VSS34

VSS181

VSS182

VSS31

VSS32

VSS179

VSS180

VSS29

VSS30

VSS177

VSS178

U22

U24V1V4V5V21

VSS27

VSS28

VSS175

VSS176

VSS25

VSS26

VSS173

VSS174

T26U2U6

VSS23

VSS24

VSS171

VSS172

T21

T23

VSS21

VSS22

VSS169

VSS170

R25T3T5

VSS19

VSS20

VSS167

VSS168

VSS17

VSS18

VSS165

VSS166

VSS15

VSS16

VSS163

VSS164

P21

P24R1R4R6R22

VSS13

VSS14

VSS161

VSS162

VSS11

VSS12

VSS159

VSS160

N23

N26P2P5

VSS9

VSS10

VSS157

VSS158

N22

VSS7

VSS8

VSS155

VSS156

VSS6

VSS154

M24N3N6

VSS4

VSS5

VSS152

VSS153

VSS2

VSS3

VSS150

VSS151

L25M1M4M5M21

VSS1

VSS149

L22

VSS97

VSS98

VSS0

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

A2A5A8

A11

A14

A17

A20

A23

A26

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

U6C

+VCORE

AC19

AC9

AD10

AD12

AD14

AD16

AD18

AD8

AE11

AE13

AE15

AE17

AE19

AE9

AF10

AF12

AF14

AF16

AF18

AF8

D18

D20

D22

D6

D8

E17

E19

E21

E5

E7

E9

F18

F20

F22

F6

PENTIUM M-PROCESSOR

+V1.8 +VCCA

NO_STUFF 3 resistors

of VCCA pins for

Banias B0 support

and no stuff 6caps

of those 3 pins.

AB6

AB8

AC11

AC13

AC15

AC17

U6D

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC17

VCC18

VCC19

VCC20

VCC21

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

F8

G21G5H22H6J21J5K22U5V22V6W21W5Y22Y6F26B1N1

AA21

AA5

VCC5

VCC6

VCC7

VCCA0

VCCA1

C267

10UF1206

CPU_VID[0..5]

+VCCP_CPU

AA11

AA13

AA15

AA17

AA19

VCC3

VCC4

VCCA2

VCCA3

AC26

C279

0.01uF0402

VCC0

VCC1

VCC2

VCCSENSE

VSSSENSE

AE7

AF6

C283

10UF1206

D10

VCCP0

D12

VCCP1

D14

VCCP2

D16

VCCP3

E11

VCCP4

E13

VCCP5

E15

VCCP6

F10

VCCP7

F12

VCCP8

F14

VCCP9

F16

VCCP10

K6

VCCP11

L21

VCCP12

L5

VCCP13

M22

VCCP14

M6

VCCP15

N21

VCCP16

N5

VCCP17

P22

VCCP18

P6

VCCP19

R21

VCCP20

R5

VCCP21

T22

VCCP22

T6

VCCP23

U21

VCCP24

P23

VCCQ0

W4

VCCQ1

LAYOUT NOTE: Provide a test point (with no

stub) to connect differential probe between

VCCSENSE and VSSSENSE at the location where

the two 54.9ohm resistors

terminate the 55ohm tranmisssion lines.

C278

0.01uF0402

CPU_VID0

E2

VID0

CPU_VID1

F2

VID1

CPU_VID2

F3

VID2

CPU_VID3

G3

VID3

CPU_VID4

G4

VID4

CPU_VID5

H4

VID5

R195 X_54.9R1%

R201 X_54.9R1%

C276

C270

0.01uF0402

10UF1206

C282

10UF1206

C265

0.01uF0402

+VCCA

VCore HF and Bulk DecouplingVCCP Decoupling

+VCORE +VCORE+VCCP +VCCP_CPU

C10150u_2.5V

C400.1UF_0402

C2260.1UF_0402

C2360.1UF_0402

C2690.1UF_0402

A A

C2600.1UF_0402

C2000.1UF_0402

C370.1UF_0402

C2570.1UF_0402

C2310.1UF_0402

EC2 220U2SP

1 2

+

EC5 220U2SP

1 2

+

EC4 220U2SP

1 2

+

PLACE NEAR CPU

5

4

3

EC1 220U2SP

1 2

+

C21710UF1206

C21910UF1206

C24310UF1206C1870.1UF_0402

C28010UF1206

C21610UF1206

C21810UF1206

C24210UF1206

C28110UF1206

Title

Processor-2

Size Document Number Rev

Custom

2

Date: Sheet

MS-1006

438Monday, June 28, 2004

1

of

R110

Page 5

8

A

HDSTBP-[0..3]3

HDSTBN-[0..3]3

DBI-[0..3]3

HD-[0..63]3

HASTB-[0..1]3

HA-[3..31]3

D D

HREQ-[0..4]3

RS-[0..2]3

CPUPWRGD3

C C

B B

+VCCP_NB

R9

20R1%0402

R7

R180

100R1%

R177

169R1%

112R1%0402

C204

0.01uF0402

C229

0.01uF0402

place this capacitor

under 660FX solder side

8

+VCCP_NB +VCCP_NB

HDSTBP-[0..3]

HDSTBN-[0..3]

DBI-[0..3]

HD-[0..63]

HASTB-[0..1]

HA-[3..31]

HREQ-[0..4]

RS-[0..2]

CPUCLK113

CPUCLK-113

HLOCK-3

DEFER-3

HTRDY-3

CPURST-3

BPRI-3

BREQ0-3

ADS-3

HITM-3

HIT-3

DRDY-3

DBSY-3

BNR-3

DPWR#3

HNCOMP

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

HPCOMP

Rds-on(p) = 56 ohm

HPCVERF = 2/3 VCCP

CPUCLK1

CPUCLK-1

HLOCKDEFERHTRDYCPURSTCPUPWRGD

BPRIBREQ0-

RS-2

RS-1

RS-0

ADSHITM-

HITDRDYDBSYBNR-

HREQ-4

HREQ-3

HREQ-2

HREQ-1

HREQ-0

HASTB-1

HASTB-0

DPWR#

HVREF

C222

0.1UF_0402

HA-31

HA-30

HA-29

HA-28

HA-27

HA-26

HA-25

HA-24

HA-23

HA-22

HA-21

HA-20

HA-19

HA-18

HA-17

HA-16

HA-15

HA-14

HA-13

HA-12

HA-11

HA-10

HA-9

HA-8

HA-7

HA-6

HA-5

HA-4

HA-3

AJ31

AJ33

V32

B23

R34

U31

R33

U35

V35

R35

U34

W34

U33

V33

W35

Y33

W31

W33

Y35

AG31

AA33

R36

AH33

AG33

AJ35

AF32

AJ34

AH32

AG35

AE31

AH35

AF35

AE35

AE33

AE34

AF33

AG34

AC33

AD32

AD33

AC35

AD35

AC31

AC34

AB35

AB32

AB33

AA35

AA31

Y32

AA34

T33

T35

F22

T32

7

U5A

CPUCLK

CPUCLK#

HLOCK#

DEFER#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS#2

RS#1

RS#0

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ4#

HREQ3#

HREQ2#

HREQ1#

HREQ0#

HASTB1#

HASTB0#

DPWR#

HA31#

HA30#

HA29#

HA28#

HA27#

HA26#

HA25#

HA24#

HA23#

HA22#

HA21#

HA20#

HA19#

HA18#

HA17#

HA16#

HA15#

HA14#

HA13#

HA12#

HA11#

HA10#

HA9#

HA8#

HA7#

HA6#

HA5#

HA4#

HA3#

M661MX

R27

150R1%

R23

75R1%

7

C1XAVDD

C4XAVSS

C4XAVDD

C1XAVSS

AL36

AK34

C1XAVSS

C1XAVDD

AJ36

AK35

C4XAVSS

C4XAVDD

HVREF

AA26

HVREF0

Host Bus Interface

HD63#

HD62#

HD61#

HD60#

HD59#

HD58#

HD57#

HD56#

HD55#

HD54#

C24

E23

B24

D23

D25

F24

C26

B25

B26

D27

HD-57

HD-59

HD-58

C24

0.01uF0402

C6

0.01uF0402

HD-56

HD-54

HD-55

HNCVREF

HD-62

HD-61

HD-63

HD-60

W26

U26

HVREF1

HVREF2

HD53#

HD52#

D26

E27

HD-52

HD-53

6

HNCOMP

HNCVREF

HPCOMP

VBD3

VBD6

VBD7

VBD2

VAD6

VBD0

VBD4

VBD5

VBD1

D22

C22

B22B6F7B5Y5W4V2W6V4U2V5U4R2T4R3T5P2R4N2R6L3L4K2L6J2J3K4J4J6H4G3H5F2G4E2G6E3F4D2F5E4B2E6

R26

L20

ST0

ST1

ST2

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

HVREF3

HVREF4

HCOMP_P

HCOMP_N

HCOMPVREF_N

AAD7

VAD5

AAD8

VAD4

AAD9

VAD7

AAD10

AAD11

VAD8

AAD12

VAD9

AAD13

5

VAD11

VAD10

AAD14

VADE

AAD15

AAD16

AVSYNC

VBD11

AHSYNC

AAD17

AAD18

VBD10

AAD19

AAD20

VBD8

AAD21

VBD9

AAD22

VAD1

AAD23

VAD0

AAD24

VAD2

AAD25

VAD3

AAD26

VBDE

AAD27

VBCTL0

AAD28

LVDS/AGP

M661MX-1

HD51#

HD50#

HD49#

HD48#

HD47#

HD46#

HD45#

HD44#

HD43#

HD42#

HD41#

HD40#

HD39#

HD38#

HD37#

HD36#

HD35#

HD34#

HD33#

HD32#

HD31#

HD30#

HD29#

HD28#

HD27#

HD26#

HD25#

HD24#

HD23#

HD22#

HD21#

HD20#

HD19#

HD18#

HD17#

HD16#

HD15#

HD14#

HD13#

B27

D28

C28

B28

E29

F28

B29

C30

B30

B31

C32

D29

C33

B33

B35

D32

B34

E31

D31

D33

D35

G31

C35

F33

E33

D34

E35

F32

J34

G34

H35

F35

J33

J31

G35

H33

J35

K32

N33

HD-48

HD-51

HD-50

HD-49

C1XAVDD

C1XAVSS

HD-47

6

HD-46

HD-45

HD-44

C252

0.1UF_0402

HD-27

HD-32

HD-31

+V3.3

HD-29

HD-30

C61

10UF1206

HD-26

HD-25

HD-28

HD-24

HD-37

HD-38

HD-36

HD-39

HD-35

HD-34

L16

60S/0603

C256

0.01uF0402

HD-33

HD-40

HD-41

HD-42

HD-43

5

HD-17

HD-22

HD-19

HD-20

HD-21

C4XAVDD

C4XAVSS

HD-18

HD-16

HD-14

HD-13

HD-15

C255

0.1UF_0402

HD-23

VBCTL1

BHSYNC

AAD29

AAD30

HD12#

HD11#

K33

L31

HD-11

HD-12

BVSYNC

AAD31

HD10#

HD9#

L33

K35

HD-9

HD-10

4

SBA7

SBA6

SBA5

HD8#

HD7#

HD6#

L35

M35

M33

P32

HD-8

HD-6

HD-7

L15

60S/0603

C247

0.01uF0402

4

SBA4

HD5#

HD-5

P33

HD-4

SBA3

HD4#

L34

SBA2

HD3#

HD-3

BCLK

SBA1

HD2#

N34

HD-2

+V3.3

B3

SBA0

HD1#

N35

HD-1

AC/BE3#

AC/BE2#

AC/BE1#

AC/BE0#

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

GC_DET#

ADBIH/PIPE#

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

AGPCLK

AGPCOMP_P

AGPCOMP_N

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

HDSTBN3#

HDSTBN2#

HDSTBN1#

HDSTBN0#

HDSTBP3#

HDSTBP2#

HDSTBP1#

HDSTBP0#

HD0#

DBI3#

DBI2#

P35

F26

B32

DBI-3

HD-0

DBI-2

C57

10UF1206

K5

M5

P4

U6

C6

E8

N6

M4

N4

L2

P5

M2

N3

APAR

D7

RBF#

B4

WBF#

C7

C4

D6

ADBIL

C2

D3

T2

U3

G2

H2

D8

W2

Y2

B8

C8

A7

B7

W3

Y4

D24

F30

G33

N31

E25

D30

H32

M32

DBI1#

DBI0#

E34

R31

DBI-0

DBI-1

AGP3.0 = 50 ohm

AGPRCOMN

AGPRCOMP

3

BCAD

BHCLK

AGCLK

BGCLK

AGPCLK0

AGPRCOMP

AGPRCOMN

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AVREFGC

HDSTBN-3

HDSTBN-2

HDSTBN-1

HDSTBN-0

HDSTBP-3

HDSTBP-2

HDSTBP-1

HDSTBP-0

3

VAD[0..11]

VBD[0..11]

VBCTL[0..1]

AHSYNC

AVSYNC

VAD[0..11] 17

VBD[0..11] 17

VBCTL[0..1] 17

VAHSYNC 17

VAVSYNC 17

C30~C34 is noise issue(Optional Use)

BCLK

R36

10R0402

VBCAD 17

VBHCLK 17

BGCLK

AGPCLK0 13

R169

100

C195

22P

AGCLK

R46

10R0402

BHSYNC

BVSYNC

VADE

VBDE

+VDDQ

R51

50R1%0402

R50

43.75R1%0402

AVREFGC

MSI CORPORATION

Title

Size Document Number Rev

A3

Date: Sheet

2

VBCLK 17

A4XAVDD

C20

0.1UF_0402

A4XAVSS

R43

10R0402

VAGCLK 17

C42

10p

VBHSYNC 17

VBVSYNC 17

VADE 17

VBDE 17

C43

0.1UF_0402

M661MX-1 (HOST/AGP)

2

A1XAVDD

C18

0.1UF_0402

A1XAVSS

+VDDQ

L4

C14

0.01uF0402

VBGCLK 17

C36

10p

L5

C13

0.01uF0402

R49

300R1%0402

R48

200R1%0402

TEL:886-2-32345599

1

+V3.3

60S/0603

60S/0603

538Monday, June 28, 2004

1

C1

10UF1206

+V3.3

of

C28

10UF1206

R110

A

Page 6

8

A

M661MX-2

DRAM Controller

D D

C C

B B

Rs place close to DIMM1

/RMD5

/RMD1

/RMD4

8P4R-10R0402

/RMD0

/RMD6

/RMD2

/RDQM0

8P4R-10R0402

/RDQS0

/RMD12

/RMD8

/RMD7

8P4R-10R0402

/RMD3

/RDQM1

/RDQS1

/RMD13

8P4R-10R0402

/RMD9

/RMD15

/RMD11

/RMD14

8P4R-10R0402

/RMD10

/RMD21

/RMD17

/RMD20

8P4R-10R0402

/RMD16

/RMD22

/RMD18

/RDQM2

8P4R-10R0402

/RDQS2

/RMD28

/RMD24

/RMD23

8P4R-10R0402

/RMD19

/RDQM3

/RDQS3

/RMD25

8P4R-10R0402

/RMD29

/RMD27

/RMD31

/RMD30

8P4R-10R0402

/RMD26

/RMD37

/RMD33

/RMD36

8P4R-10R0402

/RMD32

/RMD38

/RMD34

/RDQM4

8P4R-10R0402

/RDQS4

/RMD44

/RMD40

/RMD35

8P4R-10R0402

/RMD39

/RDQM5

/RDQS5

/RMD45

8P4R-10R0402

/RMD41

/RMD47

/RMD43

/RMD46

8P4R-10R0402

/RMD42

/RMD49

/RMD52

/RMD48

8P4R-10R0402

/RMD53

/RMD54

/RMD50

/RDQM6

8P4R-10R0402

/RDQS6

/RMD60

/RMD56

/RMD55

8P4R-10R0402

/RMD51

/RDQM7

/RDQS7

/RMD61

8P4R-10R0402

/RMD57

/RMD63

/RMD59

/RMD58

8P4R-10R0402

/RMD62

RN1

RN2

RN12

RN17

RN5

RN4

RN3

RN7

RN10

RN11

RN20

RN16

RN9

RN8

RN6

RN13

RN15

RN14

RN18

RN19

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

/RMD[0..63]

/RDQM[0..7]

/RDQS[0..7]

/RMA[0..15]

/RCS-[0..3]

/RCKE[0..3]

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

MD5

MD1

MD4

MD0

MD6

MD2

DQM0

DQS0

MD12

MD8

MD7

MD3

DQM1

DQS1

MD13

MD9

MD15

MD11

MD14

MD10

MD21

MD17

MD20

MD16

MD22

MD18

DQM2

DQS2

MD28

MD24

MD23

MD19

DQM3

DQS3

MD25

MD29

MD27

MD31

MD30

MD26

MD37

MD33

MD36

MD32

MD38

MD34

DQM4

DQS4

MD44

MD40

MD35

MD39

DQM5

DQS5

MD45

MD41

MD47

MD43

MD46

MD42

MD49

MD52

MD48

MD53

MD54

MD50

DQM6

DQS6

MD60

MD56

MD55

MD51

DQM7

DQS7

MD61

MD57

MD63

MD59

MD58

MD62

6

/RMD[0..63] 15,16

/RDQM[0..7] 15,16

/RDQS[0..7] 15,16

/RMA[0..15] 15,16

/RCS-[0..3] 15,16

/RCKE[0..3] 15,16

MD0

AN35

MD1

AP36

MD2

AK33

MD3

AM33

MD4

AN34

MD5

AK32

MD6

AR34

MD7

AN33

DQM0

AR35

DQS0

AP34

MD8

AM32

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7

AL31

AR31

AL30

AN32

AR33

AN31

AM31

AR32

AP32

AP30

AR30

AM29

AL27

AN30

AN29

AL28

AN28

AL29

AR29

AP26

AN25

AR24

AL24

AL25

AR26

AM25

AN24

AP24

AR25

AN21

AP20

AN20

AL18

AM21

AR21

AL19

AM19

AL20

AR20

AL15

AL14

AN15

AR15

AN16

AM15

AN14

AL13

AP16

AR16

AM13

AL12

AL11

AR12

AP14

AR14

AN13

AP12

AN12

AR13

AL10

AR11

AM9

AR9

AM11

AN11

AP10

AN9

AN10

AR10

U5B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0/CSB0#

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1/CSB1#

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2/CSB2#

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3/CSB3#

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB4#

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB5#

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB6#

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB7#

M661MX

5

DDRVREFB/DDRVREFA

DDRVREFA/DDRVREFB

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

MA15/TEST1

SRAS#

SCAS#

SWE#

CS0#

CS1#

CS2#

CS3#

CS4#

CS5#

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

FWDSDCLKO

SDRCLKI/DRAMTEST

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

DRAM_SEL

DDRCOMP_P

DDRCOMP_N

AR23

AN23

AN22

AM23

AL23

AL26

AN26

AN27

AR27

AR28

AP22

AN18

AR22

AP28

AM27

AT14

AL17

AR19

AN19

AM17

AL16

AN17

AR17

AP18

AR18

AP4

AT3

AR3

AP3

AR2

AN4

AP2

AL21

AL22

AL35

AL34

AM35

AN36

AF16

AF23

AP1

AR8

AP8

4

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12 MA8

MA13

MA14

MA15

SRASSCASSWE-

CS-0

CS-1

CS-2

CS-3

ADCLKO

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

DDRVREFB

DDRVREFA

DDRCOMP

DDRCOMN

/RCKE0

/RCKE1

/RCKE2

/RCKE3

Rs place close to DIMM1

MA3

MA4

MA2

MA1

MA0

MA10

MA12

MA6

MA11

MA5

MA15

MA7

MA9

MA13

CS-1

CS-0

R91 X_4.7KR0402

R92 X_4.7KR0402

R73 X_4.7KR0402

R90 X_4.7KR0402

R213 0R

R227 0R

R220 0R

R97 0R

R221 0R

R85 0R

R96 0R

R83 0R

R214 0R

R95 0R

R226 0R

R94 0R

R86 0R

R225 0R

R88 0R

R87 0R

R217 0R

R82 0R

R216 0R

R219 0R

R218 0R

R81 0R

R80 0R

For debug mode

R78

0R

R84 22

3

/RCKE0

/RCKE1

/RCKE2

/RCKE3

S3AUXSW-

FWDSDCLKO

40 ohms

DDRCOMN

40 ohms

DDRCOMP

+V2.5S_MEM

/RMA14MA14

/RMA3

/RMA4

/RMA2

/RMA1

/RMA0

/RMA10

/RMA12

/RMA6

/RMA11

/RMA5

/RMA15

/RMA8

/RMA7

/RMA9

/RMA13

/RSRAS/RSCAS/RSWE-

/RCS-1

/RCS-0

/RCS-2CS-2

/RCS-3CS-3

/RSRAS- 15,16

/RSCAS- 15,16

/RSWE- 15,16

S3AUXSW- 25

FWDSDCLKO 14

R74

40.2R1%0402

R75

40.2R1%0402

+V2.5S_MEM

DDRAVDD

DDRAVSS

2

DDRVREFB

DDRVREFA

FWDSDCLKO

DLLAVDD

DLLAVSS

C258

0.1UF_0402

C263

0.1UF_0402

C79

0.01uF0402

C74

0.01uF0402

C285

0.01uF0402

C277

0.01uF0402

C75 10p

L18

C262

0.01uF0402

L22

60S/0603

C261

0.01uF0402

+V2.5S_MEM

+V2.5S_MEM

60S/0603

+V3.3

1

R93

150R1%0402

R79

150R1%0402

R224

150R1%

R215

150R1%0402

+V3.3

C67

10UF1206

C73

10UF1206

A

MSI CORPORATION

Title

M661MX-2 (MEMORY for DDR)

Size Document Number Rev

B

8

7

6

5

4

3

Date: Sheet

2

638Monday, June 28, 2004

1

R110

of

Page 7

8

A

ZAD[0..16]9

ZAD[0..16]

D D

+V1.8

R229

150R1%0402

R230

75R1%

R228

150R1%0402

C C

+V3.3

L24

60S/0603

60S/0603

C69

0.1UF_0402

C64

0.1UF_0402

+V3.3

C66

10UF1206

L20

C198

10UF1206

B B

C286

0.1UF_0402

ZVREF

C288

0.1UF_0402

7

Z1XAVDD

C68

0.01uF0402

Z1XAVSS

Z4XAVDD

C65

0.01uF0402

Z4XAVSS

6

ZCLK0

R190

100

C251

22P

ZCLK013

ZUREQ9

ZDREQ9

ZSTB-09

ZSTB-19

ZCLK0

ZUREQ

ZDREQ

ZSTB0

ZSTB09

ZSTB-0

ZSTB1

ZSTB19

ZSTB-1

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZVREF

ZCMP_N

ZCMP_P

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

DELAY_IMVP_PWRGD10,30,37

U5C

AL6

ZCLK

AL4

ZUREQ

AK5

ZDREQ

AJ2

ZSTB0

AJ3

ZSTB0#

AE3

ZSTB1

AF2

ZSTB1#

AH5

ZAD0

AK2

ZAD1

AJ4

ZAD2

AJ6

ZAD3

AH2

ZAD4

AH4

ZAD5

AG3

ZAD6

AG6

ZAD7

AF4

ZAD8

AG2

ZAD9

AF5

ZAD10

AG4

ZAD11

AD2

ZAD12

AE6

ZAD13

AE2

ZAD14

AE4

ZAD15

AL3

ZAD16

AK4

ZVREF

AD5

ZCOMP_N

AD4

ZCOMP_P

AN1

Z1XAVDD

AM2

Z1XAVSS

AL2

Z4XAVDD

AL1

Z4XAVSS

M661MX

PCI_RST-9,20,21

AUXOK10,27

M661MX-3

HyperZip

AUXOK

PCIRST#

PWROK

AUXOK

AN2

AM4

AN3F9D10C9B9

5

TRAP2

AP1

TRAP1

TRAP0

TRAP1

TRAP0

4

REFCLK0

A15

VOSCI

B12

ROUT

B13

GOUT

A13

BOUT

HSYNC

VGA

TESTMODE2

TESTMODE1

TESTMODE0

DLLEN#

ENTEST

B10

E10

D9

TMODE2

DLLEN-

TMODE0

ENTEST

TMODE1

VSYNC

VGPIO0

VGPIO1

INT#A

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

A11

B11

E13

C11

C10

D12

E12

D11

E15

D15

E14

D13

C12

D14

C13

B15

C15

B14

C14

R15

R5

R25

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD

DACAVSS

DACAVDD

DACAVSS

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

33R0402

33R0402

0R

R168

100

C194

22P

3

REFCLK0 13

ROUT 18

GOUT 18

BOUT 18

HSYNC 18

VSYNC 18

DDC1CLK 18

DDC1DATA 18

INT-A 9,17,21

2

NB Hardware Trap

(for SiS internal test only)

DLLENTRAP0

TRAP1

TMODE0

TMODE1

TMODE2

RSYNC

LSYNC

CSYNC VB

RSYNC

LSYNC

CSYNC

RSYNC

LSYNC

CSYNC

ENTEST

DELAY_IMVP_PWRGD

AUXOK

VGA

panel link

R3

R29

R17

R4

R30

R18

R14

C290

C291

R26

R2

R31

R32

R16

R1

X_4.7KR0402

X_4.7KR0402

X_4.7KR0402

X_4.7KR0402

X_4.7KR0402

X_4.7KR0402

4.7KR0402

X_4.7KR0402

X_4.7KR0402

X_4.7KR0402

4.7KR0402

4.7KR0402

4.7KR0402

0.1UF_0402

0.1UF_0402

1

+V3.3

+V3.3

Enable Disable

1

1

1

+V3.3

0

0

0

+V1.8

L13

C237

10UF1206

60S/0603

C50

0.1UF_0402

R57

C51

0.01uF0402

R55

56R0402

56R0402

ZCMP_N

ZCMP_P

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

C15

0.01uF0402

C23

0.01uF0402

L1

60S/0603

C21

0.1UF_0402

L2

60S/0603

C17

0.1UF_0402

+V3.3

+V3.3

C4

10UF1206

C12

10UF1206

VVBWN

VCOMP

DACAVDD

0.1UF_0402

DACAVSS

C22

C16

C11

0.1UF_0402

0.1UF_0402

VRSET

+V1.8

L3

C5

1u

60S/0603

C196

10UF1206

R20

130R1%0402

A

MSI CORPORATION

Title

M661MX-3 (HyperZip/VGA/Misc.)

Size Document Number Rev

B

8

7

6

5

4

3

Date: Sheet

2

738Monday, June 28, 2004

1

R110

of

Page 8

8

A

M661MX-4

Power

+VCCP_NB

A17

A18

A19

A20

A21

B17

L25

VTT

L26

VTT

M18

VTT

M19

VTT

M20

VTT

M21

D D

+V2.5S_MEM

C C

B B

VTT

M22

VTT

M23

VTT

M24

VTT

M25

VTT

M26

VTT

N25

VTT

P25

VTT

R25

VTT

T25

VTT

U25

VTT

V25

VTT

W25

VTT

Y25

VTT

AA25

VTT

AL7

VDDM

AL8

VDDM

AL9

VDDM

AM6

VDDM

AM7

VDDM

AM8

VDDM

AN5

VDDM

AN6

VDDM

AN7

VDDM

AN8

VDDM

AP5

VDDM

AP6

VDDM

AP7

VDDM

AR4

VDDM

AR5

VDDM

AR6

VDDM

AR7

VDDM

AT4

VDDM

AT5

VDDM

AT6

VDDM

AT7

VDDM

AB25

VDDM

AC25

VDDM

AD12

VDDM

AD25

VDDM

AE11

VDDM

AE12

VDDM

AE13

VDDM

AE14

VDDM

AE15

VDDM

AE16

VDDM

AE17

VDDM

AE18

VDDM

AE19

VDDM

AE20

VDDM

AE21

VDDM

AE22

VDDM

AE23

VDDM

AE24

VDDM

AE25

VDDM

AE26

VDDM

AF11

VDDM

AF12

VDDM

AF25

VDDM

AF26

VDDM

AB24

PVDDM

AC13

PVDDM

AD14

PVDDM

AD16

PVDDM

AD18

PVDDM

AD20

PVDDM

AD22

PVDDM

P14

VSS

P15

VSS

P16

VSS

P17

VSS

P18

VSS

P19

VSS

P20

VSS

P21

VSS

P22

VSS

P23

VSS

R14

VSS

R15

VSS

R16

VSS

R17

VSS

R18

VSS

R19

VSS

R20

VSS

R21

VSS

R22

VSS

R23

VSS

T14

VSS

T15

VSS

T16

VSS

T17

VSS

T18

VSS

T19

VSS

T20

VSS

T21

VSS

T22

VSS

T23

VSS

U14

VSS

U15

VSS

U16

VSS

U17

VSS

U18

VSS

U19

VSS

U20

VSS

U21

VSS

U22

VSS

U23

VSS

V14

VSS

V15

VSS

V16

VSS

V17

VSS

V18

VSS

V19

VSS

V20

VSS

V21

VSS

V22

VSS

V23

VSS

W14

VSS

W15

VSS

W16

VSS

W17

VSS

W18

VSS

W19

VSS

W20

VSS

W21

VSS

W22

VSS

W23

VSS

B18

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

7

IVDD

B19

B20

B21

C17

C18

C19

C20

C21

D17

D18

D19

D20

D21

E17

E18

E19

E20

E21

F17

F18

F19

F20

F21

N13

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

N14

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

IVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y22

Y23

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AA23

AB14

AB15

AB16

VSS

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AC14

AC15

AC16

6

+V1.8

N16

N18

N19

N20

N21

N22

N23

N24

P13

P24

R24

T13

T24

U24

V13

V24

W13

W24

Y13

Y24

AA24

AB13

AC24

AD13

AD15

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

PVDD

PVDD

PVDD

PVDD

PVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AC17

AC18

AC19

AC20

AC21

VSS

VSS

VSS

VSS

AC32

AC36

AD34

AE32

AE36

AF34

AG32

AC22

AC23

PVDD

VSS

IVDD

PVDD

PVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM10

AM12

AM14

AM16

AM18

AM20

AG36

AH34

AJ32

5

+V1.8 IVDD IVDD+V3.3

AD17

AD19

AD21

AD23

AD24

N15

R13

U13

AA13

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

PVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM22

VSS

AM24

AM26

AM28

AM30

AP9

AP11

AP13

AP15

AP17

AD3

AE1

AF3

AH3

AJ1

AK3

VDDZ

VDDZ

VDDZ

VSS

VSS

VSS

AP19

AP21

AP23

AG1

AM3

W11

W12

Y11

Y12

AA12

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AP25

AP27

VSS

AP29

AP31

AP33

AP35

AT8

AT10

AT12

AT16

D4D5AM5

NCNCNC

VSS

AT18

4

U5D

L17

M17

N17

AUX_IVDD

VDD3.3

VDD3.3

VDD3.3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AT20

AT22

AT24

AT26

AT28

AT30

AT32

AT34

AUX3.3

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

AL32

+V1.8S

AB12

AC12

+3VALW

AA1

+VDDQ

AA2

AA3

AA4

AA5

AA6

AB1

AB2

AB3

AB4

AB5

AB6

AC1

AC2

AC3

AC4

AC5

AC6

L11

L12

L13

M11

M12

M13

M14

M15

M16

N11

N12

P12

R12

T12

U12

V12

B16

IVDD

C16

IVDD

D16

IVDD

E16

IVDD

F15

IVDD

E11

NC

F11

NC

F13

NC

AL33

NC

AM34

NC

A9

NC

A3

VSS

A5

VSS

C1

VSS

C3

VSS

C5

VSS

E1

VSS

E5

VSS

E7

VSS

E9

VSS

F3

VSS

G1

VSS

G5

VSS

H3

VSS

J1

VSS

J5

VSS

K3

VSS

L1

VSS

L5

VSS

M3

VSS

N1

VSS

N5

VSS

P3

VSS

R1

VSS

R5

VSS

T3

VSS

U1

VSS

U5

VSS

V3

VSS

W1

VSS

W5

VSS

Y3

VSS

AE5

VSS

AG5

VSS

AJ5

VSS

AL5

VSS

A22

VSS

A24

VSS

A26

VSS

A28

VSS

A30

VSS

A32

VSS

A34

VSS

C23

VSS

C25

VSS

C27

VSS

C29

VSS

C31

VSS

C34

VSS

C36

VSS

E22

VSS

E24

VSS

E26

VSS

E28

VSS

E30

VSS

E32

VSS

E36

VSS

F34

VSS

G32

VSS

G36

VSS

H34

VSS

J32

VSS

J36

VSS

K34

VSS

L32

VSS

L36

VSS

M34

VSS

N32

VSS

N36

VSS

P34

VSS

R32

VSS

T34

VSS

U32

VSS

U36

VSS

V34

VSS

W32

VSS

W36

VSS

Y34

VSS

AA32

VSS

AA36

VSS

AB34

VSS

VSS

M661MX

+V1.8

IVDD

+V2.5S

change to DPWR#

3

C62

10UF1206

C238

0.1UF_0402

C214

0.1UF_0402

C223

0.1UF_0402

C211

0.1UF_0402

C205

0.1UF_0402

C299

10UF1206

C296

10UF1206

C241

10UF1206

C292

10UF1206

+V3.3S

648 solder side

close to 648

and on VDDQ

plane

+V1.8

C409

0.1UF_0402

C453

10UF1206

C78

1u

C246

0.1UF_0402

C49

0.1UF_0402

C201

0.1UF_0402

C224

0.1UF_0402

C202

0.1UF_0402

C76

1u

C77

1u

C72

0.1UF_0402

C71

0.1UF_0402

+V2.5S_MEM

+V1.8S

+VDDQ

+V2.5S_MEM

Place these capacitors under 648 solder side

C250

0.1UF_0402

C98

0.1UF_0402

C248

0.1UF_0402

C244

0.1UF_0402

2

+V1.8

+VCCP

C249

1u

C245

1u

C88

0.1UF_0402

C94

0.1UF_0402

C594

10UF1206

C19

0.1UF_0402

C220

0.1UF_0402

C191

0.1UF_0402

C199

10UF1206

+VCCP_NB

C586

0.1UF_0402

C588

0.1UF_0402

C590

0.1UF_0402

C592

0.1UF_0402

C595

0.1UF_0402

C9

10UF1206

C213

0.1UF_0402

C8

10UF1206

C188

1u

C186

0.1UF_0402

+V3.3S

+VDDQ

C233

0.1UF_0402

C215

0.1UF_0402

C240

0.1UF_0402

C227

0.1UF_0402

C239

0.1UF_0402

C346

0.1UF_0402

C569

0.1UF_0402

C46

0.1UF_0402

C587

0.1UF_0402

C589

0.1UF_0402

C591

0.1UF_0402

C593

0.1UF_0402

C596

0.1UF_0402

1

+V3.3

C558

0.1UF_0402

+V1.8

C394

0.1UF_0402

C356

10UF1206

C364

1u

C374

0.1UF_0402

C367

0.1UF_0402

A

change to MA15

MSI CORPORATION

Title

M661MX-4 (Powers)

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

2

1

R110

of

838Monday, June 28, 2004

Page 9

8

A

7

6

5

4

3

2

+V1.8

1

R113

150R1%

C172

0.1UF_0402

PCI_RST-7,20,21

1 2

3 4

5 6

7 8

RN44 8.2K_8P4R

1 2

3 4

5 6

7 8

RN52 8.2K_8P4R

RN43

1 2

3 4

5 6

7 8

8.2K_8P4R

R135 4.7K

R134 4.7K

R130 4.7K

R132 4.7K

+V1.8

C420

0.1UF_0402

IDERST-24

ENAVDD17

ENAVDD-18

+V3.3

R115

14

13

12

11

10

9

8

0.1UF_0402

0.1UF_0402

0.1UF_0402

2

+V3.3

C168

C166

C399

150R1%

PCIRSTO#

PCIRST- 17,25,29

R64 X_10K

R59 X_10K

R62 X_10K

R61 X_10K

C169

0.01uF0402

C165

0.01uF0402

C404

0.01uF0402

R117

75R1%

U12

1

I1

Vcc

2

O1

I6

3

I2

O6

4

O2

I5

5

I3

O5

6

O3

I4

7

O4

GND

74LVC14

Put near 96X Chip.

only for MUTIOL 1.0 backup solution

ZSTB0

ZSTB1

ZSTB-0

ZSTB-1

Analog Power supplies of Transzip function for 96X Chip.

+V3.3

L29 0.1U220m

C507

10UF1206

+V3.3

L28 0.1U220m

C516

10UF1206

+V1.8

L46 0.1U220m

C385

10UF1206

MSI CORPORATION

Title

963-1 (PCI/IDE/HyperZip)

Size Document Number Rev

B

Date: Sheet

3

U13A

AD020,21

22P

R140

100

C174

+V3.3

AD1020,21

AD1120,21

AD1220,21

AD1320,21

AD1420,21

AD1520,21

AD1620,21

AD1720,21

AD1820,21

AD1920,21

AD2020,21

AD2120,21

AD2220,21

AD2320,21

AD2420,21

AD2520,21

AD2620,21

AD2720,21

AD2820,21

AD2920,21

AD3020,21

AD3120,21

PREQ-120

PREQ-021

PGNT-120

PGNT-021

INT-A7,17,21

INT-B20,21

INT-C20,21

FRAME-20,21

IRDY-20,21

TRDY-20,21

STOP-20,21

SERR-20,21

DEVSEL-20,21

96XPCLK

ZCLK113

AD120,21

AD220,21

AD320,21

AD420,21

AD520,21

AD620,21

AD720,21

AD820,21

AD920,21

PAR20,21

pull hi

R129 4.7K

R133 4.7K

R128 4.7K

PREQ-1

PREQ-0

PGNT-1

PGNT-0

C/BE-3

C/BE-2

C/BE-1

C/BE-0

INT-A

INT-B

INT-C

INT-D

FRAMEIRDYTRDYSTOP-

SERRPAR

DEVSELPLOCK-

PCIRSTO#

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

SZVREF

ZCLK1

R372

100

C430

22P

D D

C C

C/BE-[0..3]20,21

B B

96XPCLK13

ZAD[0..16]7

8

V1

AD0

U3

AD1

R5

AD2

T3

AD3

U2

AD4

U1

AD5

T2

AD6

P5

AD7

T1

AD8

R1

AD9

R3

AD10

R2

AD11

P4

AD12

P3

AD13

P2

AD14

N5

AD15

L2

AD16

L5

AD17

L4

AD18

L1

AD19

K1

AD20

L3

AD21

K2

AD22

K5

AD23

J1

AD24

J2

AD25

K4

AD26

J3

AD27

H1

AD28

H2

AD29

J4

AD30

J5

AD31

F1

PREQ4#

F2

PREQ3#

E1

PREQ2#

H5

PREQ1#

F3

PREQ0#

H3

PGNT4#

G1

PGNT3#

G2

PGNT2#

G3

PGNT1#

H4

PGNT0#

K3

C/BE3#

M4

C/BE2#

P1

C/BE1#

R4

C/BE0#

E3

INTA#

F4

INTB#

E2

INTC#

G4

INTD#

M3

FRAME#

M1

IRDY#

M2

TRDY#

N4

STOP#

M5

SERR#

N3

PAR

N1

DEVSEL#

N2

PLOCK#

Y2

PCICLK

C3

PCIRST#

M18

ZAD0

N19

ZAD1

M17

ZAD2

M16

ZAD3

M20

ZAD4

L16

ZAD5

L20

ZAD6

L18

ZAD7

K18

ZAD8

K19

ZAD9

K17

ZAD10

K16

ZAD11

H20

ZAD12

J18

ZAD13

H19

ZAD14

H18

ZAD15

P20

ZAD16

R20

ZVREF

V20 M19

ZCLK ZSTB0

7

PCI Interface

IDE Interface

HyperZip

6

IDEAVDD

IDEAVSS

ICHRDYA

IDREQA

IIRQA

CBLIDA

IIORA#

IIOWA#

IDACKA#

IDSAA2

IDSAA1

IDSAA0

IDECSA1#

IDECSA0#

ICHRDYB

IDREQB

IIRQB

CBLIDB

IIORB#

IIOWB#

IDACKB#

IDSAB2

IDSAB1

IDSAB0

IDECSB1#

IDECSB0#

IDA0

IDA1

IDA2

IDA3

IDA4

IDA5

IDA6

IDA7

IDA8

IDA9

IDA10

IDA11

IDA12

IDA13

IDA14

IDA15

IDB0

IDB1

IDB2

IDB3

IDB4

IDB5

IDB6

IDB7

IDB8

IDB9

IDB10

IDB11

IDB12

IDB13

IDB14

IDB15

Z4XAVSS

Z4XAVDD

Z1XAVSS

Z1XAVDD

VSSZCMP

ZCMP_P

ZCMP_N

VDDZCMP

ZDREQ

ZUREQ

ZSTB1#

ZSTB1

ZSTB0#

SIS-963L

Y3

Y4

W10

V10

Y11

U12

V11

Y9

Y10

T11

U11

W11

T12

V12

W17

Y17

T16

U17

T14

W16

V16

Y18

T15

V17

U16

W18

U10

V9

W8

T9

Y7

V7

Y6

Y5

W6

U8

W7

V8

U9

Y8

T10

W9

Y16

V15

U14

W14

V13

T13

Y13

Y12

W12

W13

U13

Y14

V14

W15

Y15

U15

T19

T20

U19

U20

P18

R18

N18

R19

N17

N16

K20

J20

N20

5

ICHRDYA

IDEREQA

IDEIRQA

CBLIDA

IDEIOR-A

IDEIOW-A

IDACK-A

IDESAA2

IDESAA1

IDESAA0

IDECS-A1

IDECS-A0

ICHRDYB

IDEREQB

IDEIRQB

CBLIDB

IDEIOR-B

IDEIOW-B

IDACK-B

IDESAB2

IDESAB1

IDESAB0

IDECS-B1

IDECS-B0

IDEDA0

IDEDA1

IDEDA2

IDEDA3

IDEDA4

IDEDA5

IDEDA6

IDEDA7

IDEDA8

IDEDA9

IDEDA10

IDEDA11

IDEDA12

IDEDA13

IDEDA14

IDEDA15

IDEDB0

IDEDB1

IDEDB2

IDEDB3

IDEDB4

IDEDB5

IDEDB6

IDEDB7

IDEDB8

IDEDB9

IDEDB10

IDEDB11

IDEDB12

IDEDB13

IDEDB14

IDEDB15

SZ4XAVSS

SZ4XAVDD

SZ1XAVSS

SZ1XAVDD

SVSSZCMP

SZCMP_P

SZCMP_N

SVDDZCMP

ZDREQ

ZUREQ

ZSTB-1

ZSTB1

ZSTB-0

ZSTB0

ICHRDYA 24

IDEREQA 24

IDEIRQA 24

CBLIDA 24

IDEIOR-A 24

IDEIOW-A 24

IDACK-A 24

ICHRDYB 24

IDEREQB 24

IDEIRQB 24

CBLIDB 24

IDEIOR-B 24

IDEIOW-B 24

IDACK-B 24

ZDREQ 7

ZUREQ 7

ZSTB-1 7

ZSTB1 7

ZSTB-0 7

ZSTB0 7

C171

0.01uF0402

IDESAA[0..2] 24

IDECS-A[0..1] 24

IDESAB[0..2] 24

IDECS-B[0..1] 24

IDEDA[0..15] 24

IDEDB[0..15] 24

FRAMEIRDYTRDYDEVSEL-

STOPPLOCK-

SERR-

INT-D

INT-A

INT-B

INT-C

PGNT-1

PREQ-1

PREQ-0

PGNT-0

4

C163

0.1UF_0402

SZVREF

C164

0.1UF_0402

+V1.8

SZ1XAVDD

SZ1XAVSS

SZ4XAVDD

SZ4XAVSS

R364 56R0402

R362 56R0402

SVDDZCMP

SZCMP_N

SZCMP_P

SVSSZCMP

of

938Monday, June 28, 2004

1

R110

A

Page 10

8

A

D D

REFCLK1

R450

100

C C

P_CLKRUN-

SMBALT-

Place near to 96X

BIT_CLK

C555

22P

R141X_10K

R33810K

R353

0 ohm stuff or not ?

X_0

B B

+V3.3S

PME-

R1104.7K0402

BAT1

C173

7

PROCHOT-3

THERMTRIP-3

LAD[0..3]25,29

SDATI030

SDATI126

SDATO11,26,30

SYNC26,30

AC_RESET-26,30

BIT_CLK26,30

DELAY_IMVP_PWRGD7,30,37

+V3.3

+V3.3S

10p

+3VALW RTCVDD

1

2

Programable on-die pull-high strength for CPU_S:

( Infinite, 150, 110, 56 Ohm)

INIT-3,29

A20M-3

SMI-3

INTR3

NMI3

IGNNE-3

FERR-3

STPCLK-3

CPUSLP-3

+V3.3

S-BAT54C_SOT23

R127 10K

LAD0

LAD1

LAD2

LAD3

LFRAME-25,29

SIRQ21,25

SDATI0

SDATI1

SDATO

SYNC

AC_RESETBIT_CLK

REFCLK113

SPKR11,30

PWRSW-25,28

PME-20,21

PSON-25

AUXOK7,27

RTCVDD

OSC32KHI

OSC32KHO

D25

3

INIT-

A20MSMIINTR

NMI

IGNNEFERRSTPCLKCPUSLP-

LFRAMELDRQSIRQ

REFCLK1

SENTEST

SPKR

PMEPSON-

AUXOK

BATOK

SBPWRGD

6

T18

INIT#

P16

A20M#

R17

SMI#

R16

INTR

Y20

NMI

U18

IGNNE#

T17

FERR#

W20

STPCLK#

V19

CPUSLP#

Y19

APICCK/LDTREQ#

V18

APICD0/THERM2#

W19

APICD1/GPIOFF#

V5

LAD0

T7

LAD1

U6

LAD2

W5

LAD3

W4

LFRAME#

U7

LDRQ#

V6

SIRQ

A2

AC_SDIN0

D5

AC_SDIN1

W2

AC_SDOUT

T5

AC_SYNC

D6

AC_RESET#

Y1

AC_BIT_CLK

W3

OSCI

G5

ENTEST

V3

SPK

A14

PWRBTN#

B14

PME#

D14

PSON#

ACPI/OTHER

A3

AUXOK

A15

ACPILED

D3

BATOK

D1

PWROK

C1

RTCVDD

E4

RTCVSS

C2

OSC32KHI

D2

OSC32KHO

Put closed to 963 CHIP

MCLK25O

MCLK25I

R474

10K

R116 X_1M

1 2

25MHZ18P_D-1

C162

15P

HOST

APIC

LPC

AC LINK

RTC

X2

C160

20P

BATOK

5

GPIO1/LDRQ1#

GPIO2/THERM#

GPIO3/EXTSMI#

GPIO4/CLKRUN#

GPIO5/PREQ5#

GPIO6/PGNT5#

GPIO8/RING

GPIO9/AC_SDIN2

GPIO10/AC_SDIN3

GPIO11/OSC25M/STP_PCI#

GPIOMAC CONTROLLER

GPIO12/CPUSTP#

GPIO13/DPRSLPVR

GPIO15/VR_HILO#

GPIO16/LO_HI#

GPIO17/PMDAT

GPIO18/PMCLK

GPIO0

GPIO7

GPIO14

GPIO19

GPIO20

TXCLK

TXEN

TXD0

TXD1

TXD2

TXD3

RXER

RXCLK

RXDV

RXD0

RXD1

RXD2

RXD3

COL

CRS

MDC

MDIO

MIIAVDD

MIIAVSS

OSC25MHI

OSC25MHO

U13B

SIS-963L

4

V2

T8

T4

T6

W1

U5

U4

C4

C14

E6

B3

F5

D4

B1

E5

E13

A16

D13

B15

A1

B2

A6

B6

E8

D7

C6

B4

C8

A7

C7

D8

A5

B5

A4

B7

E9

C5

E7

B9

B8

A8

A9

LDRQ1THERMEXTSMIP_CLKRUNMSI_WLAN_DETECTGPIO6

SMBALT-

GPIO11

CPUSTPDPRSLPVR

GPIO15

GPIO18

SMBCLK

SMBDAT

Put closed to 963 CHIP

R350 22

R331 22

MIIAVDD

MIIAVSS

MCLK25I

MCLK25O

R120 22

R118 22

R119 22

R346 22

R122 22

+V3.3

R351

4.7K

DDR2_6V 34

PANELID1 18

SMBCLK 13,14,15

SMBDAT 13,14,15

R121

24.3KR1%

N-MMBT3904_SOT23

(To PWM regulator)

AUXOK

C167

0.1UF_0402

SBPWRGD

C170

0.1UF_0402

3

ENBLT 18

CPU_THRM_ALERT- 27

EXTSMI- 25

P_CLKRUN- 20

MSI_WLAN_DETECT- 28

PANELID0 18

1394_SUSP- 21

KBSCI- 25

1

TP16

.

TXCLK 19

TXEN 19

TXD0 19

TXD1 19

TXD2 19

TXD3 19

RXER 19

RXCLK 19

RXDV 19

RXD0 19

RXD1 19

RXD2 19

RXD3 19

COL 19

CRS 19

MDC 19

MDIO 19

H_DPSLP# 3

Ic=200mA

Q10

Vebo=6V

Vceo=40V

CPUSTP- 13,37

2

Put closed to 96X CHIP

OSC32KHO

OSC32KHI

NEED NOT to place

close to 96X

LAD1

LAD0

LAD3

LAD2

LDRQLDRQ1SIRQ

EXTSMISENTEST

GPIO pins pull down

NEED NOT to place

close to 96X

THERMMSI_WLAN_DETECTCPUSTPSMBDAT

SMBCLK

GPIO18

GPIO11

GPIO6

KBSCI-

GPIO15

MIIAVDD

MIIAVSS

Analog power of MII

R390 10M

32K-12.5pf-S

C456

15p

RN8SMDA

RN45

1 2

3 4

5 6

7 8

X_8.2K_8P4R

R426 0R

C159

C161

0.1UF_0402

0.01uF0402

1

X5

14

23

+V3.3

R429X_4.7K0402

R4054.7K0402

R136X_4.7K0402

R4404.7K0402

+V3.3

R138X_4.7K0402

R1374.7K0402

R363X_4.7K0402

R1254.7K0402

R1264.7K0402

R1094.7K0402

R1314.7K0402

R1394.7K0402

+V3.3S

R1244.7K0402

R112X_4.7K0402

+V3.3S

L27 0.1U220m

C489

20P

C373

10UF1206

5

+V3.3S

D11

AC

1N4148_SOD123

R244 1K

R250

100K

4

AUXOK

C321

22uF1206

THERM_FAIL# 7,27

A

Title

Size Document Number Rev

Custom

Date: Sheet

3

MSI CORPORATION

963-2 (LPC/MII/GPIO)

2

R110

of

10 38Monday, June 28, 2004

1

C567

RTC_BAT

8

7

R477

10K

1

2

3 4

CN13

BH1X2S_white-1.25pitch

1u

6

C568

10UF1206

Page 11

8

A

7

6

5

4

3

2

1

U13C

C16

IVDD_AUX

C17

IVDD_AUX

B20

A18

USBPVDD

C15

USBPVSS

F19

USBVSS

E19

USBVSS

B19

USBVSS

B17

USBVSS

D16

USBVDD

D17

USBVDD

E17

USBVDD

F17

USBVDD

E11

NC

C19

NC

A19

NC

A20

NC

B11

NC

D10

NC

A11

NC

E10

NC

D9

NC

C10

NC

C9

NC

A12

NC

B12

NC

C12

NC

D12

NC

E12

NC

A13

NC

B13

NC

C13

NC

D11

NC

C11

NC

SIS-963L

C156

C152

1u

10UF1206 C359

22P

R448

100

C554

UCLK48M

UV0+28

UV0-28

UV1+28

UV1-28

UV2+28

UV2-28

OC0-28

OC1-28

OC2-28

R311

412_1%

GPIO24

GPIO23

GPIO22

GPIO21

OSC12MHI

OSC12MHO

D D

UCLK48M13

C C

UV0+

UV0-

UV1+

UV1-

UV2+

UV2-

UV3+

UV3-

UV4+

UV4-

UV5+

UV5-

OC0OC1OC2OC3OC4OC5-

USBREF

V4

USBCLK48M

B18

UV0+

C18

UV0-

D18

UV1+

D19

UV1-

E14

UV2+